Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFI

| Product Status             | Active                                                                         |

|----------------------------|--------------------------------------------------------------------------------|

| Core Processor             | MIPS32® M4K™                                                                   |

| Core Size                  | 32-Bit Single-Core                                                             |

| Speed                      | 80MHz                                                                          |

| Connectivity               | Ethernet, I <sup>2</sup> C, SPI, UART/USART, USB OTG                           |

| Peripherals                | Brown-out Detect/Reset, DMA, POR, PWM, WDT                                     |

| Number of I/O              | 53                                                                             |

| Program Memory Size        | 64KB (64K x 8)                                                                 |

| Program Memory Type        | FLASH                                                                          |

| EEPROM Size                | -                                                                              |

| RAM Size                   | 32K x 8                                                                        |

| Voltage - Supply (Vcc/Vdd) | 2.3V ~ 3.6V                                                                    |

| Data Converters            | A/D 16x10b                                                                     |

| Oscillator Type            | Internal                                                                       |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                              |

| Mounting Type              | Surface Mount                                                                  |

| Package / Case             | 64-VFQFN Exposed Pad                                                           |

| Supplier Device Package    | 64-VQFN (9x9)                                                                  |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic32mx664f064h-i-mr |

|                            |                                                                                |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

1

#### TABLE 9: PIN NAMES FOR 100-PIN USB, ETHERNET, AND CAN DEVICES (CONTINUED)

#### **100-PIN TQFP (TOP VIEW)**

PIC32MX764F128L PIC32MX775F256L PIC32MX775F512L PIC32MX795F512L

100

| Pin # | Full Pin Name                   | Pin # | Full Pin Name                        |

|-------|---------------------------------|-------|--------------------------------------|

| 71    | EMDC/AEMDC/IC4/PMCS1/PMA14/RD11 | 86    | VDD                                  |

| 72    | SDO1/OC1/INT0/RD0               | 87    | C1RX/ETXD1/PMD11/RF0                 |

| 73    | SOSCI/CN1/RC13                  | 88    | C1TX/ETXD0/PMD10/RF1                 |

| 74    | SOSCO/T1CK/CN0/RC14             | 89    | C2TX <sup>(1)</sup> /ETXERR/PMD9/RG1 |

| 75    | Vss                             | 90    | C2RX <sup>(1)</sup> /PMD8/RG0        |

| 76    | OC2/RD1                         | 91    | TRCLK/RA6                            |

| 77    | OC3/RD2                         | 92    | TRD3/RA7                             |

| 78    | OC4/RD3                         | 93    | PMD0/RE0                             |

| 79    | ETXD2/IC5/PMD12/RD12            | 94    | PMD1/RE1                             |

| 80    | ETXD3/PMD13/CN19/RD13           | 95    | TRD2/RG14                            |

| 81    | OC5/PMWR/CN13/RD4               | 96    | TRD1/RG12                            |

| 82    | PMRD/CN14/RD5                   | 97    | TRD0/RG13                            |

| 83    | ETXEN/PMD14/CN15/RD6            | 98    | PMD2/RE2                             |

| 84    | ETXCLK/PMD15/CN16/RD7           | 99    | PMD3/RE3                             |

| 85    | VCAP/VDDCORE                    | 100   | PMD4/RE4                             |

Note 1: This pin is not available on PIC32MX764F128L devices.

2: Shaded pins are 5V tolerant.

## 2.5 ICSP Pins

The PGECx and PGEDx pins are used for In-Circuit Serial Programming<sup>TM</sup> (ICSP<sup>TM</sup>) and debugging. It is recommended to keep the trace length between the ICSP connector and the ICSP pins on the device as short as possible. If the ICSP connector is expected to experience an ESD event, a series resistor is recommended, with the value in the range of a few tens of Ohms, not to exceed 100 Ohms.

Pull-up resistors, series diodes and capacitors on the PGECx and PGEDx pins are not recommended as they will interfere with the programmer/debugger communications to the device. If such discrete components are an application requirement, they should be removed from the circuit during programming and debugging. Alternatively, refer to the AC/DC characteristics and timing requirements information in the respective device Flash programming specification for information on capacitive loading limits and pin input voltage high (VIH) and input low (VIL) requirements.

Ensure that the "Communication Channel Select" (i.e., PGECx/PGEDx pins) programmed into the device matches the physical connections for the ICSP to MPLAB<sup>®</sup> ICD 3 or MPLAB<sup>®</sup> REAL ICE<sup>TM</sup>.

For more information on ICD 3 and REAL ICE connection requirements, refer to the following documents that are available on the Microchip web site.

- "Using MPLAB<sup>®</sup> ICD 3" (poster) (DS50001765)

- "MPLAB<sup>®</sup> ICD 3 Design Advisory" (DS50001764)

- "MPLAB<sup>®</sup> REAL ICE<sup>™</sup> In-Circuit Emulator User's Guide" (DS50001616)

- "Using MPLAB<sup>®</sup> REAL ICE™ Emulator" (poster) (DS50001749)

### 2.6 JTAG

The TMS, TDO, TDI and TCK pins are used for testing and debugging according to the Joint Test Action Group (JTAG) standard. It is recommended to keep the trace length between the JTAG connector and the JTAG pins on the device as short as possible. If the JTAG connector is expected to experience an ESD event, a series resistor is recommended, with the value in the range of a few tens of Ohms, not to exceed 100 Ohms.

Pull-up resistors, series diodes and capacitors on the TMS, TDO, TDI and TCK pins are not recommended as they will interfere with the programmer/debugger communications to the device. If such discrete components are an application requirement, they should be removed from the circuit during programming and debugging. Alternatively, refer to the AC/DC characteristics and timing requirements information in the respective device Flash programming specification for information on capacitive loading limits and pin input voltage high (VIH) and input low (VIL) requirements.

# 2.7 Trace

The trace pins can be connected to a hardware-traceenabled programmer to provide a compress real time instruction trace. When used for trace the TRD3, TRD2, TRD1, TRD0 and TRCLK pins should be dedicated for this use. The trace hardware requires a  $22\Omega$  series resistor between the trace pins and the trace connector.

# 2.8 External Oscillator Pins

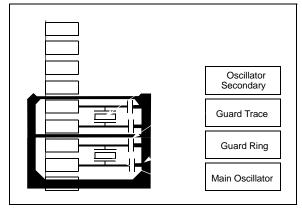

Many MCUs have options for at least two oscillators: a high-frequency primary oscillator and a low-frequency secondary oscillator. Refer to **Section 8.0 "Oscillator Configuration"** for details.

The oscillator circuit should be placed on the same side of the board as the device. Also, place the oscillator circuit close to the respective oscillator pins, not exceeding one-half inch (12 mm) distance between them. The load capacitors should be placed next to the oscillator itself, on the same side of the board. Use a grounded copper pour around the oscillator circuit to isolate them from surrounding circuits. The grounded copper pour should be routed directly to the MCU ground. Do not run any signal traces or power traces inside the ground pour. Also, if using a two-sided board, avoid any traces on the other side of the board where the crystal is placed. A suggested layout is illustrated in Figure 2-3.

#### FIGURE 2-3: SUGGESTED OSCILLATOR CIRCUIT PLACEMENT

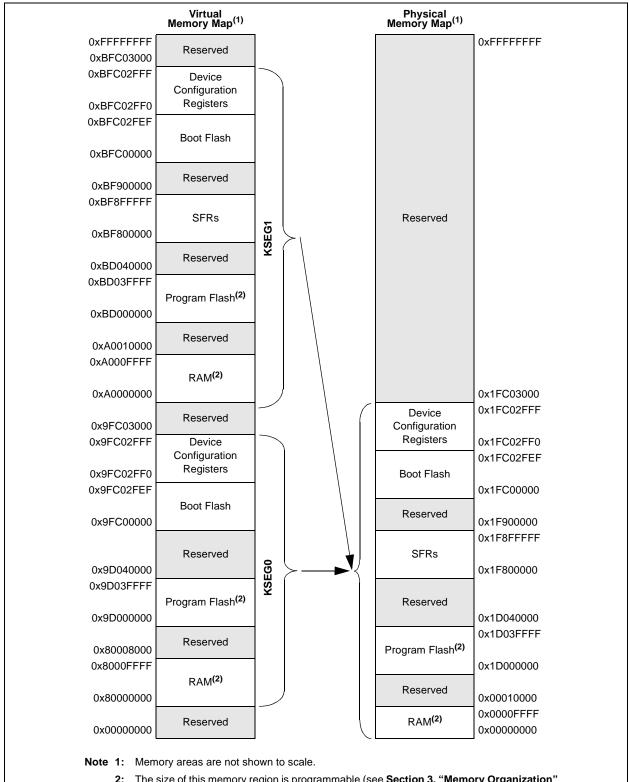

#### FIGURE 4-4: MEMORY MAP ON RESET FOR PIC32MX575F256H, PIC32MX575F256L, PIC32MX675F256H, PIC32MX675F256L, PIC32MX775F256H AND PIC32MX775F256L DEVICES

2: The size of this memory region is programmable (see Section 3. "Memory Organization" (DS60001115)) and can be changed by initialization code provided by end user development tools (refer to the specific development tool documentation for information).

#### REGISTER 10-14: DCHxSPTR: DMA CHANNEL 'x' SOURCE POINTER REGISTER

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|--|

| 31:24        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |  |

| 31.24        |                   | —                 | _                 |                   | _                 | _                 |                  |                  |  |

| 23:16        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |  |

| 23.10        |                   | —                 | _                 | _                 | _                 | _                 | —                | —                |  |

| 45.0         | R-0               | R-0               | R-0               | R-0               | R-0               | R-0               | R-0              | R-0              |  |

| 15:8         | CHSPTR<15:8>      |                   |                   |                   |                   |                   |                  |                  |  |

| 7:0          | R-0               | R-0               | R-0               | R-0               | R-0               | R-0               | R-0              | R-0              |  |

|              |                   |                   |                   | CHSPTF            | R<7:0>            |                   |                  |                  |  |

### Legend:

| Logona.                           |                  |                                    |                    |  |  |

|-----------------------------------|------------------|------------------------------------|--------------------|--|--|

| R = Readable bit W = Writable bit |                  | U = Unimplemented bit, read as '0' |                    |  |  |

| -n = Value at POR                 | '1' = Bit is set | '0' = Bit is cleared               | x = Bit is unknown |  |  |

#### bit 31-16 Unimplemented: Read as '0'

bit 15-0 CHSPTR<15:0>: Channel Source Pointer bits

111111111111111 = Points to byte 65,535 of the source

Note: When in Pattern Detect mode, this register is reset on a pattern detect.

#### Bit Bit Bit Bit Bit Bit Bit Bit Bit Range 31/23/15/7 30/22/14/6 29/21/13/5 28/20/12/4 27/19/11/3 26/18/10/2 25/17/9/1 24/16/8/0 U-0 U-0 U-0 U-0 U-0 U-0 U-0 U-0 31:24 \_\_\_\_ \_\_\_ \_\_\_\_ \_\_\_\_ \_\_\_\_ \_\_\_\_ U-0 U-0 U-0 U-0 U-0 U-0 U-0 U-0 23:16 R-0 R-0 R-0 R-0 R-0 R-0 R-0 R-0 15:8 CHDPTR<15:8> R-0 R-0 R-0 R-0 R-0 R-0 R-0 R-0 7:0 CHDPTR<7:0>

### **REGISTER 10-15: DCHxDPTR: DMA CHANNEL 'x' DESTINATION POINTER REGISTER**

#### Legend:

| R = Readable bit W = Writable bit |                  | U = Unimplemented bit, read as '0' |                    |  |  |

|-----------------------------------|------------------|------------------------------------|--------------------|--|--|

| -n = Value at POR                 | '1' = Bit is set | '0' = Bit is cleared               | x = Bit is unknown |  |  |

bit 31-16 Unimplemented: Read as '0'

bit 15-0 CHDPTR<15:0>: Channel Destination Pointer bits

111111111111111 = Points to byte 65,535 of the destination

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1      | Bit<br>24/16/8/0 |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|-----------------------|------------------|

| 24.24        | U-0                   | U-0              |

| 31:24        |                   | _                 | _                 | _                 | —                 | —                 | _                     | —                |

| 22.10        | U-0                   | U-0              |

| 23:16        | _                 | _                 | _                 | _                 | _                 | —                 | _                     | —                |

| 15:8         | U-0                   | U-0              |

| 10.0         |                   | _                 | _                 | _                 | —                 | —                 | _                     | —                |

|              | R/W-0                 | R/W-0            |

| 7:0          | DTOFF             | BTSEE BMXEE DMA   | DMAEE             | BTOEF             |                   |                   | CRC5EE <sup>(1)</sup> | DIDEE            |

|              | DISEE             |                   | DIVIAEE           | BTOEE             | DFN8EE            | CRC16EE           | EOFEE <sup>(2)</sup>  | PIDEE            |

### REGISTER 11-9: U1EIE: USB ERROR INTERRUPT ENABLE REGISTER

#### Legend:

| 5                 |                  |                          |                    |

|-------------------|------------------|--------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, r | ead as '0'         |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared     | x = Bit is unknown |

| bit 31-8 | Unimplemented: Read as '0'                                                               |

|----------|------------------------------------------------------------------------------------------|

| bit 7    | BTSEE: Bit Stuff Error Interrupt Enable bit                                              |

|          | <ul><li>1 = BTSEF interrupt is enabled</li><li>0 = BTSEF interrupt is disabled</li></ul> |

| bit 6    | BMXEE: Bus Matrix Error Interrupt Enable bit                                             |

|          | 1 = BMXEF interrupt is enabled                                                           |

|          | 0 = BMXEF interrupt is disabled                                                          |

| bit 5    | DMAEE: DMA Error Interrupt Enable bit                                                    |

|          | <ul><li>1 = DMAEF interrupt is enabled</li><li>0 = DMAEF interrupt is disabled</li></ul> |

| bit 4    | BTOEE: Bus Turnaround Time-out Error Interrupt Enable bit                                |

|          | 1 = BTOEF interrupt is enabled                                                           |

- 0 = BTOEF interrupt is disabled

- bit 3 DFN8EE: Data Field Size Error Interrupt Enable bit

- 1 = DFN8EF interrupt is enabled

- 0 = DFN8EF interrupt is disabled

- bit 2 CRC16EE: CRC16 Failure Interrupt Enable bit

- 1 = CRC16EF interrupt is enabled

- 0 = CRC16EF interrupt is disabled

- CRC5EE: CRC5 Host Error Interrupt Enable bit<sup>(1)</sup> bit 1

- 1 = CRC5EF interrupt is enabled

- 0 = CRC5EF interrupt is disabled

- EOFEE: EOF Error Interrupt Enable bit<sup>(2)</sup>

- 1 = EOF interrupt is enabled

- 0 = EOF interrupt is disabled

- bit 0 PIDEE: PID Check Failure Interrupt Enable bit

- 1 = PIDEF interrupt is enabled

- 0 = PIDEF interrupt is disabled

- Note 1: Device mode.

- 2: Host mode.

Note: For an interrupt to propagate USBIF, the UERRIE bit (U1IE<1>) must be set.

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|

| 21.24        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 31:24        |                   | —                 | -                 | -                 | _                 | _                 | —                | —                |

| 23:16        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 23.10        | —                 | —                 | _                 | _                 | —                 | _                 | -                | —                |

| 15.0         | R/W-0             | U-0               | R/W-0             | R/W-0             | R-0               | U-0               | U-0              | U-0              |

| 15:8         | ON <sup>(1)</sup> | —                 | SIDL              | TWDIS             | TWIP              | -                 |                  | —                |

| 7.0          | R/W-0             | U-0               | R/W-0             | R/W-0             | U-0               | R/W-0             | R/W-0            | U-0              |

| 7:0          | TGATE             | —                 | TCKPS             | S<1:0>            | _                 | TSYNC             | TCS              | —                |

#### REGISTER 13-1: T1CON: TYPE A TIMER CONTROL REGISTER

#### Legend:

| R = Readable bit $W = Writable bit$ |                  | U = Unimplemented bit, read as '0' |                    |  |

|-------------------------------------|------------------|------------------------------------|--------------------|--|

| -n = Value at POR                   | '1' = Bit is set | '0' = Bit is cleared               | x = Bit is unknown |  |

#### bit 31-16 Unimplemented: Read as '0'

- bit 15 **ON:** Timer On bit<sup>(1)</sup>

- 1 = Timer is enabled 0 = Timer is disabled

#### bit 14 Unimplemented: Read as '0'

#### bit 13 **SIDL:** Stop in Idle Mode bit

- 1 = Discontinue operation when device enters Idle mode

- 0 = Continue operation when device is in Idle mode

# bit 12 **TWDIS:** Asynchronous Timer Write Disable bit

- 1 = Writes to TMR1 are ignored until pending write operation completes

- 0 = Back-to-back writes are enabled (Legacy Asynchronous Timer functionality)

#### bit 11 TWIP: Asynchronous Timer Write in Progress bit

In Asynchronous Timer mode:

1 = Asynchronous write to TMR1 register in progress

0 = Asynchronous write to TMR1 register complete

In Synchronous Timer mode:

This bit is read as '0'.

- bit 10-8 **Unimplemented:** Read as '0'

- bit 7 TGATE: Timer Gated Time Accumulation Enable bit

<u>When TCS = 1:</u> This bit is ignored.

When TCS = 0:

- 1 = Gated time accumulation is enabled

- 0 =Gated time accumulation is disabled

- bit 6 Unimplemented: Read as '0'

- bit 5-4 TCKPS<1:0>: Timer Input Clock Prescale Select bits

- 11 = 1:256 prescale value

- 10 = 1:64 prescale value

- 01 = 1:8 prescale value

- 00 = 1:1 prescale value

- **Note 1:** When using the 1:1 PBCLK divisor, the user's software should not read/write the peripheral SFRs in the SYSCLK cycle immediately following the instruction that clears the module's ON bit.

| Bit<br>Range | Bit<br>31/23/15/7   | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

|--------------|---------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|

| 04.04        | U-0                 | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 31:24        |                     |                   |                   |                   | _                 |                   | _                | —                |

| 00.40        | U-0                 | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 23:16        | _                   | _                 | _                 |                   | —                 | —                 | _                | —                |

| 45.0         | R/W-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 15:8         | ON <sup>(1,2)</sup> |                   | _                 | —                 | —                 | —                 | —                | —                |

| 7.0          | U-0                 | R-y               | R-y               | R-y               | R-y               | R-y               | R/W-0            | R/W-0            |

| 7:0          | _                   | SWDTPS<4:0>       |                   |                   |                   |                   | WDTWINEN         | WDTCLR           |

#### REGISTER 15-1: WDTCON: WATCHDOG TIMER CONTROL REGISTER

| Legend:           | y = Values set from Configuration bits on POR |                                    |                    |  |  |  |

|-------------------|-----------------------------------------------|------------------------------------|--------------------|--|--|--|

| R = Readable bit  | W = Writable bit                              | U = Unimplemented bit, read as '0' |                    |  |  |  |

| -n = Value at POR | '1' = Bit is set                              | '0' = Bit is cleared               | x = Bit is unknown |  |  |  |

bit 31-16 Unimplemented: Read as '0'

bit 0

- bit 15 **ON:** Watchdog Timer Enable bit<sup>(1,2)</sup>

- 1 = Enables the WDT if it is not enabled by the device configuration 0 = Disable the WDT if it was enabled in software

- bit 14-7 **Unimplemented:** Read as '0'

- bit 6-2 **SWDTPS<4:0>:** Shadow Copy of Watchdog Timer Postscaler Value from Device Configuration bits On reset, these bits are set to the values of the WDTPS <4:0> Configuration bits.

- bit 1 WDTWINEN: Watchdog Timer Window Enable bit

- 1 = Enable windowed Watchdog Timer

- 0 = Disable windowed Watchdog Timer

- WDTCLR: Watchdog Timer Reset bit

- 1 = Writing a '1' will clear the WDT

- 0 = Software cannot force this bit to a '0'

- Note 1: A read of this bit results in a '1' if the Watchdog Timer is enabled by the device configuration or software.

- 2: When using the 1:1 PBCLK divisor, the user's software should not read or write the peripheral's SFRs in the SYSCLK cycle immediately following the instruction that clears the module's ON bit.

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0      |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|-----------------------|

| 24.24        | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0                 |

| 31:24        | FRMEN             | FRMSYNC           | FRMPOL            | MSSEN             | FRMSYPW           | F                 | RMCNT<2:0        | >                     |

| 00.40        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | R/W-0            | R/W-0                 |

| 23:16        | _                 | —                 | _                 | —                 | —                 |                   | SPIFE            | ENHBUF <sup>(2)</sup> |

| 15.0         | R/W-0             | U-0               | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0                 |

| 15:8         | 0N <sup>(1)</sup> | —                 | SIDL              | DISSDO            | MODE32            | MODE16            | SMP              | CKE <sup>(3)</sup>    |

| 7.0          | R/W-0             | R/W-0             | R/W-0             | U-0               | R/W-0             | R/W-0             | R/W-0            | R/W-0                 |

| 7:0          | SSEN              | CKP               | MSTEN             |                   | STXISE            | L<1:0>            | SRXIS            | EL<1:0>               |

#### REGISTER 18-1: SPIxCON: SPI CONTROL REGISTER

#### Legend:

| F  | R = Readable bit | W = Writable bit | U = Unimplemented bit, re | ad as '0'          |

|----|------------------|------------------|---------------------------|--------------------|

| -1 | n = Value at POR | '1' = Bit is set | '0' = Bit is cleared      | x = Bit is unknown |

| bit 31 | FRMEN: Framed SPI Support | bit |

|--------|---------------------------|-----|

|        |                           | Dir |

- 1 = Framed SPI support is enabled (SSx pin used as FSYNC input/output)

- 0 = Framed SPI support is disabled

- bit 30 **FRMSYNC:** Frame Sync Pulse Direction Control on SSx pin bit (only Framed SPI mode) 1 = Frame sync pulse input (Slave mode)

- 0 = Frame sync pulse output (Master mode)

- bit 29 **FRMPOL:** Frame Sync Polarity bit (only Framed SPI mode)

- 1 = Frame pulse is active-high

- 0 = Frame pulse is active-low

- bit 28 MSSEN: Master Mode Slave Select Enable bit

- 1 = Slave select SPI support enabled. The SS pin is automatically driven during transmission in Master mode. Polarity is determined by the FRMPOL bit.

- 0 = Slave select SPI support is disabled.

- bit 27 FRMSYPW: Frame Sync Pulse Width bit

- 1 = Frame sync pulse is one character wide

- 0 = Frame sync pulse is one clock wide

- bit 26-24 **FRMCNT<2:0>:** Frame Sync Pulse Counter bits. Controls the number of data characters transmitted per pulse. This bit is only valid in Framed Sync mode.

- 111 = Reserved

- 110 = Reserved

- 101 = Generate a frame sync pulse on every 32 data characters

- 100 = Generate a frame sync pulse on every 16 data characters

- 011 = Generate a frame sync pulse on every 8 data characters

- 010 = Generate a frame sync pulse on every 4 data characters

- 001 = Generate a frame sync pulse on every 2 data characters

- 000 = Generate a frame sync pulse on every data character

- bit 23-18 Unimplemented: Read as '0'

- bit 17 SPIFE: Frame Sync Pulse Edge Select bit (only Framed SPI mode)

- 1 = Frame synchronization pulse coincides with the first bit clock

- 0 = Frame synchronization pulse precedes the first bit clock

- bit 16 ENHBUF: Enhanced Buffer Enable bit<sup>(2)</sup>

- 1 = Enhanced Buffer mode is enabled

- 0 = Enhanced Buffer mode is disabled

- **Note 1:** When using the 1:1 PBCLK divisor, the user's software should not read or write the peripheral's SFRs in the SYSCLK cycle immediately following the instruction that clears the module's ON bit.

- **2:** This bit can only be written when the ON bit = 0.

- **3:** This bit is not used in the Framed SPI mode. The user should program this bit to '0' for the Framed SPI mode (FRMEN = 1).

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|

| 24.24        | U-0               | U-0               | U-0               | U-0               | S/HC-0            | R/W-1             | R/W-0            | R/W-0            |

| 31:24        | —                 | _                 | _                 | —                 | ABAT              | F                 | REQOP<2:0>       | •                |

| 23:16        | R-1               | R-0               | R-0               | R/W-0             | U-0               | U-0               | U-0              | U-0              |

| 23.10        | OPMOD<2:0>        |                   | CANCAP            | —                 | —                 | —                 | —                |                  |

| 15.0         | R/W-0             | U-0               | R/W-0             | U-0               | R-0               | U-0               | U-0              | U-0              |

| 15:8         | ON <sup>(1)</sup> | _                 | SIDLE             | —                 | CANBUSY           | —                 | —                | —                |

| 7.0          | U-0               | U-0               | U-0               | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |

| 7:0          | —                 | _                 |                   |                   | [                 | DNCNT<4:0>        |                  |                  |

#### REGISTER 24-1: CICON: CAN MODULE CONTROL REGISTER

| Legend:           | HC = Hardware Clear S = Settable bit |                        |                    |

|-------------------|--------------------------------------|------------------------|--------------------|

| R = Readable bit  | W = Writable bit                     | U = Unimplemented bit, | , read as '0'      |

| -n = Value at POR | '1' = Bit is set                     | '0' = Bit is cleared   | x = Bit is unknown |

#### bit 31-28 Unimplemented: Read as '0'

- bit 27 **ABAT:** Abort All Pending Transmissions bit

- 1 = Signal all transmit buffers to abort transmission

- 0 = Module will clear this bit when all transmissions aborted

#### bit 26-24 REQOP<2:0>: Request Operation Mode bits

- 111 = Set Listen All Messages mode

- 110 = Reserved

- 101 = Reserved

- 100 = Set Configuration mode

- 011 = Set Listen Only mode

- 010 = Set Loopback mode

- 001 = Set Disable mode

- 000 = Set Normal Operation mode

#### bit 23-21 OPMOD<2:0>: Operation Mode Status bits

- 111 = Module is in Listen All Messages mode

- 110 = Reserved

- 101 = Reserved

- 100 = Module is in Configuration mode

- 011 = Module is in Listen Only mode

- 010 = Module is in Loopback mode

- 001 = Module is in Disable mode

- 000 = Module is in Normal Operation mode

#### bit 20 CANCAP: CAN Message Receive Time Stamp Timer Capture Enable bit

- 1 = CANTMR value is stored on valid message reception and is stored with the message

- 0 = Disable CAN message receive time stamp timer capture and stop CANTMR to conserve power

- bit 19-16 Unimplemented: Read as '0'

- bit 15 ON: CAN On bit<sup>(1)</sup>

- 1 = CAN module is enabled

- 0 = CAN module is disabled

- bit 14 Unimplemented: Read as '0'

- **Note 1:** If the user application clears this bit, it may take a number of cycles before the CAN module completes the current transaction and responds to this request. The user application should poll the CANBUSY bit to verify that the request has been honored.

### REGISTER 24-2: CiCFG: CAN BAUD RATE CONFIGURATION REGISTER (CONTINUED)

```

bit 10-8 PRSEG<2:0>: Propagation Time Segment bits<sup>(4)</sup>

111 = \text{Length is 8 x Tq}

000 = \text{Length is } 1 \times TQ

SJW<1:0>: Synchronization Jump Width bits<sup>(3)</sup>

bit 7-6

11 = \text{Length is } 4 \times \text{Tq}

10 = Length is 3 x TQ

01 = Length is 2 x TQ

00 = \text{Length is } 1 \times TQ

BRP<5:0>: Baud Rate Prescaler bits

bit 5-0

111111 = TQ = (2 x 64)/FSYS

111110 = TQ = (2 x 63)/FSYS

000001 = TQ = (2 \times 2)/FSYS

000000 = TQ = (2 \times 1)/FSYS

Note 1: SEG2PH \leq SEG1PH. If SEG2PHTS is clear, SEG2PH will be set automatically.

2: 3 Time bit sampling is not allowed for BRP < 2.

```

- $\textbf{3:} \quad SJW \leq SEG2PH.$

- **4:** The Time Quanta per bit must be greater than 7 (that is, TQBIT > 7).

Note: This register can only be modified when the CAN module is in Configuration mode (OPMOD<2:0> (CiCON<23:21>) = 100).

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|

| 31:24        | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |

| 31.24        | FLTEN11           | MSEL1             | 1<1:0>            |                   | FSEL11<4:0>       |                   |                  |                  |

| 23:16        | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |

| 23.10        | FLTEN10           | MSEL10<1:0>       |                   | FSEL10<4:0>       |                   |                   |                  |                  |

| 15:8         | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |

| 10.0         | FLTEN9            | MSEL              | 9<1:0>            | FSEL9<4:0>        |                   |                   |                  |                  |

| 7.0          | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |

| 7:0          | FLTEN8            | MSEL              | 8<1:0>            |                   | F                 | SEL8<4:0>         |                  |                  |

#### REGISTER 24-12: CIFLTCON2: CAN FILTER CONTROL REGISTER 2

#### Legend:

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read as '0' |                    |  |  |

|-------------------|------------------|------------------------------------|--------------------|--|--|

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared               | x = Bit is unknown |  |  |

| bit 31    | FLTEN11: Filter 11 Enable bit                                                                                                                                                  |

|-----------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|           | 1 = Filter is enabled<br>0 = Filter is disabled                                                                                                                                |

| bit 30-29 | MSEL11<1:0>: Filter 11 Mask Select bits                                                                                                                                        |

|           | <ul> <li>11 = Acceptance Mask 3 selected</li> <li>10 = Acceptance Mask 2 selected</li> <li>01 = Acceptance Mask 1 selected</li> <li>00 = Acceptance Mask 0 selected</li> </ul> |

| bit 28-24 | FSEL11<4:0>: FIFO Selection bits                                                                                                                                               |

|           | 11111 = Message matching filter is stored in FIFO buffer 31<br>11110 = Message matching filter is stored in FIFO buffer 30                                                     |

|           |                                                                                                                                                                                |

|           | 00001 = Message matching filter is stored in FIFO buffer 1<br>00000 = Message matching filter is stored in FIFO buffer 0                                                       |

| bit 23    | FLTEN10: Filter 10 Enable bit                                                                                                                                                  |

|           | <ul><li>1 = Filter is enabled</li><li>0 = Filter is disabled</li></ul>                                                                                                         |

| bit 22-21 | MSEL10<1:0>: Filter 10 Mask Select bits                                                                                                                                        |

|           | <ul> <li>11 = Acceptance Mask 3 selected</li> <li>10 = Acceptance Mask 2 selected</li> <li>01 = Acceptance Mask 1 selected</li> <li>00 = Acceptance Mask 0 selected</li> </ul> |

| bit 20-16 | FSEL10<4:0>: FIFO Selection bits                                                                                                                                               |

|           | 11111 = Message matching filter is stored in FIFO buffer 31                                                                                                                    |

|           | 11110 = Message matching filter is stored in FIFO buffer 30                                                                                                                    |

|           | •                                                                                                                                                                              |

|           | •                                                                                                                                                                              |

|           | 00001 = Message matching filter is stored in FIFO buffer 1<br>00000 = Message matching filter is stored in FIFO buffer 0                                                       |

|           |                                                                                                                                                                                |

Note: The bits in this register can only be modified if the corresponding filter enable (FLTENn) bit is '0'.

#### REGISTER 25-28: EMAC1MAXF: ETHERNET CONTROLLER MAC MAXIMUM FRAME LENGTH REGISTER

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6            | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |  |

|--------------|-------------------|------------------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|--|--|

| 31:24        | U-0               | U-0                          | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |  |  |

| 31.24        |                   | —                            | _                 | _                 | —                 | —                 | _                | _                |  |  |

| 22:16        | U-0               | U-0                          | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |  |  |

| 23:16        | —                 | —                            | —                 | —                 | —                 | —                 | _                | —                |  |  |

| 15.0         | R/W-0             | R/W-0                        | R/W-0             | R/W-0             | R/W-0             | R/W-1             | R/W-0            | R/W-1            |  |  |

| 15:8         |                   | MACMAXF<15:8> <sup>(1)</sup> |                   |                   |                   |                   |                  |                  |  |  |

| 7.0          | R/W-1             | R/W-1                        | R/W-1             | R/W-0             | R/W-1             | R/W-1             | R/W-1            | R/W-0            |  |  |

| 7:0          |                   | MACMAXF<7:0> <sup>(1)</sup>  |                   |                   |                   |                   |                  |                  |  |  |

| Legend:           |                  |                          |                    |

|-------------------|------------------|--------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, r | ead as '0'         |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared     | x = Bit is unknown |

#### bit 31-16 Unimplemented: Read as '0'

bit 15-0 MACMAXF<15:0>: Maximum Frame Length bits<sup>(1)</sup>

These bits reset to 0x05EE, which represents a maximum receive frame of 1518 octets. An untagged maximum size Ethernet frame is 1518 octets. A tagged frame adds four octets for a total of 1522 octets. If a shorter/longer maximum length restriction is desired, program this 16-bit field.

**Note 1:** If a proprietary header is allowed, this bit should be adjusted accordingly. For example, if 4-byte headers are prepended to frames, MACMAXF could be set to 1527 octets. This would allow the maximum VLAN tagged frame plus the 4-byte header.

**Note:** Both 16-bit and 32-bit accesses are allowed to these registers (including the SET, CLR and INV registers). 8-bit accesses are not allowed and are ignored by the hardware.

| REGISTE | ER 29-4: D | DEVCFG3: DE | EVICE CON | FIGURATIO | N WORD 3 |  |

|---------|------------|-------------|-----------|-----------|----------|--|

|         |            |             |           |           |          |  |

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2     | Bit<br>25/17/9/1      | Bit<br>24/16/8/0      |  |  |  |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-----------------------|-----------------------|-----------------------|--|--|--|

| 04-04        | R/P               | R/P               | r-1               | r-1               | r-1               | R/P                   | R/P                   | R/P                   |  |  |  |

| 31:24        | FVBUSONIO         | FUSBIDIO          | _                 | —                 | —                 | FCANIO <sup>(1)</sup> | FETHIO <sup>(2)</sup> | FMIIEN <sup>(2)</sup> |  |  |  |

| 22.46        | r-1               | r-1               | r-1               | r-1               | r-1               | R/P                   | R/P                   | R/P                   |  |  |  |

| 23:16        | —                 | —                 | —                 | —                 | —                 | F                     | FSRSSEL<2:0>          |                       |  |  |  |

| 45.0         | R/P               | R/P               | R/P               | R/P               | R/P               | R/P                   | R/P                   | R/P                   |  |  |  |

| 15:8         | USERID<15:8>      |                   |                   |                   |                   |                       |                       |                       |  |  |  |

| 7.0          | R/P               | R/P               | R/P               | R/P               | R/P               | R/P                   | R/P                   | R/P                   |  |  |  |

| 7:0          |                   | USERID<7:0>       |                   |                   |                   |                       |                       |                       |  |  |  |

| Legend:           | r = Reserved bit | P = Programmable bit               |                  |  |  |

|-------------------|------------------|------------------------------------|------------------|--|--|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read as '0' |                  |  |  |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared x             | = Bit is unknown |  |  |

1 = VBUSON pin is controlled by the USB module 0 = VBUSON pin is controlled by the port function

bit 30

FUSBIDIO: USB USBID Selection bit 1 = USBID pin is controlled by the USB module 0 = USBID pin is controlled by the port function

bit 29-27

Reserved: Write '1'

bit 26

FCANIO: CAN I/O Pin Selection bit<sup>(1)</sup> 1 = Default CAN I/O Pins 0 = Alternate CAN I/O Pins

bit 25

FETHIO: Ethernet I/O Pins

1 = Default Ethernet I/O Pins

FVBUSONIO: USB VBUSON Selection bit

- 0 =Alternate Ethernet I/O Pins

- bit 24 FMIIEN: Ethernet MII Enable bit<sup>(2)</sup>

- 1 = MII is enabled

- 0 = RMII is enabled

- bit 23-19 Reserved: Write '1'

- bit 18-16 FSRSSEL<2:0>: SRS Select bits

- 111 = Assign Interrupt Priority 7 to a shadow register set

- 110 = Assign Interrupt Priority 6 to a shadow register set

- •

bit 31

- 001 = Assign Interrupt Priority 1 to a shadow register set

000 = All interrupt priorities are assigned to a shadow register set

- bit 15-0 **USERID<15:0>:** User ID bits This is a 16-bit value that is user-defined and is readable via ICSP<sup>™</sup> and JTAG.

- Note 1: This bit is Reserved and reads '1' on PIC32MX664/675/695 devices.

- 2: This bit is Reserved and reads '1' on PIC32MX534/564/575 devices.

| Bit<br>Range | Bit<br>31/23/15/7           | Bit<br>30/22/14/6 | Bit<br>29/21/13/5  | Bit<br>28/20/12/4 | Bit<br>27/19/11/3   | Bit<br>26/18/10/2 | Bit<br>25/17/9/1      | Bit<br>24/16/8/0 |  |  |  |

|--------------|-----------------------------|-------------------|--------------------|-------------------|---------------------|-------------------|-----------------------|------------------|--|--|--|

| 04-04        | R                           | R                 | R                  | R                 | R                   | R                 | R                     | R                |  |  |  |

| 31:24        |                             | VER<3             | :0> <sup>(1)</sup> |                   |                     | DEVID<2           | 27:24> <sup>(1)</sup> |                  |  |  |  |

| 00.40        | R                           | R                 | R                  | R                 | R                   | R                 | R                     | R                |  |  |  |

| 23:16        | DEVID<23:16> <sup>(1)</sup> |                   |                    |                   |                     |                   |                       |                  |  |  |  |

| 45.0         | R                           | R                 | R                  | R                 | R                   | R                 | R                     | R                |  |  |  |

| 15:8         | DEVID<15:8> <sup>(1)</sup>  |                   |                    |                   |                     |                   |                       |                  |  |  |  |

| 7.0          | R                           | R                 | R                  | R                 | R                   | R                 | R                     | R                |  |  |  |

| 7:0          |                             |                   |                    | DEVID<            | 7:0> <sup>(1)</sup> |                   |                       |                  |  |  |  |

#### REGISTER 29-5: DEVID: DEVICE AND REVISION ID REGISTER

# Legend:

| Legena.           |                  |                          |                    |

|-------------------|------------------|--------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, r | ead as '0'         |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared     | x = Bit is unknown |

bit 31-28 VER<3:0>: Revision Identifier bits<sup>(1)</sup>

bit 27-0 DEVID<27:0>: Device ID bits<sup>(1)</sup>

Note 1: See the "PIC32 Flash Programming Specification" (DS60001145) for a list of Revision and Device ID values.

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|

| 21.24        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 31:24        |                   | _                 |                   |                   |                   |                   | _                | —                |

| 00.40        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 23:16        | _                 | _                 | _                 | _                 | _                 | _                 | _                | —                |

| 45.0         | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 15:8         | _                 | _                 | _                 | _                 | _                 | _                 | _                | —                |

| 7.0          | U-0               | U-0               | U-0               | U-0               | R/W-1             | R/W-0             | U-0              | R/W-0            |

| 7:0          | _                 | _                 | _                 | _                 | JTAGEN            | TROEN             |                  | TDOEN            |

### REGISTER 29-6: DDPCON: DEBUG DATA PORT CONTROL REGISTER

| Legend:           |                  |                      |                    |

|-------------------|------------------|----------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bi | it, read as '0'    |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared | x = Bit is unknown |

#### bit 31-4 Unimplemented: Read as '0'

- bit 3 JTAGEN: JTAG Port Enable bit

- 1 = Enable the JTAG port

- 0 = Disable the JTAG port

- bit 2 **TROEN:** Trace Output Enable bit

- 1 = Enable the trace port

- 0 = Disable the trace port

- bit 1 Unimplemented: Read as '0'

- bit 0 TDOEN: TDO Enable for 2-Wire JTAG

- 1 = 2-wire JTAG protocol uses TDO

- 0 = 2-wire JTAG protocol does not use TDO

### 31.11 Demonstration/Development Boards, Evaluation Kits, and Starter Kits

A wide variety of demonstration, development and evaluation boards for various PIC MCUs and dsPIC DSCs allows quick application development on fully functional systems. Most boards include prototyping areas for adding custom circuitry and provide application firmware and source code for examination and modification.

The boards support a variety of features, including LEDs, temperature sensors, switches, speakers, RS-232 interfaces, LCD displays, potentiometers and additional EEPROM memory.

The demonstration and development boards can be used in teaching environments, for prototyping custom circuits and for learning about various microcontroller applications.

In addition to the PICDEM<sup>™</sup> and dsPICDEM<sup>™</sup> demonstration/development board series of circuits, Microchip has a line of evaluation kits and demonstration software for analog filter design, KEELOQ<sup>®</sup> security ICs, CAN, IrDA<sup>®</sup>, PowerSmart battery management, SEEVAL<sup>®</sup> evaluation system, Sigma-Delta ADC, flow rate sensing, plus many more.

Also available are starter kits that contain everything needed to experience the specified device. This usually includes a single application and debug capability, all on one board.

Check the Microchip web page (www.microchip.com) for the complete list of demonstration, development and evaluation kits.

# 31.12 Third-Party Development Tools

Microchip also offers a great collection of tools from third-party vendors. These tools are carefully selected to offer good value and unique functionality.

- Device Programmers and Gang Programmers from companies, such as SoftLog and CCS

- Software Tools from companies, such as Gimpel and Trace Systems

- Protocol Analyzers from companies, such as Saleae and Total Phase

- Demonstration Boards from companies, such as MikroElektronika, Digilent<sup>®</sup> and Olimex

- Embedded Ethernet Solutions from companies, such as EZ Web Lynx, WIZnet and IPLogika<sup>®</sup>

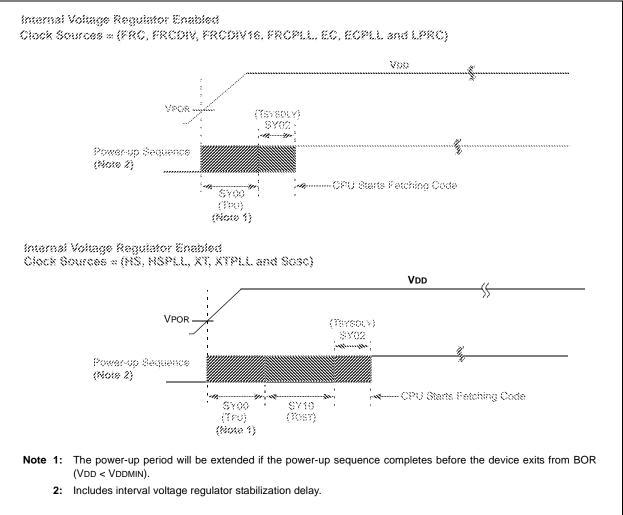

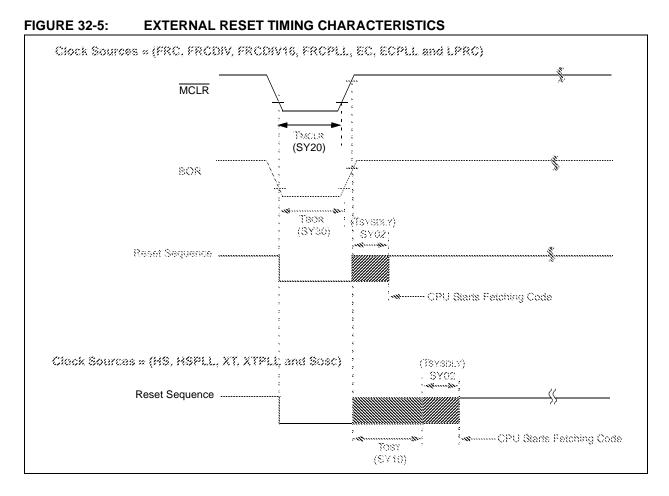

# FIGURE 32-4: POWER-ON RESET TIMING CHARACTERISTICS

### TABLE 32-22: RESETS TIMING

| AC CHARACTERISTICS |         |                                                                                                                                            | $\begin{tabular}{lllllllllllllllllllllllllllllllllll$ |                              |      |       |                |  |  |

|--------------------|---------|--------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------|------------------------------|------|-------|----------------|--|--|

| Param.<br>No.      | Symbol  | Characteristics <sup>(1)</sup>                                                                                                             | Min.                                                  | Typical <sup>(2)</sup>       | Max. | Units | Conditions     |  |  |

| SY00               | Τρυ     | Power-up Period<br>Internal Voltage Regulator Enabled                                                                                      | _                                                     | 400                          | 600  | μS    | -40°C to +85°C |  |  |

| SY02               | TSYSDLY | System Delay Period:<br>Time Required to Reload Device<br>Configuration Fuses plus SYSCLK<br>Delay before First instruction is<br>Fetched. |                                                       | 1 μs +<br>8 SYSCLK<br>cycles | _    | _     | -40°C to +85°C |  |  |

| SY20               | TMCLR   | MCLR Pulse Width (low)                                                                                                                     | —                                                     | 2                            | _    | μS    | -40°C to +85°C |  |  |

| SY30               | TBOR    | BOR Pulse Width (low)                                                                                                                      | —                                                     | 1                            |      | μS    | -40°C to +85°C |  |  |

**Note 1:** These parameters are characterized, but not tested in manufacturing.

2: Data in "Typ" column is at 3.3V, 25°C unless otherwise stated. Characterized by design but not tested.

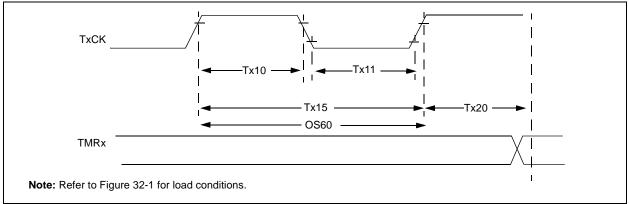

### FIGURE 32-6: TIMER1, 2, 3, 4, 5 EXTERNAL CLOCK TIMING CHARACTERISTICS

# TABLE 32-23: TIMER1 EXTERNAL CLOCK TIMING REQUIREMENTS<sup>(1)</sup>

| AC CHA        |           | TICS                                                                                                 |                                                                   | (unl | Standard Operating Conditions: 2.3V to 3.6V(unless otherwise stated)Operating temperature $-40^{\circ}C \le TA \le +85^{\circ}C$ for Industrial $-40^{\circ}C \le TA \le +105^{\circ}C$ for V-Temp |         |                                            |       |                               |    |                                  |

|---------------|-----------|------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------|------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------|--------------------------------------------|-------|-------------------------------|----|----------------------------------|

| Param.<br>No. | Symbol    | ymbol Characteristics <sup>(2)</sup>                                                                 |                                                                   |      | Min.                                                                                                                                                                                               | Typical | Max.                                       | Units | Conditions                    |    |                                  |

| TA10          | T⊤xH      | TxCK<br>High Time                                                                                    | Synchronous with prescale                                         |      | [(12.5 ns or 1 ТРВ)/N]<br>+ 25 ns                                                                                                                                                                  | —       | —                                          | ns    | Must also meet parameter TA15 |    |                                  |

|               |           |                                                                                                      | Asynchron<br>with presca                                          |      | 10                                                                                                                                                                                                 |         | —                                          | ns    | —                             |    |                                  |

| TA11          | T⊤xL      | TxCK<br>Low Time                                                                                     | Synchronous,<br>with prescaler<br>Asynchronous,<br>with prescaler |      |                                                                                                                                                                                                    |         | [(12.5 ns or 1 Трв)/N]<br>+ 25 ns          | _     | _                             | ns | Must also meet<br>parameter TA15 |

|               |           |                                                                                                      |                                                                   |      |                                                                                                                                                                                                    |         | 10                                         | _     | —                             | ns | _                                |

| TA15          | ΤτχΡ      | TxCK<br>Input Period                                                                                 |                                                                   |      | Synchronous, with prescaler                                                                                                                                                                        |         | [(Greater of 25 ns or<br>2 TPB)/N] + 30 ns |       | _                             | ns | VDD > 2.7V                       |

|               |           |                                                                                                      |                                                                   |      | [(Greater of 25 ns or<br>2 TPB)/N] + 50 ns                                                                                                                                                         | —       | _                                          | ns    | Vdd < 2.7V                    |    |                                  |

|               |           |                                                                                                      |                                                                   |      | Asynchronou with prescale                                                                                                                                                                          |         | 20                                         | —     | _                             | ns | VDD > 2.7V<br>(Note 3)           |

|               |           |                                                                                                      |                                                                   |      | 50                                                                                                                                                                                                 | —       | _                                          | ns    | VDD < 2.7V<br>(Note 3)        |    |                                  |

| OS60          | FT1       | SOSC1/T1CK Oscillator<br>Input Frequency Range<br>(oscillator enabled by sett<br>TCS bit (T1CON<1>)) |                                                                   |      | 32                                                                                                                                                                                                 | —       | 100                                        | kHz   | _                             |    |                                  |

| TA20          | TCKEXTMRL | Delay from External TxCK<br>Clock Edge to Timer<br>Increment                                         |                                                                   | ĸ    | —                                                                                                                                                                                                  | —       | 1                                          | Трв   | —                             |    |                                  |

Note 1: Timer1 is a Type A.

2: This parameter is characterized, but not tested in manufacturing.

**3:** N = Prescale Value (1, 8, 64, 256).

#### TABLE 32-36: ADC MODULE SPECIFICATIONS (CONTINUED)

| AC CHA        |            | STICS                             | $\begin{array}{l} \mbox{Standard Operating Conditions (see Note 5): 2.5V to 3.6V \\ \mbox{(unless otherwise stated)} \\ \mbox{Operating temperature} & -40^{\circ}C \leq TA \leq +85^{\circ}C \mbox{ for Industrial} \\ & -40^{\circ}C \leq TA \leq +105^{\circ}C \mbox{ for V-Temp} \end{array}$ |              |      |       |                                                         |  |  |  |

|---------------|------------|-----------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------|------|-------|---------------------------------------------------------|--|--|--|

| Param.<br>No. | Symbol     | Characteristics                   | Min.                                                                                                                                                                                                                                                                                              | Typical      | Max. | Units | Conditions                                              |  |  |  |

| ADC Ac        | curacy – N | leasurements with Inter           | nal VREF+/VR                                                                                                                                                                                                                                                                                      | EF-          |      |       |                                                         |  |  |  |

| AD20d         | Nr         | Resolution                        |                                                                                                                                                                                                                                                                                                   | 10 data bits |      | bits  | (Note 3)                                                |  |  |  |

| AD21d         | INL        | Integral Nonlinearity             | > -1                                                                                                                                                                                                                                                                                              | —            | < 1  | LSb   | VINL = AVSS = 0V,<br>AVDD = 2.5V to 3.6V<br>(Note 3)    |  |  |  |

| AD22d         | DNL        | Differential Nonlinearity         | > -1                                                                                                                                                                                                                                                                                              |              | < 1  | LSb   | VINL = AVSS = 0V,<br>AVDD = 2.5V to 3.6V<br>(Notes 2,3) |  |  |  |

| AD23d         | Gerr       | Gain Error                        | > -4                                                                                                                                                                                                                                                                                              | -            | < 4  | LSb   | VINL = AVSS = 0V,<br>AVDD = 2.5V to 3.6V<br>(Note 3)    |  |  |  |

| AD24d         | EOFF       | Offset Error                      | > -2                                                                                                                                                                                                                                                                                              | -            | < 2  | LSb   | VINL = AVSS = 0V,<br>AVDD = 2.5V to 3.6V<br>(Note 3)    |  |  |  |

| AD25d         | —          | Monotonicity                      | —                                                                                                                                                                                                                                                                                                 | —            | _    | —     | Guaranteed                                              |  |  |  |

| Dynami        | c Performa | ance                              |                                                                                                                                                                                                                                                                                                   |              |      |       |                                                         |  |  |  |

| AD31b         | SINAD      | Signal to Noise and<br>Distortion | 55                                                                                                                                                                                                                                                                                                | 58.5         |      | dB    | (Notes 3,4)                                             |  |  |  |

| AD34b         | ENOB       | Effective Number of Bits          | 9.0                                                                                                                                                                                                                                                                                               | 9.5          |      | bits  | (Notes 3,4)                                             |  |  |  |

**Note 1:** These parameters are not characterized or tested in manufacturing.

2: With no missing codes.

**3:** These parameters are characterized, but not tested in manufacturing.

4: Characterized with a 1 kHz sine wave.

**5:** The ADC module is functional at VBORMIN < VDD < 2.5V, but with degraded performance. Unless otherwise stated, module functionality is tested, but not characterized.

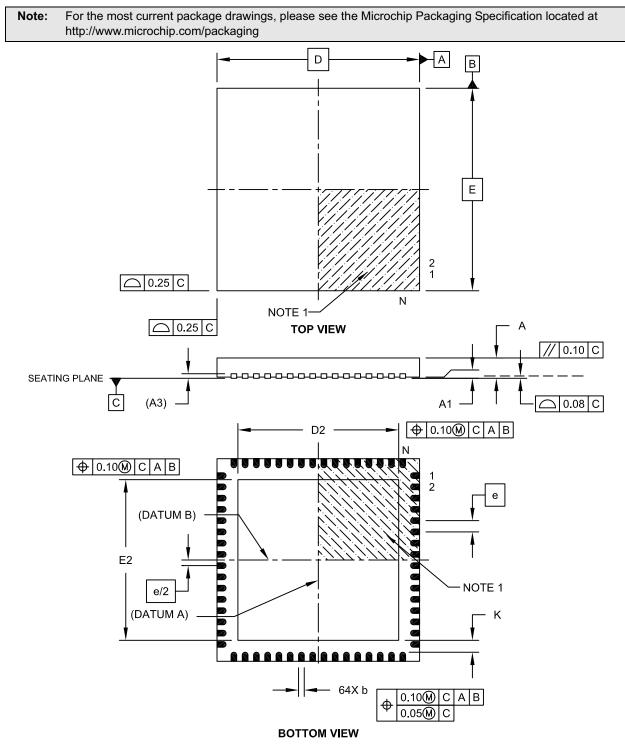

# 64-Lead Plastic Quad Flat, No Lead Package (MR) – 9x9x0.9 mm Body [QFN] With 7.15 x 7.15 Exposed Pad [QFN]

Microchip Technology Drawing C04-149C Sheet 1 of 2