Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFl

| Product Status             | Active                                                                         |

|----------------------------|--------------------------------------------------------------------------------|

| Core Processor             | MIPS32® M4K™                                                                   |

| Core Size                  | 32-Bit Single-Core                                                             |

| Speed                      | 80MHz                                                                          |

| Connectivity               | Ethernet, I <sup>2</sup> C, SPI, UART/USART, USB OTG                           |

| Peripherals                | Brown-out Detect/Reset, DMA, POR, PWM, WDT                                     |

| Number of I/O              | 53                                                                             |

| Program Memory Size        | 64KB (64K x 8)                                                                 |

| Program Memory Type        | FLASH                                                                          |

| EEPROM Size                | -                                                                              |

| RAM Size                   | 32K x 8                                                                        |

| Voltage - Supply (Vcc/Vdd) | 2.3V ~ 3.6V                                                                    |

| Data Converters            | A/D 16x10b                                                                     |

| Oscillator Type            | Internal                                                                       |

| Operating Temperature      | -40°C ~ 105°C (TA)                                                             |

| Mounting Type              | Surface Mount                                                                  |

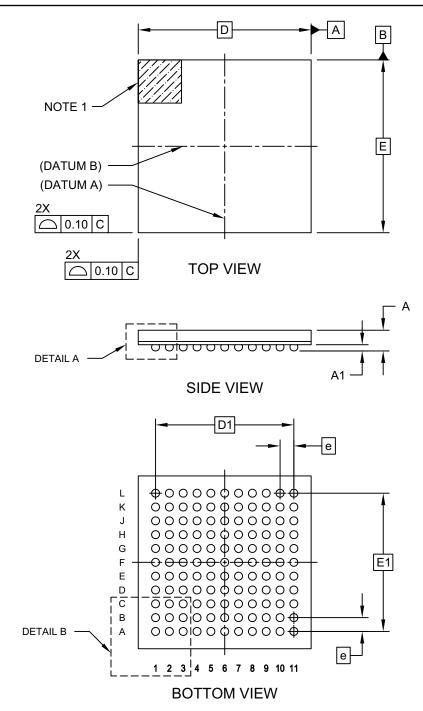

| Package / Case             | 64-VFQFN Exposed Pad                                                           |

| Supplier Device Package    | 64-VQFN (9x9)                                                                  |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic32mx664f064h-v-mr |

|                            |                                                                                |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

#### TABLE 1-1: PINOUT I/O DESCRIPTIONS (CONTINUED)

|           |                    | Pin Nun         | nber <sup>(1)</sup> |                 |             | D              |                                                            |

|-----------|--------------------|-----------------|---------------------|-----------------|-------------|----------------|------------------------------------------------------------|

| Pin Name  | 64-Pin<br>QFN/TQFP | 100-Pin<br>TQFP | 121-Pin<br>TFBGA    | 124-pin<br>VTLA | Pin<br>Type | Buffer<br>Type | Description                                                |

| AC2TX     | —                  | 7               | E4                  | B4              | 0           | —              | Alternate CAN2 bus transmit pin                            |

| ERXD0     | 61                 | 41              | J7                  | B23             | I           | ST             | Ethernet Receive Data 0 <sup>(2)</sup>                     |

| ERXD1     | 60                 | 42              | L7                  | A28             | I           | ST             | Ethernet Receive Data 1 <sup>(2)</sup>                     |

| ERXD2     | 59                 | 43              | K7                  | B24             | I           | ST             | Ethernet Receive Data 2 <sup>(2)</sup>                     |

| ERXD3     | 58                 | 44              | L8                  | A29             | I           | ST             | Ethernet Receive Data 3 <sup>(2)</sup>                     |

| ERXERR    | 64                 | 35              | J5                  | B20             | I           | ST             | Ethernet receive error input <sup>(2)</sup>                |

| ERXDV     | 62                 | 12              | F2                  | A8              | I           | ST             | Ethernet receive data valid <sup>(2)</sup>                 |

| ECRSDV    | 62                 | 12              | F2                  | A8              | I           | ST             | Ethernet carrier sense data valid <sup>(2)</sup>           |

| ERXCLK    | 63                 | 14              | F3                  | A9              | I           | ST             | Ethernet receive clock <sup>(2)</sup>                      |

| EREFCLK   | 63                 | 14              | F3                  | A9              | I           | ST             | Ethernet reference clock <sup>(2)</sup>                    |

| ETXD0     | 2                  | 88              | A6                  | A60             | 0           | _              | Ethernet Transmit Data 0 <sup>(2)</sup>                    |

| ETXD1     | 3                  | 87              | B6                  | B49             | 0           | _              | Ethernet Transmit Data 1 <sup>(2)</sup>                    |

| ETXD2     | 43                 | 79              | A9                  | B43             | 0           | _              | Ethernet Transmit Data 2 <sup>(2)</sup>                    |

| ETXD3     | 42                 | 80              | D8                  | A54             | 0           | _              | Ethernet Transmit Data 3 <sup>(2)</sup>                    |

| ETXERR    | 54                 | 89              | E6                  | B50             | 0           | _              | Ethernet transmit error <sup>(2)</sup>                     |

| ETXEN     | 1                  | 83              | D7                  | B45             | 0           | _              | Ethernet transmit enable <sup>(2)</sup>                    |

| ETXCLK    | 55                 | 84              | C7                  | A56             | I           | ST             | Ethernet transmit clock <sup>(2)</sup>                     |

| ECOL      | 44                 | 10              | E3                  | A7              | I           | ST             | Ethernet collision detect <sup>(2)</sup>                   |

| ECRS      | 45                 | 11              | F4                  | B6              | I           | ST             | Ethernet carrier sense <sup>(2)</sup>                      |

| EMDC      | 30                 | 71              | C11                 | A46             | 0           | _              | Ethernet management data clock <sup>(2)</sup>              |

| EMDIO     | 49                 | 68              | E9                  | B37             | I/O         | _              | Ethernet management data <sup>(2)</sup>                    |

| AERXD0    | 43                 | 18              | G1                  | A11             | I           | ST             | Alternate Ethernet Receive Data 0 <sup>(2)</sup>           |

| AERXD1    | 42                 | 19              | G2                  | B10             | I           | ST             | Alternate Ethernet Receive Data 1 <sup>(2)</sup>           |

| AERXD2    | —                  | 28              | L2                  | A21             | I           | ST             | Alternate Ethernet Receive Data 2(2)                       |

| AERXD3    | —                  | 29              | K3                  | B17             | I           | ST             | Alternate Ethernet Receive Data 3 <sup>(2)</sup>           |

| AERXERR   | 55                 | 1               | B2                  | A2              | I           | ST             | Alternate Ethernet receive error input <sup>(2)</sup>      |

| AERXDV    | —                  | 12              | F2                  | A8              | I           | ST             | Alternate Ethernet receive data valid <sup>(2)</sup>       |

| AECRSDV   | 44                 | 12              | F2                  | A8              | I           | ST             | Alternate Ethernet carrier sense data valid <sup>(2)</sup> |

| AERXCLK   | —                  | 14              | F3                  | A9              | I           | ST             | Alternate Ethernet receive clock <sup>(2)</sup>            |

| AEREFCLK  | 45                 | 14              | F3                  | A9              | I           | ST             | Alternate Ethernet reference clock <sup>(2)</sup>          |

| AETXD0    | 59                 | 47              | L9                  | B26             | 0           |                | Alternate Ethernet Transmit Data 0 <sup>(2)</sup>          |

| AETXD1    | 58                 | 48              | K9                  | A31             | 0           |                | Alternate Ethernet Transmit Data 1 <sup>(2)</sup>          |

| AETXD2    |                    | 44              | L8                  | A29             | 0           |                | Alternate Ethernet Transmit Data 2 <sup>(2)</sup>          |

| AETXD3    |                    | 43              | K7                  | B24             | 0           |                | Alternate Ethernet Transmit Data 3 <sup>(2)</sup>          |

| AETXERR   |                    | 35              | J5                  | B20             | 0           |                | Alternate Ethernet transmit error <sup>(2)</sup>           |

| AETXEN    | 54                 | 67              | E8                  | A44             | 0           |                | Alternate Ethernet transmit enable <sup>(2)</sup>          |

| AETXCLK   | _                  | 66              | E11                 | B36             | 1           | ST             | Alternate Ethernet transmit clock <sup>(2)</sup>           |

| AECOL     |                    | 42              | L7                  | A28             | 1           | ST             | Alternate Ethernet collision detect <sup>(2)</sup>         |

| Leaend: C | MOS = CMO          | S compatib      | le input or c       | butput          | A           | nalog = A      | Analog input P = Power                                     |

Legend: CMOS = CMOS compatible input or output ST = Schmitt Trigger input with CMOS levels

Analog = Analog input P = PowerO = Output I = Input

TTL = TTL input buffer

Note 1: Pin numbers are only provided for reference. See the "Device Pin Tables" section for device pin availability.

2: See 25.0 "Ethernet Controller" for more information.

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |  |  |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|--|--|--|

| 04.04        | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |  |

| 31:24        |                   |                   |                   | NVMDA             | TA<31:24>         |                   |                  |                  |  |  |  |

| 00.40        | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |  |

| 23:16        |                   |                   |                   | NVMDA             | TA<23:16>         |                   |                  |                  |  |  |  |

| 45.0         | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |  |

| 15:8         |                   |                   |                   | NVMDA             | TA<15:8>          |                   |                  |                  |  |  |  |

| 7.0          | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |  |

| 7:0          | NVMDATA<7:0>      |                   |                   |                   |                   |                   |                  |                  |  |  |  |

#### REGISTER 5-4: NVMDATA: FLASH PROGRAM DATA REGISTER

| Legend:           |                  |                           |                    |

|-------------------|------------------|---------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, re | ad as '0'          |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared      | x = Bit is unknown |

bit 31-0 NVMDATA<31:0>: Flash Programming Data bits

**Note:** The bits in this register are only reset by a Power-on Reset (POR).

#### REGISTER 5-5: NVMSRCADDR: SOURCE DATA ADDRESS REGISTER

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |  |  |  |  |  |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|--|--|--|--|--|--|

| 04.04        | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |  |  |  |  |

| 31:24        | NVMSRCADDR<31:24> |                   |                   |                   |                   |                   |                  |                  |  |  |  |  |  |  |

| 00.40        | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |  |  |  |  |

| 23:16        |                   | NVMSRCADDR<23:16> |                   |                   |                   |                   |                  |                  |  |  |  |  |  |  |

| 45.0         | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |  |  |  |  |

| 15:8         |                   |                   |                   | NVMSRC/           | ADDR<15:8>        |                   |                  |                  |  |  |  |  |  |  |

| 7.0          | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |  |  |  |  |

| 7:0          | NVMSRCADDR<7:0>   |                   |                   |                   |                   |                   |                  |                  |  |  |  |  |  |  |

| Legend:                                                              |                  |                      |                    |  |  |  |  |

|----------------------------------------------------------------------|------------------|----------------------|--------------------|--|--|--|--|

| R = Readable bit W = Writable bit U = Unimplemented bit, read as '0' |                  |                      |                    |  |  |  |  |

| -n = Value at POR                                                    | '1' = Bit is set | '0' = Bit is cleared | x = Bit is unknown |  |  |  |  |

#### bit 31-0 NVMSRCADDR<31:0>: Source Data Address bits

The system physical address of the data to be programmed into the Flash when the NVMOP<3:0> bits (NVMCON<3:0>) are set to perform row programming.

|                             |                                 | P             | PIC32M        | X695F5 <sup>°</sup> | 12H DE      | VICES                         |                               |                               |                               |                             |                               |                               |                             |                       |               |        |        |        |            |

|-----------------------------|---------------------------------|---------------|---------------|---------------------|-------------|-------------------------------|-------------------------------|-------------------------------|-------------------------------|-----------------------------|-------------------------------|-------------------------------|-----------------------------|-----------------------|---------------|--------|--------|--------|------------|

| ess                         |                                 |               |               |                     |             |                               |                               |                               |                               | В                           | its                           |                               |                             |                       |               |        |        |        |            |

| Virtual Address<br>(BF88_#) | Register<br>Name <sup>(1)</sup> | Bit Range     | 31/15         | 30/14               | 29/13       | 28/12                         | 27/11                         | 26/10                         | 25/9                          | 24/8                        | 23/7                          | 22/6                          | 21/5                        | 20/4                  | 19/3          | 18/2   | 17/1   | 16/0   | All Resets |

| 1000                        | INTCON                          | 31:16         |               |                     | —           | —                             | _                             |                               | _                             |                             | _                             | —                             |                             | _                     |               |        | _      | SS0    | 0000       |

| 1000                        | INTCON                          | 15:0          | —             | _                   | _           | MVEC                          | _                             |                               | TPC<2:0>                      |                             | _                             | _                             |                             | INT4EP                | INT3EP        | INT2EP | INT1EP | INT0EP | 0000       |

| 1010                        | INTSTAT <sup>(3)</sup>          | 31:16         | —             | —                   | —           | —                             | —                             | —                             | —                             | —                           | —                             | —                             | —                           | —                     | —             | —      | —      | —      | 0000       |

| 1010                        |                                 | 15:0          |               | —                   | —           | —                             | _                             |                               | SRIPL<2:0>                    |                             | —                             | —                             |                             |                       | VEC           | <5:0>  |        |        | 0000       |

| 1020                        | IPTMR                           | 31:16<br>15:0 |               |                     |             |                               |                               |                               |                               | IPTMR                       | <31:0>                        |                               |                             |                       |               |        |        |        | 0000       |

| 1030                        | IFS0                            | 31:16         | I2C1MIF       | I2C1SIF             | I2C1BIF     | U1TXIF<br>SPI3TXIF<br>I2C3MIF | U1RXIF<br>SPI3RXIF<br>I2C3SIF | U1EIF<br>SPI3EIF<br>I2C3BIF   | _                             | _                           | _                             | OC5IF                         | IC5IF                       | T5IF                  | INT4IF        | OC4IF  | IC4IF  | T4IF   | 0000       |

|                             |                                 | 15:0          | INT3IF        | OC3IF               | IC3IF       | T3IF                          | INT2IF                        | OC2IF                         | IC2IF                         | T2IF                        | INT1IF                        | OC1IF                         | IC1IF                       | T1IF                  | <b>INT0IF</b> | CS1IF  | CS0IF  | CTIF   | 0000       |

|                             |                                 | 31:16         | <b>IC3EIF</b> | IC2EIF              | IC1EIF      | ETHIF                         | —                             | _                             | USBIF                         | FCEIF                       | DMA7IF <sup>(2)</sup>         | DMA6IF <sup>(2)</sup>         | DMA5IF <sup>(2)</sup>       | DMA4IF <sup>(2)</sup> | DMA3IF        | DMA2IF | DMA1IF | DMA0IF | 0000       |

| 1040                        | IFS1                            | 15:0          | RTCCIF        | FSCMIF              | _           | _                             | _                             | U2TXIF<br>SPI4TXIF<br>I2C5MIF | U2RXIF<br>SPI4RXIF<br>I2C5SIF | U2EIF<br>SPI4EIF<br>I2C5BIF | U3TXIF<br>SPI2TXIF<br>I2C4MIF | U3RXIF<br>SPI2RXIF<br>I2C4SIF | U3EIF<br>SPI2EIF<br>I2C4BIF | CMP2IF                | CMP1IF        | PMPIF  | AD1IF  | CNIF   | 0000       |

|                             |                                 | 31:16         |               |                     |             |                               | _                             | _                             | _                             | _                           | _                             | _                             | _                           | _                     |               | _      | _      | _      | 0000       |

| 1050                        | IFS2                            | 15:0          | _             | _                   | _           | _                             | U5TXIF                        | U5RXIF                        | U5EIF                         | U6TXIF                      | U6RXIF                        | U6EIF                         | U4TXIF                      | U4RXIF                | U4EIF         | PMPEIF | IC5EIF | IC4EIF | 0000       |

| 1060                        | IEC0                            | 31:16         | I2C1MIE       | I2C1SIE             | I2C1BIE     | U1TXIE<br>SPI3TXIE<br>I2C3MIE | U1RXIE<br>SPI3RXIE<br>I2C3SIE | U1EIE<br>SPI3EIE<br>I2C3BIE   | _                             |                             | _                             | OC5IE                         | IC5IE                       | T5IE                  | INT4IE        | OC4IE  | IC4IE  | T4IE   | 0000       |

|                             |                                 | 15:0          | INT3IE        | OC3IE               | IC3IE       | T3IE                          | INT2IE                        | OC2IE                         | IC2IE                         | T2IE                        | INT1IE                        | OC1IE                         | IC1IE                       | T1IE                  | INT0IE        | CS1IE  | CS0IE  | CTIE   | 0000       |

|                             |                                 | 31:16         | IC3EIE        | IC2EIE              | IC1EIE      | ETHIE                         | _                             | _                             | USBIE                         | FCEIE                       | DMA7IE <sup>(2)</sup>         | DMA6IE <sup>(2)</sup>         | DMA5IE <sup>(2)</sup>       | DMA4IE <sup>(2)</sup> | <b>DMA3IE</b> | DMA2IE | DMA1IE | DMA0IE | 0000       |

| 1070                        | IEC1                            | 15:0          | RTCCIE        | FSCMIE              | _           | _                             | -                             | U2TXIE<br>SPI4TXIE<br>I2C5MIE | U2RXIE<br>SPI4RXIE<br>I2C5SIE | U2EIE<br>SPI4EIE<br>I2C5BIE | U3TXIE<br>SPI2TXIE<br>I2C4MIE | U3RXIE<br>SPI2RXIE<br>I2C4SIE | U3EIE<br>SPI2EIE<br>I2C4BIE | CMP2IE                | CMP1IE        | PMPIE  | AD1IE  | CNIE   | 0000       |

|                             |                                 | 31:16         |               | _                   | _           | _                             | _                             | _                             |                               | _                           | _                             | _                             | _                           | _                     |               | _      | _      | _      | 0000       |

| 1080                        | IEC2                            | 15:0          | _             | _                   | _           | _                             | U5TXIE                        | U5RXIE                        | U5EIE                         | U6TXIE                      | U6RXIE                        | U6EIE                         | U4TXIE                      | U4RXIE                | U4EIE         | PMPEIE | IC5EIE | IC4EIE | 0000       |

|                             |                                 | 31:16         | _             | _                   | _           |                               | INT0IP<2:0>                   |                               | INTOIS                        |                             | _                             | _                             | _                           |                       | CS1IP<2:0>    |        | CS1IS  |        | 0000       |

| 1090                        | IPC0                            | 15:0          | _             | _                   | _           |                               | CS0IP<2:0>                    |                               | CSOIS                         | S<1:0>                      | _                             | _                             | _                           |                       | CTIP<2:0>     |        | CTIS   |        | 0000       |

| 1040                        | IPC1                            | 31:16         | _             | _                   | _           |                               | INT1IP<2:0>                   |                               | INT1IS                        | S<1:0>                      | _                             | _                             | _                           | (                     | OC1IP<2:0>    |        | OC1IS  | S<1:0> | 0000       |

| 10A0                        | IPUT                            | 15:0          | _             | _                   | _           |                               | IC1IP<2:0>                    |                               | IC1IS                         | <1:0>                       | _                             | _                             |                             |                       | T1IP<2:0>     |        | T1IS-  | <1:0>  | 0000       |

| 10B0                        | IPC2                            | 31:16         |               | —                   | _           |                               | INT2IP<2:0>                   |                               | INT2IS                        | S<1:0>                      | —                             | —                             | _                           | (                     | OC2IP<2:0>    | •      | OC2IS  | S<1:0> | 0000       |

| IUD0                        | 1602                            | 15:0          | _             | —                   | —           |                               | IC2IP<2:0>                    |                               | IC2IS                         | <1:0>                       | —                             | —                             | _                           |                       | T2IP<2:0>     |        | T2IS-  | <1:0>  | 0000       |

| 10C0                        | IPC3                            | 31:16         | —             | —                   | -           |                               | INT3IP<2:0>                   |                               | INT3IS                        | S<1:0>                      | —                             | —                             |                             | (                     | OC3IP<2:0>    |        | OC3IS  | S<1:0> | 0000       |

| 1000                        | 1 00                            | 15:0          |               | —                   | —           |                               | IC3IP<2:0>                    |                               | IC3IS                         | <1:0>                       | —                             | —                             | —                           |                       | T3IP<2:0>     |        | T3IS-  | <1:0>  | 0000       |

| Legend                      | <b>d:</b> x =                   | unknow        | n value on    | Reset; — = I        | unimplement | ted, read as                  | '0'. Reset va                 | lues are sho                  | wn in hexad                   | ecimal.                     |                               |                               |                             |                       |               |        |        |        |            |

#### **TABLE 7-3:** INTERRUPT REGISTER MAP FOR PIC32MX664F064H, PIC32MX664F128H, PIC32MX675F256H, PIC32MX675F512H AND DIC22MV605E512U DEVICES

DS60001156J-page 79

Except where noted, all registers in this table have corresponding CLR, SET and INV registers at their virtual addresses, plus offsets of 0x4, 0x8 and 0xC respectively. See Section 12.1.1 "CLR, SET and INV Note 1: Registers" for more information.

These bits are not available on PIC32MX664 devices. 2:

This register does not have associated CLR, SET, and INV registers. 3:

© 2009-2016 Microchip Technology Inc.

#### **Control Registers** 10.1

#### TABLE 10-1: DMA GLOBAL REGISTER MAP

| ess                         |                              | â         |       |       |       |         |         |       |      | Bi   | its  |      |      |      |      |      |           |      | ő          |

|-----------------------------|------------------------------|-----------|-------|-------|-------|---------|---------|-------|------|------|------|------|------|------|------|------|-----------|------|------------|

| Virtual Address<br>(BF88_#) | Register<br>Name             | Bit Range | 31/15 | 30/14 | 29/13 | 28/12   | 27/11   | 26/10 | 25/9 | 24/8 | 23/7 | 22/6 | 21/5 | 20/4 | 19/3 | 18/2 | 17/1      | 16/0 | All Resets |

| 0000                        | DMACON <sup>(1)</sup>        | 31:16     | _     | _     | -     | _       | _       |       | _    | _    | _    | _    | _    | _    | _    | _    | _         | _    | 0000       |

| 3000                        | DMACON                       | 15:0      | ON    | _     | _     | SUSPEND | DMABUSY | _     | _    | _    | _    | _    | _    | _    | _    | _    | _         | _    | 0000       |

| 2010                        | DMASTAT                      | 31:16     | _     | _     | _     | _       | —       | _     | _    | _    | _    | -    | _    | _    | —    | _    | _         | _    | 0000       |

| 3010                        | DIVIASTAT                    | 15:0      | _     | —     |       | —       | —       | _     |      |      |      | —    | _    | _    | RDWR | D    | MACH<2:0> | (2)  | 0000       |

| 2020                        |                              | 31.16     |       |       |       |         |         |       |      |      |      |      |      |      |      |      |           |      |            |

| 3020                        | 0 DMAADDR 0100 DMAADDR<31:0> |           |       |       |       |         |         |       |      |      |      |      |      |      |      |      |           |      |            |

| Legen                       |                              |           |       |       |       |         |         |       |      |      |      |      |      |      |      |      |           |      |            |

This register has corresponding CLR, SET and INV registers at its virtual address, plus an offset of 0x4, 0x8 and 0xC, respectively. See Section 12.1.1 "CLR, SET and INV Registers" for more information. Note 1:

DMACH<3> bit is not available on PIC32MX534/564/664/764 devices. 2:

### TABLE 10-2: DMA CRC REGISTER MAP<sup>(1)</sup>

| ess                         |                                 | 0         |       |                     |       |                        |       |           |      | В    | ts       |        |        |      |      |      |           |      | ú          |

|-----------------------------|---------------------------------|-----------|-------|---------------------|-------|------------------------|-------|-----------|------|------|----------|--------|--------|------|------|------|-----------|------|------------|

| Virtual Address<br>(BF88_#) | Register<br>Name <sup>(1)</sup> | Bit Range | 31/15 | 30/14               | 29/13 | 28/12                  | 27/11 | 26/10     | 25/9 | 24/8 | 23/7     | 22/6   | 21/5   | 20/4 | 19/3 | 18/2 | 17/1      | 16/0 | All Resets |

| 2020                        | DCRCCON                         | 31:16     | _     | _                   | BYTO  | BYTO<1:0> WBO BITO 000 |       |           |      |      |          |        |        |      | 0000 |      |           |      |            |

| 3030                        | DURCUUN                         | 15:0      | —     | —                   | —     |                        |       | PLEN<4:0> |      |      | CRCEN    | CRCAPP | CRCTYP | _    | —    | (    | CRCCH<2:0 | >    | 0000       |

| 3040                        | DCRCDATA                        | 31:16     |       |                     |       |                        |       |           |      |      | TA-31:05 |        |        |      |      |      |           |      | 0000       |

| 3040                        | DONODAIA                        | 15:0      |       | DCRCDATA<31:0> 0000 |       |                        |       |           |      |      |          |        |        |      |      |      |           |      |            |

| 3050                        | DCRCXOR                         | 31:16     |       | DCRCXOR<31:0>       |       |                        |       |           |      |      |          |        |        |      |      |      |           |      |            |

| 3030                        | DUNUAUK                         | 15:0      |       | DCRCX0R<31:0>       |       |                        |       |           |      |      |          |        |        |      |      |      |           |      |            |

Legend: x = unknown value on Reset; — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

Note 1: All registers in this table have corresponding CLR, SET and INV registers at their virtual addresses, plus offsets of 0x4, 0x8 and 0xC, respectively. See Section 12.1.1 "CLR, SET and INV Registers" for more information.

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |  |  |  |  |  |  |  |  |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|--|--|--|--|--|--|--|--|--|

| 24.24        | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |  |  |  |  |  |  |  |

| 31:24        |                   |                   |                   | DCRCDAT/          | 4<31:24>          |                   |                  |                  |  |  |  |  |  |  |  |  |  |

| 22:16        | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |  |  |  |  |  |  |  |

| 23:16        |                   |                   |                   | DCRCDAT           | A<23:16>          |                   |                  |                  |  |  |  |  |  |  |  |  |  |

| 15.0         | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |  |  |  |  |  |  |  |

| 15:8         |                   |                   |                   | DCRCDAT           | A<15:8>           |                   |                  |                  |  |  |  |  |  |  |  |  |  |

| 7.0          | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |  |  |  |  |  |  |  |

| 7:0          |                   |                   |                   | DCRCDA            | ΓA<7:0>           |                   | DCRCDATA<7:0>    |                  |  |  |  |  |  |  |  |  |  |

#### REGISTER 10-5: DCRCDATA: DMA CRC DATA REGISTER

### Legend:

| Legend:           |                  |                           |                    |

|-------------------|------------------|---------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, re | ead as '0'         |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared      | x = Bit is unknown |

#### bit 31-0 DCRCDATA<31:0>: CRC Data Register bits

Writing to this register will seed the CRC generator. Reading from this register will return the current value of the CRC. Bits greater than PLEN will return '0' on any read.

<u>When CRCTYP (DCRCCON<15>) = 1</u> (CRC module is in IP Header mode): Only the lower 16 bits contain IP header checksum information. The upper 16 bits are always '0'. Data written to this register is converted and read back in 1's complement form (current IP header checksum value).

<u>When CRCTYP (DCRCCON<15>) = 0</u> (CRC module is in LFSR mode): Bits greater than PLEN will return '0' on any read.

#### REGISTER 10-6: DCRCXOR: DMA CRCXOR ENABLE REGISTER

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |  |  |  |  |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|--|--|--|--|--|

| 31:24        | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |  |  |  |

| 31.24        |                   | DCRCXOR<31:24>    |                   |                   |                   |                   |                  |                  |  |  |  |  |  |

| 00.40        | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |  |  |  |

| 23:16        |                   |                   |                   | DCRCXOF           | 23:16>            |                   |                  |                  |  |  |  |  |  |

| 15.0         | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |  |  |  |

| 15:8         |                   |                   |                   | DCRCXO            | R<15:8>           |                   |                  |                  |  |  |  |  |  |

| 7.0          | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |  |  |  |

| 7:0          |                   |                   |                   | DCRCXO            | R<7:0>            |                   |                  |                  |  |  |  |  |  |

| Legend:           |                  |                          |                    |

|-------------------|------------------|--------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, r | ead as '0'         |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared     | x = Bit is unknown |

#### bit 31-0 DCRCXOR<31:0>: CRC XOR Register bits

<u>When CRCTYP (DCRCCON<15>) = 1</u> (CRC module is in IP Header mode): This register is unused.

<u>When CRCTYP (DCRCCON<15>) = 0</u> (CRC module is in LFSR mode):

#### 1 = Enable the XOR input to the Shift register

0 = Disable the XOR input to the Shift register; data is shifted in directly from the previous stage in the register

| Bit<br>Range | Bit<br>31/23/15/7   | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

|--------------|---------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|

| 04.04        | U-0                 | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 31:24        |                     |                   |                   | -                 | _                 |                   | _                | —                |

| 00.40        | U-0                 | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 23:16        | _                   | _                 | _                 |                   | _                 | —                 | _                | —                |

| 45.0         | R/W-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 15:8         | ON <sup>(1,2)</sup> |                   | _                 | —                 | —                 | —                 | —                | —                |

| 7.0          | U-0                 | R-y               | R-y               | R-y               | R-y               | R-y               | R/W-0            | R/W-0            |

| 7:0          | _                   |                   | SWDTPS<4:0> WDT\  |                   |                   |                   |                  |                  |

#### REGISTER 15-1: WDTCON: WATCHDOG TIMER CONTROL REGISTER

| Legend:           | y = Values set from Configuration bits on POR |                        |                    |  |

|-------------------|-----------------------------------------------|------------------------|--------------------|--|

| R = Readable bit  | W = Writable bit                              | U = Unimplemented bit, | read as '0'        |  |

| -n = Value at POR | '1' = Bit is set                              | '0' = Bit is cleared   | x = Bit is unknown |  |

bit 31-16 Unimplemented: Read as '0'

bit 0

- bit 15 **ON:** Watchdog Timer Enable bit<sup>(1,2)</sup>

- 1 = Enables the WDT if it is not enabled by the device configuration 0 = Disable the WDT if it was enabled in software

- bit 14-7 **Unimplemented:** Read as '0'

- bit 6-2 **SWDTPS<4:0>:** Shadow Copy of Watchdog Timer Postscaler Value from Device Configuration bits On reset, these bits are set to the values of the WDTPS <4:0> Configuration bits.

- bit 1 WDTWINEN: Watchdog Timer Window Enable bit

- 1 = Enable windowed Watchdog Timer

- 0 = Disable windowed Watchdog Timer

- WDTCLR: Watchdog Timer Reset bit

- 1 = Writing a '1' will clear the WDT

- 0 = Software cannot force this bit to a '0'

- Note 1: A read of this bit results in a '1' if the Watchdog Timer is enabled by the device configuration or software.

- 2: When using the 1:1 PBCLK divisor, the user's software should not read or write the peripheral's SFRs in the SYSCLK cycle immediately following the instruction that clears the module's ON bit.

#### 21.0 PARALLEL MASTER PORT (PMP)

Note: This data sheet summarizes the features of the PIC32MX5XX/6XX/7XX family of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to Section 13. "Parallel Master Port (PMP)" (DS60001128) in the "PIC32 Family Reference Manual", which is available from the Microchip web site (www.microchip.com/PIC32).

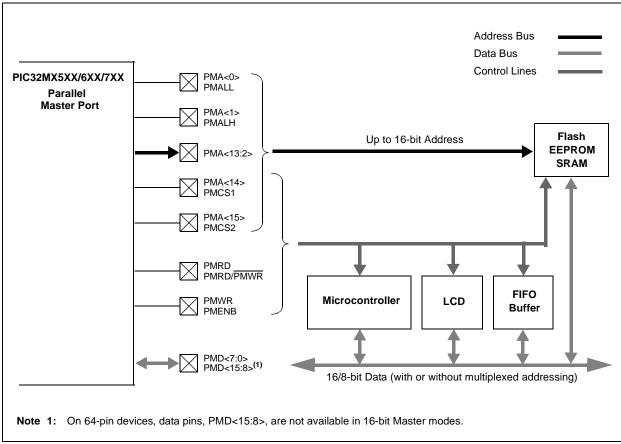

The PMP is a parallel 8-bit/16-bit input/output module specifically designed to communicate with a wide variety of parallel devices, such as communications peripherals, LCDs, external memory devices and microcontrollers. Because the interface to parallel peripherals varies significantly, the PMP module is highly configurable. Figure 21-1 shows the PMP module pinout and its connections to external devices.

**FIGURE 21-1:**

The following are key features of the PMP module:

- 8-bit and 16-bit interface

- Up to 16 programmable address lines

- Up to two Chip Select lines

- Programmable strobe options

- Individual read and write strobes, or

- Read/Write strobe with enable strobe

- · Address auto-increment/auto-decrement

- · Programmable address/data multiplexing

- Programmable polarity on control signals

- · Parallel Slave Port support

- Legacy addressable

- Address support

- 4-byte deep auto-incrementing buffer

- · Programmable wait states

- · Operates during Sleep and Idle modes

- Fast bit manipulation using CLR, SET and INV registers

Note: On 64-pin devices, the PMD<15:8> data pins are not available.

PMP MODULE PINOUT AND CONNECTIONS TO EXTERNAL DEVICES

### 21.1 Control Registers

### TABLE 21-1: PARALLEL MASTER PORT REGISTER MAP

|                                         |                                 |           |                                                                                                                                                       |               |       |       |         |        |        | Bi     | ts      |       |      |      |      |      |      |      |            |

|-----------------------------------------|---------------------------------|-----------|-------------------------------------------------------------------------------------------------------------------------------------------------------|---------------|-------|-------|---------|--------|--------|--------|---------|-------|------|------|------|------|------|------|------------|

| Virtual Address<br>(BF80_#)<br>Register | Register<br>Name <sup>(1)</sup> | Bit Range | 31/15                                                                                                                                                 | 30/14         | 29/13 | 28/12 | 27/11   | 26/10  | 25/9   | 24/8   | 23/7    | 22/6  | 21/5 | 20/4 | 19/3 | 18/2 | 17/1 | 16/0 | All Resets |

| 7000 PM0                                | /CON                            | 31:16     | _                                                                                                                                                     | _             | _     | _     | _       | _      | _      | _      | _       | _     | _    | _    | —    | _    | —    | _    | 0000       |

| 7000 1 100                              |                                 | 15:0      | ON                                                                                                                                                    | —             | SIDL  | ADRMU | IX<1:0> | PMPTTL | PTWREN | PTRDEN | CSF     | <1:0> | ALP  | CS2P | CS1P | —    | WRSP | RDSP | 0000       |

| 7010 PMM                                | MODE                            | 31:16     | —                                                                                                                                                     | —             | —     | —     | —       | —      | —      | —      | —       | —     | —    | —    | —    | —    | —    | —    | 0000       |

| 7010 Pivily                             | NODE                            | 15:0      | BUSY         IRQM<1:0>         INCM<1:0>         MODE16         MODE<1:0>         WAITB<1:0>         WAITM<3:0>         WAITE<1:0>         WAITE<1:0> |               |       |       | 0000    |        |        |        |         |       |      |      |      |      |      |      |            |

| 7020 PMA                                |                                 | 31:16     |                                                                                                                                                       | _             | _     | _     | _       | _      | _      |        | _       | -     | -    | _    | _    | _    | _    | _    | 0000       |

| 7020 PINA                               | IADDR                           | 15:0      | CS2EN/A15 CS1EN/A14 ADDR<13:0> 00                                                                                                                     |               |       |       |         |        |        | 0000   |         |       |      |      |      |      |      |      |            |

| 7000 040                                |                                 | 31:16     |                                                                                                                                                       | DATAOUT<31:0> |       |       |         |        |        | 0000   |         |       |      |      |      |      |      |      |            |

| 7030 PMD                                |                                 | 15:0      |                                                                                                                                                       |               |       |       |         |        |        | DATAOU | 1<31:0> |       |      |      |      |      |      |      | 0000       |

| 7040 DM                                 | MDIN                            | 31:16     |                                                                                                                                                       |               |       |       |         |        |        |        | .01.0   |       |      |      |      |      |      |      | 0000       |

| 7040 PM                                 |                                 | 15:0      |                                                                                                                                                       | DATAIN<31:0>  |       |       |         |        |        | 0000   |         |       |      |      |      |      |      |      |            |

| 7050 014                                | MAEN                            | 31:16     |                                                                                                                                                       | _             | _     | _     | _       | _      | _      |        | _       | -     | -    | _    | _    | _    | _    | _    | 0000       |

| 7050 PM/                                | VIAEN                           | 15:0      |                                                                                                                                                       |               |       |       |         |        |        | PTEN<  | :15:0>  |       |      |      |      |      |      |      | 0000       |

| 7000 0140                               | 10TAT                           | 31:16     | _                                                                                                                                                     | _             | _     | _     | _       | _      | _      | _      | _       | _     | —    | _    | _    | _    | _    | _    | 0000       |

| 7060 PMS                                | ISTAL                           | 15:0      | IBF                                                                                                                                                   | IBOV          | _     | -     | IB3F    | IB2F   | IB1F   | IB0F   | OBE     | OBUF  | —    | -    | OB3E | OB2E | OB1E | OB0E | 008F       |

Legend: x = unknown value on Reset; — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

Note 1: All registers in this table have corresponding CLR, SET and INV registers at their virtual addresses, plus offsets of 0x4, 0x8 and 0xC, respectively. See Section 12.1.1 "CLR, SET and INV Registers" for more information.

| REGISTER 23-2: AD1CON2: ADC CONTROL REGISTER 2 |

|------------------------------------------------|

|------------------------------------------------|

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|

| 24.24        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 31:24        | —                 | —                 | —                 | —                 | —                 | —                 | —                | —                |

| 00.40        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 23:16        |                   |                   | —                 | _                 | —                 | —                 | —                | —                |

| 45.0         | R/W-0             | R/W-0             | R/W-0             | R/W-0             | U-0               | R/W-0             | U-0              | U-0              |

| 15:8         | VCFG<2:0>         |                   |                   | OFFCAL            | —                 | CSCNA             | —                | —                |

| 7.0          | R-0               | U-0               | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |

| 7:0          | BUFS              | _                 |                   | SMPI<3:0>         |                   |                   |                  | ALTS             |

#### Legend:

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, re | ad as '0'          |

|-------------------|------------------|---------------------------|--------------------|

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared      | x = Bit is unknown |

#### bit 31-16 Unimplemented: Read as '0'

bit 15-13 VCFG<2:0>: Voltage Reference Configuration bits

| Bit Value | VREFH              | VREFL              |

|-----------|--------------------|--------------------|

| lxx       | AVdd               | AVss               |

| 011       | External VREF+ pin | External VREF- pin |

| 010       | AVdd               | External VREF- pin |

| 001       | External VREF+ pin | AVss               |

| 000       | AVDD               | AVss               |

#### bit 12 **OFFCAL:** Input Offset Calibration Mode Select bit

1 = Enable Offset Calibration mode

Positive and negative inputs of the S&H circuit are connected to VREFL.

- 0 = Disable Offset Calibration mode

- The inputs to the S&H circuit are controlled by AD1CHS or AD1CSSL.

#### bit 11 Unimplemented: Read as '0'

- bit 10 CSCNA: Input Scan Select bit

- 1 = Scan inputs

- 0 = Do not scan inputs

- bit 9-8 Unimplemented: Read as '0'

- bit 7 BUFS: Buffer Fill Status bit

- Only valid when BUFM = 1.

- 1 = ADC is currently filling buffer 0x8-0xF, user should access data in 0x0-0x7

- 0 = ADC is currently filling buffer 0x0-0x7, user should access data in 0x8-0xF

#### bit 6 Unimplemented: Read as '0'

#### bit 5-2 SMPI<3:0>: Sample/Convert Sequences Per Interrupt Selection bits

- 1111 = Interrupts at the completion of conversion for each 16<sup>th</sup> sample/convert sequence 1110 = Interrupts at the completion of conversion for each 15<sup>th</sup> sample/convert sequence

- $\pm\pm\pm\pm$  = interrupts at the completion of conversion for each 15"' sample/convert sequence

- •

- 0001 = Interrupts at the completion of conversion for each  $2^{nd}$  sample/convert sequence 0000 = Interrupts at the completion of conversion for each sample/convert sequence

- bit 1 BUFM: ADC Result Buffer Mode Select bit

- 1 = Buffer configured as two 8-word buffers, ADC1BUF7-ADC1BUF0, ADC1BUFF-ADCBUF8

- 0 = Buffer configured as one 16-word buffer ADC1BUFF-ADC1BUF0

- bit 0 ALTS: Alternate Input Sample Mode Select bit

- 1 = Uses Sample A input multiplexer settings for first sample, and then alternates between Sample B and Sample A input multiplexer settings for all subsequent samples

- 0 = Always use Sample A input multiplexer settings

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3       | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------------|-------------------|------------------|------------------|

| 24.24        | U-0               | U-0               | U-0               | U-0               | U-0                     | U-0               | U-0              | U-0              |

| 31:24        | _                 | _                 | _                 | —                 | —                       |                   | _                | —                |

| 22:46        | U-0               | U-0               | U-0               | U-0               | U-0                     | U-0               | U-0              | U-0              |

| 23:16        | —                 | —                 | _                 | —                 | _                       | _                 | —                | —                |

| 15.0         | U-0               | U-0               | U-0               | R-0               | R-0                     | R-0               | R-0              | R-0              |

| 15:8         | —                 | —                 | _                 |                   | FILHIT<4:0>             |                   |                  |                  |

| 7.0          | U-0               | R-1               | R-0               | R-0               | R-0                     | R-0               | R-0              | R-0              |

| 7:0          | _                 |                   |                   | l                 | CODE<6:0> <sup>(1</sup> | )                 |                  |                  |

#### REGISTER 24-4: CiVEC: CAN INTERRUPT CODE REGISTER

#### Legend:

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, r | read as '0'        |

|-------------------|------------------|--------------------------|--------------------|

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared     | x = Bit is unknown |

#### bit 31-13 Unimplemented: Read as '0'

| bit 12-8 | FILHIT<4:0>: Filter Hit Number bit                  |

|----------|-----------------------------------------------------|

|          | 11111 = Filter 31                                   |

|          | 11110 = Filter 30                                   |

|          | •                                                   |

|          | •                                                   |

|          | 00001 = Filter 1                                    |

|          | 00000 = Filter 0                                    |

| bit 7    | Unimplemented: Read as '0'                          |

| bit 6-0  | ICODE<6:0>: Interrupt Flag Code bits <sup>(1)</sup> |

|          | 11111111 = Reserved                                 |

|          | •                                                   |

|          | •                                                   |

|          | •<br>1001001 = Reserved                             |

|          | 1001000 = Invalid message received (IVRIF)          |

|          | 1001111 = CAN module mode change (MODIF)            |

|          | 1000110 = CAN timestamp timer (CTMRIF)              |

|          | 1000101 = Bus bandwidth error (SERRIF)              |

|          | 1000100 = Address error interrupt (SERRIF)          |

|          | 1000011 = Receive FIFO overflow interrupt (RBOVIF)  |

|          | 1000010 = Wake-up interrupt (WAKIF)                 |

|          | 1000001 = Error Interrupt (CERRIF)                  |

|          | 1000000 = No interrupt                              |

|          | 0111111 = Reserved                                  |

|          | •                                                   |

|          | •                                                   |

|          | 0100000 = Reserved                                  |

|          | 0011111 = FIFO31 Interrupt (CiFSTAT<31> set)        |

|          | 0011110 = FIFO30 Interrupt (CiFSTAT<30> set)        |

|          | •                                                   |

|          | •                                                   |

|          | 0000001 = FIFO1 Interrupt (CiFSTAT<1> set)          |

|          | 0000000 = FIFO0 Interrupt (CiFSTAT<0> set)          |

|          |                                                     |

Note 1: These bits are only updated for enabled interrupts.

| REGISTER 25-23: | EMAC1CFG1: ETHERNET CONTROLLER MAC CONFIGURATION 1 REGISTER |

|-----------------|-------------------------------------------------------------|

|                 |                                                             |

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|

| 31:24        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 31.24        | —                 | —                 | —                 |                   | _                 | —                 | —                | —                |

| 23:16        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 23.10        |                   | —                 | —                 | _                 | _                 |                   |                  | —                |

|              | R/W-1             | R/W-0             | U-0               | U-0               | R/W-0             | R/W-0             | R/W-0            | R/W-0            |

| 15:8         | SOFT<br>RESET     | SIM<br>RESET      | —                 |                   | RESET<br>RMCS     | RESET<br>RFUN     | RESET<br>TMCS    | RESET<br>TFUN    |

| 7:0          | U-0               | U-0               | U-0               | R/W-0             | R/W-1             | R/W-1             | R/W-0            | R/W-1            |

|              |                   |                   | _                 | LOOPBACK          | TX<br>PAUSE       | RX<br>PAUSE       | PASSALL          | RX<br>ENABLE     |

| Legend: |  |

|---------|--|

| Logona.           |                  |                                    |                    |  |  |

|-------------------|------------------|------------------------------------|--------------------|--|--|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read as '0' |                    |  |  |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared               | x = Bit is unknown |  |  |

#### bit 31-16 Unimplemented: Read as '0'

| bit 15    | SOFTRESET: Soft Reset bit                                                                               |

|-----------|---------------------------------------------------------------------------------------------------------|

|           | Setting this bit will put the MACMII in reset. Its default value is '1'.                                |

| bit 14    | SIMRESET: Simulation Reset bit                                                                          |

|           | Setting this bit will cause a reset to the random number generator within the Transmit Function.        |

| bit 13-12 | Unimplemented: Read as '0'                                                                              |

| bit 11    | RESETRMCS: Reset MCS/RX bit                                                                             |

|           | Setting this bit will put the MAC Control Sub-layer/Receive domain logic in reset.                      |

| bit 10    | RESETRFUN: Reset RX Function bit                                                                        |

|           | Setting this bit will put the MAC Receive function logic in reset.                                      |

| bit 9     | RESETTMCS: Reset MCS/TX bit                                                                             |

|           | Setting this bit will put the MAC Control Sub-layer/TX domain logic in reset.                           |

| bit 8     | RESETTFUN: Reset TX Function bit                                                                        |

|           | Setting this bit will put the MAC Transmit function logic in reset.                                     |

| bit 7-5   | Unimplemented: Read as '0'                                                                              |

| bit 4     | LOOPBACK: MAC Loopback mode bit                                                                         |

|           | 1 = MAC Transmit interface is loop backed to the MAC Receive interface                                  |

| bit 3     | 0 = MAC normal operation<br><b>TXPAUSE:</b> MAC TX Flow Control bit                                     |

| DILS      | 1 = PAUSE Flow Control frames are allowed to be transmitted                                             |

|           | 1 = PAUSE Flow Control frames are allowed to be transmitted $0 = PAUSE Flow Control frames are blocked$ |

| bit 2     | RXPAUSE: MAC RX Flow Control bit                                                                        |

|           | 1 = The MAC acts upon received PAUSE Flow Control frames                                                |

|           | 0 = Received PAUSE Flow Control frames are ignored                                                      |

| bit 1     | PASSALL: MAC Pass all Receive Frames bit                                                                |

|           | 1 = The MAC will accept all frames regardless of type (Normal vs. Control)                              |

|           | 0 = The received Control frames are ignored                                                             |

| bit 0     | RXENABLE: MAC Receive Enable bit                                                                        |

|           | 1 = Enable the MAC receiving of frames                                                                  |

|           |                                                                                                         |

0 = Disable the MAC receiving of frames

**Note:** Both 16-bit and 32-bit accesses are allowed to these registers (including the SET, CLR and INV registers). 8-bit accesses are not allowed and are ignored by the hardware.

### REGISTER 25-24: EMAC1CFG2: ETHERNET CONTROLLER MAC CONFIGURATION 2 REGISTER (CONTINUED)

- VLANPAD: VLAN Pad Enable bit<sup>(1,2)</sup> bit 6 1 = The MAC will pad all short frames to 64 bytes and append a valid CRC 0 = The MAC does not perform padding of short frames PADENABLE: Pad/CRC Enable bit<sup>(1,3)</sup> bit 5 1 = The MAC will pad all short frames 0 = The frames presented to the MAC have a valid length bit 4 CRCENABLE: CRC Enable1 bit 1 = The MAC will append a CRC to every frame whether padding was required or not. Must be set if the PADENABLE bit is set. 0 = The frames presented to the MAC have a valid CRC bit 3 DELAYCRC: Delayed CRC bit This bit determines the number of bytes, if any, of proprietary header information that exist on the front of the IEEE 802.3 frames. 1 = Four bytes of header (ignored by the CRC function) 0 = No proprietary header bit 2 HUGEFRM: Huge Frame enable bit 1 = Frames of any length are transmitted and received 0 = Huge frames are not allowed for receive or transmit LENGTHCK: Frame Length checking bit bit 1 1 = Both transmit and receive frame lengths are compared to the Length/Type field. If the Length/Type field represents a length then the check is performed. Mismatches are reported on the transmit/receive statistics vector. 0 = Length/Type field check is not performed bit 0 FULLDPLX: Full-Duplex Operation bit 1 = The MAC operates in Full-Duplex mode 0 = The MAC operates in Half-Duplex mode

- Note 1: Table 25-6 provides a description of the pad function based on the configuration of this register.

- 2: This bit is ignored if the PADENABLE bit is cleared.

- **3:** This bit is used in conjunction with the AUTOPAD and VLANPAD bits.

**Note:** Both 16-bit and 32-bit accesses are allowed to these registers (including the SET, CLR and INV registers). 8-bit accesses are not allowed and are ignored by the hardware

#### TABLE 25-6:PAD OPERATION

| Туре | AUTOPAD | VLANPAD | PADENABLE | Action                                                                                  |  |

|------|---------|---------|-----------|-----------------------------------------------------------------------------------------|--|

| Any  | x       | x       | 0         | No pad, check CRC                                                                       |  |

| Any  | 0       | 0       | 1         | Pad to 60 Bytes, append CRC                                                             |  |

| Any  | x       | 1       | 1         | Pad to 64 Bytes, append CRC                                                             |  |

| Any  | 1       | 0       | 1         | If untagged: Pad to 60 Bytes, append CRC<br>If VLAN tagged: Pad to 64 Bytes, append CRC |  |

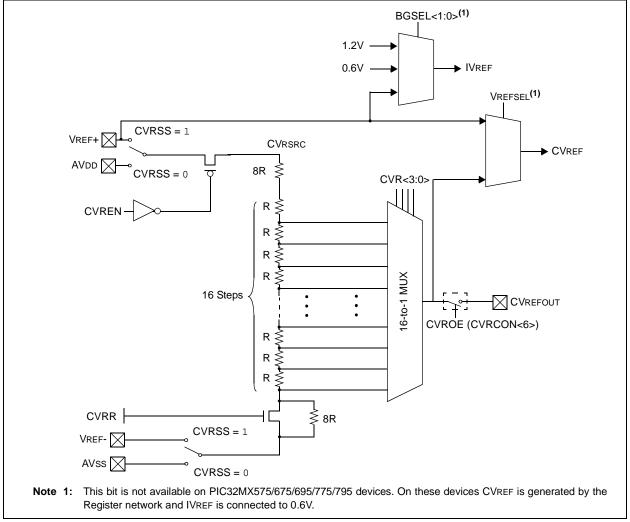

### 27.0 COMPARATOR VOLTAGE REFERENCE (CVREF)

Note: This data sheet summarizes the features of the PIC32MX5XX/6XX/7XX family of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to Section 20. "Comparator Voltage Reference (CVREF)" (DS60001109) in the "PIC32 Family Reference Manual", which is available from the Microchip web site (www.microchip.com/PIC32).

The CVREF module is a 16-tap, resistor ladder network that provides a selectable reference voltage. Although its primary purpose is to provide a reference for the analog comparators, it also may be used independently of them. A block diagram of the module is illustrated in Figure 27-1. The resistor ladder is segmented to provide two ranges of voltage reference values and has a power-down function to conserve power when the reference is not being used. The module's supply reference can be provided from either device VDD/Vss or an external voltage reference. The CVREF output is available for the comparators and typically available for pin output.

Key features of the CVREF module include:

- High and low range selection

- Sixteen output levels available for each range

- Internally connected to comparators to conserve device pins

- · Output can be connected to a pin

NOTES:

#### REGISTER 29-2: DEVCFG1: DEVICE CONFIGURATION WORD 1 (CONTINUED)

- bit 13-12 **FPBDIV<1:0>:** Peripheral Bus Clock Divisor Default Value bits

- 11 = PBCLK is SYSCLK divided by 8

- 10 = PBCLK is SYSCLK divided by 4

- 01 = PBCLK is SYSCLK divided by 2

- 00 = PBCLK is SYSCLK divided by 1

- bit 11 Reserved: Write '1'

- bit 10 OSCIOFNC: CLKO Enable Configuration bit

- 1 = CLKO output is disabled

- 0 = CLKO output signal is active on the OSCO pin; the Primary Oscillator must be disabled or configured for External Clock mode (EC) for the CLKO to be active (POSCMOD<1:0> = 11 or 00)

- bit 9-8 **POSCMOD<1:0>:** Primary Oscillator Configuration bits

- 11 = Primary Oscillator is disabled

- 10 = HS Oscillator mode is selected

- 01 = XT Oscillator mode is selected

- 00 = External Clock mode is selected

- bit 7 IESO: Internal External Switchover bit

- 1 = Internal External Switchover mode is enabled (Two-Speed Start-up is enabled)

- 0 = Internal External Switchover mode is disabled (Two-Speed Start-up is disabled)

- bit 6 Reserved: Write '1'

- bit 5 FSOSCEN: Secondary Oscillator Enable bit

- 1 = Enable the Secondary Oscillator

- 0 = Disable the Secondary Oscillator

- bit 4-3 Reserved: Write '1'

- bit 2-0 **FNOSC<2:0>:** Oscillator Selection bits

- 111 = Fast RC Oscillator with divide-by-N (FRCDIV)

- 110 = FRCDIV16 Fast RC Oscillator with fixed divide-by-16 postscaler

- 101 = Low-Power RC Oscillator (LPRC)

- 100 = Secondary Oscillator (Sosc)

- 011 = Primary Oscillator (Posc) with PLL module (XT+PLL, HS+PLL, EC+PLL)

- 010 = Primary Oscillator (XT, HS, EC)<sup>(1)</sup>

- 001 = Fast RC Oscillator with divide-by-N with PLL module (FRCDIV+PLL)

- 000 = Fast RC Oscillator (FRC)

- **Note 1:** Do not disable the POSC (POSCMOD = 11) when using this oscillator source.

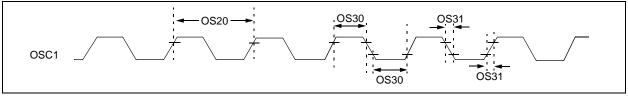

#### 32.2 AC Characteristics and Timing Parameters

The information contained in this section defines PIC32MX5XX/6XX/7XX AC characteristics and timing parameters.

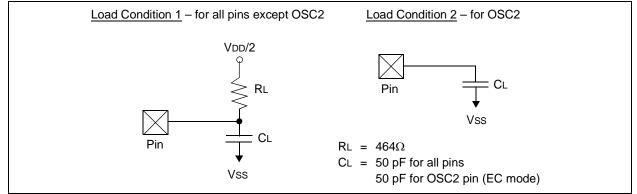

#### FIGURE 32-1: LOAD CONDITIONS FOR DEVICE TIMING SPECIFICATIONS

#### TABLE 32-16: CAPACITIVE LOADING REQUIREMENTS ON OUTPUT PINS

| AC CHARACTERISTICS |        |                       | $\begin{array}{l} \mbox{Standard Operating Conditions: 2.3V to 3.6V} \\ \mbox{(unless otherwise stated)} \\ \mbox{Operating temperature} & -40^\circ C \leq TA \leq +85^\circ C \mbox{ for Industrial} \\ & -40^\circ C \leq TA \leq +105^\circ C \mbox{ for V-Temp} \end{array}$ |                        |      |       |                                                                         |

|--------------------|--------|-----------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------|------|-------|-------------------------------------------------------------------------|

| Param.<br>No.      | Symbol | Characteristics       | Min.                                                                                                                                                                                                                                                                              | Typical <sup>(1)</sup> | Max. | Units | Conditions                                                              |

| DO50               | Cosco  | OSC2 pin              |                                                                                                                                                                                                                                                                                   | _                      | 15   | pF    | In XT and HS modes when an<br>external crystal is used to drive<br>OSC1 |