Welcome to **E-XFL.COM**

What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded - Microcontrollers</u>"

| Details                    |                                                                                 |

|----------------------------|---------------------------------------------------------------------------------|

| Product Status             | Active                                                                          |

| Core Processor             | MIPS32® M4K™                                                                    |

| Core Size                  | 32-Bit Single-Core                                                              |

| Speed                      | 80MHz                                                                           |

| Connectivity               | Ethernet, I <sup>2</sup> C, SPI, UART/USART, USB OTG                            |

| Peripherals                | Brown-out Detect/Reset, DMA, POR, PWM, WDT                                      |

| Number of I/O              | 53                                                                              |

| Program Memory Size        | 64KB (64K x 8)                                                                  |

| Program Memory Type        | FLASH                                                                           |

| EEPROM Size                | -                                                                               |

| RAM Size                   | 32K x 8                                                                         |

| Voltage - Supply (Vcc/Vdd) | 2.3V ~ 3.6V                                                                     |

| Data Converters            | A/D 16x10b                                                                      |

| Oscillator Type            | Internal                                                                        |

| Operating Temperature      | -40°C ~ 105°C (TA)                                                              |

| Mounting Type              | Surface Mount                                                                   |

| Package / Case             | 64-VFQFN Exposed Pad                                                            |

| Supplier Device Package    | 64-VQFN (9x9)                                                                   |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic32mx664f064ht-v-mr |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

#### TABLE 7: PIN NAMES FOR 100-PIN USB AND CAN DEVICES

#### 100-PIN TQFP (TOP VIEW)

PIC32MX534F064L PIC32MX564F064L PIC32MX564F128L PIC32MX575F512L PIC32MX575F256L

100

1

| Pin# | Full Pin Name                |

|------|------------------------------|

| 1    | RG15                         |

| 2    | VDD                          |

| 3    | PMD5/RE5                     |

| 4    | PMD6/RE6                     |

| 5    | PMD7/RE7                     |

| 6    | T2CK/RC1                     |

| 7    | T3CK/RC2                     |

| 8    | T4CK/RC3                     |

| 9    | T5CK/SDI1/RC4                |

| 10   | SCK2/U6TX/U3RTS/PMA5/CN8/RG6 |

| 11   | SDA4/SDI2/U3RX/PMA4/CN9/RG7  |

| 12   | SCL4/SDO2/U3TX/PMA3/CN10/RG8 |

| 13   | MCLR                         |

| 14   | SS2/U6RX/U3CTS/PMA2/CN11/RG9 |

| 15   | Vss                          |

| 16   | VDD                          |

| 17   | TMS/RA0                      |

| 18   | INT1/RE8                     |

| 19   | INT2/RE9                     |

| 20   | AN5/C1IN+/VBUSON/CN7/RB5     |

| 21   | AN4/C1IN-/CN6/RB4            |

| 22   | AN3/C2IN+/CN5/RB3            |

| 23   | AN2/C2IN-/CN4/RB2            |

| 24   | PGEC1/AN1/CN3/RB1            |

| 25   | PGED1/AN0/CN2/RB0            |

| 26   | PGEC2/AN6/OCFA/RB6           |

| 27   | PGED2/AN7/RB7                |

| 28   | VREF-/CVREF-/PMA7/RA9        |

| 29   | VREF+/CVREF+/PMA6/RA10       |

| 30   | AVDD                         |

| 31   | AVss                         |

| 32   | AN8/C1OUT/RB8                |

| 33   | AN9/C2OUT/RB9                |

| 34   | AN10/CVREFOUT/PMA13/RB10     |

| 35   | AN11/PMA12/RB11              |

| Pin a | Full Pin Name                  |

|-------|--------------------------------|

| 36    | Vss                            |

| 37    | VDD                            |

| 38    | TCK/RA1                        |

| 39    | AC1TX/SCK4/U5TX/U2RTS/RF13     |

| 40    | AC1RX/SS4/U5RX/U2CTS/RF12      |

| 41    | AN12/PMA11/RB12                |

| 42    | AN13/PMA10/RB13                |

| 43    | AN14/PMALH/PMA1/RB14           |

| 44    | AN15/OCFB/PMALL/PMA0/CN12/RB15 |

| 45    | Vss                            |

| 46    | VDD                            |

| 47    | SS3/U4RX/U1CTS/CN20/RD14       |

| 48    | SCK3/U4TX/U1RTS/CN21/RD15      |

| 49    | SDA5/SDI4/U2RX/PMA9/CN17/RF4   |

| 50    | SCL5/SDO4/U2TX/PMA8/CN18/RF5   |

| 51    | USBID/RF3                      |

| 52    | SDA3/SDI3/U1RX/RF2             |

| 53    | SCL3/SDO3/U1TX/RF8             |

| 54    | VBUS                           |

| 55    | VUSB3V3                        |

| 56    | D-/RG3                         |

| 57    | D+/RG2                         |

| 58    | SCL2/RA2                       |

| 59    | SDA2/RA3                       |

| 60    | TDI/RA4                        |

| 61    | TDO/RA5                        |

| 62    | VDD                            |

| 63    | OSC1/CLKI/RC12                 |

| 64    | OSC2/CLKO/RC15                 |

| 65    | Vss                            |

| 66    | SCL1/INT3/RA14                 |

| 67    | SDA1/INT4/RA15                 |

| 68    | RTCC/IC1/RD8                   |

| 69    | SS1/IC2/RD9                    |

| 70    | SCK1/IC3/PMCS2/PMA15/RD10      |

|       | <u> </u>                       |

Note 1: Shaded pins are 5V tolerant.

#### TABLE 8: PIN NAMES FOR 100-PIN USB AND ETHERNET DEVICES (CONTINUED)

#### 100-PIN TQFP (TOP VIEW)

PIC32MX664F064L PIC32MX664F128L PIC32MX675F256L PIC32MX675F512L PIC32MX695F512L

100

1

| Pin# | Full Pin Name                   |

|------|---------------------------------|

| 71   | EMDC/AEMDC/IC4/PMCS1/PMA14/RD11 |

| 72   | SDO1/OC1/INT0/RD0               |

| 73   | SOSCI/CN1/RC13                  |

| 74   | SOSCO/T1CK/CN0/RC14             |

| 75   | Vss                             |

| 76   | OC2/RD1                         |

| 77   | OC3/RD2                         |

| 78   | OC4/RD3                         |

| 79   | ETXD2/IC5/PMD12/RD12            |

| 80   | ETXD3/PMD13/CN19/RD13           |

| 81   | OC5/PMWR/CN13/RD4               |

| 82   | PMRD/CN14/RD5                   |

| 83   | ETXEN/PMD14/CN15/RD6            |

| 84   | ETXCLK/PMD15/CN16/RD7           |

| 85   | VCAP/VDDCORE                    |

| Pin# | Full Pin Name   |

|------|-----------------|

| 86   | VDD             |

| 87   | ETXD1/PMD11/RF0 |

| 88   | ETXD0/PMD10/RF1 |

| 89   | ETXERR/PMD9/RG1 |

| 90   | PMD8/RG0        |

| 91   | TRCLK/RA6       |

| 92   | TRD3/RA7        |

| 93   | PMD0/RE0        |

| 94   | PMD1/RE1        |

| 95   | TRD2/RG14       |

| 96   | TRD1/RG12       |

| 97   | TRD0/RG13       |

| 98   | PMD2/RE2        |

| 99   | PMD3/RE3        |

| 100  | PMD4/RE4        |

Note 1: Shaded pins are 5V tolerant.

**NOTES:**

NOTES:

TABLE 10-3: DMA CHANNELS 0-7 REGISTER MAP (CONTINUED)

| ess                         |                                 | 0         |                  |       |       |       |       |       |      | Ві     | its     |      |      |       |         |      |      |      | "          |

|-----------------------------|---------------------------------|-----------|------------------|-------|-------|-------|-------|-------|------|--------|---------|------|------|-------|---------|------|------|------|------------|

| Virtual Address<br>(BF88_#) | Register<br>Name <sup>(1)</sup> | Bit Range | 31/15            | 30/14 | 29/13 | 28/12 | 27/11 | 26/10 | 25/9 | 24/8   | 23/7    | 22/6 | 21/5 | 20/4  | 19/3    | 18/2 | 17/1 | 16/0 | All Resets |

| 35F0                        | DCH7SSIZ 3                      | 31:16     | _                | _     | _     | _     | _     | _     | _    | _      | _       | _    | _    | _     | _       | _    | _    | _    | 0000       |

| 00. 0                       | 2000.2                          | 15:0      |                  |       |       |       |       |       |      | CHSSIZ | Z<15:0> |      |      |       |         |      | _    |      | 0000       |

| 2000                        | DOUZDOIZ                        | 31:16     | _                | _     | _     | _     | _     | _     | _    | _      | _       | _    | _    | _     | _       | _    | _    | _    | 0000       |

| 3600                        | DCH7DSIZ                        | 15:0      | CHDSIZ<15:0> 000 |       |       |       |       |       |      |        |         |      |      |       | 0000    |      |      |      |            |

| 2610                        | DCH7SPTR                        | 31:16     | -                | _     | -     | _     | _     | -     | ı    | -      | _       | _    | _    | _     | _       | _    | _    | 1    | 0000       |

| 3610                        | DCH/3P1K                        | 15:0      | CHSPTR<15:0> 000 |       |       |       |       |       |      |        |         |      |      | 0000  |         |      |      |      |            |

| 2620                        | DCH7DPTR                        | 31:16     | -                | _     | _     | _     | -     | _     | _    | _      | _       | _    | _    | _     | _       | _    | _    | _    | 0000       |

| 3620                        | DCH/DP1K                        | 15:0      |                  |       |       |       |       |       |      | CHDPT  | R<15:0> |      |      |       |         |      |      |      | 0000       |

| 0000                        | DOLUZO017                       | 31:16     | _                | _     | _     | _     | _     | _     | _    | _      | _       | _    | _    | _     | _       | _    | _    | _    | 0000       |

| 3630                        | DCH7CSIZ                        | 15:0      |                  |       |       |       |       |       |      | CHCSIZ | Z<15:0> |      |      |       |         |      |      |      | 0000       |

| 0040                        | DOUZODED                        | 31:16     | _                | _     | _     | _     | _     | _     | _    | _      | _       | _    | _    | _     | _       | _    | _    | _    | 0000       |

| 3640                        | DCH7CPTR                        | 15:0      |                  |       |       |       |       |       |      | CHCPT  | R<15:0> | •    | •    | •     | •       | •    | •    |      | 0000       |

| 0050                        | DOLLZDAT                        | 31:16     | _                | _     | _     | _     | _     | _     | _    | _      | _       | _    | _    | _     | _       | _    | _    | _    | 0000       |

| 3650                        | 3650 DCH7DAT                    | 15:0      | _                | _     |       | _     | _     |       |      | _      |         | •    | •    | CHPDA | \T<7:0> | •    | •    |      | 0000       |

Legend: x = unknown value on Reset; — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

Note 1: All registers in this table have corresponding CLR, SET and INV registers at their virtual addresses, plus offsets of 0x4, 0x8 and 0xC, respectively. See Section 12.1.1 "CLR, SET and INV Registers" for more information.

2: DMA channels 4-7 are not available on PIC32MX534/564/664/764 devices.

#### 11.0 USB ON-THE-GO (OTG)

Note:

This data sheet summarizes the features of the PIC32MX5XX/6XX/7XX family of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to **Section 27. "USB On-The-Go (OTG)"** (DS60001126) in the "PIC32 Family Reference Manual", which is available from the Microchip web site (www.microchip.com/PIC32).

The Universal Serial Bus (USB) module contains analog and digital components to provide a USB 2.0 full-speed and low-speed embedded Host, full-speed Device or OTG implementation with a minimum of external components. This module in Host mode is intended for use as an embedded host and therefore does not implement a UHCI or OHCI controller.

The USB module consists of the clock generator, the USB voltage comparators, the transceiver, the Serial Interface Engine (SIE), a dedicated USB DMA controller, pull-up and pull-down resistors, and the register interface. A block diagram of the PIC32 USB OTG module is presented in Figure 11-1.

The clock generator provides the 48 MHz clock required for USB full-speed and low-speed communication. The voltage comparators monitor the voltage on the VBUS pin to determine the state of the bus. The transceiver provides the analog translation between the USB bus and the digital logic. The SIE is a state machine that transfers data to and from the endpoint buffers and generates the hardware protocol for data transfers. The USB DMA controller transfers data between the data buffers in RAM and the SIE. The integrated pull-up and pull-down resistors eliminate the need for external signaling components. The register interface allows the CPU to configure and communicate with the module.

The USB module includes the following features:

- USB Full-speed support for host and device

- · Low-speed host support

- USB OTG support

- · Integrated signaling resistors

- Integrated analog comparators for VBUS monitoring

- · Integrated USB transceiver

- · Transaction handshaking performed by hardware

- Endpoint buffering anywhere in system RAM

- Integrated DMA to access system RAM and Flash

Note:

The implementation and use of the USB specifications, as well as other third party specifications or technologies, may require licensing; including, but not limited to, USB Implementers Forum, Inc. (also referred to as USB-IF). The user is fully responsible for investigating and satisfying any applicable licensing obligations.

#### REGISTER 11-11: U1CON: USB CONTROL REGISTER (CONTINUED)

- bit 1 PPBRST: Ping-Pong Buffers Reset bit

- 1 = Reset all Even/Odd buffer pointers to the Even buffer descriptor banks

- 0 = Even/Odd buffer pointers are not reset

- bit 0 USBEN: USB Module Enable bit(4)

- 1 = USB module and supporting circuitry is enabled

- 0 = USB module and supporting circuitry is disabled

SOFEN: SOF Enable bit (5)

- 1 = SOF token is sent every 1 ms

- 0 = SOF token is disabled

- **Note 1:** Software is required to check this bit before issuing another token command to the U1TOK register (see Register 11-15).

- 2: All host control logic is reset any time that the value of this bit is toggled.

- 3: Software must set RESUME for 10 ms in Device mode, or for 25 ms in Host mode, and then clear it to enable remote wake-up. In Host mode, the USB module will append a low-speed EOP to the RESUME signaling when this bit is cleared.

- 4: Device mode.

- 5: Host mode.

REGISTER 13-1: T1CON: TYPE A TIMER CONTROL REGISTER

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|

| 24.24        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 31:24        | -                 | _                 | _                 |                   |                   | -                 | -                | _                |

| 23:16        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 23.10        | _                 | _                 | _                 | _                 | _                 | _                 | _                | _                |

| 15.0         | R/W-0             | U-0               | R/W-0             | R/W-0             | R-0               | U-0               | U-0              | U-0              |

| 15:8         | ON <sup>(1)</sup> | _                 | SIDL              | TWDIS             | TWIP              | _                 | _                | _                |

| 7.0          | R/W-0             | U-0               | R/W-0             | R/W-0             | U-0               | R/W-0             | R/W-0            | U-0              |

| 7:0          | TGATE             | _                 | TCKPS             | S<1:0>            | _                 | TSYNC             | TCS              | _                |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

bit 31-16 Unimplemented: Read as '0'

bit 15 **ON:** Timer On bit<sup>(1)</sup>

1 = Timer is enabled

0 = Timer is disabled

bit 14 Unimplemented: Read as '0'

bit 13 SIDL: Stop in Idle Mode bit

1 = Discontinue operation when device enters Idle mode

0 = Continue operation when device is in Idle mode

bit 12 TWDIS: Asynchronous Timer Write Disable bit

1 = Writes to TMR1 are ignored until pending write operation completes

0 = Back-to-back writes are enabled (Legacy Asynchronous Timer functionality)

bit 11 TWIP: Asynchronous Timer Write in Progress bit

In Asynchronous Timer mode:

1 = Asynchronous write to TMR1 register in progress

0 = Asynchronous write to TMR1 register complete

In Synchronous Timer mode:

This bit is read as '0'.

bit 10-8 Unimplemented: Read as '0'

bit 7 TGATE: Timer Gated Time Accumulation Enable bit

When TCS = 1:

This bit is ignored.

When TCS = 0:

1 = Gated time accumulation is enabled

0 = Gated time accumulation is disabled

bit 6 Unimplemented: Read as '0'

bit 5-4 TCKPS<1:0>: Timer Input Clock Prescale Select bits

11 = 1:256 prescale value

10 = 1:64 prescale value

01 = 1:8 prescale value

00 = 1:1 prescale value

Note 1: When using the 1:1 PBCLK divisor, the user's software should not read/write the peripheral SFRs in the SYSCLK cycle immediately following the instruction that clears the module's ON bit.

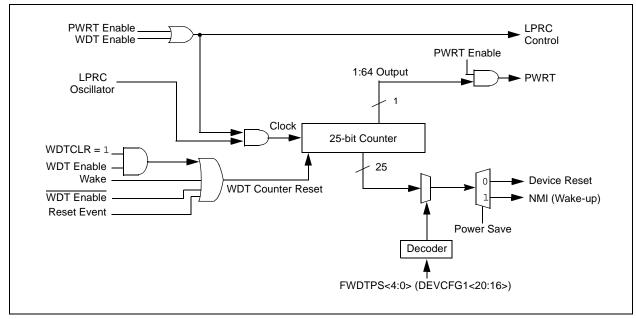

#### 15.0 WATCHDOG TIMER (WDT)

Note:

This data sheet summarizes the features of the PIC32MX5XX/6XX/7XX family of devices. However, it is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to Section 8. "Watchdog Timer and Power-up Timer" in the "PIC32 (DS60001114) Family Reference Manual", which is available from the Microchip web site (www.microchip.com/PIC32).

This section describes the operation of the WDT and Power-up Timer of the PIC32MX5XX/6XX/7XX.

The WDT, when enabled, operates from the internal Low-Power Oscillator (LPRC) clock source and can be used to detect system software malfunctions by resetting the device if the WDT is not cleared periodically in software. Various WDT time-out periods can be selected using the WDT postscaler. The WDT can also be used to wake the device from Sleep or Idle mode.

The following are key features of the WDT module:

- · Configuration or software controlled

- · User-configurable time-out period

- · Can wake the device from Sleep or Idle mode

FIGURE 15-1: WATCHDOG TIMER AND POWER-UP TIMER BLOCK DIAGRAM

NOTES:

#### REGISTER 21-4: PMAEN: PARALLEL PORT PIN ENABLE REGISTER

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |  |  |  |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|--|--|--|--|

| 24.24        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |  |  |  |  |

| 31:24        | _                 | -                 | -                 | -                 | -                 | -                 | _                | 1                |  |  |  |  |

| 22.40        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |  |  |  |  |

| 23:16        | _                 | _                 | _                 | _                 | _                 | _                 | _                | -                |  |  |  |  |

| 45.0         | U-0               | R/W-0             | U-0               | U-0               | U-0               | R/W-0             | R/W-0            | R/W-0            |  |  |  |  |

| 15:8         | _                 | PTEN14            | _                 | _                 | _                 |                   | PTEN<10:8>       |                  |  |  |  |  |

| 7.0          | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |  |  |

| 7:0          |                   | PTEN<7:0>         |                   |                   |                   |                   |                  |                  |  |  |  |  |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

bit 31-15 Unimplemented: Read as '0'

bit 15-14 PTEN14: PMCS1 Strobe Enable bits

1 = PMA14 functions as either PMA14 or PMCS1(1)

0 = PMA14 functions as port I/O

bit 13-11 Unimplemented: Read as '0'

bit 10-2 PTEN<10:2>: PMP Address Port Enable bits

1 = PMA<10:2> function as PMP address lines

0 = PMA<10:2> function as port I/O

bit 1-0 PTEN<1:0>: PMALH/PMALL Strobe Enable bits

1 = PMA1 and PMA0 function as either PMA<1:0> or PMALH and PMALL(2)

0 = PMA1 and PMA0 pads function as port I/O

Note 1: The use of this pin as PMA14 or CS1 is selected by the CSF<1:0> bits in the PMCON register.

2: The use of these pins as PMA1/PMA0 or PMALH/PMALL depends on the Address/Data Multiplex mode selected by bits ADRMUX<1:0> in the PMCON register.

#### REGISTER 22-1: RTCCON: RTC CONTROL REGISTER (CONTINUED)

- bit 3 RTCWREN: RTC Value Registers Write Enable bit (4)

- 1 = RTC Value registers can be written to by the user

- 0 = RTC Value registers are locked out from being written to by the user

- bit 2 RTCSYNC: RTCC Value Registers Read Synchronization bit

- 1 = RTC Value registers can change while reading, due to a rollover ripple that results in an invalid data read. If the register is read twice and results in the same data, the data can be assumed to be valid.

- 0 = RTC Value registers can be read without concern about a rollover ripple

- bit 1 HALFSEC: Half-Second Status bit<sup>(5)</sup>

- 1 = Second half period of a second

- 0 = First half period of a second

- bit 0 RTCOE: RTCC Output Enable bit

- 1 = RTCC clock output is enabled (clock presented onto an I/O)

- 0 = RTCC clock output is disabled

- **Note 1:** The ON bit is only writable when RTCWREN = 1.

- 2: When using the 1:1 PBCLK divisor, the user's software should not read/write the peripheral's SFRs in the SYSCLK cycle immediately following the instruction that clears the module's ON bit.

- 3: Requires RTCOE = 1 (RTCCON<0>) for the output to be active.

- **4:** The RTCWREN bit can only be set when the write sequence is enabled.

- 5: This bit is read-only. It is cleared to '0' on a write to the seconds bit fields (RTCTIME<14:8>).

Note: This register is only reset on a Power-on Reset (POR).

#### REGISTER 24-1: CICON: CAN MODULE CONTROL REGISTER (CONTINUED)

bit 13 SIDLE: CAN Stop in Idle bit

1 = CAN Stops operation when system enters Idle mode 0 = CAN continues operation when system enters Idle mode

bit 12 Unimplemented: Read as '0'

bit 11 CANBUSY: CAN Module is Busy bit

1 = The CAN module is active

0 = The CAN module is completely disabled

bit 10-5 Unimplemented: Read as '0'

bit 4-0 **DNCNT<4:0>:** Device Net Filter Bit Number bits

10011-11111 = Invalid Selection (compare up to 18-bits of data with EID) 10010 = Compare up to data byte 2 bit 6 with EID17 (CiRXFn<17>)

•

•

•

00001 = Compare up to data byte 0 bit 7 with EID0 (CiRXFn<0>)

00000 = Do not compare data bytes

**Note 1:** If the user application clears this bit, it may take a number of cycles before the CAN module completes the current transaction and responds to this request. The user application should poll the CANBUSY bit to verify that the request has been honored.

## REGISTER 25-16: ETHRXOVFLOW: ETHERNET CONTROLLER RECEIVE OVERFLOW STATISTICS REGISTER

| Bit Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |  |

|-----------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|--|--|

| 31:24     | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |  |  |

| 31.24     | _                 | _                 | _                 | -                 | _                 | _                 | -                | _                |  |  |

| 23:16     | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |  |  |

| 23.10     | _                 | _                 | _                 | -                 | _                 | _                 | -                | _                |  |  |

| 15:8      | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |

| 15.6      | RXOVFLWCNT<15:8>  |                   |                   |                   |                   |                   |                  |                  |  |  |

| 7:0       | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |

| 7.0       |                   |                   |                   | RXOVFLW           | /CNT<7:0>         |                   |                  |                  |  |  |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

bit 31-16 Unimplemented: Read as '0'

bit 15-0 RXOVFLWCNT<15:0>: Dropped Receive Frames Count bits

Increment counter for frames accepted by the RX filter and subsequently dropped due to internal receive error (RXFIFO overrun). This event also sets the RXOVFLW bit (ETHIRQ<0>) interrupt flag.

- **Note 1:** This register is only used for RX operations.

- 2: This register is automatically cleared by hardware after a read operation, unless the byte enables for bytes 0/1 are '0'.

- **3:** It is recommended to use the SET, CLR, or INV registers to set or clear any bit in this register. Setting or clearing any bits in this register should only be done for debug/test purposes.

## REGISTER 25-20: ETHFRMRXOK: ETHERNET CONTROLLER FRAMES RECEIVED OK STATISTICS REGISTER

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |  |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|--|--|

| 31:24        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |  |  |

| 31.24        | _                 | _                 | -                 | _                 | _                 | _                 | -                |                  |  |  |

| 23:16        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |  |  |

| 23.10        | _                 | _                 | -                 | _                 | _                 | _                 | -                |                  |  |  |

| 15.0         | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |

| 15:8         | FRMRXOKCNT<15:8>  |                   |                   |                   |                   |                   |                  |                  |  |  |

| 7.0          | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |

| 7:0          |                   |                   |                   | FRMRXO            | (CNT<7:0>         |                   |                  |                  |  |  |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

bit 31-16 Unimplemented: Read as '0'

bit 15-0 FRMRXOKCNT<15:0>: Frames Received OK Count bits

Increment count for frames received successfully by the RX Filter. This count will not be incremented if there is a Frame Check Sequence (FCS) or Alignment error.

- **Note 1:** This register is only used for RX operations.

- 2: This register is automatically cleared by hardware after a read operation, unless the byte enables for bytes 0/1 are '0'.

- 3: It is recommended to use the SET, CLR, or INV registers to set or clear any bit in this register. Setting or clearing any bits in this register should only be done for debug/test purposes.

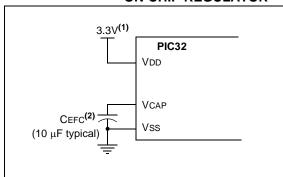

#### 29.2 On-Chip Voltage Regulator

All PIC32MX5XX/6XX/7XX devices' core and digital logic are designed to operate at a nominal 1.8V. To simplify system designs, most devices in the PIC32MX-5XX/6XX/7XX family incorporate an on-chip regulator providing the required core logic voltage from VDD.

A low-ESR capacitor (such as tantalum) must be connected to the VCAP pin (see Figure 29-1). This helps to maintain the stability of the regulator. The recommended value for the filter capacitor is provided in **Section 32.1** "**DC Characteristics**".

**Note:** It is important that the low-ESR capacitor is placed as close as possible to the VCAP pin.

#### 29.2.1 ON-CHIP REGULATOR AND POR

It takes a fixed delay for the on-chip regulator to generate an output. During this time, designated as TPU, code execution is disabled. TPU is applied every time the device resumes operation after any power-down, including Sleep mode.

#### 29.2.2 ON-CHIP REGULATOR AND BOR

PIC32MX5XX/6XX/7XX devices also have a simple brown-out capability. If the voltage supplied to the regulator is inadequate to maintain a regulated level, the regulator Reset circuitry will generate a Brown-out Reset (BOR). This event is captured by the BOR flag bit (RCON<1>). The brown-out voltage levels are specified in **Section 32.1 "DC Characteristics"**.

# FIGURE 29-1: CONNECTIONS FOR THE ON-CHIP REGULATOR

Note 1: These are typical operating voltages. Refer to Section 32.1 "DC Characteristics" for the full operating ranges of VDD.

2: It is important that the low-ESR capacitor is placed as close as possible to the VCAP pin.

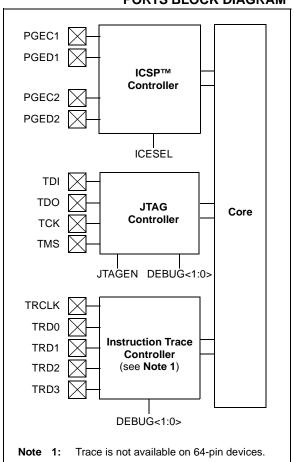

#### 29.3 Programming and Diagnostics

PIC32MX5XX/6XX/7XX devices provide a complete range of programming and diagnostic features that can increase the flexibility of any application using them. These features allow system designers to include:

- Simplified field programmability using two-wire In-Circuit Serial Programming™ (ICSP™) interfaces

- Debugging using ICSP

- Programming and debugging capabilities using the EJTAG extension of JTAG

- JTAG boundary scan testing for device and board diagnostics

PIC32 devices incorporate two programming and diagnostic modules, and a trace controller, that provide a range of functions to the application developer.

FIGURE 29-2: PROGRAMMING,

DEBUGGING, AND TRACE

PORTS BLOCK DIAGRAM

#### 31.0 DEVELOPMENT SUPPORT

The PIC<sup>®</sup> microcontrollers (MCU) and dsPIC<sup>®</sup> digital signal controllers (DSC) are supported with a full range of software and hardware development tools:

- · Integrated Development Environment

- MPLAB® X IDE Software

- · Compilers/Assemblers/Linkers

- MPLAB XC Compiler

- MPASM<sup>TM</sup> Assembler

- MPLINK<sup>™</sup> Object Linker/ MPLIB<sup>™</sup> Object Librarian

- MPLAB Assembler/Linker/Librarian for Various Device Families

- Simulators

- MPLAB X SIM Software Simulator

- Emulators

- MPLAB REAL ICE™ In-Circuit Emulator

- In-Circuit Debuggers/Programmers

- MPLAB ICD 3

- PICkit™ 3

- Device Programmers

- MPLAB PM3 Device Programmer

- Low-Cost Demonstration/Development Boards, Evaluation Kits and Starter Kits

- Third-party development tools

## 31.1 MPLAB X Integrated Development Environment Software

The MPLAB X IDE is a single, unified graphical user interface for Microchip and third-party software, and hardware development tool that runs on Windows<sup>®</sup>, Linux and Mac OS<sup>®</sup> X. Based on the NetBeans IDE, MPLAB X IDE is an entirely new IDE with a host of free software components and plug-ins for high-performance application development and debugging. Moving between tools and upgrading from software simulators to hardware debugging and programming tools is simple with the seamless user interface.

With complete project management, visual call graphs, a configurable watch window and a feature-rich editor that includes code completion and context menus, MPLAB X IDE is flexible and friendly enough for new users. With the ability to support multiple tools on multiple projects with simultaneous debugging, MPLAB X IDE is also suitable for the needs of experienced users.

#### Feature-Rich Editor:

- · Color syntax highlighting

- Smart code completion makes suggestions and provides hints as you type

- Automatic code formatting based on user-defined rules

- · Live parsing

User-Friendly, Customizable Interface:

- Fully customizable interface: toolbars, toolbar buttons, windows, window placement, etc.

- · Call graph window

Project-Based Workspaces:

- · Multiple projects

- · Multiple tools

- · Multiple configurations

- · Simultaneous debugging sessions

File History and Bug Tracking:

- · Local file history feature

- · Built-in support for Bugzilla issue tracker

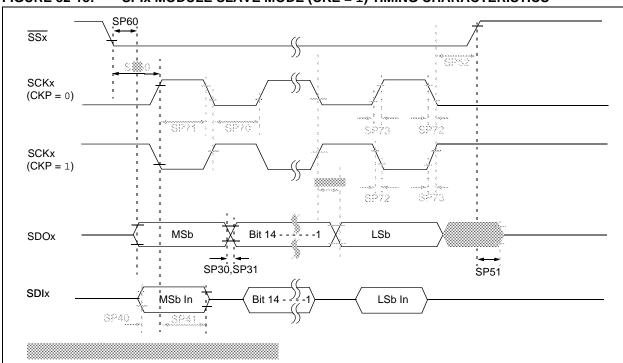

FIGURE 32-13: SPIX MODULE SLAVE MODE (CKE = 1) TIMING CHARACTERISTICS

TABLE 32-31: SPIx MODULE SLAVE MODE (CKE = 1) TIMING REQUIREMENTS

| AC CHA        | ARACTERIS <sup>*</sup> | тісѕ                                                                                         | Standard Operating Conditions: 2.3V to 3.6V (unless otherwise stated) Operating temperature $-40^{\circ}\text{C} \le \text{TA} \le +85^{\circ}\text{C}$ for Industrial $-40^{\circ}\text{C} \le \text{TA} \le +105^{\circ}\text{C}$ for V-Temp |                        |      |       |                    |  |  |

|---------------|------------------------|----------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------|------|-------|--------------------|--|--|

| Param.<br>No. | Symbol                 | Characteristics <sup>(1)</sup>                                                               | Min.                                                                                                                                                                                                                                           | Typical <sup>(2)</sup> | Max. | Units | Conditions         |  |  |

| SP70          | TscL                   | SCKx Input Low Time <sup>(3)</sup>                                                           | Tsck/2                                                                                                                                                                                                                                         | _                      | _    | ns    | _                  |  |  |

| SP71          | TscH                   | SCKx Input High Time <sup>(3)</sup>                                                          | Tsck/2                                                                                                                                                                                                                                         | _                      | _    | ns    | _                  |  |  |

| SP72          | TscF                   | SCKx Input Fall Time                                                                         | _                                                                                                                                                                                                                                              | 5                      | 10   | ns    | _                  |  |  |

| SP73          | TscR                   | SCKx Input Rise Time                                                                         | _                                                                                                                                                                                                                                              | 5                      | 10   | ns    | _                  |  |  |

| SP30          | TDOF                   | SDOx Data Output Fall Time(4)                                                                | _                                                                                                                                                                                                                                              | _                      | _    | ns    | See parameter DO32 |  |  |

| SP31          | TDOR                   | SDOx Data Output Rise Time(4)                                                                | _                                                                                                                                                                                                                                              | _                      | _    | ns    | See parameter DO31 |  |  |

| SP35          |                        | SDOx Data Output Valid after                                                                 | _                                                                                                                                                                                                                                              | _                      | 20   | ns    | VDD > 2.7V         |  |  |

|               | TscL2doV               | SCKx Edge                                                                                    | _                                                                                                                                                                                                                                              | _                      | 30   | ns    | VDD < 2.7V         |  |  |

| SP40          | TDIV2scH,<br>TDIV2scL  | Setup Time of SDIx Data Input to SCKx Edge                                                   | 10                                                                                                                                                                                                                                             | _                      | _    | ns    | _                  |  |  |

| SP41          | TscH2DIL,<br>TscL2DIL  | Hold Time of SDIx Data Input to SCKx Edge                                                    | 10                                                                                                                                                                                                                                             | _                      | _    | ns    | _                  |  |  |

| SP50          | TssL2scH,<br>TssL2scL  | $\overline{SSx} \downarrow \text{ to SCKx} \downarrow \text{ or SCKx} \uparrow \text{Input}$ | 175                                                                                                                                                                                                                                            | _                      |      | ns    | _                  |  |  |

- Note 1: These parameters are characterized, but not tested in manufacturing.

- 2: Data in "Typical" column is at 3.3V, 25°C unless otherwise stated. Parameters are for design guidance only and are not tested.

- 3: The minimum clock period for SCKx is 40 ns.

- 4: Assumes 50 pF load on all SPIx pins.

TABLE 32-36: ADC MODULE SPECIFICATIONS (CONTINUED)

| AC CHA                                                | ARACTERIS  | STICS                          | Standard Operating Conditions (see Note 5): 2.5V to 3.6V (unless otherwise stated) Operating temperature $-40^{\circ}\text{C} \le \text{TA} \le +85^{\circ}\text{C}$ for Industrial $-40^{\circ}\text{C} \le \text{TA} \le +105^{\circ}\text{C}$ for V-Temp |              |      |       |                                                         |  |  |  |  |

|-------------------------------------------------------|------------|--------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------|------|-------|---------------------------------------------------------|--|--|--|--|

| Param.<br>No.                                         | Symbol     | Characteristics                | Min.                                                                                                                                                                                                                                                        | Typical      | Max. | Units | Conditions                                              |  |  |  |  |

| ADC Accuracy – Measurements with Internal VREF+/VREF- |            |                                |                                                                                                                                                                                                                                                             |              |      |       |                                                         |  |  |  |  |

| AD20d                                                 | Nr         | Resolution                     | ,                                                                                                                                                                                                                                                           | 10 data bits |      | bits  | (Note 3)                                                |  |  |  |  |

| AD21d                                                 | INL        | Integral Nonlinearity          | > -1                                                                                                                                                                                                                                                        |              | < 1  | LSb   | VINL = AVSS = 0V,<br>AVDD = 2.5V to 3.6V<br>(Note 3)    |  |  |  |  |

| AD22d                                                 | DNL        | Differential Nonlinearity      | > -1                                                                                                                                                                                                                                                        |              | < 1  | LSb   | VINL = AVSS = 0V,<br>AVDD = 2.5V to 3.6V<br>(Notes 2,3) |  |  |  |  |

| AD23d                                                 | GERR       | Gain Error                     | > -4                                                                                                                                                                                                                                                        | _            | < 4  | LSb   | VINL = AVSS = 0V,<br>AVDD = 2.5V to 3.6V<br>(Note 3)    |  |  |  |  |

| AD24d                                                 | EOFF       | Offset Error                   | > -2                                                                                                                                                                                                                                                        | _            | < 2  | LSb   | VINL = AVSS = 0V,<br>AVDD = 2.5V to 3.6V<br>(Note 3)    |  |  |  |  |

| AD25d                                                 |            | Monotonicity                   | _                                                                                                                                                                                                                                                           |              | _    | _     | Guaranteed                                              |  |  |  |  |

| Dynami                                                | c Performa | ance                           |                                                                                                                                                                                                                                                             |              |      |       |                                                         |  |  |  |  |

| AD31b                                                 | SINAD      | Signal to Noise and Distortion | 55                                                                                                                                                                                                                                                          | 58.5         | _    | dB    | (Notes 3,4)                                             |  |  |  |  |

| AD34b                                                 | ENOB       | Effective Number of Bits       | 9.0                                                                                                                                                                                                                                                         | 9.5          | _    | bits  | (Notes 3,4)                                             |  |  |  |  |

Note 1: These parameters are not characterized or tested in manufacturing.

- 2: With no missing codes.

- 3: These parameters are characterized, but not tested in manufacturing.

- 4: Characterized with a 1 kHz sine wave.

- **5:** The ADC module is functional at VBORMIN < VDD < 2.5V, but with degraded performance. Unless otherwise stated, module functionality is tested, but not characterized.

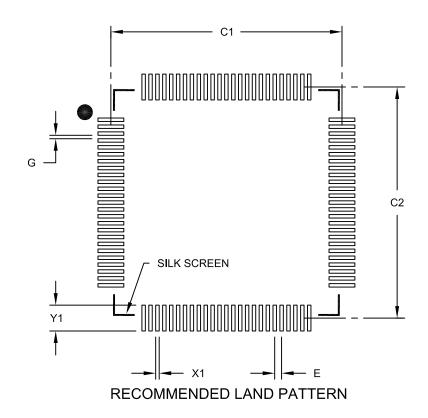

100-Lead Plastic Thin Quad Flatpack (PT)-12x12x1mm Body, 2.00 mm Footprint [TQFP]

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

| Units                     |    | MILLIMETERS |       |      |

|---------------------------|----|-------------|-------|------|

| Dimension Limits          |    | MIN         | NOM   | MAX  |

| Contact Pitch             | E  | 0.40 BSC    |       |      |

| Contact Pad Spacing       | C1 |             | 13.40 |      |

| Contact Pad Spacing       | C2 |             | 13.40 |      |

| Contact Pad Width (X100)  | X1 |             |       | 0.20 |

| Contact Pad Length (X100) | Y1 |             |       | 1.50 |

| Distance Between Pads     | G  | 0.20        |       |      |

#### Notes:

1. Dimensioning and tolerancing per ASME Y14.5M

BSC: Basic Dimension. Theoretically exact value shown without tolerances.

Microchip Technology Drawing No. C04-2100B