Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFI

| Detuils                    |                                                                                |

|----------------------------|--------------------------------------------------------------------------------|

| Product Status             | Active                                                                         |

| Core Processor             | MIPS32® M4K™                                                                   |

| Core Size                  | 32-Bit Single-Core                                                             |

| Speed                      | 80MHz                                                                          |

| Connectivity               | Ethernet, I <sup>2</sup> C, SPI, UART/USART, USB OTG                           |

| Peripherals                | Brown-out Detect/Reset, DMA, POR, PWM, WDT                                     |

| Number of I/O              | 83                                                                             |

| Program Memory Size        | 64KB (64K x 8)                                                                 |

| Program Memory Type        | FLASH                                                                          |

| EEPROM Size                | -                                                                              |

| RAM Size                   | 32K x 8                                                                        |

| Voltage - Supply (Vcc/Vdd) | 2.3V ~ 3.6V                                                                    |

| Data Converters            | A/D 16x10b                                                                     |

| Oscillator Type            | Internal                                                                       |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                              |

| Mounting Type              | Surface Mount                                                                  |

| Package / Case             | 121-TFBGA                                                                      |

| Supplier Device Package    | 121-TFBGA (10x10)                                                              |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic32mx664f064l-i-bg |

|                            |                                                                                |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

## TABLE 10: PIN NAMES FOR USB AND CAN DEVICES

| 121        | PIN TFBGA (BOTTOM VIEW)                                                                     |       | L11                              |     |

|------------|---------------------------------------------------------------------------------------------|-------|----------------------------------|-----|

|            | PIC32MX534F064L<br>PIC32MX564F064L<br>PIC32MX564F128L<br>PIC32MX575F256L<br>PIC32MX575F512L | L1    |                                  | A11 |

|            | The TFBGA package skips from row "H" to                                                     |       |                                  |     |

| Pin #      | Full Pin Name                                                                               | Pin # | Full Pin Name                    |     |

| A1         | PMD4/RE4                                                                                    | E2    | T4CK/RC3                         |     |

| A2         | PMD3/RE3                                                                                    | E3    | SCK2/U6TXU6TX/U3RTS/PMA5/CN8/RG6 |     |

| A3         | TRD0/RG13                                                                                   | E4    | T3CK/RC2                         |     |

| A4         | PMD0/RE0                                                                                    | E5    | Vdd                              |     |

| A5         | PMD8/RG0                                                                                    | E6    | PMD9/RG1                         |     |

| A6         | C1TX/PMD10/RF1                                                                              | E7    | Vss                              |     |

| A7         | Vdd                                                                                         | E8    | SDA1/INT4/RA15                   |     |

| A8         | Vss                                                                                         | E9    | RTCC/IC1/RD8                     |     |

| A9         | IC5/PMD12/RD12                                                                              | E10   | SS1/IC2/RD9                      |     |

| A10        | OC3/RD2                                                                                     | E11   | SCL1/INT3/RA14                   |     |

| A11        | OC2/RD1                                                                                     | F1    | MCLR                             |     |

| B1         | No Connect (NC)                                                                             | F2    | SCL4/SDO2/U3TX/PMA3/CN10/RG8     |     |

| B2         | RG15                                                                                        | F3    | SS2/U6RX/U3CTS/PMA2/CN11/RG9     |     |

| B3         | PMD2/RE2                                                                                    | F4    | SDA4/SDI2/U3RX/PMA4/CN9/RG7      |     |

| B3<br>B4   | PMD1/RE1                                                                                    | F5    | Vss                              |     |

| B5         | TRD3/RA7                                                                                    | F6    | No Connect (NC)                  |     |

| B6         | C1RX/PMD11/RF0                                                                              | F7    | No Connect (NC)                  |     |

| B7         | VCAP                                                                                        | F8    | VDD                              |     |

| B8         | PMRD/CN14/RD5                                                                               | F9    | OSC1/CLKI/RC12                   |     |

| B9         | OC4/RD3                                                                                     |       | Vss                              |     |

| B10        | Vss                                                                                         | F11   | OSC2/CLKO/RC15                   |     |

| B10<br>B11 | SOSCO/T1CK/CN0/RC14                                                                         | G1    | INT1/RE8                         |     |

| C1         | PMD6/RE6                                                                                    | G2    | INT2/RE9                         |     |

| C2         | VDD                                                                                         | G3    | TMS/RA0                          |     |

| C3         | TRD1/RG12                                                                                   | G4    | No Connect (NC)                  |     |

| C4         | TRD2/RG14                                                                                   | G5    | VDD                              |     |

| C5         | TRCLK/RA6                                                                                   | G6    | Vss                              |     |

| C6         | No Connect (NC)                                                                             | G7    | Vss                              |     |

| C7         | PMD15/CN16/RD7                                                                              | G8    | No Connect (NC)                  |     |

| C8         | OC5/PMWR/CN13/RD4                                                                           | G9    | TDO/RA5                          |     |

| C9         | VDD                                                                                         | G10   | SDA2/RA3                         |     |

| C10        | SOSCI/CN1/RC13                                                                              | G11   | TDI/RA4                          |     |

| C11        | IC4/PMCS1/PMA14/RD11                                                                        | H1    | AN5/C1IN+/VBUSON/CN7/RB5         |     |

| D1         | T2CK/RC1                                                                                    | H2    | AN4/C1IN-/CN6/RB4                |     |

| D2         | PMD7/RE7                                                                                    | H3    | Vss                              |     |

| D3         | PMD5/RE5                                                                                    | H4    | VDD                              |     |

| D4         | Vss                                                                                         | H5    | No Connect (NC)                  |     |

| D5         | Vss                                                                                         | H6    | VDD                              |     |

| D6         | No Connect (NC)                                                                             | H7    | No Connect (NC)                  |     |

| D7         | PMD14/CN15/RD6                                                                              | H8    | VBUS                             |     |

| D8         | PMD13/CN19/RD13                                                                             | H9    | VUSB3V3                          |     |

| D9         | SDO1/OC1/INT0/RD0                                                                           | H10   | D+/RG2                           |     |

| D10        | No Connect (NC)                                                                             | H11   | SCL2/RA2                         |     |

| D11        | SCK1/IC3/PMCS2/PMA15/RD10                                                                   | J1    | AN3/C2IN+/CN5/RB3                |     |

|            |                                                                                             | 51    |                                  |     |

## 1.0 DEVICE OVERVIEW

**Note:** This data sheet summarizes the features of the PIC32MX5XX/6XX/7XX family of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to the documents listed in the *Documentation* > *Reference Manual* section of the Microchip PIC32 web site (www.microchip.com/pic32).

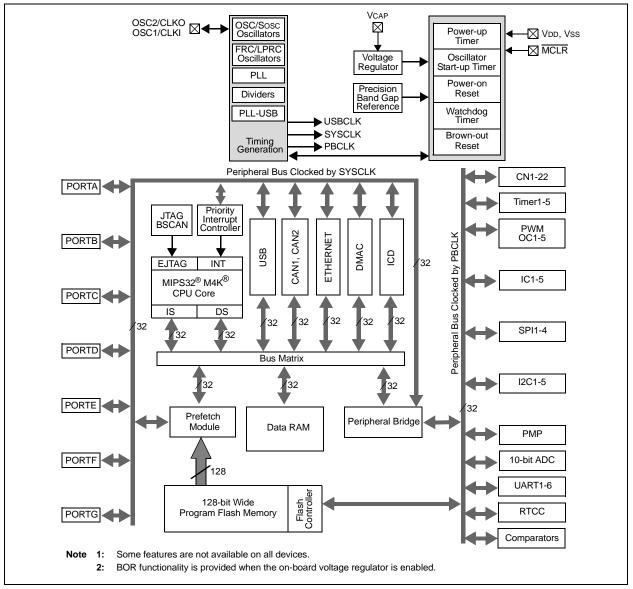

FIGURE 1-1: BLOCK DIAGRAM<sup>(1,2)</sup>

This document contains device-specific information for PIC32MX5XX/6XX/7XX devices.

Figure 1-1 illustrates a general block diagram of the core and peripheral modules in the PIC32MX5XX/6XX/7XX family of devices.

Table 1-1 lists the functions of the various pins shown in the pinout diagrams.

## PIC32MX5XX/6XX/7XX

## TABLE 1-1: PINOUT I/O DESCRIPTIONS (CONTINUED)

|           |                    | Pin Nun         | nber <sup>(1)</sup> |                 |             | D              |                                                            |

|-----------|--------------------|-----------------|---------------------|-----------------|-------------|----------------|------------------------------------------------------------|

| Pin Name  | 64-Pin<br>QFN/TQFP | 100-Pin<br>TQFP | 121-Pin<br>TFBGA    | 124-pin<br>VTLA | Pin<br>Type | Buffer<br>Type | Description                                                |

| AC2TX     | —                  | 7               | E4                  | B4              | 0           | —              | Alternate CAN2 bus transmit pin                            |

| ERXD0     | 61                 | 41              | J7                  | B23             | I           | ST             | Ethernet Receive Data 0 <sup>(2)</sup>                     |

| ERXD1     | 60                 | 42              | L7                  | A28             | I           | ST             | Ethernet Receive Data 1 <sup>(2)</sup>                     |

| ERXD2     | 59                 | 43              | K7                  | B24             | I           | ST             | Ethernet Receive Data 2 <sup>(2)</sup>                     |

| ERXD3     | 58                 | 44              | L8                  | A29             | I           | ST             | Ethernet Receive Data 3 <sup>(2)</sup>                     |

| ERXERR    | 64                 | 35              | J5                  | B20             | I           | ST             | Ethernet receive error input <sup>(2)</sup>                |

| ERXDV     | 62                 | 12              | F2                  | A8              | I           | ST             | Ethernet receive data valid <sup>(2)</sup>                 |

| ECRSDV    | 62                 | 12              | F2                  | A8              | I           | ST             | Ethernet carrier sense data valid <sup>(2)</sup>           |

| ERXCLK    | 63                 | 14              | F3                  | A9              | I           | ST             | Ethernet receive clock <sup>(2)</sup>                      |

| EREFCLK   | 63                 | 14              | F3                  | A9              | I           | ST             | Ethernet reference clock <sup>(2)</sup>                    |

| ETXD0     | 2                  | 88              | A6                  | A60             | 0           | _              | Ethernet Transmit Data 0 <sup>(2)</sup>                    |

| ETXD1     | 3                  | 87              | B6                  | B49             | 0           | _              | Ethernet Transmit Data 1 <sup>(2)</sup>                    |

| ETXD2     | 43                 | 79              | A9                  | B43             | 0           | _              | Ethernet Transmit Data 2 <sup>(2)</sup>                    |

| ETXD3     | 42                 | 80              | D8                  | A54             | 0           | _              | Ethernet Transmit Data 3 <sup>(2)</sup>                    |

| ETXERR    | 54                 | 89              | E6                  | B50             | 0           | _              | Ethernet transmit error <sup>(2)</sup>                     |

| ETXEN     | 1                  | 83              | D7                  | B45             | 0           | _              | Ethernet transmit enable <sup>(2)</sup>                    |

| ETXCLK    | 55                 | 84              | C7                  | A56             | I           | ST             | Ethernet transmit clock <sup>(2)</sup>                     |

| ECOL      | 44                 | 10              | E3                  | A7              | I           | ST             | Ethernet collision detect <sup>(2)</sup>                   |

| ECRS      | 45                 | 11              | F4                  | B6              | I           | ST             | Ethernet carrier sense <sup>(2)</sup>                      |

| EMDC      | 30                 | 71              | C11                 | A46             | 0           | _              | Ethernet management data clock <sup>(2)</sup>              |

| EMDIO     | 49                 | 68              | E9                  | B37             | I/O         | _              | Ethernet management data <sup>(2)</sup>                    |

| AERXD0    | 43                 | 18              | G1                  | A11             | I           | ST             | Alternate Ethernet Receive Data 0 <sup>(2)</sup>           |

| AERXD1    | 42                 | 19              | G2                  | B10             | I           | ST             | Alternate Ethernet Receive Data 1 <sup>(2)</sup>           |

| AERXD2    | —                  | 28              | L2                  | A21             | I           | ST             | Alternate Ethernet Receive Data 2(2)                       |

| AERXD3    | —                  | 29              | K3                  | B17             | I           | ST             | Alternate Ethernet Receive Data 3 <sup>(2)</sup>           |

| AERXERR   | 55                 | 1               | B2                  | A2              | I           | ST             | Alternate Ethernet receive error input <sup>(2)</sup>      |

| AERXDV    | —                  | 12              | F2                  | A8              | I           | ST             | Alternate Ethernet receive data valid <sup>(2)</sup>       |

| AECRSDV   | 44                 | 12              | F2                  | A8              | I           | ST             | Alternate Ethernet carrier sense data valid <sup>(2)</sup> |

| AERXCLK   | —                  | 14              | F3                  | A9              | I           | ST             | Alternate Ethernet receive clock <sup>(2)</sup>            |

| AEREFCLK  | 45                 | 14              | F3                  | A9              | I           | ST             | Alternate Ethernet reference clock <sup>(2)</sup>          |

| AETXD0    | 59                 | 47              | L9                  | B26             | 0           |                | Alternate Ethernet Transmit Data 0 <sup>(2)</sup>          |

| AETXD1    | 58                 | 48              | K9                  | A31             | 0           |                | Alternate Ethernet Transmit Data 1 <sup>(2)</sup>          |

| AETXD2    |                    | 44              | L8                  | A29             | 0           |                | Alternate Ethernet Transmit Data 2 <sup>(2)</sup>          |

| AETXD3    |                    | 43              | K7                  | B24             | 0           |                | Alternate Ethernet Transmit Data 3 <sup>(2)</sup>          |

| AETXERR   |                    | 35              | J5                  | B20             | 0           |                | Alternate Ethernet transmit error <sup>(2)</sup>           |

| AETXEN    | 54                 | 67              | E8                  | A44             | 0           |                | Alternate Ethernet transmit enable <sup>(2)</sup>          |

| AETXCLK   | _                  | 66              | E11                 | B36             | 1           | ST             | Alternate Ethernet transmit clock <sup>(2)</sup>           |

| AECOL     |                    | 42              | L7                  | A28             | 1           | ST             | Alternate Ethernet collision detect <sup>(2)</sup>         |

| Leaend: C | MOS = CMO          | S compatib      | le input or c       | butput          | A           | nalog = A      | Analog input P = Power                                     |

Legend: CMOS = CMOS compatible input or output ST = Schmitt Trigger input with CMOS levels

Analog = Analog input P = PowerO = Output I = Input

TTL = TTL input buffer

Note 1: Pin numbers are only provided for reference. See the "Device Pin Tables" section for device pin availability.

2: See 25.0 "Ethernet Controller" for more information.

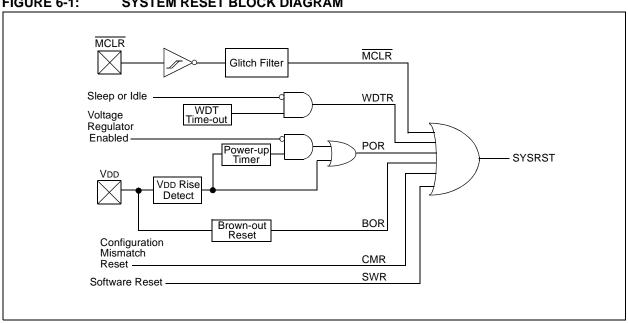

## 6.0 RESETS

Note: This data sheet summarizes the features of the PIC32MX5XX/6XX/7XX family of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to **Section 7.** "**Resets**" (DS60001118) in the "*PIC32 Family Reference Manual*", which is available from the Microchip web site (www.microchip.com/PIC32).

The Reset module combines all Reset sources and controls the device Master Reset signal, SYSRST. The following is a list of device Reset sources:

- Power-on Reset (POR)

- Master Clear Reset pin (MCLR)

- Software Reset (SWR)

- Watchdog Timer Reset (WDTR)

- Brown-out Reset (BOR)

- Configuration Mismatch Reset (CMR)

A simplified block diagram of the Reset module is illustrated in Figure 6-1.

## FIGURE 6-1: SYSTEM RESET BLOCK DIAGRAM

## 8.1 Control Registers

#### TABLE 8-1: OSCILLATOR REGISTER MAP

| ess                         |                                 | Ð         |       |       |           |            |       |       |           | В    | its     |         |       |       |       |        |            |       | (2)        |

|-----------------------------|---------------------------------|-----------|-------|-------|-----------|------------|-------|-------|-----------|------|---------|---------|-------|-------|-------|--------|------------|-------|------------|

| Virtual Address<br>(BF80_#) | Register<br>Name <sup>(1)</sup> | Bit Range | 31/15 | 30/14 | 29/13     | 28/12      | 27/11 | 26/10 | 25/9      | 24/8 | 23/7    | 22/6    | 21/5  | 20/4  | 19/3  | 18/2   | 17/1       | 16/0  | All Resets |

| E000                        | OSCCON                          | 31:16     | —     | _     | P         | LLODIV<2:0 | >     | F     | RCDIV<2:0 | >    | —       | SOSCRDY | _     | PBDIV | <1:0> | Р      | LLMULT<2:0 | >     | 0000       |

| FUUU                        | USCCON                          | 15:0      | _     |       | COSC<2:0> |            | _     |       | NOSC<2:0> |      | CLKLOCK | ULOCK   | SLOCK | SLPEN | CF    | UFRCEN | SOSCEN     | OSWEN | 0000       |

| E010                        | OSCTUN                          | 31:16     | —     | _     | _         | —          | _     | _     |           | -    | _       | —       | _     | —     | —     | _      | _          | —     | 0000       |

| FUIU                        | USCIUN                          | 15:0      | _     |       | □         |            |       |       |           |      | 0000    |         |       |       |       |        |            |       |            |

Legend: x = unknown value on Reset; — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

Note 1: All registers in this table have corresponding CLR, SET and INV registers at their virtual addresses, plus offsets of 0x4, 0x8 and 0xC, respectively. See Section 12.1.1 "CLR, SET and INV Registers" for more information.

2: Reset values are dependent on the DEVCFGx Configuration bits and the type of Reset.

#### TABLE 10-3: DMA CHANNELS 0-7 REGISTER MAP (CONTINUED)

| ess                         |                                 |                     |             |              |             |                |                |              |              | В       | its          |        |        |        |         |         |        |        |            |

|-----------------------------|---------------------------------|---------------------|-------------|--------------|-------------|----------------|----------------|--------------|--------------|---------|--------------|--------|--------|--------|---------|---------|--------|--------|------------|

| Virtual Address<br>(BF88_#) | Register<br>Name <sup>(1)</sup> | Bit Range           | 31/15       | 30/14        | 29/13       | 28/12          | 27/11          | 26/10        | 25/9         | 24/8    | 23/7         | 22/6   | 21/5   | 20/4   | 19/3    | 18/2    | 17/1   | 16/0   | All Resets |

|                             |                                 | 31:16               | _           |              | _           | _              | _              | _            | _            | _       | —            | _      | _      | _      | _       | _       | _      | _      | 0000       |

| 3290                        | DCH2DAT                         | 15:0                | _           |              | _           | _              | _              | _            | _            | _       |              |        |        | CHPDA  | AT<7:0> |         |        |        | 0000       |

| 32A0                        | DCH3CON                         | 31:16               | _           |              | _           | _              | _              | _            |              | _       | _            |        | _      | _      | —       | —       | _      | _      | 0000       |

| 32A0                        | Denseon                         | 15:0                | CHBUSY      | -            | —           | —              | —              | —            | —            | CHCHNS  | CHEN         | CHAED  | CHCHN  | CHAEN  | —       | CHEDET  | CHPR   | l<1:0> | 0000       |

| 32B0                        | DCH3ECON                        | 31:16               |             | _            | —           | —              | —              | —            |              | —       |              | 1      | ł      |        | Q<7:0>  |         |        |        | 00FF       |

|                             |                                 | 15:0                |             |              |             |                | Q<7:0>         |              |              | -       | CFORCE       | CABORT | PATEN  | SIRQEN | AIRQEN  | _       | —      | —      | FF00       |

| 32C0                        | <b>DCH3INT</b>                  | 31:16               | —           | _            | —           | —              | _              | _            | _            | —       | CHSDIE       | CHSHIE | CHDDIE | CHDHIE | CHBCIE  | CHCCIE  | CHTAIE | CHERIE | 0000       |

|                             |                                 | 15:0                |             | —            | —           | -              | —              | —            | —            | —       | CHSDIF       | CHSHIF | CHDDIF | CHDHIF | CHBCIF  | CHCCIF  | CHTAIF | CHERIF | 0000       |

| 32D0                        | DCH3SSA                         | 31:16               |             |              |             |                |                |              |              | CHSSA   | A<31:0>      |        |        |        |         |         |        |        | 0000       |

|                             |                                 | 15:0<br>31:16       |             |              |             |                |                |              |              |         |              |        |        |        |         |         |        |        | 0000       |

| 32E0                        | DCH3DSA                         | 15:0                |             |              |             |                |                |              |              | CHDSA   | A<31:0>      |        |        |        |         |         |        |        | 0000       |

|                             |                                 | 31:16               | _           | _            | _           | _              | _              | _            | _            | _       | _            | _      | _      | _      | _       | _       | _      | _      | 0000       |

| 32F0                        | DCH3SSIZ                        |                     |             |              |             |                |                |              |              |         | 0000         |        |        |        |         |         |        |        |            |

|                             |                                 | 31:16               |             |              |             |                |                |              |              |         |              | 0000   |        |        |         |         |        |        |            |

| 3300                        | DCH3DSIZ                        | 15:0                |             |              |             |                |                |              |              | CHDSI   | Z<15:0>      |        |        |        |         |         |        |        | 0000       |

|                             | DOLIGODITO                      | 31:16               | _           | _            | _           | _              | _              | —            | _            | _       | _            | _      | _      | _      | _       | _       | _      | _      | 0000       |

| 3310                        | DCH3SPTR                        | 15:0                |             |              |             | •              | •              |              |              | CHSPT   | R<15:0>      |        | •      |        | •       |         |        |        | 0000       |

| 2220                        | DCH3DPTR                        | 31:16               | _           |              | _           | —              | _              | _            | _            | —       | _            | _      | _      | _      | —       | —       | _      | _      | 0000       |

| 3320                        | DCH3DFTK                        | 15:0                |             |              |             |                |                |              |              | CHDPT   | R<15:0>      |        |        |        |         |         |        |        | 0000       |

| 3330                        | DCH3CSIZ                        | 31:16               | —           | —            | —           | —              | —              | —            | —            | —       | —            | —      | —      | —      | —       | —       | —      | —      | 0000       |

| 0000                        | DOI 130012                      | 15:0                |             |              |             |                |                |              |              | CHCSI   | Z<15:0>      |        | -      |        | -       |         |        |        | 0000       |

| 3340                        | DCH3CPTR                        | 31:16               | —           | —            | —           | —              | —              | —            | —            | —       | —            | —      | -      | —      | —       | —       | —      | —      | 0000       |

|                             |                                 | 15:0                |             |              |             | -              | -              |              |              | CHCPT   | R<15:0>      |        | -      |        | -       |         |        |        | 0000       |

| 3350                        | DCH3DAT                         | 31:16               | _           | _            | —           | _              |                | _            | _            |         | _            |        | —      | —      | —       | _       | _      |        | 0000       |

|                             |                                 | 15:0                | _           |              | _           |                |                | _            | -            |         |              |        |        |        | AT<7:0> | 1       |        |        | 0000       |

| 3360                        | DCH4CON                         | 31:16               | -           |              | _           | _              | _              | _            | _            | -       | -            | -      | -      | -      | -       |         | -      | —      | 0000       |

|                             |                                 | 15:0                |             |              |             |                |                |              |              | 0000    |              |        |        |        |         |         |        |        |            |

| 3370                        | DCH4ECON                        | 4ECON               |             |              |             |                |                |              |              |         | 00FF<br>FF00 |        |        |        |         |         |        |        |            |

|                             |                                 | 31:16               | _           | _            |             |                |                |              |              | _       | CHSDIE       | CHSHIE | CHDDIE | CHDHIE | CHBCIE  | CHCCIE  | CHTAIE | CHERIE | 0000       |

| 3380                        | DCH4INT                         | 15:0                |             | _            | _           | _              | _              | _            |              | _       | CHSDIE       | CHSHIE | CHDDIE | CHDHIE | CHBCIE  | CHCCIE  | CHTAIE | CHERIE | 0000       |

|                             |                                 | 31:16               |             |              |             |                |                | 1            |              |         |              | Shorm  | 51000  |        | 0110011 | 0110011 | JIIAI  | SHER   | 0000       |

| 3390                        | DCH4SSA                         | DCH4SSA CHSSA<31:0> |             |              |             |                |                |              |              |         |              |        |        |        |         |         |        |        |            |

|                             |                                 | 31:16               |             |              |             |                |                |              |              |         |              |        |        |        |         |         |        |        | 0000       |

| 33A0                        | DCH4DSA                         | 15:0                |             |              |             |                |                |              |              | CHDSA   | \<31:0>      |        |        |        |         |         |        |        | 0000       |

| Legen                       | <b>d:</b> x = u                 | nknown              | value on Re | eset; — = ur | nimplemente | ed, read as '0 | )'. Reset valu | ues are show | vn in hexade | ecimal. |              |        |        |        |         |         |        |        | <u>ا</u> ا |

All registers in this table have corresponding CLR, SET and INV registers at their virtual addresses, plus offsets of 0x4, 0x8 and 0xC, respectively. See Section 12.1.1 "CLR, SET and INV Registers" for more Note 1: information.

2: DMA channels 4-7 are not available on PIC32MX534/564/664/764 devices.

## TABLE 10-3: DMA CHANNELS 0-7 REGISTER MAP (CONTINUED)

| ess                         |                                 |                          |                     |       |       |       |       |       |      | Bi     | its     |      |      |      |      |      |      |      |            |

|-----------------------------|---------------------------------|--------------------------|---------------------|-------|-------|-------|-------|-------|------|--------|---------|------|------|------|------|------|------|------|------------|

| Virtual Address<br>(BF88_#) | Register<br>Name <sup>(1)</sup> | Bit Range                | 31/15               | 30/14 | 29/13 | 28/12 | 27/11 | 26/10 | 25/9 | 24/8   | 23/7    | 22/6 | 21/5 | 20/4 | 19/3 | 18/2 | 17/1 | 16/0 | All Resets |

| 35E0                        | DCH7SSIZ                        | 31:16                    | _                   |       | —     |       | -     | —     | —    |        |         |      |      | —    | —    |      | —    | -    | 0000       |

| 001 0                       | DOINCOL                         | 15:0                     |                     |       |       |       |       |       |      | CHSSIZ | Z<15:0> |      |      |      |      |      |      |      | 0000       |

| 2600                        | DCH7DSIZ                        | 31:16                    | —                   |       | —     | _     | _     | —     | —    | _      | _       | _    | _    | —    | —    | _    | —    | _    | 0000       |

| 3600                        | DCHIDSIZ                        | 15:0                     |                     |       |       |       |       |       |      | CHDSIZ | Z<15:0> |      |      |      |      |      |      |      | 0000       |

| 2610                        | DCH7SPTR                        | 31:16                    | Ι                   | _     | _     | _     | _     | _     | _    | _      | _       | _    | _    | _    | -    | _    | _    | _    | 0000       |

| 3010                        | DCH/SPIK                        | 15:0                     |                     |       |       |       |       |       |      | CHSPT  | R<15:0> |      |      |      |      |      |      |      | 0000       |

| 2620                        | DCH7DPTR                        | 31:16                    |                     |       | _     |       |       | _     | _    |        |         |      |      | _    | _    |      | _    |      | 0000       |

| 3020                        | DCHIDFIK                        | 15:0                     |                     |       |       |       |       |       |      | CHDPT  | R<15:0> |      |      |      |      |      |      |      | 0000       |

| 2620                        | DCH7CSIZ                        | 31:16                    | _                   |       | _     | -     |       | _     |      |        |         |      | -    | -    | _    | _    | _    |      | 0000       |

| 3030                        | DCH/CSIZ                        | 15:0                     | CHCSIZ<15:0> 0000   |       |       |       |       |       |      |        |         |      |      |      |      |      |      |      |            |

| 2640                        | DCH7CPTR                        | 31:16                    | Ι                   | _     | _     | _     | _     | _     | _    | _      | _       | _    | _    | _    | -    | _    | _    | _    | 0000       |

| 3040                        | DCH/CPIK                        | 15:0                     | 5:0 CHCPTR<15:0> 00 |       |       |       |       |       |      |        |         |      | 0000 |      |      |      |      |      |            |

| 2650                        | DCH7DAT                         | 31:16                    | Ι                   | _     | _     | _     | _     | _     | _    | _      | _       | _    | _    | _    | -    | _    | _    | _    | 0000       |

| 3050                        |                                 | AT 15:0 CHPDAT<7:0> 0000 |                     |       |       |       |       |       |      |        |         |      |      |      |      |      |      |      |            |

PIC32MX5XX/6XX/7XX

Legend: x = unknown value on Reset; — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

Note 1: All registers in this table have corresponding CLR, SET and INV registers at their virtual addresses, plus offsets of 0x4, 0x8 and 0xC, respectively. See Section 12.1.1 "CLR, SET and INV Registers" for more information.

2: DMA channels 4-7 are not available on PIC32MX534/564/664/764 devices.

## 15.1 Control Registers

## TABLE 15-1: WATCHDOG TIMER REGISTER MAP

| ess                      |                                 |           |       |       |       |       |       |       |      | В    | its  |      |      |      |      |      |      |      | (2)        |

|--------------------------|---------------------------------|-----------|-------|-------|-------|-------|-------|-------|------|------|------|------|------|------|------|------|------|------|------------|

| Virtual Addr<br>(BF80_#) | Register<br>Name <sup>(1)</sup> | Bit Range | 31/15 | 30/14 | 29/13 | 28/12 | 27/11 | 26/10 | 25/9 | 24/8 | 23/7 | 22/6 | 21/5 | 20/4 | 19/3 | 18/2 | 17/1 | 16/0 | All Resets |

| 0000                     | WDTOON                          | 31:16     | _     | —     | —     | —     | _     | _     | _    | _    | _    | _    | —    | —    | _    | —    | _    | _    | 0000       |

| 0000                     | WDTCON                          | 15:0      | ON    | _     |       | _     | _     | _     | _    | _    | _    |      |      |      |      |      | 0000 |      |            |

Legend: x = unknown value on Reset; -- = unimplemented, read as '0'. Reset values are shown in hexadecimal.

Note 1: All registers in this table have corresponding CLR, SET and INV registers at their virtual addresses, plus offsets of 0x4, 0x8 and 0xC, respectively. See Section 12.1.1 "CLR, SET and INV Registers" for more information.

2: Reset values are dependent on the DEVCFGx Configuration bits and the type of Reset.

#### 17.1 **Control Registers**

| ess                         |                                 |               | Bits        |             |       |       |       |       |      |       |          |      |          |       |        |      |              |      |            |

|-----------------------------|---------------------------------|---------------|-------------|-------------|-------|-------|-------|-------|------|-------|----------|------|----------|-------|--------|------|--------------|------|------------|

| Virtual Address<br>(BF80_#) | Register<br>Name <sup>(1)</sup> | Bit Range     | 31/15       | 30/14       | 29/13 | 28/12 | 27/11 | 26/10 | 25/9 | 24/8  | 23/7     | 22/6 | 21/5     | 20/4  | 19/3   | 18/2 | 17/1         | 16/0 | All Resets |

|                             | OC1CON                          | 31:16         | _           | —           |       | —     | —     | _     |      | _     | _        |      | —        | -     | —      | _    | _            | _    | 0000       |

| 3000                        | OCICON                          | 15:0          | ON          | _           | SIDL  | _     | -     | -     | -    |       | _        |      | OC32     | OCFLT | OCTSEL |      | OCM<2:0>     |      | 0000       |

| 3010                        | OC1R                            | 31:16         |             |             |       |       |       |       |      | OC1R  | <31:0>   |      |          |       |        |      |              |      | xxxx       |

| 00.0                        |                                 | 15:0          |             |             |       |       |       |       |      | 00.11 | 101107   |      |          |       |        |      |              |      | XXXX       |

| 3020                        | OC1RS                           | 31:16         |             |             |       |       |       |       |      | OC1RS | <31:0>   |      |          |       |        |      |              |      | XXXX       |

|                             |                                 | 15:0<br>31:16 | _           | _           | _     | _     | _     | _     | _    | _     | _        | _    | _        | _     | _      | _    |              | _    | XXXX       |

| 3200                        | OC2CON                          | 15:0          | ON          | _           | SIDL  |       |       |       |      |       |          |      | <br>OC32 | OCFLT | OCTSEL |      | <br>OCM<2:0> | _    | 0000       |

|                             |                                 | 31:16         |             |             | OIDE  |       |       |       |      |       |          |      | 0002     | OOLEI | OUTOLL |      | 0011112.02   |      | xxxx       |

| 3210                        | OC2R                            | 15:0          |             | OC2R<31:0>  |       |       |       |       |      |       |          |      |          |       |        |      |              |      |            |

| 0000                        | 000000                          | 31:16         |             |             |       |       |       |       |      |       |          |      |          |       |        |      |              |      |            |

| 3220                        | OC2RS                           | 15:0          |             | OC2RS<31:0> |       |       |       |       |      |       |          |      |          |       |        |      |              |      |            |

| 3400                        | OC3CON                          | 31:16         | -           | —           | _     | —     | —     | _     | _    | _     | _        | —    | —        | -     | —      | _    | —            | _    | 0000       |

| 3400                        | 003001                          | 15:0          | ON          | _           | SIDL  | —     | _     |       |      | _     | —        | —    | OC32     | OCFLT | OCTSEL |      | OCM<2:0>     |      | 0000       |

| 3410                        | OC3R                            | 31:16         |             |             |       |       |       |       |      | OC3R  | <31:0>   |      |          |       |        |      |              |      | xxxx       |

|                             |                                 | 15:0          |             |             |       |       |       |       |      |       |          |      |          |       |        |      |              |      | XXXX       |

| 3420                        | OC3RS                           | 31:16<br>15:0 |             |             |       |       |       |       |      | OC3R5 | <31:0>   |      |          |       |        |      |              |      | XXXX       |

|                             |                                 | 31:16         | _           | _           |       | _     | _     | _     | _    | _     |          | _    | _        | _     | _      |      |              | _    | xxxx 0000  |

| 3600                        | OC4CON                          | 15:0          | ON          |             | SIDL  | _     | _     | _     | _    | _     | _        | _    | OC32     | OCFLT | OCTSEL |      | OCM<2:0>     |      | 0000       |

|                             |                                 | 31:16         |             |             |       |       |       |       |      |       |          |      |          |       | ]      |      |              |      | xxxx       |

| 3610                        | OC4R                            | 15:0          |             |             |       |       |       |       |      | OC4R  | <31:0>   |      |          |       |        |      |              |      | xxxx       |

| 3620                        | OC4RS                           | 31:16         | OC4RS<31:0> |             |       |       |       |       |      |       |          |      |          |       |        |      |              |      |            |

| 3020                        | 004K3                           | 15:0          |             |             |       |       |       |       |      | 00483 | \$<31.0> |      |          |       |        |      |              |      | xxxx       |

| 3800                        | OC5CON                          | 31:16         | _           | —           |       | —     | —     | _     |      | _     | _        | _    | —        | —     | —      |      | —            |      | 0000       |

| 0000                        |                                 | 15:0          | ON          | —           | SIDL  | —     | —     | —     | _    | —     | —        | —    | OC32     | OCFLT | OCTSEL |      | OCM<2:0>     |      | 0000       |

| 3810                        | OC5R                            | 31:16         |             |             |       |       |       |       |      | OC5R  | <31:0>   |      |          |       |        |      |              |      | XXXX       |

|                             |                                 | 15:0          |             |             |       |       |       |       |      |       |          |      |          |       |        |      |              |      | xxxx       |

| 3820                        | OC5RS                           | 31:16<br>15:0 |             |             |       |       |       |       |      | OC5RS | 6<31:0>  |      |          |       |        |      |              |      | xxxx       |

|                             |                                 | 10.0          |             |             |       |       |       |       |      |       |          |      |          |       |        |      |              |      | 1 ~~~~~    |

PIC32MX5XX/6XX/7

## TABLE 17-1: OUTPUT COMPARE 1-OUTPUT COMPARE 5 REGISTER MAP

Legend:

x = unknown value on Reset; ---- = unimplemented, read as '0'. Reset values are shown in hexadecimal.

All registers in this table have corresponding CLR, SET and INV registers at their virtual addresses, plus offsets of 0x4, 0x8 and 0xC, respectively. See Section 12.1.1 "CLR, SET and INV Registers" for more Note 1: information.

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4    | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

|--------------|-------------------|-------------------|-------------------|----------------------|-------------------|-------------------|------------------|------------------|

| 24.24        | U-0               | U-0               | U-0               | U-0                  | U-0               | U-0               | U-0              | U-0              |

| 31:24        |                   | —                 | _                 | -                    | —                 | —                 | —                | —                |

| 00.40        | U-0               | U-0               | U-0               | U-0                  | U-0               | U-0               | U-0              | U-0              |

| 23:16        |                   | —                 | _                 | —                    | —                 | —                 | —                | —                |

| 45.0         | R/W-0             | U-0               | R/W-0             | U-0                  | U-0               | U-0               | U-0              | U-0              |

| 15:8         | 0N <sup>(1)</sup> | —                 | SIDL              | —                    | —                 | —                 | —                | —                |

| 7.0          | U-0               | U-0               | R/W-0             | R-0                  | R/W-0             | R/W-0             | R/W-0            | R/W-0            |

| 7:0          | _                 | —                 | OC32              | OCFLT <sup>(2)</sup> | OCTSEL            |                   | OCM<2:0>         |                  |

#### REGISTER 17-1: OCxCON: OUTPUT COMPARE 'x' CONTROL REGISTER

#### Legend:

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, r | read as '0'        |

|-------------------|------------------|--------------------------|--------------------|

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared     | x = Bit is unknown |

#### bit 31-16 Unimplemented: Read as '0'

- bit 15 **ON:** Output Compare Module On bit<sup>(1)</sup>

- 1 = Output Compare module is enabled

- 0 = Output Compare module is disabled

- bit 14 Unimplemented: Read as '0'

- bit 13 SIDL: Stop in Idle Mode bit

- 1 = Discontinue operation when CPU enters Idle mode

- 0 = Continue operation when CPU is in Idle mode

- bit 12-6 Unimplemented: Read as '0'

- bit 5 **OC32:** 32-bit Compare Mode bit

- 1 = OCxR<31:0> and/or OCxRS<31:0> are used for comparisons to the 32-bit timer source

- 0 = OCxR<15:0> and OCxRS<15:0> are used for comparisons to the 16-bit timer source

- bit 4 **OCFLT:** PWM Fault Condition Status bit<sup>(2)</sup>

- 1 = PWM Fault condition has occurred (only cleared in hardware)

- 0 = PWM Fault condition has not occurred

#### bit 3 OCTSEL: Output Compare Timer Select bit

- 1 = Timer3 is the clock source for this Output Compare module

- 0 = Timer2 is the clock source for this Output Compare module

- bit 2-0 OCM<2:0>: Output Compare Mode Select bits

- 111 = PWM mode on OCx; Fault pin enabled

- 110 = PWM mode on OCx; Fault pin disabled

- 101 = Initialize OCx pin low; generate continuous output pulses on OCx pin

- 100 = Initialize OCx pin low; generate single output pulse on OCx pin

- 011 = Compare event toggles OCx pin

- 010 = Initialize OCx pin high; compare event forces OCx pin low

- 001 = Initialize OCx pin low; compare event forces OCx pin high

- 000 = Output compare peripheral is disabled but continues to draw current

- **Note 1:** When using the 1:1 PBCLK divisor, the user's software should not read/write the peripheral's SFRs in the SYSCLK cycle immediately following the instruction that clears the module's ON bit.

- **2:** This bit is only used when OCM < 2:0 > = 111. It is read as '0' in all other modes.

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |  |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|--|--|

| 04.04        | U-0               | U-0               | U-0               | R-0               | R-0               | R-0               | R-0              | R-0              |  |  |

| 31:24        | —                 | —                 | —                 | RXBUFELM<4:0>     |                   |                   |                  |                  |  |  |

| 00.40        | U-0               | U-0               | U-0               | R-0               | R-0               | R-0               | R-0              | R-0              |  |  |

| 23:16        | —                 | —                 | —                 |                   | Tک                | (BUFELM<4:(       | )>               |                  |  |  |

| 45.0         | U-0               | U-0               | U-0               | U-0               | R-0               | U-0               | U-0              | R-0              |  |  |

| 15:8         | —                 | —                 | —                 | _                 | SPIBUSY           | _                 | _                | SPITUR           |  |  |

| 7.0          | R-0               | R/W-0             | R-0               | U-0               | R-1               | U-0               | R-0              | R-0              |  |  |

| 7:0          | SRMT              | SPIROV            | SPIRBE            |                   | SPITBE            |                   | SPITBF           | SPIRBF           |  |  |

#### **REGISTER 18-2: SPIxSTAT: SPI STATUS REGISTER**

| Legend:           | C = Clearable bit | HS = Set in hardware      |                    |

|-------------------|-------------------|---------------------------|--------------------|

| R = Readable bit  | W = Writable bit  | U = Unimplemented bit, re | ead as '0'         |

| -n = Value at POR | '1' = Bit is set  | '0' = Bit is cleared      | x = Bit is unknown |

- bit 31-29 Unimplemented: Read as '0'

- bit 28-24 **RXBUFELM<4:0>:** Receive Buffer Element Count bits (only valid when ENHBUF = 1)

- bit 23-21 Unimplemented: Read as '0'

- bit 20-16 **TXBUFELM<4:0>:** Transmit Buffer Element Count bits (only valid when ENHBUF = 1)

- bit 15-12 Unimplemented: Read as '0'

- bit 11 SPIBUSY: SPI Activity Status bit 1 = SPI peripheral is currently busy with some transactions 0 = SPI peripheral is currently idle

- Unimplemented: Read as '0'

- bit 10-9

- bit 8 SPITUR: Transmit Under Run bit

- 1 = Transmit buffer has encountered an underrun condition

- 0 = Transmit buffer has no underrun condition

This bit is only valid in Framed Sync mode; the underrun condition must be cleared by disabling/re-enabling the module.

- bit 7 **SRMT:** Shift Register Empty bit (only valid when ENHBUF = 1)

- 1 = When SPI module shift register is empty

- 0 = When SPI module shift register is not empty

- bit 6 SPIROV: Receive Overflow Flag bit

- 1 = A new data is completely received and discarded. The user software has not read the previous data in the SPIxBUF register.

- 0 = No overflow has occurred

- This bit is set in hardware; can only be cleared (= 0) in software.

- bit 5 **SPIRBE:** RX FIFO Empty bit (only valid when ENHBUF = 1) 1 = RX FIFO is empty (CRPTR = SWPTR) 0 = RX FIFO is not empty (CRPTR  $\neq$  SWPTR)

- bit 4 Unimplemented: Read as '0'

- bit 3 SPITBE: SPI Transmit Buffer Empty Status bit

- 1 = Transmit buffer, SPIxTXB is empty

- 0 = Transmit buffer, SPIxTXB is not empty

- Automatically set in hardware when SPI transfers data from SPIxTXB to SPIxSR.

- Automatically cleared in hardware when SPIxBUF is written to, loading SPIxTXB.

- bit 2 Unimplemented: Read as '0'

## REGISTER 20-2: UxSTA: UARTx STATUS AND CONTROL REGISTER (CONTINUED)

- bit 8 **TRMT:** Transmit Shift Register is Empty bit (read-only) 1 = Transmit shift register is empty and transmit buffer is empty (the last transmission has completed) 0 = Transmit shift register is not empty, a transmission is in progress or queued in the transmit buffer bit 7-6 URXISEL<1:0>: Receive Interrupt Mode Selection bit 11 = Reserved 10 = Interrupt flag bit is asserted while receive buffer is 3/4 or more full (has 6 or more data characters) 01 = Interrupt flag bit is asserted while receive buffer is 1/2 or more full (has 4 or more data characters) 00 = Interrupt flag bit is asserted while receive buffer is not empty (has at least 1 data character) **ADDEN:** Address Character Detect bit (bit 8 of received data = 1) bit 5 1 = Address Detect mode is enabled. If 9-bit mode is not selected, this control bit has no effect. 0 = Address Detect mode is disabled bit 4 **RIDLE:** Receiver Idle bit (read-only) 1 =Receiver is idle 0 = Data is being received bit 3 PERR: Parity Error Status bit (read-only) 1 = Parity error has been detected for the current character 0 = Parity error has not been detected FERR: Framing Error Status bit (read-only) bit 2 1 = Framing error has been detected for the current character 0 = Framing error has not been detected bit 1 **OERR:** Receive Buffer Overrun Error Status bit. This bit is set in hardware and can only be cleared (= 0) in software. Clearing a previously set OERR bit resets the receiver buffer and RSR to an empty state.

- 1 = Receive buffer has overflowed

- 0 = Receive buffer has not overflowed

- bit 0 **URXDA:** Receive Buffer Data Available bit (read-only)

- 1 = Receive buffer has data, at least one more character can be read

- 0 = Receive buffer is empty

### REGISTER 24-13: CIFLTCON3: CAN FILTER CONTROL REGISTER 3 (CONTINUED)

|           | · · · · · · · · · · · · · · · · · · ·                       |

|-----------|-------------------------------------------------------------|

| bit 15    | FLTEN13: Filter 13 Enable bit                               |

|           | 1 = Filter is enabled                                       |

|           | 0 = Filter is disabled                                      |

| bit 14-13 | MSEL13<1:0>: Filter 13 Mask Select bits                     |

|           | 11 = Acceptance Mask 3 selected                             |

|           | 10 = Acceptance Mask 2 selected                             |

|           | 01 = Acceptance Mask 1 selected                             |

|           | 00 = Acceptance Mask 0 selected                             |

| bit 12-8  | FSEL13<4:0>: FIFO Selection bits                            |

|           | 11111 = Message matching filter is stored in FIFO buffer 31 |

|           | 11110 = Message matching filter is stored in FIFO buffer 30 |

|           | •                                                           |

|           |                                                             |

|           | 00001 = Message matching filter is stored in FIFO buffer 1  |

|           | 00000 = Message matching filter is stored in FIFO buffer 0  |

| bit 7     | FLTEN12: Filter 12 Enable bit                               |

|           | 1 = Filter is enabled                                       |

|           | 0 = Filter is disabled                                      |

| bit 6-5   | MSEL12<1:0>: Filter 12 Mask Select bits                     |

|           | 11 = Acceptance Mask 3 selected                             |

|           | 10 = Acceptance Mask 2 selected                             |

|           | 01 = Acceptance Mask 1 selected                             |

|           | 00 = Acceptance Mask 0 selected                             |

| bit 4-0   | FSEL12<4:0>: FIFO Selection bits                            |

|           | 11111 = Message matching filter is stored in FIFO buffer 31 |

|           | 11110 = Message matching filter is stored in FIFO buffer 30 |

|           |                                                             |

|           | •                                                           |

|           | 00001 = Message matching filter is stored in FIFO buffer 1  |

|           | 00000 = Message matching filter is stored in FIFO buffer 0  |

|           |                                                             |

|           |                                                             |

Note: The bits in this register can only be modified if the corresponding filter enable (FLTENn) bit is '0'.

## REGISTER 25-16: ETHRXOVFLOW: ETHERNET CONTROLLER RECEIVE OVERFLOW STATISTICS REGISTER

| Bit Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |  |

|-----------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|--|--|

| 31:24     | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |  |  |

| 31.24     | -                 | —                 | _                 | —                 | _                 | _                 | _                | —                |  |  |

| 00.46     | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |  |  |

| 23:16     | _                 | —                 | _                 | _                 | _                 | —                 | —                | —                |  |  |

| 15.0      | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |

| 15:8      | RXOVFLWCNT<15:8>  |                   |                   |                   |                   |                   |                  |                  |  |  |

| 7:0       | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |

|           |                   |                   |                   | RXOVFLW           | /CNT<7:0>         |                   |                  |                  |  |  |

## Legend:

| Logona.           |                  |                        |                    |

|-------------------|------------------|------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, | read as '0'        |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared   | x = Bit is unknown |

#### bit 31-16 Unimplemented: Read as '0'

bit 15-0 **RXOVFLWCNT<15:0>:** Dropped Receive Frames Count bits Increment counter for frames accepted by the RX filter and subsequently dropped due to internal receive error (RXFIFO overrun). This event also sets the RXOVFLW bit (ETHIRQ<0>) interrupt flag.

**Note 1:** This register is only used for RX operations.

- 2: This register is automatically cleared by hardware after a read operation, unless the byte enables for bytes 0/1 are '0'.

- **3:** It is recommended to use the SET, CLR, or INV registers to set or clear any bit in this register. Setting or clearing any bits in this register should only be done for debug/test purposes.

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3        | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0         |

|--------------|-------------------|-------------------|-------------------|-------------------|--------------------------|-------------------|------------------|--------------------------|

| 31:24        | U-0               | U-0               | U-0               | U-0               | U-0                      | U-0               | U-0              | U-0                      |

| 31.24        |                   | —                 | -                 | -                 | —                        | —                 | —                | —                        |

| 23:16        | U-0               | U-0               | U-0               | U-0               | U-0                      | U-0               | U-0              | U-0                      |

| 23.10        |                   | —                 | -                 | -                 | —                        | —                 | —                | —                        |

| 15:8         | U-0               | U-0               | U-0               | U-0               | R/W-0                    | U-0               | U-0              | R/W-0                    |

| 10.0         | _                 | —                 | _                 | _                 | RESETRMII <sup>(1)</sup> | —                 | —                | SPEEDRMII <sup>(1)</sup> |

| 7:0          | U-0               | U-0               | U-0               | U-0               | U-0                      | U-0               | U-0              | U-0                      |

| 7.0          |                   | _                 |                   |                   | _                        | _                 |                  | —                        |

#### REGISTER 25-29: EMAC1SUPP: ETHERNET CONTROLLER MAC PHY SUPPORT REGISTER

#### Legend:

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, rea | ad as '0'          |

|-------------------|------------------|----------------------------|--------------------|

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared       | x = Bit is unknown |

- bit 31-12 Unimplemented: Read as '0'

- bit 11 **RESETRMII:** Reset RMII Logic bit<sup>(1)</sup>

- 1 = Reset the MAC RMII module

- 0 = Normal operation.

- bit 10-9 Unimplemented: Read as '0'

- bit 8 SPEEDRMII: RMII Speed bit<sup>(1)</sup>

- This bit configures the Reduced MII logic for the current operating speed.

- 1 = RMII is running at 100 Mbps

- 0 = RMII is running at 10 Mbps

- bit 7-0 Unimplemented: Read as '0'

- Note 1: This bit is only used for the RMII module.

**Note:** Both 16-bit and 32-bit accesses are allowed to these registers (including the SET, CLR and INV registers). 8-bit accesses are not allowed and are ignored by the hardware.

# PIC32MX5XX/6XX/7XX

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |  |  |  |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|--|--|--|--|

| 31:24        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |  |  |  |  |

| 51.24        |                   | _                 |                   | —                 | —                 | _                 | -                | —                |  |  |  |  |

| 23:16        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |  |  |  |  |

| 23.10        | —                 | —                 | —                 | —                 | —                 | —                 | -                | —                |  |  |  |  |

| 15.0         | R/W-P             | R/W-P             | R/W-P             | R/W-P             | R/W-P             | R/W-P             | R/W-P            | R/W-P            |  |  |  |  |

| 15:8         | STNADDR6<7:0>     |                   |                   |                   |                   |                   |                  |                  |  |  |  |  |

| 7:0          | R/W-P             | R/W-P             | R/W-P             | R/W-P             | R/W-P             | R/W-P             | R/W-P            | R/W-P            |  |  |  |  |

| 7.0          |                   | STNADDR5<7:0>     |                   |                   |                   |                   |                  |                  |  |  |  |  |

#### REGISTER 25-37: EMAC1SA0: ETHERNET CONTROLLER MAC STATION ADDRESS 0 REGISTER

| Legend:           |                  | P = Programmable bi  | t                  |

|-------------------|------------------|----------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented b  | oit, read as '0'   |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared | x = Bit is unknown |

bit 31-16 Unimplemented: Read as '0'

- bit 15-8 **STNADDR6<7:0>:** Station Address Octet 6 bits These bits hold the sixth transmitted octet of the station address.

- bit 7-0 **STNADDR5<7:0>:** Station Address Octet 5 bits These bits hold the fifth transmitted octet of the station address.

Note 1: Both 16-bit and 32-bit accesses are allowed to these registers (including the SET, CLR and INV registers). 8-bit accesses are not allowed and are ignored by the hardware.

2: This register is loaded at reset from the factory preprogrammed station address.

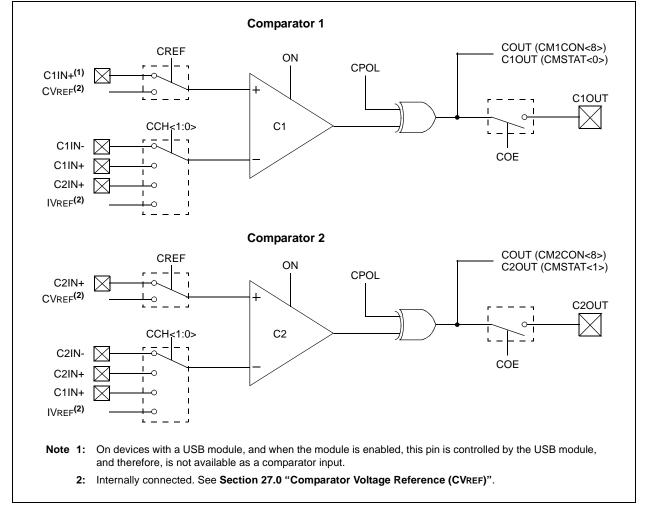

## 26.0 COMPARATOR

Note: This data sheet summarizes the features of the PIC32MX5XX/6XX/7XX family of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to **Section 19.** "Comparator" (DS60001110) in the "PIC32 Family Reference Manual", which is available from the Microchip web site (www.microchip.com/PIC32). The Comparator module contains two comparators that can be configured in a variety of ways.

Key features of the Comparator module include:

- Selectable inputs available include:

- Analog inputs multiplexed with I/O pins

- On-chip internal absolute voltage reference (IVREF)

- Comparator voltage reference (CVREF)

- · Outputs can be inverted

- Selectable interrupt generation

A block diagram of the Comparator module is illustrated in Figure 26-1.

| DC CHA        | RACTERIST              | ICS                                 | $\begin{array}{l} \mbox{Standard Operating Conditions: 2.3V to 3.6V} \\ \mbox{(unless otherwise stated)} \\ \mbox{Operating temperature} & -40^{\circ}C \leq TA \leq +85^{\circ}C \mbox{ for Industrial} \\ & -40^{\circ}C \leq TA \leq +105^{\circ}C \mbox{ for V-Temp} \end{array}$ |                              |                           |      |               |  |  |  |

|---------------|------------------------|-------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------|---------------------------|------|---------------|--|--|--|

| Param.<br>No. | Typical <sup>(3)</sup> | Max.                                | Units                                                                                                                                                                                                                                                                                 | Units Conditions             |                           |      |               |  |  |  |

| Operatir      | ng Current (I          | DD) <sup>(1,2,4)</sup> f <b>O</b> I | PIC32MX5                                                                                                                                                                                                                                                                              | 575/675/695/775/795 Family D | )evices                   |      |               |  |  |  |

| DC20          | 6                      | 9                                   | mA                                                                                                                                                                                                                                                                                    | Code executing from Flash    | -40ºC,<br>+25ºC,<br>+85ºC |      | 4 MHz         |  |  |  |

| DC20b         | 7                      | 10                                  |                                                                                                                                                                                                                                                                                       |                              | +105⁰C                    |      |               |  |  |  |

| DC20a         | 4                      |                                     |                                                                                                                                                                                                                                                                                       | Code executing from SRAM     | _                         |      |               |  |  |  |

| DC21          | 37                     | 40                                  | mA                                                                                                                                                                                                                                                                                    | Code executing from Flash    |                           | _    | 25 MHz        |  |  |  |

| DC21a         | 25                     |                                     | IIIA                                                                                                                                                                                                                                                                                  | Code executing from SRAM     | _                         |      |               |  |  |  |

| DC22          | 64                     | 70                                  | mA                                                                                                                                                                                                                                                                                    | Code executing from Flash    |                           | _    | 60 MHz        |  |  |  |

| DC22a         | 61                     | _                                   | IIIA                                                                                                                                                                                                                                                                                  | Code executing from SRAM     |                           |      |               |  |  |  |

| DC23          | 85                     | 98                                  | mA                                                                                                                                                                                                                                                                                    | Code executing from Flash    | -40ºC,<br>+25ºC,<br>+85ºC |      | 80 MHz        |  |  |  |

| DC23b         | 90                     | 120                                 | ]                                                                                                                                                                                                                                                                                     |                              | +105⁰C                    |      |               |  |  |  |