Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFI

| Product Status             | Active                                                                         |

|----------------------------|--------------------------------------------------------------------------------|

| Core Processor             | MIPS32® M4K™                                                                   |

| Core Size                  | 32-Bit Single-Core                                                             |

| Speed                      | 80MHz                                                                          |

| Connectivity               | Ethernet, I <sup>2</sup> C, SPI, UART/USART, USB OTG                           |

| Peripherals                | Brown-out Detect/Reset, DMA, POR, PWM, WDT                                     |

| Number of I/O              | 85                                                                             |

| Program Memory Size        | 64KB (64K x 8)                                                                 |

| Program Memory Type        | FLASH                                                                          |

| EEPROM Size                | -                                                                              |

| RAM Size                   | 32K x 8                                                                        |

| Voltage - Supply (Vcc/Vdd) | 2.3V ~ 3.6V                                                                    |

| Data Converters            | A/D 16x10b                                                                     |

| Oscillator Type            | Internal                                                                       |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                              |

| Mounting Type              | Surface Mount                                                                  |

| Package / Case             | 100-TQFP                                                                       |

| Supplier Device Package    | 100-TQFP (12x12)                                                               |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic32mx664f064l-i-pt |

|                            |                                                                                |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# 2.0 GUIDELINES FOR GETTING STARTED WITH 32-BIT MCUS

**Note:** This data sheet summarizes the features of the PIC32MX5XX/6XX/7XX family of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to the related section of the *"PIC32 Family Reference Manual"*, which is available from the Microchip web site (www.microchip.com/PIC32).

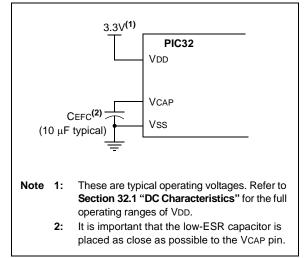

# 2.1 Basic Connection Requirements

Getting started with the PIC32MX5XX/6XX/7XX family of 32-bit Microcontrollers (MCUs) requires attention to a minimal set of device pin connections before proceeding with development. The following is a list of pin names, which must always be connected:

- All VDD and Vss pins (see 2.2 "Decoupling Capacitors")

- All AVDD and AVss pins even if the ADC module is not used (see 2.2 "Decoupling Capacitors")

- VCAP pin (see 2.3 "Capacitor on Internal Voltage Regulator (VCAP)")

- MCLR pin (see 2.4 "Master Clear (MCLR) Pin")

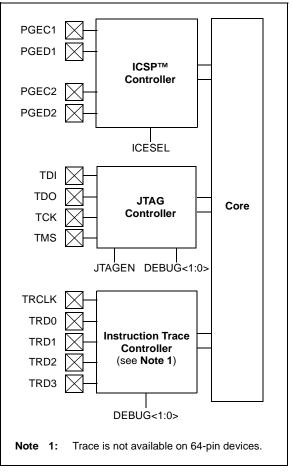

- PGECx/PGEDx pins used for In-Circuit Serial Programming<sup>™</sup> (ICSP<sup>™</sup>) and debugging purposes (see **2.5** "ICSP Pins")

- OSC1 and OSC2 pins when external oscillator source is used (see 2.8 "External Oscillator Pins")

The following pin may be required, as well: VREF+/ VREF- pins used when external voltage reference for ADC module is implemented.

**Note:** The AVDD and AVSS pins must be connected, regardless of the ADC use and the ADC voltage reference source.

# 2.2 Decoupling Capacitors

The use of decoupling capacitors on power supply pins, such as VDD, VSS, AVDD and AVSS is required. See Figure 2-1.

Consider the following criteria when using decoupling capacitors:

- Value and type of capacitor: A value of 0.1  $\mu$ F (100 nF), 10-20V is recommended. The capacitor should be a low Equivalent Series Resistance (low-ESR) capacitor and have resonance frequency in the range of 20 MHz and higher. It is further recommended to use ceramic capacitors.

- Placement on the printed circuit board: The decoupling capacitors should be placed as close to the pins as possible. It is recommended that the capacitors be placed on the same side of the board as the device. If space is constricted, the capacitor can be placed on another layer on the PCB using a via; however, ensure that the trace length from the pin to the capacitor is within one-quarter inch (6 mm) in length.

- Handling high frequency noise: If the board is experiencing high frequency noise, upward of tens of MHz, add a second ceramic-type capacitor in parallel to the above described decoupling capacitor. The value of the second capacitor can be in the range of 0.01  $\mu$ F to 0.001  $\mu$ F. Place this second capacitor next to the primary decoupling capacitor. In high-speed circuit designs, consider implementing a decade pair of capacitances as close to the power and ground pins as possible. For example, 0.1  $\mu$ F in parallel with 0.001  $\mu$ F.

- Maximizing performance: On the board layout from the power supply circuit, run the power and return traces to the decoupling capacitors first, and then to the device pins. This ensures that the decoupling capacitors are first in the power chain. Equally important is to keep the trace length between the capacitor and the power pins to a minimum, thereby reducing PCB track inductance.

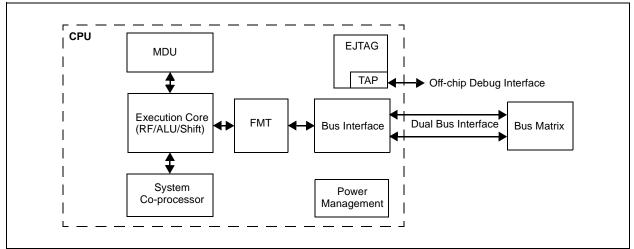

# 3.0 CPU

Note: This data sheet summarizes the features of the PIC32MX5XX/6XX/7XX family of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to Section 2. "CPU" (DS60001113) in the "PIC32 Family Reference Manual", which is available from the Microchip web site (www.microchip.com/PIC32). Resources for the MIPS32<sup>®</sup> M4K<sup>®</sup> Processor Core are available at http://www.imgtec.com.

The MIPS32<sup>®</sup> M4K<sup>®</sup> Processor core is the heart of the PIC32MX5XX/6XX/7XX family processor. The CPU fetches instructions, decodes each instruction, fetches source operands, executes each instruction and writes the results of instruction execution to the proper destinations.

# 3.1 Features

- 5-stage pipeline

- · 32-bit address and data paths

- MIPS32 Enhanced Architecture (Release 2)

- Multiply-accumulate and multiply-subtract instructions

- Targeted multiply instruction

- Zero/One detect instructions

- WAIT instruction

- Conditional move instructions (MOVN, MOVZ)

- Vectored interrupts

- Programmable exception vector base

- Atomic interrupt enable/disable

- GPR shadow registers to minimize latency for interrupt handlers

- Bit field manipulation instructions

- MIPS16e<sup>®</sup> code compression

- 16-bit encoding of 32-bit instructions to improve code density

- Special PC-relative instructions for efficient loading of addresses and constants

- SAVE and RESTORE macro instructions for setting up and tearing down stack frames within subroutines

- Improved support for handling 8-bit and 16-bit data types

- Simple Fixed Mapping Translation (FMT) mechanism

- Simple dual bus interface

- Independent 32-bit address and data busses

- Transactions can be aborted to improve interrupt latency

- · Autonomous multiply/divide unit

- Maximum issue rate of one 32x16 multiply per clock

- Maximum issue rate of one 32x32 multiply every other clock

- Early-in iterative divide. Minimum 11 and maximum 33 clock latency (dividend (*rs*) sign extension-dependent)

- Power control

- Minimum frequency: 0 MHz

- Low-Power mode (triggered by WAIT instruction)

- Extensive use of local gated clocks

- EJTAG debug and instruction trace

- Support for single stepping

- Virtual instruction and data address/value

- Breakpoints

- PC tracing with trace compression

# FIGURE 3-1: MIPS32<sup>®</sup> M4K<sup>®</sup> PROCESSOR CORE BLOCK DIAGRAM

|                             |                                 | PI            | C32MX   | 5/5-25  | 6L DEV  | ICES                          |                               |                               |                               |                             |                               |                               |                             |                       |                         |          |               |        |            |

|-----------------------------|---------------------------------|---------------|---------|---------|---------|-------------------------------|-------------------------------|-------------------------------|-------------------------------|-----------------------------|-------------------------------|-------------------------------|-----------------------------|-----------------------|-------------------------|----------|---------------|--------|------------|

| ss                          |                                 |               |         |         |         |                               |                               |                               |                               | В                           | its                           |                               |                             |                       |                         |          |               |        |            |

| Virtual Address<br>(BF88_#) | Register<br>Name <sup>(1)</sup> | Bit Range     | 31/15   | 30/14   | 29/13   | 28/12                         | 27/11                         | 26/10                         | 25/9                          | 24/8                        | 23/7                          | 22/6                          | 21/5                        | 20/4                  | 19/3                    | 18/2     | 17/1          | 16/0   | All Resets |

| 1000                        | INTCON                          | 31:16         |         | _       | _       | _                             | _                             |                               |                               | —                           | —                             |                               | _                           | _                     | 1                       |          | —             | SS0    | 0000       |

| 1000                        | INTCOM                          | 15:0          | _       | _       | —       | MVEC                          | _                             |                               | TPC<2:0>                      |                             | _                             | —                             | —                           | INT4EP                | INT3EP                  | INT2EP   | INT1EP        | INT0EP | 0000       |

| 1010                        | INTSTAT <sup>(3)</sup>          | 31:16         | —       | —       | —       | —                             | —                             | _                             | —                             | —                           | —                             | —                             |                             | —                     | —                       | _        | —             | —      | 0000       |

|                             | -                               | 15:0          | —       | —       | —       | —                             | —                             |                               | SRIPL<2:0>                    | •                           | —                             | —                             |                             |                       | VEC                     | <5:0>    |               |        | 0000       |

| 1020                        | IPTMR                           | 31:16<br>15:0 |         |         |         |                               |                               |                               |                               | IPTMR                       | <31:0>                        |                               |                             |                       |                         |          |               |        | 0000       |

| 1030                        | IFS0                            | 31:16         | I2C1MIF | I2C1SIF | I2C1BIF | U1TXIF<br>SPI3TXIF<br>I2C3MIF | U1RXIF<br>SPI3RXIF<br>I2C3SIF | U1EIF<br>SPI3EIF<br>I2C3BIF   | SPI1TXIF                      | SPI1RXIF                    | SPI1EIF                       | OC5IF                         | IC5IF                       | T5IF                  | INT4IF                  | OC4IF    | IC4IF         | T4IF   | 0000       |

|                             |                                 | 15:0          | INT3IF  | OC3IF   | IC3IF   | T3IF                          | INT2IF                        | OC2IF                         | IC2IF                         | T2IF                        | INT1IF                        | OC1IF                         | IC1IF                       | T1IF                  | INT0IF                  | CS1IF    | CS0IF         | CTIF   | 0000       |

|                             |                                 | 31:16         | IC3EIF  | IC2EIF  | IC1EIF  | —                             | _                             | CAN1IF                        | USBIF                         | FCEIF                       | DMA7IF <sup>(2)</sup>         | DMA6IF <sup>(2)</sup>         | DMA5IF <sup>(2)</sup>       | DMA4IF <sup>(2)</sup> | DMA3IF                  | DMA2IF   | DMA1IF        | DMA0IF | 0000       |

| 1040                        | IFS1                            | 15:0          | RTCCIF  | FSCMIF  | I2C2MIF | I2C2SIF                       | I2C2BIF                       | U2TXIF<br>SPI4TXIF<br>I2C5MIF | U2RXIF<br>SPI4RXIF<br>I2C5SIF | U2EIF<br>SPI4EIF<br>I2C5BIF | U3TXIF<br>SPI2TXIF<br>I2C4MIF | U3RXIF<br>SPI2RXIF<br>I2C4SIF | U3EIF<br>SPI2EIF<br>I2C4BIF | CMP2IF                | CMP1IF                  | PMPIF    | AD1IF         | CNIF   | 0000       |

| 1050                        | 1500                            | 31:16         | —       | _       | _       | —                             | _                             | _                             | _                             | _                           | _                             | _                             | _                           |                       | _                       | _        | _             | _      | 0000       |

| 1050                        | IFS2                            | 15:0          | _       | _       | _       | _                             | U5TXIF                        | U5RXIF                        | U5EIF                         | U6TXIF                      | U6RXIF                        | U6EIF                         | U4TXIF                      | U4RXIF                | U4EIF                   | PMPEIF   | IC5EIF        | IC4EIF | 0000       |

| 1060                        | IEC0                            | 31:16         | I2C1MIE | I2C1SIE | I2C1BIE | U1TXIE<br>SPI3TXIE<br>I2C3MIE | U1RXIE<br>SPI3RXIE<br>I2C3SIE | U1EIE<br>SPI3EIE<br>I2C3BIE   | SPI1TXIE                      | SPI1RXIE                    | SPI1EIE                       | OC5IE                         | IC5IE                       | T5IE                  | INT4IE                  | OC4IE    | IC4IE         | T4IE   | 0000       |

|                             |                                 | 15:0          | INT3IE  | OC3IE   | IC3IE   | T3IE                          | INT2IE                        | OC2IE                         | IC2IE                         | T2IE                        | INT1IE                        | OC1IE                         | IC1IE                       | T1IE                  | INT0IE                  | CS1IE    | CS0IE         | CTIE   | 0000       |

|                             |                                 | 31:16         | IC3EIE  | IC2EIE  | IC1EIE  | _                             | _                             | CAN1IE                        | USBIE                         | FCEIE                       | DMA7IE <sup>(2)</sup>         | DMA6IE <sup>(2)</sup>         | DMA5IE <sup>(2)</sup>       | DMA4IE <sup>(2)</sup> | <b>DMA3IE</b>           | DMA2IE   | DMA1IE        | DMA0IE | 0000       |

| 1070                        | IEC1                            | 15:0          | RTCCIE  | FSCMIE  | I2C2MIE | I2C2SIE                       | I2C2BIE                       | U2TXIE<br>SPI4TXIE<br>I2C5MIE | U2RXIE<br>SPI4RXIE<br>I2C5SIE | U2EIE<br>SPI4EIE<br>I2C5BIE | U3TXIE<br>SPI2TXIE<br>I2C4MIE | U3RXIE<br>SPI2RXIE<br>I2C4SIE | U3EIE<br>SPI2EIE<br>I2C4BIE | CMP2IE                | CMP1IE                  | PMPIE    | AD1IE         | CNIE   | 0000       |

|                             |                                 | 31:16         | _       | _       | _       | _                             | _                             | -                             | _                             | _                           | _                             | _                             | _                           | _                     |                         | _        | _             | _      | 0000       |

| 1080                        | IEC2                            | 15:0          | _       | _       | _       | _                             | U5TXIE                        | U5RXIE                        | U5EIE                         | U6TXIE                      | U6RXIE                        | U6EIE                         | U4TXIE                      | U4RXIE                | U4EIE                   | PMPEIE   | IC5EIE        | IC4EIE | 0000       |

| 1090                        | IPC0                            | 31:16         |         |         | _       |                               | INT0IP<2:0>                   |                               | INTOIS                        | 6<1:0>                      | —                             |                               |                             |                       | CS1IP<2:0>              |          | CS1IS         | S<1:0> | 0000       |

| 1090                        | IPCU                            | 15:0          |         | _       | —       |                               | CS0IP<2:0>                    |                               | CSOIS                         | S<1:0>                      | -                             | _                             | _                           |                       | CTIP<2:0>               |          | CTIS          | <1:0>  | 0000       |

| 10A0                        | IPC1                            | 31:16         | _       | _       | —       |                               | INT1IP<2:0>                   |                               |                               | 6<1:0>                      | _                             | —                             | —                           |                       | OC1IP<2:0>              | <b>`</b> |               | 6<1:0> | 0000       |

| 10/10                       |                                 | 15:0          | —       | —       | —       |                               | IC1IP<2:0>                    |                               |                               | <1:0>                       | —                             | —                             | —                           |                       | T1IP<2:0>               |          | T1IS          | -      | 0000       |

| 10B0                        | IPC2                            | 31:16         | —       | _       | —       |                               | INT2IP<2:0>                   | •                             |                               | S<1:0>                      | —                             | —                             | -                           | (                     | OC2IP<2:0>              | <b>`</b> |               | S<1:0> | 0000       |

|                             |                                 | 15:0          | _       | —       |         |                               | IC2IP<2:0>                    |                               |                               | <1:0>                       | _                             | —                             | —                           |                       | T2IP<2:0>               |          | -             | <1:0>  | 0000       |

| 10C0                        | IPC3                            | 31:16<br>15:0 |         |         |         |                               | INT3IP<2:0><br>IC3IP<2:0>     | •                             |                               | S<1:0><br><1:0>             |                               |                               |                             |                       | OC3IP<2:0><br>T3IP<2:0> | <b>`</b> | OC3IS<br>T3IS | S<1:0> | 0000       |

| Legend                      |                                 |               |         |         |         |                               |                               | oc oro chou                   | n in hexadeo                  |                             | _                             | _                             | _                           | l                     | 131552.0>               |          | 1313          | \$1.02 | 0000       |

# TABLE 7-5: INTERRUPT REGISTER MAP FOR PIC32MX534F064L, PIC32MX564F064L, PIC32MX564F128L PIC32MX575F512L AND PIC32MX575F256L DEVICES

x = unknown value on Reset; - = unimplemented, read as '0'. Reset values are shown in nexadecimal.

Note 1: Except where noted, all registers in this table have corresponding CLR, SET and INV registers at their virtual addresses, plus offsets of 0x4, 0x8 and 0xC, respectively. See Section 12.1.1 "CLR, SET and INV Registers" for more information.

PIC32MX5XX/6XX/7XX

2: These bits are not available on PIC32MX534/564 devices.

3: This register does not have associated CLR, SET, and INV registers.

#### **TABLE 7-7:** INTERRUPT REGISTER MAP FOR PIC32MX764F128L, PIC32MX775F256L, PIC32MX775F512L AND PIC32MX795F512L DEVICES (CONTINUED)

| ess                         |                                 |           |       |       |       |           |             |       |             | В                     | its         |      |             |             |             |        |             |                      |             |  |             |  |             |  |   |   |   |  |             |   |        |        |      |

|-----------------------------|---------------------------------|-----------|-------|-------|-------|-----------|-------------|-------|-------------|-----------------------|-------------|------|-------------|-------------|-------------|--------|-------------|----------------------|-------------|--|-------------|--|-------------|--|---|---|---|--|-------------|---|--------|--------|------|

| Virtual Address<br>(BF88_#) | Register<br>Name <sup>(1)</sup> | Bit Range | 31/15 | 30/14 | 29/13 | 28/12     | 27/11       | 26/10 | 25/9        | 24/8                  | 23/7        | 22/6 | 21/5        | 20/4        | 19/3        | 18/2   | 17/1        | 16/0                 | All Resets  |  |             |  |             |  |   |   |   |  |             |   |        |        |      |

| 10D0                        | IPC4                            | 31:16     | _     | —     | -     |           | INT4IP<2:0> |       | INT4IS      | S<1:0>                | _           | _    | _           |             | OC4IP<2:0>  |        | OC4IS       | 5<1:0>               | 0000        |  |             |  |             |  |   |   |   |  |             |   |        |        |      |

| TODO                        | IPC4                            | 15:0      | _     | _     | _     |           | IC4IP<2:0>  |       | IC4IS<1:0>  |                       | _           | _    | -           |             | T4IP<2:0>   |        | T4IS-       | <1:0>                | 0000        |  |             |  |             |  |   |   |   |  |             |   |        |        |      |

| 10E0                        | IPC5                            | 31:16     | _     |       | —     |           | SPI1IP<2:0> | •     | SPI1IS<1:0> |                       | _           | _    | _           |             | OC5IP<2:0>  | •      | OC5IS       | S<1:0>               | 0000        |  |             |  |             |  |   |   |   |  |             |   |        |        |      |

| IUEU                        | IPC5                            | 15:0      | —     | _     | _     |           | IC5IP<2:0>  |       | IC5IS<1:0>  |                       | _           | _    | _           |             | T5IP<2:0>   |        | T5IS-       | <1:0>                | 0000        |  |             |  |             |  |   |   |   |  |             |   |        |        |      |

|                             |                                 | 31:16     | —     | _     | _     |           | AD1IP<2:0>  |       | AD1IS<1:0>  |                       | _           | _    | _           |             | CNIP<2:0>   |        | CNIS        | <1:0>                | 0000        |  |             |  |             |  |   |   |   |  |             |   |        |        |      |

| 10F0                        | IPC6                            |           |       |       |       |           |             |       |             |                       |             |      |             |             | U1IP<2:0>   |        | U1IS-       | <1:0>                |             |  |             |  |             |  |   |   |   |  |             |   |        |        |      |

| 1000                        | IFCO                            | 15:0      | _     | -     | -     |           | I2C1IP<2:0> |       | I2C1IS<1:0> |                       | I2C1IS<1:0> |      | I2C1IS<1:0> |             | I2C1IS<1:0> |        | I2C1IS<1:0> |                      | I2C1IS<1:0> |  | I2C1IS<1:0> |  | I2C1IS<1:0> |  | — | — | — |  | SPI3IP<2:0> | • | SPI3IS | S<1:0> | 0000 |

|                             |                                 |           |       |       |       |           |             |       |             |                       |             |      |             | 12C3IP<2:0> |             | 12C315 | 5<1:0>      |                      |             |  |             |  |             |  |   |   |   |  |             |   |        |        |      |

|                             |                                 |           |       |       |       |           | U3IP<2:0>   |       | U3IS        | <1:0>                 |             |      |             |             |             |        |             |                      |             |  |             |  |             |  |   |   |   |  |             |   |        |        |      |

| 1100                        | IPC7                            | 31:16     | —     | —     | -     |           | SPI2IP<2:0> |       | SPI2IS      | S<1:0>                | —           | —    | -           |             | CMP2IP<2:0  | >      | CMP2I       | S<1:0>               | 0000        |  |             |  |             |  |   |   |   |  |             |   |        |        |      |

| 1100                        | 11 07                           |           |       |       |       |           | I2C4IP<2:0> |       | 12C418      | S<1:0>                |             |      |             |             |             |        |             |                      |             |  |             |  |             |  |   |   |   |  |             |   |        |        |      |

|                             |                                 | 15:0      | _     |       |       | (         | CMP1IP<2:0  | >     | CMP1I       | S<1:0>                | —           | —    | —           |             | PMPIP<2:0>  | •      | PMPIS       | S<1:0>               | 0000        |  |             |  |             |  |   |   |   |  |             |   |        |        |      |

|                             |                                 | 31:16     | _     | —     | —     | F         | RTCCIP<2:0  | >     | RTCCI       | S<1:0>                | —           | —    | —           | I           | SCMIP<2:0   | >      | FSCMI       | S<1:0>               | 0000        |  |             |  |             |  |   |   |   |  |             |   |        |        |      |

| 1110                        | IPC8                            |           |       |       |       |           |             |       |             |                       |             |      |             |             | U2IP<2:0>   |        | U2IS        | <1:0>                |             |  |             |  |             |  |   |   |   |  |             |   |        |        |      |

| 1110                        | 11 00                           | 15:0      | —     | —     | -     |           | I2C2IP<2:0> |       | 12C218      | S<1:0>                | —           | —    | —           |             | SPI4IP<2:0> | •      | SPI4IS      | S<1:0>               | 0000        |  |             |  |             |  |   |   |   |  |             |   |        |        |      |

|                             |                                 |           |       |       |       |           |             |       |             |                       |             |      |             |             | I2C5IP<2:0> | •      | 12C515      | 5<1:0>               |             |  |             |  |             |  |   |   |   |  |             |   |        |        |      |

| 1120                        | IPC9                            | 31:16     | —     | —     | —     | [         | DMA3IP<2:0  | >     | DMA3I       | S<1:0>                | —           | —    | —           | I           | DMA2IP<2:0  | >      | DMA2I       | S<1:0>               | 0000        |  |             |  |             |  |   |   |   |  |             |   |        |        |      |

| 1120                        | IFC9                            | 15:0      | —     | -     | —     |           | DMA1IP<2:0  |       | DMA1I       | S<1:0>                | —           | —    | —           |             | DMA0IP<2:0  |        | DMA0I       | S<1:0>               | 0000        |  |             |  |             |  |   |   |   |  |             |   |        |        |      |

| 1130                        | IPC10                           | 31:16     | —     | —     | —     | D         | MA7IP<2:0>  | (2)   | DMA7IS      | S<1:0> <sup>(2)</sup> | —           | —    | —           | D           | MA6IP<2:0>  | (2)    | DMA6IS      | <1:0> <sup>(2)</sup> | 0000        |  |             |  |             |  |   |   |   |  |             |   |        |        |      |

| 1130                        | IFCIU                           | 15:0      | —     | _     | _     | D         | MA5IP<2:0>  | (2)   | DMA5IS      | S<1:0> <sup>(2)</sup> | _           | _    | _           | D           | MA4IP<2:0>  | (2)    | DMA4IS      | <1:0> <sup>(2)</sup> | 0000        |  |             |  |             |  |   |   |   |  |             |   |        |        |      |

| 1140                        | IPC11                           | 31:16     |       | -     | —     | C         | AN2IP<2:0>  | (2)   | CAN2IS      | S<1:0> <sup>(2)</sup> | _           | _    | _           |             | CAN1IP<2:0  | >      | CAN1        | S<1:0>               | 0000        |  |             |  |             |  |   |   |   |  |             |   |        |        |      |

| 1140                        | IFCII                           | 15:0      | —     | _     | —     |           | USBIP<2:0>  |       | USBIS       | S<1:0>                | _           | —    | _           |             | FCEIP<2:0>  | ,      | FCEIS       | <1:0>                | 0000        |  |             |  |             |  |   |   |   |  |             |   |        |        |      |

| 1150                        | IPC12                           | 31:16     | _     | _     | —     | U5IP<2:0> |             | U5IS  | <1:0>       | —                     | —           | —    | U6IP<2:0>   |             | U6IS-       | <1:0>  | 0000        |                      |             |  |             |  |             |  |   |   |   |  |             |   |        |        |      |

| 1150                        | IFC12                           | 15:0      |       | —     | _     |           | U4IP<2:0>   |       | U4IS        | <1:0>                 | —           | _    | —           |             | ETHIP<2:0>  |        | ETHIS       | <1:0>                | 0000        |  |             |  |             |  |   |   |   |  |             |   |        |        |      |

DS60001156J-page 88

Legend: x = unknown value on Reset; — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

Except where noted, all registers in this table have corresponding CLR, SET and INV registers at their virtual addresses, plus offsets of 0x4, 0x8 and 0xC, respectively. See Section 12.1.1 "CLR, SET and INV Note 1: Registers" for more information.

2: This bit is unimplemented on PIC32MX764F128L device.

3: This register does not have associated CLR, SET, and INV registers.

# REGISTER 7-6: IPCx: INTERRUPT PRIORITY CONTROL REGISTER (CONTINUED)

| REGIST    |                                                                                                                       |

|-----------|-----------------------------------------------------------------------------------------------------------------------|

| bit 12-10 | IP01<2:0>: Interrupt Priority bits                                                                                    |

|           | 111 = Interrupt priority is 7                                                                                         |

|           | •                                                                                                                     |

|           |                                                                                                                       |

|           | 010 = Interrupt priority is 2                                                                                         |

|           | 001 = Interrupt priority is 1                                                                                         |

|           | 000 = Interrupt is disabled                                                                                           |

| bit 9-8   | IS01<1:0>: Interrupt Sub-priority bits                                                                                |

|           | 11 = Interrupt sub-priority is 3                                                                                      |

|           | 10 = Interrupt sub-priority is 2                                                                                      |

|           | 01 = Interrupt sub-priority is 1                                                                                      |

|           | 00 = Interrupt sub-priority is 0                                                                                      |

| bit 7-5   | Unimplemented: Read as '0'                                                                                            |

| bit 4-2   | IP00<2:0>: Interrupt Priority bits                                                                                    |

|           | 111 = Interrupt priority is 7                                                                                         |

|           | •                                                                                                                     |

|           |                                                                                                                       |

|           | 010 = Interrupt priority is 2                                                                                         |

|           | 001 = Interrupt priority is 1                                                                                         |

|           | 000 = Interrupt is disabled                                                                                           |

| bit 1-0   | IS00<1:0>: Interrupt Sub-priority bits                                                                                |

|           | 11 = Interrupt sub-priority is 3                                                                                      |

|           | 10 = Interrupt sub-priority is 2                                                                                      |

|           | 01 = Interrupt sub-priority is 1                                                                                      |

|           | 00 = Interrupt sub-priority is 0                                                                                      |

| Nete      | This projection proposed to a proposite definition of the IDOs projection Defaulty T-11 T-1 ( ) ( )                   |

| Note:     | This register represents a generic definition of the IPCx register. Refer to Table 7-1 for the exact bit definitions. |

|           |                                                                                                                       |

# TABLE 10-3: DMA CHANNELS 0-7 REGISTER MAP (CONTINUED)

| ess                         |                                 |               |        |                   |       |              |        |       |      | Bi     | ts       |        |        |        |         |        |        |         |            |

|-----------------------------|---------------------------------|---------------|--------|-------------------|-------|--------------|--------|-------|------|--------|----------|--------|--------|--------|---------|--------|--------|---------|------------|

| Virtual Address<br>(BF88_#) | Register<br>Name <sup>(1)</sup> | Bit Range     | 31/15  | 30/14             | 29/13 | 28/12        | 27/11  | 26/10 | 25/9 | 24/8   | 23/7     | 22/6   | 21/5   | 20/4   | 19/3    | 18/2   | 17/1   | 16/0    | All Resets |

| 3180                        | DCH1DSIZ                        | 31:16         | _      | -                 | —     | _            | -      | -     | _    | —      | _        | _      | _      | —      | —       | _      | _      | _       | 0000       |

| 5100                        |                                 | 15:0          |        |                   |       | -            |        |       | -    | CHDSIZ | <15:0>   |        |        | -      | -       |        |        |         | 0000       |

| 3190                        | DCH1SPTR                        | 31:16         | —      | —                 | —     | —            | —      | —     | _    | —      | —        | —      | —      | —      | —       | —      | —      | —       | 0000       |

| 5150                        | Donnor IIX                      | 15:0          |        |                   |       |              |        |       |      | CHSPTI | R<15:0>  |        |        |        |         |        |        |         | 0000       |

| 31A0                        | DCH1DPTR                        | 31:16         | —      | —                 | —     | —            | —      | —     | —    | —      | —        | —      | —      | —      | —       | —      | —      | —       | 0000       |

| 5170                        |                                 | 15:0          |        |                   |       |              |        |       |      | CHDPTI | R<15:0>  |        |        |        |         |        |        |         | 0000       |

| 31B0                        | DCH1CSIZ                        | 31:16         | —      | —                 | —     | —            | —      | —     | _    | —      | —        | —      | —      | —      | —       | —      | —      | —       | 0000       |

| 0100                        |                                 | 15:0          |        |                   |       |              |        |       |      |        |          |        |        |        |         | 0000   |        |         |            |

| 31C0                        | DCH1CPTR                        | 31:16         | _      |                   |       |              |        |       |      |        |          |        |        |        |         |        |        |         |            |

| 0100                        |                                 | 15:0          |        | CHCPTR<15:0> 0000 |       |              |        |       |      |        |          |        |        |        |         | 0000   |        |         |            |

| 31D0                        | DCH1DAT                         | 31:16         | _      | _                 | —     | _            | _      | _     | _    | —      | —        | —      | —      | —      | _       | —      | —      | —       | 0000       |

| 0120                        | Bonnbra                         | 15:0          | _      | _                 | —     | _            | _      | _     | _    | —      |          |        |        | CHPDA  | \T<7:0> | -      | -      | -       | 0000       |

| 31E0                        | DCH2CON                         | 31:16         | —      | —                 | —     | —            | —      | —     |      | —      | —        | —      | —      | —      | —       | —      | —      | —       | 0000       |

| 0120                        | DONZOON                         | 15:0          | CHBUSY | _                 | —     | —            | _      | _     |      | CHCHNS | CHEN     | CHAED  | CHCHN  | CHAEN  | _       | CHEDET | CHPR   | :l<1:0> | 0000       |

| 31E0                        | DCH2ECON                        | 31:16         | —      | —                 | —     | —            | —      | —     | _    | —      |          |        |        | CHAIR  |         |        |        |         | OOFF       |

| 511.0                       | DONZEOON                        | 15:0          |        |                   |       | CHSIR        | Q<7:0> |       |      |        | CFORCE   | CABORT | PATEN  | SIRQEN | AIRQEN  | —      | —      | —       | FF00       |

| 3200                        | DCH2INT                         | 31:16         | _      | _                 | —     | —            | _      | _     |      | —      | CHSDIE   | CHSHIE | CHDDIE | CHDHIE | CHBCIE  | CHCCIE | CHTAIE | CHERIE  | 0000       |

| 5200                        | DONZINI                         | 15:0          | —      | —                 | —     | —            | —      | —     | _    | —      | CHSDIF   | CHSHIF | CHDDIF | CHDHIF | CHBCIF  | CHCCIF | CHTAIF | CHERIF  | 0000       |

| 3210                        | DCH2SSA                         | 31:16<br>15:0 |        |                   |       |              |        |       |      | CHSSA  | <31:0>   |        |        |        |         |        |        |         | 0000       |

| 3220                        | DCH2DSA                         | 31:16<br>15:0 |        |                   |       |              |        |       |      | CHDSA  | <31:0>   |        |        |        |         |        |        |         | 0000       |

|                             |                                 | 31:16         |        | _                 | _     | _            | _      | _     | _    |        | _        | _      | _      | _      |         |        | _      |         | 0000       |

| 3230                        | DCH2SSIZ                        | 15:0          |        |                   |       |              |        |       |      | CHSSIZ |          |        |        |        |         |        |        |         | 0000       |

|                             |                                 | 31:16         | _      | _                 | _     | _            | _      | _     | _    | _      | _        | _      | _      | _      |         | _      | _      | _       | 0000       |

| 3240                        | DCH2DSIZ                        | 15:0          |        |                   |       |              |        |       |      | CHDSIZ |          |        |        |        |         |        |        |         | 0000       |

|                             |                                 | 31:16         | _      | _                 | _     | _            | _      | _     | _    | _      | _        | _      | _      | _      | _       | _      | _      | _       | 0000       |

| 3250                        | DCH2SPTR                        | 15:0          |        |                   |       |              |        |       |      | CHSPTI |          |        |        |        |         |        |        |         | 0000       |

| <u> </u>                    |                                 | 31:16         | _      | _                 | _     | _            | _      | _     | _    | _      |          | _      | _      | _      |         |        | _      |         | 0000       |

| 3260                        | DCH2DPTR                        | 15:0          |        |                   |       |              |        |       |      |        |          |        |        |        |         |        |        |         |            |

|                             |                                 | 31:16         | _      |                   |       |              |        |       | _    |        |          | _      |        | _      | _       |        | _      | _       | 0000       |

| 3270                        | DCH2CSIZ                        | 15:0          |        |                   |       |              |        |       |      | CHCSIZ |          |        |        |        |         |        |        |         | 0000       |

|                             |                                 |               |        |                   |       |              |        |       |      | 010312 | .< 10.02 |        |        |        |         |        |        |         |            |

| 3280                        | DCH2CPTR                        | 31:16         | _      |                   |       |              |        |       |      |        |          |        |        |        |         |        |        |         |            |

|                             |                                 | 15:0          |        |                   |       | n, se pear p |        |       |      | CHCPTI | ۲<15:0>  |        |        |        |         |        |        |         | 0000       |

Legend: x = unknown value on Reset; - = unimplemented, read as '0'. Reset values are shown in hexadecimal.

Note 1: All registers in this table have corresponding CLR, SET and INV registers at their virtual addresses, plus offsets of 0x4, 0x8 and 0xC, respectively. See Section 12.1.1 "CLR, SET and INV Registers" for more information.

2: DMA channels 4-7 are not available on PIC32MX534/564/664/764 devices.

#### 11.1 **Control Registers**

### TABLE 11-1: USB REGISTER MAP

| Signature         Signature           5040         U10TGIR <sup>(2)</sup> 5050         U10TGIR <sup>(2)</sup> 5060         U10TGSTAT           5070         U10TGCO           5080         U11PWRC           5200         U11R <sup>(2)</sup> 5210         U11EIR <sup>(2)</sup> 5220         U1EIR <sup>(2)</sup> 5220         U1EIR <sup>(2)</sup> | 2) 31:<br>15:<br>15:<br>15:<br>15:<br>15:<br>15:<br>15:<br>1                                | i:16       5:0       1:16       5:0       1:16       5:0       1:16       5:0       1:16 | 31/15<br>        | 30/14<br> | 29/13<br> | 28/12 | 27/11 | 26/10 | 25/9 | 24/8 | Bits<br>23/7           | 22/6               | 04/5                 |            |           |          |                 | r        | Resets |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------|------------------|-----------|-----------|-------|-------|-------|------|------|------------------------|--------------------|----------------------|------------|-----------|----------|-----------------|----------|--------|

| 5040         U10TGIR <sup>(2)</sup> 5050         U10TGIE           5060         U10TGSTAT           5070         U10TGCO           5080         U1PWRC           5200         U1IR <sup>(2)</sup> 5210         U1IE           5220         U1EIR <sup>(2)</sup>                                                                                      | 2) 31:<br>15:<br>15:<br>15:<br>15:<br>15:<br>15:<br>15:<br>1                                | 1:16<br>5:0<br>1:16<br>5:0<br>1:16<br>5:0<br>1:16                                        |                  | -         |           | -     |       |       | 25/9 | 24/8 | 23/7                   | 22/6               | 04/5                 |            |           | ļ        |                 |          | eset   |

| 5050         U10TGIE           5060         U10TGSTAT           5070         U10TGCO           5080         U1PWRC           5200         U1IR <sup>(2)</sup> 5210         U1IE           5220         U1EIR <sup>(2)</sup>                                                                                                                          | 2) 15<br>31:<br>15<br>(3) 31:<br>(3) 31:<br>15<br>15<br>31:<br>31:<br>31                    | 5:0<br>1:16<br>5:0<br>1:16<br>5:0<br>1:16                                                | —<br>—<br>—<br>— | -         | _         |       | _     |       |      |      |                        | 22/0               | 21/5                 | 20/4       | 19/3      | 18/2     | 17/1            | 16/0     | All Re |

| 5050         U10TGIE           5060         U10TGSTAT           5070         U10TGCO           5080         U1PWRC           5200         U1IR <sup>(2)</sup> 5210         U1IE           5220         U1EIR <sup>(2)</sup>                                                                                                                          | 15<br>31:<br>15<br>(3)<br>31:<br>15<br>31:<br>Ν<br>31:<br>31:                               | 1:16<br>5:0<br>1:16<br>5:0<br>1:16                                                       | -<br>-<br>-      |           |           |       |       | —     | -    | _    | _                      | —                  | —                    | —          | _         | —        | —               | —        | 0000   |

| 5060         U1OTGSTAT           5070         U1OTGCO           5080         U1PWRC           5200         U1IR <sup>(2)</sup> 5210         U1IE           5220         U1EIR <sup>(2)</sup>                                                                                                                                                         | 15<br>(3) 31:<br>15:<br>Ν 31:<br>15:<br>31:<br>31:<br>31:<br>31:<br>31:<br>31:<br>31:<br>31 | 5:0<br>1:16<br>5:0<br>1:16                                                               | -                | —         |           |       | -     |       |      | —    | IDIF                   | T1MSECIF           | LSTATEIF             | ACTVIF     | SESVDIF   | SESENDIF | _               | VBUSVDIF | 0000   |

| 5060         U1OTGSTAT           5070         U1OTGCO           5080         U1PWRC           5200         U1IR <sup>(2)</sup> 5210         U1IE           5220         U1EIR <sup>(2)</sup>                                                                                                                                                         | 15:<br>T <sup>(3)</sup> 31:<br>15:<br>N 31:<br>15:<br>31:<br>31:                            | 1:16<br>5:0<br>1:16                                                                      | -                | -         | —         |       | -     |       |      | —    | _                      | —                  | _                    | -          | _         | —        | _               | _        | 0000   |

| 5070         U1OTGCO           5080         U1PWRC           5200         U1IR <sup>(2)</sup> 5210         U1IE           5220         U1EIR <sup>(2)</sup>                                                                                                                                                                                          | N 15:<br>31:<br>31:<br>31:                                                                  | 5:0<br>1:16                                                                              |                  |           |           | _     | _     |       | _    | _    | IDIE                   | T1MSECIE           | LSTATEIE             | ACTVIE     | SESVDIE   | SESENDIE | _               | VBUSVDIE | 0000   |

| 5070         U1OTGCO           5080         U1PWRC           5200         U1IR <sup>(2)</sup> 5210         U1IE           5220         U1EIR <sup>(2)</sup>                                                                                                                                                                                          | N 31:<br>31:<br>31:<br>31:                                                                  | 1:16                                                                                     |                  | -         | _         |       | -     |       |      | —    | _                      | —                  | _                    | -          | —         | —        |                 | —        | 0000   |

| 5080         U1PWRC           5200         U1IR <sup>(2)</sup> 5210         U1IE           5220         U1EIR <sup>(2)</sup>                                                                                                                                                                                                                         | N 15                                                                                        |                                                                                          | _                | -         | _         |       | -     |       |      | —    | ID                     | —                  | LSTATE               | -          | SESVD     | SESEND   |                 | VBUSVD   | 0000   |

| 5080         U1PWRC           5200         U1IR <sup>(2)</sup> 5210         U1IE           5220         U1EIR <sup>(2)</sup>                                                                                                                                                                                                                         | 31                                                                                          | E:0                                                                                      | _                | _         | _         | _     | —     | _     | _    | _    |                        | _                  | —                    | —          | —         | —        | —               | —        | 0000   |

| 5200         U1IR <sup>(2)</sup> 5210         U1IE           5220         U1EIR <sup>(2)</sup>                                                                                                                                                                                                                                                       | 31:                                                                                         | 5.0                                                                                      | _                | _         | _         | _     | —     | _     |      |      | DPPULUP                | DMPULUP            | DPPULDWN             | DMPULDWN   | VBUSON    | OTGEN    | VBUSCHG         | VBUSDIS  | 0000   |

| 5200         U1IR <sup>(2)</sup> 5210         U1IE           5220         U1EIR <sup>(2)</sup>                                                                                                                                                                                                                                                       |                                                                                             | 1:16                                                                                     | _                | -         | _         |       | -     |       |      | —    | _                      | —                  | _                    | -          | —         | _        |                 | —        | 0000   |

| 5210 U1IE<br>5220 U1EIR <sup>(2)</sup>                                                                                                                                                                                                                                                                                                               | 15                                                                                          | 5:0                                                                                      | _                | _         | _         | _     | —     | _     | _    | _    | UACTPND <sup>(4)</sup> | _                  | —                    | USLPGRD    | USBBUSY   | —        | USUSPEND        | USBPWR   | 0000   |

| 5210 U1IE<br>5220 U1EIR <sup>(2)</sup>                                                                                                                                                                                                                                                                                                               | 31:                                                                                         | 1:16                                                                                     | _                | _         | _         | _     | —     | _     |      |      |                        | _                  | —                    | —          | —         | —        | —               | —        | 0000   |

| 5220 U1EIR <sup>(2)</sup>                                                                                                                                                                                                                                                                                                                            | 15                                                                                          | 5:0                                                                                      | _                | _         | _         |       | _     |       |      | _    | STALLIF                | ATTACHIF           | RESUMEIF             | IDLEIF     | TRNIF     | SOFIF    | UERRIF          | URSTIF   | 0000   |

| 5220 U1EIR <sup>(2)</sup>                                                                                                                                                                                                                                                                                                                            | _                                                                                           |                                                                                          |                  |           |           |       |       |       |      |      | -                      |                    |                      |            |           |          |                 | DETACHIF | 0000   |

| 5220 U1EIR <sup>(2)</sup>                                                                                                                                                                                                                                                                                                                            | 31:                                                                                         | 1:16                                                                                     | _                | _         | —         | —     | —     | —     | —    | _    | —                      | —                  | —                    | —          | —         | —        | —               |          | 0000   |

|                                                                                                                                                                                                                                                                                                                                                      | 15                                                                                          | 5:0                                                                                      | _                | _         | _         | _     | _     | _     | _    | _    | STALLIE                | ATTACHIE           | RESUMEIE             | IDLEIE     | TRNIE     | SOFIE    | UERRIE          | URSTIE   | 0000   |

|                                                                                                                                                                                                                                                                                                                                                      |                                                                                             |                                                                                          |                  |           |           |       |       |       |      |      |                        |                    |                      |            |           |          |                 |          | 0000   |

|                                                                                                                                                                                                                                                                                                                                                      | 31:                                                                                         | 1:16                                                                                     | _                | _         | _         | _     | _     | _     | _    | _    | —                      |                    | —                    | —          | _         | —        | _               | —        | 0000   |

| 5230 U1EIE                                                                                                                                                                                                                                                                                                                                           | 15                                                                                          | 5:0                                                                                      | _                | _         | _         | _     | _     | _     | _    | —    | BTSEF                  | BMXEF              | DMAEF                | BTOEF      | DFN8EF    | CRC16EF  | CRC5EF<br>EOFEF | PIDEF    | 0000   |

| 5230 U1EIE                                                                                                                                                                                                                                                                                                                                           | 31.                                                                                         | 1:16                                                                                     | _                | _         | _         | _     | _     | _     | _    |      | _                      | _                  | _                    | _          | _         | _        | _               | _        | 0000   |

| SZSG OTELE                                                                                                                                                                                                                                                                                                                                           | 51.                                                                                         | 1.10                                                                                     |                  |           |           |       |       |       |      |      |                        |                    |                      |            |           |          | CRC5EE          |          | 0000   |

|                                                                                                                                                                                                                                                                                                                                                      | 15                                                                                          | 5:0                                                                                      | —                | —         | —         | —     | —     | —     | —    | —    | BTSEE                  | BMXEE              | DMAEE                | BTOEE      | DFN8EE    | CRC16EE  | EOFEE           | PIDEE    | 0000   |

| (2)                                                                                                                                                                                                                                                                                                                                                  | 、 31:                                                                                       | 1:16                                                                                     | _                | _         | _         | _     | _     |       | _    | _    | _                      | _                  | _                    | _          | _         |          | _               | _        | 0000   |

| 5240 U1STAT <sup>(3)</sup>                                                                                                                                                                                                                                                                                                                           | ,                                                                                           | 5:0                                                                                      | _                | _         | _         | _     | _     | _     | _    | _    |                        | ENDPT              | <3:0> <sup>(4)</sup> |            | DIR       | PPBI     | _               | _        | 0000   |

|                                                                                                                                                                                                                                                                                                                                                      | -                                                                                           | 1:16                                                                                     | _                | _         | _         | _     | _     | _     | _    | _    | _                      | _                  | _                    | _          | _         | _        | _               | _        | 0000   |

| 5250 U1CON                                                                                                                                                                                                                                                                                                                                           |                                                                                             |                                                                                          |                  |           |           |       |       |       |      |      | 10TATE(4)              | 0.5 0(4)           | PKTDIS               |            |           |          |                 | USBEN    | 0000   |

|                                                                                                                                                                                                                                                                                                                                                      |                                                                                             | 5:0                                                                                      | —                | _         | _         | —     | —     | —     | —    |      | JSTATE <sup>(4)</sup>  | SE0 <sup>(4)</sup> | TOKBUSY              | USBRST     | HOSTEN    | RESUME   | PPBRST          | SOFEN    | 0000   |

| 5260 U1ADDR                                                                                                                                                                                                                                                                                                                                          | 15                                                                                          | 1:16                                                                                     | _                | _         | _         | _     | _     | _     | _    | _    |                        | —                  | _                    | _          | —         | —        | _               | —        | 0000   |

| 5200 UTADDR                                                                                                                                                                                                                                                                                                                                          | 31:                                                                                         | 5:0                                                                                      | _                | _         | —         | _     | —     | _     | _    | _    | LSPDEN                 |                    |                      | DE         | VADDR<6:0 | 1>       |                 |          | 0000   |

| 5270 U1BDTP1                                                                                                                                                                                                                                                                                                                                         | 31:                                                                                         |                                                                                          | _                | _         | —         | _     | —     | _     | _    | _    | _                      | _                  | —                    | _          | _         | —        | _               | —        | 0000   |

| JZIU UIBDIPI                                                                                                                                                                                                                                                                                                                                         | 31:<br>15:                                                                                  | 1:16                                                                                     |                  | _         | _         | _     | _     | _     |      | _    |                        |                    | BD                   | TPTRL<7:1> |           |          |                 |          | 0000   |

x = unknown value on Reset; — = unimplemented, read as '0'. Reset values are shown in hexadecimal. Legend:

All registers in this table (except as noted) have corresponding CLR, SET and INV registers at its virtual address, plus an offset of 0x4, 0x8 and 0xC respectively. See Section 12.1.1 "CLR, SET and INV Registers" for Note 1: more information.

2:

This register does not have associated SET and INV registers. This register does not have associated CLR, SET and INV registers. 3:

4: Reset value for this bit is undefined.

|              | -                 |                   |                   |                   |                   |                   |                  |                  |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

| 31:24        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 31.24        | -                 | —                 | _                 | -                 | _                 | _                 | -                | —                |

| 23:16        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 23.10        | -                 | —                 | _                 | -                 | _                 | _                 | -                | —                |

| 15:8         | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 15.6         |                   | _                 |                   |                   |                   |                   |                  | —                |

| 7:0          | R-0               | U-0               | R-0               | U-0               | R-0               | R-0               | U-0              | R-0              |

| 7.0          | ID                | —                 | LSTATE            |                   | SESVD             | SESEND            |                  | VBUSVD           |

### REGISTER 11-3: U10TGSTAT: USB OTG STATUS REGISTER

# Legend:

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, r | ead as '0'         |  |

|-------------------|------------------|--------------------------|--------------------|--|

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared     | x = Bit is unknown |  |

#### bit 31-8 Unimplemented: Read as '0'

- bit 7 ID: ID Pin State Indicator bit

- 1 = No cable is attached or a "type B" cable has been inserted into the USB receptacle

- 0 = A "type A" OTG cable has been inserted into the USB receptacle

- bit 6 Unimplemented: Read as '0'

- bit 5 LSTATE: Line State Stable Indicator bit

- 1 = USB line state (SE0 (U1CON<6> and JSTATE (U1CON<7>) has been stable for the previous 1 ms

- 0 = USB line state (SE0 (U1CON<6> and JSTATE (U1CON<7>) has not been stable for the previous 1 ms

#### bit 4 Unimplemented: Read as '0'

- bit 3 SESVD: Session Valid Indicator bit

- 1 = VBUS voltage is above Session Valid on the A or B device

- 0 = VBUS voltage is below Session Valid on the A or B device

- bit 2 SESEND: B-Device Session End Indicator bit

- 1 = VBUS voltage is below Session Valid on the B device

- 0 = VBUS voltage is above Session Valid on the B device

#### bit 1 Unimplemented: Read as '0'

- bit 0 VBUSVD: A-Device VBUS Valid Indicator bit

- 1 = VBUS voltage is above Session Valid on the A device

- 0 = VBUS voltage is below Session Valid on the A device

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|

| 31:24        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 31.24        |                   |                   |                   | _                 |                   |                   | _                | _                |