Welcome to **E-XFL.COM**

What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded - Microcontrollers</u>"

| Details                    |                                                                                |

|----------------------------|--------------------------------------------------------------------------------|

| Product Status             | Active                                                                         |

| Core Processor             | MIPS32® M4K™                                                                   |

| Core Size                  | 32-Bit Single-Core                                                             |

| Speed                      | 80MHz                                                                          |

| Connectivity               | Ethernet, I <sup>2</sup> C, SPI, UART/USART, USB OTG                           |

| Peripherals                | Brown-out Detect/Reset, DMA, POR, PWM, WDT                                     |

| Number of I/O              | 83                                                                             |

| Program Memory Size        | 64KB (64K x 8)                                                                 |

| Program Memory Type        | FLASH                                                                          |

| EEPROM Size                | -                                                                              |

| RAM Size                   | 32K x 8                                                                        |

| Voltage - Supply (Vcc/Vdd) | 2.3V ~ 3.6V                                                                    |

| Data Converters            | A/D 16x10b                                                                     |

| Oscillator Type            | Internal                                                                       |

| Operating Temperature      | -40°C ~ 105°C (TA)                                                             |

| Mounting Type              | Surface Mount                                                                  |

| Package / Case             | 100-TQFP                                                                       |

| Supplier Device Package    | 100-TQFP (14x14)                                                               |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic32mx664f064l-v-pf |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

#### TABLE 6: PIN NAMES FOR 64-PIN USB, ETHERNET, AND CAN DEVICES

64-PIN QFN<sup>(3)</sup> AND TQFP (TOP VIEW)

PIC32MX764F128H PIC32MX775F256H PIC32MX775F512H PIC32MX795F512H

64 1

QFN<sup>(3)</sup> 64 TQFP

| Pin# | Full Pin Name                                             |

|------|-----------------------------------------------------------|

| 1    | ETXEN/PMD5/RE5                                            |

| 2    | ETXD0/PMD6/RE6                                            |

| 3    | ETXD1/PMD7/RE7                                            |

| 4    | SCK2/U6TX/U3RTS/PMA5/CN8/RG6                              |

| 5    | SDA4/SDI2/U3RX/PMA4/CN9/RG7                               |

| 6    | SCL4/SDO2/U3TX/PMA3/CN10/RG8                              |

| 7    | MCLR                                                      |

| 8    | SS2/U6RX/U3CTS/PMA2/CN11/RG9                              |

| 9    | Vss                                                       |

| 10   | VDD                                                       |

| 11   | AN5/C1IN+/VBUSON/CN7/RB5                                  |

| 12   | AN4/C1IN-/CN6/RB4                                         |

| 13   | AN3/C2IN+/CN5/RB3                                         |

| 14   | AN2/C2IN-/CN4/RB2                                         |

| 15   | PGEC1/AN1/VREF-/CVREF-/CN3/RB1                            |

| 16   | PGED1/AN0/VREF+/CVREF+/PMA6/CN2/RB0                       |

| 17   | PGEC2/AN6/OCFA/RB6                                        |

| 18   | PGED2/AN7/RB7                                             |

| 19   | AVDD                                                      |

| 20   | AVss                                                      |

| 21   | AN8/C2TX <sup>(2)</sup> /SS4/U5RX/U2CTS/C1OUT/RB8         |

| 22   | AN9/C2OUT/PMA7/RB9                                        |

| 23   | TMS/AN10/CVrefout/PMA13/RB10                              |

| 24   | TDO/AN11/PMA12/RB11                                       |

| 25   | Vss                                                       |

| 26   | VDD                                                       |

| 27   | TCK/AN12/PMA11/RB12                                       |

| 28   | TDI/AN13/PMA10/RB13                                       |

| 29   | AN14/C2RX <sup>(2)</sup> /SCK4/U5TX/U2RTS/PMALH/PMA1/RB14 |

| 30   | AN15/EMDC/AEMDC/OCFB/PMALL/PMA0/CN12/RB15                 |

| 31   | AC1TX/SDA5/SDI4/U2RX/PMA9/CN17/RF4                        |

| 32   | AC1RX/SCL5/SDO4/U2TX/PMA8/CN18/RF5                        |

| Note | 1: Shaded pins are 5V tolerant.                           |

| Pin # | Full Pin Name                                 |

|-------|-----------------------------------------------|

| 33    | USBID/RF3                                     |

| 34    | VBUS                                          |

| 35    | Vusb3v3                                       |

| 36    | D-/RG3                                        |

| 37    | D+/RG2                                        |

| 38    | VDD                                           |

| 39    | OSC1/CLKI/RC12                                |

| 40    | OSC2/CLKO/RC15                                |

| 41    | Vss                                           |

| 42    | RTCC/AERXD1/ETXD3/IC1/INT1/RD8                |

| 43    | AERXD0/ETXD2/SS3/U4RX/U1CTS/SDA1/IC2/INT2/RD9 |

| 44    | ECOL/AECRSDV/SCL1/IC3/PMCS2/PMA15/INT3/RD10   |

| 45    | ECRS/AEREFCLK/IC4/PMCS1/PMA14/INT4/RD11       |

| 46    | OC1/INT0/RD0                                  |

| 47    | SOSCI/CN1/RC13                                |

| 48    | SOSCO/T1CK/CN0/RC14                           |

| 49    | EMDIO/AEMDIO/SCK3/U4TX/U1RTS/OC2/RD1          |

| 50    | SDA3/SDI3/U1RX/OC3/RD2                        |

| 51    | SCL3/SDO3/U1TX/OC4/RD3                        |

| 52    | OC5/IC5/PMWR/CN13/RD4                         |

| 53    | PMRD/CN14/RD5                                 |

| 54    | AETXEN/ETXERR/CN15/RD6                        |

| 55    | ETXCLK/AERXERR/CN16/RD7                       |

| 56    | VCAP                                          |

| 57    | VDD                                           |

| 58    | C1RX/AETXD1/ERXD3/RF0                         |

| 59    | C1TX/AETXD0/ERXD2/RF1                         |

| 60    | ERXD1/PMD0/RE0                                |

| 61    | ERXD0/PMD1/RE1                                |

| 62    | ERXDV/ECRSDV/PMD2/RE2                         |

| 63    | ERXCLK/EREFCLKPMD3/RE3                        |

| 64    | ERXERR/PMD4/RE4                               |

- Note 1: Shaded pins are 5V tolerant

- 2: This pin is not available on PIC32MX765F128H devices.

- 3: The metal plane at the bottom of the QFN device is not connected to any pins and is recommended to be connected to Vss externally.

## PIC32MX5XX/6XX/7XX

#### **Table of Contents**

| 1.0     | Device Overview                                    | 25  |

|---------|----------------------------------------------------|-----|

| 2.0     | Guidelines for Getting Started with 32-bit MCUs    | 37  |

| 3.0     | CPU                                                | 41  |

| 4.0     | Memory Organization                                | 47  |

| 5.0     | Flash Program Memory                               | 63  |

| 6.0     | Resets                                             |     |

| 7.0     | Interrupt Controller                               | 73  |

| 8.0     | Oscillator Configuration                           | 95  |

| 9.0     | Prefetch Cache                                     | 101 |

| 10.0    | Direct Memory Access (DMA) Controller              | 111 |

| 11.0    | USB On-The-Go (OTG)                                | 133 |

| 12.0    | VO Ports                                           | 157 |

| 13.0    | Timer1                                             | 167 |

| 14.0    | Timer2/3, Timer4/5                                 | 171 |

| 15.0    | Watchdog Timer (WDT)                               | 177 |

| 16.0    | Input Capture                                      | 181 |

| 17.0    | Output Compare                                     | 185 |

| 18.0    | Serial Peripheral Interface (SPI)                  | 189 |

| 19.0    | Inter-Integrated Circuit (I <sup>2</sup> C)        | 195 |

| 20.0    | Universal Asynchronous Receiver Transmitter (UART) | 203 |

| 21.0    | Parallel Master Port (PMP)                         | 211 |

| 22.0    | Real-Time Clock and Calendar (RTCC)                | 221 |

| 23.0    | 10-bit Analog-to-Digital Converter (ADC)           | 231 |

| 24.0    | Controller Area Network (CAN)                      | 241 |

| 25.0    | Ethernet Controller                                | 279 |

| 26.0    | Comparator                                         | 323 |

| 27.0    | Comparator Voltage Reference (CVREF)               | 327 |

| 28.0    | Power-Saving Features                              | 331 |

| 29.0    | Special Features                                   | 333 |

| 30.0    | Instruction Set                                    | 345 |

| 31.0    | Development Support                                | 347 |

| 32.0    | Electrical Characteristics                         | 351 |

|         | DC and AC Device Characteristics Graphs            |     |

| 34.0    | Packaging Information                              | 401 |

| The N   | Microchip Web Site                                 | 437 |

| Custo   | omer Change Notification Service                   | 437 |

| Custo   | omer Support                                       | 437 |

| חיים או | ust Identification System                          | 120 |

#### 1.0 DEVICE OVERVIEW

Note:

This data sheet summarizes the features of the PIC32MX5XX/6XX/7XX family of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to the documents listed in the *Documentation* > *Reference Manual* section of the Microchip PIC32 web site (www.microchip.com/pic32).

This document contains device-specific information for PIC32MX5XX/6XX/7XX devices.

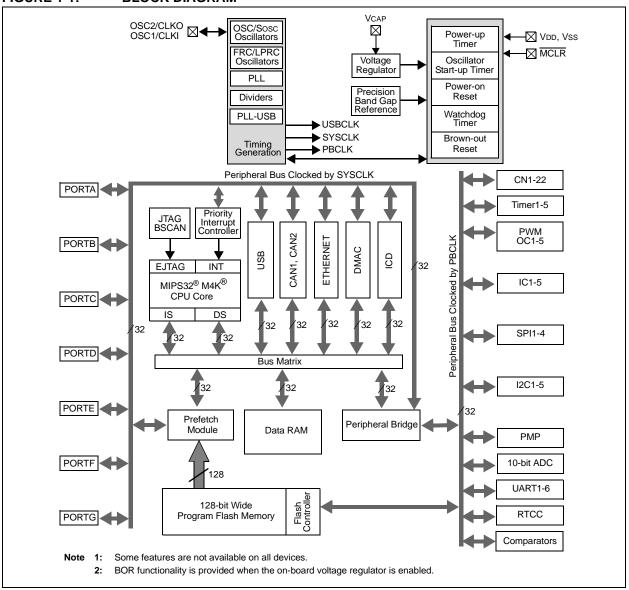

Figure 1-1 illustrates a general block diagram of the core and peripheral modules in the PIC32MX5XX/6XX/7XX family of devices.

Table 1-1 lists the functions of the various pins shown in the pinout diagrams.

FIGURE 1-1: BLOCK DIAGRAM<sup>(1,2)</sup>

## 2.0 GUIDELINES FOR GETTING STARTED WITH 32-BIT MCUS

Note:

This data sheet summarizes the features of the PIC32MX5XX/6XX/7XX family of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to the related section of the "PIC32 Family Reference Manual", which is available from the Microchip web site (www.microchip.com/PIC32).

#### 2.1 Basic Connection Requirements

Getting started with the PIC32MX5XX/6XX/7XX family of 32-bit Microcontrollers (MCUs) requires attention to a minimal set of device pin connections before proceeding with development. The following is a list of pin names, which must always be connected:

- All VDD and Vss pins (see 2.2 "Decoupling Capacitors")

- All AVDD and AVSS pins even if the ADC module is not used (see 2.2 "Decoupling Capacitors")

- VCAP pin (see 2.3 "Capacitor on Internal Voltage Regulator (VCAP)")

- MCLR pin (see 2.4 "Master Clear (MCLR) Pin")

- PGECx/PGEDx pins used for In-Circuit Serial Programming™ (ICSP™) and debugging purposes (see 2.5 "ICSP Pins")

- OSC1 and OSC2 pins when external oscillator source is used (see 2.8 "External Oscillator Pins")

The following pin may be required, as well: VREF+/ VREF- pins used when external voltage reference for ADC module is implemented.

Note:

The AVDD and AVSS pins must be connected, regardless of the ADC use and the ADC voltage reference source.

#### 2.2 Decoupling Capacitors

The use of decoupling capacitors on power supply pins, such as VDD, VSS, AVDD and AVSS is required. See Figure 2-1.

Consider the following criteria when using decoupling capacitors:

- Value and type of capacitor: A value of 0.1 µF (100 nF), 10-20V is recommended. The capacitor should be a low Equivalent Series Resistance (low-ESR) capacitor and have resonance frequency in the range of 20 MHz and higher. It is further recommended to use ceramic capacitors.

- Placement on the printed circuit board: The

decoupling capacitors should be placed as close

to the pins as possible. It is recommended that

the capacitors be placed on the same side of

the board as the device. If space is constricted,

the capacitor can be placed on another layer on

the PCB using a via; however, ensure that the

trace length from the pin to the capacitor is

within one-quarter inch (6 mm) in length.

- Handling high frequency noise: If the board is experiencing high frequency noise, upward of tens of MHz, add a second ceramic-type capacitor in parallel to the above described decoupling capacitor. The value of the second capacitor can be in the range of 0.01 μF to 0.001 μF. Place this second capacitor next to the primary decoupling capacitor. In high-speed circuit designs, consider implementing a decade pair of capacitances as close to the power and ground pins as possible. For example, 0.1 μF in parallel with 0.001 μF.

- Maximizing performance: On the board layout from the power supply circuit, run the power and return traces to the decoupling capacitors first, and then to the device pins. This ensures that the decoupling capacitors are first in the power chain. Equally important is to keep the trace length between the capacitor and the power pins to a minimum, thereby reducing PCB track inductance.

REGISTER 7-4: IFSx: INTERRUPT FLAG STATUS REGISTER

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|

| 24.24        | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |

| 31:24        | IFS31             | IFS30             | IFS29             | IFS28             | IFS27             | IFS26             | IFS25            | IFS24            |

| 23:16        | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |

| 23.10        | IFS23             | IFS22             | IFS21             | IFS20             | IFS19             | IFS18             | IFS17            | IFS16            |

| 15:8         | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |

| 13.6         | IFS15             | IFS14             | IFS13             | IFS12             | IFS11             | IFS10             | IFS09            | IFS08            |

| 7.0          | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |

| 7:0          | IFS07             | IFS06             | IFS05             | IFS04             | IFS03             | IFS02             | IFS01            | IFS00            |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

bit 31-0 IFS31-IFS00: Interrupt Flag Status bits

1 = Interrupt request has occurred0 = Interrupt request has not occurred

Note: This register represents a generic definition of the IFSx register. Refer to Table 7-1 for the exact bit

definitions.

#### REGISTER 7-5: IECx: INTERRUPT ENABLE CONTROL REGISTER

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|

| 24.24        | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |

| 31:24        | IEC31             | IEC30             | IEC29             | IEC28             | IEC27             | IEC26             | IEC25            | IEC24            |

| 23:16        | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |

| 23.10        | IEC23             | IEC22             | IEC21             | IEC20             | IEC19             | IEC18             | IEC17            | IEC16            |

| 15.0         | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |

| 15:8         | IEC15             | IEC14             | IEC13             | IEC12             | IEC11             | IEC10             | IEC09            | IEC08            |

| 7.0          | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |

| 7:0          | IEC07             | IEC06             | IEC05             | IEC04             | IEC03             | IEC02             | IEC01            | IEC00            |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

bit 31-0 **IEC31-IEC00**: Interrupt Enable bits

1 = Interrupt is enabled0 = Interrupt is disabled

Note: This register represents a generic definition of the IECx register. Refer to Table 7-1 for the exact bit

definitions.

#### REGISTER 10-8: DCHxECON: DMA CHANNEL 'x' EVENT CONTROL REGISTER

| Bit<br>Range | Bit<br>31/23/15/7          | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |  |

|--------------|----------------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|--|--|

| 31:24        | U-0                        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |  |  |

| 31.24        |                            |                   | _                 | _                 | _                 |                   | _                | _                |  |  |

| 22,46        | R/W-1                      | R/W-1             | R/W-1             | R/W-1             | R/W-1             | R/W-1             | R/W-1            | R/W-1            |  |  |

| 23:16        | CHAIRQ<7:0> <sup>(1)</sup> |                   |                   |                   |                   |                   |                  |                  |  |  |

| 45.0         | R/W-1                      | R/W-1             | R/W-1             | R/W-1             | R/W-1             | R/W-1             | R/W-1            | R/W-1            |  |  |

| 15:8         | CHSIRQ<7:0> <sup>(1)</sup> |                   |                   |                   |                   |                   |                  |                  |  |  |

| 7.0          | S-0                        | S-0               | R/W-0             | R/W-0             | R/W-0             | U-0               | U-0              | U-0              |  |  |

| 7:0          | CFORCE                     | CABORT            | PATEN             | SIRQEN            | AIRQEN            | _                 | _                | _                |  |  |

Legend:S = Settable bitR = Readable bitW = Writable bitU = Unimplemented bit, read as '0'-n = Value at POR'1' = Bit is set'0' = Bit is clearedx = Bit is unknown

bit 31-24 Unimplemented: Read as '0'

bit 23-16 CHAIRQ<7:0>: Channel Transfer Abort IRQ bits<sup>(1)</sup>

11111111 = Interrupt 255 will abort any transfers in progress and set CHAIF flag

•

•

•

00000001 = Interrupt 1 will abort any transfers in progress and set CHAIF flag 00000000 = Interrupt 0 will abort any transfers in progress and set CHAIF flag

bit 15-8 CHSIRQ<7:0>: Channel Transfer Start IRQ bits(1)

11111111 = Interrupt 255 will initiate a DMA transfer

•

•

00000001 = Interrupt 1 will initiate a DMA transfer 00000000 = Interrupt 0 will initiate a DMA transfer

bit 7 CFORCE: DMA Forced Transfer bit

1 = A DMA transfer is forced to begin when this bit is written to a '1'

0 = This bit always reads '0'

bit 6 CABORT: DMA Abort Transfer bit

1 = A DMA transfer is aborted when this bit is written to a '1'

0 = This bit always reads '0'

bit 5 PATEN: Channel Pattern Match Abort Enable bit

1 = Abort transfer and clear CHEN on pattern match

0 = Pattern match is disabled

bit 4 SIRQEN: Channel Start IRQ Enable bit

1 = Start channel cell transfer if an interrupt matching CHSIRQ occurs

0 = Interrupt number CHSIRQ is ignored and does not start a transfer

bit 3 AIRQEN: Channel Abort IRQ Enable bit

1 = Channel transfer is aborted if an interrupt matching CHAIRQ occurs

0 = Interrupt number CHAIRQ is ignored and does not terminate a transfer

bit 2-0 Unimplemented: Read as '0'

Note 1: See Table 7-1: "Interrupt IRQ, Vector and Bit Location" for the list of available interrupt IRQ sources.

#### REGISTER 10-16: DCHxCSIZ: DMA CHANNEL 'x' CELL-SIZE REGISTER

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3   | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |  |

|--------------|-------------------|-------------------|-------------------|-------------------|---------------------|-------------------|------------------|------------------|--|--|

| 31:24        | U-0               | U-0               | U-0               | U-0               | U-0                 | U-0               | U-0              | U-0              |  |  |

| 31.24        | _                 | _                 | _                 | _                 | _                   |                   |                  |                  |  |  |

| 23:16        | U-0               | U-0               | U-0               | U-0               | U-0                 | U-0               | U-0              | U-0              |  |  |

| 23.10        | _                 | _                 | _                 | _                 | _                   | _                 | _                | _                |  |  |

| 15:8         | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0               | R/W-0             | R/W-0            | R/W-0            |  |  |

| 15.6         | CHCSIZ<15:8>      |                   |                   |                   |                     |                   |                  |                  |  |  |

| 7:0          | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0               | R/W-0             | R/W-0            | R/W-0            |  |  |

| 7:0          |                   |                   | •                 | CHCSIZ            | <b>'&lt;7:0&gt;</b> |                   | •                |                  |  |  |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

bit 31-16 Unimplemented: Read as '0'

bit 15-0 CHCSIZ<15:0>: Channel Cell-Size bits

111111111111111 = 65,535 bytes transferred on an event

•

•

#### REGISTER 10-17: DCHxCPTR: DMA CHANNEL 'x' CELL POINTER REGISTER

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |  |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|--|--|

| 24.24        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |  |  |

| 31:24        |                   | _                 |                   | _                 |                   |                   | _                | _                |  |  |

| 22.40        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |  |  |

| 23:16        | _                 | _                 | _                 | _                 |                   | _                 | _                | _                |  |  |

| 45.0         | R-0               | R-0               | R-0               | R-0               | R-0               | R-0               | R-0              | R-0              |  |  |

| 15:8         | CHCPTR<15:8>      |                   |                   |                   |                   |                   |                  |                  |  |  |

| 7.0          | R-0               | R-0               | R-0               | R-0               | R-0               | R-0               | R-0              | R-0              |  |  |

| 7:0          |                   |                   |                   | CHCPTF            | R<7:0>            |                   |                  |                  |  |  |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

bit 31-16 Unimplemented: Read as '0'

oit 15-0 CHCPTR<7:0>: Channel Cell Progress Pointer bits

111111111111111 = 65,535 bytes have been transferred since the last event

•

**Note:** When in Pattern Detect mode, this register is reset on a pattern detect.

#### REGISTER 11-10: U1STAT: USB STATUS REGISTER

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|

| 31:24        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 31.24        | -                 | _                 | -                 | _                 | _                 | -                 | -                | 1                |

| 23:16        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 23.10        | -                 | _                 | -                 | _                 | _                 | -                 | -                | 1                |

| 15.0         | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 15:8         | _                 | _                 | _                 | _                 | _                 | _                 | _                | -                |

| 7:0          | R-x               | R-x               | R-x               | R-x               | R-x               | R-x               | U-0              | U-0              |

| 7.0          |                   | ENDP              | T<3:0>            |                   | DIR               | PPBI              | _                |                  |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

bit 31-8 Unimplemented: Read as '0'

bit 7-4 ENDPT<3:0>: Encoded Number of Last Endpoint Activity bits

(Represents the number of the BDT, updated by the last USB transfer.)

1111 = Endpoint 15

1110 = Endpoint 14

•

•

0001 = Endpoint 1

0000 = Endpoint 0

bit 3 DIR: Last Buffer Descriptor Direction Indicator bit

1 = Last transaction was a transmit transfer (TX)

0 = Last transaction was a receive transfer (RX)

bit 2 PPBI: Ping-Pong Buffer Descriptor Pointer Indicator bit

1 = The last transaction was to the Odd buffer descriptor bank

0 = The last transaction was to the Even buffer descriptor bank

bit 1-0 Unimplemented: Read as '0'

Note: The U1STAT register is a window into a 4-byte FIFO maintained by the USB module. U1STAT value is only valid when U1IR<TRNIF> is active. Clearing the U1IR<TRNIF> bit advances the FIFO. Data in register is invalid when U1IR<TRNIF> = 0.

### PIC32MX5XX/6XX/7XX

#### REGISTER 11-11: U1CON: USB CONTROL REGISTER (CONTINUED)

- bit 1 PPBRST: Ping-Pong Buffers Reset bit

- 1 = Reset all Even/Odd buffer pointers to the Even buffer descriptor banks

- 0 = Even/Odd buffer pointers are not reset

- bit 0 USBEN: USB Module Enable bit(4)

- 1 = USB module and supporting circuitry is enabled

- 0 = USB module and supporting circuitry is disabled

SOFEN: SOF Enable bit (5)

- 1 = SOF token is sent every 1 ms

- 0 = SOF token is disabled

- **Note 1:** Software is required to check this bit before issuing another token command to the U1TOK register (see Register 11-15).

- 2: All host control logic is reset any time that the value of this bit is toggled.

- 3: Software must set RESUME for 10 ms in Device mode, or for 25 ms in Host mode, and then clear it to enable remote wake-up. In Host mode, the USB module will append a low-speed EOP to the RESUME signaling when this bit is cleared.

- 4: Device mode.

- 5: Host mode.

#### 12.0 **I/O PORTS**

Note:

This data sheet summarizes the features of the PIC32MX5XX/6XX/7XX family of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to **Section 12.** "I/O Ports" (DS60001120) in the "PIC32 Family Reference Manual", which is available from the Microchip web site (www.microchip.com/PIC32).

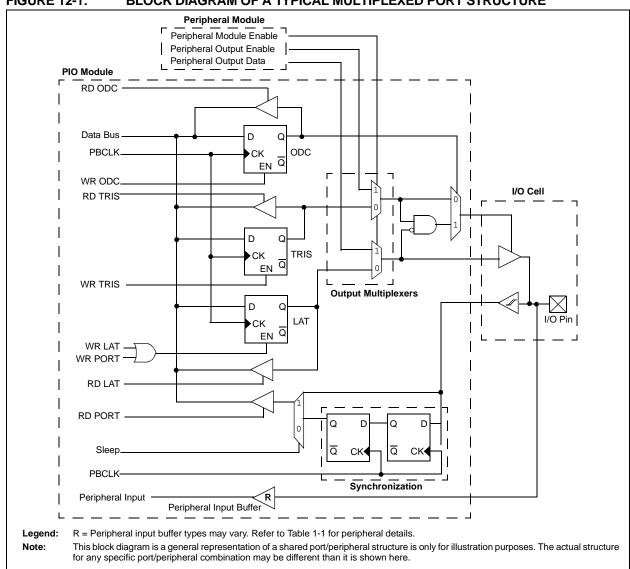

General purpose I/O pins are the simplest of peripherals. They allow the PIC32 MCU to monitor and control other devices. To add flexibility and functionality, some pins are multiplexed with alternate function(s). These functions depend on which peripheral features are on the device. In general, when a peripheral is functioning, that pin may not be used as a general purpose I/O pin.

Following are some of the key features of this module:

- Individual output pin open-drain enable/disable

- Individual input pin weak pull-up enable/disable

- Monitor selective inputs and generate interrupt when change in pin state is detected

- · Operation during Sleep and Idle modes

- Fast bit manipulation using CLR, SET and INV registers

Figure 12-1 illustrates a block diagram of a typical multiplexed I/O port.

FIGURE 12-1: BLOCK DIAGRAM OF A TYPICAL MULTIPLEXED PORT STRUCTURE

#### 15.0 WATCHDOG TIMER (WDT)

Note:

This data sheet summarizes the features of the PIC32MX5XX/6XX/7XX family of devices. However, it is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to Section 8. "Watchdog Timer and Power-up Timer" in the "PIC32 (DS60001114) Family Reference Manual", which is available from the Microchip web site (www.microchip.com/PIC32).

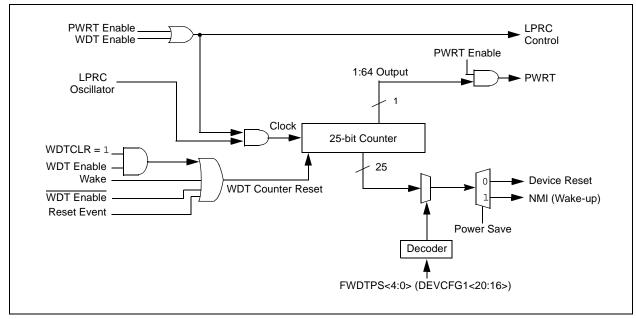

This section describes the operation of the WDT and Power-up Timer of the PIC32MX5XX/6XX/7XX.

The WDT, when enabled, operates from the internal Low-Power Oscillator (LPRC) clock source and can be used to detect system software malfunctions by resetting the device if the WDT is not cleared periodically in software. Various WDT time-out periods can be selected using the WDT postscaler. The WDT can also be used to wake the device from Sleep or Idle mode.

The following are key features of the WDT module:

- · Configuration or software controlled

- · User-configurable time-out period

- · Can wake the device from Sleep or Idle mode

FIGURE 15-1: WATCHDOG TIMER AND POWER-UP TIMER BLOCK DIAGRAM

REGISTER 21-1: PMCON: PARALLEL PORT CONTROL REGISTER

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6   | Bit<br>29/21/13/5  | Bit<br>28/20/12/4 | Bit<br>27/19/11/3   | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

|--------------|-------------------|---------------------|--------------------|-------------------|---------------------|-------------------|------------------|------------------|

| 31:24        | U-0               | U-0                 | U-0                | U-0               | U-0                 | U-0               | U-0              | U-0              |

|              | _                 | _                   | _                  | -                 | _                   | -                 | _                | _                |

| 00.40        | U-0               | U-0                 | U-0                | U-0               | U-0                 | U-0               | U-0              | U-0              |

| 23:16        | _                 | _                   | -                  | -                 | _                   | -                 | _                | _                |

| 45.0         | R/W-0             | U-0                 | R/W-0              | R/W-0             | R/W-0               | R/W-0             | R/W-0            | R/W-0            |

| 15:8         | ON <sup>(1)</sup> | _                   | SIDL               | ADRMU             | ADRMUX<1:0>         |                   | PTWREN           | PTRDEN           |

| 7.0          | R/W-0             | R/W-0               | R/W-0              | U-0               | R/W-0               | U-0               | R/W-0            | R/W-0            |

| 7:0          | CSF<              | 1:0> <sup>(2)</sup> | ALP <sup>(2)</sup> | 1                 | CS1P <sup>(2)</sup> | 1                 | WRSP             | RDSP             |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

bit 31-16 Unimplemented: Read as '0'

bit 15 **ON:** Parallel Master Port Enable bit<sup>(1)</sup>

1 = PMP is enabled

0 = PMP is disabled, no off-chip access performed

bit 14 **Unimplemented:** Read as '0' bit 13 **SIDL:** Stop in Idle Mode bit

1 = Discontinue module operation when device enters Idle mode

0 = Continue module operation when device enters Idle mode

bit 12-11 ADRMUX<1:0>: Address/Data Multiplexing Selection bits

11 = All 16 bits of address are multiplexed on PMD<15:0> pins

10 = All 16 bits of address are multiplexed on PMD<7:0> pins

01 = Lower 8 bits of address are multiplexed on PMD<7:0> pins, upper bits are on PMA<15:8>

00 = Address and data appear on separate pins

bit 10 PMPTTL: PMP Module TTL Input Buffer Select bit

1 = PMP module uses TTL input buffers

0 = PMP module uses Schmitt Trigger input buffer

bit 9 PTWREN: Write Enable Strobe Port Enable bit

1 = PMWR/PMENB port is enabled

0 = PMWR/PMENB port is disabled

bit 8 PTRDEN: Read/Write Strobe Port Enable bit

1 = PMRD/PMWR port is enabled

0 = PMRD/PMWR port is disabled

bit 7-6 CSF<1:0>: Chip Select Function bits(2)

11 = Reserved

10 = PMCS2 and PMCS1 function as Chip Select

01 = PMCS2 functions as Chip Select, PMCS1 functions as address bit 14

00 = PMCS2 and PMCS1 function as address bits 15 and 14(2)

bit 5 **ALP:** Address Latch Polarity bit<sup>(2)</sup>

1 = Active-high (PMALL and PMALH)

$0 = Active-low (\overline{PMALL} \text{ and } \overline{PMALH})$

bit 4 Unimplemented: Read as '0'

**Note 1:** When using the 1:1 PBCLK divisor, the user's software should not read/write the peripheral's SFRs in the SYSCLK cycle immediately following the instruction that clears the module's ON control bit.

2: These bits have no effect when their corresponding pins are used as address lines.

REGISTER 21-3: PMADDR: PARALLEL PORT ADDRESS REGISTER

| Bit<br>Range | Bit<br>31/23/15/7     | Bit<br>30/22/14/6     | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |  |

|--------------|-----------------------|-----------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|--|--|

| 24.04        | U-0                   | U-0                   | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |  |  |

| 31:24        | _                     | _                     | _                 | _                 | _                 | _                 | _                | _                |  |  |

| 23:16        | U-0                   | U-0                   | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |  |  |

| 23:16        | _                     | _                     | _                 | _                 | _                 | _                 | _                | _                |  |  |

|              | R/W-0                 | R/W-0                 | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |

| 15:8         | CS2 <sup>(1)</sup>    | CS1 <sup>(3)</sup>    |                   | ADDR<13:8>        |                   |                   |                  |                  |  |  |

|              | ADDR15 <sup>(2)</sup> | ADDR14 <sup>(4)</sup> |                   |                   |                   |                   |                  |                  |  |  |

| 7:0          | R/W-0                 | R/W-0                 | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |

|              |                       |                       |                   | ADDR-             | <7:0>             |                   |                  |                  |  |  |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

bit 31-16 Unimplemented: Read as '0'

bit 15 CS2: Chip Select 2 bit<sup>(1)</sup>

1 = Chip Select 2 is active0 = Chip Select 2 is inactive

bit 15 ADDR<15>: Destination Address bit 15<sup>(2)</sup>

bit 14 CS1: Chip Select 1 bit (3)

1 = Chip Select 1 is active

0 = Chip Select 1 is inactive

bit 14 ADDR<14>: Destination Address bit 14<sup>(4)</sup>

bit 13-0 ADDR<13:0>: Address bits

Note 1: When the CSF<1:0> bits (PMCON<7:6>) = 10 or 01.

**2:** When the CSF<1:0> bits (PMCON<7:6>) = 00.

3: When the CSF<1:0> bits (PMCON<7:6>) = 10.

**4:** When the CSF<1:0> bits (PMCON<7:6>) = 00 or 01.

#### REGISTER 21-5: PMSTAT: PARALLEL PORT STATUS REGISTER (ONLY SLAVE MODES)

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|

| 04:04        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 31:24        | _                 | _                 |                   | _                 | -                 | _                 | _                | _                |

| 22,46        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 23:16        | _                 | _                 | -                 | _                 | _                 | _                 | -                | _                |

| 45.0         | R-0               | R/W-0, HS, SC     | U-0               | U-0               | R-0               | R-0               | R-0              | R-0              |

| 15:8         | IBF               | IBOV              | -                 | _                 | IB3F              | IB2F              | IB1F             | IB0F             |

| 7.0          | R-1               | R/W-0, HS, SC     | U-0               | U-0               | R-1               | R-1               | R-1              | R-1              |

| 7:0          | OBE               | OBUF              | _                 | _                 | OB3E              | OB2E              | OB1E             | OB0E             |

Legend:HS = Set by HardwareSC = Cleared by softwareR = Readable bitW = Writable bitU = Unimplemented bit, read as '0'-n = Value at POR'1' = Bit is set'0' = Bit is clearedx = Bit is unknown

bit 31-16 Unimplemented: Read as '0'

bit 15 IBF: Input Buffer Full Status bit

1 = All writable input buffer registers are full

0 = Some or all of the writable input buffer registers are empty

bit 14 IBOV: Input Buffer Overflow Status bit

1 = A write attempt to a full input byte buffer occurred (must be cleared in software)

0 = An overflow has not occurred

bit 13-12 Unimplemented: Read as '0'

bit 11-8 IBxF: Input Buffer 'x' Status Full bits

1 = Input buffer contains data that has not been read (reading buffer will clear this bit)

0 = Input buffer does not contain any unread data

bit 7 OBE: Output Buffer Empty Status bit

1 = All readable output buffer registers are empty

0 = Some or all of the readable output buffer registers are full

bit 6 **OBUF:** Output Buffer Underflow Status bit

1 = A read occurred from an empty output byte buffer (must be cleared in software)

0 = An underflow has not occurred

bit 5-4 Unimplemented: Read as '0'

bit 3-0 OBxE: Output Buffer 'x' Status Empty bits

1 = Output buffer is empty (writing data to the buffer will clear this bit)

0 = Output buffer contains data that has not been transmitted

# 24.0 CONTROLLER AREA NETWORK (CAN)

Note:

This data sheet summarizes the features of the PIC32MX5XX/6XX/7XX family of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to **Section 34.** "Controller Area Network (CAN)" (DS60001154) in the "PIC32 Family Reference Manual", which is available from the Microchip web site (www.microchip.com/PIC32).

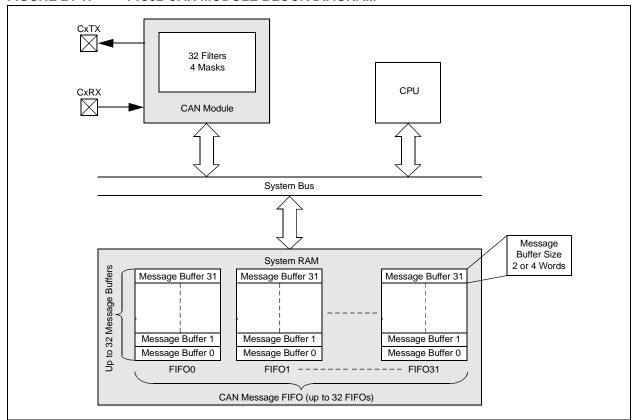

The Controller Area Network (CAN) module supports the following key features:

- Standards Compliance:

- Full CAN 2.0B compliance

- Programmable bit rate up to 1 Mbps

- · Message Reception and Transmission:

- 32 message FIFOs

- Each FIFO can have up to 32 messages for a total of 1024 messages

- FIFO can be a transmit message FIFO or a receive message FIFO

- User-defined priority levels for message FIFOs used for transmission

- 32 acceptance filters for message filtering

- Four acceptance filter mask registers for message filtering

- Automatic response to remote transmit request

- DeviceNet<sup>™</sup> addressing support

- · Additional Features:

- Loopback, Listen All Messages, and Listen Only modes for self-test, system diagnostics and bus monitoring

- Low-power operating modes

- CAN module is a bus master on the PIC32 system bus

- Use of DMA is not required

- Dedicated time-stamp timer

- Dedicated DMA channels

- Data-only Message Reception mode

Figure 24-1 illustrates the general structure of the CAN module.

#### FIGURE 24-1: PIC32 CAN MODULE BLOCK DIAGRAM

DS60001156J-page 283

TABLE 25-5: ETHERNET CONTROLLER REGISTER SUMMARY FOR PIC32MX664F064H, PIC32MX664F128H, PIC32MX664F064L, PIC32MX664F128L, PIC32MX675F256H, PIC32MX675F512H, PIC32MX775F256H, PIC32MX775F512H, PIC32MX775F512H, PIC32MX775F512L, PIC32MX764F128L, PIC32MX775F256L, PIC32MX775F256L, PIC32MX775F256L, PIC32MX775F256L, PIC32MX775F512L AND PIC32MX795F512L DEVICES (CONTINUED)

|                             |                                 |               |               |       |       |          |               |            |      |               |        |      | <u> </u> |               |          |             |           |          |            |

|-----------------------------|---------------------------------|---------------|---------------|-------|-------|----------|---------------|------------|------|---------------|--------|------|----------|---------------|----------|-------------|-----------|----------|------------|

| ess                         |                                 |               |               |       |       |          |               |            |      | В             | its    |      |          |               |          |             |           |          |            |

| Virtual Address<br>(BF88_#) | Register<br>Name <sup>(1)</sup> | Bit Range     | 31/15         | 30/14 | 29/13 | 28/12    | 27/11         | 26/10      | 25/9 | 24/8          | 23/7   | 22/6 | 21/5     | 20/4          | 19/3     | 18/2        | 17/1      | 16/0     | All Resets |

|                             | EMAC1                           | 31:16         | _             | _     | _     | _        | _             | _          | _    | _             | _      | _    | _        | _             | _        | _           | _         | _        | 0000       |

| 9260                        | SUPP                            | 15:0          | _             | _     | _     | _        | RESET<br>RMII | _          | _    | SPEED<br>RMII | _      | _    | _        | _             | _        | _           | _         | _        | 1000       |

| 9270                        | EMAC1                           | 31:16         | I             | _     | _     | _        | _             | _          | _    | I             | _      | _    | _        | _             | _        | _           | I         | ı        | 0000       |

| 9270                        | TEST                            | 15:0          | I             | 1     | _     | _        | 1             | 1          | _    | I             | 1      | _    | _        | _             | _        | TESTBP      | TESTPAUSE | SHRTQNTA | 0000       |

|                             | EMAC1                           | 31:16         |               | -     | _     | _        | _             | _          | _    |               | -      | _    | _        | _             | _        | _           | _         |          | 0000       |

| 9280                        |                                 | 15:0          | RESET<br>MGMT | _     | _     | _        | _             | _          | _    | _             | _      | _    |          | CLKSE         | L<3:0>   |             | NOPRE     | SCANINC  | 0020       |

| 9290                        | EMAC1                           | 31:16         | 1             | _     | _     | _        | _             | _          | _    | 1             | _      | _    | _        | _             | _        | _           | 1         | 1        | 0000       |

| 9290                        | MCMD                            | 15:0          | 1             | -     | _     | _        | -             | 1          | _    | 1             | 1      | _    | _        | _             | _        | _           | SCAN      | READ     | 0000       |

| 92A0                        | EMAC1                           | 31:16         | _             | _     | _     | _        | _             | _          | _    | _             | _      | _    | _        | _             | _        | _           | _         | _        | 0000       |

| 02,10                       | MADR                            | 15:0          | _             | _     | _     |          | P             | HYADDR<4:0 | )>   |               | _      | _    | _        |               | F        | REGADDR<4:0 | )>        |          | 0100       |

| 92B0                        | EMAC1                           | 31:16         | _             | _     | _     | _        | _             | _          | _    |               | _      | _    | _        | _             | _        | _           |           | _        | 0000       |

|                             | MWTD                            | 15:0          |               |       |       | ı        |               |            | ı    | MWTD          | <15:0> | ı    | 1        | ı             | 1        |             |           |          | 0000       |

| 92C0                        | EMAC1<br>MRDD                   | 31:16         | _             | _     | _     | _        | _             | _          | _    | _             | _      | _    | _        | _             | _        | _           | _         | _        | 0000       |

|                             |                                 | 15:0          |               |       |       |          |               |            |      | MRDD          |        |      |          |               |          | 1           |           |          | 0000       |

| 92D0                        | EMAC1<br>MIND                   | 31:16         |               |       |       | _        |               |            | _    |               |        | _    | _        | _             |          | _           | _         | _        | 0000       |

|                             |                                 | 15:0          |               | _     | _     | _        | _             | _          | _    | _             | _      | _    | _        | _             | LINKFAIL | NOTVALID    | SCAN      | MIIMBUSY | 0000       |

| 9300                        | EMAC1<br>SA0 <sup>(2)</sup>     | 31:16         | _             | _     | _     | — OTNADE | —<br>D0 7.0   | _          | _    | _             |        |      |          |               |          | _           | xxxx      |          |            |

|                             |                                 | 15:0          |               |       |       | STNADE   |               |            |      |               |        |      |          |               | JK5<7:U> |             |           |          | xxxx       |

| 9310                        | EMAC1<br>SA1 <sup>(2)</sup>     | 31:16<br>15:0 |               |       |       |          |               |            | _    |               |        |      |          |               | _        | xxxx        |           |          |            |

|                             |                                 | 31:16         | _             | _     | _     | —        | -<br>-        | _          | _    | _             | _      | _    | _        |               |          | _           | _         | _        | xxxx       |

| 9320                        | EMAC1<br>SA2 <sup>(2)</sup>     | 15:0          |               |       |       | STNADE   |               |            |      |               |        |      |          |               | DR1<7:0> |             |           |          | xxxx       |

|                             |                                 | . 5.0         |               |       |       |          |               |            |      |               |        |      |          | OTTO DOTTO TO |          |             |           |          |            |

eqend: x = unknown value on Reset; — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

2: Reset values default to the factory programmed value.

te 1: All registers in this table (with the exception of ETHSTAT) have corresponding CLR, SET and INV registers at their virtual addresses, plus offsets of 0x4, 0x8 and 0xC, respectively. See Section 12.1.1 "CLR, SET and INV Registers" for more information.

### PIC32MX5XX/6XX/7XX

#### REGISTER 25-13: ETHIEN: ETHERNET CONTROLLER INTERRUPT ENABLE REGISTER

| Bit<br>Range | Bit<br>31/23/15/7       | Bit<br>30/22/14/6        | Bit<br>29/21/13/5       | Bit<br>28/20/12/4 | Bit<br>27/19/11/3       | Bit<br>26/18/10/2        | Bit<br>25/17/9/1         | Bit<br>24/16/8/0         |

|--------------|-------------------------|--------------------------|-------------------------|-------------------|-------------------------|--------------------------|--------------------------|--------------------------|

| 31:24        | U-0                     | U-0                      | U-0                     | U-0               | U-0                     | U-0                      | U-0                      | U-0                      |

| 31.24        | _                       | _                        | _                       | _                 | _                       | _                        | _                        | _                        |

| 23:16        | U-0                     | U-0                      | U-0                     | U-0               | U-0                     | U-0                      | U-0                      | U-0                      |

| 23.10        | _                       | _                        | _                       | _                 | _                       | _                        | _                        | _                        |

| 15:8         | U-0                     | R/W-0                    | R/W-0                   | U-0               | U-0                     | U-0                      | R/W-0                    | R/W-0                    |

| 13.6         | _                       | TXBUSEIE <sup>(1)</sup>  | RXBUSEIE <sup>(2)</sup> | _                 | _                       | _                        | EWMARKIE <sup>(2)</sup>  | FWMARKIE <sup>(2)</sup>  |

| 7:0          | R/W-0                   | R/W-0                    | R/W-0                   | U-0               | R/W-0                   | R/W-0                    | R/W-0                    | R/W-0                    |

| 7.0          | RXDONEIE <sup>(2)</sup> | PKTPENDIE <sup>(2)</sup> | RXACTIE <sup>(2)</sup>  | _                 | TXDONEIE <sup>(1)</sup> | TXABORTIE <sup>(1)</sup> | RXBUFNAIE <sup>(2)</sup> | RXOVFLWIE <sup>(2)</sup> |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

bit 31-15 Unimplemented: Read as '0'

bit 14 **TXBUSEIE:** Transmit BVCI Bus Error Interrupt Enable bit<sup>(1)</sup>

1 = Enable TXBUS Error Interrupt 0 = Disable TXBUS Error Interrupt

bit 13 **RXBUSEIE:** Receive BVCI Bus Error Interrupt Enable bit<sup>(2)</sup>

1 = Enable RXBUS Error Interrupt0 = Disable RXBUS Error Interrupt

bit 12-10 Unimplemented: Read as '0'

bit 9 **EWMARKIE:** Empty Watermark Interrupt Enable bit<sup>(2)</sup>

1 = Enable EWMARK Interrupt 0 = Disable EWMARK Interrupt

bit 8 FWMARKIE: Full Watermark Interrupt Enable bit (2)

1 = Enable FWMARK Interrupt0 = Disable FWMARK Interrupt

bit 7 **RXDONEIE:** Receiver Done Interrupt Enable bit<sup>(2)</sup>

1 = Enable RXDONE Interrupt0 = Disable RXDONE Interrupt

bit 6 **PKTPENDIE**: Packet Pending Interrupt Enable bit<sup>(2)</sup>

1 = Enable PKTPEND Interrupt0 = Disable PKTPEND Interrupt

bit 5 RXACTIE: RX Activity Interrupt Enable bit

1 = Enable RXACT Interrupt0 = Disable RXACT Interrupt

bit 4 Unimplemented: Read as '0'

bit 3 **TXDONEIE:** Transmitter Done Interrupt Enable bit<sup>(1)</sup>

1 = Enable TXDONE Interrupt0 = Disable TXDONE Interrupt

bit 2 **TXABORTIE:** Transmitter Abort Interrupt Enable bit<sup>(1)</sup>

1 = Enable TXABORT Interrupt0 = Disable TXABORT Interrupt

bit 1 **RXBUFNAIE**: Receive Buffer Not Available Interrupt Enable bit<sup>(2)</sup>

1 = Enable RXBUFNA Interrupt0 = Disable RXBUFNA Interrupt

bit 0 RXOVFLWIE: Receive FIFO Overflow Interrupt Enable bit(2)

1 = Enable RXOVFLW Interrupt0 = Disable RXOVFLW Interrupt

**Note 1:** This bit is only used for TX operations.

2: This bit is only used for RX operations.

#### REGISTER 25-29: EMAC1SUPP: ETHERNET CONTROLLER MAC PHY SUPPORT REGISTER

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3        | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0         |

|--------------|-------------------|-------------------|-------------------|-------------------|--------------------------|-------------------|------------------|--------------------------|

| 31:24        | U-0               | U-0               | U-0               | U-0               | U-0                      | U-0               | U-0              | U-0                      |

| 31.24        | _                 | _                 | _                 | _                 | _                        | _                 | _                | _                        |

| 23:16        | U-0               | U-0               | U-0               | U-0               | U-0                      | U-0               | U-0              | U-0                      |

| 23.10        | _                 | _                 | _                 | _                 | _                        | _                 | _                | _                        |

| 15:8         | U-0               | U-0               | U-0               | U-0               | R/W-0                    | U-0               | U-0              | R/W-0                    |

| 15.6         | _                 | _                 | _                 | _                 | RESETRMII <sup>(1)</sup> | _                 | _                | SPEEDRMII <sup>(1)</sup> |

| 7:0          | U-0               | U-0               | U-0               | U-0               | U-0                      | U-0               | U-0              | U-0                      |

| 7.0          | _                 | _                 | -                 | 1                 | _                        | _                 | _                | _                        |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

bit 31-12 Unimplemented: Read as '0'

bit 11 RESETRMII: Reset RMII Logic bit<sup>(1)</sup>

1 = Reset the MAC RMII module

0 = Normal operation.

bit 10-9 **Unimplemented:** Read as '0' bit 8 **SPEEDRMII:** RMII Speed bit<sup>(1)</sup>

This bit configures the Reduced MII logic for the current operating speed.

1 = RMII is running at 100 Mbps 0 = RMII is running at 10 Mbps

bit 7-0 **Unimplemented:** Read as '0'

Note 1: This bit is only used for the RMII module.

**Note:** Both 16-bit and 32-bit accesses are allowed to these registers (including the SET, CLR and INV registers).

8-bit accesses are not allowed and are ignored by the hardware.

REGISTER 29-3: DEVCFG2: DEVICE CONFIGURATION WORD 2

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|--|

| 24.24        | r-1               | r-1               | r-1               | r-1               | r-1               | r-1               | r-1              | r-1              |  |

| 31:24        | _                 | _                 | _                 | _                 | _                 | _                 | _                | _                |  |

| 22.40        | r-1               | r-1               | r-1               | r-1               | r-1               | R/P               | R/P              | R/P              |  |

| 23:16        | _                 | _                 | _                 | _                 | _                 | FPLLODIV<2:0>     |                  |                  |  |

| 45.0         | R/P               | r-1               | r-1               | r-1               | r-1               | R/P               | R/P              | R/P              |  |

| 15:8         | UPLLEN            | _                 | _                 | _                 | _                 | UPLLIDIV<2:0>     |                  |                  |  |

| 7.0          | r-1               | R/P-1             | R/P               | R/P-1             | r-1               | R/P               | R/P              | R/P              |  |

| 7:0          | _                 | F                 | PLLMUL<2:0        | >                 | _                 | FPLLIDIV<2:0>     |                  |                  |  |

Legend:r = Reserved bitP = Programmable bitR = Readable bitW = Writable bitU = Unimplemented bit, read as '0'-n = Value at POR'1' = Bit is set'0' = Bit is clearedx = Bit is unknown

bit 31-19 Reserved: Write '1'

bit 18-16 FPLLODIV<2:0>: PLL Output Divider bits

111 = PLL output divided by 256

110 = PLL output divided by 64

101 = PLL output divided by 32

100 = PLL output divided by 16

011 = PLL output divided by 8

010 = PLL output divided by 4

001 = PLL output divided by 2 000 = PLL output divided by 1

bit 15 UPLLEN: USB PLL Enable bit

1 = Disable and bypass USB PLL

0 = Enable USB PLL

bit 14-11 Reserved: Write '1'

bit 10-8 UPLLIDIV<2:0>: USB PLL Input Divider bits

111 = 12x divider

110 = 10x divider

101 = 6x divider

100 = 5x divider

011 = 4x divider

010 = 3x divider

001 = 2x divider

000 = 1x divider

bit 7 Reserved: Write '1'

bit 6-4 FPLLMUL<2:0>: PLL Multiplier bits

111 = 24x multiplier

110 = 21x multiplier

101 = 20x multiplier

100 = 19x multiplier

011 = 18x multiplier

010 = 17x multiplier

001 = 16x multiplier

000 = 15x multiplier

bit 3 Reserved: Write '1'

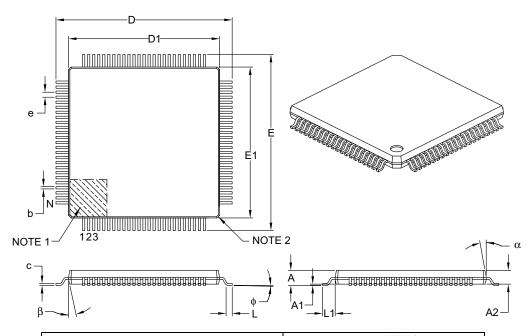

#### 100-Lead Plastic Thin Quad Flatpack (PT) - 12x12x1 mm Body, 2.00 mm [TQFP]

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

|                          | Units            | MILLIMETERS |           |      |  |  |  |

|--------------------------|------------------|-------------|-----------|------|--|--|--|

|                          | Dimension Limits | MIN         | NOM       | MAX  |  |  |  |

| Number of Leads          | N                |             | 100       |      |  |  |  |

| Lead Pitch               | е                |             | 0.40 BSC  |      |  |  |  |

| Overall Height           | A                | -           | _         | 1.20 |  |  |  |

| Molded Package Thickness | A2               | 0.95        | 1.00      | 1.05 |  |  |  |

| Standoff                 | A1               | 0.05        | _         | 0.15 |  |  |  |

| Foot Length              | L                | 0.45        | 0.60      | 0.75 |  |  |  |

| Footprint                | L1               | 1.00 REF    |           |      |  |  |  |

| Foot Angle               | ф                | 0°          | 3.5°      | 7°   |  |  |  |

| Overall Width            | E                |             | 14.00 BSC |      |  |  |  |

| Overall Length           | D                | 14.00 BSC   |           |      |  |  |  |

| Molded Package Width     | E1               | 12.00 BSC   |           |      |  |  |  |

| Molded Package Length    | D1               | 12.00 BSC   |           |      |  |  |  |

| Lead Thickness           | С                | 0.09        | _         | 0.20 |  |  |  |

| Lead Width               | b                | 0.13        | 0.18      | 0.23 |  |  |  |

| Mold Draft Angle Top     | α                | 11°         | 12°       | 13°  |  |  |  |

| Mold Draft Angle Bottom  | β                | 11°         | 12°       | 13°  |  |  |  |

#### Notes:

- 1. Pin 1 visual index feature may vary, but must be located within the hatched area.

- 2. Chamfers at corners are optional; size may vary.

- 3. Dimensions D1 and E1 do not include mold flash or protrusions. Mold flash or protrusions shall not exceed 0.25 mm per side.

- 4. Dimensioning and tolerancing per ASME Y14.5M.

BSC: Basic Dimension. Theoretically exact value shown without tolerances.

REF: Reference Dimension, usually without tolerance, for information purposes only.

Microchip Technology Drawing C04-100B