Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFI

| Product Status             | Active                                                                         |

|----------------------------|--------------------------------------------------------------------------------|

| Core Processor             | MIPS32® M4K™                                                                   |

| Core Size                  | 32-Bit Single-Core                                                             |

| Speed                      | 80MHz                                                                          |

| Connectivity               | Ethernet, I <sup>2</sup> C, SPI, UART/USART, USB OTG                           |

| Peripherals                | Brown-out Detect/Reset, DMA, POR, PWM, WDT                                     |

| Number of I/O              | 53                                                                             |

| Program Memory Size        | 128KB (128K x 8)                                                               |

| Program Memory Type        | FLASH                                                                          |

| EEPROM Size                |                                                                                |

| RAM Size                   | 32K x 8                                                                        |

| Voltage - Supply (Vcc/Vdd) | 2.3V ~ 3.6V                                                                    |

| Data Converters            | A/D 16x10b                                                                     |

| Oscillator Type            | Internal                                                                       |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                              |

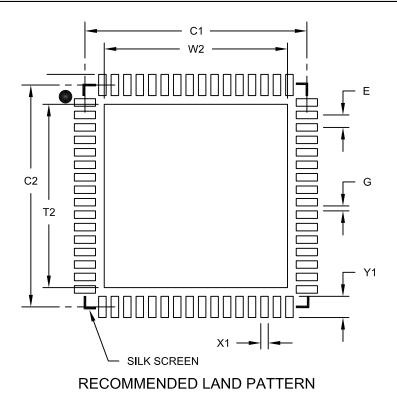

| Mounting Type              | Surface Mount                                                                  |

| Package / Case             | 64-VFQFN Exposed Pad                                                           |

| Supplier Device Package    | 64-VQFN (9x9)                                                                  |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic32mx664f128h-i-mr |

|                            |                                                                                |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# TO OUR VALUED CUSTOMERS

It is our intention to provide our valued customers with the best documentation possible to ensure successful use of your Microchip products. To this end, we will continue to improve our publications to better suit your needs. Our publications will be refined and enhanced as new volumes and updates are introduced.

If you have any questions or comments regarding this publication, please contact the Marketing Communications Department via E-mail at **docerrors@microchip.com** or fax the **Reader Response Form** in the back of this data sheet to (480) 792-4150. We welcome your feedback.

## Most Current Data Sheet

To obtain the most up-to-date version of this data sheet, please register at our Worldwide Web site at:

#### http://www.microchip.com

You can determine the version of a data sheet by examining its literature number found on the bottom outside corner of any page. The last character of the literature number is the version number, (e.g., DS30000000A is version A of document DS30000000).

#### Errata

An errata sheet, describing minor operational differences from the data sheet and recommended workarounds, may exist for current devices. As device/documentation issues become known to us, we will publish an errata sheet. The errata will specify the revision of silicon and revision of document to which it applies.

To determine if an errata sheet exists for a particular device, please check with one of the following:

- Microchip's Worldwide Web site; http://www.microchip.com

- Your local Microchip sales office (see last page)

When contacting a sales office, please specify which device, revision of silicon and data sheet (include literature number) you are using.

#### **Customer Notification System**

Register on our web site at www.microchip.com to receive the most current information on all of our products.

|          |                    | Pin Nur         | nber <sup>(1)</sup> |                 | <b>D</b> '  | D ((           |                                                                                                                                                                                                |

|----------|--------------------|-----------------|---------------------|-----------------|-------------|----------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Pin Name | 64-Pin<br>QFN/TQFP | 100-Pin<br>TQFP | 121-Pin<br>TFBGA    | 124-pin<br>VTLA | Pin<br>Type | Buffer<br>Type | Description                                                                                                                                                                                    |

| AN0      | 16                 | 25              | K2                  | B14             | I           | Analog         | Analog input channels                                                                                                                                                                          |

| AN1      | 15                 | 24              | K1                  | A15             | I           | Analog         |                                                                                                                                                                                                |

| AN2      | 14                 | 23              | J2                  | B13             | I           | Analog         |                                                                                                                                                                                                |

| AN3      | 13                 | 22              | J1                  | A13             | I           | Analog         |                                                                                                                                                                                                |

| AN4      | 12                 | 21              | H2                  | B11             | I           | Analog         |                                                                                                                                                                                                |

| AN5      | 11                 | 20              | H1                  | A12             | I           | Analog         |                                                                                                                                                                                                |

| AN6      | 17                 | 26              | L1                  | A20             | I           | Analog         |                                                                                                                                                                                                |

| AN7      | 18                 | 27              | J3                  | B16             | I           | Analog         |                                                                                                                                                                                                |

| AN8      | 21                 | 32              | K4                  | A23             | I           | Analog         |                                                                                                                                                                                                |

| AN9      | 22                 | 33              | L4                  | B19             | I           | Analog         |                                                                                                                                                                                                |

| AN10     | 23                 | 34              | L5                  | A24             | I           | Analog         |                                                                                                                                                                                                |

| AN11     | 24                 | 35              | J5                  | B20             | I           | Analog         |                                                                                                                                                                                                |

| AN12     | 27                 | 41              | J7                  | B23             | I           | Analog         |                                                                                                                                                                                                |

| AN13     | 28                 | 42              | L7                  | A28             | I           | Analog         |                                                                                                                                                                                                |

| AN14     | 29                 | 43              | K7                  | B24             | I           | Analog         |                                                                                                                                                                                                |

| AN15     | 30                 | 44              | L8                  | A29             | I           | Analog         |                                                                                                                                                                                                |

| CLKI     | 39                 | 63              | F9                  | B34             | I           | ST/<br>CMOS    | External clock source input. Always associated with OSC1 pin function.                                                                                                                         |

| CLKO     | 40                 | 64              | F11                 | A42             | 0           | _              | Oscillator crystal output. Connects to<br>crystal or resonator in Crystal Oscillator<br>mode. Optionally functions as CLKO in<br>RC and EC modes. Always associated<br>with OSC2 pin function. |

| OSC1     | 39                 | 63              | F9                  | B34             | I           | ST/<br>CMOS    | Oscillator crystal input. ST buffer when configured in RC mode; CMOS otherwise.                                                                                                                |

| OSC2     | 40                 | 64              | F11                 | A42             | I/O         |                | Oscillator crystal output. Connects to<br>crystal or resonator in Crystal Oscillator<br>mode. Optionally functions as CLKO in<br>RC and EC modes.                                              |

| SOSCI    | 47                 | 73              | C10                 | A47             | I           | ST/<br>CMOS    | 32.768 kHz low-power oscillator crystal<br>input; CMOS otherwise                                                                                                                               |

| SOSCO    | 48                 | 74              | B11                 | B40             | 0           | _              | 32.768 kHz low-power oscillator crystal<br>output                                                                                                                                              |

# TABLE 1-1: PINOUT I/O DESCRIPTIONS

ST = Schmitt Trigger input with CMOS levels O = Output I = Input I = Input I = Input I = TTL = TTL input buffer

Note 1: Pin numbers are only provided for reference. See the "Device Pin Tables" section for device pin availability.

2: See 25.0 "Ethernet Controller" for more information.

# 2.9 Configuration of Analog and Digital Pins During ICSP Operations

If MPLAB ICD 3 or REAL ICE is selected as a debugger, it automatically initializes all of the Analog-to-Digital input pins (ANx) as "digital" pins by setting all bits in the AD1PCFG register.

The bits in this register that correspond to the Analogto-Digital pins that are initialized by MPLAB ICD 3 or REAL ICE, must not be cleared by the user application firmware; otherwise, communication errors will result between the debugger and the device.

If your application needs to use certain ADC pins as analog input pins during the debug session, the user application must clear the corresponding bits in the AD1PCFG register during initialization of the ADC module.

When MPLAB ICD 3 or REAL ICE is used as a programmer, the user application firmware must correctly configure the AD1PCFG register. Automatic initialization of this register is only done during debugger operation. Failure to correctly configure the register(s) will result in all ADC pins being recognized as analog input pins, resulting in the port value being read as a logic '0', which may affect user application functionality.

# 2.10 Unused I/Os

Unused I/O pins should not be allowed to float as inputs. They can be configured as outputs and driven to a logic-low state.

Alternatively, inputs can be reserved by connecting the pin to Vss through a 1k to 10k resistor and configuring the pin as an input.

# 2.11 EMI/EMC/EFT (IEC 61000-4-4 and IEC 61000-4-2) Suppression Considerations

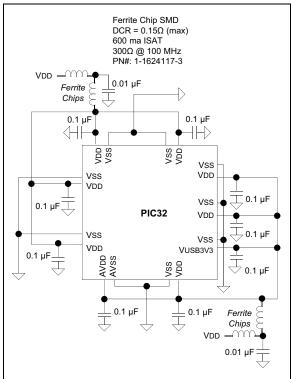

The use of LDO regulators is preferred to reduce overall system noise and provide a cleaner power source. However, when utilizing switching Buck/ Boost regulators as the local power source for PIC32 devices, as well as in electrically noisy environments or test conditions required for IEC 61000-4-4 and IEC 61000-4-2, users should evaluate the use of T-Filters (i.e., L-C-L) on the power pins, as shown in Figure 2-4. In addition to a more stable power source, use of this type of T-Filter can greatly reduce susceptibility to EMI sources and events.

#### FIGURE 2-4: EMI/EMC/EFT SUPPRESSION CIRCUIT

# 3.3 Power Management

The MIPS32 M4K Processor core offers a number of power management features, including low-power design, active power management and power-down modes of operation. The core is a static design that supports slowing or halting the clocks, which reduces system power consumption during idle periods.

#### 3.3.1 INSTRUCTION-CONTROLLED POWER MANAGEMENT

The mechanism for invoking Power-Down mode is through execution of the WAIT instruction. For more information on power management, see Section 28.0 "Power-Saving Features".

#### 3.3.2 LOCAL CLOCK GATING

The majority of the power consumed by the PIC32MX-5XX/6XX/7XX family core is in the clock tree and clocking registers. The PIC32 family uses extensive use of local gated clocks to reduce this dynamic power consumption.

# 3.4 EJTAG Debug Support

The MIPS32 M4K Processor core provides for an Enhanced JTAG (EJTAG) interface for use in the software debug of application and kernel code. In addition to standard User mode and Kernel modes of operation, the MIPS M4K core provides a Debug mode that is entered after a debug exception (derived from a hardware breakpoint, single-step exception, etc.) is taken and continues until a Debug Exception Return (DERET) instruction is executed. During this time, the processor executes the debug exception handler routine.

The EJTAG interface operates through the Test Access Port (TAP), a serial communication port used for transferring test data in and out of the MIPS32 M4K processor core. In addition to the standard JTAG instructions, special instructions defined in the EJTAG specification define which registers are selected and how they are used.

# TABLE 7-6: INTERRUPT REGISTER MAP FOR PIC32MX664F064L, PIC32MX664F128L, PIC32MX675F256L, PIC32MX675F512L AND PIC32MX695F512L DEVICES (CONTINUED)

| ess                         |                                 |           |       |       |       |           |             |           |             | Bi                    | its         |      |             |             |             |             |             |                      |             |       |            |        |       |        |      |  |  |  |  |  |  |  |             |  |        |        |  |

|-----------------------------|---------------------------------|-----------|-------|-------|-------|-----------|-------------|-----------|-------------|-----------------------|-------------|------|-------------|-------------|-------------|-------------|-------------|----------------------|-------------|-------|------------|--------|-------|--------|------|--|--|--|--|--|--|--|-------------|--|--------|--------|--|

| Virtual Address<br>(BF88_#) | Register<br>Name <sup>(1)</sup> | Bit Range | 31/15 | 30/14 | 29/13 | 28/12     | 27/11       | 26/10     | 25/9        | 24/8                  | 23/7        | 22/6 | 21/5        | 20/4        | 19/3        | 18/2        | 17/1        | 16/0                 | All Resets  |       |            |        |       |        |      |  |  |  |  |  |  |  |             |  |        |        |  |

| 10D0                        | IPC4                            | 31:16     | _     | —     | -     |           | INT4IP<2:0> |           | INT4IS      | S<1:0>                | _           | —    | -           |             | OC4IP<2:0>  |             | OC4IS       | 6<1:0>               | 0000        |       |            |        |       |        |      |  |  |  |  |  |  |  |             |  |        |        |  |

| 1000                        | IPC4                            | 15:0      | _     | _     | _     |           | IC4IP<2:0>  |           | IC4IS       | <1:0>                 | _           | _    | _           |             | T4IP<2:0>   |             | T4IS-       | <1:0>                | 0000        |       |            |        |       |        |      |  |  |  |  |  |  |  |             |  |        |        |  |

| 4050                        | IPC5                            | 31:16     | —     | _     | _     |           | SPI1IP<2:0> |           | SPI1IS      | 6<1:0>                | _           | _    | _           |             | OC5IP<2:0>  |             | OC5IS       | S<1:0>               | 0000        |       |            |        |       |        |      |  |  |  |  |  |  |  |             |  |        |        |  |

| 10E0                        | IPC5                            | 15:0      | _     | _     | _     |           | IC5IP<2:0>  |           | IC5IS       | <1:0>                 | -           |      | _           |             | T5IP<2:0>   |             | T5IS-       | <1:0>                | 0000        |       |            |        |       |        |      |  |  |  |  |  |  |  |             |  |        |        |  |

|                             |                                 | 31:16     | _     | _     | _     |           | AD1IP<2:0>  |           | AD1IS       | S<1:0>                | _           | _    | _           | CNIP<2:0>   |             |             | CNIS        | <1:0>                | 0000        |       |            |        |       |        |      |  |  |  |  |  |  |  |             |  |        |        |  |

| 10F0                        | IPC6                            |           |       |       |       |           |             |           |             |                       |             |      |             |             |             |             | U1IP<2:0>   |                      | U1IS-       | <1:0> |            |        |       |        |      |  |  |  |  |  |  |  |             |  |        |        |  |

| IUFU                        | IFCO                            | 15:0      | —     | —     | —     |           | I2C1IP<2:0> |           | I2C1IS<1:0> |                       | I2C1IS<1:0> |      | I2C1IS<1:0> |             | —           | —           | —           |                      | SPI3IP<2:0> | •     | SPI3IS     | S<1:0> | 0000  |        |      |  |  |  |  |  |  |  |             |  |        |        |  |

|                             |                                 |           |       |       |       |           |             |           |             |                       |             |      |             | I2C3IP<2:0> |             | 12C315      | S<1:0>      |                      |             |       |            |        |       |        |      |  |  |  |  |  |  |  |             |  |        |        |  |

|                             |                                 |           |       |       |       |           | U3IP<2:0>   |           | U3IS        | <1:0>                 |             |      |             |             |             |             |             |                      |             |       |            |        |       |        |      |  |  |  |  |  |  |  |             |  |        |        |  |

| 1100                        | IPC7                            | 31:16     | —     | —     | —     |           | SPI2IP<2:0> |           | SPI2IS      | S<1:0>                | —           | —    | —           | (           | CMP2IP<2:0  | >           | CMP2IS<1:0> |                      | 0000        |       |            |        |       |        |      |  |  |  |  |  |  |  |             |  |        |        |  |

| 1100                        | 11 07                           |           |       |       |       |           | I2C4IP<2:0> |           | 12C415      | S<1:0>                |             |      |             |             |             |             |             |                      |             |       |            |        |       |        |      |  |  |  |  |  |  |  |             |  |        |        |  |

|                             |                                 | 15:0      | _     |       |       | (         | CMP1IP<2:0  | >         | CMP1I       | S<1:0>                | _           | _    |             |             | PMPIP<2:0>  |             | PMPI        |                      | 0000        |       |            |        |       |        |      |  |  |  |  |  |  |  |             |  |        |        |  |

|                             |                                 | 31:16     | _     |       |       | F         | RTCCIP<2:0> |           | RTCCIP<2:0> |                       | RTCCIP<2:0> |      | RTCCIP<2:0> |             | RTCCI       | RTCCIS<1:0> |             | _                    |             | I     | FSCMIP<2:0 | >      | FSCMI | S<1:0> | 0000 |  |  |  |  |  |  |  |             |  |        |        |  |

| 1110                        | IPC8                            |           |       |       |       |           |             |           |             |                       |             |      |             |             | U2IP<2:0>   |             | U2IS-       | <1:0>                |             |       |            |        |       |        |      |  |  |  |  |  |  |  |             |  |        |        |  |

| 1110                        | 11 00                           | 15:0      | —     | —     | —     |           | I2C2IP<2:0> |           | 12C215      | I2C2IS<1:0>           |             | —    | —           |             | SPI4IP<2:0> |             | SPI4IS      | S<1:0>               | 0000        |       |            |        |       |        |      |  |  |  |  |  |  |  |             |  |        |        |  |

|                             |                                 |           |       |       |       |           |             |           |             |                       |             |      |             |             |             |             |             |                      |             |       |            |        |       |        |      |  |  |  |  |  |  |  | I2C5IP<2:0> |  | 12C515 | S<1:0> |  |

| 1120                        | IPC9                            | 31:16     | _     | _     |       |           | DMA3IP<2:0  |           | DMA3I       | S<1:0>                | _           |      |             |             | DMA2IP<2:0  |             | DMA2I       | S<1:0>               | 0000        |       |            |        |       |        |      |  |  |  |  |  |  |  |             |  |        |        |  |

| 1120                        | 11 03                           | 15:0      | _     | _     |       |           | DMA1IP<2:0  |           | DMA1I       |                       | _           |      |             |             | DMA0IP<2:0  |             | DMA0I       | S<1:0>               | 0000        |       |            |        |       |        |      |  |  |  |  |  |  |  |             |  |        |        |  |

| 1130                        | IPC10                           | 31:16     | —     | —     | —     | DI        | MA7IP<2:0>  | (2)       | DMA7IS      | i<1:0> <sup>(2)</sup> | —           | _    | —           | D           | MA6IP<2:0>  | (2)         | DMA6IS      | <1:0> <sup>(2)</sup> | 0000        |       |            |        |       |        |      |  |  |  |  |  |  |  |             |  |        |        |  |

| 1130                        | 11 010                          | 15:0      | —     | —     | —     | DI        | MA5IP<2:0>  | (2)       | DMA5IS      | i<1:0> <sup>(2)</sup> | _           | _    | —           | D           | MA4IP<2:0>  | (2)         | DMA4IS      | <1:0> <sup>(2)</sup> | 0000        |       |            |        |       |        |      |  |  |  |  |  |  |  |             |  |        |        |  |

| 1140                        | IPC11                           | 31:16     | —     | -     | _     | _         | _           |           | _           |                       |             |      | _           | _           | —           |             | —           |                      | 0000        |       |            |        |       |        |      |  |  |  |  |  |  |  |             |  |        |        |  |

| 1140                        | IFCII                           | 15:0      | —     | —     | —     |           | USBIP<2:0>  |           | USBIS       | S<1:0>                | _           | _    | —           |             | FCEIP<2:0>  |             | FCEIS       | <1:0>                | 0000        |       |            |        |       |        |      |  |  |  |  |  |  |  |             |  |        |        |  |

| 1150                        | IPC12                           | 31:16     | _     | _     | -     | U5IP<2:0> |             | U5IP<2:0> |             | <1:0>                 | _           |      | -           | U6IP<2:0>   |             |             | U6IP<2:0>   |                      | U6IS-       | <1:0> | 0000       |        |       |        |      |  |  |  |  |  |  |  |             |  |        |        |  |

| 1150                        | IFUIZ                           | 15:0      | _     | -     |       |           |             |           | U4IP<2:0>   |                       |             |      |             |             | U4IS-       | <1:0>       |             |                      |             |       | ETHIP<2:0> |        | ETHIS | i<1:0> | 0000 |  |  |  |  |  |  |  |             |  |        |        |  |

Legend: x = unknown value on Reset; -- = unimplemented, read as '0'. Reset values are shown in hexadecimal.

Note 1: Except where noted, all registers in this table have corresponding CLR, SET and INV registers at their virtual addresses, plus offsets of 0x4, 0x8 and 0xC, respectively. See Section 12.1.1 "CLR, SET and INV Registers" for more information.

2: These bits are not available on PIC32MX664 devices.

3: This register does note have associated CLR, SET, and INV registers.

|                             | PIC32MX795F512L DEVICES Bits    |               |         |         |         |                               |                               |                               |                               |                             |                               |                               |                             |                       |                         |        |               |        |            |

|-----------------------------|---------------------------------|---------------|---------|---------|---------|-------------------------------|-------------------------------|-------------------------------|-------------------------------|-----------------------------|-------------------------------|-------------------------------|-----------------------------|-----------------------|-------------------------|--------|---------------|--------|------------|

| SS                          |                                 |               |         |         |         |                               |                               |                               |                               | В                           | its                           |                               |                             |                       |                         |        |               |        |            |

| Virtual Address<br>(BF88_#) | Register<br>Name <sup>(1)</sup> | Bit Range     | 31/15   | 30/14   | 29/13   | 28/12                         | 27/11                         | 26/10                         | 25/9                          | 24/8                        | 23/7                          | 22/6                          | 21/5                        | 20/4                  | 19/3                    | 18/2   | 17/1          | 16/0   | All Resets |

| 1000                        | INTCON                          | 31:16         | _       | _       | —       | _                             | _                             | -                             | —                             | _                           | _                             | —                             | —                           | _                     |                         | —      | —             | SS0    | 0000       |

| 1000                        | INTCON                          | 15:0          | _       | _       | _       | MVEC                          | _                             |                               | TPC<2:0>                      |                             | _                             | _                             | _                           | INT4EP                | INT3EP                  | INT2EP | INT1EP        | INT0EP | 0000       |

| 1010                        | INTSTAT <sup>(3)</sup>          | 31:16         |         | —       | _       | —                             | —                             | _                             | —                             | —                           | _                             | _                             | —                           |                       | —                       | —      | —             |        | 0000       |

|                             |                                 | 15:0          | _       | —       | —       | —                             | —                             |                               | SRIPL<2:0>                    |                             | —                             | —                             |                             |                       | VEC                     | <5:0>  |               |        | 0000       |

| 1020                        | IPTMR                           | 31:16<br>15:0 |         |         |         |                               |                               |                               |                               | IPTMR                       | <31:0>                        |                               |                             |                       |                         |        |               |        | 0000       |

| 1030                        | IFS0                            | 31:16         | I2C1MIF | I2C1SIF | I2C1BIF | U1TXIF<br>SPI3TXIF<br>I2C3MIF | U1RXIF<br>SPI3RXIF<br>I2C3SIF | U1EIF<br>SPI3EIF<br>I2C3BIF   | SPI1TXIF                      | SPI1RXIF                    | SPI1EIF                       | OC5IF                         | IC5IF                       | T5IF                  | INT4IF                  | OC4IF  | IC4IF         | T4IF   | 0000       |

|                             |                                 | 15:0          | INT3IF  | OC3IF   | IC3IF   | T3IF                          | INT2IF                        | OC2IF                         | IC2IF                         | T2IF                        | INT1IF                        | OC1IF                         | IC1IF                       | T1IF                  | INT0IF                  | CS1IF  | CS0IF         | CTIF   | 0000       |

|                             |                                 | 31:16         | IC3EIF  | IC2EIF  | IC1EIF  | ETHIF                         | CAN2IF <sup>(2)</sup>         | CAN1IF                        | USBIF                         | FCEIF                       | DMA7IF <sup>(2)</sup>         | DMA6IF <sup>(2)</sup>         | DMA5IF <sup>(2)</sup>       | DMA4IF <sup>(2)</sup> | DMA3IF                  | DMA2IF | DMA1IF        | DMA0IF | 0000       |

| 1040                        | IFS1                            | 15:0          | RTCCIF  | FSCMIF  | I2C2MIF | I2C2SIF                       | I2C2BIF                       | U2TXIF<br>SPI4TXIF<br>I2C5MIF | U2RXIF<br>SPI4RXIF<br>I2C5SIF | U2EIF<br>SPI4EIF<br>I2C5BIF | U3TXIF<br>SPI2TXIF<br>I2C4MIF | U3RXIF<br>SPI2RXIF<br>I2C4SIF | U3EIF<br>SPI2EIF<br>I2C4BIF | CMP2IF                | CMP1IF                  | PMPIF  | AD1IF         | CNIF   | 0000       |

|                             |                                 | 31:16         | _       | _       | _       | _                             | _                             | _                             | _                             | _                           | _                             | _                             | _                           | _                     | _                       | _      | _             | _      | 0000       |

| 1050                        | IFS2                            | 15:0          |         | _       | _       | _                             | U5TXIF                        | U5RXIF                        | U5EIF                         | U6TXIF                      | U6RXIF                        | U6EIF                         | U4TXIF                      | U4RXIF                | U4EIF                   | PMPEIF | IC5EIF        | IC4EIF | 0000       |

| 1060                        | IEC0                            | 31:16         | I2C1MIE | I2C1SIE | I2C1BIE | U1TXIE<br>SPI3TXIE<br>I2C3MIE | U1RXIE<br>SPI3RXIE<br>I2C3SIE | U1EIE<br>SPI3EIE<br>I2C3BIE   | SPI1TXIE                      | SPI1RXIE                    | SPI1EIE                       | OC5IE                         | IC5IE                       | T5IE                  | INT4IE                  | OC4IE  | IC4IE         | T4IE   | 0000       |

|                             |                                 | 15:0          | INT3IE  | OC3IE   | IC3IE   | T3IE                          | INT2IE                        | OC2IE                         | IC2IE                         | T2IE                        | INT1IE                        | OC1IE                         | IC1IE                       | T1IE                  | INT0IE                  | CS1IE  | CS0IE         | CTIE   | 0000       |

|                             |                                 | 31:16         | IC3EIE  | IC2EIE  | IC1EIE  | ETHIE                         | CAN2IE <sup>(2)</sup>         | CAN1IE                        | USBIE                         | FCEIE                       | DMA7IE <sup>(2)</sup>         | DMA6IE <sup>(2)</sup>         | DMA5IE <sup>(2)</sup>       | DMA4IE <sup>(2)</sup> | DMA3IE                  | DMA2IE | DMA1IE        | DMA0IE | 0000       |

| 1070                        | IEC1                            | 15:0          | RTCCIE  | FSCMIE  | I2C2MIE | I2C2SIE                       | I2C2BIE                       | U2TXIE<br>SPI4TXIE<br>I2C5MIE | U2RXIE<br>SPI4RXIE<br>I2C5SIE | U2EIE<br>SPI4EIE<br>I2C5BIE | U3TXIE<br>SPI2TXIE<br>I2C4MIE | U3RXIE<br>SPI2RXIE<br>I2C4SIE | U3EIE<br>SPI2EIE<br>I2C4BIE | CMP2IE                | CMP1IE                  | PMPIE  | AD1IE         | CNIE   | 0000       |

|                             | 1500                            | 31:16         | _       | _       | _       | _                             | _                             | _                             | _                             | _                           | _                             | _                             | _                           | _                     | _                       | _      | _             | _      | 0000       |

| 1080                        | IEC2                            | 15:0          | _       | —       | _       | _                             | U5TXIE                        | U5RXIE                        | U5EIE                         | U6TXIE                      | U6RXIE                        | U6EIE                         | U4TXIE                      | U4RXIE                | U4EIE                   | PMPEIE | IC5EIE        | IC4EIE | 0000       |

| 1090                        | IPC0                            | 31:16         |         | _       | —       |                               | INT0IP<2:0>                   |                               | INTOIS                        | S<1:0>                      | _                             | —                             | —                           |                       | CS1IP<2:0>              | >      | CS1IS         | S<1:0> | 0000       |

| 1090                        | IFCU                            | 15:0          | —       | —       | —       |                               | CS0IP<2:0>                    |                               | CSOIS                         | 5<1:0>                      | —                             | —                             | —                           |                       | CTIP<2:0>               |        | CTIS          | <1:0>  | 0000       |

| 10A0                        | IPC1                            | 31:16         |         | —       |         |                               | INT1IP<2:0>                   |                               | INT1IS                        |                             | —                             |                               | —                           |                       | OC1IP<2:0>              | >      | OC1IS         |        | 0000       |

|                             |                                 | 15:0          |         | —       | —       |                               | IC1IP<2:0>                    |                               | IC1IS                         |                             | _                             | —                             | —                           |                       | T1IP<2:0>               |        | T1IS          |        | 0000       |

| 10B0                        | IPC2                            | 31:16         |         | —       |         |                               | INT2IP<2:0>                   |                               | INT2IS                        |                             | _                             |                               | —                           |                       | OC2IP<2:0>              | >      | OC2IS         |        | 0000       |

|                             |                                 | 15:0          | _       | _       | _       |                               | IC2IP<2:0>                    |                               | IC2IS                         |                             | _                             | _                             | _                           |                       | T2IP<2:0>               |        | T2IS          |        | 0000       |

| 10C0                        | IPC3                            | 31:16<br>15:0 |         |         | _       |                               | INT3IP<2:0><br>IC3IP<2:0>     |                               | INT3IS<br>IC3IS               |                             |                               |                               |                             |                       | OC3IP<2:0><br>T3IP<2:0> | >      | OC3IS<br>T3IS |        | 0000       |

| í                           |                                 | 15.0          |         |         |         |                               | 10315 <2.0>                   |                               | 10313                         | <1.U2                       |                               |                               | _                           |                       | 1015 <2.0>              |        | 1313          | <1.02  | 0000       |

# TABLE 7-7:INTERRUPT REGISTER MAP FOR PIC32MX764F128L, PIC32MX775F256L, PIC32MX775F512L AND<br/>PIC32MX795F512L DEVICES

**d:** x = unknown value on Reset; — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

Note 1: Except where noted, all registers in this table have corresponding CLR, SET and INV registers at their virtual addresses, plus offsets of 0x4, 0x8 and 0xC, respectively. See Section 12.1.1 "CLR, SET and INV Registers" for more information.

PIC32MX5XX/6XX/7XX

2: This bit is unimplemented on PIC32MX764F128L device.

3: This register does not have associated CLR, SET, and INV registers.

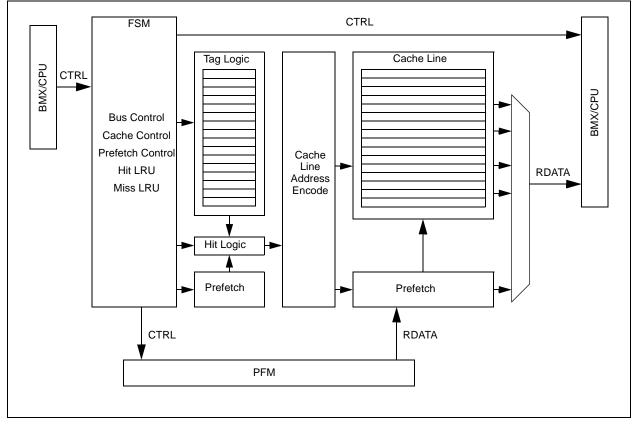

# 9.0 PREFETCH CACHE

Note: This data sheet summarizes the features of the PIC32MX5XX/6XX/7XX family of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to Section 4. "Prefetch Cache" (DS60001119) in the "PIC32 Family Reference Manual", which is available from the Microchip web site (www.microchip.com/PIC32).

Prefetch cache increases performance for applications executing out of the cacheable program Flash memory regions by implementing instruction caching, constant data caching and instruction prefetching.

# 9.1 Features

- 16 fully-associative lockable cache lines

- 16-byte cache lines

- Up to four cache lines allocated to data

- Two cache lines with address mask to hold repeated instructions

- Pseudo-LRU replacement policy

- All cache lines are software writable

- 16-byte parallel memory fetch

- Predictive instruction prefetch

A simplified block diagram of the Prefetch Cache module is illustrated in Figure 9-1.

# FIGURE 9-1: PREFETCH CACHE MODULE BLOCK DIAGRAM

# TABLE 11-1: USB REGISTER MAP (CONTINUED)

| ess                         |                                 |           |       |       | · · · |       |       |       |      |      | Bits  |          |       |          |        |        |           |          |            |

|-----------------------------|---------------------------------|-----------|-------|-------|-------|-------|-------|-------|------|------|-------|----------|-------|----------|--------|--------|-----------|----------|------------|

| Virtual Address<br>(BF88_#) | Register<br>Name <sup>(1)</sup> | Bit Range | 31/15 | 30/14 | 29/13 | 28/12 | 27/11 | 26/10 | 25/9 | 24/8 | 23/7  | 22/6     | 21/5  | 20/4     | 19/3   | 18/2   | 17/1      | 16/0     | All Resets |

| 5280                        | U1FRML <sup>(3)</sup>           | 31:16     |       | —     | —     | —     | —     | —     | —    | —    | _     | —        | _     | —        | —      | —      | _         | _        | 0000       |

| 5200                        | OTTRIME                         | 15:0      | —     | _     | —     | —     | —     | —     | —    | —    |       |          |       | FRML<    | 7:0>   |        |           |          | 0000       |

| 5290                        | U1FRMH <sup>(3)</sup>           | 31:16     | —     | —     | —     | —     | —     | —     | —    | —    | —     | —        | —     | —        | —      | —      | —         | —        | 0000       |

| 0200                        | 01110                           | 15:0      | —     | —     | —     | —     | —     | —     | —    | —    | _     | —        | _     | -        | —      |        | FRMH<2:0> | •        | 0000       |

| 52A0                        | U1TOK                           | 31:16     | —     | —     | —     | —     | —     | —     | —    | —    | —     | —        | —     | —        | —      | —      | —         | —        | 0000       |

| 02/10                       | orron                           | 15:0      | —     | —     | —     | —     | —     | —     | —    | —    |       | PID      | <3:0> |          |        | EP     | <3:0>     |          | 0000       |

| 52B0                        | U1SOF                           | 31:16     | —     | —     | —     | —     | —     | —     | —    | —    | _     | —        | _     | —        | —      | —      | _         | —        | 0000       |

| 5260                        | 0130F                           | 15:0      | —     | _     | _     | —     | _     | _     | _    |      |       |          |       | CNT<7    | 7:0>   |        |           |          | 0000       |

| 52C0                        | U1BDTP2                         | 31:16     | —     | -     | —     | —     | _     | _     | -    |      | —     | —        |       | —        | —      | _      |           | _        | 0000       |

| 5200                        | OIBDIF2                         | 15:0      | —     | —     | —     | —     | —     | —     | —    | —    |       |          |       | BDTPTRH  | H<7:0> |        |           |          | 0000       |

| 52D0                        | U1BDTP3                         | 31:16     | —     | _     | _     | —     | _     | _     | _    |      | —     | _        |       | —        | _      | _      |           | _        | 0000       |

| 5200                        | UIBDIF3                         | 15:0      | —     | _     | _     | _     | _     | _     | -    |      |       |          |       | BDTPTRU  | J<7:0> |        |           |          | 0000       |

| 52E0                        | U1CNFG1                         | 31:16     | —     | _     | _     | —     | _     | _     | _    |      | —     | _        |       | —        | _      | _      |           | _        | 0000       |

| 52E0                        | UTCINFGT                        | 15:0      | —     | _     | _     | —     | _     | _     | _    |      | UTEYE | UOEMON   |       | USBSIDL  | —      | _      |           | UASUSPND | 0001       |

| 5300                        | U1EP0                           | 31:16     | —     | _     | _     | _     | _     | _     | -    |      | —     | _        |       | —        | _      | _      |           | _        | 0000       |

| 5300                        | UIEPU                           | 15:0      | —     | _     | _     | —     | _     | _     | _    |      | LSPD  | RETRYDIS |       | EPCONDIS | EPRXEN | EPTXEN | EPSTALL   | EPHSHK   | 0000       |

| 5310                        | U1EP1                           | 31:16     | —     | _     | _     | —     | _     | _     | _    |      | —     | _        |       | —        | _      | _      |           | _        | 0000       |

| 5310                        | UIEPI                           | 15:0      | —     | _     | _     | _     | _     | _     | _    | _    | —     | _        | -     | EPCONDIS | EPRXEN | EPTXEN | EPSTALL   | EPHSHK   | 0000       |

| 5320                        | U1EP2                           | 31:16     | —     | _     | _     | —     | _     | _     | _    |      | —     | _        |       | —        | _      | _      |           | _        | 0000       |

| 5520                        | UIEFZ                           | 15:0      | _     | _     | _     | _     | _     | _     | _    |      | —     | _        | -     | EPCONDIS | EPRXEN | EPTXEN | EPSTALL   | EPHSHK   | 0000       |

| 5330                        | U1EP3                           | 31:16     | —     | _     | _     | _     | _     | _     | _    | _    | —     | _        | -     | —        | _      |        |           | _        | 0000       |

| 5330                        | UIEP3                           | 15:0      | —     | _     | _     | —     | _     | _     | _    |      | —     | _        |       | EPCONDIS | EPRXEN | EPTXEN | EPSTALL   | EPHSHK   | 0000       |

| 5340                        | U1EP4                           | 31:16     | _     | _     | -     | -     | -     | -     | -    | _    | _     | _        | _     | —        | -      | _      | _         | _        | 0000       |

| 5540                        | UTEP4                           | 15:0      | —     | _     | _     | _     | _     | _     | _    | _    | —     | _        | -     | EPCONDIS | EPRXEN | EPTXEN | EPSTALL   | EPHSHK   | 0000       |

| 5350                        | U1EP5                           | 31:16     | _     | _     | -     | -     | -     | -     | -    | _    | _     | _        | _     | —        | -      | _      | _         | _        | 0000       |

| 5350                        | UIEP5                           | 15:0      | _     | _     | -     | -     | -     | -     | -    | _    | _     | _        | _     | EPCONDIS | EPRXEN | EPTXEN | EPSTALL   | EPHSHK   | 0000       |

| 5260                        | U1EP6                           | 31:16     |       |       | _     | —     | _     |       | _    | _    | —     |          |       | —        | _      | —      |           |          | 0000       |

| 5360                        | UIEP6                           | 15:0      | _     | _     | -     | -     | -     | -     | -    | _    | _     | _        | _     | EPCONDIS | EPRXEN | EPTXEN | EPSTALL   | EPHSHK   | 0000       |

| 5270                        | U1EP7                           | 31:16     | _     | _     | _     | _     | _     | _     | _    | —    | _     | —        | _     | —        | _      | _      | -         | _        | 0000       |

| 5370                        | UTEPT                           | 15:0      |       |       | _     | _     | _     |       |      | _    | —     |          |       | EPCONDIS | EPRXEN | EPTXEN | EPSTALL   | EPHSHK   | 0000       |

| 5200                        |                                 | 31:16     | _     | _     | _     | _     | _     | _     | _    | —    | -     | —        | _     | —        | _      | —      | _         | _        | 0000       |

| 5380                        | U1EP8                           | 15:0      | —     | _     | —     | —     | _     | _     | —    | _    | _     | _        | -     | EPCONDIS | EPRXEN | EPTXEN | EPSTALL   | EPHSHK   | 0000       |

| 5000                        |                                 | 31:16     | _     | —     | _     | _     | _     | _     | _    | —    | _     | —        | _     | —        | —      | —      | —         | —        | 0000       |

| 5390                        | U1EP9                           | 15:0      | _     | —     | _     | _     | _     | _     | _    | _    | _     | _        | _     | EPCONDIS | EPRXEN | EPTXEN | EPSTALL   | EPHSHK   | 0000       |

5390

U1EP9

Legend:

x =

Note

1:

All n

end: x = unknown value on Reset; — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

1: All registers in this table (except as noted) have corresponding CLR, SET and INV registers at its virtual address, plus an offset of 0x4, 0x8 and 0xC respectively. See Section 12.1.1 "CLR, SET and INV Registers" for more information.

2: This register does not have associated SET and INV registers.

3: This register does not have associated CLR, SET and INV registers.

4: Reset value for this bit is undefined.

# PIC32MX5XX/6XX/7XX

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |  |  |  |  |  |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|--|--|--|--|--|--|

| 31:24        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |  |  |  |  |  |  |

| 31.24        |                   | _                 |                   |                   |                   |                   |                  | —                |  |  |  |  |  |  |

| 22.10        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |  |  |  |  |  |  |

| 23:16        |                   |                   |                   |                   |                   |                   |                  | —                |  |  |  |  |  |  |

| 15.0         | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |  |  |  |  |  |  |

| 15:8         | —                 | —                 | _                 | _                 | —                 | _                 | —                | —                |  |  |  |  |  |  |

| 7.0          | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |  |  |  |  |

| 7:0          |                   |                   |                   | CNT               | <7:0>             |                   |                  |                  |  |  |  |  |  |  |

#### REGISTER 11-16: U1SOF: USB SOF THRESHOLD REGISTER

#### Legend:

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read as '0' |                    |  |  |  |  |  |  |

|-------------------|------------------|------------------------------------|--------------------|--|--|--|--|--|--|

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared               | x = Bit is unknown |  |  |  |  |  |  |

#### bit 31-8 Unimplemented: Read as '0'

- bit 7-0 CNT<7:0>: SOF Threshold Value bits

- Typical values of the threshold are: 01001010 = 64-byte packet 00101010 = 32-byte packet 00011010 = 16-byte packet

00010010 = 8-byte packet

#### REGISTER 11-17: U1BDTP1: USB BUFFER DESCRIPTOR TABLE PAGE 1 REGISTER

| Bit<br>Range         Bit<br>31/23/15/7         30           31:24         U-0         1 |       | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

|-----------------------------------------------------------------------------------------|-------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|

| 24.24                                                                                   | U-0   | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 31.24                                                                                   | —     |                   |                   |                   |                   |                   |                  | —                |

| 23:16                                                                                   | U-0   | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 23.10                                                                                   | —     |                   |                   |                   |                   |                   |                  | —                |

| 45.0                                                                                    | U-0   | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 15:8                                                                                    | —     | -                 | —                 | -                 | -                 | -                 | —                | —                |

| 7.0                                                                                     | R/W-0 | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | U-0              |

| 7:0                                                                                     |       |                   | В                 | DTPTRL<15:9       | )>                |                   |                  | —                |

# Legend:

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, r | ead as '0'         |

|-------------------|------------------|--------------------------|--------------------|

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared     | x = Bit is unknown |

#### bit 31-8 Unimplemented: Read as '0'

#### bit 7-1 BDTPTRL<15:9>: BDT Base Address bits

This 7-bit value provides address bits 15 through 9 of the BDT base address, which defines the starting location of the BDT in system memory.

The 32-bit BDT base address is 512-byte aligned.

bit 0 Unimplemented: Read as '0'

# 12.1 Parallel I/O (PIO) Ports

All port pins have three registers (TRIS, LAT and PORT) that are directly associated with their operation.

TRIS is a Data Direction or Tri-State Control register that determines whether a digital pin is an input or an output. Setting a TRISx register bit = 1, configures the corresponding I/O pin as an input; setting a TRISx register bit = 0, configures the corresponding I/O pin as an output. All port I/O pins are defined as inputs after a device Reset. Certain I/O pins are shared with analog peripherals and default to analog inputs after a device Reset.

PORT is a register used to read the current state of the signal applied to the port I/O pins. Writing to a PORTx register performs a write to the port's latch, LATx register, latching the data to the port's I/O pins.

LAT is a register used to write data to the port I/O pins. The LATx Latch register holds the data written to either the LATx or PORTx registers. Reading the LATx Latch register reads the last value written to the corresponding PORT or Latch register.

Not all port I/O pins are implemented on some devices, therefore, the corresponding PORTx, LATx and TRISx register bits will read as zeros.

#### 12.1.1 CLR, SET AND INV REGISTERS

Every I/O module register has a corresponding Clear (CLR), Set (SET) and Invert (INV) register designed to provide fast atomic bit manipulations. As the name of the register implies, a value written to a SET, CLR or INV register effectively performs the implied operation, but only on the corresponding base register and only bits specified as '1' are modified. Bits specified as '0' are not modified.

Reading SET, CLR and INV registers returns undefined values. To see the affects of a write operation to a SET, CLR or INV register, the base register must be read.

| Note: | Using a PORTxINV register to toggle a bit |

|-------|-------------------------------------------|

|       | is recommended because the operation is   |

|       | performed in hardware atomically, using   |

|       | fewer instructions, as compared to the    |

|       | traditional read-modify-write method, as  |

|       | follows:                                  |

|       | PORTC $^{ = 0x0001:}$                     |

## 12.1.2 DIGITAL INPUTS

Pins are configured as digital inputs by setting the corresponding TRIS register bits = 1. When configured as inputs, they are either TTL buffers or Schmitt Triggers. Several digital pins share functionality with analog inputs and default to the analog inputs at POR. Setting the corresponding bit in the AD1PCFG register = 1 enables the pin as a digital pin.

The maximum input voltage allowed on the input pins is the same as the maximum VIH specification. Refer to **Section 32.0 "Electrical Characteristics"** for VIH specification details.

| Note: | Analog levels on any pin that is defined as<br>a digital input (including the ANx pins)<br>may cause the input buffer to consume |

|-------|----------------------------------------------------------------------------------------------------------------------------------|

|       | current that exceeds the device specifications.                                                                                  |

#### 12.1.3 ANALOG INPUTS

Certain pins can be configured as analog inputs used by the ADC and comparator modules. Setting the corresponding bits in the AD1PCFG register = 0 enables the pin as an analog input pin and must have the corresponding TRIS bit set = 1 (input). If the TRIS bit is cleared = 0 (output), the digital output level (VOH or VOL) will be converted. Any time a port I/O pin is configured as analog, its digital input is disabled and the corresponding PORTx register bit will read '0'. The AD1PCFG register has a default value of 0x0000; therefore, all pins that share ANx functions are analog (not digital) by default.

## 12.1.4 DIGITAL OUTPUTS

Pins are configured as digital outputs by setting the corresponding TRIS register bits = 0. When configured as digital outputs, these pins are CMOS drivers or can be configured as open-drain outputs by setting the corresponding bits in the Open-Drain Configuration (ODCx) register.

The open-drain feature allows generation of outputs higher than VDD (e.g., 5V) on any desired 5V tolerant pins by using external pull-up resistors. The maximum open-drain voltage allowed is the same as the maximum VIH specification.

See the **"Device Pin Tables"** section for the available pins and their functionality.

## 12.1.5 ANALOG OUTPUTS

Certain pins can be configured as analog outputs, such as the CVREF output voltage used by the comparator module. Configuring the comparator reference module to provide this output will present the analog output voltage on the pin, independent of the TRIS register setting for the corresponding pin.

## 12.1.6 INPUT CHANGE NOTIFICATION

The input change notification function of the I/O ports (CNx) allows devices to generate interrupt requests in response to change-of-state on selected pin.

Each CNx pin also has a weak pull-up, which acts as a current source connected to the pin. The pull-ups are enabled by setting the corresponding bit in the CNPUE register.

# TABLE 12-9: PORTF REGISTER MAP FOR PIC32MX534F064H, PIC32MX564F064H, PIC32MX564F128H, PIC32MX575F512H, PIC32MX664F064H, PIC32MX664F128H, PIC32MX675F256H, PIC32MX675F512H, PIC32MX695F512H, PIC32MX775F512H, PIC32MX775F512H, PIC32MX775F512H, PIC32MX795F512H, DEVICES

| ess                         |                                 | e         |       |       |       |       |       |       |      | Bi   | its  |      |        |        |        |      |        |        |            |

|-----------------------------|---------------------------------|-----------|-------|-------|-------|-------|-------|-------|------|------|------|------|--------|--------|--------|------|--------|--------|------------|

| Virtual Address<br>(BF88_#) | Register<br>Name <sup>(1)</sup> | Bit Range | 31/15 | 30/14 | 29/13 | 28/12 | 27/11 | 26/10 | 25/9 | 24/8 | 23/7 | 22/6 | 21/5   | 20/4   | 19/3   | 18/2 | 17/1   | 16/0   | All Resets |

| 6140                        | TRISF                           | 31:16     | _     | —     | _     | —     | -     | —     | —    | —    | _    | —    | _      | —      | —      | _    | -      | —      | 0000       |

| 6140                        | IRIOF                           | 15:0      |       | _     | _     | _     | _     | _     | _    | _    | _    | _    | TRISF5 | TRISF4 | TRISF3 | _    | TRISF1 | TRISF0 | 003B       |

| 6150                        | PORTF                           | 31:16     | _     | _     |       | _     |       | _     |      |      |      |      | -      | _      | _      | _    |        | -      | 0000       |

| 6150                        | PURIF                           | 15:0      |       | _     | -     | —     | —     | —     | -    | -    | -    | -    | RF5    | RF4    | RF3    |      | RF1    | RF0    | xxxx       |

| 6160                        | LATF                            | 31:16     |       | _     | _     | _     | _     | _     | _    | _    | _    | _    | -      | _      | _      | _    | _      | _      | 0000       |

| 6160                        | LAIF                            | 15:0      | -     | _     | —     | _     | _     | _     | _    | _    | _    | _    | LATF5  | LATF4  | LATF3  | —    | LATF1  | LATF0  | xxxx       |

| 6170                        | ODCF                            | 31:16     |       | _     | _     | _     | _     | _     | _    | _    | _    | _    | -      | _      | _      | _    | _      | _      | 0000       |

| 0170                        | ODCF                            | 15:0      | _     | _     | _     |       | -     |       |      |      |      |      | ODCF5  | ODCF4  | ODCF3  |      | ODCF1  | ODCF0  | 0000       |

Legend: x = unknown value on Reset; - = unimplemented, read as '0'. Reset values are shown in hexadecimal.

Note 1: All registers in this table have corresponding CLR, SET and INV registers at their virtual addresses, plus offsets of 0x4, 0x8 and 0xC, respectively. See Section 12.1.1 "CLR, SET and INV Registers" for more information.

# TABLE 12-10: PORTF REGISTER MAP PIC32MX534F064L, PIC32MX564F064L, PIC32MX564F128L, PIC32MX575F256L, PIC32MX575F512L, PIC32MX664F064L, PIC32MX664F128L, PIC32MX675F256L, PIC32MX675F512L, PIC32MX775F512L, PIC32MX7

| ess                         |                                 | â         |       |       |         |         |       |       |      | Bi     | ts   |      |        |        |        |        |        |        | - y       |

|-----------------------------|---------------------------------|-----------|-------|-------|---------|---------|-------|-------|------|--------|------|------|--------|--------|--------|--------|--------|--------|-----------|

| Virtual Address<br>(BF88_#) | Register<br>Name <sup>(1)</sup> | Bit Range | 31/15 | 30/14 | 29/13   | 28/12   | 27/11 | 26/10 | 25/9 | 24/8   | 23/7 | 22/6 | 21/5   | 20/4   | 19/3   | 18/2   | 17/1   | 16/0   | All Reset |

|                             | TDIOF                           | 31:16     | _     | _     | _       | _       | _     | _     | _    | _      | _    | _    | _      | _      | _      | _      | _      | _      | 0000      |

| 6140                        | TRISF                           | 15:0      | _     | _     | TRISF13 | TRISF12 | _     | _     | _    | TRISF8 | _    | _    | TRISF5 | TRISF4 | TRISF3 | TRISF2 | TRISF1 | TRISF0 | 313F      |

| 6150                        | PORTF                           | 31:16     | -     | _     | _       | _       | _     | -     | _    | _      | -    |      | -      |        | _      |        | _      | _      | 0000      |

| 0150                        | FUNIF                           | 15:0      | -     | —     | RF13    | RF12    | _     |       | _    | RF8    |      |      | RF5    | RF4    | RF3    | RF2    | RF1    | RF0    | xxxx      |

| 6160                        | LATF                            | 31:16     | —     | —     | _       |         | —     | _     | _    |        | -    | _    | _      | _      | _      | _      | —      | —      | 0000      |

| 0100                        | LAIF                            | 15:0      |       | —     | LATF13  | LATF12  |       | -     |      | LATF8  |      | -    | LATF5  | LATF4  | LATF3  | LATF2  | LATF1  | LATF0  | xxxx      |

| 6170                        | ODCF                            | 31:16     | —     | _     | _       | —       | _     |       | _    |        |      |      | _      |        | —      |        | -      | -      | 0000      |

| 0170                        | ODCF                            | 15:0      | _     | _     | ODCF13  | ODCF12  | _     | -     | —    | ODCF8  | _    | -    | ODCF5  | ODCF4  | ODCF3  | ODCF2  | ODCF1  | ODCF0  | 0000      |

Legend: x = unknown value on Reset; — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

Note 1: All registers in this table have corresponding CLR, SET and INV registers at their virtual addresses, plus offsets of 0x4, 0x8 and 0xC, respectively. See Section 12.1.1 "CLR, SET and INV Registers" for more information.

## REGISTER 24-11: CIFLTCON1: CAN FILTER CONTROL REGISTER 1 (CONTINUED)

| bit 15    | FLTEN5: Filter 17 Enable bit                                                                           |

|-----------|--------------------------------------------------------------------------------------------------------|

|           | 0 = Filter is disabled                                                                                 |

| bit 14-13 | MSEL5<1:0>: Filter 5 Mask Select bits                                                                  |

|           | 11 = Acceptance Mask 3 selected                                                                        |

|           | 10 = Acceptance Mask 2 selected                                                                        |

|           | 01 = Acceptance Mask 1 selected<br>00 = Acceptance Mask 0 selected                                     |

| bit 12-8  | FSEL5<4:0>: FIFO Selection bits                                                                        |

|           | 11111 = Message matching filter is stored in FIFO buffer 31                                            |

|           | 11110 = Message matching filter is stored in FIFO buffer 30                                            |

|           | •                                                                                                      |

|           | •                                                                                                      |

|           | 00001 = Message matching filter is stored in FIFO buffer 1                                             |

|           | 00000 = Message matching filter is stored in FIFO buffer 0                                             |

| bit 7     | FLTEN4: Filter 4 Enable bit                                                                            |

|           | <ul><li>1 = Filter is enabled</li><li>0 = Filter is disabled</li></ul>                                 |

| bit 6-5   | MSEL4<1:0>: Filter 4 Mask Select bits                                                                  |

|           | 11 = Acceptance Mask 3 selected                                                                        |

|           | 10 = Acceptance Mask 2 selected                                                                        |

|           | 01 = Acceptance Mask 1 selected<br>00 = Acceptance Mask 0 selected                                     |

| bit 4-0   | FSEL4<4:0>: FIFO Selection bits                                                                        |

|           | 11111 = Message matching filter is stored in FIFO buffer 31                                            |

|           | 11110 = Message matching filter is stored in FIFO buffer 30                                            |

|           | •                                                                                                      |

|           | •                                                                                                      |

|           | 00001 = Message matching filter is stored in FIFO buffer 1                                             |

|           | 00000 = Message matching filter is stored in FIFO buffer 0                                             |

| Note:     | The bits in this register can only be modified if the corresponding filter enable (FLTENn) bit is '0'. |

#### TABLE 25-5: ETHERNET CONTROLLER REGISTER SUMMARY FOR PIC32MX664F064H, PIC32MX664F128H, PIC32MX664F064L, PIC32MX664F128L, PIC32MX675F256H, PIC32MX675F512H, PIC32MX695F512H, PIC32MX775F256H, PIC32MX775F512H, PIC32MX795F512H, PIC32MX695F512L, PIC32MX675F256L, PIC32MX675F512L, PIC32MX764F128H, PIC32MX764F128L, PIC32MX775F256L, PIC32MX775F512L AND PIC32MX795F512L DEVICES (CONTINUED)

| ess                         |                                 | 0             |               |               |               |         |               |               |               | В             | its       |         |               |               |            |         |          |          | ŝ          |

|-----------------------------|---------------------------------|---------------|---------------|---------------|---------------|---------|---------------|---------------|---------------|---------------|-----------|---------|---------------|---------------|------------|---------|----------|----------|------------|

| Virtual Address<br>(BF88_#) | Register<br>Name <sup>(1)</sup> | Bit Range     | 31/15         | 30/14         | 29/13         | 28/12   | 27/11         | 26/10         | 25/9          | 24/8          | 23/7      | 22/6    | 21/5          | 20/4          | 19/3       | 18/2    | 17/1     | 16/0     | All Resets |

| 90E0                        | ETHSTAT                         | 31:16<br>15:0 | _             |               | _             | _       | _             |               |               | _             | BUSY      | TXBUSY  | RXBUSY        | BUFC          | NT<7:0>    | _       | _        | _        | 0000       |

|                             | ETH                             | 31:16         | _             |               | _             | _       |               |               | _             |               | _         |         | _             |               | _          | _       | _        |          | 0000       |

| 9100                        | RXOVFLOW                        | 15:0          |               |               |               |         |               |               |               | RXOVFLW       | CNT<15:0> |         |               |               |            |         |          |          | 0000       |

|                             | ETH                             | 31:16         | _             | _             | _             | _       |               | _             | _             |               | _         | _       |               | _             |            |         |          | _        | 0000       |

| 9110                        | FRMTXOK                         | 15:0          |               |               |               |         |               |               |               | FRMTXOK       | CNT<15:0> |         |               |               |            |         |          |          | 0000       |

| 9120                        | ETH                             | 31:16         | _             | -             |               | _       | _             | -             | —             | -             | _         | _       | _             | -             |            | _       | _        | —        | 0000       |

| 9120                        | SCOLFRM                         | 15:0          |               |               |               |         |               |               |               | SCOLFRM       | CNT<15:0> |         |               |               |            |         |          |          | 0000       |

| 9130                        | ETH                             | 31:16         | —             | _             | _             | —       | _             | _             | —             | —             | —         | —       | _             | _             | —          | —       | —        | —        | 0000       |

|                             | MCOLFRM                         | 15:0          |               |               |               |         |               |               |               | MCOLFRM       | CNT<15:0> |         |               |               |            |         |          |          | 0000       |