Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFI

| Details                    |                                                                                |

|----------------------------|--------------------------------------------------------------------------------|

| Product Status             | Active                                                                         |

| Core Processor             | MIPS32® M4K™                                                                   |

| Core Size                  | 32-Bit Single-Core                                                             |

| Speed                      | 80MHz                                                                          |

| Connectivity               | Ethernet, I <sup>2</sup> C, SPI, UART/USART, USB OTG                           |

| Peripherals                | Brown-out Detect/Reset, DMA, POR, PWM, WDT                                     |

| Number of I/O              | 53                                                                             |

| Program Memory Size        | 128KB (128K x 8)                                                               |

| Program Memory Type        | FLASH                                                                          |

| EEPROM Size                | -                                                                              |

| RAM Size                   | 32K x 8                                                                        |

| Voltage - Supply (Vcc/Vdd) | 2.3V ~ 3.6V                                                                    |

| Data Converters            | A/D 16x10b                                                                     |

| Oscillator Type            | Internal                                                                       |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                              |

| Mounting Type              | Surface Mount                                                                  |

| Package / Case             | 64-TQFP                                                                        |

| Supplier Device Package    | 64-TQFP (10x10)                                                                |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic32mx664f128h-i-pt |

|                            |                                                                                |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

#### TABLE 7: **PIN NAMES FOR 100-PIN USB AND CAN DEVICES**

#### **100-PIN TQFP (TOP VIEW)**

#### PIC32MX534F064L PIC32MX564F064L PIC32MX564F128L PIC32MX575F512L PIC32MX575F256L

100

|       |                              |       | 1                              |

|-------|------------------------------|-------|--------------------------------|

| Pin # | Full Pin Name                | Pin # | Full Pin Name                  |

| 1     | RG15                         | 36    | Vss                            |

| 2     | VDD                          | 37    | Vdd                            |

| 3     | PMD5/RE5                     | 38    | TCK/RA1                        |

| 4     | PMD6/RE6                     | 39    | AC1TX/SCK4/U5TX/U2RTS/RF13     |

| 5     | PMD7/RE7                     | 40    | AC1RX/SS4/U5RX/U2CTS/RF12      |

| 6     | T2CK/RC1                     | 41    | AN12/PMA11/RB12                |

| 7     | T3CK/RC2                     | 42    | AN13/PMA10/RB13                |

| 8     | T4CK/RC3                     | 43    | AN14/PMALH/PMA1/RB14           |

| 9     | T5CK/SDI1/RC4                | 44    | AN15/OCFB/PMALL/PMA0/CN12/RB15 |

| 10    | SCK2/U6TX/U3RTS/PMA5/CN8/RG6 | 45    | Vss                            |

| 11    | SDA4/SDI2/U3RX/PMA4/CN9/RG7  | 46    | VDD                            |

| 12    | SCL4/SDO2/U3TX/PMA3/CN10/RG8 | 47    | SS3/U4RX/U1CTS/CN20/RD14       |

| 13    | MCLR                         | 48    | SCK3/U4TX/U1RTS/CN21/RD15      |

| 14    | SS2/U6RX/U3CTS/PMA2/CN11/RG9 | 49    | SDA5/SDI4/U2RX/PMA9/CN17/RF4   |

| 15    | Vss                          | 50    | SCL5/SDO4/U2TX/PMA8/CN18/RF5   |

| 16    | VDD                          | 51    | USBID/RF3                      |

| 17    | TMS/RA0                      | 52    | SDA3/SDI3/U1RX/RF2             |

| 18    | INT1/RE8                     | 53    | SCL3/SDO3/U1TX/RF8             |

| 19    | INT2/RE9                     | 54    | VBUS                           |

| 20    | AN5/C1IN+/VBUSON/CN7/RB5     | 55    | VUSB3V3                        |

| 21    | AN4/C1IN-/CN6/RB4            | 56    | D-/RG3                         |

| 22    | AN3/C2IN+/CN5/RB3            | 57    | D+/RG2                         |

| 23    | AN2/C2IN-/CN4/RB2            | 58    | SCL2/RA2                       |

| 24    | PGEC1/AN1/CN3/RB1            | 59    | SDA2/RA3                       |

| 25    | PGED1/AN0/CN2/RB0            | 60    | TDI/RA4                        |

| 26    | PGEC2/AN6/OCFA/RB6           | 61    | TDO/RA5                        |

| 27    | PGED2/AN7/RB7                | 62    | Vdd                            |

| 28    | VREF-/CVREF-/PMA7/RA9        | 63    | OSC1/CLKI/RC12                 |

| 29    | VREF+/CVREF+/PMA6/RA10       | 64    | OSC2/CLKO/RC15                 |

| 30    | AVDD                         | 65    | Vss                            |

| 31    | AVss                         | 66    | SCL1/INT3/RA14                 |

| 32    | AN8/C1OUT/RB8                | 67    | SDA1/INT4/RA15                 |

| 33    | AN9/C2OUT/RB9                | 68    | RTCC/IC1/RD8                   |

| 34    | AN10/CVREFOUT/PMA13/RB10     | 69    | SS1/IC2/RD9                    |

| 35    | AN11/PMA12/RB11              | 70    | SCK1/IC3/PMCS2/PMA15/RD10      |

Shaded pins are 5V tolerant. Note 1:

## PIC32MX5XX/6XX/7XX

NOTES:

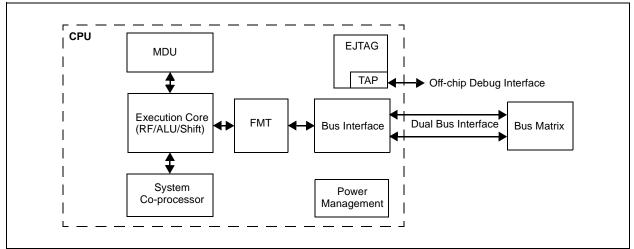

## 3.0 CPU

Note: This data sheet summarizes the features of the PIC32MX5XX/6XX/7XX family of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to Section 2. "CPU" (DS60001113) in the "PIC32 Family Reference Manual", which is available from the Microchip web site (www.microchip.com/PIC32). Resources for the MIPS32<sup>®</sup> M4K<sup>®</sup> Processor Core are available at http://www.imgtec.com.

The MIPS32<sup>®</sup> M4K<sup>®</sup> Processor core is the heart of the PIC32MX5XX/6XX/7XX family processor. The CPU fetches instructions, decodes each instruction, fetches source operands, executes each instruction and writes the results of instruction execution to the proper destinations.

## 3.1 Features

- 5-stage pipeline

- · 32-bit address and data paths

- MIPS32 Enhanced Architecture (Release 2)

- Multiply-accumulate and multiply-subtract instructions

- Targeted multiply instruction

- Zero/One detect instructions

- WAIT instruction

- Conditional move instructions (MOVN, MOVZ)

- Vectored interrupts

- Programmable exception vector base

- Atomic interrupt enable/disable

- GPR shadow registers to minimize latency for interrupt handlers

- Bit field manipulation instructions

- MIPS16e<sup>®</sup> code compression

- 16-bit encoding of 32-bit instructions to improve code density

- Special PC-relative instructions for efficient loading of addresses and constants

- SAVE and RESTORE macro instructions for setting up and tearing down stack frames within subroutines

- Improved support for handling 8-bit and 16-bit data types

- Simple Fixed Mapping Translation (FMT) mechanism

- Simple dual bus interface

- Independent 32-bit address and data busses

- Transactions can be aborted to improve interrupt latency

- · Autonomous multiply/divide unit

- Maximum issue rate of one 32x16 multiply per clock

- Maximum issue rate of one 32x32 multiply every other clock

- Early-in iterative divide. Minimum 11 and maximum 33 clock latency (dividend (*rs*) sign extension-dependent)

- Power control

- Minimum frequency: 0 MHz

- Low-Power mode (triggered by WAIT instruction)

- Extensive use of local gated clocks

- EJTAG debug and instruction trace

- Support for single stepping

- Virtual instruction and data address/value

- Breakpoints

- PC tracing with trace compression

## FIGURE 3-1: MIPS32<sup>®</sup> M4K<sup>®</sup> PROCESSOR CORE BLOCK DIAGRAM

# PIC32MX5XX/6XX/7XX

| Bit Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |  |  |

|-----------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|--|--|--|

|           | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |  |

| 31:24     |                   | CHSSA<31:24>      |                   |                   |                   |                   |                  |                  |  |  |  |

| 00.40     | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |  |

| 23:16     | CHSSA<23:16>      |                   |                   |                   |                   |                   |                  |                  |  |  |  |

| 45.0      | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |  |

| 15:8      | CHSSA<15:8>       |                   |                   |                   |                   |                   |                  |                  |  |  |  |

| 7.0       | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |  |

| 7:0       |                   |                   |                   | CHSSA             | <7:0>             |                   |                  |                  |  |  |  |

## REGISTER 10-10: DCHxSSA: DMA CHANNEL 'x' SOURCE START ADDRESS REGISTER

| Legend:           |                  |                                    |                    |  |

|-------------------|------------------|------------------------------------|--------------------|--|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read as '0' |                    |  |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared               | x = Bit is unknown |  |

bit 31-0 CHSSA<31:0> Channel Source Start Address bits Channel source start address. Note: This must be the physical address of the source.

## REGISTER 10-11: DCHxDSA: DMA CHANNEL 'x' DESTINATION START ADDRESS REGISTER

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |  |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|--|--|

| 04.04        | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |

| 31:24        |                   |                   |                   | CHDSA<            | 31:24>            |                   |                  |                  |  |  |

| 00.40        | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |

| 23:16        | CHDSA<23:16>      |                   |                   |                   |                   |                   |                  |                  |  |  |

| 45.0         | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |

| 15:8         | CHDSA<15:8>       |                   |                   |                   |                   |                   |                  |                  |  |  |

| 7.0          | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |

| 7:0          |                   |                   |                   | CHDSA             | <7:0>             |                   |                  |                  |  |  |

| Legend:           |                  |                                    |                    |  |

|-------------------|------------------|------------------------------------|--------------------|--|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read as '0' |                    |  |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared               | x = Bit is unknown |  |

bit 31-0 CHDSA<31:0>: Channel Destination Start Address bits Channel destination start address.

Note: This must be the physical address of the destination.

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5    | Bit<br>28/20/12/4    | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1       | Bit<br>24/16/8/0 |  |

|--------------|-------------------|-------------------|----------------------|----------------------|-------------------|-------------------|------------------------|------------------|--|

| 31:24        | U-0               | U-0               | U-0                  | U-0                  | U-0               | U-0               | U-0                    | U-0              |  |

| 31.24        |                   |                   | —                    |                      | —                 | —                 | —                      | —                |  |

| 23:16        | U-0               | U-0               | U-0                  | U-0                  | U-0               | U-0               | U-0                    | U-0              |  |

| 23.10        |                   |                   | —                    |                      | —                 | —                 | —                      | —                |  |

| 15:8         | U-0               | U-0               | U-0                  | U-0                  | U-0               | U-0               | U-0                    | U-0              |  |

| 15.0         | _                 | _                 | —                    | _                    | _                 |                   | —                      | _                |  |

|              | R/WC-0, HS        | R/WC-0, HS        | R/WC-0, HS           | R/WC-0, HS           | R/WC-0, HS        | R/WC-0, HS        | R/WC-0, HS             | R/WC-0, HS       |  |

| 7:0          | BTSEF             | BMXEF             | DMAEF <sup>(1)</sup> | BTOEF <sup>(2)</sup> | DFN8EF            | CRC16EF           | CRC5EF <sup>(4)</sup>  | PIDEF            |  |

|              | DIGLI             | DIVIALI           |                      | DIOLIN               |                   | ONCIULI           | EOFEF <sup>(3,5)</sup> | TIDLI            |  |

#### REGISTER 11-8: U1EIR: USB ERROR INTERRUPT STATUS REGISTER

| Legend:           | WC = Write '1' to clear | HS = Hardware Settable bit         |                    |

|-------------------|-------------------------|------------------------------------|--------------------|

| R = Readable bit  | W = Writable bit        | U = Unimplemented bit, read as '0' |                    |

| -n = Value at POR | '1' = Bit is set        | '0' = Bit is cleared               | x = Bit is unknown |

- bit 31-8 Unimplemented: Read as '0'

bit 7 BTSEF: Bit Stuff Error Flag bit 1 = Packet is rejected due to bit stuff error 0 = Packet is accepted

bit 6 BMXEF: Bus Matrix Error Flag bit 1 = Invalid base address of the BDT, or the address of an individual buffer pointed to by a BDT entry 0 = No address error

bit 5 DMAEF: DMA Error Flag bit<sup>(1)</sup> 1 = USB DMA error condition detected 0 = No DMA error

- bit 4 **BTOEF:** Bus Turnaround Time-Out Error Flag bit<sup>(2)</sup> 1 = Bus turnaround time-out has occurred

- 0 = No bus turnaround time-out

- bit 3 DFN8EF: Data Field Size Error Flag bit

1 = Data field received is not an integral number of bytes

0 = Data field received is an integral number of bytes

- bit 2 CRC16EF: CRC16 Failure Flag bit

- 1 = Data packet is rejected due to CRC16 error

0 = Data packet is accepted

- bit 1 CRC5EF: CRC5 Host Error Flag bit<sup>(4)</sup> 1 = Token packet is rejected due to CRC5 error 0 = Token packet is accepted EOFEF: EOF Error Flag bit<sup>(3,5)</sup> 1 = EOF error condition is detected

- 0 = No EOF error condition

- bit 0 PIDEF: PID Check Failure Flag bit

- 1 = PID check is failed

- 0 = PID check is passed

- **Note 1:** This type of error occurs when the module's request for the DMA bus is not granted in time to service the module's demand for memory, resulting in an overflow or underflow condition, and/or the allocated buffer size is not sufficient to store the received data packet causing it to be truncated.

- 2: This type of error occurs when more than 16-bit-times of Idle from the previous End-of-Packet (EOP) has elapsed.

- **3:** This type of error occurs when the module is transmitting or receiving data and the SOF counter has reached zero.

- 4: Device mode.

- 5: Host mode.

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|

| 04-04        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 31:24        | _                 | _                 |                   | —                 |                   |                   |                  | —                |

| 23:16        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 23.10        | _                 | _                 |                   | —                 |                   |                   |                  | —                |

| 15:8         | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 10.0         | —                 | _                 | —                 | —                 | —                 | -                 | —                | —                |

| 7:0          | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |

|              |                   |                   |                   | BDTPTR            | H<23:16>          |                   |                  |                  |

#### REGISTER 11-18: U1BDTP2: USB BUFFER DESCRIPTOR TABLE PAGE 2 REGISTER

#### Legend:

| 0                 |                  |                                    |                    |

|-------------------|------------------|------------------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read as '0' |                    |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared               | x = Bit is unknown |

#### bit 31-8 Unimplemented: Read as '0'

#### bit 7-0 BDTPTRH<23:16>: BDT Base Address bits

This 8-bit value provides address bits 23 through 16 of the BDT base address, which defines the starting location of the BDT in system memory.

The 32-bit BDT base address is 512-byte aligned.

#### REGISTER 11-19: U1BDTP3: USB BUFFER DESCRIPTOR TABLE PAGE 3 REGISTER

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|

| 31:24        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 31.24        |                   | —                 |                   | —                 |                   |                   | —                | —                |

| 22:16        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 23:16        |                   | —                 |                   | —                 |                   |                   | —                | —                |

| 15:8         | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 10.0         |                   | —                 |                   | —                 |                   |                   | —                | —                |

| 7.0          | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |

| 7:0          |                   |                   |                   | BDTPTR            | U<31:24>          |                   |                  |                  |

| Legend:           |                  |                      |                    |

|-------------------|------------------|----------------------|--------------------|

| R = Readable bit  | ead as '0'       |                      |                    |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared | x = Bit is unknown |

#### bit 31-8 Unimplemented: Read as '0'

#### bit 7-0 BDTPTRU<31:24>: BDT Base Address bits

This 8-bit value provides address bits 31 through 24 of the BDT base address, defines the starting location of the BDT in system memory.

The 32-bit BDT base address is 512-byte aligned.

## 15.1 Control Registers

## TABLE 15-1: WATCHDOG TIMER REGISTER MAP

| Bits                     |                                 |           |       |       |       |       |       |       |      |      | (2)  |      |      |           |      |      |      |        |            |

|--------------------------|---------------------------------|-----------|-------|-------|-------|-------|-------|-------|------|------|------|------|------|-----------|------|------|------|--------|------------|

| Virtual Addr<br>(BF80_#) | Register<br>Name <sup>(1)</sup> | Bit Range | 31/15 | 30/14 | 29/13 | 28/12 | 27/11 | 26/10 | 25/9 | 24/8 | 23/7 | 22/6 | 21/5 | 20/4      | 19/3 | 18/2 | 17/1 | 16/0   | All Resets |

| 0000                     | WDTOON                          | 31:16     | _     | —     | —     | —     | _     | _     | _    | _    | _    | _    | —    | —         | _    | —    | _    | _      | 0000       |

| 0000                     | WDTCON                          | 15:0      | ON    | _     |       | _     | _     | _     | _    | _    | _    |      | S    | WDTPS<4:0 | )>   |      | _    | WDTCLR | 0000       |

Legend: x = unknown value on Reset; -- = unimplemented, read as '0'. Reset values are shown in hexadecimal.

Note 1: All registers in this table have corresponding CLR, SET and INV registers at their virtual addresses, plus offsets of 0x4, 0x8 and 0xC, respectively. See Section 12.1.1 "CLR, SET and INV Registers" for more information.

2: Reset values are dependent on the DEVCFGx Configuration bits and the type of Reset.

#### REGISTER 16-1: ICxCON: INPUT CAPTURE 'x' CONTROL REGISTER (CONTINUED)

- bit 2-0 ICM<2:0>: Input Capture Mode Select bits

- 111 = Interrupt-Only mode (only supported while in Sleep mode or Idle mode)

- 110 = Simple Capture Event mode every edge, specified edge first and every edge thereafter

- 101 = Prescaled Capture Event mode every sixteenth rising edge

- 100 = Prescaled Capture Event mode every fourth rising edge

- 011 = Simple Capture Event mode every rising edge

- 010 = Simple Capture Event mode every falling edge

- 001 = Edge Detect mode every edge (rising and falling)

- 000 = Input Capture module is disabled

- **Note 1:** When using the 1:1 PBCLK divisor, the user's software should not read/write the peripheral's SFRs in the SYSCLK cycle immediately following the instruction that clears the module's ON bit.

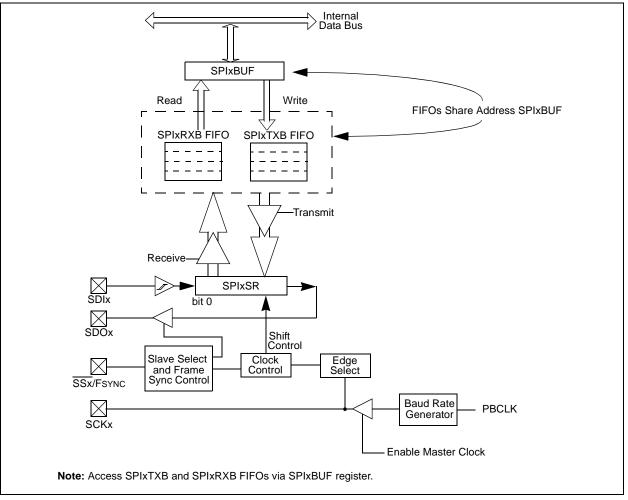

## 18.0 SERIAL PERIPHERAL INTERFACE (SPI)

Note: This data sheet summarizes the features of the PIC32MX5XX/6XX/7XX family of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to Section 23. "Serial Peripheral Interface (SPI)" (DS60001106) in the "PIC32 Family Reference Manual", which is available from the Microchip web site (www.microchip.com/PIC32).

The SPI module is a synchronous serial interface that is useful for communicating with external peripherals and other microcontroller devices. These peripheral devices may be Serial EEPROMs, Shift registers, display drivers, Analog-to-Digital Converters, etc. The PIC32 SPI module is compatible with Motorola<sup>®</sup> SPI and SIOP interfaces. The following are some of the key features of the SPI module:

- Master mode and Slave mode support

- · Four different clock formats

- Enhanced Framed SPI protocol support

- User-configurable 8-bit, 16-bit and 32-bit data width

- Separate SPI FIFO buffers for receive and transmit

FIFO buffers act as 4/8/16-level deep FIFOs

- based on 32/16/8-bit data width

Programmable interrupt event on every 8-bit, 16-bit and 32-bit data transfer

- Operation during Sleep and Idle modes

- Fast bit manipulation using CLR, SET and INV registers

## **19.1 Control Registers**

#### TABLE 19-1: I2C1THROUGH I2C5 REGISTER MAP

| ss                          |                                 |               |              |             |       |        |        |       |             | Bi         | ts    |             |              |              |               |          |          |          |            |

|-----------------------------|---------------------------------|---------------|--------------|-------------|-------|--------|--------|-------|-------------|------------|-------|-------------|--------------|--------------|---------------|----------|----------|----------|------------|

| Virtual Address<br>(BF80_#) | Register<br>Name <sup>(1)</sup> | Bit Range     | 31/15        | 30/14       | 29/13 | 28/12  | 27/11  | 26/10 | 25/9        | 24/8       | 23/7  | 22/6        | 21/5         | 20/4         | 19/3          | 18/2     | 17/1     | 16/0     | All Resets |

| 5000                        | I2C3CON                         | 31:16         | _            | _           | —     | _      |        |       | _           | _          |       |             | —            | _            | —             |          |          |          | 0000       |

|                             |                                 | 15:0          | ON           | —           | SIDL  | SCLREL | STRICT | A10M  | DISSLW      | SMEN       | GCEN  | STREN       | ACKDT        | ACKEN        | RCEN          | PEN      | RSEN     | SEN      | 1000       |

| 5010                        | I2C3STAT                        | 31:16<br>15:0 | —<br>ACKSTAT | —<br>TRSTAT |       |        | _      | BCL   | —<br>GCSTAT | —<br>ADD10 |       | –<br>I2COV  | —<br>D/A     | —<br>P       |               | —<br>R/W | —<br>RBF | —<br>TBF | 0000       |

|                             | 1000100                         | 31:16         | —            | -           | _     | _      | _      | -     |             | -          | —     | -           |              | -            | _             | -        | —        | —        | 0000       |

| 5020                        | I2C3ADD                         | 15:0          | _            | _           | _     | _      | _      | _     |             |            |       |             | ADD          | <9:0>        |               |          |          |          | 0000       |

| 5000                        | IOCOMOK                         | 31:16         | _            | _           | —     | —      | —      | _     | —           | _          | —     | _           | —            | —            | —             | _        | _        | _        | 0000       |

| 5030                        | I2C3MSK                         | 15:0          | _            | _           | —     | _      | _      |       |             |            |       |             | MSK          | <9:0>        |               |          |          |          | 0000       |

| 5040                        | I2C3BRG                         | 31:16         | _            | _           | —     | _      | _      | _     | _           | _          | -     | _           | _            | _            | _             | _        | _        | _        | 0000       |

| 5040                        | IZCODKG                         | 15:0          | _            | _           | —     | —      |        |       |             |            | Ba    | ud Rate Ger | nerator Regi | ster         |               |          |          |          | 0000       |

| 5050                        | I2C3TRN                         | 31:16         | —            | —           |       |        | —      |       |             | _          |       | —           | _            | _            | _             | —        | —        | —        | 0000       |

| 5050                        | 120311(1)                       | 15:0          | —            | —           |       |        | —      |       |             | _          |       |             | -            | Transmit     | Register      |          |          |          | 0000       |

| 5060                        | I2C3RCV                         | 31:16         | —            | —           | —     | —      | —      | _     | —           | —          | _     | —           | —            | —            | —             | —        | —        | —        | 0000       |

| 0000                        | 12001101                        | 15:0          | _            | _           | —     | _      | —      | _     | _           | —          |       |             |              | Receive      | Register      | -        | -        |          | 0000       |

| 5100                        | I2C4CON                         | 31:16         | _            | _           | —     | _      | _      | _     | _           | —          | _     | —           | _            | _            | _             | —        | —        | —        | 0000       |

|                             |                                 | 15:0          | ON           | _           | SIDL  | SCLREL | STRICT | A10M  | DISSLW      | SMEN       | GCEN  | STREN       | ACKDT        | ACKEN        | RCEN          | PEN      | RSEN     | SEN      | 1000       |

| 5110                        | I2C4STAT                        | 31:16         | —            | —           | —     |        | _      | —     | —           | _          | —     | —           |              | —            |               | —        | —        | —        | 0000       |

| L                           |                                 | 15:0          | ACKSTAT      | TRSTAT      | —     | —      | —      | BCL   | GCSTAT      | ADD10      | IWCOL | I2COV       | D/A          | Р            | S             | R/W      | RBF      | TBF      | 0000       |

| 5120                        | I2C4ADD                         | 31:16         | _            | _           | —     | _      | _      | _     | —           |            | —     | —           | —            | —            | —             | _        | _        | —        | 0000       |

|                             |                                 | 15:0          | _            | _           | _     | _      | _      |       |             |            |       |             | ADD          | <9:0>        |               |          |          |          | 0000       |

| 5130                        | I2C4MSK                         | 31:16         | _            | _           |       |        |        |       |             | _          | _     | _           |              |              |               |          | _        | _        | 0000       |

| ┢────┼                      |                                 | 15:0          |              | _           |       |        | _      |       |             |            |       |             | MSK          | <9:0>        |               |          |          |          | 0000       |

| 5140                        | I2C4BRG                         | 31:16         |              | _           | _     |        |        | —     | —           |            | -     | —           | —            | —            | —             | _        | _        | —        | 0000       |

|                             |                                 | 15:0<br>31:16 | _            | _           | _     |        |        |       |             |            |       | ud Rate Ger | erator Regi  | ster         |               |          |          |          | 0000       |

| 5150                        | I2C4TRN                         | 15:0          |              |             |       |        |        |       |             |            | _     | _           | _            | <br>Transmit | —<br>Register | —        | —        | —        | 0000       |

| ł                           |                                 | 31:16         |              |             |       |        |        |       |             |            |       |             |              |              |               | _        | _        | _        | 0000       |

| 5160                        | I2C4RCV                         | 15:0          | _            | _           |       |        |        |       |             | _          | _     |             |              | Receive      | Register      |          |          |          | 0000       |

|                             |                                 | 31:16         | _            | _           | _     | _      | _      | _     | _           | _          | _     | _           | _            | _            | _             | _        | _        | _        | 0000       |

| 5200                        | I2C5CON                         | 15:0          | ON           | _           | SIDL  | SCLREL | STRICT | A10M  | DISSLW      | SMEN       | GCEN  | STREN       | ACKDT        | ACKEN        | RCEN          | PEN      | RSEN     | SEN      | 1000       |

| 5040                        | 10050747                        | 31:16         | _            | _           | —     | —      | _      | _     | —           |            | _     | _           | —            | —            | —             | _        | _        | _        | 0000       |

| 5210                        | I2C5STAT                        | 15:0          | ACKSTAT      | TRSTAT      | —     | —      | —      | BCL   | GCSTAT      | ADD10      | IWCOL | I2COV       | D/A          | Р            | S             | R/W      | RBF      | TBF      | 0000       |

| 5000                        | 1005405                         | 31:16         | _            | _           | —     | —      | _      | —     | —           | _          | —     | _           | —            | —            | —             | _        | _        | _        | 0000       |

| 5220                        | I2C5ADD                         | 15:0          | _            | _           | _     | _      | _      | _     |             |            |       |             | ADD          | <9:0>        |               |          |          |          | 0000       |

Legend: x = unknown value on Reset; - = unimplemented, read as '0'. Reset values are shown in hexadecimal.

Note 1: All registers in this table except I2CxRCV have corresponding CLR, SET and INV registers at their virtual addresses, plus offsets of 0x4, 0x8 and 0xC, respectively. See Section 12.1.1 "CLR, SET and INV Registers" for more information.

PIC32MX5XX/6XX/7XX

2: This register is not available on 64-pin devices.

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |  |  |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|--|--|--|

| 31:24        | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |  |

| 31.24        | SID<10:3>         |                   |                   |                   |                   |                   |                  |                  |  |  |  |

| 22:16        | R/W-0             | R/W-0             | R/W-0             | U-0               | R/W-0             | U-0               | R/W-0            | R/W-0            |  |  |  |

| 23:16        |                   | SID<2:0>          |                   | —                 | MIDE              | —                 | EID<             | 17:16>           |  |  |  |

| 15:8         | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |  |

| 10.0         | EID<15:8>         |                   |                   |                   |                   |                   |                  |                  |  |  |  |

| 7.0          | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |  |

| 7:0          |                   |                   |                   | EID<7             | 7:0>              |                   |                  |                  |  |  |  |

#### REGISTER 24-9: CIRXMn: CAN ACCEPTANCE FILTER MASK 'n' REGISTER (n = 0, 1, 2 OR 3)

#### Legend:

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, r | ead as '0'         |

|-------------------|------------------|--------------------------|--------------------|

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared     | x = Bit is unknown |

bit 31-21 SID<10:0>: Standard Identifier bits

- 1 = Include the SIDx bit in filter comparison

- 0 = The SIDx bit is a 'don't care' in filter operation

- bit 20 Unimplemented: Read as '0'

- bit 19 MIDE: Identifier Receive Mode bit

- 1 = Match only message types (standard/extended address) that correspond to the EXID bit in filter

- 0 = Match either standard or extended address message if filters match (that is, if (Filter SID) = (Message SID) or if (FILTER SID/EID) = (Message SID/EID))

#### bit 18 Unimplemented: Read as '0'

bit 17-0 EID<17:0>: Extended Identifier bits

- 1 = Include the EIDx bit in filter comparison

- 0 = The EIDx bit is a 'don't care' in filter operation

**Note:** This register can only be modified when the CAN module is in Configuration mode (OPMOD<2:0> (CiCON<23:21>) = 100).

#### REGISTER 24-12: CIFLTCON2: CAN FILTER CONTROL REGISTER 2 (CONTINUED)

| bit 15    | FLTEN9: Filter 9 Enable bit<br>1 = Filter is enabled<br>0 = Filter is disabled                                                                                                    |

|-----------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| bit 14-13 | MSEL9<1:0>: Filter 9 Mask Select bits<br>11 = Acceptance Mask 3 selected<br>10 = Acceptance Mask 2 selected<br>01 = Acceptance Mask 1 selected<br>00 = Acceptance Mask 0 selected |

| bit 12-8  | FSEL9<4:0>: FIFO Selection bits<br>11111 = Message matching filter is stored in FIFO buffer 31<br>11110 = Message matching filter is stored in FIFO buffer 30                     |

|           | 00001 = Message matching filter is stored in FIFO buffer 1<br>00000 = Message matching filter is stored in FIFO buffer 0                                                          |

| bit 7     | FLTEN8: Filter 8 Enable bit<br>1 = Filter is enabled<br>0 = Filter is disabled                                                                                                    |

| bit 6-5   | MSEL8<1:0>: Filter 8 Mask Select bits<br>11 = Acceptance Mask 3 selected<br>10 = Acceptance Mask 2 selected<br>01 = Acceptance Mask 1 selected<br>00 = Acceptance Mask 0 selected |

| bit 4-0   | <pre>FSEL8&lt;4:0&gt;: FIFO Selection bits 11111 = Message matching filter is stored in FIFO buffer 31 11110 = Message matching filter is stored in FIFO buffer 30</pre>          |

Note: The bits in this register can only be modified if the corresponding filter enable (FLTENn) bit is '0'.

### REGISTER 24-17: CIFLTCON7: CAN FILTER CONTROL REGISTER 7 (CONTINUED)

| bit 15    | FLTEN29: Filter 29 Enable bit<br>1 = Filter is enabled<br>0 = Filter is disabled                                                                                               |

|-----------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| bit 14-13 | MSEL29<1:0>: Filter 29 Mask Select bits                                                                                                                                        |

|           | <ul> <li>11 = Acceptance Mask 3 selected</li> <li>10 = Acceptance Mask 2 selected</li> <li>01 = Acceptance Mask 1 selected</li> <li>00 = Acceptance Mask 0 selected</li> </ul> |

| bit 12-8  | FSEL29<4:0>: FIFO Selection bits                                                                                                                                               |

|           | 11111 = Message matching filter is stored in FIFO buffer 31                                                                                                                    |

|           | 11110 = Message matching filter is stored in FIFO buffer 30                                                                                                                    |

|           | •                                                                                                                                                                              |

|           |                                                                                                                                                                                |

|           | 00001 = Message matching filter is stored in FIFO buffer 1<br>00000 = Message matching filter is stored in FIFO buffer 0                                                       |

| bit 7     | FLTEN28: Filter 28 Enable bit                                                                                                                                                  |

|           | <ul><li>1 = Filter is enabled</li><li>0 = Filter is disabled</li></ul>                                                                                                         |

| bit 6-5   | MSEL28<1:0>: Filter 28 Mask Select bits                                                                                                                                        |

|           | 11 = Acceptance Mask 3 selected                                                                                                                                                |

|           | 10 = Acceptance Mask 2 selected                                                                                                                                                |

|           | 01 = Acceptance Mask 1 selected<br>00 = Acceptance Mask 0 selected                                                                                                             |

| bit 4-0   | FSEL28<4:0>: FIFO Selection bits                                                                                                                                               |

|           | 11111 = Message matching filter is stored in FIFO buffer 31                                                                                                                    |

|           | 11110 = Message matching filter is stored in FIFO buffer 30                                                                                                                    |

|           | •                                                                                                                                                                              |

|           |                                                                                                                                                                                |

|           | 00001 = Message matching filter is stored in FIFO buffer 1                                                                                                                     |

|           | 00000 = Message matching filter is stored in FIFO buffer 0                                                                                                                     |

| Note:     | The bits in this register can only be modified if the corresponding filter enable (FLTENn) bit is '0'.                                                                         |

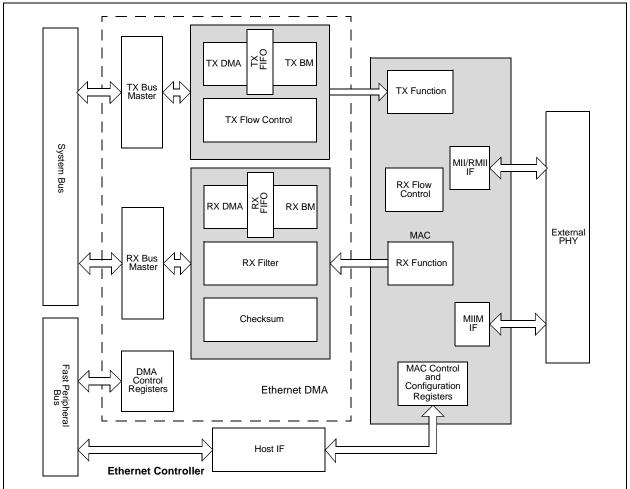

## 25.0 ETHERNET CONTROLLER

Note: This data sheet summarizes the features of the PIC32MX5XX/6XX/7XX family of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to Section 35. "Ethernet Controller" (DS60001155) in the "PIC32 Family Reference Manual", which is available from the Microchip web site (www.microchip.com/PIC32).

The Ethernet controller is a bus master module that interfaces with an off-chip Physical Layer (PHY) to implement a complete Ethernet node in a system.

Key features of the Ethernet Controller include:

- Supports 10/100 Mbps data transfer rates

- Supports full-duplex and half-duplex operation

- Supports RMII and MII PHY interface

- Supports MIIM PHY management interface

- Supports both manual and automatic Flow Control

- RAM descriptor-based DMA operation for both receive and transmit path

- · Fully configurable interrupts

- Configurable receive packet filtering

- CRC check

- 64-byte pattern match

- Broadcast, multicast and unicast packets

- Magic Packet™

- 64-bit hash table

- Runt packet

- Supports packet payload checksum calculation

- · Supports various hardware statistics counters

Figure 25-1 illustrates a block diagram of the Ethernet controller.

#### FIGURE 25-1: ETHERNET CONTROLLER BLOCK DIAGRAM

| Bit<br>Range | Bit<br>31/23/15/7      | Bit<br>30/22/14/6     | Bit<br>29/21/13/5     | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |  |  |

|--------------|------------------------|-----------------------|-----------------------|-------------------|-------------------|-------------------|------------------|------------------|--|--|--|

| 31:24        | U-0                    | U-0                   | U-0                   | U-0               | U-0               | U-0               | U-0              | U-0              |  |  |  |

| 31.24        | —                      |                       | _                     | _                 | _                 | _                 | _                | _                |  |  |  |

| 23:16        | R/W-0                  | R/W-0                 | R/W-0                 | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |  |

| 23.10        | BUFCNT<7:0>            |                       |                       |                   |                   |                   |                  |                  |  |  |  |

| 15:8         | U-0                    | U-0                   | U-0                   | U-0               | U-0               | U-0               | U-0              | U-0              |  |  |  |

| 15.0         | —                      |                       | _                     | _                 | _                 | _                 | _                | _                |  |  |  |

| 7.0          | R/W-0                  | R/W-0                 | R/W-0                 | U-0               | U-0               | U-0               | U-0              | U-0              |  |  |  |

| 7:0          | ETHBUSY <sup>(1)</sup> | TXBUSY <sup>(2)</sup> | RXBUSY <sup>(2)</sup> | —                 |                   | _                 |                  | _                |  |  |  |

## REGISTER 25-15: ETHSTAT: ETHERNET CONTROLLER STATUS REGISTER

## Legend:

| Legena.           |                  |                       |                    |

|-------------------|------------------|-----------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit | , read as '0'      |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared  | x = Bit is unknown |

#### bit 31-24 Unimplemented: Read as '0'

#### bit 23-16 **BUFCNT<7:0>:** Packet Buffer Count bits

Number of packet buffers received in memory. Once a packet has been successfully received, this register is incremented by hardware based on the number of descriptors used by the packet. Software decrements the counter (by writing to the BUFCDEC bit (ETHCON1<0>) for each descriptor used) after a packet has been read out of the buffer. The register does not roll over (0xFF to 0x00) when hardware tries to increment the register and the register is already at 0xFF. Conversely, the register does not roll under (0x00 to 0xFF) when software tries to decrement the register and the register is already at 0x000. When software attempts to decrement the same time that the hardware attempts to increment the counter, the counter value will remain unchanged.

When this register value reaches 0xFF, the RX logic will halt (only if automatic Flow Control is enabled) awaiting software to write the BUFCDEC bit in order to decrement the register below 0xFF.

If automatic Flow Control is disabled, the RXDMA will continue processing and the BUFCNT will saturate at a value of 0xFF.

When this register is non-zero, the PKTPEND status bit will be set and an interrupt may be generated, depending on the value of the ETHIEN bit <PKTPENDIE> register.

When the ETHRXST register is written, the BUFCNT counter is automatically cleared to 0x00.

- **Note:** BUFCNT will not be cleared when ON is set to '0'. This enables software to continue to utilize and decrement this count.

- bit 15-8 **Unimplemented:** Read as '0'

- bit 7 ETHBUSY: Ethernet Module busy bit<sup>(1)</sup>

1 = Ethernet logic has been turned on (ON (ETHCON1<15>) = 1) or is completing a transaction 0 = Ethernet logic is idle

This bit indicates that the module has been turned on or is completing a transaction after being turned off.

- bit 6 **TXBUSY:** Transmit Busy bit<sup>(2)</sup>

- 1 = TX logic is receiving data

- 0 = TX logic is idle

This bit indicates that a packet is currently being transmitted. A change in this status bit is not necessarily reflected by the TXDONE interrupt, as TX packets may be aborted or rejected by the MAC.

- **Note 1:** This bit will be *set* when the ON bit (ETHCON1<15>) = 1.

- **2:** This bit will be *cleared* when the ON bit (ETHCON1<15>) = 0.

#### REGISTER 25-25: EMAC1IPGT: ETHERNET CONTROLLER MAC BACK-TO-BACK INTERPACKET GAP REGISTER

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|

| 31:24        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 31.24        | —                 | —                 | _                 | _                 | _                 | —                 | —                | _                |

| 22:16        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 23:16        | —                 | —                 | —                 | _                 | _                 | —                 | _                | —                |

| 45.0         | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 15:8         |                   | _                 | _                 | _                 | _                 | —                 | _                | _                |

| 7.0          | U-0               | R/W-0             | R/W-0             | R/W-1             | R/W-0             | R/W-0             | R/W-1            | R/W-0            |

| 7:0          | _                 |                   |                   | B2                | BIPKTGP<6:(       | )>                |                  |                  |

#### Legend:

| Logona.           |                  |                        |                    |

|-------------------|------------------|------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, | read as '0'        |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared   | x = Bit is unknown |

#### bit 31-7 Unimplemented: Read as '0'

#### bit 6-0 B2BIPKTGP<6:0>: Back-to-Back Interpacket Gap bits

This is a programmable field representing the nibble time offset of the minimum possible period between the end of any transmitted packet, to the beginning of the next. In Full-Duplex mode, the register value should be the desired period in nibble times minus 3. In Half-Duplex mode, the register value should be the desired period in nibble times minus 6. In Full-Duplex the recommended setting is 0x15 (21d), which represents the minimum IPG of 0.96  $\mu$ s (in 100 Mbps) or 9.6  $\mu$ s (in 10 Mbps). In Half-Duplex mode, the recommended setting is 0x12 (18d), which also represents the minimum IPG of 0.96  $\mu$ s (in 100 Mbps) or 9.6  $\mu$ s (in 100 Mbps) (in 100 Mbps) or 9.6  $\mu$ s (in 100 Mbps) (in 100 Mbps) (in 100 Mbps) or 9.6  $\mu$ s (in 100 Mbps) (in

**Note:** Both 16-bit and 32-bit accesses are allowed to these registers (including the SET, CLR and INV registers). 8-bit accesses are not allowed and are ignored by the hardware.

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5   | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

|--------------|-------------------|-------------------|---------------------|-------------------|-------------------|-------------------|------------------|------------------|

| 31:24        | U-0               | U-0               | U-0                 | U-0               | U-0               | U-0               | U-0              | U-0              |

| 31.24        |                   | —                 |                     | _                 | _                 | _                 | _                | _                |

| 23:16        | U-0               | U-0               | U-0                 | U-0               | U-0               | U-0               | U-0              | U-0              |

| 23.10        | —                 | —                 | —                   | -                 | —                 | —                 | —                | —                |

| 15.0         | R/W-0             | R/W-0             | R/W-0               | U-0               | U-0               | U-0               | U-0              | R-0              |

| 15:8         | 0N <sup>(1)</sup> | COE               | CPOL <sup>(2)</sup> | -                 | —                 | —                 | —                | COUT             |

| 7:0          | R/W-1             | R/W-1             | U-0                 | R/W-0             | U-0               | U-0               | R/W-1            | R/W-1            |

| 7.0          | EVPOL<1:0>        |                   |                     | CREF              | _                 |                   | CCH              | <1:0>            |

#### REGISTER 26-1: CMxCON: COMPARATOR 'x' CONTROL REGISTER

#### Legend:

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, re | ead as '0'         |

|-------------------|------------------|---------------------------|--------------------|

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared      | x = Bit is unknown |

#### bit 31-16 Unimplemented: Read as '0'

bit 15 ON: Comparator ON bit<sup>(1)</sup>

Clearing this bit does not affect the other bits in this register.

- 1 = Module is enabled. Setting this bit does not affect the other bits in this register

- 0 = Module is disabled and does not consume current.

- bit 14 COE: Comparator Output Enable bit

- 1 = Comparator output is driven on the output CxOUT pin

- 0 = Comparator output is not driven on the output CxOUT pin

- bit 13 **CPOL:** Comparator Output Inversion bit<sup>(2)</sup>

- 1 = Output is inverted

- 0 = Output is not inverted

#### bit 12-9 Unimplemented: Read as '0'

- bit 8 COUT: Comparator Output bit

- 1 =Output of the Comparator is a '1'

- 0 = Output of the Comparator is a '0'

- bit 7-6 EVPOL<1:0>: Interrupt Event Polarity Select bits

- 11 = Comparator interrupt is generated on a low-to-high or high-to-low transition of the comparator output

- 10 = Comparator interrupt is generated on a high-to-low transition of the comparator output

- 01 = Comparator interrupt is generated on a low-to-high transition of the comparator output

- 00 = Comparator interrupt generation is disabled

#### bit 5 Unimplemented: Read as '0'

- bit 4 **CREF:** Comparator Positive Input Configure bit

- 1 = Comparator non-inverting input is connected to the internal CVREF

- 0 = Comparator non-inverting input is connected to the CxIN+ pin

- bit 3-2 Unimplemented: Read as '0'

- bit 1-0 **CCH<1:0>:** Comparator Negative Input Select bits for Comparator

- 11 = Comparator inverting input is connected to the IVREF

- 10 = Comparator inverting input is connected to the C2IN+ pin for C1 and C1IN+ pin for C2

- 01 = Comparator inverting input is connected to the C1IN+ pin for C1 and C2IN+ pin for C2

- 00 = Comparator inverting input is connected to the C1IN- pin for C1 and C2IN- pin for C2

- **Note 1:** When using the 1:1 PBCLK divisor, the user's software should not read/write the peripheral's SFRs in the SYSCLK cycle immediately following the instruction that clears the module's ON bit.

- 2: Setting this bit will invert the signal to the comparator interrupt generator as well. This will result in an interrupt being generated on the opposite edge from the one selected by EVPOL<1:0>.

## 29.0 SPECIAL FEATURES

Note: This data sheet summarizes the features of the PIC32MX5XX/6XX/7XX family of devices. However, it is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to Section 33. "Programming and Diagnostics" (DS60001129) in the "PIC32 Family Reference Manual", which are available from the Microchip web site (www.microchip.com/PIC32).

The PIC32MX5XX/6XX/7XX family of devices include several features intended to maximize application flexibility and reliability and minimize cost through elimination of external components. Key features include:

- Flexible device configuration

- Watchdog Timer (WDT)

- Joint Test Action Group (JTAG) interface

- In-Circuit Serial Programming<sup>™</sup> (ICSP<sup>™</sup>)

## 29.1 Configuration Bits

The Configuration bits can be programmed using the following registers to select various device configurations.

- DEVCFG0: Device Configuration Word 0

- DEVCFG1: Device Configuration Word 1

- DEVCFG2: Device Configuration Word 2

- DEVCFG3: Device Configuration Word 3

- DEVID: Device and Revision ID Register

## APPENDIX B: REVISION HISTORY

## **Revision A (August 2009)**

This is the initial released version of this document.

## **Revision B (November 2009)**

The revision includes the following global update:

Added Note 2 to the shaded table that appears at the beginning of each chapter. This new note provides information regarding the availability of registers and their associated bits.

Other major changes are referenced by their respective chapter/section in Table B-1.

| Section Name                                                                  | Update Description                                                                                                                                                       |

|-------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| "High-Performance, USB, CAN and<br>Ethernet 32-bit Flash<br>Microcontrollers" | Added the following devices:<br>- PIC32MX575F256L<br>- PIC32MX695F512L                                                                                                   |

|                                                                               | <ul> <li>PIC32MX695F512H</li> <li>The 100-pin TQFP pin diagrams have been updated to reflect the current pin name locations (see the "Pin Diagrams" section).</li> </ul> |

|                                                                               | Added the 121-pin Ball Grid Array (XBGA) pin diagram.                                                                                                                    |

|                                                                               | Updated Table 1: "PIC32 USB and CAN – Features"                                                                                                                          |

|                                                                               | Added the following tables:                                                                                                                                              |

|                                                                               | <ul> <li>Table 4: "Pin Names: PIC32MX534F064L, PIC32MX564F064L,<br/>PIC32MX564F128L, PIC32MX575F256L and PIC32MX575F512L<br/>Devices"</li> </ul>                         |

|                                                                               | <ul> <li>Table 5: "Pin Names: PIC32MX664F064L, PIC32MX664F128L,<br/>PIC32MX675F256L, PIC32MX675F512L and PIC32MX695F512L<br/>Devices"</li> </ul>                         |

|                                                                               | <ul> <li>Table 6: "Pin Names: PIC32MX775F256L, PIC32MX775F512L and<br/>PIC32MX795F512L Devices"</li> </ul>                                                               |

|                                                                               | Updated the following pins as 5V tolerant:                                                                                                                               |

|                                                                               | - 64-pin QFN: Pin 36 (D-/RG3) and Pin 37 (D+/RG2)                                                                                                                        |

|                                                                               | <ul> <li>64-pin TQFP: Pin 36 (D-/RG3) and Pin 37 (D+/RG2)</li> <li>100-pin TQFP: Pin 56 (D-/RG3) and Pin 57 (D+/RG2)</li> </ul>                                          |

| 1.0 "Guidelines for Getting Started with 32-bit Microcontrollers"             | Removed the last sentence of 1.3.1 "Internal Regulator Mode".                                                                                                            |

|                                                                               | Removed Section 2.3.2 "External Regulator Mode"                                                                                                                          |

#### TABLE B-1: MAJOR SECTION UPDATES

## **Revision J (September 2016)**

This revision includes typographical and formatting updates throughout the data sheet text. In addition, all SFR Register maps were moved from the Memory chapter to their respective peripheral chapters.

All other major updates are referenced by their respective section in Table B-7.

| Section Name                                                                     | Update Description                                                                                                      |

|----------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------|

| "32-bit Microcontrollers (up to 512                                              | Updated Communication Interfaces for LIN support to 2.1.                                                                |

| KB Flash and 128 KB SRAM) with<br>Graphics Interface, USB, CAN, and<br>Ethernet" | Updated Qualification and Class B Support to AEC-Q100 REVH.                                                             |

| 2.0 "Guidelines for Getting Started with 32-bit MCUs"                            | The Recommended Minimum Connection diagram was updated (see Figure 2-1).                                                |

|                                                                                  | The Example of MCLR Pin Connections diagram was updated (see Figure 2-<br>2).                                           |

|                                                                                  | 2.11 "EMI/EMC/EFT (IEC 61000-4-4 and IEC 61000-4-2) Suppression Considerations" was added.                              |

| 4.0 "Memory Organization"                                                        | The SFR Memory Map was added (see Table 4-1).                                                                           |

| 7.0 "Interrupt Controller"                                                       | The UART interrupt sources were updated in the Interrupt IRQ, Vector, and Bit location table (see Table 7-1).           |

| 8.0 "Oscillator Configuration"                                                   | Updated the bit value definitions for the TUN<5:0> bits in the OCSTUN register (see Register 8-2).                      |

| 15.0 "Watchdog Timer (WDT)"                                                      | The content in this chapter was relocated from the Special Features chapter to its own chapter.                         |

| 18.0 "Serial Peripheral Interface (SPI)"                                         | The register map tables were combined (see Table 18-1).                                                                 |

| 19.0 "Inter-Integrated Circuit (I <sup>2</sup> C)"                               | The register map tables were combined (see Table 19-1).                                                                 |

|                                                                                  | The PMADDR register was updated (see Register 21-3).                                                                    |

| 21.0 "Parallel Master Port (PMP)"                                                | The bit value definitions for the ADRMUX<1:0> and CSF<1:0> bits in the PMCON register were updated (see Register 21-1). |

| 29.0 "Special Features"                                                          | Removed the duplicate bit value definition for '010' in the DEVCFG2 register (see Register 29-3).                       |

|                                                                                  | Note 1 was added to the Programming, Debugging, and Trace Ports block diagram (see Figure 29-2).                        |

|                                                                                  | The DDPCON register was relocated (see Register 29-6).                                                                  |

|                                                                                  | The Device ID, Revision, and Configuration Summary was updated (see Table 29-2).                                        |