Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFl

| 2 014110                   |                                                                                |

|----------------------------|--------------------------------------------------------------------------------|

| Product Status             | Active                                                                         |

| Core Processor             | MIPS32® M4K™                                                                   |

| Core Size                  | 32-Bit Single-Core                                                             |

| Speed                      | 80MHz                                                                          |

| Connectivity               | Ethernet, I <sup>2</sup> C, SPI, UART/USART, USB OTG                           |

| Peripherals                | Brown-out Detect/Reset, DMA, POR, PWM, WDT                                     |

| Number of I/O              | 53                                                                             |

| Program Memory Size        | 128KB (128K x 8)                                                               |

| Program Memory Type        | FLASH                                                                          |

| EEPROM Size                | · ·                                                                            |

| RAM Size                   | 32K x 8                                                                        |

| Voltage - Supply (Vcc/Vdd) | 2.3V ~ 3.6V                                                                    |

| Data Converters            | A/D 16x10b                                                                     |

| Oscillator Type            | Internal                                                                       |

| Operating Temperature      | -40°C ~ 105°C (TA)                                                             |

| Mounting Type              | Surface Mount                                                                  |

| Package / Case             | 64-VFQFN Exposed Pad                                                           |

| Supplier Device Package    | 64-VQFN (9x9)                                                                  |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic32mx664f128h-v-mr |

|                            |                                                                                |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

|                  | USB and Ethernet |                         |                  |     |          |                        |                                          |                       |                    |                                 |                              |             |         |      |       |                         |

|------------------|------------------|-------------------------|------------------|-----|----------|------------------------|------------------------------------------|-----------------------|--------------------|---------------------------------|------------------------------|-------------|---------|------|-------|-------------------------|

| Device           | Pins             | Program Memory (KB)     | Data Memory (KB) | USB | Ethernet | Timers/Capture/Compare | DMA Channels<br>(Programmable/Dedicated) | UART <sup>(2,3)</sup> | SPI <sup>(3)</sup> | I <sup>2</sup> C <sup>(3)</sup> | 10-bit 1 Msps ADC (Channels) | Comparators | dSP/PMP | JTAG | Trace | Packages <sup>(4)</sup> |

| PIC32MX664F064H  | 64               | 64 + 12 <sup>(1)</sup>  | 32               | 1   | 1        | 5/5/5                  | 4/4                                      | 6                     | 3                  | 4                               | 16                           | 2           | Yes     | Yes  | No    | PT,<br>MR               |

| PIC32MX664F128H  | 64               | 128 + 12 <sup>(1)</sup> | 32               | 1   | 1        | 5/5/5                  | 4/4                                      | 6                     | 3                  | 4                               | 16                           | 2           | Yes     | Yes  | No    | PT,<br>MR               |

| PIC32MX675F256H  | 64               | 256 + 12 <sup>(1)</sup> | 64               | 1   | 1        | 5/5/5                  | 8/4                                      | 6                     | 3                  | 4                               | 16                           | 2           | Yes     | Yes  | No    | PT,<br>MR               |

| PIC32MX675F512H  | 64               | 512 + 12 <sup>(1)</sup> | 64               | 1   | 1        | 5/5/5                  | 8/4                                      | 6                     | 3                  | 4                               | 16                           | 2           | Yes     | Yes  | No    | PT,<br>MR               |

| PIC32MX695F512H  | 64               | 512 + 12 <sup>(1)</sup> | 128              | 1   | 1        | 5/5/5                  | 8/4                                      | 6                     | 3                  | 4                               | 16                           | 2           | Yes     | Yes  | No    | PT,<br>MR               |

| PIC32MX664F064L  | 100              | 64 + 12 <sup>(1)</sup>  | 32               | 1   | 1        | 5/5/5                  | 4/4                                      | 6                     | 4                  | 5                               | 16                           | 2           | Yes     | Yes  | Yes   | PT, PF,<br>BG           |

| PIC32MX664F128L  | 100              | 128 + 12 <sup>(1)</sup> | 32               | 1   | 1        | 5/5/5                  | 4/4                                      | 6                     | 4                  | 5                               | 16                           | 2           | Yes     | Yes  | Yes   | PT, PF,<br>BG           |

| PIC32MX675F256L  | 100              | 256 + 12 <sup>(1)</sup> | 64               | 1   | 1        | 5/5/5                  | 8/4                                      | 6                     | 4                  | 5                               | 16                           | 2           | Yes     | Yes  | Yes   | PT, PF,<br>BG           |

| PIC32MX675F512L  | 100              | 512 + 12 <sup>(1)</sup> | 64               | 1   | 1        | 5/5/5                  | 8/4                                      | 6                     | 4                  | 5                               | 16                           | 2           | Yes     | Yes  | Yes   | PT, PF,<br>BG, TL       |

| PIC32MX695F512L  | 100              | 512 + 12 <sup>(1)</sup> | 128              | 1   | 1        | 5/5/5                  | 8/4                                      | 6                     | 4                  | 5                               | 16                           | 2           | Yes     | Yes  | Yes   | PT, PF,<br>BG, TL       |

| Legend: PF, PT = | TQFP             | MR = QF                 | N                |     | BG =     | TFBGA                  | 4                                        | TL =                  | VTL/               | ų( <del>5</del> )               |                              |             |         |      |       |                         |

| TABLE 2: PIC32MX6XX USB AND ETHERNET FEATURES |

|-----------------------------------------------|

|-----------------------------------------------|

Legend: PF, PT = TQFP MR = QFN BG = Note 1: This device features 12 KB boot Flash memory.

2: CTS and RTS pins may not be available for all UART modules. Refer to the "Device Pin Tables" section for more information.

3: Some pins between the UART, SPI and I<sup>2</sup>C modules may be shared. Refer to the "Device Pin Tables" section for more information.

4: Refer to 34.0 "Packaging Information" for more information.

5: 100-pin devices other than those listed here are available in the VTLA package upon request. Please contact your local Microchip Sales Office for details.

L11

### TABLE 10: PIN NAMES (CONTINUED)FOR USB AND CAN DEVICES

#### 121-PIN TFBGA (BOTTOM VIEW)

PIC32MX534F064L PIC32MX564F064L PIC32MX564F128L PIC32MX575F256L PIC32MX575F512L

L1

A11

Note: The TFBGA package skips from row "H" to row "J" and has no "I" row. A1

| Pin # | Full Pin Name             |

|-------|---------------------------|

| J3    | PGED2/AN7/RB7             |

| J4    | AVdd                      |

| J5    | AN11/PMA12/RB11           |

| J6    | TCK/RA1                   |

| J7    | AN12/PMA11/RB12           |

| J8    | No Connect (NC)           |

| J9    | No Connect (NC)           |

| J10   | SCL3/SDO3/U1TX/RF8        |

| J11   | D-/RG3                    |

| K1    | PGEC1/AN1/CN3/RB1         |

| K2    | PGED1/AN0/CN2/RB0         |

| K3    | VREF+/CVREF+/PMA6/RA10    |

| K4    | AN8/C1OUT/RB8             |

| K5    | No Connect (NC)           |

| K6    | AC1RX/SS4/U5RX/U2CTS/RF12 |

| K7    | AN14/PMALH/PMA1/RB14      |

| Pin # | Full Pin Name                  |

|-------|--------------------------------|

| K8    | Vdd                            |

| K9    | SCK3/U4TX/U1RTS/CN21/RD15      |

| K10   | USBID/RF3                      |

| K11   | SDA3/SDI3/U1RX/RF2             |

| L1    | PGEC2/AN6/OCFA/RB6             |

| L2    | VREF-/CVREF-/PMA7/RA9          |

| L3    | AVss                           |

| L4    | AN9/C2OUT/RB9                  |

| L5    | AN10/CVREFOUT/PMA13/RB10       |

| L6    | AC1TX/SCK4/U5TX/U2RTS/RF13     |

| L7    | AN13/PMA10/RB13                |

| L8    | AN15/OCFB/PMALL/PMA0/CN12/RB15 |

| L9    | SS3/U4RX/U1CTS/CN20/RD14       |

| L10   | SDA5/SDI4/U2RX/PMA9/CN17/RF4   |

| L11   | SCL5/SDO4/U2TX/PMA8/CN18/RF5   |

Note 1: Shaded pins are 5V tolerant.

#### **TABLE 13:** PIN NAMES FOR 124-PIN USB, ETHERNET, AND CAN DEVICES (CONTINUED)

| 124               | 4-PIN VTLA (BOTTOM VIEW) <sup>(2,3)</sup>             |     |                   | A34                       |                           |  |

|-------------------|-------------------------------------------------------|-----|-------------------|---------------------------|---------------------------|--|

|                   |                                                       | B13 | B29               |                           | Conductive<br>Thermal Pad |  |

|                   | PIC32MX675F512L<br>PIC32MX695F512L<br>PIC32MX795F512L | B1  | B56               | B41                       | A51                       |  |

|                   | A1                                                    |     |                   |                           |                           |  |

|                   | Polarity Indicator                                    |     | A68               |                           |                           |  |

| Package<br>Bump # | Full Pin Name                                         |     | Package<br>Bump # | F                         | ull Pin Name              |  |

| B8                | Vss                                                   |     | B33               | TDO/RA5                   |                           |  |

| B9                | TMS/RA0                                               |     | B34               | OSC1/CLKI/RC              | 212                       |  |

| B10               | AERXD1/INT2/RE9                                       |     | B35               | No Connect (N             | C)                        |  |

| B11               | AN4/C1IN-/CN6/RB4                                     |     | B36               | AETXCLK/SCL               | .1/INT3/RA14              |  |

| B12               | Vss                                                   |     | B37               | RTCC/EMDIO/               | AEMDIO/IC1/RD8            |  |

| B13               | AN2/C2IN-/CN4/RB2                                     |     | B38               | SCK1/IC3/PMC              | CS2/PMA15/RD10            |  |

| B14               | PGED1/AN0/CN2/RB0                                     |     | B39               | SDO1/OC1/INT              | [0/RD0                    |  |

| B15               | No Connect (NC)                                       |     | B40               | SOSCO/T1CK/               | CN0/RC14                  |  |

| B16               | PGED2/AN7/RB7                                         |     | B41               | Vss                       |                           |  |

| B17               | VREF+/CVREF+/AERXD3/PMA6/RA10                         |     | B42               | OC3/RD2                   |                           |  |

| B18               | AVss                                                  |     | B43               | ETXD2/IC5/PN              | ID12/RD12                 |  |

| B19               | AN9/C2OUT/RB9                                         |     | B44               | OC5/PMWR/CI               | N13/RD4                   |  |

| B20               | AN11/ERXERR/AETXERR/PMA12/RB11                        |     | B45               | ETXEN/PMD14               | 4/CN15/RD6                |  |

| B21               | Vdd                                                   |     | B46               | Vss                       |                           |  |

| B22               | AC1TX/SCK4/U5TX/U2RTS/RF13                            |     | B47               | No Connect (N             | C)                        |  |

| B23               | AN12/ERXD0/AECRS/PMA11/RB12                           |     | B48               | VCAP                      |                           |  |

| B24               | AN14/ERXD2/AETXD3/PMALH/PMA1/RB14                     |     | B49               | C1RX <sup>(1)</sup> /ETXD | 1/PMD11/RF0               |  |

| B25               | Vss                                                   |     | B50               | C2TX <sup>(1)</sup> /ETXE | RR/PMD9/RG1               |  |

| B26               | AETXD0/SS3/U4RX/U1CTS/CN20/RD14                       |     | B51               | TRCLK/RA6                 |                           |  |

| B27               | SDA5/SDI4/U2RX/PMA9/CN17/RF4                          |     | B52               | PMD0/RE0                  |                           |  |

| B28               | No Connect (NC)                                       |     | B53               | Vdd                       |                           |  |

| B29               | SCL3/SDO3/U1TX/RF8                                    |     | B54               | TRD2/RG14                 |                           |  |

| B30               | VUSB3V3                                               |     | B55               | TRD0/RG13                 |                           |  |

| B31               | D+/RG2                                                |     | B56               | PMD3/RE3                  |                           |  |

This pin is only available on PIC32MX795F512L devices. Note 1:

2:

Shaded package bumps are 5V tolerant. It is recommended that the user connect the printed circuit board (PCB) ground to the conductive thermal pad on the bottom of the package. And to not run non-Vss PCB traces under the conductive thermal pad on the same side of the PCB layout. 3:

### **Referenced Sources**

This device data sheet is based on the following individual chapters of the *"PIC32 Family Reference Manual"*. These documents should be considered as the general reference for the operation of a particular module or device feature.

- Note 1: To access the documents listed below, browse to the documentation section of the PIC32MX795F512L product page on the Microchip web site (www.microchip.com) or select a family reference manual section from the following list. In addition to parameters, features, and other documentation, the resulting page provides links to the related family

- Section 1. "Introduction" (DS60001127)

- Section 2. "CPU" (DS60001113)

- Section 4. "Prefetch Cache" (DS60001119)

- Section 3. "Memory Organization" (DS60001115)

reference manual sections.

- Section 5. "Flash Program Memory" (DS60001121)

- Section 6. "Oscillator Configuration" (DS60001112)

- Section 7. "Resets" (DS60001118)

- Section 8. "Interrupt Controller" (DS60001108)

- Section 9. "Watchdog Timer and Power-up Timer (DS60001114)

- Section 10. "Power-Saving Features" (DS60001130)

- Section 12. "I/O Ports" (DS60001120)

- Section 13. "Parallel Master Port (PMP)" (DS60001128)

- Section 14. "Timers" (DS60001105)

- Section 15. "Input Capture" (DS60001122)

- Section 16. "Output Capture" (DS60001111)

- Section 17. "10-bit Analog-to-Digital Converter (ADC)" (DS60001104)

- Section 19. "Comparator" (DS60001110)

- Section 20. "Comparator Voltage Reference (CVREF)" (DS60001109)

- Section 21. "Universal Asynchronous Receiver Transmitter (UART)" (DS60001107)

- Section 23. "Serial Peripheral Interface (SPI)" (DS60001106)

- Section 24. "Inter-Integrated Circuit (I2C)" (DS60001116)

- Section 27. "USB On-The-Go (OTG)" (DS60001126)

- Section 29. "Real-Time Clock and Calendar (RTCC)" (DS60001125)

- Section 31. "Direct Memory Access (DMA) Controller" (DS60001117)

- Section 32. "Configuration" (DS60001124)

- Section 33. "Programming and Diagnostics" (DS60001129)

- Section 34. "Controller Area Network (CAN)" (DS60001154)

- Section 35. "Ethernet Controller" (DS60001155)

| AECRS  | 64-Pin<br>QFN/TQFP | 100-Pin                  |                                                      |                                                        | Pin  | Buffer |                                                                                    |  |  |

|--------|--------------------|--------------------------|------------------------------------------------------|--------------------------------------------------------|------|--------|------------------------------------------------------------------------------------|--|--|

|        |                    | TQFP                     | 121-Pin<br>TFBGA                                     | 124-pin<br>VTLA                                        | Туре | Туре   | Description                                                                        |  |  |

|        |                    | 41                       | J7                                                   | B23                                                    | I    | ST     | Alternate Ethernet carrier sense <sup>(2)</sup>                                    |  |  |

| AEMDC  | 30                 | 71                       | C11                                                  | A46                                                    | 0    |        | Alternate Ethernet Management Data clock <sup>(2)</sup>                            |  |  |

| AEMDIO | 49                 | 68                       | E9                                                   | B37                                                    | I/O  |        | Alternate Ethernet Management Data <sup>(2</sup>                                   |  |  |

| TRCLK  | _                  | 91                       | C5                                                   | B51                                                    | 0    |        | Trace clock                                                                        |  |  |

| TRD0   |                    | 97                       | A3                                                   | B55                                                    | 0    | _      | Trace Data bits 0-3                                                                |  |  |

| TRD1   | _                  | 96                       | C3                                                   | A65                                                    | 0    | _      |                                                                                    |  |  |

| TRD2   | _                  | 95                       | C4                                                   | B54                                                    | 0    | _      |                                                                                    |  |  |

| TRD3   | _                  | 92                       | B5                                                   | A62                                                    | 0    |        |                                                                                    |  |  |

| PGED1  | 16                 | 25                       | K2                                                   | B14                                                    | I/O  | ST     | Data I/O pin for Programming/<br>Debugging Communication Channel 1                 |  |  |

| PGEC1  | 15                 | 24                       | K1                                                   | A15                                                    | I    | ST     | Clock input pin for Programming/<br>Debugging Communication Channel 1              |  |  |

| PGED2  | 18                 | 27                       | J3                                                   | B16                                                    | I/O  | ST     | Data I/O pin for Programming/<br>Debugging Communication Channel 2                 |  |  |

| PGEC2  | 17                 | 26                       | L1                                                   | A20                                                    | Ι    | ST     | Clock input pin for Programming/<br>Debugging Communication Channel 2              |  |  |

| MCLR   | 7                  | 13                       | F1                                                   | B7                                                     | I/P  | ST     | Master Clear (Reset) input. This pin is an active-low Reset to the device.         |  |  |

| AVdd   | 19                 | 30                       | J4                                                   | A22                                                    | Р    | Р      | Positive supply for analog modules.<br>This pin must be connected at all times     |  |  |

| AVss   | 20                 | 31                       | L3                                                   | B18                                                    | Р    | Р      | Ground reference for analog modules                                                |  |  |

| Vdd    | 10, 26, 38,<br>57  | 2, 16, 37,<br>46, 62, 86 | A7, C2,<br>C9, E5,<br>K8, F8,<br>G5, H4,<br>H6       | A10, A14,<br>A30, A41,<br>A48, A59,<br>B1, B21,<br>B53 | Ρ    | _      | Positive supply for peripheral logic and I/O pins                                  |  |  |

| VCAP   | 56                 | 85                       | B7                                                   | B48                                                    | Р    |        | Capacitor for Internal Voltage Regulato                                            |  |  |

| Vss    | 9, 25, 41          | 15, 36, 45,<br>65, 75    | A8, B10,<br>D4, D5,<br>E7, F5,<br>F10, G6,<br>G7, H3 | A3, A25,<br>A43, A63,<br>B8, B12,<br>B25, B41,<br>B46  | Ρ    | _      | Ground reference for logic and I/O pins<br>This pin must be connected at all times |  |  |

| Vref+  | 16                 | 29                       | K3                                                   | B17                                                    | I    | Analog | Analog voltage reference (high) input                                              |  |  |

| Vref-  | 15                 | 28                       | L2                                                   | A21                                                    | I    | Analog | Analog voltage reference (low) input                                               |  |  |

## TABLE 1-1: PINOUT I/O DESCRIPTIONS (CONTINUED)

TTL = TTL input buffer

Note 1: Pin numbers are only provided for reference. See the "Device Pin Tables" section for device pin availability.

2: See 25.0 "Ethernet Controller" for more information.

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0     |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|----------------------|

| 24.24        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0                  |

| 31:24        | —                 | _                 | _                 | —                 | _                 | _                 | -                | —                    |

| 22.16        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0                  |

| 23:16        | -                 | _                 | _                 | —                 | _                 | _                 | _                | —                    |

| 45.0         | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0                  |

| 15:8         | _                 | _                 | _                 | —                 | _                 | _                 | _                | —                    |

| 7.0          | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | W-0, HC              |

| 7:0          |                   | _                 | _                 | —                 | —                 |                   |                  | SWRST <sup>(1)</sup> |

#### REGISTER 6-2: RSWRST: SOFTWARE RESET REGISTER

| Le   | gend:          | HC = Cleared by hardware |                                    |                    |  |  |  |  |

|------|----------------|--------------------------|------------------------------------|--------------------|--|--|--|--|

| R =  | = Readable bit | W = Writable bit         | U = Unimplemented bit, read as '0' |                    |  |  |  |  |

| -n : | = Value at POR | '1' = Bit is set         | '0' = Bit is cleared               | x = Bit is unknown |  |  |  |  |

bit 31-1 Unimplemented: Read as '0'

- bit 0 SWRST: Software Reset Trigger bit<sup>(1)</sup> 1 = Enable software Reset event 0 = No effect

- Note 1: The system unlock sequence must be performed before the SWRST bit can be written. Refer to Section 6. "Oscillator" (DS60001112) in the "PIC32 Family Reference Manual" for details.

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|

| 24.24        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 31:24        |                   |                   | _                 | —                 | -                 | _                 | _                | _                |

| 23:16        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | R/W-0            |

| 23.10        | —                 | —                 | —                 | —                 | _                 | —                 | —                | SS0              |

| 45.0         | U-0               | U-0               | U-0               | R/W-0             | U-0               | R/W-0             | R/W-0            | R/W-0            |

| 15:8         | _                 | —                 | —                 | MVEC              | _                 | TPC<2:0>          |                  |                  |

| 7.0          | U-0               | U-0               | U-0               | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |

| 7:0          |                   |                   | _                 | INT4EP            | INT3EP            | INT2EP            | INT1EP           | INT0EP           |

#### REGISTER 7-1: INTCON: INTERRUPT CONTROL REGISTER

#### Legend:

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, re | ad as '0'          |

|-------------------|------------------|---------------------------|--------------------|

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared      | x = Bit is unknown |

#### bit 31-17 Unimplemented: Read as '0'

- bit 16 **SS0:** Single Vector Shadow Register Set bit

- 1 = Single vector is presented with a shadow register set

- 0 = Single vector is not presented with a shadow register set

- bit 15-13 Unimplemented: Read as '0'

- bit 12 MVEC: Multiple Vector Configuration bit

- 1 = Interrupt controller configured for Multi-vector mode

- 0 = Interrupt controller configured for Single-vector mode

- bit 11 Unimplemented: Read as '0'

- bit 10-8 TPC<2:0>: Interrupt Proximity Timer Control bits

- 111 = Interrupts of group priority 7 or lower start the Interrupt Proximity timer 110 = Interrupts of group priority 6 or lower start the Interrupt Proximity timer 101 = Interrupts of group priority 5 or lower start the Interrupt Proximity timer 100 = Interrupts of group priority 4 or lower start the Interrupt Proximity timer 011 = Interrupts of group priority 3 or lower start the Interrupt Proximity timer

- 010 = Interrupts of group priority 2 or lower start the Interrupt Proximity timer

- 001 = Interrupts of group priority 1 start the Interrupt Proximity timer

- 000 = Disables Interrupt Proximity timer

- bit 7-5 Unimplemented: Read as '0'

- bit 4 INT4EP: External Interrupt 4 Edge Polarity Control bit

- 1 = Rising edge

- 0 = Falling edge

- bit 3 INT3EP: External Interrupt 3 Edge Polarity Control bit

- 1 = Rising edge

- 0 = Falling edge

- bit 2 INT2EP: External Interrupt 2 Edge Polarity Control bit

- 1 = Rising edge

- 0 = Falling edge

- bit 1 **INT1EP:** External Interrupt 1 Edge Polarity Control bit

- 1 = Rising edge

- 0 = Falling edge

- bit 0 INTOEP: External Interrupt 0 Edge Polarity Control bit

- 1 = Rising edge

- 0 = Falling edge

# PIC32MX5XX/6XX/7XX

## REGISTER 10-18: DCHxDAT: DMA CHANNEL 'x' PATTERN DATA REGISTER

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|

| 24.24        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 31:24        | —                 | -                 |                   | —                 | —                 | _                 | —                | —                |

| 23:16        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 23.10        | —                 |                   |                   |                   | —                 |                   | —                | —                |

| 45.0         | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 15:8         | —                 | _                 | _                 | _                 | —                 | _                 | —                | —                |

| 7.0          | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |

| 7:0          |                   |                   |                   | CHPDAT            | [<7:0>            |                   |                  |                  |

## Legend:

| 5                 |                  |                          |                    |

|-------------------|------------------|--------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, r | ead as '0'         |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared     | x = Bit is unknown |

#### bit 31-8 Unimplemented: Read as '0'

bit 7-0 **CHPDAT<7:0>:** Channel Data Register bits <u>Pattern Terminate mode:</u> Data to be matched must be stored in this register to allow terminate on match.

> All other modes: Unused.

## 11.0 USB ON-THE-GO (OTG)

Note: This data sheet summarizes the features of the PIC32MX5XX/6XX/7XX family of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to Section 27. "USB On-The-Go (OTG)" (DS60001126) in the "PIC32 Family Reference Manual", which is available from the Microchip web site (www.microchip.com/PIC32).

The Universal Serial Bus (USB) module contains analog and digital components to provide a USB 2.0 full-speed and low-speed embedded Host, full-speed Device or OTG implementation with a minimum of external components. This module in Host mode is intended for use as an embedded host and therefore does not implement a UHCI or OHCI controller.

The USB module consists of the clock generator, the USB voltage comparators, the transceiver, the Serial Interface Engine (SIE), a dedicated USB DMA controller, pull-up and pull-down resistors, and the register interface. A block diagram of the PIC32 USB OTG module is presented in Figure 11-1.

The clock generator provides the 48 MHz clock required for USB full-speed and low-speed communication. The voltage comparators monitor the voltage on the VBUS pin to determine the state of the bus. The transceiver provides the analog translation between the USB bus and the digital logic. The SIE is a state machine that transfers data to and from the endpoint buffers and generates the hardware protocol for data transfers. The USB DMA controller transfers data between the data buffers in RAM and the SIE. The integrated pull-up and pull-down resistors eliminate the need for external signaling components. The register interface allows the CPU to configure and communicate with the module.

The USB module includes the following features:

- USB Full-speed support for host and device

- Low-speed host support

- USB OTG support

- Integrated signaling resistors

- Integrated analog comparators for VBUS monitoring

- Integrated USB transceiver

- Transaction handshaking performed by hardware

- Endpoint buffering anywhere in system RAM

- Integrated DMA to access system RAM and Flash

- The implementation and use of the USB Note: specifications, as well as other third party may specifications or technologies, require licensing; including, but not limited to, USB Implementers Forum, Inc. (also referred to as USB-IF). The user is fully responsible for investigating and satisfying any applicable licensing obligations.

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|

| 31:24        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 31.24        |                   | —                 |                   |                   |                   | —                 |                  | —                |

| 22.16        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 23:16        |                   | _                 |                   |                   |                   | _                 |                  | _                |

| 15.0         | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 15:8         |                   | _                 |                   |                   |                   | _                 |                  | _                |

| 7:0          | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | U-0              | R/W-0            |

| 7.0          | IDIE              | T1MSECIE          | LSTATEIE          | ACTVIE            | SESVDIE           | SESENDIE          |                  | VBUSVDIE         |

#### REGISTER 11-2: U10TGIE: USB OTG INTERRUPT ENABLE REGISTER

#### Legend:

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, re | ead as '0'         |

|-------------------|------------------|---------------------------|--------------------|

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared      | x = Bit is unknown |

#### bit 31-8 Unimplemented: Read as '0'

- bit 7 IDIE: ID Interrupt Enable bit

- 1 = ID interrupt enabled

- 0 = ID interrupt disabled

- bit 6 T1MSECIE: 1 Millisecond Timer Interrupt Enable bit

- 1 = 1 millisecond timer interrupt enabled

- 0 = 1 millisecond timer interrupt disabled

- bit 5 LSTATEIE: Line State Interrupt Enable bit

- 1 = Line state interrupt enabled

- 0 = Line state interrupt disabled

- bit 4 ACTVIE: Bus ACTIVITY Interrupt Enable bit

- 1 = ACTIVITY interrupt enabled

- 0 = ACTIVITY interrupt disabled

- bit 3 SESVDIE: Session Valid Interrupt Enable bit

- 1 = Session valid interrupt enabled

- 0 = Session valid interrupt disabled

- bit 2 SESENDIE: B-Session End Interrupt Enable bit

- 1 = B-session end interrupt enabled

- 0 = B-session end interrupt disabled

- bit 1 Unimplemented: Read as '0'

- bit 0 **VBUSVDIE:** A-VBUS Valid Interrupt Enable bit

- 1 = A-VBUS valid interrupt enabled

- 0 = A-VBUS valid interrupt disabled

| Bit<br>Range | Bit<br>31/23/15/7   | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

|--------------|---------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|

| 04.04        | U-0                 | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 31:24        |                     |                   |                   | -                 | _                 |                   | _                | —                |

| 00.40        | U-0                 | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 23:16        | _                   | _                 | _                 |                   | _                 | —                 | _                | —                |

| 45.0         | R/W-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 15:8         | ON <sup>(1,2)</sup> |                   | _                 | —                 | —                 | —                 | —                | —                |

| 7.0          | U-0                 | R-y               | R-y               | R-y               | R-y               | R-y               | R/W-0            | R/W-0            |

| 7:0          | _                   |                   | S                 | WDTWINEN          | WDTCLR            |                   |                  |                  |

#### REGISTER 15-1: WDTCON: WATCHDOG TIMER CONTROL REGISTER

| Legend:           | y = Values set from Configuration bits on POR |                                    |                    |  |  |

|-------------------|-----------------------------------------------|------------------------------------|--------------------|--|--|

| R = Readable bit  | W = Writable bit                              | U = Unimplemented bit, read as '0' |                    |  |  |

| -n = Value at POR | '1' = Bit is set                              | '0' = Bit is cleared               | x = Bit is unknown |  |  |

bit 31-16 Unimplemented: Read as '0'

bit 0

- bit 15 **ON:** Watchdog Timer Enable bit<sup>(1,2)</sup>

- 1 = Enables the WDT if it is not enabled by the device configuration 0 = Disable the WDT if it was enabled in software

- bit 14-7 **Unimplemented:** Read as '0'

- bit 6-2 **SWDTPS<4:0>:** Shadow Copy of Watchdog Timer Postscaler Value from Device Configuration bits On reset, these bits are set to the values of the WDTPS <4:0> Configuration bits.

- bit 1 WDTWINEN: Watchdog Timer Window Enable bit

- 1 = Enable windowed Watchdog Timer

- 0 = Disable windowed Watchdog Timer

- WDTCLR: Watchdog Timer Reset bit

- 1 = Writing a '1' will clear the WDT

- 0 = Software cannot force this bit to a '0'

- Note 1: A read of this bit results in a '1' if the Watchdog Timer is enabled by the device configuration or software.

- 2: When using the 1:1 PBCLK divisor, the user's software should not read or write the peripheral's SFRs in the SYSCLK cycle immediately following the instruction that clears the module's ON bit.

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3                        | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

|--------------|-------------------|-------------------|-------------------|-------------------|------------------------------------------|-------------------|------------------|------------------|

| 04-04        | R/W-x             | R/W-x             | R/W-x             | R/W-x             | R/W-x                                    | R/W-x             | R/W-x            | R/W-x            |

| 31:24        |                   | HR10-             | <3:0>             |                   |                                          | HR01              | <3:0>            |                  |

| 00.40        | R/W-x             | R/W-x             | R/W-x             | R/W-x             | R/W-x                                    | R/W-x             | R/W-x            | R/W-x            |

| 23:16        | MIN10<3:0>        |                   |                   |                   | MIN01<3:0>                               |                   |                  |                  |

| 45.0         | R/W-x             | R/W-x             | R/W-x             | R/W-x             | R/W-x                                    | R/W-x             | R/W-x            | R/W-x            |

| 15:8         |                   | SEC10             | <3:0>             |                   | SEC01<3:0>                               |                   |                  |                  |

| 7.0          | U-0               | U-0               | U-0               | U-0               | U-0                                      | U-0               | U-0              | U-0              |

| 7:0          | —                 | —                 | _                 | _                 | —                                        | _                 | —                | _                |

|              |                   |                   |                   |                   |                                          |                   |                  |                  |

| Legend:      |                   |                   |                   |                   |                                          |                   |                  |                  |

| R = Read     | able bit          |                   | W = Writable      | e bit             | U = Unimplemented bit, read as '0'       |                   |                  |                  |

| -n = Value   | e at POR          |                   | '1' = Bit is se   | t                 | 0' = Bit is cleared $x = Bit is unknown$ |                   |                  | known            |

## REGISTER 22-5: ALRMTIME: ALARM TIME VALUE REGISTER

bit 31-28 HR10<3:0>: Binary Coded Decimal value of hours bits, 10 digits; contains a value from 0 to 2

bit 27-24 HR01<3:0>: Binary Coded Decimal value of hours bits, 1 digit; contains a value from 0 to 9

bit 23-20 MIN10<3:0>: Binary Coded Decimal value of minutes bits, 10 digits; contains a value from 0 to 5

bit 19-16 MIN01<3:0>: Binary Coded Decimal value of minutes bits, 1 digit; contains a value from 0 to 9

bit 15-12 SEC10<3:0>: Binary Coded Decimal value of seconds bits, 10 digits; contains a value from 0 to 5

bit 11-8 SEC01<3:0>: Binary Coded Decimal value of seconds bits, 1 digit; contains a value from 0 to 9

bit 7-0 Unimplemented: Read as '0'

| REGISTER 23-2: AD1CON2: ADC CONTROL REGISTER 2 |

|------------------------------------------------|

|------------------------------------------------|

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|

| 24.24        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 31:24        | —                 | —                 | —                 | —                 | —                 | —                 | —                | —                |

| 00.40        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 23:16        |                   |                   | —                 | _                 | —                 | —                 | —                | —                |

| 45.0         | R/W-0             | R/W-0             | R/W-0             | R/W-0             | U-0               | R/W-0             | U-0              | U-0              |

| 15:8         | VCFG<2:0>         |                   |                   | OFFCAL            | —                 | CSCNA             | —                | —                |

| 7.0          | R-0               | U-0               | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |

| 7:0          | BUFS              | _                 |                   | SMP               | l<3:0>            |                   | BUFM             | ALTS             |

#### Legend:

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, re | ad as '0'          |

|-------------------|------------------|---------------------------|--------------------|

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared      | x = Bit is unknown |

#### bit 31-16 Unimplemented: Read as '0'

bit 15-13 VCFG<2:0>: Voltage Reference Configuration bits

| Bit Value | VREFH              | VREFL              |  |  |

|-----------|--------------------|--------------------|--|--|

| lxx       | AVdd               | AVss               |  |  |

| 011       | External VREF+ pin | External VREF- pin |  |  |

| 010       | AVdd               | External VREF- pin |  |  |

| 001       | External VREF+ pin | AVss               |  |  |

| 000       | AVDD               | AVss               |  |  |

#### bit 12 **OFFCAL:** Input Offset Calibration Mode Select bit

1 = Enable Offset Calibration mode

Positive and negative inputs of the S&H circuit are connected to VREFL.

0 = Disable Offset Calibration mode

The inputs to the S&H circuit are controlled by AD1CHS or AD1CSSL.

#### bit 11 Unimplemented: Read as '0'

- bit 10 **CSCNA:** Input Scan Select bit

- 1 = Scan inputs

0 = Do not scan inputs

- bit 9-8 Unimplemented: Read as '0'

- bit 7 BUFS: Buffer Fill Status bit

- Only valid when BUFM = 1.

- 1 = ADC is currently filling buffer 0x8-0xF, user should access data in 0x0-0x7

- 0 = ADC is currently filling buffer 0x0-0x7, user should access data in 0x8-0xF

#### bit 6 Unimplemented: Read as '0'

#### bit 5-2 SMPI<3:0>: Sample/Convert Sequences Per Interrupt Selection bits

- 1111 = Interrupts at the completion of conversion for each 16<sup>th</sup> sample/convert sequence 1110 = Interrupts at the completion of conversion for each 15<sup>th</sup> sample/convert sequence

- 1110 = Interrupts at the completion of conversion for each 15" sample/convert sequence

- •

0001 = Interrupts at the completion of conversion for each 2<sup>nd</sup> sample/convert sequence 0000 = Interrupts at the completion of conversion for each sample/convert sequence

- bit 1 BUFM: ADC Result Buffer Mode Select bit

- 1 = Buffer configured as two 8-word buffers, ADC1BUF7-ADC1BUF0, ADC1BUFF-ADCBUF8

- 0 = Buffer configured as one 16-word buffer ADC1BUFF-ADC1BUF0

- bit 0 ALTS: Alternate Input Sample Mode Select bit

- 1 = Uses Sample A input multiplexer settings for first sample, and then alternates between Sample B and Sample A input multiplexer settings for all subsequent samples

- 0 = Always use Sample A input multiplexer settings

## PIC32MX5XX/6XX/7XX

| Bit Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

|-----------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|

| 31:24     | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |

| 31.24     | FLTEN3            | MSEL3<1:0>        |                   | FSEL3<4:0>        |                   |                   |                  |                  |

| 22.46     | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |

| 23:16     | FLTEN2            | MSEL2<1:0>        |                   | FSEL2<4:0>        |                   |                   |                  |                  |

| 15.0      | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |

| 15:8      | FLTEN1            | MSEL1<1:0>        |                   | I:0> FSEL1<4:0>   |                   |                   |                  |                  |

| 7:0       | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |

|           | FLTEN0            | MSEL              | 0<1:0>            | FSEL0<4:0>        |                   |                   |                  |                  |

#### REGISTER 24-10: CIFLTCON0: CAN FILTER CONTROL REGISTER 0

#### Legend:

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read as '0' |                    |

|-------------------|------------------|------------------------------------|--------------------|

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared               | x = Bit is unknown |

| bit 31    | FLTEN3: Filter 3 Enable bit                                 |

|-----------|-------------------------------------------------------------|

|           | 1 = Filter is enabled                                       |

|           | 0 = Filter is disabled                                      |

| bit 30-29 | MSEL3<1:0>: Filter 3 Mask Select bits                       |

|           | 11 = Acceptance Mask 3 selected                             |

|           | 10 = Acceptance Mask 2 selected                             |

|           | 01 = Acceptance Mask 1 selected                             |

|           | 00 = Acceptance Mask 0 selected                             |

| bit 28-24 | FSEL3<4:0>: FIFO Selection bits                             |

|           | 11111 = Message matching filter is stored in FIFO buffer 31 |

|           | 11110 = Message matching filter is stored in FIFO buffer 30 |

|           | •                                                           |

|           | •                                                           |

|           | 00001 = Message matching filter is stored in FIFO buffer 1  |

|           | 00000 = Message matching filter is stored in FIFO buffer 0  |

| bit 23    | FLTEN2: Filter 2 Enable bit                                 |

|           | 1 = Filter is enabled                                       |

|           | 0 = Filter is disabled                                      |

| bit 22-21 | MSEL2<1:0>: Filter 2 Mask Select bits                       |

|           | 11 = Acceptance Mask 3 selected                             |

|           | 10 = Acceptance Mask 2 selected                             |

|           | 01 = Acceptance Mask 1 selected                             |

|           | 00 = Acceptance Mask 0 selected                             |

| bit 20-16 | FSEL2<4:0>: FIFO Selection bits                             |

|           | 11111 = Message matching filter is stored in FIFO buffer 31 |

|           | 11110 = Message matching filter is stored in FIFO buffer 30 |

|           | •                                                           |

|           | •                                                           |

|           | 00001 = Message matching filter is stored in FIFO buffer 1  |

|           | 00000 = Message matching filter is stored in FIFO buffer 0  |

|           |                                                             |

Note: The bits in this register can only be modified if the corresponding filter enable (FLTENn) bit is '0'.

## **REGISTER 24-21:** CiFIFOINTn: CAN FIFO INTERRUPT REGISTER 'n' (n = 0 THROUGH 31)

- bit 9 TXHALFIF: FIFO Transmit FIFO Half Empty Interrupt Flag bit<sup>(1)</sup> TXEN = 1: (FIFO configured as a transmit buffer) 1 = FIFO is  $\leq$  half full 0 = FIFO is > half full TXEN = 0: (FIFO configured as a receive buffer) Unused, reads '0' bit 8 **TXEMPTYIF:** Transmit FIFO Empty Interrupt Flag bit<sup>(1)</sup> TXEN = 1: (FIFO configured as a transmit buffer) 1 = FIFO is empty 0 = FIFO is not empty, at least 1 message queued to be transmitted TXEN = 0: (FIFO configured as a receive buffer) Unused, reads '0' bit 7-4 Unimplemented: Read as '0' bit 3 **RXOVFLIF:** Receive FIFO Overflow Interrupt Flag bit TXEN = 1: (FIFO configured as a transmit buffer) Unused, reads '0' TXEN = 0: (FIFO configured as a receive buffer) 1 = Overflow event has occurred 0 = No overflow event occuredbit 2 **RXFULLIF:** Receive FIFO Full Interrupt Flag bit<sup>(1)</sup> TXEN = 1: (FIFO configured as a transmit buffer) Unused, reads '0' TXEN = 0: (FIFO configured as a receive buffer) 1 = FIFO is full 0 = FIFO is not full RXHALFIF: Receive FIFO Half Full Interrupt Flag bit<sup>(1)</sup> bit 1 TXEN = 1: (FIFO configured as a transmit buffer) Unused, reads '0' TXEN = 0: (FIFO configured as a receive buffer) 1 = FIFO is  $\geq$  half full 0 = FIFO is < half full bit 0 **RXNEMPTYIF:** Receive Buffer Not Empty Interrupt Flag bit<sup>(1)</sup> TXEN = 1: (FIFO configured as a transmit buffer) Unused, reads '0' TXEN = 0: (FIFO configured as a receive buffer) 1 = FIFO is not empty, has at least 1 message 0 = FIFO is empty

- Note 1: This bit is read-only and reflects the status of the FIFO.

## REGISTER 25-16: ETHRXOVFLOW: ETHERNET CONTROLLER RECEIVE OVERFLOW STATISTICS REGISTER

| Bit Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |  |

|-----------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|--|--|

| 04-04     | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |  |  |

| 31:24     | -                 | —                 | _                 | —                 | _                 | _                 | _                | —                |  |  |

| 00.46     | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |  |  |

| 23:16     | _                 | —                 | _                 | _                 | _                 | —                 | —                | —                |  |  |

| 45.0      | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |

| 15:8      | RXOVFLWCNT<15:8>  |                   |                   |                   |                   |                   |                  |                  |  |  |

| 7.0       | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |

| 7:0       | RXOVFLWCNT<7:0>   |                   |                   |                   |                   |                   |                  |                  |  |  |

## Legend:

| Logona.                           |                  |                                    |                    |  |  |  |

|-----------------------------------|------------------|------------------------------------|--------------------|--|--|--|

| R = Readable bit W = Writable bit |                  | U = Unimplemented bit, read as '0' |                    |  |  |  |

| -n = Value at POR                 | '1' = Bit is set | '0' = Bit is cleared               | x = Bit is unknown |  |  |  |

#### bit 31-16 Unimplemented: Read as '0'

bit 15-0 **RXOVFLWCNT<15:0>:** Dropped Receive Frames Count bits Increment counter for frames accepted by the RX filter and subsequently dropped due to internal receive error (RXFIFO overrun). This event also sets the RXOVFLW bit (ETHIRQ<0>) interrupt flag.

**Note 1:** This register is only used for RX operations.

- 2: This register is automatically cleared by hardware after a read operation, unless the byte enables for bytes 0/1 are '0'.

- **3:** It is recommended to use the SET, CLR, or INV registers to set or clear any bit in this register. Setting or clearing any bits in this register should only be done for debug/test purposes.

## 28.0 POWER-SAVING FEATURES

Note: This data sheet summarizes the features of the PIC32MX5XX/6XX/7XX family of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to Section 10. "Power-Saving Features" (DS60001130) in the "PIC32 Family Reference Manual", which is available from the Microchip web site (www.microchip.com/PIC32).

This section describes power-saving features for the PIC32MX5XX/6XX/7XX family of devices. These devices offer a total of nine methods and modes, organized into two categories, that allow the user to balance power consumption with device performance. In all of the methods and modes described in this section, power-saving is controlled by software.

## 28.1 Power-Saving with CPU Running

When the CPU is running, power consumption can be controlled by reducing the CPU clock frequency, lowering the Peripheral Bus Clock (PBCLK) and by individually disabling modules. These methods are grouped into the following categories:

- FRC Run mode: the CPU is clocked from the FRC clock source with or without postscalers.

- LPRC Run mode: the CPU is clocked from the LPRC clock source.

- Sosc Run mode: the CPU is clocked from the Sosc clock source.

In addition, the Peripheral Bus Scaling mode is available where peripherals are clocked at the programmable fraction of the CPU clock (SYSCLK).

## 28.2 CPU Halted Methods

The device supports two power-saving modes, Sleep and Idle, both of which Halt the clock to the CPU. These modes operate with all clock sources, as listed below:

- **Posc Idle mode:** the system clock is derived from the Posc. The system clock source continues to operate. Peripherals continue to operate, but can optionally be individually disabled.

- FRC Idle mode: the system clock is derived from the FRC with or without postscalers. Peripherals continue to operate, but can optionally be individually disabled.

- **Sosc Idle mode:** the system clock is derived from the Sosc. Peripherals continue to operate, but can optionally be individually disabled.

- LPRC Idle mode: the system clock is derived from the LPRC. Peripherals continue to operate, but can optionally be individually disabled. This is the lowest power mode for the device with a clock running.

- Sleep mode: the CPU, the system clock source and any peripherals that operate from the system clock source are Halted. Some peripherals can operate in Sleep using specific clock sources. This is the lowest power mode for the device.

## 28.3 Power-Saving Operation

Peripherals and the CPU can be halted or disabled to further reduce power consumption.

#### 28.3.1 SLEEP MODE

Sleep mode has the lowest power consumption of the device power-saving operating modes. The CPU and most peripherals are halted. Select peripherals can continue to operate in Sleep mode and can be used to wake the device from Sleep. See the individual peripheral module sections for descriptions of behavior in Sleep.

Sleep mode includes the following characteristics:

- The CPU is halted

- The system clock source is typically shutdown. See Section 28.3.3 "Peripheral Bus Scaling Method" for specific information.

- There can be a wake-up delay based on the oscillator selection

- The Fail-Safe Clock Monitor (FSCM) does not operate during Sleep mode

- The BOR circuit, if enabled, remains operative during Sleep mode

- The WDT, if enabled, is not automatically cleared prior to entering Sleep mode

- Some peripherals can continue to operate at limited functionality in Sleep mode. These peripherals include I/O pins that detect a change in the input signal, WDT, ADC, UART and peripherals that use an external clock input or the internal LPRC oscillator (e.g., RTCC, Timer1 and Input Capture).

- I/O pins continue to sink or source current in the same manner as they do when the device is not in Sleep

- Modules can be individually disabled by software prior to entering Sleep in order to further reduce consumption

#### REGISTER 29-3: DEVCFG2: DEVICE CONFIGURATION WORD 2 (CONTINUED)

- bit 2-0 **FPLLIDIV<2:0>:** PLL Input Divider bits

- 111 = 12x divider

- 110 = 10x divider

- 101 = 6x divider

- 100 = 5x divider

- 011 = 4x divider

- 010 = 3x divider

- 001 = 2x divider

- 000 = 1x divider

## TABLE 32-18: PLL CLOCK TIMING SPECIFICATIONS (VDD = 2.3V TO 3.6V)

| AC CHARACTERISTICS |                                     |                                                                     | Standard Operating Conditions: 2.3V to 3.6V(unless otherwise stated)Operating temperature $-40^{\circ}C \le TA \le +85^{\circ}C$ for Industrial $-40^{\circ}C \le TA \le +105^{\circ}C$ for V-Temp |       |         |       |       |                                      |

|--------------------|-------------------------------------|---------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------|---------|-------|-------|--------------------------------------|

| Param.<br>No.      | Param.<br>No. Symbol Characteristic |                                                                     | ics <sup>(1)</sup>                                                                                                                                                                                 | Min.  | Typical | Max.  | Units | Conditions                           |

| OS50               | Fplli                               | PLL Voltage Controlled<br>Oscillator (VCO) Input<br>Frequency Range |                                                                                                                                                                                                    | 3.92  | _       | 5     | MHz   | ECPLL, HSPLL, XTPLL,<br>FRCPLL modes |

| OS51               | Fsys                                | On-Chip VCO System<br>Frequency                                     |                                                                                                                                                                                                    | 60    | _       | 120   | MHz   | _                                    |

| OS52               | TLOCK                               | PLL Start-up Time (Lock Time)                                       |                                                                                                                                                                                                    | _     | _       | 2     | ms    | —                                    |

| OS53               | DCLK                                | CLKO Stability <sup>(2)</sup><br>(Period Jitter or Cumulative)      |                                                                                                                                                                                                    | -0.25 |         | +0.25 | %     | Measured over 100 ms<br>period       |

Note 1: These parameters are characterized, but not tested in manufacturing.

2: This jitter specification is based on clock-cycle by clock-cycle measurements. To get the effective jitter for individual time-bases on communication clocks, use the following formula:

$$EffectiveJitter = \frac{D_{CLK}}{\sqrt{\frac{SYSCLK}{CommunicationClock}}}$$

For example, if SYSCLK = 80 MHz and SPI bit rate = 20 MHz, the effective jitter is as follows:

$$EffectiveJitter = \frac{D_{CLK}}{\sqrt{\frac{80}{20}}} = \frac{D_{CLK}}{2}$$

### TABLE 32-19: INTERNAL FRC ACCURACY

| AC CHARACTERISTICS                                                                            |                 | Standard Operating Conditions: 2.3V to 3.6V(unless otherwise stated)Operating temperature $-40^{\circ}C \le TA \le +85^{\circ}C$ for Industrial $-40^{\circ}C \le TA \le +105^{\circ}C$ for V-Temp |         |      |       |            |  |  |

|-----------------------------------------------------------------------------------------------|-----------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------|------|-------|------------|--|--|

| Param.<br>No.                                                                                 | Characteristics |                                                                                                                                                                                                    | Typical | Max. | Units | Conditions |  |  |

| Internal FRC Accuracy @ 8.00 MHz <sup>(1)</sup> for PIC32MX575/675/695/775/795 Family Devices |                 |                                                                                                                                                                                                    |         |      |       |            |  |  |

| F20a                                                                                          | FRC             | -2                                                                                                                                                                                                 | —       | +2   | %     | —          |  |  |

| Internal FRC Accuracy @ 8.00 MHz <sup>(1)</sup> for PIC32MX534/564/664/764 Family Devices     |                 |                                                                                                                                                                                                    |         |      |       |            |  |  |

| F20b                                                                                          | FRC             | -0.9                                                                                                                                                                                               | —       | +0.9 | %     | —          |  |  |

Note 1: Frequency calibrated at 25°C and 3.3V. The TUN bits can be used to compensate for temperature drift.

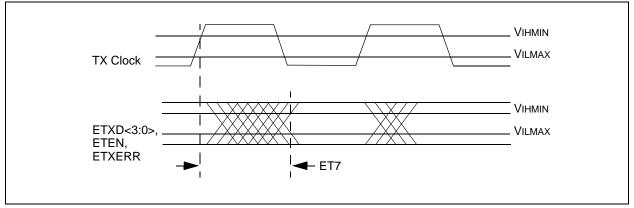

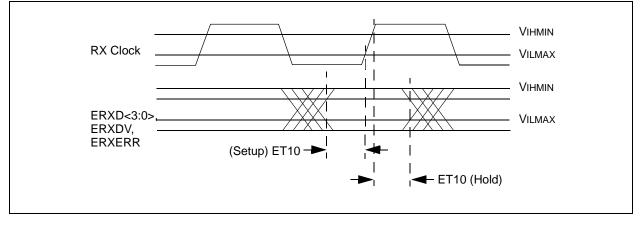

#### FIGURE 32-21: TRANSMIT SIGNAL TIMING RELATIONSHIPS AT THE MII