Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFl

| 2 014110                   |                                                                                 |

|----------------------------|---------------------------------------------------------------------------------|

| Product Status             | Active                                                                          |

| Core Processor             | MIPS32® M4K™                                                                    |

| Core Size                  | 32-Bit Single-Core                                                              |

| Speed                      | 80MHz                                                                           |

| Connectivity               | Ethernet, I <sup>2</sup> C, SPI, UART/USART, USB OTG                            |

| Peripherals                | Brown-out Detect/Reset, DMA, POR, PWM, WDT                                      |

| Number of I/O              | 53                                                                              |

| Program Memory Size        | 128KB (128K x 8)                                                                |

| Program Memory Type        | FLASH                                                                           |

| EEPROM Size                |                                                                                 |

| RAM Size                   | 32K x 8                                                                         |

| Voltage - Supply (Vcc/Vdd) | 2.3V ~ 3.6V                                                                     |

| Data Converters            | A/D 16x10b                                                                      |

| Oscillator Type            | Internal                                                                        |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                               |

| Mounting Type              | Surface Mount                                                                   |

| Package / Case             | 64-VFQFN Exposed Pad                                                            |

| Supplier Device Package    | 64-VQFN (9x9)                                                                   |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic32mx664f128ht-i-mr |

|                            |                                                                                 |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# PIC32MX5XX/6XX/7XX

## TABLE 1-1: PINOUT I/O DESCRIPTIONS (CONTINUED)

|          |                                              | Pin Nun         | nber <sup>(1)</sup> |                 | Pin         | Buffer               |                                                                                                |  |  |  |

|----------|----------------------------------------------|-----------------|---------------------|-----------------|-------------|----------------------|------------------------------------------------------------------------------------------------|--|--|--|

| Pin Name | 64-Pin<br>QFN/TQFP                           | 100-Pin<br>TQFP | 121-Pin<br>TFBGA    | 124-pin<br>VTLA | Ріп<br>Туре | Type                 | Description                                                                                    |  |  |  |

| TMS      | 23                                           | 17              | G3                  | B9              | I           | ST                   | JTAG Test mode select pin                                                                      |  |  |  |

| ТСК      | 27                                           | 38              | J6                  | A26             | I           | ST                   | JTAG test clock input pin                                                                      |  |  |  |

| TDI      | 28                                           | 60              | G11                 | A40             | I           | ST                   | JTAG test data input pin                                                                       |  |  |  |

| TDO      | 24                                           | 61              | G9                  | B33             | 0           |                      | JTAG test data output pin                                                                      |  |  |  |

| RTCC     | 42                                           | 68              | E9                  | B37             | 0           |                      | Real-Time Clock alarm output                                                                   |  |  |  |

| CVREF-   | 15                                           | 28              | L2                  | A21             | I           | Analog               | Comparator Voltage Reference (low)                                                             |  |  |  |

| CVREF+   | 16                                           | 29              | K3                  | B17             | I           | Analog               | Comparator Voltage Reference (high)                                                            |  |  |  |

| CVREFOUT | 23                                           | 34              | L5                  | A24             | 0           | Analog               | Comparator Voltage Reference output                                                            |  |  |  |

| C1IN-    | 12                                           | 21              | H2                  | B11             | I           | Analog               | Comparator 1 negative input                                                                    |  |  |  |

| C1IN+    | 11                                           | 20              | H1                  | A12             | I           | Analog               | Comparator 1 positive input                                                                    |  |  |  |

| C1OUT    | 21                                           | 32              | K4                  | A23             | 0           |                      | Comparator 1 output                                                                            |  |  |  |

| C2IN-    | 14                                           | 23              | J2                  | B13             | I           | Analog               | Comparator 2 negative input                                                                    |  |  |  |

| C2IN+    | 13                                           | 22              | J1                  | A13             | I           | Analog               | Comparator 2 positive input                                                                    |  |  |  |

| C2OUT    | 22                                           | 33              | L4                  | B19             | 0           |                      | Comparator 2 output                                                                            |  |  |  |

| PMA0     | 30                                           | 44              | L8                  | A29             | I/O         | TTL/ST               | Parallel Master Port Address bit 0 inpu<br>(Buffered Slave modes) and output<br>(Master modes) |  |  |  |

| PMA1     | 29                                           | 43              | K7                  | B24             | I/O         | TTL/ST               | Parallel Master Port Address bit 1 inpu<br>(Buffered Slave modes) and output<br>(Master modes) |  |  |  |

| PMA2     | 8                                            | 14              | F3                  | A9              | 0           | _                    | Parallel Master Port address                                                                   |  |  |  |

| PMA3     | 6                                            | 12              | F2                  | A8              | 0           |                      | (Demultiplexed Master modes)                                                                   |  |  |  |

| PMA4     | 5                                            | 11              | F4                  | B6              | 0           | _                    |                                                                                                |  |  |  |

| PMA5     | 4                                            | 10              | E3                  | A7              | 0           | _                    |                                                                                                |  |  |  |

| PMA6     | 16                                           | 29              | K3                  | B17             | 0           | —                    |                                                                                                |  |  |  |

| PMA7     | 22                                           | 28              | L2                  | A21             | 0           | —                    |                                                                                                |  |  |  |

| PMA8     | 32                                           | 50              | L11                 | A32             | 0           | _                    |                                                                                                |  |  |  |

| PMA9     | 31                                           | 49              | L10                 | B27             | 0           | _                    |                                                                                                |  |  |  |

| PMA10    | 28                                           | 42              | L7                  | A28             | 0           | _                    |                                                                                                |  |  |  |

| PMA11    | 27                                           | 41              | J7                  | B23             | 0           |                      |                                                                                                |  |  |  |

| PMA12    | 24                                           | 35              | J5                  | B20             | 0           |                      |                                                                                                |  |  |  |

| PMA13    | 23                                           | 34              | L5                  | A24             | 0           | _                    | 1                                                                                              |  |  |  |

| PMA14    | 45                                           | 71              | C11                 | A46             | 0           | _                    | 1                                                                                              |  |  |  |

| PMA15    | 44                                           | 70              | D11                 | B38             | 0           | _                    | 1                                                                                              |  |  |  |

| PMCS1    | 45                                           | 71              | C11                 | A46             | 0           |                      | Parallel Master Port Chip Select 1<br>strobe                                                   |  |  |  |

| PMCS2    | 44                                           | 70              | D11                 | B38             | 0           | _                    | Parallel Master Port Chip Select 2 strobe                                                      |  |  |  |

| 5        | CMOS = CMO<br>ST = Schmitt 1<br>TL = TTL inp | rigger input    |                     |                 |             | nalog = A<br>= Outpu | Analog input P = Power<br>t I = Input                                                          |  |  |  |

Note 1: Pin numbers are only provided for reference. See the "Device Pin Tables" section for device pin availability.

2: See 25.0 "Ethernet Controller" for more information.

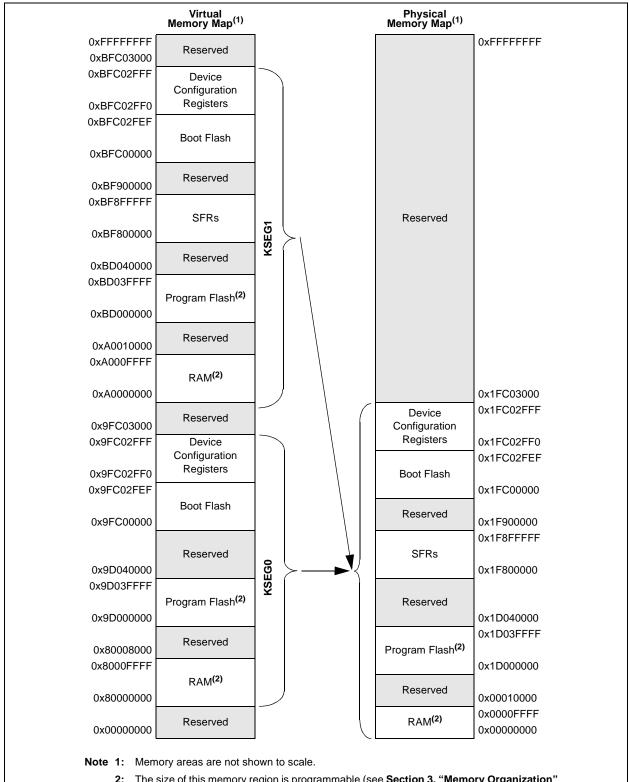

#### FIGURE 4-4: MEMORY MAP ON RESET FOR PIC32MX575F256H, PIC32MX575F256L, PIC32MX675F256H, PIC32MX675F256L, PIC32MX775F256H AND PIC32MX775F256L DEVICES

2: The size of this memory region is programmable (see Section 3. "Memory Organization" (DS60001115)) and can be changed by initialization code provided by end user development tools (refer to the specific development tool documentation for information).

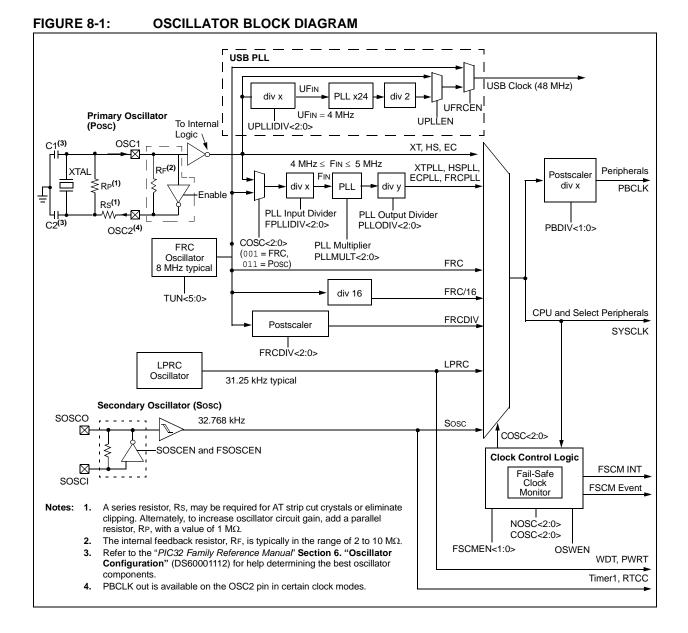

# 8.0 OSCILLATOR CONFIGURATION

Note: This data sheet summarizes the features of the PIC32MX5XX/6XX/7XX family of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to Section 6. "Oscillator" (DS60001112) in the "PIC32 Family Reference Manual", which is available from the Microchip web site (www.microchip.com/PIC32). The Oscillator module has the following features:

- A total of four external and internal oscillator options as clock sources

- On-chip PLL with user-selectable input divider, multiplier and output divider to boost operating frequency on select internal and external oscillator sources

- On-chip user-selectable divisor postscaler on select oscillator sources

- Software-controllable switching between various clock sources

- A Fail-Safe Clock Monitor (FSCM) that detects clock failure and permits safe application recovery or shutdown

- Dedicated On-Chip PLL for USB peripheral

Figure 8-1shows the Oscillator module block diagram.

# PIC32MX5XX/6XX/7XX

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |  |  |  |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|--|--|--|--|

| 31:24        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |  |  |  |  |

| 31.24        |                   | —                 |                   |                   | —                 |                   | —                | —                |  |  |  |  |

| 23:16        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |  |  |  |  |

| 23.10        |                   | —                 |                   |                   | —                 |                   | —                | —                |  |  |  |  |

| 15:8         | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |  |  |

| 10.0         | LMASK<10:3>       |                   |                   |                   |                   |                   |                  |                  |  |  |  |  |

| 7:0          | R/W-0             | R/W-0             | R/W-0             | U-0               | U-0               | U-0               | U-0              | U-0              |  |  |  |  |

| 7:0          | l                 | LMASK<2:0>        |                   | —                 | —                 | —                 | —                | —                |  |  |  |  |

### REGISTER 9-4: CHEMSK: CACHE TAG MASK REGISTER

## Legend:

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read as '0' |                    |  |  |  |  |

|-------------------|------------------|------------------------------------|--------------------|--|--|--|--|

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared               | x = Bit is unknown |  |  |  |  |

bit 31-16 Unimplemented: Write '0'; ignore read

#### bit 15-5 LMASK<10:0>: Line Mask bits

- 1 = Enables mask logic to force a match on the corresponding bit position in LTAG<19:0> bits (CHETAG<23:4>) and the physical address

- 0 = Only writeable for values of CHEIDX<3:0> bits (CHEACC<3:0>) equal to 0x0A and 0x0B (disables mask logic)

- bit 4-0 **Unimplemented:** Write '0'; ignore read

|              |                   |                   |                   | •                 |                   |                   |                  |                  |  |  |  |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|--|--|--|

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |  |  |

| 21.24        | R/W-x             | R/W-x             | R/W-x             | R/W-x             | R/W-x             | R/W-x             | R/W-x            | R/W-x            |  |  |  |

| 31:24        |                   |                   |                   | CHEW0<            | :31:24>           |                   |                  |                  |  |  |  |

| 22.16        | R/W-x             | R/W-x             | R/W-x             | R/W-x             | R/W-x             | R/W-x             | R/W-x            | R/W-x            |  |  |  |

| 23:16        | CHEW0<23:16>      |                   |                   |                   |                   |                   |                  |                  |  |  |  |

| 45.0         | R/W-x             | R/W-x             | R/W-x             | R/W-x             | R/W-x             | R/W-x             | R/W-x            | R/W-x            |  |  |  |

| 15:8         | CHEW0<15:8>       |                   |                   |                   |                   |                   |                  |                  |  |  |  |

| 7.0          | R/W-x             | R/W-x             | R/W-x             | R/W-x             | R/W-x             | R/W-x             | R/W-x            | R/W-x            |  |  |  |

| 7:0          |                   |                   |                   | CHEWO             | <7:0>             |                   |                  |                  |  |  |  |

#### REGISTER 9-5: CHEW0: CACHE WORD 0

| Legend:           |                  |                           |                    |

|-------------------|------------------|---------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, re | ead as '0'         |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared      | x = Bit is unknown |

bit 31-0 **CHEW0<31:0>:** Word 0 of the cache line selected by CHEIDX<3:0> bits (CHEACC<3:0>) Readable only if the device is not code-protected.

### REGISTER 10-9: DCHxINT: DMA CHANNEL 'x' INTERRUPT CONTROL REGISTER (CONTINUED)

- bit 5 **CHDDIF:** Channel Destination Done Interrupt Flag bit

- 1 = Channel Destination Pointer has reached end of destination (CHDPTR = CHDSIZ)

- 0 = No interrupt is pending

- bit 4 CHDHIF: Channel Destination Half Full Interrupt Flag bit

- 1 = Channel Destination Pointer has reached midpoint of destination (CHDPTR = CHDSIZ/2)

0 = No interrupt is pending

#### bit 3 CHBCIF: Channel Block Transfer Complete Interrupt Flag bit

- 1 = A block transfer has been completed (the larger of CHSSIZ/CHDSIZ bytes has been transferred), or a pattern match event occurs

- 0 = No interrupt is pending

#### bit 2 CHCCIF: Channel Cell Transfer Complete Interrupt Flag bit

- 1 = A cell transfer has been completed (CHCSIZ bytes have been transferred)

- 0 = No interrupt is pending

- bit 1 CHTAIF: Channel Transfer Abort Interrupt Flag bit

- 1 = An interrupt matching CHAIRQ has been detected and the DMA transfer has been aborted

- 0 = No interrupt is pending

#### bit 0 CHERIF: Channel Address Error Interrupt Flag bit

- 1 = A channel address error has been detected (either the source or the destination address is invalid)

- 0 = No interrupt is pending

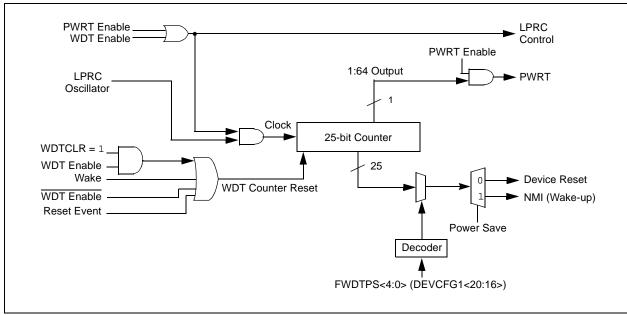

# 15.0 WATCHDOG TIMER (WDT)

Note: This data sheet summarizes the features of the PIC32MX5XX/6XX/7XX family of devices. However, it is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to Section 8. "Watchdog Timer and Power-up Timer" in the "PIC32 (DS60001114) Family Reference Manual", which is available from the Microchip web site (www.microchip.com/PIC32).

This section describes the operation of the WDT and Power-up Timer of the PIC32MX5XX/6XX/7XX.

The WDT, when enabled, operates from the internal Low-Power Oscillator (LPRC) clock source and can be used to detect system software malfunctions by resetting the device if the WDT is not cleared periodically in software. Various WDT time-out periods can be selected using the WDT postscaler. The WDT can also be used to wake the device from Sleep or Idle mode.

The following are key features of the WDT module:

- Configuration or software controlled

- User-configurable time-out period

- Can wake the device from Sleep or Idle mode

#### FIGURE 15-1: WATCHDOG TIMER AND POWER-UP TIMER BLOCK DIAGRAM

## REGISTER 20-2: UxSTA: UARTx STATUS AND CONTROL REGISTER (CONTINUED)

- bit 8 **TRMT:** Transmit Shift Register is Empty bit (read-only) 1 = Transmit shift register is empty and transmit buffer is empty (the last transmission has completed) 0 = Transmit shift register is not empty, a transmission is in progress or queued in the transmit buffer bit 7-6 URXISEL<1:0>: Receive Interrupt Mode Selection bit 11 = Reserved 10 = Interrupt flag bit is asserted while receive buffer is 3/4 or more full (has 6 or more data characters) 01 = Interrupt flag bit is asserted while receive buffer is 1/2 or more full (has 4 or more data characters) 00 = Interrupt flag bit is asserted while receive buffer is not empty (has at least 1 data character) **ADDEN:** Address Character Detect bit (bit 8 of received data = 1) bit 5 1 = Address Detect mode is enabled. If 9-bit mode is not selected, this control bit has no effect. 0 = Address Detect mode is disabled bit 4 **RIDLE:** Receiver Idle bit (read-only) 1 =Receiver is idle 0 = Data is being received bit 3 PERR: Parity Error Status bit (read-only) 1 = Parity error has been detected for the current character 0 = Parity error has not been detected FERR: Framing Error Status bit (read-only) bit 2 1 = Framing error has been detected for the current character 0 = Framing error has not been detected bit 1 **OERR:** Receive Buffer Overrun Error Status bit. This bit is set in hardware and can only be cleared (= 0) in software. Clearing a previously set OERR bit resets the receiver buffer and RSR to an empty state.

- 1 = Receive buffer has overflowed

- 0 = Receive buffer has not overflowed

- bit 0 **URXDA:** Receive Buffer Data Available bit (read-only)

- 1 = Receive buffer has data, at least one more character can be read

- 0 = Receive buffer is empty

### REGISTER 25-1: ETHCON1: ETHERNET CONTROLLER CONTROL REGISTER 1 (CONTINUED)

- bit 7 **AUTOFC:** Automatic Flow Control bit

- 1 = Automatic Flow Control is enabled

- 0 = Automatic Flow Control is disabled

Setting this bit will enable automatic Flow Control. If set, the full and empty watermarks are used to automatically enable and disable the Flow Control, respectively. When the number of received buffers BUFCNT (ETHSTAT<16:23>) rises to the full watermark, Flow Control is automatically enabled. When the BUFCNT falls to the empty watermark, Flow Control is automatically disabled.

This bit is only used for Flow Control operations and affects both TX and RX operations.

#### bit 6-5 Unimplemented: Read as '0'

#### bit 4 MANFC: Manual Flow Control bit

- 1 = Manual Flow Control is enabled

- 0 = Manual Flow Control is disabled

Setting this bit will enable manual Flow Control. If set, the Flow Control logic will send a PAUSE frame using the PAUSE timer value in the PTV register. It will then resend a PAUSE frame every 128 \* PTV<15:0>/2 TX clock cycles until the bit is cleared.

**Note:** For 10 Mbps operation, TX clock runs at 2.5 MHz. For 100 Mbps operation, TX clock runs at 25 MHz.

When this bit is cleared, the Flow Control logic will automatically send a PAUSE frame with a 0x0000 PAUSE timer value to disable Flow Control.

This bit is only used for Flow Control operations and affects both TX and RX operations.

#### bit 3-1 Unimplemented: Read as '0'

bit 0 BUFCDEC: Descriptor Buffer Count Decrement bit

The BUFCDEC bit is a write-1 bit that reads as '0'. When written with a '1', the Descriptor Buffer Counter, BUFCNT, will decrement by one. If BUFCNT is incremented by the RX logic at the same time that this bit is written, the BUFCNT value will remain unchanged. Writing a '0' will have no effect.

This bit is only used for RX operations.

**Note 1:** It is not recommended to clear the RXEN bit and then make changes to any RX related field/register. The Ethernet Controller must be reinitialized (ON cleared to '0'), and then the RX changes applied.

#### REGISTER 25-18: ETHSCOLFRM: ETHERNET CONTROLLER SINGLE COLLISION FRAMES STATISTICS REGISTER

| Bit Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 |       |       | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |       |  |  |  |

|-----------|-------------------|-------------------|-------|-------|-------------------|------------------|------------------|-------|--|--|--|

| 31:24     | U-0               | U-0               | U-0   | U-0   | U-0               | U-0              | U-0              | U-0   |  |  |  |

| 31.24     | -                 | —                 | _     | —     | -                 | —                | _                | —     |  |  |  |

| 22.46     | U-0               | U-0               | U-0   | U-0   | U-0               | U-0              | U-0              | U-0   |  |  |  |

| 23:16     | _                 | —                 | _     | _     | _                 | —                | _                | —     |  |  |  |

| 15.0      | R/W-0             | R/W-0             | R/W-0 | R/W-0 | R/W-0             | R/W-0            | R/W-0            | R/W-0 |  |  |  |

| 15:8      | SCOLFRMCNT<15:8>  |                   |       |       |                   |                  |                  |       |  |  |  |

| 7.0       | R/W-0             | R/W-0             | R/W-0 | R/W-0 | R/W-0             | R/W-0            | R/W-0            | R/W-0 |  |  |  |

| 7:0       | SCOLFRMCNT<7:0>   |                   |       |       |                   |                  |                  |       |  |  |  |

## Legend:

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, | read as '0'        |  |

|-------------------|------------------|------------------------|--------------------|--|

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared   | x = Bit is unknown |  |

#### bit 31-16 Unimplemented: Read as '0'

bit 15-0 **SCOLFRMCNT<15:0>:** Single Collision Frame Count bits Increment count for frames that were successfully transmitted on the second try.

Note 1: This register is only used for TX operations.

2: This register is automatically cleared by hardware after a read operation, unless the byte enables for bytes 0/1 are '0'.

**3:** It is recommended to use the SET, CLR, or INV registers to set or clear any bit in this register. Setting or clearing any bits in this register should only be done for debug/test purposes.

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3        | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0         |  |

|--------------|-------------------|-------------------|-------------------|-------------------|--------------------------|-------------------|------------------|--------------------------|--|

| 31:24        | U-0               | U-0               | U-0               | U-0               | U-0                      | U-0               | U-0              | U-0                      |  |

| 31.24        |                   | —                 | -                 | -                 | —                        | —                 | —                | —                        |  |

| 23:16        | U-0               | U-0               | U-0               | U-0               | U-0                      | U-0               | U-0              | U-0                      |  |

| 23.10        |                   | —                 | -                 | -                 | —                        | —                 | —                | —                        |  |

| 15:8         | U-0               | U-0               | U-0               | U-0               | R/W-0                    | U-0               | U-0              | R/W-0                    |  |

| 10.0         | _                 | —                 | _                 | _                 | RESETRMII <sup>(1)</sup> | —                 | —                | SPEEDRMII <sup>(1)</sup> |  |

| 7:0          | U-0               | U-0               | U-0               | U-0               | U-0                      | U-0               | U-0              | U-0                      |  |

| 7.0          |                   | _                 |                   |                   | _                        | _                 |                  | —                        |  |

#### REGISTER 25-29: EMAC1SUPP: ETHERNET CONTROLLER MAC PHY SUPPORT REGISTER

#### Legend:

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read as '0' |                    |  |  |  |

|-------------------|------------------|------------------------------------|--------------------|--|--|--|

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared               | x = Bit is unknown |  |  |  |

- bit 31-12 Unimplemented: Read as '0'

- bit 11 **RESETRMII:** Reset RMII Logic bit<sup>(1)</sup>

- 1 = Reset the MAC RMII module

- 0 = Normal operation.

- bit 10-9 Unimplemented: Read as '0'

- bit 8 SPEEDRMII: RMII Speed bit<sup>(1)</sup>

- This bit configures the Reduced MII logic for the current operating speed.

- 1 = RMII is running at 100 Mbps

- 0 = RMII is running at 10 Mbps

- bit 7-0 Unimplemented: Read as '0'

- Note 1: This bit is only used for the RMII module.

**Note:** Both 16-bit and 32-bit accesses are allowed to these registers (including the SET, CLR and INV registers). 8-bit accesses are not allowed and are ignored by the hardware.

# 27.1 Control Register

# TABLE 27-1: COMPARATOR VOLTAGE REFERENCE REGISTER MAP

| lress<br>¢)              |                                 | e         |       | Bits  |       |       |       |                        |       |                      |      |       | 6    |       |      |      |      |      |            |

|--------------------------|---------------------------------|-----------|-------|-------|-------|-------|-------|------------------------|-------|----------------------|------|-------|------|-------|------|------|------|------|------------|

| Virtual Addr<br>(BF80_#) | Register<br>Name <sup>(1)</sup> | Bit Range | 31/15 | 30/14 | 29/13 | 28/12 | 27/11 | 26/10                  | 25/9  | 24/8                 | 23/7 | 22/6  | 21/5 | 20/4  | 19/3 | 18/2 | 17/1 | 16/0 | All Resets |

| 0000                     | CVRCON                          | 31:16     |       |       | —     | —     | —     | -                      | —     | _                    | _    | _     |      | _     |      | —    |      | —    | 0000       |

| 9800                     | CVRCON                          | 15:0      | ON    | -     | _     | —     | _     | VREFSEL <sup>(2)</sup> | BGSEL | <1:0> <sup>(2)</sup> | _    | CVROE | CVRR | CVRSS |      | CVR< | 3:0> |      | 0100       |

Legend: x = unknown value on Reset; — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

Note 1: All registers in this table have corresponding CLR, SET and INV registers at their virtual addresses, plus offsets of 0x4, 0x8 and 0xC, respectively. See Section 12.1.1 "CLR, SET and INV Registers" for more information.

2: These bits are not available on PIC32MX575/675/695/775/795 devices. On these devices, reset value for CVRCON is '0000'.

# PIC32MX5XX/6XX/7XX

| DC CHARACT       | ERISTICS                     |            | (unless ot   |                     | <b>2.3V to 3.6V</b><br>TA ≤ +85°C for Indus<br>TA ≤ +105°C for V-Te |               |  |

|------------------|------------------------------|------------|--------------|---------------------|---------------------------------------------------------------------|---------------|--|

| Parameter<br>No. | Typical <sup>(2)</sup>       | Max.       | Units        |                     | Conditions                                                          |               |  |

| Idle Current (I  | IDLE) <sup>(1,3)</sup> for P | PIC32MX575 | /675/695/775 | 795 Family Devices  |                                                                     |               |  |

| DC30             | 4.5                          | 6.5        | mA           | -40°C, +25°C, +85°C |                                                                     | 4 MHz         |  |

| DC30b            | 5                            | 7          | mA           | +105°C              | —                                                                   | 4 IVITIZ      |  |

| DC31             | 13                           | 15         | mA           | -40°C, +25°C, +85°C | —                                                                   | 25 MHz        |  |

| DC32             | 28                           | 30         | mA           | -40°C, +25°C, +85°C | —                                                                   | 60 MHz        |  |

| DC33             | 36                           | 42         | mA           | -40°C, +25°C, +85°C |                                                                     | 80 MHz        |  |

| DC33b            | 39                           | 45         | mA           | +105°C              | —                                                                   |               |  |

| DC34             |                              | 40         |              | -40°C               | 0°C                                                                 |               |  |

| DC34a            |                              | 75         |              | +25°C               | 2.3V                                                                |               |  |

| DC34b            |                              | 800        | μA           | +85°C               | 2.3V                                                                |               |  |

| DC34c            |                              | 1000       |              | +105°C              |                                                                     |               |  |

| DC35             | 35                           |            |              | -40°C               |                                                                     |               |  |

| DC35a            | 65                           |            |              | +25°C               | 3.3V                                                                | LPRC (31 kHz) |  |

| DC35b            | 600                          | _          | μA           | +85°C               | 3.3V                                                                |               |  |

| DC35c            | 800                          |            |              | +105°C              |                                                                     |               |  |

| DC36             |                              | 43         |              | -40°C               |                                                                     |               |  |

| DC36a            |                              | 106        |              | +25°C               | 3.6V                                                                |               |  |

| DC36b            | o 800                        |            | μA           | +85°C               | 3.0V                                                                |               |  |

| DC36c            |                              | 1000       |              | +105°C              |                                                                     |               |  |

#### TABLE 32-6: DC CHARACTERISTICS: IDLE CURRENT (IIDLE)

Note 1: The test conditions for IIDLE current measurements are as follows:

- Oscillator mode is EC (for 8 MHz and below) and EC+PLL (for above 8 MHz) with OSC1 driven by external square wave from rail-to-rail, (OSC1 input clock input over/undershoot < 100 mV required)</li>

- OSC2/CLKO is configured as an I/O input pin

- USB PLL oscillator is disabled if the USB module is implemented, PBCLK divisor = 1:8

- CPU is in Idle mode, program Flash memory Wait states = 111, Program Cache and Prefetch are disabled and SRAM data memory Wait states = 1

- No peripheral modules are operating, (ON bit = 0)

- WDT, Clock Switching, Fail-Safe Clock Monitor, and Secondary Oscillator are disabled

- All I/O pins are configured as inputs and pulled to Vss

- MCLR = VDD

- RTCC and JTAG are disabled

- 2: Data in "Typical" column is at 3.3V, 25°C unless otherwise stated. Parameters are for design guidance only and are not tested.

- 3: This parameter is characterized, but not tested in manufacturing.

- **4:** All parameters are characterized, but only those parameters listed for 4 MHz and 80 MHz are tested at 3.3V in manufacturing.

#### TABLE 32-36: ADC MODULE SPECIFICATIONS (CONTINUED)

| AC CHARACTERISTICS |            |                                   | $\begin{array}{l} \mbox{Standard Operating Conditions (see Note 5): 2.5V to 3.6V} \\ \mbox{(unless otherwise stated)} \\ \mbox{Operating temperature} & -40^\circ C \leq TA \leq +85^\circ C \mbox{ for Industrial} \\ & -40^\circ C \leq TA \leq +105^\circ C \mbox{ for V-Temp} \end{array}$ |              |      |       |                                                         |

|--------------------|------------|-----------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------|------|-------|---------------------------------------------------------|

| Param.<br>No.      | Symbol     | Characteristics                   | Min.                                                                                                                                                                                                                                                                                           | Typical      | Max. | Units | Conditions                                              |

| ADC Ac             | curacy – N | leasurements with Inter           | nal VREF+/VR                                                                                                                                                                                                                                                                                   | EF-          |      |       |                                                         |

| AD20d              | Nr         | Resolution                        |                                                                                                                                                                                                                                                                                                | 10 data bits |      | bits  | (Note 3)                                                |

| AD21d              | INL        | Integral Nonlinearity             | > -1                                                                                                                                                                                                                                                                                           | —            | < 1  | LSb   | VINL = AVSS = 0V,<br>AVDD = 2.5V to 3.6V<br>(Note 3)    |

| AD22d              | DNL        | Differential Nonlinearity         | > -1                                                                                                                                                                                                                                                                                           |              | < 1  | LSb   | VINL = AVSS = 0V,<br>AVDD = 2.5V to 3.6V<br>(Notes 2,3) |

| AD23d              | Gerr       | Gain Error                        | > -4                                                                                                                                                                                                                                                                                           | -            | < 4  | LSb   | VINL = AVSS = 0V,<br>AVDD = 2.5V to 3.6V<br>(Note 3)    |

| AD24d              | EOFF       | Offset Error                      | > -2                                                                                                                                                                                                                                                                                           | -            | < 2  | LSb   | VINL = AVSS = 0V,<br>AVDD = 2.5V to 3.6V<br>(Note 3)    |

| AD25d              | —          | Monotonicity                      | —                                                                                                                                                                                                                                                                                              | —            | _    | —     | Guaranteed                                              |

| Dynami             | c Performa | ance                              |                                                                                                                                                                                                                                                                                                |              |      |       |                                                         |

| AD31b              | SINAD      | Signal to Noise and<br>Distortion | 55                                                                                                                                                                                                                                                                                             | 58.5         |      | dB    | (Notes 3,4)                                             |

| AD34b              | ENOB       | Effective Number of Bits          | 9.0                                                                                                                                                                                                                                                                                            | 9.5          |      | bits  | (Notes 3,4)                                             |

**Note 1:** These parameters are not characterized or tested in manufacturing.

2: With no missing codes.

**3:** These parameters are characterized, but not tested in manufacturing.

4: Characterized with a 1 kHz sine wave.

**5:** The ADC module is functional at VBORMIN < VDD < 2.5V, but with degraded performance. Unless otherwise stated, module functionality is tested, but not characterized.

## TABLE 32-37: 10-BIT ADC CONVERSION RATE PARAMETERS

| Standard Operating Conditions (see Note 3): 2.5V to 3.6V(unless otherwise stated)Operating temperature $-40^{\circ}C \le TA \le +85^{\circ}C$ for Industrial $-40^{\circ}C \le TA \le +105^{\circ}C$ for V-Temp |                |                             |               |              |                            |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------|-----------------------------|---------------|--------------|----------------------------|

| ADC Speed <sup>(2)</sup>                                                                                                                                                                                        | TAD<br>Minimum | Sampling<br>Time<br>Minimum | Rs<br>Maximum | Vdd          | ADC Channels Configuration |

| 1 Msps to<br>400 ksps <sup>(1)</sup>                                                                                                                                                                            | 65 ns          | 132 ns                      | 500Ω          | 3.0V to 3.6V | ANX CHX<br>S&H<br>ADC      |

| Up to 400 ksps                                                                                                                                                                                                  | 200 ns         | 200 ns                      | 5.0 kΩ        | 2.5V to 3.6V | ANX ADC<br>ANX or VREF-    |

Note 1: External VREF- and VREF+ pins must be used for correct operation.

2: These parameters are characterized, but not tested in manufacturing.

**3:** The ADC module is functional at VBORMIN < VDD < 2.5V, but with degraded performance. Unless otherwise stated, module functionality is tested, but not characterized.

# PIC32MX5XX/6XX/7XX

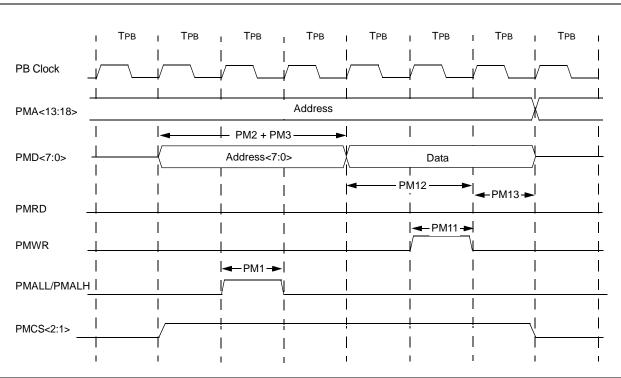

### FIGURE 32-27: PARALLEL MASTER PORT WRITE TIMING DIAGRAM

## TABLE 32-41: PARALLEL MASTER PORT WRITE TIMING REQUIREMENTS

| AC CHARACTERISTICS |         |                                                                           | $\begin{array}{l} \mbox{Standard Operating Conditions: 2.3V to 3.6V} \\ \mbox{(unless otherwise stated)} \\ \mbox{Operating temperature} & -40^{\circ}C \leq TA \leq +85^{\circ}C \mbox{ for Industrial} \\ & -40^{\circ}C \leq TA \leq +105^{\circ}C \mbox{ for V-Temp} \end{array}$ |         |      |       |            |

|--------------------|---------|---------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------|------|-------|------------|

| Param.<br>No.      | Symbol  | Characteristics <sup>(1)</sup>                                            | Min.                                                                                                                                                                                                                                                                                  | Typical | Max. | Units | Conditions |

| PM11               | Twr     | PMWR Pulse Width                                                          | _                                                                                                                                                                                                                                                                                     | 1 Трв   |      | —     | _          |

| PM12               | TDVSU   | Data Out Valid before PMWR or<br>PMENB goes Inactive (data setup<br>time) | —                                                                                                                                                                                                                                                                                     | 2 Трв   | _    | —     | _          |

| PM13               | TDVHOLD | PMWR or PMEMB Invalid to Data<br>Out Invalid (data hold time)             | —                                                                                                                                                                                                                                                                                     | 1 Трв   |      |       | —          |

**Note 1:** These parameters are characterized, but not tested in manufacturing.

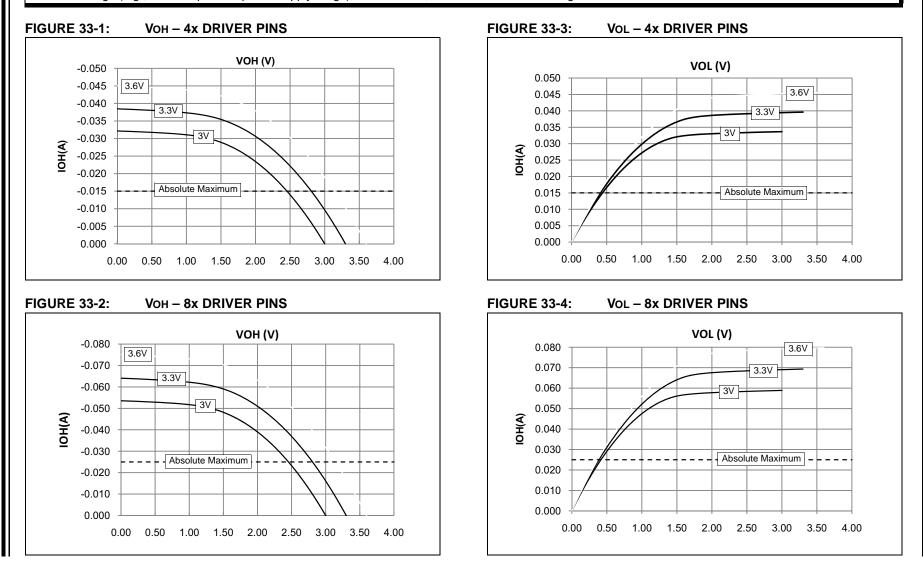

# 33.0 DC AND AC DEVICE CHARACTERISTICS GRAPHS

**Note:** The graphs provided following this note are a statistical summary based on a limited number of samples and are provided for design guidance purposes only. The performance characteristics listed herein are not tested or guaranteed. In some graphs, the data presented may be outside the specified operating range (e.g., outside specified power supply range) and therefore, outside the warranted range.

PIC32MX5XX/6XX/7X

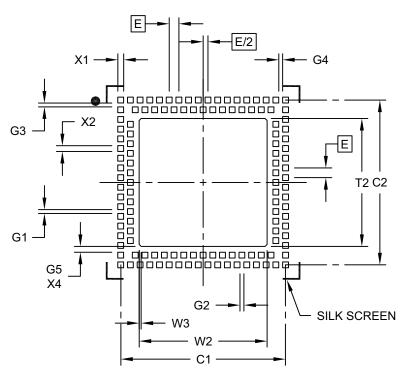

# 124-Very Thin Leadless Array Package (TL) – 9x9x0.9 mm Body [VTLA]

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

|                                      | MILLIMETERS |      |          |      |

|--------------------------------------|-------------|------|----------|------|

| Dimension                            | Limits      | MIN  | NOM      | MAX  |

| Contact Pitch                        | E           |      | 0.50 BSC |      |

| Pad Clearance                        | G1          | 0.20 |          |      |

| Pad Clearance                        | G2          | 0.20 |          |      |

| Pad Clearance                        | G3          | 0.20 |          |      |

| Pad Clearance                        | G4          | 0.20 |          |      |

| Contact to Center Pad Clearance (X4) | G5          | 0.30 |          |      |

| Optional Center Pad Width            | T2          |      |          | 6.60 |

| Optional Center Pad Length           | W2          |      |          | 6.60 |

| Optional Center Pad Chamfer (X4)     | W3          |      | 0.10     |      |

| Contact Pad Spacing                  | C1          |      | 8.50     |      |

| Contact Pad Spacing                  | C2          |      | 8.50     |      |

| Contact Pad Width (X124)             |             |      |          | 0.30 |

| Contact Pad Length (X124)            |             |      |          | 0.30 |

#### Notes:

1. Dimensioning and tolerancing per ASME Y14.5M

BSC: Basic Dimension. Theoretically exact value shown without tolerances.

Microchip Technology Drawing No. C04-2193A

## APPENDIX A: MIGRATING FROM PIC32MX3XX/4XX TO PIC32MX5XX/6XX/7XX DEVICES

This appendix provides an overview of considerations for migrating from PIC32MX3XX/4XX devices to the PIC32MX5XX/6XX/7XX family of devices. The code developed for the PIC32MX3XX/4XX devices can be ported to the PIC32MX5XX/6XX/7XX devices after making the appropriate changes outlined below.

## A.1 DMA

PIC32MX5XX/6XX/7XX devices do not support stopping DMA transfers in Idle mode.

## A.2 Interrupts

PIC32MX5XX/6XX/7XX devices have persistent interrupts for some of the peripheral modules. This means that the interrupt condition for these peripherals must be cleared before the interrupt flag can be cleared.

For example, to clear a UART receive interrupt, the user application must first read the UART Receive register to clear the interrupt condition and then clear the associated UxIF flag to clear the pending UART interrupt. In other words, the UxIF flag cannot be cleared by software until the UART Receive register is read.

Table A-1 outlines the peripherals and associated interrupts that are implemented differently on PIC32MX5XX/6XX/7XX versus PIC32MX3XX/4XX devices.

In addition, on the SPI module, the IRQ numbers for the receive done interrupts were changed from 25 to 24 and the transfer done interrupts were changed from 24 to 25.

# TABLE A-1: PIC32MX3XX/4XX VERSUS PIC32MX5XX/6XX/7XX INTERRUPT IMPLEMENTATION DIFFERENCES

| Module        | Interrupt Implementation                                                                                                                                                                                                                                                                                                                                                                                     |  |  |  |  |

|---------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| Input Capture | To clear an interrupt source, read the Buffer Result (ICxBUF) register to obtain the number of capture results in the buffer that are below the interrupt threshold (specified by ICI<1:0> bits).                                                                                                                                                                                                            |  |  |  |  |

| SPI           | Receive and transmit interrupts are controlled by the SRXISEL<1:0> and STXISEL<1:0> bits, respectively. To clear an interrupt source, data must be written to, or read from, the SPIxBUF register to obtain the number of data to receive/transmit below the level specified by the SRXISEL<1:0> and STXISEL<1:0> bits.                                                                                      |  |  |  |  |

| UART          | TX interrupt will be generated as soon as the UART module is enabled.<br>Receive and transmit interrupts are controlled by the URXISEL<1:0> and UTXISEL<1:0> bits, respectively. To clear an interrupt source, data must be read from, or written to, the UxRXREG or UxTXREG registers to obtain the number of data to receive/transmit below the level specified by the URXISEL<1:0> and UTXISEL<1:0> bits. |  |  |  |  |

| ADC           | All samples must be read from the result registers (ADC1BUFx) to clear the interrupt source.                                                                                                                                                                                                                                                                                                                 |  |  |  |  |

| PMP           | To clear an interrupt source, read the Parallel Master Port Data Input/Output (PMDIN/PMDOUT) register.                                                                                                                                                                                                                                                                                                       |  |  |  |  |

## TABLE B-3: MAJOR SECTION UPDATES (CONTINUED)

| Section Name                             | Update Description                                                                                                                                                                                                                                                                                                                                                                                                |  |  |  |

|------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| 4.0 "Memory Organization"<br>(Continued) | Made the following bit name changes in the I2C1, I2C3, I2C4 and I2C5 Register Map (Table 4-11):                                                                                                                                                                                                                                                                                                                   |  |  |  |

|                                          | <ul> <li>I2C3BRG SFR: I2C1BRG was changed to I2C3BRG</li> <li>I2C4BRG SFR: I2C1BRG was changed to I2C4BRG</li> <li>I2C5BRG SFR: I2C1BRG was changed to I2C5BRG</li> <li>I2C4TRN SFR: I2CT1DATA was changed to I2CT2ADATA</li> <li>I2C4RCV SFR: I2CR2DATA was changed to I2CR2ADATA</li> <li>I2C5TRN SFR: I2CT1DATA was changed to I2CT3ADATA</li> <li>I2C5RCV SFR: I2CR1DATA was changed to I2CR3ADATA</li> </ul> |  |  |  |

|                                          | Added the RTSMD bit and UEN<1:0> bits to the UART1A, UART1B, UART2A, UART2B, UART3A and UART3B Register Map (Table 4-13)                                                                                                                                                                                                                                                                                          |  |  |  |

|                                          | Added the SIDL bit to the DMA Global Register Map (Table 4-17).                                                                                                                                                                                                                                                                                                                                                   |  |  |  |

|                                          | Changed the CM bit to CMR in the System Control Register Map (Table 4-23).                                                                                                                                                                                                                                                                                                                                        |  |  |  |

|                                          | Added the following devices to the I2C2, SPI1, PORTA, PORTC, PORTD, PORTE, PORTF, PORTG, Change Notice and Pull-up Register Maps (Table 4-12, Table 4-14, Table 4-24, Table 4-27, Table 4-29, Table 4-31, Table 4-33, Table 4-35 and Table 4-36):                                                                                                                                                                 |  |  |  |

|                                          | <ul> <li>PIC32MX534F064L</li> <li>PIC32MX564F064L</li> <li>PIC32MX564F128L</li> <li>PIC32MX664F064L</li> <li>PIC32MX664F128L</li> <li>PIC32MX764F128L</li> </ul>                                                                                                                                                                                                                                                  |  |  |  |

|                                          | Added the following devices to the PORTC, PORTD, PORTE, PORTF, PORTG, Change Notice and Pull-up Register Maps (Table 4-26, Table 4-28, Table 4-30, Table 4-32, Table 4-34 and Table 4-37):                                                                                                                                                                                                                        |  |  |  |

|                                          | <ul> <li>PIC32MX534F064H</li> <li>PIC32MX564F064H</li> <li>PIC32MX564F128H</li> <li>PIC32MX664F064H</li> <li>PIC32MX664F128H</li> <li>PIC32MX764F128H</li> </ul>                                                                                                                                                                                                                                                  |  |  |  |

|                                          | Added the following devices to the CAN1 Register Map (Table 4-45):                                                                                                                                                                                                                                                                                                                                                |  |  |  |

|                                          | <ul> <li>PIC32MX534F064H</li> <li>PIC32MX564F064H</li> <li>PIC32MX564F128H</li> <li>PIC32MX764F128H</li> <li>PIC32MX534F064L</li> <li>PIC32MX564F064L</li> <li>PIC32MX564F128L</li> <li>PIC32MX764F128L</li> </ul>                                                                                                                                                                                                |  |  |  |

|                                          | Added the following devices to the Ethernet Controller Register Map (Table 4-47): <ul> <li>PIC32MX664F064H</li> <li>PIC32MX664F128H</li> <li>PIC32MX764F128H</li> <li>PIC32MX664F064L</li> </ul>                                                                                                                                                                                                                  |  |  |  |

|                                          | <ul><li>PIC32MX664F128L</li><li>PIC32MX764F128L</li></ul>                                                                                                                                                                                                                                                                                                                                                         |  |  |  |

# **PRODUCT IDENTIFICATION SYSTEM**

To order or obtain information, e.g., on pricing or delivery, refer to the factory or the listed sales office.

| PIC32 MX 5XX F 512 H T - 80 I/PT - XXX       Example:         Microchip Brand |                                                                                                                                                                                                                                                                                                                                                                     |  |  |  |

|-------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| Flash Memory Fan                                                              | nily                                                                                                                                                                                                                                                                                                                                                                |  |  |  |

| Architecture                                                                  | MX = 32-bit RISC MCU core                                                                                                                                                                                                                                                                                                                                           |  |  |  |

| Product Groups                                                                | 5XX = General purpose microcontroller family<br>6XX = General purpose microcontroller family<br>7XX = General purpose microcontroller family                                                                                                                                                                                                                        |  |  |  |

| Flash Memory Family                                                           | F = Flash program memory                                                                                                                                                                                                                                                                                                                                            |  |  |  |

| Program Memory Size                                                           | <b>64 = 64K</b><br><b>128 = 128K</b><br>256 = 256K<br>512 = 512K                                                                                                                                                                                                                                                                                                    |  |  |  |

| Pin Count                                                                     | H = 64-pin<br>L = 100-pin, 121-pin, 124-pin                                                                                                                                                                                                                                                                                                                         |  |  |  |

| Speed (see Note 1)                                                            | Blank or 80 = 80 MHz                                                                                                                                                                                                                                                                                                                                                |  |  |  |

| Temperature Range                                                             | I = -40°C to +85°C (Industrial)<br>V = -40°C to +105°C (V-Temp)                                                                                                                                                                                                                                                                                                     |  |  |  |

| Package                                                                       | PT = 64-Lead (10x10x1 mm) TQFP (Thin Quad Flatpack)<br>PT = 100-Lead (12x12x1 mm) TQFP (Thin Quad Flatpack)<br>PF = 100-Lead (14x14x1 mm) TQFP (Thin Quad Flatpack)<br>MR = 64-Lead (9x9x0.9 mm) QFN (Plastic Quad Flat)<br>BG = 121-Lead (10x10x1.1 mm) TFBGA (Plastic Thin Profile Ball Grid Array)<br>TL = 124-Lead (9x9x0.9 mm) VTLA (Very Thin Leadless Array) |  |  |  |

| Pattern                                                                       | Three-digit QTP, SQTP, Code or Special Requirements (blank otherwise)<br>ES = Engineering Sample                                                                                                                                                                                                                                                                    |  |  |  |

| Note 1: This option is not available for PIC32MX534/564/664/764 devices.      |                                                                                                                                                                                                                                                                                                                                                                     |  |  |  |