Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFl

| Details                    |                                                                                 |

|----------------------------|---------------------------------------------------------------------------------|

| Product Status             | Active                                                                          |

| Core Processor             | MIPS32® M4K™                                                                    |

| Core Size                  | 32-Bit Single-Core                                                              |

| Speed                      | 80MHz                                                                           |

| Connectivity               | Ethernet, I <sup>2</sup> C, SPI, UART/USART, USB OTG                            |

| Peripherals                | Brown-out Detect/Reset, DMA, POR, PWM, WDT                                      |

| Number of I/O              | 53                                                                              |

| Program Memory Size        | 128KB (128K x 8)                                                                |

| Program Memory Type        | FLASH                                                                           |

| EEPROM Size                | -                                                                               |

| RAM Size                   | 32K x 8                                                                         |

| Voltage - Supply (Vcc/Vdd) | 2.3V ~ 3.6V                                                                     |

| Data Converters            | A/D 16x10b                                                                      |

| Oscillator Type            | Internal                                                                        |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                               |

| Mounting Type              | Surface Mount                                                                   |

| Package / Case             | 64-TQFP                                                                         |

| Supplier Device Package    | 64-TQFP (10x10)                                                                 |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic32mx664f128ht-i-pt |

|                            |                                                                                 |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

## PIC32MX5XX/6XX/7XX

|                  |      |                         |                  |     | USB      | , Ethe | ernet, a               | nd CA                                    | N                     |                    |                                 |                              |             |         |      |       |                         |

|------------------|------|-------------------------|------------------|-----|----------|--------|------------------------|------------------------------------------|-----------------------|--------------------|---------------------------------|------------------------------|-------------|---------|------|-------|-------------------------|

| Device           | Pins | Program Memory (KB)     | Data Memory (KB) | USB | Ethernet | CAN    | Timers/Capture/Compare | DMA Channels<br>(Programmable/Dedicated) | UART <sup>(2,3)</sup> | SPI <sup>(3)</sup> | I <sup>2</sup> C <sup>(3)</sup> | 10-bit 1 Msps ADC (Channels) | Comparators | dSd/dMd | JTAG | Trace | Packages <sup>(4)</sup> |

| PIC32MX764F128H  | 64   | 128 + 12 <sup>(1)</sup> | 32               | 1   | 1        | 1      | 5/5/5                  | 4/8                                      | 6                     | 3                  | 4                               | 16                           | 2           | Yes     | Yes  | No    | PT,<br>MR               |

| PIC32MX775F256H  | 64   | 256 + 12 <sup>(1)</sup> | 64               | 1   | 1        | 2      | 5/5/5                  | 8/8                                      | 6                     | 3                  | 4                               | 16                           | 2           | Yes     | Yes  | No    | PT,<br>MR               |

| PIC32MX775F512H  | 64   | 512 + 12 <sup>(1)</sup> | 64               | 1   | 1        | 2      | 5/5/5                  | 8/8                                      | 6                     | 3                  | 4                               | 16                           | 2           | Yes     | Yes  | No    | PT,<br>MR               |

| PIC32MX795F512H  | 64   | 512 + 12 <sup>(1)</sup> | 128              | 1   | 1        | 2      | 5/5/5                  | 8/8                                      | 6                     | 3                  | 4                               | 16                           | 2           | Yes     | Yes  | No    | PT,<br>MR               |

| PIC32MX764F128L  | 100  | 128 + 12 <sup>(1)</sup> | 32               | 1   | 1        | 1      | 5/5/5                  | 4/6                                      | 6                     | 4                  | 5                               | 16                           | 2           | Yes     | Yes  | Yes   | PT, PF,<br>BG           |

| PIC32MX775F256L  | 100  | 256 + 12 <sup>(1)</sup> | 64               | 1   | 1        | 2      | 5/5/5                  | 8/8                                      | 6                     | 4                  | 5                               | 16                           | 2           | Yes     | Yes  | Yes   | PT, PF,<br>BG           |

| PIC32MX775F512L  | 100  | 512 + 12 <sup>(1)</sup> | 64               | 1   | 1        | 2      | 5/5/5                  | 8/8                                      | 6                     | 4                  | 5                               | 16                           | 2           | Yes     | Yes  | Yes   | PT, PF,<br>BG           |

| PIC32MX795F512L  | 100  | 512 + 12 <sup>(1)</sup> | 128              | 1   | 1        | 2      | 5/5/5                  | 8/8                                      | 6                     | 4                  | 5                               | 16                           | 2           | Yes     | Yes  | Yes   | PT, PF,<br>BG, TL       |

| Legend: PF, PT = | TQFF | P MR = C                | QFN              |     | BG       | G = TF | BGA                    |                                          | TL = \                | /TLA               | 5)                              |                              |             |         |      |       |                         |

#### TABLE 3: PIC32MX7XX USB, ETHERNET, AND CAN FEATURES

Note 1: This device features 12 KB boot Flash memory.

2: CTS and RTS pins may not be available for all UART modules. Refer to the "Device Pin Tables" section for more information.

3: Some pins between the UART, SPI and I<sup>2</sup>C modules may be shared. Refer to the "Device Pin Tables" section for more information.

4: Refer to Section 34.0 "Packaging Information" for more information.

5: 100-pin devices other than those listed here are available in the VTLA package upon request. Please contact your local Microchip Sales Office for details.

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6           | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |  |  |

|--------------|-------------------|-----------------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|--|--|--|

| 04.04        | W-0               | W-0                         | W-0               | W-0               | W-0               | W-0               | W-0              | W-0              |  |  |  |

| 31:24        |                   | NVMKEY<31:24>               |                   |                   |                   |                   |                  |                  |  |  |  |

| 00.40        | W-0               | W-0                         | W-0               | W-0               | W-0               | W-0               | W-0              | W-0              |  |  |  |

| 23:16        | NVMKEY<23:16>     |                             |                   |                   |                   |                   |                  |                  |  |  |  |

| 45.0         | W-0               | W-0                         | W-0               | W-0               | W-0               | W-0               | W-0              | W-0              |  |  |  |

| 15:8         |                   |                             |                   | NVMK              | EY<15:8>          |                   |                  |                  |  |  |  |

| 7.0          | W-0               | W-0 W-0 W-0 W-0 W-0 W-0 W-0 |                   |                   |                   |                   |                  |                  |  |  |  |

| 7:0          | NVMKEY<7:0>       |                             |                   |                   |                   |                   |                  |                  |  |  |  |

#### REGISTER 5-2: NVMKEY: PROGRAMMING UNLOCK REGISTER

# Legend:R = Readable bitW = Writable bitU = Unimplemented bit, read as '0'-n = Value at POR'1' = Bit is set'0' = Bit is clearedx = Bit is unknown

### bit 31-0 NVMKEY<31:0>: Unlock Register bits

These bits are write-only, and read as '0' on any read.

Note: This register is used as part of the unlock sequence to prevent inadvertent writes to the PFM.

## REGISTER 5-3: NVMADDR: FLASH ADDRESS REGISTER

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |  |  |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|--|--|--|

| 24.24        | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |  |

| 31:24        | NVMADDR<31:24>    |                   |                   |                   |                   |                   |                  |                  |  |  |  |

| 00.40        | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |  |

| 23:16        | NVMADDR<23:16>    |                   |                   |                   |                   |                   |                  |                  |  |  |  |

| 45.0         | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |  |

| 15:8         |                   |                   |                   | NVMAD             | DR<15:8>          |                   |                  |                  |  |  |  |

| 7.0          | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |  |

| 7:0          |                   |                   |                   | NVMAE             | DDR<7:0>          |                   |                  |                  |  |  |  |

| Legend:           |                                                     |                      |                    |  |

|-------------------|-----------------------------------------------------|----------------------|--------------------|--|

| R = Readable bit  | W = Writable bit U = Unimplemented bit, read as '0' |                      |                    |  |

| -n = Value at POR | '1' = Bit is set                                    | '0' = Bit is cleared | x = Bit is unknown |  |

bit 31-0 NVMADDR<31:0>: Flash Address bits Bulk/Chip/PFM Erase: Address is ignored. Page Erase: Address identifies the page to erase. Row Program: Address identifies the row to program. Word Program: Address identifies the word to program.

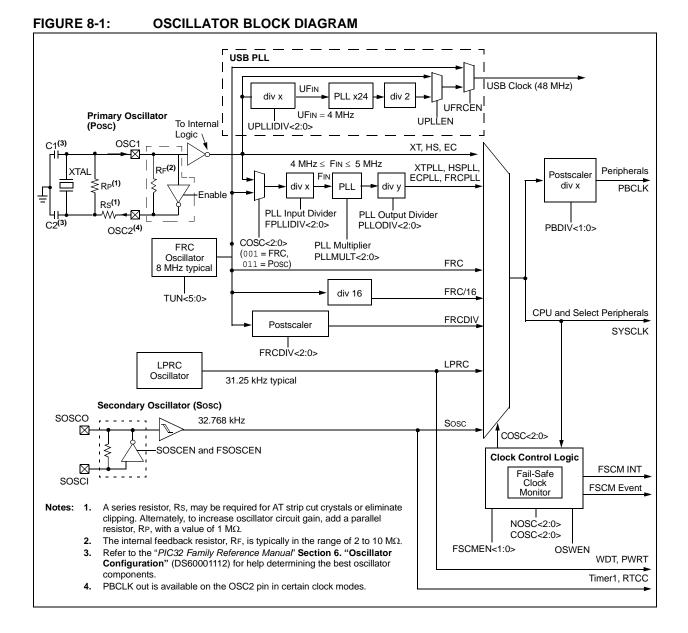

## 8.0 OSCILLATOR CONFIGURATION

Note: This data sheet summarizes the features of the PIC32MX5XX/6XX/7XX family of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to Section 6. "Oscillator" (DS60001112) in the "PIC32 Family Reference Manual", which is available from the Microchip web site (www.microchip.com/PIC32). The Oscillator module has the following features:

- A total of four external and internal oscillator options as clock sources

- On-chip PLL with user-selectable input divider, multiplier and output divider to boost operating frequency on select internal and external oscillator sources

- On-chip user-selectable divisor postscaler on select oscillator sources

- Software-controllable switching between various clock sources

- A Fail-Safe Clock Monitor (FSCM) that detects clock failure and permits safe application recovery or shutdown

- Dedicated On-Chip PLL for USB peripheral

Figure 8-1shows the Oscillator module block diagram.

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|

| 04.04        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 31:24        | _                 | _                 | _                 | —                 | —                 | —                 | —                | _                |

| 23:16        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 23.10        | _                 | _                 |                   | —                 | —                 |                   | —                | —                |

| 45.0         | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 15:8         | _                 | _                 | _                 | —                 | —                 | _                 | —                | —                |

| 7.0          | U-0               | U-0               | U-0               | U-0               | R-0               | R-0               | R-0              | R-0              |

| 7:0          |                   |                   |                   | —                 | RDWR              | [                 | DMACH<2:0>       | •                |

### REGISTER 10-2: DMASTAT: DMA STATUS REGISTER

## Legend:

| 0                 |                  |                      |                    |  |

|-------------------|------------------|----------------------|--------------------|--|

| R = Readable bit  | W = Writable bit | U = Unimplemented b  | it, read as '0'    |  |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared | x = Bit is unknown |  |

#### bit 31-4 Unimplemented: Read as '0'

#### bit 3 RDWR: Read/Write Status bit

1 = Last DMA bus access was a read

0 = Last DMA bus access was a write

## bit 2-0 **DMACH<2:0>:** DMA Channel bits These bits contain the value of the most recent active DMA channel.

## REGISTER 10-3: DMAADDR: DMA ADDRESS REGISTER

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |  |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|--|--|

| 04-04        | R-0               | R-0               | R-0               | R-0               | R-0               | R-0               | R-0              | R-0              |  |  |

| 31:24        | DMAADDR<31:24>    |                   |                   |                   |                   |                   |                  |                  |  |  |

| 00.40        | R-0               | R-0               | R-0               | R-0               | R-0               | R-0               | R-0              | R-0              |  |  |

| 23:16        | DMAADDR<23:16>    |                   |                   |                   |                   |                   |                  |                  |  |  |

| 45.0         | R-0               | R-0               | R-0               | R-0               | R-0               | R-0               | R-0              | R-0              |  |  |

| 15:8         |                   |                   |                   | DMAADDI           | R<15:8>           |                   |                  |                  |  |  |

| 7.0          | R-0               | R-0               | R-0               | R-0               | R-0               | R-0               | R-0              | R-0              |  |  |

| 7:0          |                   |                   | R<7:0>            |                   |                   |                   |                  |                  |  |  |

## Legend:

| Logona.           |                  |                          |                    |

|-------------------|------------------|--------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, r | ead as '0'         |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared     | x = Bit is unknown |

## bit 31-0 DMAADDR<31:0>: DMA Module Address bits

These bits contain the address of the most recent DMA access.

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|

| 31:24        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 31.24        | _                 | _                 |                   | _                 |                   |                   | —                | —                |

| 23:16        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 23.10        | _                 | -                 | _                 | _                 |                   | _                 | —                | _                |

| 15:8         | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 15.0         | _                 | -                 | _                 | _                 |                   | _                 | —                | _                |

| 7:0          | R-0               | U-0               | U-0               | R/W-0             | R/W-0             | U-0               | R/W-0            | R/W-0            |

| 7.0          | UACTPND           | _                 |                   | USLPGRD           | USBBUSY           |                   | USUSPEND         | USBPWR           |

#### REGISTER 11-5: U1PWRC: USB POWER CONTROL REGISTER

## Legend:

| Logona.           |                  |                            |                    |

|-------------------|------------------|----------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, rea | id as '0'          |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared       | x = Bit is unknown |

#### bit 31-8 Unimplemented: Read as '0'

- bit 7 UACTPND: USB Activity Pending bit

- 1 = USB bus activity has been detected; but an interrupt is pending, it has not been generated yet

- 0 = An interrupt is not pending

#### bit 6-5 Unimplemented: Read as '0'

- bit 4 USLPGRD: USB Sleep Entry Guard bit

- 1 = Sleep entry is blocked if USB bus activity is detected or if a notification is pending

- 0 = USB module does not block Sleep entry

#### bit 3 USBBUSY: USB Module Busy bit

- 1 = USB module is active or disabled, but not ready to be enabled

- 0 = USB module is not active and is ready to be enabled

- **Note:** When USBPWR = 0 and USBBUSY = 1, status from all other registers is invalid and writes to all USB module registers produce undefined results.

#### bit 2 Unimplemented: Read as '0'

#### bit 1 USUSPEND: USB Suspend Mode bit

- 1 = USB module is placed in Suspend mode

- (The 48 MHz USB clock will be gated off. The transceiver is placed in a low-power state.)

- 0 = USB module operates normally

- bit 0 USBPWR: USB Operation Enable bit

- 1 = USB module is turned on

- 0 = USB module is disabled

(Outputs held inactive, device pins not used by USB, analog features are shut down to reduce power consumption.)

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|

| 31:24        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 31.24        | _                 | _                 |                   | —                 |                   |                   |                  | —                |

| 23:16        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 23.10        | _                 | _                 |                   | —                 |                   |                   |                  | —                |

| 15:8         | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 10.0         | —                 | _                 | —                 | —                 | —                 | -                 | —                | —                |

| 7.0          | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |

| 7:0          |                   |                   |                   | BDTPTR            | H<23:16>          |                   |                  |                  |

### REGISTER 11-18: U1BDTP2: USB BUFFER DESCRIPTOR TABLE PAGE 2 REGISTER

#### Legend:

| 0                 |                  |                           |                    |

|-------------------|------------------|---------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, re | ead as '0'         |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared      | x = Bit is unknown |

#### bit 31-8 Unimplemented: Read as '0'

#### bit 7-0 BDTPTRH<23:16>: BDT Base Address bits

This 8-bit value provides address bits 23 through 16 of the BDT base address, which defines the starting location of the BDT in system memory.

The 32-bit BDT base address is 512-byte aligned.

#### REGISTER 11-19: U1BDTP3: USB BUFFER DESCRIPTOR TABLE PAGE 3 REGISTER

| Bit<br>Range   | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

|----------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|

| 31:24          | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 31.24          |                   | —                 |                   | —                 |                   |                   | —                | —                |

| 22:16          | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 23:16          |                   | —                 |                   | —                 |                   |                   | —                | —                |

| 15:8           | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 10.0           |                   | —                 |                   | —                 |                   |                   | —                | —                |

| 7:0            | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |

| BDTPTRU<31:24> |                   |                   |                   |                   |                   |                   |                  |                  |

| Legend:           |                  |                           |                    |

|-------------------|------------------|---------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, re | ead as '0'         |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared      | x = Bit is unknown |

#### bit 31-8 Unimplemented: Read as '0'

#### bit 7-0 BDTPTRU<31:24>: BDT Base Address bits

This 8-bit value provides address bits 31 through 24 of the BDT base address, defines the starting location of the BDT in system memory.

The 32-bit BDT base address is 512-byte aligned.

## PIC32MX5XX/6XX/7XX

NOTES:

## TABLE 12-7: PORTE REGISTER MAP FOR PIC32MX534F064H, PIC32MX564F064H, PIC32MX564F128H, PIC32MX575F256H, PIC32MX575F512H, PIC32MX664F064H, PIC32MX664F128H, PIC32MX675F256H, PIC32MX675F512H, PIC32MX695F512H,

#### PIC32MX775F256H, PIC32MX775F512H AND PIC32MX795F512H DEVICES Virtual Address (BF88\_#) Bits Resets Bit Range Register Name<sup>(1)</sup> 31/15 30/14 29/13 28/12 27/11 26/10 25/9 24/8 23/7 22/6 21/5 20/4 19/3 18/2 17/1 16/0 ₹ 31:16 \_ 0000 \_ 6100 TRISE 15:0 TRISE7 TRISE6 TRISE5 TRISE4 TRISE3 TRISE2 TRISE1 TRISE0 00FF \_ \_ \_ \_ \_ \_ 31:16 0000 PORTE 6110 15:0 \_ \_ \_ \_ \_ \_ RE7 RE6 RE5 RE4 RE3 RE2 RE1 RE0 xxxx \_ \_ 0000 31:16 \_ \_ \_ \_ 6120 LATE 15:0 \_ \_ \_ \_ \_ \_ \_ \_ LATE7 LATE6 LATE5 LATE4 LATE3 LATE2 LATE1 LATE0 xxxx 31:16 0000 \_ \_ \_ \_ \_ \_ \_ \_ 6130 ODCE 15:0 \_ \_ \_ ODCE7 0DCE6 ODCE5 ODCE4 ODCE3 ODCE2 ODCE1 ODCE0 0000 Leaend:

All registers in this table have corresponding CLR, SET and INV registers at their virtual addresses, plus offsets of 0x4, 0x8 and 0xC, respectively. See Section 12.1.1 "CLR, SET and INV Registers" for more Note 1: information.

#### TABLE 12-8: PORTE REGISTER MAP FOR PIC32MX534F064L, PIC32MX564F064L, PIC32MX564F128L, PIC32MX575F256L, PIC32MX575F512L, PIC32MX664F064L, PIC32MX664F128L, PIC32MX675F256L, PIC32MX675F512L, PIC32MX695F512L, PIC32MX764F128L, PIC32MX775F256L, PIC32MX775F512L AND PIC32MX795F512L DEVICES

| ess                        |                                 | 0         |       |       |       |       |       |       |        | Bi     | its    |        |        |        |        |        |        |        | s          |

|----------------------------|---------------------------------|-----------|-------|-------|-------|-------|-------|-------|--------|--------|--------|--------|--------|--------|--------|--------|--------|--------|------------|

| Virtual Addres<br>(BF88_#) | Register<br>Name <sup>(1)</sup> | Bit Range | 31/15 | 30/14 | 29/13 | 28/12 | 27/11 | 26/10 | 25/9   | 24/8   | 23/7   | 22/6   | 21/5   | 20/4   | 19/3   | 18/2   | 17/1   | 16/0   | All Resets |

| 6100                       | TRISE                           | 31:16     | _     | _     | -     | _     | -     | _     | _      | —      | _      | _      | -      | —      | _      | —      | -      | _      | 0000       |

| 6100                       | IRISE                           | 15:0      | Ι     | _     | _     | -     | _     | _     | TRISE9 | TRISE8 | TRISE7 | TRISE6 | TRISE5 | TRISE4 | TRISE3 | TRISE2 | TRISE1 | TRISE0 | 03FF       |

| 6110                       | PORTE                           | 31:16     | -     | —     | —     | _     | -     | —     | —      | —      | —      | —      | -      | —      | —      | —      |        | -      | 0000       |

| 6110                       | PORTE                           | 15:0      | -     | —     | _     | _     | _     | _     | RE9    | RE8    | RE7    | RE6    | RE5    | RE4    | RE3    | RE2    | RE1    | RE0    | xxxx       |

| C4 00                      | LATE                            | 31:16     | -     | _     | _     | -     | -     | _     | _      | _      | _      | _      | -      | _      | _      | _      | -      | _      | 0000       |

| 6120                       | LATE                            | 15:0      | —     | _     | _     | _     | _     | _     | LATE9  | LATE8  | LATE7  | LATE6  | LATE5  | LATE4  | LATE3  | LATE2  | LATE1  | LATE0  | xxxx       |

| 6130                       | ODCE                            | 31:16     | _     | -     |       | _     | _     |       |        |        |        |        | —      |        |        |        | —      | —      | 0000       |

| 0130                       | ODCE                            | 15:0      | _     | _     | _     | —     | _     | _     | ODCE9  | ODCE8  | ODCE7  | 0DCE6  | ODCE5  | ODCE4  | ODCE3  | ODCE2  | ODCE1  | ODCE0  | 0000       |

Legend: x = unknown value on Reset; --- = unimplemented, read as '0'. Reset values are shown in hexadecimal.

Note 1: All registers in this table have corresponding CLR, SET and INV registers at their virtual addresses, plus offsets of 0x4, 0x8 and 0xC, respectively. See Section 12.1.1 "CLR, SET and INV Registers" for more information

| Bit   | Bit        | Bit        | Bit        | Bit        | Bit        | Bit        | Bit       | Bit       |

|-------|------------|------------|------------|------------|------------|------------|-----------|-----------|

| Range | 31/23/15/7 | 30/22/14/6 | 29/21/13/5 | 28/20/12/4 | 27/19/11/3 | 26/18/10/2 | 25/17/9/1 | 24/16/8/0 |

| 24.24 | U-0        | U-0        | U-0        | U-0        | U-0        | U-0        | U-0       | U-0       |

| 31:24 | —          | _          | -          | —          | —          | —          | _         | _         |

| 00.40 | U-0        | U-0        | U-0        | U-0        | U-0        | U-0        | U-0       | U-0       |

| 23:16 | —          | _          | _          | _          | _          | —          | _         | _         |

| 45.0  | R-0, HSC   | R-0, HSC   | U-0        | U-0        | U-0        | R/C-0, HS  | R-0, HSC  | R-0, HSC  |

| 15:8  | ACKSTAT    | TRSTAT     | _          | —          | —          | BCL        | GCSTAT    | ADD10     |

| 7.0   | R/C-0, HS  | R/C-0, HS  | R-0, HSC   | R/C-0, HSC | R/C-0, HSC | R-0, HSC   | R-0, HSC  | R-0, HSC  |

| 7:0   | IWCOL      | I2COV      | D_A        | Р          | S          | R_W        | RBF       | TBF       |

## REGISTER 19-2: I2CxSTAT: I<sup>2</sup>C STATUS REGISTER

| Legend:                           | HS = Set by hardware | HSC = Hardware set/cleared |                   |  |

|-----------------------------------|----------------------|----------------------------|-------------------|--|

| R = Readable bit W = Writable bit |                      | U = Unimplemented bit, r   | ead as '0'        |  |

| -n = Value at POR                 | '1' = Bit is set     | '0' = Bit is cleared       | C = Clearable bit |  |

#### bit 31-16 Unimplemented: Read as '0'

- bit 15 **ACKSTAT:** Acknowledge Status bit (when operating as I<sup>2</sup>C master, applicable to master transmit operation) This bit is set or cleared by hardware at the end of a slave Acknowledge.

- 1 = NACK received from slave

- 0 = ACK received from slave

- bit 14 **TRSTAT:** Transmit Status bit (when operating as I<sup>2</sup>C master, applicable to master transmit operation) This bit is set by hardware at the beginning of a master transmission, and is cleared by hardware at the end of a slave Acknowledge.

- 1 = Master transmit is in progress (8 bits + ACK)

- 0 = Master transmit is not in progress

- bit 13-11 Unimplemented: Read as '0'

- bit 10 BCL: Master Bus Collision Detect bit

This bit is set by hardware at the detection of a bus collision.

- 1 = A bus collision has been detected during a master operation

- 0 = No collision

- bit 9 GCSTAT: General Call Status bit

This bit is set by hardware when the address matches the general call address, and is cleared by hardware clear at a Stop detection.

- 1 = General call address was received

- 0 = General call address was not received

#### bit 8 ADD10: 10-bit Address Status bit

This bit is set by hardware upon a match of the 2nd byte of the matched 10-bit address, and is cleared by hardware at a Stop detection.

- 1 = 10-bit address was matched

- 0 = 10-bit address was not matched

#### bit 7 IWCOL: Write Collision Detect bit

- This bit is set by hardware at the occurrence of a write to I2CxTRN while busy (cleared by software).

- 1 = An attempt to write the I2CxTRN register failed because the  $I^2C$  module is busy

- 0 = No collision

## bit 6 I2COV: Receive Overflow Flag bit

- This bit is set by hardware at an attempt to transfer I2CxRSR to I2CxRCV (cleared by software).

- 1 = A byte was received while the I2CxRCV register is still holding the previous byte

- 0 = No overflow

#### I2CxSTAT: I<sup>2</sup>C STATUS REGISTER (CONTINUED) REGISTER 19-2: **D\_A:** Data/Address bit (when operating as I<sup>2</sup>C slave) bit 5 This bit is cleared by hardware upon a device address match, and is set by hardware by reception of the slave byte. 1 = Indicates that the last byte received was data 0 = Indicates that the last byte received was device address bit 4 P: Stop bit This bit is set or cleared by hardware when a Start, Repeated Start, or Stop condition is detected. 1 = Indicates that a Stop bit has been detected last 0 = Stop bit was not detected last bit 3 S: Start bit This bit is set or cleared by hardware when a Start, Repeated Start, or Stop condition is detected. 1 = Indicates that a Start (or Repeated Start) bit has been detected last 0 = Start bit was not detected last **R\_W:** Read/Write Information bit (when operating as I<sup>2</sup>C slave) bit 2 This bit is set or cleared by hardware after reception of an I<sup>2</sup>C device address byte. 1 = Read – indicates data transfer is output from slave 0 = Write - indicates data transfer is input to slave **RBF:** Receive Buffer Full Status bit bit 1 This bit is set by hardware when the I2CxRCV register is written with a received byte, and is cleared by hardware when software reads I2CxRCV. 1 = Receive complete, I2CxRCV is full 0 = Receive not complete, I2CxRCV is empty bit 0 TBF: Transmit Buffer Full Status bit This bit is set by hardware when software writes to the I2CxTRN register, and is cleared by hardware upon completion of data transmission.

1 = Transmit in progress, I2CxTRN is full

0 = Transmit complete, I2CxTRN is empty

|                             |                                 | PIC32MX775F512L AND PIC32MX795F512L DEVICES (CONTINUED) |         |                |        |       |       |            |      |         |         |                |         |       |       |            |             |        |            |

|-----------------------------|---------------------------------|---------------------------------------------------------|---------|----------------|--------|-------|-------|------------|------|---------|---------|----------------|---------|-------|-------|------------|-------------|--------|------------|

| ess                         |                                 | é                                                       |         |                |        |       |       |            |      | Bit     | s       |                |         |       |       |            |             |        |            |

| Virtual Address<br>(BF88_#) | Register<br>Name <sup>(1)</sup> | Bit Range                                               | 31/15   | 30/14          | 29/13  | 28/12 | 27/11 | 26/10      | 25/9 | 24/8    | 23/7    | 22/6           | 21/5    | 20/4  | 19/3  | 18/2       | 17/1        | 16/0   | All Resets |

| C100                        | C2FLTCON4                       | 31:16                                                   | FLTEN19 | MSEL1          | 9<1:0> |       |       | FSEL19<4:0 | >    |         | FLTEN18 | MSEL1          | 8<1:0>  |       | F     | SEL18<4:0  | >           |        | 0000       |

| 0100                        | C2FLICON4                       | 15:0                                                    | FLTEN17 | MSEL1          | 7<1:0> |       |       | FSEL17<4:0 | >    |         | FLTEN16 | MSEL1          | 6<1:0>  |       |       | FSEL16<4:0 | ):          |        | 0000       |

| C110                        | C2FLTCON5                       | 31:16                                                   | FLTEN23 | MSEL2          | 3<1:0> |       |       | FSEL23<4:0 | >    |         | FLTEN22 | MSEL2          | 22<1:0> |       | F     | SEL22<4:0  | >           |        | 0000       |

| CIIU                        | CZFLICONS                       | 15:0                                                    | FLTEN21 | MSEL2          | 1<1:0> |       |       | FSEL21<4:0 | >    |         | FLTEN20 | MSEL2          | 20<1:0> |       | F     | SEL20<4:0  | >           |        | 0000       |

| C120                        | C2FLTCON6                       | 31:16                                                   | FLTEN27 | MSEL2          | 7<1:0> |       |       | FSEL27<4:0 | >    |         | FLTEN26 | MSEL2          | 26<1:0> |       | F     | SEL26<4:0  | >           |        | 0000       |

| 0120                        | OZI EI CONO                     | 15:0                                                    | FLTEN25 | MSEL2          | 5<1:0> |       |       | FSEL25<4:0 | >    |         | FLTEN24 | MSEL2          | 24<1:0> |       | F     | SEL24<4:0  | >           |        | 0000       |

| C130                        | C2FLTCON7                       | 31:16                                                   | FLTEN31 | MSEL3          | 1<1:0> |       |       | FSEL31<4:0 | >    |         | FLTEN30 | MSEL3          | 80<1:0> |       | F     | SEL30<4:0  | >           |        | 0000       |

| 0100                        |                                 |                                                         | FLTEN29 | MSEL2          | 9<1:0> |       |       | FSEL29<4:0 | >    |         | FLTEN28 | MSEL2          | 28<1:0> |       |       | SEL28<4:0  |             |        | 0000       |

| C140                        | 02.00.11                        | 31:16                                                   |         |                |        |       |       | SID<10:0>  |      |         |         |                |         |       | EXID  | —          | EID<        | 17:16> | xxxx       |

|                             | (n = 0-31)                      | 15:0                                                    |         |                |        |       |       |            |      | EID<1   | 5:0>    |                |         |       |       |            |             |        | xxxx       |

| C340                        |                                 | 31:16<br>15:0                                           |         |                |        |       |       |            |      | C2FIFOB | A<31:0> |                |         |       |       |            |             |        | 0000       |

| 0250                        | C2FIFOCONn<br>(n = 0-31)        | 31:16                                                   | _       | —              | —      | —     | —     | -          | —    | —       | —       | _              | —       |       |       | FSIZE<4:0> | <b>&gt;</b> |        | 0000       |

| 0350                        | (n = 0-31)                      | 15:0                                                    |         | FRESET         | UINC   | DONLY |       | —          | _    |         | TXEN    | TXABAT         | TXLARB  | TXERR | TXREQ | RTREN      | TXPR        | l<1:0> | 0000       |

| C360                        | C2FIFOINTn                      | 31:16                                                   | _       | —              | —      | —     |       |            |      |         |         | RXN<br>EMPTYIE | 0000    |       |       |            |             |        |            |

| 0300                        | (n = 0-31)                      | 15:0                                                    | -       | —              | —      |       |       |            |      |         |         | RXN<br>EMPTYIF | 0000    |       |       |            |             |        |            |

| C370                        | C2FIFOUAn                       |                                                         |         | C2FIFOUA<31:0> |        |       |       |            |      |         | 0000    |                |         |       |       |            |             |        |            |

|                             | (n = 0-31)                      | 15:0                                                    |         |                |        |       |       |            |      |         |         | 0000           |         |       |       |            |             |        |            |

| C380                        | C2FIFOCIn<br>(n = 0-31)         | 31:16                                                   |         | _              | _      | _     | _     |            | _    | _       | _       | —              | _       | _     |       |            |             | —      | 0000       |

|                             | (1 = 0.31)                      | 15:0                                                    | —       | —              | —      | —     | —     | —          | —    | _       | —       | —              | —       |       | C     | 2FIFOCI<4: | 0>          |        | 0000       |

## TABLE 24-2: CAN2 REGISTER SUMMARY FOR PIC32MX775F256H, PIC32MX775F512H, PIC32MX795F512H, PIC32MX775F256L, PIC32MX775F512L, AND PIC32MX795F512L, DEVICES (CONTINUED)

Legend:

x = unknown value on Reset; — = unimplemented, read as '0'. Reset values are shown in hexadecimal. All registers in this table have corresponding CLR, SET and INV registers at their virtual addresses, plus offsets of 0x4, 0x8 and 0xC, respectively. See Section 12.1.1 "CLR, SET and INV Registers" for more Note 1: information.

## PIC32MX5XX/6XX/7XX

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4     | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

|--------------|-------------------|-------------------|-------------------|-----------------------|-------------------|-------------------|------------------|------------------|

| 31:24        | R/W-0             | R/W-0             | R/W-0             | R/W-0                 | R/W-0             | U-0               | U-0              | U-0              |

| 31.24        | IVRIE             | WAKIE             | CERRIE            | SERRIE                | RBOVIE            | —                 | —                | —                |

| 23:16        | U-0               | U-0               | U-0               | U-0                   | R/W-0             | R/W-0             | R/W-0            | R/W-0            |

| 23.10        | _                 | —                 | _                 | _                     | MODIE             | CTMRIE            | RBIE             | TBIE             |

| 15.0         | R/W-0             | R/W-0             | R/W-0             | R/W-0                 | R/W-0             | U-0               | U-0              | U-0              |

| 15:8         | IVRIF             | WAKIF             | CERRIF            | SERRIF <sup>(1)</sup> | RBOVIF            | —                 | —                | —                |

| 7.0          | U-0               | U-0               | U-0               | U-0                   | R/W-0             | R/W-0             | R/W-0            | R/W-0            |

| 7:0          |                   |                   |                   |                       | MODIF             | CTMRIF            | RBIF             | TBIF             |

## REGISTER 24-3: CIINT: CAN INTERRUPT REGISTER

### Legend:

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, r | ead as '0'         |

|-------------------|------------------|--------------------------|--------------------|

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared     | x = Bit is unknown |

| bit 31    | IVRIE: Invalid Message Received Interrupt Enable bit<br>1 = Interrupt request is enabled<br>0 = Interrupt request is not enabled                                 |

|-----------|------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| bit 30    | <b>WAKIE:</b> CAN Bus Activity Wake-up Interrupt Enable bit<br>1 = Interrupt request is enabled<br>0 = Interrupt request is not enabled                          |

| bit 29    | <b>CERRIE:</b> CAN Bus Error Interrupt Enable bit<br>1 = Interrupt request is enabled<br>0 = Interrupt request is not enabled                                    |

| bit 28    | SERRIE: System Error Interrupt Enable bit<br>1 = Interrupt request is enabled<br>0 = Interrupt request is not enabled                                            |

| bit 27    | <b>RBOVIE:</b> Receive Buffer Overflow Interrupt Enable bit<br>1 = Interrupt request is enabled<br>0 = Interrupt request is not enabled                          |

| bit 26-20 | Unimplemented: Read as '0'                                                                                                                                       |

| bit 19    | <b>MODIE:</b> Mode Change Interrupt Enable bit<br>1 = Interrupt request is enabled<br>0 = Interrupt request is not enabled                                       |

| bit 18    | <b>CTMRIE:</b> CAN Timestamp Timer Interrupt Enable bit<br>1 = Interrupt request is enabled<br>0 = Interrupt request is not enabled                              |

| bit 17    | <b>RBIE:</b> Receive Buffer Interrupt Enable bit<br>1 = Interrupt request is enabled<br>0 = Interrupt request is not enabled                                     |

| bit 16    | <b>TBIE:</b> Transmit Buffer Interrupt Enable bit<br>1 = Interrupt request is enabled<br>0 = Interrupt request is not enabled                                    |

| bit 15    | <b>IVRIF:</b> Invalid Message Received Interrupt Flag bit<br>1 = An invalid messages interrupt has occurred<br>0 = An invalid message interrupt has not occurred |

| Note 1:   | This bit can only be cleared by turning the CAN module Off and On by                                                                                             |

**Note 1:** This bit can only be cleared by turning the CAN module Off and On by clearing or setting the ON bit (CiCON<15>).

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1   | Bit<br>24/16/8/0   |  |  |  |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|--------------------|--------------------|--|--|--|

| 31:24        | R/W-0              | R/W-0              |  |  |  |

| 31.24        | CiFIFOBA<31:24>   |                   |                   |                   |                   |                   |                    |                    |  |  |  |

| 23:16        | R/W-0              | R/W-0              |  |  |  |

| 23.10        | CiFIFOBA<23:16>   |                   |                   |                   |                   |                   |                    |                    |  |  |  |

| 15:8         | R/W-0              | R/W-0              |  |  |  |

| 0.61         | CiFIFOBA<15:8>    |                   |                   |                   |                   |                   |                    |                    |  |  |  |

| 7:0          | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R-0 <sup>(1)</sup> | R-0 <sup>(1)</sup> |  |  |  |

| 7.0          |                   |                   |                   | CiFIFO            | 3A<7:0>           |                   |                    |                    |  |  |  |

### REGISTER 24-19: CIFIFOBA: CAN MESSAGE BUFFER BASE ADDRESS REGISTER

#### Legend:

| Logona.           |                  |                        |                    |

|-------------------|------------------|------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, | read as '0'        |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared   | x = Bit is unknown |

bit 31-0 CiFIFOBA<31:0>: CAN FIFO Base Address bits

These bits define the base address of all message buffers. Individual message buffers are located based on the size of the previous message buffers. This address is a physical address. Bits <1:0> are read-only and read as '0', forcing the messages to be 32-bit word-aligned in device RAM.

**Note 1:** This bit is unimplemented and will always read '0', which forces word-alignment of messages.

**Note:** This register can only be modified when the CAN module is in Configuration mode (OPMOD<2:0> (CiCON<23:21>) = 100).

## REGISTER 24-20: CiFIFOCONn: CAN FIFO CONTROL REGISTER 'n' (n = 0 THROUGH 31)

- bit 6 TXABAT: Message Aborted bit<sup>(2)</sup> 1 = Message was aborted 0 = Message completed successfully bit 5 TXLARB: Message Lost Arbitration bit<sup>(3)</sup> 1 = Message lost arbitration while being sent 0 = Message did not lose arbitration while being sent TXERR: Error Detected During Transmission bit<sup>(3)</sup> bit 4 1 = A bus error occured while the message was being sent 0 = A bus error did not occur while the message was being sent bit 3 **TXREQ:** Message Send Request TXEN = 1: (FIFO configured as a Transmit FIFO) Setting this bit to '1' requests sending a message. The bit will automatically clear when all the messages queued in the FIFO are successfully sent. Clearing the bit to '0' while set ('1') will request a message abort. TXEN = 0: (FIFO configured as a receive FIFO) This bit has no effect. bit 2 RTREN: Auto RTR Enable bit 1 = When a remote transmit is received, TXREQ will be set 0 = When a remote transmit is received, TXREQ will be unaffected bit 1-0 TXPR<1:0>: Message Transmit Priority bits 11 = Highest message priority 10 = High intermediate message priority 01 = Low intermediate message priority 00 = Lowest message priority Note 1: These bits can only be modified when the CAN module is in Configuration mode (OPMOD<2:0> bits (CiCON<23:21>) = 100).

- 2: This bit is updated when a message completes (or aborts) or when the FIFO is reset.

- 3: This bit is reset on any read of this register or when the FIFO is reset.

## REGISTER 29-1: DEVCFG0: DEVICE CONFIGURATION WORD 0 (CONTINUED)

- bit 3 ICESEL: In-Circuit Emulator/Debugger Communication Channel Select bit

- 1 = PGEC2/PGED2 pair is used

- 0 = PGEC1/PGED1 pair is used

- bit 2 Reserved: Write '1'

- bit 1-0 DEBUG<1:0>: Background Debugger Enable bits (forced to '11' if code-protect is enabled)

- 11 = Debugger is disabled

- 10 = Debugger is enabled

- 01 = Reserved (same as '11' setting)

- 00 = Reserved (same as '11' setting)

## TABLE 32-36: ADC MODULE SPECIFICATIONS

| AC CHARACTERISTICS |            |                                                      | Standard Operating Conditions (see Note 5): 2.5V to 3.6V<br>(unless otherwise stated)Operating temperature $-40^{\circ}C \le TA \le +85^{\circ}C$ for Industrial<br>$-40^{\circ}C \le TA \le +105^{\circ}C$ for V-Temp |          |                                  |          |                                                                                               |

|--------------------|------------|------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|----------------------------------|----------|-----------------------------------------------------------------------------------------------|

| Param.<br>No.      | Symbol     | Characteristics                                      | Min.                                                                                                                                                                                                                   | Typical  | Max.                             | Units    | Conditions                                                                                    |

| Device             | Supply     | ·                                                    |                                                                                                                                                                                                                        |          | •                                | •        | •                                                                                             |

| AD01               | AVdd       | Module VDD Supply                                    | Greater of<br>VDD – 0.3<br>or 2.5                                                                                                                                                                                      | _        | Lesser of<br>VDD + 0.3<br>or 3.6 | V        | _                                                                                             |

| AD02               | AVss       | Module Vss Supply                                    | Vss                                                                                                                                                                                                                    | _        | Vss + 0.3                        | V        | —                                                                                             |

| Referen            | ce Inputs  |                                                      | •                                                                                                                                                                                                                      |          |                                  |          | ·                                                                                             |

| AD05<br>AD05a      | Vrefh      | Reference Voltage High                               | AVss + 2.0<br>2.5                                                                                                                                                                                                      |          | AVDD<br>3.6                      | V<br>V   | <b>(Note 1)</b><br>VREFH = AVDD <b>(Note 3)</b>                                               |

| AD06               | Vrefl      | Reference Voltage Low                                | AVss                                                                                                                                                                                                                   | _        | Vrefh – 2.0                      | V        | (Note 1)                                                                                      |

| AD07               | Vref       | Absolute Reference<br>Voltage (VREFH – VREFL)        | 2.0                                                                                                                                                                                                                    | _        | AVdd                             | V        | (Note 3)                                                                                      |

| AD08<br>AD08a      | IREF       | Current Drain                                        | _                                                                                                                                                                                                                      | 250<br>— | 400<br>3                         | μΑ<br>μΑ | ADC operating<br>ADC off                                                                      |

| Analog             | Input      | ·                                                    |                                                                                                                                                                                                                        |          |                                  |          |                                                                                               |

| AD12               | VINH-VINL  | Full-Scale Input Span                                | VREFL                                                                                                                                                                                                                  |          | Vrefh                            | V        | —                                                                                             |

| AD13               | VINL       | Absolute VINL Input<br>Voltage                       | AVss - 0.3                                                                                                                                                                                                             |          | AVdd/2                           | V        | _                                                                                             |

| AD14               | Vin        | Absolute Input Voltage                               | AVss - 0.3                                                                                                                                                                                                             |          | AVDD + 0.3                       | V        | _                                                                                             |

| AD15               |            | Leakage Current                                      | _                                                                                                                                                                                                                      | ±0.001   | ±0.610                           | μA       | VINL = AVSS = VREFL = 0V,<br>AVDD = VREFH = $3.3V$<br>Source Impedance = $10 \text{ k}\Omega$ |

| AD17               | Rin        | Recommended<br>Impedance of Analog<br>Voltage Source | _                                                                                                                                                                                                                      | —        | 5K                               | Ω        | (Note 1)                                                                                      |

| ADC Ac             | curacy – N | leasurements with Exter                              | nal VREF+/VR                                                                                                                                                                                                           | REF-     |                                  |          | ·                                                                                             |

| AD20c              | Nr         | Resolution                                           | 10 data bits                                                                                                                                                                                                           |          | bits                             | —        |                                                                                               |

| AD21c              | INL        | Integral Nonlinearity                                | > -1                                                                                                                                                                                                                   |          | < 1                              | LSb      | VINL = AVSS = VREFL = 0V,<br>AVDD = VREFH = 3.3V                                              |

| AD22c              | DNL        | Differential Nonlinearity                            | > -1                                                                                                                                                                                                                   | —        | < 1                              | LSb      | VINL = AVSS = VREFL = 0V,<br>AVDD = VREFH = 3.3V<br>(Note 2)                                  |

| AD23c              | Gerr       | Gain Error                                           | > -1                                                                                                                                                                                                                   | —        | < 1                              | LSb      | VINL = AVSS = VREFL = 0V,<br>AVDD = VREFH = 3.3V                                              |

| AD24c              | Eoff       | Offset Error                                         | > -1                                                                                                                                                                                                                   | —        | < 1                              | LSb      | VINL = AVSS = 0V,<br>AVDD = 3.3V                                                              |

| AD25c              |            | Monotonicity                                         | —                                                                                                                                                                                                                      |          | _                                | —        | Guaranteed                                                                                    |

**Note 1:** These parameters are not characterized or tested in manufacturing.

**2:** With no missing codes.

**3:** These parameters are characterized, but not tested in manufacturing.

4: Characterized with a 1 kHz sine wave.

**5:** The ADC module is functional at VBORMIN < VDD < 2.5V, but with degraded performance. Unless otherwise stated, module functionality is tested, but not characterized.

## TABLE 32-37: 10-BIT ADC CONVERSION RATE PARAMETERS

| Standard Operating Conditions (see Note 3): 2.5V to 3.6V<br>(unless otherwise stated)Operating temperature $-40^{\circ}C \le TA \le +85^{\circ}C$ for Industrial<br>$-40^{\circ}C \le TA \le +105^{\circ}C$ for V-Temp |                |                             |               |              |                            |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------|-----------------------------|---------------|--------------|----------------------------|

| ADC Speed <sup>(2)</sup>                                                                                                                                                                                               | TAD<br>Minimum | Sampling<br>Time<br>Minimum | Rs<br>Maximum | Vdd          | ADC Channels Configuration |

| 1 Msps to<br>400 ksps <sup>(1)</sup>                                                                                                                                                                                   | 65 ns          | 132 ns                      | 500Ω          | 3.0V to 3.6V | ANX CHX<br>S&H<br>ADC      |

| Up to 400 ksps                                                                                                                                                                                                         | 200 ns         | 200 ns                      | 5.0 kΩ        | 2.5V to 3.6V | ANX ADC<br>ANX or VREF-    |

Note 1: External VREF- and VREF+ pins must be used for correct operation.

2: These parameters are characterized, but not tested in manufacturing.

**3:** The ADC module is functional at VBORMIN < VDD < 2.5V, but with degraded performance. Unless otherwise stated, module functionality is tested, but not characterized.

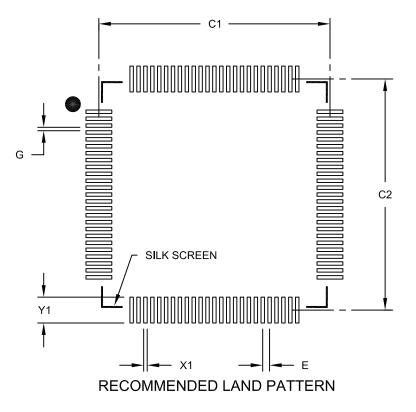

100-Lead Plastic Thin Quad Flatpack (PT)-12x12x1mm Body, 2.00 mm Footprint [TQFP]

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

|                           | MILLIMETERS |      |          |      |

|---------------------------|-------------|------|----------|------|

| Dimensior                 | MIN         | NOM  | MAX      |      |

| Contact Pitch             | E           |      | 0.40 BSC |      |

| Contact Pad Spacing       | C1          |      | 13.40    |      |

| Contact Pad Spacing       | C2          |      | 13.40    |      |

| Contact Pad Width (X100)  | X1          |      |          | 0.20 |

| Contact Pad Length (X100) | Y1          |      |          | 1.50 |

| Distance Between Pads     | G           | 0.20 |          |      |

Notes:

1. Dimensioning and tolerancing per ASME Y14.5M

BSC: Basic Dimension. Theoretically exact value shown without tolerances.

Microchip Technology Drawing No. C04-2100B

## APPENDIX B: REVISION HISTORY

## **Revision A (August 2009)**

This is the initial released version of this document.

## **Revision B (November 2009)**

The revision includes the following global update:

Added Note 2 to the shaded table that appears at the beginning of each chapter. This new note provides information regarding the availability of registers and their associated bits.

Other major changes are referenced by their respective chapter/section in Table B-1.

| Section Name                                                                  | Update Description                                                                                                                                                       |  |  |  |

|-------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| "High-Performance, USB, CAN and<br>Ethernet 32-bit Flash<br>Microcontrollers" | Added the following devices:<br>- PIC32MX575F256L<br>- PIC32MX695F512L                                                                                                   |  |  |  |

|                                                                               | <ul> <li>PIC32MX695F512H</li> <li>The 100-pin TQFP pin diagrams have been updated to reflect the current pin name locations (see the "Pin Diagrams" section).</li> </ul> |  |  |  |

|                                                                               | Added the 121-pin Ball Grid Array (XBGA) pin diagram.                                                                                                                    |  |  |  |

|                                                                               | Updated Table 1: "PIC32 USB and CAN – Features"                                                                                                                          |  |  |  |

|                                                                               | Added the following tables:                                                                                                                                              |  |  |  |

|                                                                               | <ul> <li>Table 4: "Pin Names: PIC32MX534F064L, PIC32MX564F064L,<br/>PIC32MX564F128L, PIC32MX575F256L and PIC32MX575F512L<br/>Devices"</li> </ul>                         |  |  |  |

|                                                                               | <ul> <li>Table 5: "Pin Names: PIC32MX664F064L, PIC32MX664F128L,<br/>PIC32MX675F256L, PIC32MX675F512L and PIC32MX695F512L<br/>Devices"</li> </ul>                         |  |  |  |

|                                                                               | <ul> <li>Table 6: "Pin Names: PIC32MX775F256L, PIC32MX775F512L and<br/>PIC32MX795F512L Devices"</li> </ul>                                                               |  |  |  |

|                                                                               | Updated the following pins as 5V tolerant:                                                                                                                               |  |  |  |

|                                                                               | - 64-pin QFN: Pin 36 (D-/RG3) and Pin 37 (D+/RG2)                                                                                                                        |  |  |  |

|                                                                               | <ul> <li>64-pin TQFP: Pin 36 (D-/RG3) and Pin 37 (D+/RG2)</li> <li>100-pin TQFP: Pin 56 (D-/RG3) and Pin 57 (D+/RG2)</li> </ul>                                          |  |  |  |

| 1.0 "Guidelines for Getting Started                                           | Removed the last sentence of 1.3.1 "Internal Regulator Mode".                                                                                                            |  |  |  |

| with 32-bit Microcontrollers"                                                 | Removed Section 2.3.2 "External Regulator Mode"                                                                                                                          |  |  |  |

## TABLE B-1: MAJOR SECTION UPDATES

## TABLE B-3: MAJOR SECTION UPDATES (CONTINUED)

| Section Name                             | Update Description                                                                                                                                                                                                                                                                                                                                                                                                |

|------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 4.0 "Memory Organization"<br>(Continued) | Made the following bit name changes in the I2C1, I2C3, I2C4 and I2C5 Register Map (Table 4-11):                                                                                                                                                                                                                                                                                                                   |

|                                          | <ul> <li>I2C3BRG SFR: I2C1BRG was changed to I2C3BRG</li> <li>I2C4BRG SFR: I2C1BRG was changed to I2C4BRG</li> <li>I2C5BRG SFR: I2C1BRG was changed to I2C5BRG</li> <li>I2C4TRN SFR: I2CT1DATA was changed to I2CT2ADATA</li> <li>I2C4RCV SFR: I2CR2DATA was changed to I2CR2ADATA</li> <li>I2C5TRN SFR: I2CT1DATA was changed to I2CT3ADATA</li> <li>I2C5RCV SFR: I2CR1DATA was changed to I2CR3ADATA</li> </ul> |

|                                          | Added the RTSMD bit and UEN<1:0> bits to the UART1A, UART1B, UART2A, UART2B, UART3A and UART3B Register Map (Table 4-13)                                                                                                                                                                                                                                                                                          |

|                                          | Added the SIDL bit to the DMA Global Register Map (Table 4-17).                                                                                                                                                                                                                                                                                                                                                   |

|                                          | Changed the CM bit to CMR in the System Control Register Map (Table 4-23).                                                                                                                                                                                                                                                                                                                                        |

|                                          | Added the following devices to the I2C2, SPI1, PORTA, PORTC, PORTD, PORTE, PORTF, PORTG, Change Notice and Pull-up Register Maps (Table 4-12, Table 4-14, Table 4-24, Table 4-27, Table 4-29, Table 4-31, Table 4-33, Table 4-35 and Table 4-36):                                                                                                                                                                 |

|                                          | <ul> <li>PIC32MX534F064L</li> <li>PIC32MX564F064L</li> <li>PIC32MX564F128L</li> <li>PIC32MX664F064L</li> <li>PIC32MX664F128L</li> <li>PIC32MX764F128L</li> </ul>                                                                                                                                                                                                                                                  |

|                                          | Added the following devices to the PORTC, PORTD, PORTE, PORTF, PORTG, Change Notice and Pull-up Register Maps (Table 4-26, Table 4-28, Table 4-30, Table 4-32, Table 4-34 and Table 4-37):                                                                                                                                                                                                                        |

|                                          | <ul> <li>PIC32MX534F064H</li> <li>PIC32MX564F064H</li> <li>PIC32MX564F128H</li> <li>PIC32MX664F064H</li> <li>PIC32MX664F128H</li> <li>PIC32MX764F128H</li> </ul>                                                                                                                                                                                                                                                  |