Welcome to **E-XFL.COM**

What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded - Microcontrollers</u>"

| Details                    |                                                                                |

|----------------------------|--------------------------------------------------------------------------------|

|                            |                                                                                |

| Product Status             | Active                                                                         |

| Core Processor             | MIPS32® M4K™                                                                   |

| Core Size                  | 32-Bit Single-Core                                                             |

| Speed                      | 80MHz                                                                          |

| Connectivity               | Ethernet, I <sup>2</sup> C, SPI, UART/USART, USB OTG                           |

| Peripherals                | Brown-out Detect/Reset, DMA, POR, PWM, WDT                                     |

| Number of I/O              | 83                                                                             |

| Program Memory Size        | 128KB (128K x 8)                                                               |

| Program Memory Type        | FLASH                                                                          |

| EEPROM Size                | -                                                                              |

| RAM Size                   | 32K x 8                                                                        |

| Voltage - Supply (Vcc/Vdd) | 2.3V ~ 3.6V                                                                    |

| Data Converters            | A/D 16x10b                                                                     |

| Oscillator Type            | Internal                                                                       |

| Operating Temperature      | -40°C ~ 105°C (TA)                                                             |

| Mounting Type              | Surface Mount                                                                  |

| Package / Case             | 121-TFBGA                                                                      |

| Supplier Device Package    | 121-TFBGA (10x10)                                                              |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic32mx664f128l-v-bg |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

TABLE 1-1: PINOUT I/O DESCRIPTIONS (CONTINUED)

|          |                    | Pin Nun         | nber <sup>(1)</sup> |                 | D:          | D. #-          |                                       |  |  |  |  |  |

|----------|--------------------|-----------------|---------------------|-----------------|-------------|----------------|---------------------------------------|--|--|--|--|--|

| Pin Name | 64-Pin<br>QFN/TQFP | 100-Pin<br>TQFP | 121-Pin<br>TFBGA    | 124-pin<br>VTLA | Pin<br>Type | Buffer<br>Type | Description                           |  |  |  |  |  |

| CN0      | 48                 | 74              | B11                 | B40             | I           | ST             | Change notification inputs. Can be    |  |  |  |  |  |

| CN1      | 47                 | 73              | C10                 | A47             | I           | ST             | software programmed for internal weak |  |  |  |  |  |

| CN2      | 16                 | 25              | K2                  | B14             | I           | ST             | pull-ups on all inputs.               |  |  |  |  |  |

| CN3      | 15                 | 24              | K1                  | A15             | I           | ST             |                                       |  |  |  |  |  |

| CN4      | 14                 | 23              | J2                  | B13             | I           | ST             |                                       |  |  |  |  |  |

| CN5      | 13                 | 22              | J1                  | A13             | I           | ST             |                                       |  |  |  |  |  |

| CN6      | 12                 | 21              | H2                  | B11             | I           | ST             |                                       |  |  |  |  |  |

| CN7      | 11                 | 20              | H1                  | A12             | I           | ST             |                                       |  |  |  |  |  |

| CN8      | 4                  | 10              | E3                  | A7              | I           | ST             |                                       |  |  |  |  |  |

| CN9      | 5                  | 11              | F4                  | B6              | I           | ST             |                                       |  |  |  |  |  |

| CN10     | 6                  | 12              | F2                  | A8              | I           | ST             |                                       |  |  |  |  |  |

| CN11     | 8                  | 14              | F3                  | A9              | I           | ST             |                                       |  |  |  |  |  |

| CN12     | 30                 | 44              | L8                  | A29             | I           | ST             |                                       |  |  |  |  |  |

| CN13     | 52                 | 81              | C8                  | B44             | I           | ST             |                                       |  |  |  |  |  |

| CN14     | 53                 | 82              | B8                  | A55             | I           | ST             |                                       |  |  |  |  |  |

| CN15     | 54                 | 83              | D7                  | B45             | I           | ST             |                                       |  |  |  |  |  |

| CN16     | 55                 | 84              | C7                  | A56             | I           | ST             |                                       |  |  |  |  |  |

| CN17     | 31                 | 49              | L10                 | B27             | I           | ST             |                                       |  |  |  |  |  |

| CN18     | 32                 | 50              | L11                 | A32             | I           | ST             |                                       |  |  |  |  |  |

| CN19     | _                  | 80              | D8                  | A54             | I           | ST             |                                       |  |  |  |  |  |

| CN20     | _                  | 47              | L9                  | B26             | I           | ST             |                                       |  |  |  |  |  |

| CN21     | _                  | 48              | K9                  | A31             | I           | ST             |                                       |  |  |  |  |  |

| IC1      | 42                 | 68              | E9                  | B37             | I           | ST             | Capture Inputs 1-5                    |  |  |  |  |  |

| IC2      | 43                 | 69              | E10                 | A45             | I           | ST             | 1                                     |  |  |  |  |  |

| IC3      | 44                 | 70              | D11                 | B38             | I           | ST             |                                       |  |  |  |  |  |

| IC4      | 45                 | 71              | C11                 | A46             | I           | ST             |                                       |  |  |  |  |  |

| IC5      | 52                 | 79              | A9                  | A60             | I           | ST             |                                       |  |  |  |  |  |

| OCFA     | 17                 | 26              | L1                  | A20             | I           | ST             | Output Compare Fault A Input          |  |  |  |  |  |

| OC1      | 46                 | 72              | D9                  | B39             | 0           | _              | Output Compare Output 1               |  |  |  |  |  |

| OC2      | 49                 | 76              | A11                 | A52             | 0           | _              | Output Compare Output 2               |  |  |  |  |  |

| OC3      | 50                 | 77              | A10                 | B42             | 0           | _              | Output Compare Output 3               |  |  |  |  |  |

| OC4      | 51                 | 78              | В9                  | A53             | 0           | _              | Output Compare Output 4               |  |  |  |  |  |

| OC5      | 52                 | 81              | C8                  | B44             | 0           | _              | Output Compare Output 5               |  |  |  |  |  |

| OCFB     | 30                 | 44              | L8                  | A29             | I           | ST             | Output Compare Fault B Input          |  |  |  |  |  |

| INT0     | 46                 | 72              | D9                  | B39             | I           | ST             | External Interrupt 0                  |  |  |  |  |  |

| INT1     | 42                 | 18              | G1                  | A11             | I           | ST             | External Interrupt 1                  |  |  |  |  |  |

| INT2     | 43                 | 19              | G2                  | B10             | I           | ST             | External Interrupt 2                  |  |  |  |  |  |

| INT3     | 44                 | 66              | E11                 | B36             | I           | ST             | External Interrupt 3                  |  |  |  |  |  |

| INT4     | 45                 | 67              | E8                  | A44             | I           | ST             | External Interrupt 4                  |  |  |  |  |  |

|          | MOS - CMO          |                 |                     | ٠               |             |                | Analog input P - Power                |  |  |  |  |  |

**Legend:** CMOS = CMOS compatible input or output ST = Schmitt Trigger input with CMOS levels

Analog = Analog input

O = Output

P = Power I = Input

TTL = TTL input buffer

**Note 1:** Pin numbers are only provided for reference. See the "Device Pin Tables" section for device pin availability.

2: See 25.0 "Ethernet Controller" for more information.

TABLE 7-1: INTERRUPT IRQ, VECTOR AND BIT LOCATION (CONTINUED)

| In ( (1)                          | IRQ    | Vector        |                | Interru  | ot Bit Location |              |

|-----------------------------------|--------|---------------|----------------|----------|-----------------|--------------|

| Interrupt Source <sup>(1)</sup>   | Number | Number        | Flag           | Enable   | Priority        | Sub-Priority |

| IC3E – Input Capture 3 Error      | 63     | 13            | IFS1<31>       | IEC1<31> | IPC3<12:10>     | IPC3<9:8>    |

| IC4E – Input Capture 4 Error      | 64     | 17            | IFS2<0>        | IEC2<0>  | IPC4<12:10>     | IPC4<9:8>    |

| IC5E – Input Capture 5 Error      | 65     | 21            | IFS2<1>        | IEC2<1>  | IPC5<12:10>     | IPC5<9:8>    |

| PMPE – Parallel Master Port Error | 66     | 28            | IFS2<2>        | IEC2<2>  | IPC7<4:2>       | IPC7<1:0>    |

| U4E – UART4 Error                 | 67     | 49            | IFS2<3>        | IEC2<3>  | IPC12<12:10>    | IPC12<9:8>   |

| U4RX – UART4 Receiver             | 68     | 49            | IFS2<4>        | IEC2<4>  | IPC12<12:10>    | IPC12<9:8>   |

| U4TX – UART4 Transmitter          | 69     | 49            | IFS2<5>        | IEC2<5>  | IPC12<12:10>    | IPC12<9:8>   |

| U6E – UART6 Error                 | 70     | 50            | IFS2<6>        | IEC2<6>  | IPC12<20:18>    | IPC12<17:16> |

| U6RX – UART6 Receiver             | 71     | 50            | IFS2<7>        | IEC2<7>  | IPC12<20:18>    | IPC12<17:16> |

| U6TX – UART6 Transmitter          | 72     | 50            | IFS2<8>        | IEC2<8>  | IPC12<20:18>    | IPC12<17:16> |

| U5E – UART5 Error                 | 73     | 51            | IFS2<9>        | IEC2<9>  | IPC12<28:26>    | IPC12<25:24> |

| U5RX – UART5 Receiver             | 74     | 51            | IFS2<10>       | IEC2<10> | IPC12<28:26>    | IPC12<25:24> |

| U5TX – UART5 Transmitter          | 75     | 51            | IFS2<11>       | IEC2<11> | IPC12<28:26>    | IPC12<25:24> |

| (Reserved)                        | _      | _             | _              | _        | _               | _            |

|                                   | Lowe   | est Natural ( | Order Priority | /        |                 |              |

Note 1: Not all interrupt sources are available on all devices. See TABLE 1: "PIC32MX5XX USB and CAN Features", TABLE 2: "PIC32MX6XX USB and Ethernet Features" and TABLE 3: "PIC32MX7XX USB, Ethernet, and CAN Features" for the list of available peripherals.

#### REGISTER 10-12: DCHxSSIZ: DMA CHANNEL 'x' SOURCE SIZE REGISTER

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|

| 24.24        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 31:24        | _                 | _                 | _                 | _                 | 1                 | _                 | _                | _                |

| 22,46        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 23:16        | _                 | _                 | _                 | _                 | 1                 | _                 | _                |                  |

| 45.0         | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |

| 15.8         |                   |                   |                   | CHSSIZ-           | <15:8>            |                   |                  |                  |

| 7.0          | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |

| 7:0          |                   | _                 |                   | CHSSIZ            | <7:0>             | _                 |                  |                  |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

bit 31-16 Unimplemented: Read as '0'

bit 15-0 CHSSIZ<15:0>: Channel Source Size bits

111111111111111 = 65,535 byte source size

:

•

0000000000000010 = 2 byte source size 0000000000000001 = 1 byte source size

#### REGISTER 10-13: DCHxDSIZ: DMA CHANNEL 'x' DESTINATION SIZE REGISTER

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|

| 31:24        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 31.24        | _                 | _                 | _                 | _                 | _                 | _                 | _                | _                |

| 00.40        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 23:16        | _                 | _                 | -                 | _                 | _                 | _                 | _                | _                |

| 45.0         | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |

| 15:8         |                   |                   |                   | CHDSIZ            | <15:8>            |                   |                  |                  |

| 7.0          | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |

| 7:0          |                   |                   |                   | CHDSIZ            | <7:0>             |                   |                  |                  |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

bit 31-16 Unimplemented: Read as '0'

bit 15-0 CHDSIZ<15:0>: Channel Destination Size bits

111111111111111 = 65,535 byte destination size

:

.

0000000000000001 = 1 byte destination size

0000000000000000 = 65,536 byte destination size

REGISTER 11-18: U1BDTP2: USB BUFFER DESCRIPTOR TABLE PAGE 2 REGISTER

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|

| 31:24        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 31.24        | _                 | _                 | 1                 | 1                 | -                 | _                 | -                | -                |

| 22,46        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 23:16        | _                 | _                 | 1                 | 1                 | -                 |                   | -                | -                |

| 15:8         | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 15.6         | _                 | _                 | _                 | _                 | _                 | _                 | _                | _                |

| 7.0          | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |

| 7:0          |                   |                   |                   | BDTPTRI           | H<23:16>          |                   |                  |                  |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

bit 31-8 Unimplemented: Read as '0'

bit 7-0 BDTPTRH<23:16>: BDT Base Address bits

This 8-bit value provides address bits 23 through 16 of the BDT base address, which defines the starting location of the BDT in system memory.

The 32-bit BDT base address is 512-byte aligned.

### REGISTER 11-19: U1BDTP3: USB BUFFER DESCRIPTOR TABLE PAGE 3 REGISTER

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|

| 31:24        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 31.24        | -                 | _                 | _                 | _                 | _                 | _                 | _                | _                |

| 22,46        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 23:16        |                   | _                 | _                 | _                 | _                 | _                 | _                | _                |

| 15:8         | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 15.6         | _                 | _                 | _                 | _                 | _                 | _                 | _                | _                |

| 7:0          | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |

| 7:0          |                   |                   |                   | BDTPTR            | U<31:24>          |                   |                  |                  |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

bit 31-8 Unimplemented: Read as '0'

bit 7-0 BDTPTRU<31:24>: BDT Base Address bits

This 8-bit value provides address bits 31 through 24 of the BDT base address, defines the starting location of the BDT in system memory.

The 32-bit BDT base address is 512-byte aligned.

TABLE 12-5: PORTD REGISTER MAP FOR PIC32MX534F064H, PIC32MX564F064H, PIC32MX564F128H, PIC32MX575F256H, PIC32MX575F512H, PIC32MX664F064H, PIC32MX664F128H, PIC32MX675F256H, PIC32MX675F512H, PIC32MX775F256H, PIC32MX775F512H AND PIC32MX795F512H DEVICES

| ess                         |                                 | 0         |       |       |       |       |         |         |        | Ві     | ts     |        |        |        |        |        |        |        | S          |

|-----------------------------|---------------------------------|-----------|-------|-------|-------|-------|---------|---------|--------|--------|--------|--------|--------|--------|--------|--------|--------|--------|------------|

| Virtual Address<br>(BF88_#) | Register<br>Name <sup>(1)</sup> | Bit Range | 31/15 | 30/14 | 29/13 | 28/12 | 27/11   | 26/10   | 25/9   | 24/8   | 23/7   | 22/6   | 21/5   | 20/4   | 19/3   | 18/2   | 17/1   | 16/0   | All Resets |

| 0000                        | TRISD                           | 31:16     | _     | _     | _     | _     | _       | _       | _      | _      | _      | _      | _      | _      | _      | _      | _      | _      | 0000       |

| 60C0                        | IKISD                           | 15:0      | _     | -     | _     | _     | TRISD11 | TRISD10 | TRISD9 | TRISD8 | TRISD7 | TRISD6 | TRISD5 | TRISD4 | TRISD3 | TRISD2 | TRISD1 | TRISD0 | OFFF       |

| 6000                        | PORTD                           | 31:16     | _     |       | _     | _     | _       | _       | -      | _      | _      | _      |        | _      | _      | _      | _      | _      | 0000       |

| 6000                        | PORTD                           | 15:0      | _     |       | -     | -     | RD11    | RD10    | RD9    | RD8    | RD7    | RD6    | RD5    | RD4    | RD3    | RD2    | RD1    | RD0    | xxxx       |

| 60E0                        | LATD                            | 31:16     | _     | 1     | _     | _     | _       |         | -      | _      | _      | _      | -      | _      | _      | _      | _      | _      | 0000       |

| 60E0                        | LAID                            | 15:0      | _     | _     | _     | _     | LATD11  | LATD10  | LATD9  | LATD8  | LATD7  | LATD6  | LATD5  | LATD4  | LATD3  | LATD2  | LATD1  | LATD0  | xxxx       |

| 60F0                        | ODCD                            | 31:16     | _     | -     | _     | _     | _       | _       | I      | _      | _      | _      | ı      | _      | _      | _      | _      | _      | 0000       |

| 0000                        | ODCD                            | 15:0      | _     | _     | _     | _     | ODCD11  | ODCD10  | ODCD9  | ODCD8  | ODCD7  | ODCD6  | ODCD5  | ODCD4  | ODCD3  | ODCD2  | ODCD1  | ODCD0  | 0000       |

Legend: x = unknown value on Reset; — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

Note 1: All registers in this table have corresponding CLR, SET and INV registers at their virtual addresses, plus offsets of 0x4, 0x8 and 0xC, respectively. See Section 12.1.1 "CLR, SET and INV Registers" for more information.

TABLE 12-6: PORTD REGISTER MAP FOR PIC32MX534F064L, PIC32MX564F064L, PIC32MX564F128L, PIC32MX575F256L, PIC32MX575F512L, PIC32MX664F064L, PIC32MX664F128L, PIC32MX675F256L, PIC32MX7675F512L, PIC32MX775F512L AND PIC32MX795F512L DEVICES

|                             |                                 |           | 1002111 |         | ,       |         |         | ,       |        |        |        |        |        |        |        |        |        |        |              |

|-----------------------------|---------------------------------|-----------|---------|---------|---------|---------|---------|---------|--------|--------|--------|--------|--------|--------|--------|--------|--------|--------|--------------|

| ess                         |                                 | •         |         |         |         |         |         |         |        | Ві     | ts     |        |        |        |        |        |        |        | <sub>o</sub> |

| Virtual Address<br>(BF88_#) | Register<br>Name <sup>(1)</sup> | Bit Range | 31/15   | 30/14   | 29/13   | 28/12   | 27/11   | 26/10   | 25/9   | 24/8   | 23/7   | 22/6   | 21/5   | 20/4   | 19/3   | 18/2   | 17/1   | 16/0   | All Resets   |

| 6000                        | TRISD                           | 31:16     | _       | _       | _       | _       | _       | _       | _      | _      | _      | _      | _      | _      | _      | _      | _      | _      | 0000         |

| 60C0                        | IKISD                           | 15:0      | TRISD15 | TRISD14 | TRISD13 | TRISD12 | TRISD11 | TRISD10 | TRISD9 | TRISD8 | TRISD7 | TRISD6 | TRISD5 | TRISD4 | TRISD3 | TRISD2 | TRISD1 | TRISD0 | FFFF         |

| 6000                        | PORTD                           | 31:16     | _       | _       | _       | _       | _       | _       | _      | _      | _      | _      | _      | _      | _      | _      | _      | _      | 0000         |

| 6000                        | PORTD                           | 15:0      | RD15    | RD14    | RD13    | RD12    | RD11    | RD10    | RD9    | RD8    | RD7    | RD6    | RD5    | RD4    | RD3    | RD2    | RD1    | RD0    | xxxx         |

| 60E0                        | LATD                            | 31:16     | -       | _       | _       | _       | _       | _       | -      | _      | _      | _      | -      | _      | _      | -      | _      | _      | 0000         |

| 60E0                        | LAID                            | 15:0      | LAT15   | LAT14   | LAT13   | LAT12   | LATD11  | LATD10  | LATD9  | LATD8  | LATD7  | LATD6  | LATD5  | LATD4  | LATD3  | LATD2  | LATD1  | LATD0  | xxxx         |

| 60F0                        | ODCD                            | 31:16     | _       | _       | _       | _       | _       | _       | _      | _      | _      | _      | _      | _      | _      | _      | _      | _      | 0000         |

| 6000                        | ODCD                            | 15:0      | ODCD15  | ODCD14  | ODCD13  | ODCD12  | ODCD11  | ODCD10  | ODCD9  | ODCD8  | ODCD7  | ODCD6  | ODCD5  | ODCD4  | ODCD3  | ODCD2  | ODCD1  | ODCD0  | 0000         |

PIC32MX5XX/6XX/7X

**.egend:** x = unknown value on Reset; — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

Note 1: All registers in this table have corresponding CLR, SET and INV registers at their virtual addresses, plus offsets of 0x4, 0x8 and 0xC, respectively. See Section 12.1.1 "CLR, SET and INV Registers" for more information.

TABLE 12-7: PORTE REGISTER MAP FOR PIC32MX534F064H, PIC32MX564F064H, PIC32MX564F128H, PIC32MX575F512H, PIC32MX664F064H, PIC32MX664F128H, PIC32MX675F512H, PIC32MX675F512H, PIC32MX775F512H AND PIC32MX795F512H DEVICES

| ess                         |                                 |           |       |       |       |       |       |       |      | Bi   | ts     |        |        |        |        |        |        |        | s          |

|-----------------------------|---------------------------------|-----------|-------|-------|-------|-------|-------|-------|------|------|--------|--------|--------|--------|--------|--------|--------|--------|------------|

| Virtual Address<br>(BF88_#) | Register<br>Name <sup>(1)</sup> | Bit Range | 31/15 | 30/14 | 29/13 | 28/12 | 27/11 | 26/10 | 25/9 | 24/8 | 23/7   | 22/6   | 21/5   | 20/4   | 19/3   | 18/2   | 17/1   | 16/0   | All Resets |

| 6400                        | TRISE                           | 31:16     | _     | _     | _     | _     | _     | _     | _    | _    | _      | _      | _      | _      | _      | _      | _      | _      | 0000       |

| 6100                        | IKISE                           | 15:0      | _     | _     | _     | _     | _     | _     | _    | _    | TRISE7 | TRISE6 | TRISE5 | TRISE4 | TRISE3 | TRISE2 | TRISE1 | TRISE0 | 00FF       |

| 6110                        | PORTE                           | 31:16     | _     |       | _     | _     | I     |       |      |      |        | _      | _      | _      | _      | _      | _      | _      | 0000       |

| 6110                        | PORTE                           | 15:0      | -     |       | _     | _     | I     |       |      | I    | RE7    | RE6    | RE5    | RE4    | RE3    | RE2    | RE1    | RE0    | xxxx       |

| 6120                        | LATE                            | 31:16     |       | 1     | _     | -     | -     | 1     | 1    | _    | _      | _      | _      | _      | _      | _      | _      | _      | 0000       |

| 6120                        | LAIE                            | 15:0      | _     |       | _     | _     | I     |       |      |      | LATE7  | LATE6  | LATE5  | LATE4  | LATE3  | LATE2  | LATE1  | LATE0  | xxxx       |

| 6130                        | ODCE                            | 31:16     | _     | -     | -     | _     | ı     | -     | -    | ı    | ı      | _      | _      | -      | _      | _      | _      | _      | 0000       |

| 0130                        | ODCE                            | 15:0      | _     | _     | _     | _     | _     | _     | _    | _    | ODCE7  | 0DCE6  | ODCE5  | ODCE4  | ODCE3  | ODCE2  | ODCE1  | ODCE0  | 0000       |

Legend: x = unknown value on Reset; — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

Note 1: All registers in this table have corresponding CLR, SET and INV registers at their virtual addresses, plus offsets of 0x4, 0x8 and 0xC, respectively. See Section 12.1.1 "CLR, SET and INV Registers" for more information

TABLE 12-8: PORTE REGISTER MAP FOR PIC32MX534F064L, PIC32MX564F064L, PIC32MX564F128L, PIC32MX575F256L, PIC32MX575F512L, PIC32MX664F064L, PIC32MX664F128L, PIC32MX675F256L, PIC32MX675F512L, PIC32MX764F128L, PIC32MX775F256L, PIC32MX775F512L AND PIC32MX795F512L DEVICES

| ess                       |                                 | •         |       |       |       |       |       |       |        | Ві     | its    |        |        |        |        |        |        |        | ۰,         |

|---------------------------|---------------------------------|-----------|-------|-------|-------|-------|-------|-------|--------|--------|--------|--------|--------|--------|--------|--------|--------|--------|------------|

| Virtual Addre<br>(BF88_#) | Register<br>Name <sup>(1)</sup> | Bit Range | 31/15 | 30/14 | 29/13 | 28/12 | 27/11 | 26/10 | 25/9   | 24/8   | 23/7   | 22/6   | 21/5   | 20/4   | 19/3   | 18/2   | 17/1   | 16/0   | All Resets |

| 6100                      | TRISE                           | 31:16     | _     | 1     | 1     | ĺ     | _     | I     | _      | 1      | 1      | _      | 1      | I      | _      | 1      | _      | _      | 0000       |

| 0100                      | INISE                           | 15:0      |       |       |       | 1     | _     |       | TRISE9 | TRISE8 | TRISE7 | TRISE6 | TRISE5 | TRISE4 | TRISE3 | TRISE2 | TRISE1 | TRISE0 | 03FF       |

| 6110                      | PORTE                           | 31:16     | -     | I     | -     | -     | _     | I     | _      | -      | -      | _      | -      | I      | _      | -      |        | _      | 0000       |

| 0110                      | FORTE                           | 15:0      | _     |       |       |       | _     |       | RE9    | RE8    | RE7    | RE6    | RE5    | RE4    | RE3    | RE2    | RE1    | RE0    | xxxx       |

| 6120                      | LATE                            | 31:16     |       |       |       | 1     | _     |       | _      | -      | -      | _      |        | I      | _      | -      | _      | _      | 0000       |

| 0120                      | LAIL                            | 15:0      | -     | I     | -     | -     | _     | I     | LATE9  | LATE8  | LATE7  | LATE6  | LATE5  | LATE4  | LATE3  | LATE2  | LATE1  | LATE0  | xxxx       |

| 6130                      | ODCE                            | 31:16     | _     |       | _     | -     | _     |       | _      | -      | _      | _      | -      |        | _      | _      | _      | _      | 0000       |

| 0130                      | ODCL                            | 15:0      | _     | _     | _     | _     | _     | _     | ODCE9  | ODCE8  | ODCE7  | 0DCE6  | ODCE5  | ODCE4  | ODCE3  | ODCE2  | ODCE1  | ODCE0  | 0000       |

Legend: x = unknown value on Reset; — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

Note 1: All registers in this table have corresponding CLR, SET and INV registers at their virtual addresses, plus offsets of 0x4, 0x8 and 0xC, respectively. See Section 12.1.1 "CLR, SET and INV Registers" for more information.

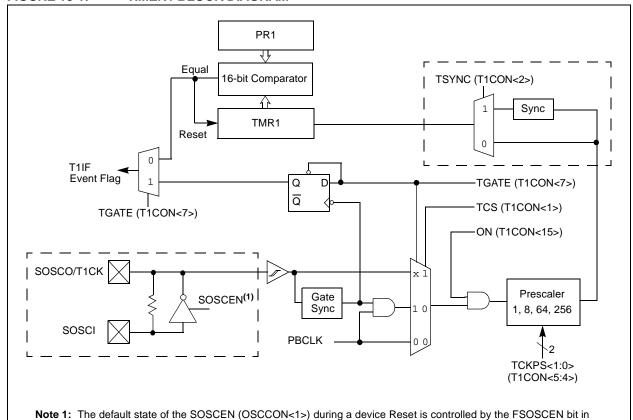

### 13.0 TIMER1

Note:

This data sheet summarizes the features of the PIC32MX5XX/6XX/7XX family of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to **Section 14.** "**Timers**" (DS60001105) in the "PIC32 Family Reference Manual", which is available from the Microchip web site (www.microchip.com/PIC32).

This family of PIC32 devices features one synchronous/ asynchronous 16-bit timer that can operate as a free-running interval timer for various timing applications and counting external events. This timer can also be used with the low-power Secondary Oscillator (Sosc) for Real-Time Clock (RTC) applications. The following modes are supported:

- · Synchronous Internal Timer

- · Synchronous Internal Gated Timer

- Synchronous External Timer

- · Asynchronous External Timer

### 13.1 Additional Supported Features

- · Selectable clock prescaler

- Timer operation during Idle and Sleep mode

- Fast bit manipulation using CLR, SET and INV registers

- Asynchronous mode can be used with the Sosc to function as a Real-Time Clock (RTC)

A simplified block diagram of the Timer1 module is illustrated in Figure 13-1.

#### FIGURE 13-1: TIMER1 BLOCK DIAGRAM

Configuration Word, DEVCFG1.

### REGISTER 14-1: TXCON: TYPE B TIMER CONTROL REGISTER (CONTINUED)

bit 3 T32: 32-Bit Timer Mode Select bit<sup>(2)</sup>

1 = Odd numbered and even numbered timers form a 32-bit timer

0 = Odd numbered and even numbered timers form a separate 16-bit timer

bit 2 Unimplemented: Read as '0'

bit 1 TCS: Timer Clock Source Select bit<sup>(3)</sup>

1 = External clock from TxCK pin

0 = Internal peripheral clock

bit 0 Unimplemented: Read as '0'

- **Note 1:** When using the 1:1 PBCLK divisor, the user's software should not read/write the peripheral SFRs in the SYSCLK cycle immediately following the instruction that clears the module's ON bit.

- 2: This bit is only available on even numbered timers (Timer2 and Timer4).

- **3:** While operating in 32-bit mode, this bit has no effect for odd numbered timers (Timer1, Timer3, and Timer5). All timer functions are set through the even numbered timers.

- **4:** While operating in 32-bit mode, this bit must be cleared on odd numbered timers to enable the 32-bit timer in Idle mode.

### 16.1 Control Registers

### TABLE 16-1: INPUT CAPTURE 1-INPUT CAPTURE 5 REGISTER MAP

| ess                         |                       |               |                                                             |              |       |       |       |       |       | Bi       | ts             |      |      |      |        |      |            |          |            |

|-----------------------------|-----------------------|---------------|-------------------------------------------------------------|--------------|-------|-------|-------|-------|-------|----------|----------------|------|------|------|--------|------|------------|----------|------------|

| Virtual Address<br>(BF80_#) | Register<br>Name      | Bit Range     | 31/15                                                       | 30/14        | 29/13 | 28/12 | 27/11 | 26/10 | 25/9  | 24/8     | 23/7           | 22/6 | 21/5 | 20/4 | 19/3   | 18/2 | 17/1       | 16/0     | All Resets |

| 2000                        | IC1CON <sup>(1)</sup> | 31:16         | _                                                           | _            | _     | _     | _     | _     | _     | _        | _              | _    | _    | _    | _      | _    | _          | _        | 0000       |

| 2000                        | IC ICON.              | 15:0          | ON                                                          | _            | SIDL  | _     | _     | _     | FEDGE | C32      | ICTMR          | ICI< | 1:0> | ICOV | ICBNE  |      | ICM<2:0>   |          | 0000       |

| 2010                        | IC1BUF                | 31:16         |                                                             |              |       |       |       |       |       | IC1BUF   | -31·0\         |      |      |      |        |      |            |          | xxxx       |

| 2010                        | 101001                | 15:0          |                                                             |              |       |       |       |       |       | 101001   | <b>CO1.0</b> 2 |      |      |      |        |      |            |          | xxxx       |

| 2200                        | IC2CON <sup>(1)</sup> | 31:16         |                                                             | _            | _     | _     | _     | _     | _     |          | _              | _    | _    | _    | _      | _    | _          | _        | 0000       |

| 2200                        | 1020011               | 15:0          | ON                                                          |              |       |       |       |       |       |          |                |      |      |      |        |      |            |          |            |

| 2210                        | IC2BUF                | 31:16<br>15:0 |                                                             | IC2BUF<31:0> |       |       |       |       |       |          |                |      |      |      |        |      |            | $\vdash$ |            |

| -                           |                       | 31:16         |                                                             | _            | _     | _     | _     | _     | _     | _        | _              | _    | _    | _    | _      | _    | _          | _        | 0000       |

| 2400                        | IC3CON <sup>(1)</sup> | 15:0          | ON                                                          | _            | SIDL  |       | _     | _     | FEDGE | C32      | ICTMR          | ICI< |      | ICOV | ICBNE  | _    | ICM<2:0>   |          | 0000       |

|                             |                       | 31:16         | ON                                                          |              | SIDL  |       |       |       | TEDGE | 032      | ICTIVIT        | 101< | 1.02 | 1001 | ICDINL |      | 10101<2.0> |          | xxxx       |

| 2410                        | IC3BUF                | 15:0          |                                                             |              |       |       |       |       |       | IC3BUF   | <31:0>         |      |      |      |        |      |            |          | XXXX       |

|                             | "                     | 31:16         |                                                             | _            | _     | _     | _     | _     | _     | _        | _              | _    | _    | _    | _      | _    | _          | _        | 0000       |

| 2600                        | IC4CON <sup>(1)</sup> | 15:0          | ON                                                          | _            | SIDL  | _     | _     | _     | FEDGE | C32      | ICTMR          | ICI< | 1:0> | ICOV | ICBNE  |      | ICM<2:0>   |          | 0000       |

|                             |                       | 31:16         |                                                             |              |       |       |       |       |       |          |                |      |      |      |        | Į.   |            |          | xxxx       |

| 2610                        | IC4BUF                | 15:0          |                                                             |              |       |       |       |       |       | IC4BUF   | <31:0>         |      |      |      |        |      |            |          | xxxx       |

|                             |                       | 31:16         | _                                                           | _            | _     | _     | _     | _     | _     | _        | _              | _    | _    | _    | _      | _    | _          | _        | 0000       |

| 2800                        | IC5CON <sup>(1)</sup> | 15:0          | ON - SIDL FEDGE C32 ICTMR ICI<1:0> ICOV ICBNE ICM<2:0> 0000 |              |       |       |       |       |       |          |                |      |      |      | -      |      |            |          |            |

| 22.45                       | 1055115               | 31:16         |                                                             |              | 1     |       |       |       |       | 10.50::- |                | 1    |      | 1    |        | ı    |            |          | xxxx       |

| 2810                        | IC5BUF                | 15:0          |                                                             |              |       |       |       |       |       | IC5BUF   | <31:0>         |      |      |      |        |      |            |          | xxxx       |

PIC32MX5XX/6XX/7XX

$\textbf{Legend:} \qquad \textbf{x} = \text{unknown value on Reset;} \\ \textbf{--} = \text{unimplemented, read as '0'. Reset values are shown in hexadecimal.}$

Note 1: This register has corresponding CLR, SET and INV registers at its virtual address, plus an offset of 0x4, 0x8 and 0xC, respectively. See Section 12.1.1 "CLR, SET and INV Registers" for more information.

REGISTER 16-1: ICXCON: INPUT CAPTURE 'x' CONTROL REGISTER

| Bit Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

|-----------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|

| 24.24     | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 31:24     | _                 | _                 | _                 | _                 | _                 | -                 | _                | _                |

| 22:40     | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 23:16     | _                 | _                 | _                 | _                 | _                 | -                 | _                |                  |

| 45.0      | R/W-0             | U-0               | R/W-0             | U-0               | U-0               | U-0               | R/W-0            | R/W-0            |

| 15:8      | ON <sup>(1)</sup> | _                 | SIDL              | _                 | _                 | _                 | FEDGE            | C32              |

| 7.0       | R/W-0             | R/W-0             | R/W-0             | R-0               | R-0               | R/W-0             | R/W-0            | R/W-0            |

| 7:0       | ICTMR             | ICI<              | 1:0>              | ICOV              | ICBNE             |                   | ICM<2:0>         |                  |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

bit 31-16 Unimplemented: Read as '0'

bit 15 **ON:** Input Capture Module Enable bit (1)

1 = Module is enabled

0 = Disable and reset module, disable clocks, disable interrupt generation and allow SFR modifications

bit 14 **Unimplemented:** Read as '0'

bit 13 SIDL: Stop in Idle Control bit

1 = Halt in Idle mode

0 = Continue to operate in Idle mode

bit 12-10 **Unimplemented:** Read as '0'

bit 9 **FEDGE:** First Capture Edge Select bit (only used in mode 6, ICM<2:0> = 110)

1 = Capture rising edge first0 = Capture falling edge first

bit 8 C32: 32-bit Capture Select bit

1 = 32-bit timer resource capture 0 = 16-bit timer resource capture

bit 7 ICTMR: Timer Select bit (Does not affect timer selection when C32 (ICxCON<8>) is '1')

1 = Timer2 is the counter source for capture 0 = Timer3 is the counter source for capture

bit 6-5 ICI<1:0>: Interrupt Control bits

11 = Interrupt on every fourth capture event

10 = Interrupt on every third capture event

01 = Interrupt on every second capture event

00 = Interrupt on every capture event

bit 4 ICOV: Input Capture Overflow Status Flag bit (read-only)

1 = Input capture overflow is occurred0 = No input capture overflow is occurred

bit 3 ICBNE: Input Capture Buffer Not Empty Status bit (read-only)

1 = Input capture buffer is not empty; at least one more capture value can be read

0 = Input capture buffer is empty

**Note 1:** When using the 1:1 PBCLK divisor, the user's software should not read/write the peripheral's SFRs in the SYSCLK cycle immediately following the instruction that clears the module's ON bit.

NOTES:

NOTES:

REGISTER 23-5: AD1CSSL: ADC INPUT SCAN SELECT REGISTER

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|

| 31:24        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 31.24        |                   | _                 | _                 | _                 |                   |                   | _                | _                |

| 22.40        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 23:16        | _                 | _                 | _                 | _                 | _                 | _                 | _                | _                |

| 45.0         | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |

| 15:8         | CSSL15            | CSSL14            | CSSL13            | CSSL12            | CSSL11            | CSSL10            | CSSL9            | CSSL8            |

| 7.0          | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |

| 7:0          | CSSL7             | CSSL6             | CSSL5             | CSSL4             | CSSL3             | CSSL2             | CSSL1            | CSSL0            |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

bit 31-16 Unimplemented: Read as '0'

bit 15-0 CSSL<15:0>: ADC Input Pin Scan Selection bits<sup>(1)</sup>

1 = Select ANx for input scan0 = Skip ANx for input scan

**Note 1:** CSSL = ANx, where 'x' = 0-15.

TABLE 32-5: DC CHARACTERISTICS: OPERATING CURRENT (IDD) (CONTINUED)

| DC CHA        | RACTERIST              | rics                       | Standard Operating Conditions: 2.3V to 3.6V (unless otherwise stated) Operating temperature $-40^{\circ}\text{C} \le \text{TA} \le +85^{\circ}\text{C}$ for Industrial $-40^{\circ}\text{C} \le \text{TA} \le +105^{\circ}\text{C}$ for V-Temp |                              |                           |      |                           |  |

|---------------|------------------------|----------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------|---------------------------|------|---------------------------|--|

| Param.<br>No. | Typical <sup>(3)</sup> | Max.                       |                                                                                                                                                                                                                                                | Conditions                   | 3                         |      |                           |  |

| Operatir      | ng Current (I          | DD) <sup>(1,2)</sup> for l | PIC32MX53                                                                                                                                                                                                                                      | 34/564/664/764 Family Device | es                        |      |                           |  |

| DC20c         | 6                      | 9                          | mA                                                                                                                                                                                                                                             | Code executing from Flash    | -40°C,<br>+25°C,<br>+85°C | _    | 4 MHz                     |  |

| DC20d         | 7                      | 10                         |                                                                                                                                                                                                                                                |                              | +105°C                    |      |                           |  |

| DC20e         | 2                      |                            |                                                                                                                                                                                                                                                | Code executing from SRAM     |                           |      |                           |  |

| DC21b         | 19                     | 32                         | mA                                                                                                                                                                                                                                             | Code executing from Flash    |                           |      | 25 MHz                    |  |

| DC21c         | 14                     | _                          | IIIA                                                                                                                                                                                                                                           | Code executing from SRAM     | _                         | _    | (Note 4)                  |  |

| DC22b         | 31                     | 50                         | mA                                                                                                                                                                                                                                             | Code executing from Flash    |                           |      | 60 MHz                    |  |

| DC22c         | 29                     | _                          | IIIA                                                                                                                                                                                                                                           | Code executing from SRAM     | _                         | _    | (Note 4)                  |  |

| DC23c         | 39                     | 65                         | mA                                                                                                                                                                                                                                             | Code executing from Flash    | -40°C,<br>+25°C,<br>+85°C | _    | 80 MHz                    |  |

| DC23d         | 49                     | 70                         | 1                                                                                                                                                                                                                                              |                              | +105°C                    |      |                           |  |

| DC23e         | 39                     | _                          |                                                                                                                                                                                                                                                | Code executing from SRAM     | _                         |      |                           |  |

| DC25b         | 100                    | 150                        | μA                                                                                                                                                                                                                                             | _                            | +25°C                     | 3.3V | LPRC (31 kHz)<br>(Note 4) |  |

- Note 1: A device's IDD supply current is mainly a function of the operating voltage and frequency. Other factors, such as PBCLK (Peripheral Bus Clock) frequency, number of peripheral modules enabled, internal code execution pattern, execution from Program Flash memory vs. SRAM, I/O pin loading and switching rate, oscillator type, as well as temperature, can have an impact on the current consumption.

- 2: The test conditions for IDD measurements are as follows:

- Oscillator mode is EC (for 8 MHz and below) and EC+PLL (for above 8 MHz) with OSC1 driven by external square wave from rail-to-rail, (OSC1 input clock input over/undershoot < 100 mV required)</li>

- OSC2/CLKO is configured as an I/O input pin

- USB PLL oscillator is disabled if the USB module is implemented, PBCLK divisor = 1:8

- CPU, program Flash, and SRAM data memory are operational, program Flash memory Wait states = 111, Program Cache and Prefetch are disabled and SRAM data memory Wait states = 1

- No peripheral modules are operating, (ON bit = 0)

- WDT, Clock Switching, Fail-Safe Clock Monitor, and Secondary Oscillator are disabled

- All I/O pins are configured as inputs and pulled to Vss

- MCLR = VDD

- CPU executing while(1) statement from Flash

- RTCC and JTAG are disabled

- **3:** Data in "Typical" column is at 3.3V, 25°C at specified operating frequency unless otherwise stated. Parameters are for design guidance only and are not tested.

- **4:** All parameters are characterized, but only those parameters listed for 4 MHz and 80 MHz are tested at 3.3V in manufacturing.

TABLE 32-7: DC CHARACTERISTICS: POWER-DOWN CURRENT (IPD) (CONTINUED)

| DC CHA                                                                            | RACTERIS               | TICS               | Standard Operating Conditions: 2.3V to 3.6V (unless otherwise stated) Operating temperature $-40^{\circ}\text{C} \le \text{TA} \le +85^{\circ}\text{C}$ for Industrial $-40^{\circ}\text{C} \le \text{TA} \le +105^{\circ}\text{C}$ for V-Temp |            |                                                         |                                                    |  |  |  |  |

|-----------------------------------------------------------------------------------|------------------------|--------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------|---------------------------------------------------------|----------------------------------------------------|--|--|--|--|

| Param.<br>No.                                                                     | Typical <sup>(2)</sup> | Max.               | Units                                                                                                                                                                                                                                          |            | Conditions                                              |                                                    |  |  |  |  |

| Power-Down Current (IPD) <sup>(1)</sup> for PIC32MX534/564/664/764 Family Devices |                        |                    |                                                                                                                                                                                                                                                |            |                                                         |                                                    |  |  |  |  |

| DC40g                                                                             | 12                     | 40                 |                                                                                                                                                                                                                                                | -40°C      |                                                         |                                                    |  |  |  |  |

| DC40h                                                                             | 20                     | 120                |                                                                                                                                                                                                                                                | +25°C      | 2.3V                                                    | Base Power-Down Current (Note 6)                   |  |  |  |  |

| DC40i                                                                             | 210                    | 600                |                                                                                                                                                                                                                                                | +85°C      | 2.3 V                                                   | Base Fower-Down Current (Note o)                   |  |  |  |  |

| DC40o                                                                             | 400                    | 1000               |                                                                                                                                                                                                                                                | +105°C     |                                                         |                                                    |  |  |  |  |

| DC40j                                                                             | 20                     | 120                | μА                                                                                                                                                                                                                                             | +25°C      | 3.3V                                                    | Base Power-Down Current                            |  |  |  |  |

| DC40k                                                                             | 15                     | 80                 | μΑ                                                                                                                                                                                                                                             | -40°C      |                                                         |                                                    |  |  |  |  |

| DC40I                                                                             | 20                     | 120                |                                                                                                                                                                                                                                                | +25°C      |                                                         |                                                    |  |  |  |  |

| DC40m                                                                             | 113                    | 350 <sup>(5)</sup> |                                                                                                                                                                                                                                                | +70°C      | 3.6V                                                    | Base Power-Down Current                            |  |  |  |  |

| DC40n                                                                             | 220                    | 650                |                                                                                                                                                                                                                                                | +85°C      |                                                         |                                                    |  |  |  |  |

| DC40p                                                                             | 500                    | 1000               |                                                                                                                                                                                                                                                | +105°C     |                                                         |                                                    |  |  |  |  |

| Module                                                                            | Differential           | Current fo         | r PIC32N                                                                                                                                                                                                                                       | IX534/564/ | 664/764                                                 | Family Devices                                     |  |  |  |  |

| DC41c                                                                             | _                      | 10                 |                                                                                                                                                                                                                                                |            | 2.5V                                                    | Watchdog Timer Current: ∆IWDT (Notes 3,6)          |  |  |  |  |

| DC41d                                                                             | 5                      | _                  | μΑ                                                                                                                                                                                                                                             | _          | 3.3V                                                    | Watchdog Timer Current: ∆IWDT (Note 3)             |  |  |  |  |

| DC41e                                                                             | _                      | 20                 |                                                                                                                                                                                                                                                |            | 3.6V                                                    | Watchdog Timer Current: ΔIWDT (Note 3)             |  |  |  |  |

| DC42c                                                                             | _                      | 40                 |                                                                                                                                                                                                                                                |            | 2.5V                                                    | RTCC + Timer1 w/32 kHz Crystal: ΔIRTCC (Notes 3,6) |  |  |  |  |

| DC42d                                                                             | 23                     | _                  | μΑ                                                                                                                                                                                                                                             | _          | 3.3V                                                    | RTCC + Timer1 w/32 kHz Crystal: ∆IRTCC (Note 3)    |  |  |  |  |

| DC42e                                                                             | _                      | 50                 |                                                                                                                                                                                                                                                |            | 3.6V RTCC + Timer1 w/32 kHz Crystal: ΔIRTCC (Note 3     |                                                    |  |  |  |  |

| DC43c                                                                             | _                      | 1300               |                                                                                                                                                                                                                                                |            | 2.5V                                                    | ADC: ΔIADC (Notes 3,4,6)                           |  |  |  |  |

| DC43d                                                                             | 1100                   | _                  | μΑ                                                                                                                                                                                                                                             | _          | 3.3V ADC: ΔΙΑΦΟ (Notes 3,4) 3.6V ADC: ΔΙΑΦΟ (Notes 3,4) |                                                    |  |  |  |  |

| DC43e                                                                             | _                      | 1300               |                                                                                                                                                                                                                                                |            |                                                         |                                                    |  |  |  |  |

**Note 1:** The test conditions for IPD current measurements are as follows:

- Oscillator mode is EC (for 8 MHz and below) and EC+PLL (for above 8 MHz) with OSC1 driven by external square wave from rail-to-rail, (OSC1 input clock input over/undershoot < 100 mV required)

- OSC2/CLKO is configured as an I/O input pin

- USB PLL oscillator is disabled if the USB module is implemented, PBCLK divisor = 1:8

- CPU is in Sleep mode, program Flash memory Wait states = 111, Program Cache and Prefetch are disabled and SRAM data memory Wait states = 1

- No peripheral modules are operating, (ON bit = 0)

- WDT, Clock Switching, Fail-Safe Clock Monitor, and Secondary Oscillator are disabled

- All I/O pins are configured as inputs and pulled to Vss

- MCLR = VDD

- · RTCC and JTAG are disabled

- **2:** Data in the "Typical" column is at 3.3V, 25°C unless otherwise stated. Parameters are for design guidance only and are not tested.

- 3: The  $\Delta$  current is the additional current consumed when the module is enabled. This current should be added to the base IPD current.

- **4:** Test conditions for ADC module differential current are as follows: Internal ADC RC oscillator enabled.

- 5: Data is characterized at +70°C and not tested. Parameter is for design guidance only.

- **6:** This parameter is characterized, but not tested in manufacturing.

TABLE 32-8: DC CHARACTERISTICS: I/O PIN INPUT SPECIFICATIONS

| DC CHA        | ARACTER | EISTICS                                                                              | Standard Operating Conditions: 2.3V to 3.6V (unless otherwise stated)  Operating temperature $-40^{\circ}\text{C} \le \text{TA} \le +85^{\circ}\text{C}$ for Industrial $-40^{\circ}\text{C} \le \text{TA} \le +105^{\circ}\text{C}$ for V-Temp |                        |                    |        |                                       |  |  |

|---------------|---------|--------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------|--------------------|--------|---------------------------------------|--|--|

| Param.<br>No. | Symbol  | Characteristics                                                                      | Min.                                                                                                                                                                                                                                            | Typical <sup>(1)</sup> | Max.               | Units  | Conditions                            |  |  |

| DI10          | VIL     | Input Low Voltage I/O Pins: with TTL Buffer                                          | Vss                                                                                                                                                                                                                                             |                        | 0.15 Vpp           | V      |                                       |  |  |

|               |         | with Schmitt Trigger Buffer                                                          | Vss                                                                                                                                                                                                                                             | _                      | 0.2 VDD            | V      |                                       |  |  |

| DI15<br>DI16  |         | MCLR <sup>(2)</sup> OSC1 (XT mode)                                                   | Vss<br>Vss                                                                                                                                                                                                                                      | _                      | 0.2 VDD<br>0.2 VDD | V      | (Note 4)                              |  |  |

| DI17<br>DI18  |         | OSC1 (HS mode)<br>SDAx, SCLx                                                         | Vss<br>Vss                                                                                                                                                                                                                                      | _<br>_                 | 0.2 VDD<br>0.3 VDD | V      | (Note 4)<br>SMBus disabled            |  |  |

| DI19          |         | SDAx, SCLx                                                                           | Vss                                                                                                                                                                                                                                             | _                      | 0.8                | V      | (Note 4)<br>SMBus enabled<br>(Note 4) |  |  |

| DI20          | VIH     | Input High Voltage I/O Pins not 5V-tolerant <sup>(5)</sup> I/O Pins 5V-tolerant with | 0.65 VDD<br>0.25 VDD + 0.8V                                                                                                                                                                                                                     |                        | VDD<br>5.5         | V<br>V | (Note 4,6)<br>(Note 4,6)              |  |  |

| DI28          |         | PMP <sup>(5)</sup> I/O Pins 5V-tolerant <sup>(5)</sup> SDAx, SCLx                    | 0.65 VDD<br>0.65 VDD                                                                                                                                                                                                                            | _                      | 5.5<br>5.5         | V      | SMBus disabled                        |  |  |

| DI29          |         | SDAx, SCLx                                                                           | 2.1                                                                                                                                                                                                                                             |                        | 5.5                | V      | (Note 4,6) SMBus enabled,             |  |  |

| 2120          |         | , 00 L                                                                               | 2.1                                                                                                                                                                                                                                             |                        | 0.0                | ľ      | 2.3V ≤ VPIN ≤ 5.5 (Note 4,6)          |  |  |