Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFI

| Product Status             | Active                                                                         |

|----------------------------|--------------------------------------------------------------------------------|

| Core Processor             | MIPS32® M4K™                                                                   |

| Core Size                  | 32-Bit Single-Core                                                             |

| Speed                      | 80MHz                                                                          |

| Connectivity               | Ethernet, I <sup>2</sup> C, SPI, UART/USART, USB OTG                           |

| Peripherals                | Brown-out Detect/Reset, DMA, POR, PWM, WDT                                     |

| Number of I/O              | 85                                                                             |

| Program Memory Size        | 128KB (128K x 8)                                                               |

| Program Memory Type        | FLASH                                                                          |

| EEPROM Size                | -                                                                              |

| RAM Size                   | 32K x 8                                                                        |

| Voltage - Supply (Vcc/Vdd) | 2.3V ~ 3.6V                                                                    |

| Data Converters            | A/D 16x10b                                                                     |

| Oscillator Type            | Internal                                                                       |

| Operating Temperature      | -40°C ~ 105°C (TA)                                                             |

| Mounting Type              | Surface Mount                                                                  |

| Package / Case             | 100-TQFP                                                                       |

| Supplier Device Package    | 100-TQFP (14x14)                                                               |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic32mx664f128l-v-pf |

|                            |                                                                                |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

#### TABLE 10: PIN NAMES FOR USB AND CAN DEVICES

| 121        | PIN TFBGA (BOTTOM VIEW)                                                                     |       | L11                              |     |

|------------|---------------------------------------------------------------------------------------------|-------|----------------------------------|-----|

|            | PIC32MX534F064L<br>PIC32MX564F064L<br>PIC32MX564F128L<br>PIC32MX575F256L<br>PIC32MX575F512L | L1    |                                  | A11 |

|            | The TFBGA package skips from row "H" to                                                     |       |                                  |     |

| Pin #      | Full Pin Name                                                                               | Pin # | Full Pin Name                    |     |

| A1         | PMD4/RE4                                                                                    | E2    | T4CK/RC3                         |     |

| A2         | PMD3/RE3                                                                                    | E3    | SCK2/U6TXU6TX/U3RTS/PMA5/CN8/RG6 |     |

| A3         | TRD0/RG13                                                                                   | E4    | T3CK/RC2                         |     |

| A4         | PMD0/RE0                                                                                    | E5    | Vdd                              |     |

| A5         | PMD8/RG0                                                                                    | E6    | PMD9/RG1                         |     |

| A6         | C1TX/PMD10/RF1                                                                              | E7    | Vss                              |     |

| A7         | Vdd                                                                                         | E8    | SDA1/INT4/RA15                   |     |

| A8         | Vss                                                                                         | E9    | RTCC/IC1/RD8                     |     |

| A9         | IC5/PMD12/RD12                                                                              | E10   | SS1/IC2/RD9                      |     |

| A10        | OC3/RD2                                                                                     | E11   | SCL1/INT3/RA14                   |     |

| A11        | OC2/RD1                                                                                     | F1    | MCLR                             |     |

| B1         | No Connect (NC)                                                                             | F2    | SCL4/SDO2/U3TX/PMA3/CN10/RG8     |     |

| B2         | RG15                                                                                        | F3    | SS2/U6RX/U3CTS/PMA2/CN11/RG9     |     |

| B3         | PMD2/RE2                                                                                    | F4    | SDA4/SDI2/U3RX/PMA4/CN9/RG7      |     |

| B3<br>B4   | PMD1/RE1                                                                                    | F5    | Vss                              |     |

| B5         | TRD3/RA7                                                                                    | F6    | No Connect (NC)                  |     |

| B6         | C1RX/PMD11/RF0                                                                              | F7    | No Connect (NC)                  |     |

| B7         | VCAP                                                                                        | F8    | VDD                              |     |

| B8         | PMRD/CN14/RD5                                                                               | F9    | OSC1/CLKI/RC12                   |     |

| B9         | OC4/RD3                                                                                     |       | Vss                              |     |

| B10        | Vss                                                                                         | F11   | OSC2/CLKO/RC15                   |     |

| B10<br>B11 | SOSCO/T1CK/CN0/RC14                                                                         | G1    | INT1/RE8                         |     |

| C1         | PMD6/RE6                                                                                    | G2    | INT2/RE9                         |     |

| C2         | VDD                                                                                         | G3    | TMS/RA0                          |     |

| C3         | TRD1/RG12                                                                                   | G4    | No Connect (NC)                  |     |

| C4         | TRD2/RG14                                                                                   | G5    | VDD                              |     |

| C5         | TRCLK/RA6                                                                                   | G6    | Vss                              |     |

| C6         | No Connect (NC)                                                                             | G7    | Vss                              |     |

| C7         | PMD15/CN16/RD7                                                                              | G8    | No Connect (NC)                  |     |

| C8         | OC5/PMWR/CN13/RD4                                                                           | G9    | TDO/RA5                          |     |

| C9         | VDD                                                                                         | G10   | SDA2/RA3                         |     |

| C10        | SOSCI/CN1/RC13                                                                              | G11   | TDI/RA4                          |     |

| C11        | IC4/PMCS1/PMA14/RD11                                                                        | H1    | AN5/C1IN+/VBUSON/CN7/RB5         |     |

| D1         | T2CK/RC1                                                                                    | H2    | AN4/C1IN-/CN6/RB4                |     |

| D2         | PMD7/RE7                                                                                    | H3    | Vss                              |     |

| D3         | PMD5/RE5                                                                                    | H4    | VDD                              |     |

| D4         | Vss                                                                                         | H5    | No Connect (NC)                  |     |

| D5         | Vss                                                                                         | H6    | VDD                              |     |

| D6         | No Connect (NC)                                                                             | H7    | No Connect (NC)                  |     |

| D7         | PMD14/CN15/RD6                                                                              | H8    | VBUS                             |     |

| D8         | PMD13/CN19/RD13                                                                             | H9    | VUSB3V3                          |     |

| D9         | SDO1/OC1/INT0/RD0                                                                           | H10   | D+/RG2                           |     |

| D10        | No Connect (NC)                                                                             | H11   | SCL2/RA2                         |     |

| D11        | SCK1/IC3/PMCS2/PMA15/RD10                                                                   | J1    | AN3/C2IN+/CN5/RB3                |     |

|            |                                                                                             | 51    |                                  |     |

#### TABLE 1-1: PINOUT I/O DESCRIPTIONS (CONTINUED)

|          |                                               | Pin Nun         | nber <sup>(1)</sup> |                 | D:          | Duffer               |                                                   |  |  |  |  |  |

|----------|-----------------------------------------------|-----------------|---------------------|-----------------|-------------|----------------------|---------------------------------------------------|--|--|--|--|--|

| Pin Name | 64-Pin<br>QFN/TQFP                            | 100-Pin<br>TQFP | 121-Pin<br>TFBGA    | 124-pin<br>VTLA | Pin<br>Type | Buffer<br>Type       | Description                                       |  |  |  |  |  |

| RG0      | —                                             | 90              | A5                  | A61             | I/O         | ST                   | PORTG is a bidirectional I/O port                 |  |  |  |  |  |

| RG1      | —                                             | 89              | E6                  | B50             | I/O         | ST                   |                                                   |  |  |  |  |  |

| RG6      | 4                                             | 10              | E3                  | A7              | I/O         | ST                   |                                                   |  |  |  |  |  |

| RG7      | 5                                             | 11              | F4                  | B6              | I/O         | ST                   |                                                   |  |  |  |  |  |

| RG8      | 6                                             | 12              | F2                  | A8              | I/O         | ST                   |                                                   |  |  |  |  |  |

| RG9      | 8                                             | 14              | F3                  | A9              | I/O         | ST                   |                                                   |  |  |  |  |  |

| RG12     | —                                             | 96              | C3                  | A65             | I/O         | ST                   |                                                   |  |  |  |  |  |

| RG13     | —                                             | 97              | A3                  | B55             | I/O         | ST                   | -                                                 |  |  |  |  |  |

| RG14     | —                                             | 95              | C4                  | B54             | I/O         | ST                   |                                                   |  |  |  |  |  |

| RG15     | —                                             | 1               | B2                  | A2              | I/O         | ST                   |                                                   |  |  |  |  |  |

| RG2      | 37                                            | 57              | H10                 | B31             | Ι           | ST                   | PORTG input pins                                  |  |  |  |  |  |

| RG3      | 36                                            | 56              | J11                 | A38             | I           | ST                   |                                                   |  |  |  |  |  |

| T1CK     | 48                                            | 74              | B11                 | B40             |             | ST                   | Timer1 external clock input                       |  |  |  |  |  |

| T2CK     | —                                             | 6               | D1                  | A5              | I           | ST                   | Timer2 external clock input                       |  |  |  |  |  |

| T3CK     | —                                             | 7               | E4                  | B4              |             | ST                   | Timer3 external clock input                       |  |  |  |  |  |

| T4CK     | —                                             | 8               | E2                  | A6              |             | ST                   | Timer4 external clock input                       |  |  |  |  |  |

| T5CK     | —                                             | 9               | E1                  | B5              |             | ST                   | Timer5 external clock input                       |  |  |  |  |  |

| U1CTS    | 43                                            | 47              | L9                  | B26             |             | ST                   | UART1 clear to send                               |  |  |  |  |  |

| U1RTS    | 49                                            | 48              | K9                  | A31             | 0           |                      | UART1 ready to send                               |  |  |  |  |  |

| U1RX     | 50                                            | 52              | K11                 | A36             | I           | ST                   | UART1 receive                                     |  |  |  |  |  |

| U1TX     | 51                                            | 53              | J10                 | B29             | 0           | _                    | UART1 transmit                                    |  |  |  |  |  |

| U3CTS    | 8                                             | 14              | F3                  | A9              | I           | ST                   | UART3 clear to send                               |  |  |  |  |  |

| U3RTS    | 4                                             | 10              | E3                  | A7              | 0           | _                    | UART3 ready to send                               |  |  |  |  |  |

| U3RX     | 5                                             | 11              | F4                  | B6              | I           | ST                   | UART3 receive                                     |  |  |  |  |  |

| U3TX     | 6                                             | 12              | F2                  | A8              | 0           | _                    | UART3 transmit                                    |  |  |  |  |  |

| U2CTS    | 21                                            | 40              | K6                  | A27             | I           | ST                   | UART2 clear to send                               |  |  |  |  |  |

| U2RTS    | 29                                            | 39              | L6                  | B22             | 0           |                      | UART2 ready to send                               |  |  |  |  |  |

| U2RX     | 31                                            | 49              | L10                 | B27             | I           | ST                   | UART2 receive                                     |  |  |  |  |  |

| U2TX     | 32                                            | 50              | L11                 | A32             | 0           |                      | UART2 transmit                                    |  |  |  |  |  |

| U4RX     | 43                                            | 47              | L9                  | B26             | 1           | ST                   | UART4 receive                                     |  |  |  |  |  |

| U4TX     | 49                                            | 48              | K9                  | A31             | 0           | _                    | UART4 transmit                                    |  |  |  |  |  |

| U6RX     | 8                                             | 14              | F3                  | A9              | I           | ST                   | UART6 receive                                     |  |  |  |  |  |

| U6TX     | 4                                             | 10              | E3                  | A7              | 0           | _                    | UART6 transmit                                    |  |  |  |  |  |

| U5RX     | 21                                            | 40              | K6                  | A27             | 1           | ST                   | UART5 receive                                     |  |  |  |  |  |

| U5TX     | 29                                            | 39              | L6                  | B22             | 0           |                      | UART5 transmit                                    |  |  |  |  |  |

| SCK1     | _                                             | 70              | D11                 | B38             | I/O         | ST                   | Synchronous serial clock input/output<br>for SPI1 |  |  |  |  |  |

| 5        | CMOS = CMO<br>ST = Schmitt T<br>TL = TTL inpu | rigger input    |                     |                 |             | nalog = A<br>= Outpu | Analog input P = Power                            |  |  |  |  |  |

Note 1: Pin numbers are only provided for reference. See the "Device Pin Tables" section for device pin availability.

2: See 25.0 "Ethernet Controller" for more information.

| TABLE 1-1:         PINOUT I/O DESCRIPTIONS (CONTINUED) |                                               |                 |                     |                 |      |                      |                                                   |  |  |  |  |

|--------------------------------------------------------|-----------------------------------------------|-----------------|---------------------|-----------------|------|----------------------|---------------------------------------------------|--|--|--|--|

|                                                        |                                               | Pin Nur         | nber <sup>(1)</sup> |                 | Pin  | Buffer               | Description                                       |  |  |  |  |

| Pin Name                                               | 64-Pin<br>QFN/TQFP                            | 100-Pin<br>TQFP | 121-Pin<br>TFBGA    | 124-pin<br>VTLA | Туре | Туре                 |                                                   |  |  |  |  |

| SDI1                                                   | —                                             | 9               | E1                  | B5              | I    | ST                   | SPI1 data in                                      |  |  |  |  |

| SDO1                                                   | —                                             | 72              | D9                  | B39             | 0    | _                    | SPI1 data out                                     |  |  |  |  |

| SS1                                                    | _                                             | 69              | E10                 | A45             | I/O  | ST                   | SPI1 slave synchronization or frame pulse I/O     |  |  |  |  |

| SCK3                                                   | 49                                            | 48              | K9                  | A31             | I/O  | ST                   | Synchronous serial clock input/output<br>for SPI3 |  |  |  |  |

| SDI3                                                   | 50                                            | 52              | K11                 | A36             | I    | ST                   | SPI3 data in                                      |  |  |  |  |

| SDO3                                                   | 51                                            | 53              | J10                 | B29             | 0    |                      | SPI3 data out                                     |  |  |  |  |

| SS3                                                    | 43                                            | 47              | L9                  | B26             | I/O  | ST                   | SPI3 slave synchronization or frame pulse I/O     |  |  |  |  |

| SCK2                                                   | 4                                             | 10              | E3                  | A7              | I/O  | ST                   | Synchronous serial clock input/output<br>for SPI2 |  |  |  |  |

| SDI2                                                   | 5                                             | 11              | F4                  | B6              | I    | ST                   | SPI2 data in                                      |  |  |  |  |

| SDO2                                                   | 6                                             | 12              | F2                  | A8              | 0    |                      | SPI2 data out                                     |  |  |  |  |

| SS2                                                    | 8                                             | 14              | F3                  | A9              | I/O  | ST                   | SPI2 slave synchronization or frame pulse I/O     |  |  |  |  |

| SCK4                                                   | 29                                            | 39              | L6                  | B22             | I/O  | ST                   | Synchronous serial clock input/output<br>for SPI4 |  |  |  |  |

| SDI4                                                   | 31                                            | 49              | L10                 | B27             | I    | ST                   | SPI4 data in                                      |  |  |  |  |

| SDO4                                                   | 32                                            | 50              | L11                 | A32             | 0    |                      | SPI4 data out                                     |  |  |  |  |

| SS4                                                    | 21                                            | 40              | K6                  | A27             | I/O  | ST                   | SPI4 slave synchronization or frame pulse I/O     |  |  |  |  |

| SCL1                                                   | 44                                            | 66              | E11                 | B36             | I/O  | ST                   | Synchronous serial clock input/output<br>for I2C1 |  |  |  |  |

| SDA1                                                   | 43                                            | 67              | E8                  | A44             | I/O  | ST                   | Synchronous serial data input/output<br>for I2C1  |  |  |  |  |

| SCL3                                                   | 51                                            | 53              | J10                 | B29             | I/O  | ST                   | Synchronous serial clock input/output<br>for I2C3 |  |  |  |  |

| SDA3                                                   | 50                                            | 52              | K11                 | A36             | I/O  | ST                   | Synchronous serial data input/output for I2C3     |  |  |  |  |

| SCL2                                                   | _                                             | 58              | H11                 | A39             | I/O  | ST                   | Synchronous serial clock input/output<br>for I2C2 |  |  |  |  |

| SDA2                                                   | _                                             | 59              | G10                 | B32             | I/O  | ST                   | Synchronous serial data input/output<br>for I2C2  |  |  |  |  |

| SCL4                                                   | 6                                             | 12              | F2                  | A8              | I/O  | ST                   | Synchronous serial clock input/outpu<br>for I2C4  |  |  |  |  |

| SDA4                                                   | 5                                             | 11              | F4                  | B6              | I/O  | ST                   | Synchronous serial data input/output<br>for I2C4  |  |  |  |  |

| SCL5                                                   | 32                                            | 50              | L11                 | A32             | I/O  | ST                   | Synchronous serial clock input/outpu<br>for I2C5  |  |  |  |  |

| SDA5                                                   | 31                                            | 49              | L10                 | B27             | I/O  | ST                   | Synchronous serial data input/output<br>for I2C5  |  |  |  |  |

| -                                                      | CMOS = CMO<br>ST = Schmitt 1<br>TTL = TTL inp | Frigger input   |                     |                 |      | nalog = A<br>= Outpu | Analog input P = Power<br>t I = Input             |  |  |  |  |

TABLE 1-1: PINOUT I/O DESCRIPTIONS (CONTINUED)

Note 1: Pin numbers are only provided for reference. See the "Device Pin Tables" section for device pin availability.

2: See 25.0 "Ethernet Controller" for more information.

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |  |  |  |  |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|--|--|--|--|--|

| 24.24        | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |  |  |  |

| 31:24        | DCRCDATA<31:24>   |                   |                   |                   |                   |                   |                  |                  |  |  |  |  |  |

| 22:16        | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |  |  |  |

| 23:16        | DCRCDATA<23:16>   |                   |                   |                   |                   |                   |                  |                  |  |  |  |  |  |

| 15.0         | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |  |  |  |

| 15:8         | DCRCDATA<15:8>    |                   |                   |                   |                   |                   |                  |                  |  |  |  |  |  |

| 7.0          | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |  |  |  |

| 7:0          |                   |                   |                   | DCRCDA            | ΓA<7:0>           |                   |                  |                  |  |  |  |  |  |

#### REGISTER 10-5: DCRCDATA: DMA CRC DATA REGISTER

#### Legend:

| Legend:           |                  |                           |                    |

|-------------------|------------------|---------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, re | ead as '0'         |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared      | x = Bit is unknown |

#### bit 31-0 DCRCDATA<31:0>: CRC Data Register bits

Writing to this register will seed the CRC generator. Reading from this register will return the current value of the CRC. Bits greater than PLEN will return '0' on any read.

<u>When CRCTYP (DCRCCON<15>) = 1</u> (CRC module is in IP Header mode): Only the lower 16 bits contain IP header checksum information. The upper 16 bits are always '0'. Data written to this register is converted and read back in 1's complement form (current IP header checksum value).

<u>When CRCTYP (DCRCCON<15>) = 0</u> (CRC module is in LFSR mode): Bits greater than PLEN will return '0' on any read.

#### REGISTER 10-6: DCRCXOR: DMA CRCXOR ENABLE REGISTER

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |  |  |  |  |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|--|--|--|--|--|

| 31:24        | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |  |  |  |

| 31.24        | DCRCXOR<31:24>    |                   |                   |                   |                   |                   |                  |                  |  |  |  |  |  |

| 00.40        | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |  |  |  |

| 23:16        | DCRCXOR<23:16>    |                   |                   |                   |                   |                   |                  |                  |  |  |  |  |  |

| 15.0         | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |  |  |  |

| 15:8         | DCRCXOR<15:8>     |                   |                   |                   |                   |                   |                  |                  |  |  |  |  |  |

| 7.0          | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |  |  |  |

| 7:0          |                   |                   |                   | DCRCXO            | R<7:0>            |                   |                  |                  |  |  |  |  |  |

| Legend:           |                  |                          |                    |

|-------------------|------------------|--------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, r | ead as '0'         |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared     | x = Bit is unknown |

#### bit 31-0 DCRCXOR<31:0>: CRC XOR Register bits

<u>When CRCTYP (DCRCCON<15>) = 1</u> (CRC module is in IP Header mode): This register is unused.

<u>When CRCTYP (DCRCCON<15>) = 0</u> (CRC module is in LFSR mode):

#### 1 = Enable the XOR input to the Shift register

0 = Disable the XOR input to the Shift register; data is shifted in directly from the previous stage in the register

#### TABLE 19-1: I2C1THROUGH I2C5 REGISTER MAP (CONTINUED)

| ess                         |                                 |               |         |        |       |        | •          |              |               | Bi      | ts    |             |             |           |          |        |      |          |            |

|-----------------------------|---------------------------------|---------------|---------|--------|-------|--------|------------|--------------|---------------|---------|-------|-------------|-------------|-----------|----------|--------|------|----------|------------|

| Virtual Address<br>(BF80_#) | Register<br>Name <sup>(1)</sup> | Bit Range     | 31/15   | 30/14  | 29/13 | 28/12  | 27/11      | 26/10        | 25/9          | 24/8    | 23/7  | 22/6        | 21/5        | 20/4      | 19/3     | 18/2   | 17/1 | 16/0     | All Resets |

| 5230                        | I2C5MSK                         | 31:16         | -       | —      | —     | _      |            | _            | —             | -       | _     | _           |             | _         | —        | —      | _    |          | 0000       |

| 5230                        | IZCONISK                        | 15:0          | -       | —      | —     | -      |            | _            |               |         |       |             | MSK         | <9:0>     |          |        |      | -        | 0000       |

| 5240                        | I2C5BRG                         | 31:16         | _       | _      | _     | —      | _          | —            | —             | —       | _     | —           | _           | —         | —        |        | -    | _        | 0000       |

| 5240                        |                                 | 15:0          | —       | —      | —     | —      |            |              |               |         | Ba    | ud Rate Ger | erator Regi | ster      |          |        | •    |          | 0000       |

| 5250                        | I2C5TRN                         | 31:16         | —       | —      | —     | —      | _          | —            | _             | —       | _     | —           | —           | —         | —        |        | —    | —        | 0000       |

| 0200                        |                                 | 15:0          | —       | _      | _     | —      | _          | —            | _             | _       |       | -           |             | Transmit  | Register |        | •    |          | 0000       |

| 5260                        | I2C5RCV                         | 31:16         | -       |        |       | _      | _          | _            |               | _       | _     | —           | —           | —         |          | _      | —    | _        | 0000       |

|                             |                                 | 15:0          | -       |        | —     | —      |            | —            |               | _       |       |             |             | Receive   | Register |        |      |          | 0000       |

| 5300                        | I2C1CON                         | 31:16         | _       | —      | —     | —      | —          | —            | —             | —       | —     | —           | —           | —         | —        | —      | —    | —        | 0000       |

|                             |                                 | 15:0          | ON      | _      | SIDL  | SCLREL | STRICT     | A10M         | DISSLW        | SMEN    | GCEN  | STREN       | ACKDT       | ACKEN     | RCEN     | PEN    | RSEN | SEN      | 1000       |

| 5310                        | I2C1STAT                        | 31:16         | —       | _      | _     | _      | _          | _            | —             | —       | _     | —           | —           | _         | _        |        | —    | _        | 0000       |

|                             |                                 |               | ACKSTAT | TRSTAT | —     | —      | —          | BCL          | GCSTAT        | ADD10   | IWCOL | I2COV       | D/A         | Р         | S        | R/W    | RBF  | TBF      | 0000       |

| 5320                        | I2C1ADD                         | 31:16         | _       | _      | —     | —      | _          |              | —             |         | _     | —           |             | _         | —        |        | —    | —        | 0000       |

|                             |                                 | 15:0          | _       | _      | _     | _      | _          | -            |               |         |       |             | ADD         | <9:0>     |          |        |      |          | 0000       |

| 5330                        | I2C1MSK                         | 31:16         | _       | _      | _     | _      | _          | -            | _             | -       | _     | _           | —           | -         | _        | -      | —    | —        | 0000       |

| 15:0 — — — — — — MSK<9:0>   |                                 |               |         |        |       |        |            |              | 0000          |         |       |             |             |           |          |        |      |          |            |

| 5340                        | I2C1BRG                         | 31:16         | _       |        |       | —      | _          | —            |               | _       | -     | -           |             | _         | —        |        | -    | _        | 0000       |

| -                           |                                 | 15:0          | _       |        |       | —      |            |              |               |         | Ва    | ud Rate Ger | Ū.          | ster      |          |        | 1    |          | 0000       |

| 5350                        | I2C1TRN                         | 31:16         | _       | —      | —     | _      | _          | _            | _             | _       | _     | _           | —           |           | —        | —      | —    | —        | 0000       |

|                             |                                 | 15:0          | _       | _      | _     | _      | _          | _            |               | _       |       |             |             | Transmit  | Register |        |      |          | 0000       |

| 5360                        | I2C1RCV                         | 31:16<br>15:0 | _       | _      |       |        |            | —            |               |         | —     | —           | —           | - Deseive |          | —      | —    | —        | 0000       |

|                             |                                 |               |         |        |       |        |            | _            |               |         |       |             |             | Receive   |          |        |      |          |            |

| 5400                        | 12C2CON(2)                      | 31:16<br>15:0 | ON      |        | -     | -      |            | -            | —<br>DI001144 | -       | -     | —<br>STREN  | —<br>ACKDT  |           |          | -      |      | -        | 0000       |

|                             |                                 |               |         | _      | SIDL  | SCLREL | STRICT     | A10M         | DISSLW        | SMEN    | GCEN  |             |             |           |          | PEN    | RSEN | SEN      | 1000       |

| 5410                        | 12C2STAT <sup>(2)</sup>         | 31:16         |         |        | _     | _      | _          | —<br>DCI     | —<br>         | -       | -     | -           | —<br>D/A    | —<br>P    | -        | —<br>• | -    | —<br>TDF | 0000       |

|                             |                                 | 15:0<br>31:16 | ACKSTAT | TRSTAT |       | _      | _          | BCL          | GCSTAT        | ADD10   | IWCOL | I2COV       | D/A         | Р         | S        | R/W    | RBF  | TBF      | 0000       |

| 5420                        | 12C2ADD(2)                      | 15:0          |         |        |       | _      | _          |              | _             | -       | —     | —           |             | <br><9:0> | —        |        | _    | —        | 0000       |

|                             |                                 | 31:16         | _       |        |       | _      |            | _            | _             |         | _     |             | ADD         | <9.0>     |          |        | _    | _        | 0000       |

| 5430                        | 12C2MSK <sup>(2)</sup>          | 15:0          |         |        |       |        |            |              | _             | _       | _     | _           |             | <0.0>     | _        |        | _    | _        | 0000       |

|                             |                                 |               |         |        |       |        | — <u> </u> |              |               |         |       |             |             | 0000      |          |        |      |          |            |

| 5440                        | I2C2BRG <sup>(2)</sup>          | 15:0          | _       |        |       | _      | _          | _            | _             |         | Ra    | ud Rate Ger | erator Regi | ster      | _        |        |      |          | 0000       |

|                             |                                 | 31:16         | _       | _      | _     | _      | _          | _            | _             | _       | Da    |             |             |           | _        |        | _    | _        | 0000       |

| 5450                        | I2C2TRN <sup>(2)</sup>          | 15:0          | _       | _      | _     |        | _          |              | _             |         |       |             |             | Transmit  | Register |        |      |          | 0000       |

|                             |                                 | 31:16         | _       | _      | _     | _      |            | _            | _             | _       | _     | _           | _           |           |          |        | _    | _        | 0000       |

| 5460                        | 12C2RCV <sup>(2)</sup>          | 15:0          | _       | _      | _     | _      | _          | _            | _             | _       |       |             |             | Receive   | Register |        |      |          | 0000       |

| Legen                       |                                 |               |         |        |       |        |            | Les are show | l<br>         | aire al |       |             |             | 110001100 |          |        |      |          | 0000       |

Legend: x = unknown value on Reset; --- = unimplemented, read as '0'. Reset values are shown in hexadecimal.

Note 1: All registers in this table except I2CxRCV have corresponding CLR, SET and INV registers at their virtual addresses, plus offsets of 0x4, 0x8 and 0xC, respectively. See Section 12.1.1 "CLR, SET and INV Registers" for more information.

2: This register is not available on 64-pin devices.

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3                  | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |  |

|--------------|-------------------|-------------------|-------------------|-------------------|------------------------------------|-------------------|------------------|------------------|--|--|

| 04-04        | R/W-x             | R/W-x             | R/W-x             | R/W-x             | R/W-x                              | R/W-x             | R/W-x            |                  |  |  |

| 31:24        |                   | YEAR1             | 0<3:0>            |                   |                                    | YEAR0             | 1<3:0>           |                  |  |  |

| 00.40        | R/W-x             | R/W-x             | R/W-x             | R/W-x             | R/W-x                              | R/W-x             | R/W-x            | R/W-x            |  |  |

| 23:16        |                   | MONTH             | 10<3:0>           |                   | MONTH01<3:0>                       |                   |                  |                  |  |  |

| 45.0         | R/W-x             | R/W-x             | R/W-x             | R/W-x             | R/W-x                              | R/W-x             | R/W-x            | R/W-x            |  |  |

| 15:8         |                   | DAY10             | <3:0>             |                   | DAY01<3:0>                         |                   |                  |                  |  |  |

| 7.0          | U-0               | U-0               | U-0               | U-0               | R/W-x                              | R/W-x             | R/W-x            | R/W-x            |  |  |

| 7:0          | —                 | —                 | _                 | _                 | WDAY01<3:0>                        |                   |                  |                  |  |  |

|              |                   | •                 |                   |                   | •                                  |                   |                  |                  |  |  |

| Legend:      |                   |                   |                   |                   |                                    |                   |                  |                  |  |  |

| R = Read     | able bit          |                   | W = Writable      | e bit             | U = Unimplemented bit, read as '0' |                   |                  |                  |  |  |

0' = Bit is cleared

#### REGISTER 22-4: RTCDATE: RTC DATE VALUE REGISTER

bit 31-28 YEAR10<3:0>: Binary-Coded Decimal Value of Years bits, 10 digits

'1' = Bit is set

bit 27-24 YEAR01<3:0>: Binary-Coded Decimal Value of Years bits, 1 digit

bit 23-20 MONTH10<3:0>: Binary-Coded Decimal Value of Months bits, 10 digits; contains a value from 0 to 1

bit 19-16 MONTH01<3:0>: Binary-Coded Decimal Value of Months bits, 1 digit; contains a value from 0 to 9

bit 15-12 DAY10<3:0>: Binary-Coded Decimal Value of Days bits, 10 digits; contains a value from 0 to 3

bit 11-8 DAY01<3:0>: Binary-Coded Decimal Value of Days bits, 1 digit; contains a value from 0 to 9

bit 7-4 Unimplemented: Read as '0'

-n = Value at POR

bit 3-0 WDAY01<3:0>: Binary-Coded Decimal Value of Weekdays bits,1 digit; contains a value from 0 to 6

**Note:** This register is only writable when RTCWREN = 1 (RTCCON<3>).

x = Bit is unknown

#### REGISTER 24-10: CIFLTCONO: CAN FILTER CONTROL REGISTER 0 (CONTINUED)

| bit 15    | FLTEN1: Filter 1 Enable bit<br>1 = Filter is enabled               |

|-----------|--------------------------------------------------------------------|

|           | 0 = Filter is disabled                                             |

| bit 14-13 | MSEL1<1:0>: Filter 1 Mask Select bits                              |

|           | 11 = Acceptance Mask 3 selected                                    |

|           | 10 = Acceptance Mask 2 selected<br>01 = Acceptance Mask 1 selected |

|           | 00 = Acceptance Mask 0 selected                                    |

| bit 12-8  | FSEL1<4:0>: FIFO Selection bits                                    |

|           | 11111 = Message matching filter is stored in FIFO buffer 31        |

|           | 11110 = Message matching filter is stored in FIFO buffer 30        |

|           | •                                                                  |

|           | •                                                                  |

|           | 00001 = Message matching filter is stored in FIFO buffer 1         |

|           | 00000 = Message matching filter is stored in FIFO buffer 0         |

| bit 7     | FLTEN0: Filter 0 Enable bit                                        |

|           | 1 = Filter is enabled<br>0 = Filter is disabled                    |

| bit 6-5   | MSEL0<1:0>: Filter 0 Mask Select bits                              |

|           | 11 = Acceptance Mask 3 selected                                    |

|           | 10 = Acceptance Mask 2 selected                                    |

|           | 01 = Acceptance Mask 1 selected<br>00 = Acceptance Mask 0 selected |

| bit 4-0   | FSEL0<4:0>: FIFO Selection bits                                    |

| DIL 4-0   | 11111 = Message matching filter is stored in FIFO buffer 31        |

|           | 11110 = Message matching filter is stored in FIFO buffer 30        |

|           | •                                                                  |

|           | •                                                                  |

|           | •<br>00001 = Message matching filter is stored in FIFO buffer 1    |

|           | 00000 = Message matching filter is stored in FIFO buffer 0         |

Note: The bits in this register can only be modified if the corresponding filter enable (FLTENn) bit is '0'.

| Bit Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

|-----------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|

| 31:24     | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 31.24     |                   | —                 | —                 | —                 |                   | —                 |                  | _                |

| 23:16     | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 23.10     | _                 | —                 | —                 | —                 | _                 | —                 | _                | —                |

| 15:8      | U-0               | U-0               | U-0               | U-0               | U-0               | R/W-0             | R/W-0            | R/W-0            |

| 10.0      | _                 | —                 | —                 | —                 | _                 | R                 | XBUFSZ<6:        | 4>               |

| 7:0       | R/W-0             | R/W-0             | R/W-0             | R/W-0             | U-0               | U-0               | U-0              | U-0              |

| 7.0       |                   | RXBUF             | SZ<3:0>           |                   |                   | _                 |                  | _                |

#### REGISTER 25-2: ETHCON2: ETHERNET CONTROLLER CONTROL REGISTER 2

#### Legend:

| Logona.           |                  |                                    |                    |  |

|-------------------|------------------|------------------------------------|--------------------|--|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read as '0' |                    |  |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared               | x = Bit is unknown |  |

#### bit 31-11 Unimplemented: Read as '0'

bit 10-4 RXBUFSZ<6:0>: RX Data Buffer Size for All RX Descriptors (in 16-byte increments) bits

1111111 = RX data Buffer size for descriptors is 2032 bytes

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.</li

Note 1: This register is only used for RX operations.

2: The bits in this register may only be changed while the RXEN bit (ETHCON1<8>) = 0.

| Bit<br>Range | Bit<br>31/23/15/7      | Bit<br>30/22/14/6     | Bit<br>29/21/13/5     | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

|--------------|------------------------|-----------------------|-----------------------|-------------------|-------------------|-------------------|------------------|------------------|

| 31:24        | U-0                    | U-0                   | U-0                   | U-0               | U-0               | U-0               | U-0              | U-0              |

| 31.24        | —                      |                       | _                     | _                 | _                 | _                 | _                | _                |

| 23:16        | R/W-0                  | R/W-0                 | R/W-0                 | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |

| 23.10        | BUFCNT<7:0>            |                       |                       |                   |                   |                   |                  |                  |

| 15:8         | U-0                    | U-0                   | U-0                   | U-0               | U-0               | U-0               | U-0              | U-0              |

| 15.0         | —                      |                       | _                     | _                 | _                 | _                 | _                | _                |

| 7.0          | R/W-0                  | R/W-0                 | R/W-0                 | U-0               | U-0               | U-0               | U-0              | U-0              |

| 7:0          | ETHBUSY <sup>(1)</sup> | TXBUSY <sup>(2)</sup> | RXBUSY <sup>(2)</sup> | —                 |                   | _                 |                  | _                |

#### REGISTER 25-15: ETHSTAT: ETHERNET CONTROLLER STATUS REGISTER

### Legend:

| Legena.           |                  |                                    |                    |

|-------------------|------------------|------------------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read as '0' |                    |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared               | x = Bit is unknown |

#### bit 31-24 Unimplemented: Read as '0'

#### bit 23-16 **BUFCNT<7:0>:** Packet Buffer Count bits

Number of packet buffers received in memory. Once a packet has been successfully received, this register is incremented by hardware based on the number of descriptors used by the packet. Software decrements the counter (by writing to the BUFCDEC bit (ETHCON1<0>) for each descriptor used) after a packet has been read out of the buffer. The register does not roll over (0xFF to 0x00) when hardware tries to increment the register and the register is already at 0xFF. Conversely, the register does not roll under (0x00 to 0xFF) when software tries to decrement the register and the register is already at 0x000. When software attempts to decrement the same time that the hardware attempts to increment the counter, the counter value will remain unchanged.

When this register value reaches 0xFF, the RX logic will halt (only if automatic Flow Control is enabled) awaiting software to write the BUFCDEC bit in order to decrement the register below 0xFF.

If automatic Flow Control is disabled, the RXDMA will continue processing and the BUFCNT will saturate at a value of 0xFF.

When this register is non-zero, the PKTPEND status bit will be set and an interrupt may be generated, depending on the value of the ETHIEN bit <PKTPENDIE> register.

When the ETHRXST register is written, the BUFCNT counter is automatically cleared to 0x00.

- **Note:** BUFCNT will not be cleared when ON is set to '0'. This enables software to continue to utilize and decrement this count.

- bit 15-8 **Unimplemented:** Read as '0'

- bit 7 ETHBUSY: Ethernet Module busy bit<sup>(1)</sup>

1 = Ethernet logic has been turned on (ON (ETHCON1<15>) = 1) or is completing a transaction 0 = Ethernet logic is idle

This bit indicates that the module has been turned on or is completing a transaction after being turned off.

- bit 6 **TXBUSY:** Transmit Busy bit<sup>(2)</sup>

- 1 = TX logic is receiving data

- 0 = TX logic is idle

This bit indicates that a packet is currently being transmitted. A change in this status bit is not necessarily reflected by the TXDONE interrupt, as TX packets may be aborted or rejected by the MAC.

- **Note 1:** This bit will be *set* when the ON bit (ETHCON1<15>) = 1.

- **2:** This bit will be *cleared* when the ON bit (ETHCON1<15>) = 0.

| REGISTER 25-23: | EMAC1CFG1: ETHERNET CONTROLLER MAC CONFIGURATION 1 REGISTER |

|-----------------|-------------------------------------------------------------|

|                 |                                                             |

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|

| 31:24        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 31.24        | —                 | —                 | —                 |                   | _                 | —                 | —                | —                |

| 23:16        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 23.10        |                   | —                 | —                 | _                 | _                 |                   |                  | —                |

|              | R/W-1             | R/W-0             | U-0               | U-0               | R/W-0             | R/W-0             | R/W-0            | R/W-0            |

| 15:8         | SOFT<br>RESET     | SIM<br>RESET      | —                 |                   | RESET<br>RMCS     | RESET<br>RFUN     | RESET<br>TMCS    | RESET<br>TFUN    |

|              | U-0               | U-0               | U-0               | R/W-0             | R/W-1             | R/W-1             | R/W-0            | R/W-1            |

| 7:0          |                   |                   | _                 | LOOPBACK          | TX<br>PAUSE       | RX<br>PAUSE       | PASSALL          | RX<br>ENABLE     |

| Legend: |  |

|---------|--|

| Logona.           |                  |                                    |                    |  |

|-------------------|------------------|------------------------------------|--------------------|--|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read as '0' |                    |  |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared               | x = Bit is unknown |  |

#### bit 31-16 Unimplemented: Read as '0'

| bit 15    | SOFTRESET: Soft Reset bit                                                                        |

|-----------|--------------------------------------------------------------------------------------------------|

|           | Setting this bit will put the MACMII in reset. Its default value is '1'.                         |

| bit 14    | SIMRESET: Simulation Reset bit                                                                   |

|           | Setting this bit will cause a reset to the random number generator within the Transmit Function. |

| bit 13-12 | Unimplemented: Read as '0'                                                                       |

| bit 11    | RESETRMCS: Reset MCS/RX bit                                                                      |

|           | Setting this bit will put the MAC Control Sub-layer/Receive domain logic in reset.               |

| bit 10    | RESETRFUN: Reset RX Function bit                                                                 |

|           | Setting this bit will put the MAC Receive function logic in reset.                               |

| bit 9     | RESETTMCS: Reset MCS/TX bit                                                                      |

|           | Setting this bit will put the MAC Control Sub-layer/TX domain logic in reset.                    |

| bit 8     | RESETTFUN: Reset TX Function bit                                                                 |

|           | Setting this bit will put the MAC Transmit function logic in reset.                              |

| bit 7-5   | Unimplemented: Read as '0'                                                                       |

| bit 4     | LOOPBACK: MAC Loopback mode bit                                                                  |

|           | 1 = MAC Transmit interface is loop backed to the MAC Receive interface                           |

| bit 3     | 0 = MAC normal operation<br><b>TXPAUSE:</b> MAC TX Flow Control bit                              |

| DILS      | 1 = PAUSE Flow Control frames are allowed to be transmitted                                      |

|           | 0 = PAUSE Flow Control frames are blocked                                                        |

| bit 2     | RXPAUSE: MAC RX Flow Control bit                                                                 |

|           | 1 = The MAC acts upon received PAUSE Flow Control frames                                         |

|           | 0 = Received PAUSE Flow Control frames are ignored                                               |

| bit 1     | PASSALL: MAC Pass all Receive Frames bit                                                         |

|           | 1 = The MAC will accept all frames regardless of type (Normal vs. Control)                       |

|           | 0 = The received Control frames are ignored                                                      |

| bit 0     | RXENABLE: MAC Receive Enable bit                                                                 |

|           | 1 = Enable the MAC receiving of frames                                                           |

|           |                                                                                                  |

0 = Disable the MAC receiving of frames

**Note:** Both 16-bit and 32-bit accesses are allowed to these registers (including the SET, CLR and INV registers). 8-bit accesses are not allowed and are ignored by the hardware.

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|--|

| 31:24        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |  |

| 31.24        |                   | —                 |                   |                   | —                 |                   | —                | —                |  |

| 22:46        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |  |

| 23:16        | —                 | —                 | _                 | _                 | —                 | _                 | _                | —                |  |

| 15.0         | R/W-P             | R/W-P             | R/W-P             | R/W-P             | R/W-P             | R/W-P             | R/W-P            | R/W-P            |  |

| 15:8         | STNADDR4<7:0>     |                   |                   |                   |                   |                   |                  |                  |  |

| 7.0          | R/W-P             | R/W-P             | R/W-P             | R/W-P             | R/W-P             | R/W-P             | R/W-P            | R/W-P            |  |

| 7:0          | STNADDR3<7:0>     |                   |                   |                   |                   |                   |                  |                  |  |

#### REGISTER 25-38: EMAC1SA1: ETHERNET CONTROLLER MAC STATION ADDRESS 1 REGISTER

| Legend:           |                  | P = Programmable bit               |                    |  |

|-------------------|------------------|------------------------------------|--------------------|--|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read as '0' |                    |  |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared               | x = Bit is unknown |  |

bit 31-16 Unimplemented: Read as '0'

- bit 15-8 **STNADDR4<7:0>:** Station Address Octet 4 bits These bits hold the fourth transmitted octet of the station address.

- bit 7-0 **STNADDR3<7:0>:** Station Address Octet 3 bits These bits hold the third transmitted octet of the station address.

Note 1: Both 16-bit and 32-bit accesses are allowed to these registers (including the SET, CLR and INV registers). 8-bit accesses are not allowed and are ignored by the hardware.

2: This register is loaded at reset from the factory preprogrammed station address.

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2      | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------------|------------------|------------------|

| 31:24        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0                    | U-0              | U-0              |

| 31.24        | —                 | —                 | —                 | —                 | —                 | —                      | —                | —                |

| 23:16        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0                    | U-0              | U-0              |

| 23.10        |                   |                   | _                 |                   | —                 | _                      |                  |                  |

| 15.0         | R/W-0             | U-0               | U-0               | U-0               | U-0               | R/W-0                  | R/W-0            | R/W-1            |

| 15:8         | ON <sup>(1)</sup> | —                 | —                 | —                 | —                 | VREFSEL <sup>(2)</sup> | BGSEL            | <1:0> <b>(2)</b> |

| 7:0          | U-0               | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0                  | R/W-0            | R/W-0            |

| 7.0          | _                 | CVROE             | CVRR              | CVRSS             | CVR<3:0>          |                        |                  |                  |

#### REGISTER 27-1: CVRCON: COMPARATOR VOLTAGE REFERENCE CONTROL REGISTER

#### Legend:

| 0                 |                  |                                    |                    |  |

|-------------------|------------------|------------------------------------|--------------------|--|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read as '0' |                    |  |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared               | x = Bit is unknown |  |

#### bit 31-16 Unimplemented: Read as '0'

ON: Comparator Voltage Reference On bit<sup>(1)</sup> bit 15 Setting or clearing this bit does not affect the other bits in this register. 1 = Module is enabled0 = Module is disabled and does not consume current bit 14-11 Unimplemented: Read as '0' VREFSEL: Voltage Reference Select bit<sup>(2)</sup> bit 10 1 = CVREF = VREF+0 = CVREF is generated by the resistor network BGSEL<1:0>: Band Gap Reference Source bits<sup>(2)</sup> bit 9-8 11 = IVRFF = VRFF+10 = Reserved 01 = IVREF = 0.6V (nominal, default)

- 00 = IVREF = 1.2V (nominal)

- bit 7 Unimplemented: Read as '0'

- bit 6 **CVROE:** CVREFOUT Enable bit

- 1 = Voltage level is output on CVREFOUT pin

- 0 = Voltage level is disconnected from CVREFOUT pin

#### bit 5 **CVRR:** CVREF Range Selection bit

- 1 = 0 to 0.625 CVRSRC, with CVRSRC/24 step size

- 0 = 0.25 CVRSRC to 0.719 CVRSRC, with CVRSRC/32 step size

#### bit 4 **CVRSS:** CVREF Source Selection bit

- 1 = Comparator voltage reference source, CVRSRC = (VREF+) (VREF-)0 = Comparator voltage reference source, CVRSRC = AVDD - AVSS **CVR<3:0>:** CVREF Value Selection  $0 \le CVR<3:0> \le 15$  bits

- bit 3-0 When CVRR = 1:  $CVREF = (CVR < 3:0 > /24) \bullet (CVRSRC)$ When CVRR = 0:  $CVREF = 1/4 \bullet (CVRSRC) + (CVR<3:0>/32) \bullet (CVRSRC)$

- Note 1: When using the 1:1 PBCLK divisor, the user's software should not read/write the peripheral's SFRs in the SYSCLK cycle immediately following the instruction that clears the module's ON bit.

- 2: These bits are not available on PIC32MX575/675/775/795 devices. On these devices, the reset value for CVRON is '0000'.

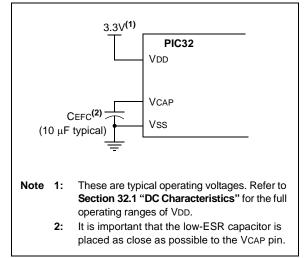

#### 29.2 On-Chip Voltage Regulator

All PIC32MX5XX/6XX/7XX devices' core and digital logic are designed to operate at a nominal 1.8V. To simplify system designs, most devices in the PIC32MX-5XX/6XX/7XX family incorporate an on-chip regulator providing the required core logic voltage from VDD.

A low-ESR capacitor (such as tantalum) must be connected to the VCAP pin (see Figure 29-1). This helps to maintain the stability of the regulator. The recommended value for the filter capacitor is provided in **Section 32.1 "DC Characteristics"**.

Note: It is important that the low-ESR capacitor is placed as close as possible to the VCAP pin.

#### 29.2.1 ON-CHIP REGULATOR AND POR

It takes a fixed delay for the on-chip regulator to generate an output. During this time, designated as TPU, code execution is disabled. TPU is applied every time the device resumes operation after any power-down, including Sleep mode.

#### 29.2.2 ON-CHIP REGULATOR AND BOR

PIC32MX5XX/6XX/7XX devices also have a simple brown-out capability. If the voltage supplied to the regulator is inadequate to maintain a regulated level, the regulator Reset circuitry will generate a Brown-out Reset (BOR). This event is captured by the BOR flag bit (RCON<1>). The brown-out voltage levels are specified in **Section 32.1 "DC Characteristics"**.

### FIGURE 29-1: CONNECTIONS FOR THE ON-CHIP REGULATOR

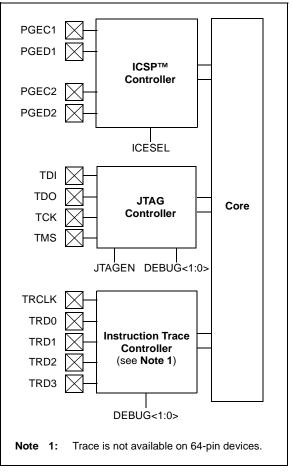

#### 29.3 **Programming and Diagnostics**

PIC32MX5XX/6XX/7XX devices provide a complete range of programming and diagnostic features that can increase the flexibility of any application using them. These features allow system designers to include:

- Simplified field programmability using two-wire In-Circuit Serial Programming<sup>™</sup> (ICSP<sup>™</sup>) interfaces

- Debugging using ICSP

- Programming and debugging capabilities using the EJTAG extension of JTAG

- JTAG boundary scan testing for device and board diagnostics

PIC32 devices incorporate two programming and diagnostic modules, and a trace controller, that provide a range of functions to the application developer.

FIGURE 29-2:

PROGRAMMING, DEBUGGING, AND TRACE PORTS BLOCK DIAGRAM

NOTES:

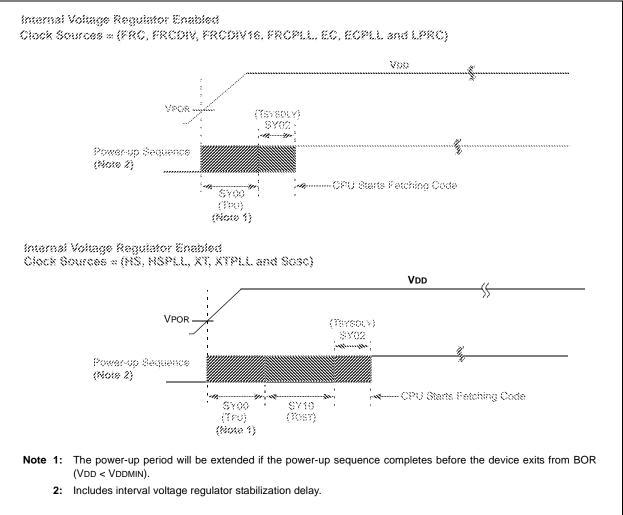

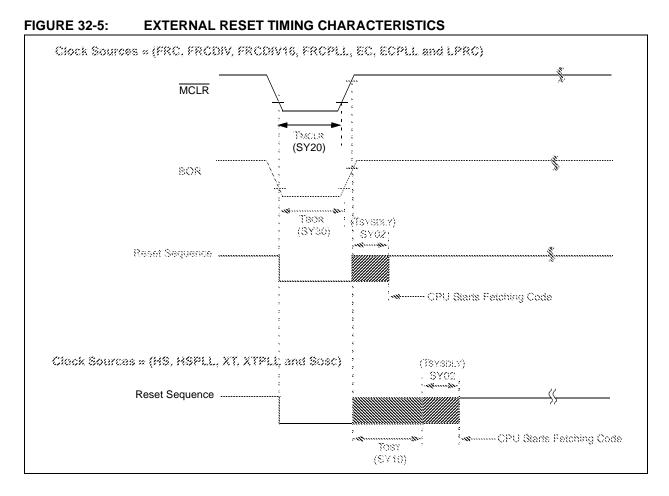

### FIGURE 32-4: POWER-ON RESET TIMING CHARACTERISTICS

#### TABLE 32-22: RESETS TIMING

| AC CHARACTERISTICS |         |                                                                                                                                            | $\begin{array}{l} \mbox{Standard Operating Conditions: 2.3V to 3.6V} \\ \mbox{(unless otherwise stated)} \\ \mbox{Operating temperature} & -40^{\circ}C \leq TA \leq +85^{\circ}C \mbox{ for Industrial} \\ & -40^{\circ}C \leq TA \leq +105^{\circ}C \mbox{ for V-Temp} \end{array}$ |                              |      |       |                |

|--------------------|---------|--------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------|------|-------|----------------|

| Param.<br>No.      | Symbol  | Characteristics <sup>(1)</sup>                                                                                                             | Min.                                                                                                                                                                                                                                                                                  | Typical <sup>(2)</sup>       | Max. | Units | Conditions     |

| SY00               | Τρυ     | Power-up Period<br>Internal Voltage Regulator Enabled                                                                                      | _                                                                                                                                                                                                                                                                                     | 400                          | 600  | μS    | -40°C to +85°C |

| SY02               | TSYSDLY | System Delay Period:<br>Time Required to Reload Device<br>Configuration Fuses plus SYSCLK<br>Delay before First instruction is<br>Fetched. |                                                                                                                                                                                                                                                                                       | 1 μs +<br>8 SYSCLK<br>cycles | _    | _     | -40°C to +85°C |