Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFI

| Product Status             | Active                                                                          |

|----------------------------|---------------------------------------------------------------------------------|

| Core Processor             | MIPS32® M4K™                                                                    |

| Core Size                  | 32-Bit Single-Core                                                              |

| Speed                      | 80MHz                                                                           |

| Connectivity               | Ethernet, I <sup>2</sup> C, SPI, UART/USART, USB OTG                            |

| Peripherals                | Brown-out Detect/Reset, DMA, POR, PWM, WDT                                      |

| Number of I/O              | 85                                                                              |

| Program Memory Size        | 128KB (128K x 8)                                                                |

| Program Memory Type        | FLASH                                                                           |

| EEPROM Size                | -                                                                               |

| RAM Size                   | 32K x 8                                                                         |

| Voltage - Supply (Vcc/Vdd) | 2.3V ~ 3.6V                                                                     |

| Data Converters            | A/D 16x10b                                                                      |

| Oscillator Type            | Internal                                                                        |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                               |

| Mounting Type              | Surface Mount                                                                   |

| Package / Case             | 100-TQFP                                                                        |

| Supplier Device Package    | 100-TQFP (12x12)                                                                |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic32mx664f128lt-i-pt |

|                            |                                                                                 |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

|                  | USB and Ethernet |                         |                  |     |          |                        |                                          |                       |                    |                                 |                              |             |         |      |       |                         |

|------------------|------------------|-------------------------|------------------|-----|----------|------------------------|------------------------------------------|-----------------------|--------------------|---------------------------------|------------------------------|-------------|---------|------|-------|-------------------------|

| Device           | Pins             | Program Memory (KB)     | Data Memory (KB) | USB | Ethernet | Timers/Capture/Compare | DMA Channels<br>(Programmable/Dedicated) | UART <sup>(2,3)</sup> | SPI <sup>(3)</sup> | I <sup>2</sup> C <sup>(3)</sup> | 10-bit 1 Msps ADC (Channels) | Comparators | dSP/PMP | JTAG | Trace | Packages <sup>(4)</sup> |

| PIC32MX664F064H  | 64               | 64 + 12 <sup>(1)</sup>  | 32               | 1   | 1        | 5/5/5                  | 4/4                                      | 6                     | 3                  | 4                               | 16                           | 2           | Yes     | Yes  | No    | PT,<br>MR               |

| PIC32MX664F128H  | 64               | 128 + 12 <sup>(1)</sup> | 32               | 1   | 1        | 5/5/5                  | 4/4                                      | 6                     | 3                  | 4                               | 16                           | 2           | Yes     | Yes  | No    | PT,<br>MR               |

| PIC32MX675F256H  | 64               | 256 + 12 <sup>(1)</sup> | 64               | 1   | 1        | 5/5/5                  | 8/4                                      | 6                     | 3                  | 4                               | 16                           | 2           | Yes     | Yes  | No    | PT,<br>MR               |

| PIC32MX675F512H  | 64               | 512 + 12 <sup>(1)</sup> | 64               | 1   | 1        | 5/5/5                  | 8/4                                      | 6                     | 3                  | 4                               | 16                           | 2           | Yes     | Yes  | No    | PT,<br>MR               |

| PIC32MX695F512H  | 64               | 512 + 12 <sup>(1)</sup> | 128              | 1   | 1        | 5/5/5                  | 8/4                                      | 6                     | 3                  | 4                               | 16                           | 2           | Yes     | Yes  | No    | PT,<br>MR               |

| PIC32MX664F064L  | 100              | 64 + 12 <sup>(1)</sup>  | 32               | 1   | 1        | 5/5/5                  | 4/4                                      | 6                     | 4                  | 5                               | 16                           | 2           | Yes     | Yes  | Yes   | PT, PF,<br>BG           |

| PIC32MX664F128L  | 100              | 128 + 12 <sup>(1)</sup> | 32               | 1   | 1        | 5/5/5                  | 4/4                                      | 6                     | 4                  | 5                               | 16                           | 2           | Yes     | Yes  | Yes   | PT, PF,<br>BG           |

| PIC32MX675F256L  | 100              | 256 + 12 <sup>(1)</sup> | 64               | 1   | 1        | 5/5/5                  | 8/4                                      | 6                     | 4                  | 5                               | 16                           | 2           | Yes     | Yes  | Yes   | PT, PF,<br>BG           |

| PIC32MX675F512L  | 100              | 512 + 12 <sup>(1)</sup> | 64               | 1   | 1        | 5/5/5                  | 8/4                                      | 6                     | 4                  | 5                               | 16                           | 2           | Yes     | Yes  | Yes   | PT, PF,<br>BG, TL       |

| PIC32MX695F512L  | 100              | 512 + 12 <sup>(1)</sup> | 128              | 1   | 1        | 5/5/5                  | 8/4                                      | 6                     | 4                  | 5                               | 16                           | 2           | Yes     | Yes  | Yes   | PT, PF,<br>BG, TL       |

| Legend: PF, PT = | TQFP             | MR = QF                 | N                |     | BG =     | TFBGA                  | 4                                        | TL =                  | VTL/               | ų( <del>5</del> )               |                              |             |         |      |       |                         |

| TABLE 2: PIC32MX6XX USB AND ETHERNET FEATURES |

|-----------------------------------------------|

|-----------------------------------------------|

Legend: PF, PT = TQFP MR = QFN BG = Note 1: This device features 12 KB boot Flash memory.

2: CTS and RTS pins may not be available for all UART modules. Refer to the "Device Pin Tables" section for more information.

3: Some pins between the UART, SPI and I<sup>2</sup>C modules may be shared. Refer to the "Device Pin Tables" section for more information.

4: Refer to 34.0 "Packaging Information" for more information.

5: 100-pin devices other than those listed here are available in the VTLA package upon request. Please contact your local Microchip Sales Office for details.

#### TABLE 12: PIN NAMES FOR USB, ETHERNET, AND CAN DEVICES (CONTINUED)

| 1     | 21-PIN TFBGA (BOTTOM VIEW                                                                                                                                                                                                                                                           | ")    | L11                                         |  |  |  |  |  |  |

|-------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------|---------------------------------------------|--|--|--|--|--|--|

| Not   | PIC32MX764F128L       L1       A11         PIC32MX775F256L       PIC32MX775F512L       A11         PIC32MX795F512L       Vote:       The TFBGA package skips from row "H" to row "J" and has no "I" row.       A1         Pin #       Full Pin Name       Pin #       Full Pin Name |       |                                             |  |  |  |  |  |  |

| Pin # | Full Pin Name                                                                                                                                                                                                                                                                       | Pin # | Full Pin Name                               |  |  |  |  |  |  |

| J3    | PGED2/AN7/RB7                                                                                                                                                                                                                                                                       | K8    | Vdd                                         |  |  |  |  |  |  |

| J4    | AVDD                                                                                                                                                                                                                                                                                | K9    | AETXD1/SCK3/U4TX/U1RTS/CN21/RD15            |  |  |  |  |  |  |

| J5    | J5 AN11/ERXERR/AETXERR/PMA12/RB11                                                                                                                                                                                                                                                   |       | USBID/RF3                                   |  |  |  |  |  |  |

| J6    | TCK/RA1                                                                                                                                                                                                                                                                             | K11   | SDA3/SDI3/U1RX/RF2                          |  |  |  |  |  |  |

| J7    | AN12/ERXD0/AECRS/PMA11/RB12                                                                                                                                                                                                                                                         | L1    | PGEC2/AN6/OCFA/RB6                          |  |  |  |  |  |  |

| J8    | No Connect (NC)                                                                                                                                                                                                                                                                     | L2    | VREF-/CVREF-/AERXD2/PMA7/RA9                |  |  |  |  |  |  |

| J9    | No Connect (NC)                                                                                                                                                                                                                                                                     | L3    | AVss                                        |  |  |  |  |  |  |

| J10   | SCL3/SDO3/U1TX/RF8                                                                                                                                                                                                                                                                  | L4    | AN9/C2OUT/RB9                               |  |  |  |  |  |  |

| J11   | D-/RG3                                                                                                                                                                                                                                                                              | L5    | AN10/CVREFOUT/PMA13/RB10                    |  |  |  |  |  |  |

| K1    | PGEC1/AN1/CN3/RB1                                                                                                                                                                                                                                                                   | L6    | AC1TX/SCK4/U5TX/U2RTS/RF13                  |  |  |  |  |  |  |

| K2    | K2 PGED1/AN0/CN2/RB0                                                                                                                                                                                                                                                                |       | AN13/ERXD1/AECOL/PMA10/RB13                 |  |  |  |  |  |  |

| K3    | K3 VREF+/CVREF+/AERXD3/PMA6/RA10                                                                                                                                                                                                                                                    |       | AN15/ERXD3/AETXD2/OCFB/PMALL/PMA0/CN12/RB15 |  |  |  |  |  |  |

| K4    | AN8/C1OUT/RB8                                                                                                                                                                                                                                                                       | L9    | AETXD0/SS3/U4RX/U1CTS/CN20/RD14             |  |  |  |  |  |  |

| K5    | No Connect (NC)                                                                                                                                                                                                                                                                     | L10   | SDA5/SDI4/U2RX/PMA9/CN17/RF4                |  |  |  |  |  |  |

| K6    | AC1RX/SS4/U5RX/U2CTS/RF12                                                                                                                                                                                                                                                           | L11   | SCL5/SDO4/U2TX/PMA8/CN18/RF5                |  |  |  |  |  |  |

| K7    | AN14/ERXD2/AETXD3/PMALH/PMA1/RB14                                                                                                                                                                                                                                                   |       |                                             |  |  |  |  |  |  |

Note 1: This pin is not available on PIC32MX764F128L devices.

2: Shaded pins are 5V tolerant.

#### REGISTER 7-6: IPCx: INTERRUPT PRIORITY CONTROL REGISTER (CONTINUED)

| REGIST    |                                                                                                                       |

|-----------|-----------------------------------------------------------------------------------------------------------------------|

| bit 12-10 | IP01<2:0>: Interrupt Priority bits                                                                                    |

|           | 111 = Interrupt priority is 7                                                                                         |

|           | •                                                                                                                     |

|           |                                                                                                                       |

|           | 010 = Interrupt priority is 2                                                                                         |

|           | 001 = Interrupt priority is 1                                                                                         |

|           | 000 = Interrupt is disabled                                                                                           |

| bit 9-8   | IS01<1:0>: Interrupt Sub-priority bits                                                                                |

|           | 11 = Interrupt sub-priority is 3                                                                                      |

|           | 10 = Interrupt sub-priority is 2                                                                                      |

|           | 01 = Interrupt sub-priority is 1                                                                                      |

|           | 00 = Interrupt sub-priority is 0                                                                                      |

| bit 7-5   | Unimplemented: Read as '0'                                                                                            |

| bit 4-2   | IP00<2:0>: Interrupt Priority bits                                                                                    |

|           | 111 = Interrupt priority is 7                                                                                         |

|           | •                                                                                                                     |

|           |                                                                                                                       |

|           | 010 = Interrupt priority is 2                                                                                         |

|           | 001 = Interrupt priority is 1                                                                                         |

|           | 000 = Interrupt is disabled                                                                                           |

| bit 1-0   | IS00<1:0>: Interrupt Sub-priority bits                                                                                |

|           | 11 = Interrupt sub-priority is 3                                                                                      |

|           | 10 = Interrupt sub-priority is 2                                                                                      |

|           | 01 = Interrupt sub-priority is 1                                                                                      |

|           | 00 = Interrupt sub-priority is 0                                                                                      |

| Nete      | This projection proposed to a proposite definition of the IDOs projection Defaulty T-11 T-1 ( ) ( )                   |

| Note:     | This register represents a generic definition of the IPCx register. Refer to Table 7-1 for the exact bit definitions. |

|           |                                                                                                                       |

#### **Control Registers** 9.2

#### **TABLE 9-1:** PREFETCH REGISTER MAP

| ess                         |                         |               |                                      |       |       |       |       |       |        | Bi      | ts                  |      |       |            |        |       |           |        |              |

|-----------------------------|-------------------------|---------------|--------------------------------------|-------|-------|-------|-------|-------|--------|---------|---------------------|------|-------|------------|--------|-------|-----------|--------|--------------|

| Virtual Address<br>(BF88_#) | Register<br>Name        | Bit Range     | 31/15                                | 30/14 | 29/13 | 28/12 | 27/11 | 26/10 | 25/9   | 24/8    | 23/7                | 22/6 | 21/5  | 20/4       | 19/3   | 18/2  | 17/1      | 16/0   | All Resets   |

| 4000                        | CHECON <sup>(1,2)</sup> | 31:16         | —                                    |       | —     | _     | _     | _     | —      | _       |                     | —    | _     |            | -      | _     | _         | CHECOH | 0000         |

| 4000                        | CHECON                  | 15:0          |                                      | _     | —     | _     | _     | _     | DCSZ   | <1:0>   | _                   | —    | PREFE | N<1:0>     | _      | F     | PFMWS<2:0 | >      | 0007         |

| 4010                        | CHEACC <sup>(1)</sup>   | 31:16         | CHEWEN                               | —     | —     | —     | —     | —     | —      | —       | -                   | —    | —     | _          | —      | —     | —         |        | 0000         |

| 4010                        |                         | 15:0          | —                                    | —     | —     | —     | —     | —     | —      | —       | -                   | —    | —     | —          |        | CHEID | X<3:0>    |        | 0000         |

| 4020                        | CHETAG <sup>(1)</sup>   |               | LTAGBOOT — — — — — — — LTAG<23:16> 0 |       |       |       |       |       |        | 00xx    |                     |      |       |            |        |       |           |        |              |

| .020                        | 01121710                | 15:0          |                                      |       |       |       |       | LTAG< | <15:4> |         |                     |      |       |            | LVALID | LLOCK | LTYPE     | —      | xxx2         |

| 4030                        | CHEMSK <sup>(1)</sup>   | 31:16         | —                                    | _     | —     | —     | _     | —     |        | —       | —                   | —    | —     | _          | _      | _     |           | —      | 0000         |

|                             |                         | 15:0          |                                      |       |       |       |       |       |        |         |                     | 0000 |       |            |        |       |           |        |              |

| 4040                        | CHEW0                   | 31:16         | CHEW0<31:0>                          |       |       |       |       |       |        |         |                     | XXXX |       |            |        |       |           |        |              |

|                             |                         | 15:0          |                                      |       |       |       |       |       |        |         |                     | XXXX |       |            |        |       |           |        |              |

| 4050                        | CHEW1                   | 31:16         | CHEW1<31:0>                          |       |       |       |       |       |        |         |                     | XXXX |       |            |        |       |           |        |              |

|                             |                         | 15:0          |                                      |       |       |       |       |       |        |         |                     | XXXX |       |            |        |       |           |        |              |

| 4060                        | CHEW2                   | 31:16<br>15:0 |                                      |       |       |       |       |       |        |         |                     | XXXX |       |            |        |       |           |        |              |

|                             |                         | 31:16         |                                      |       |       |       |       |       |        |         |                     |      |       |            |        |       |           |        | xxxx<br>xxxx |

| 4070                        | CHEW3                   | 15:0          |                                      |       |       |       |       |       |        | CHEWS   | 8<31:0>             |      |       |            |        |       |           |        | XXXX         |

|                             |                         | 31:16         | _                                    | _     | _     | _     | _     | _     | _      |         |                     |      | CI    | HELRU<24:1 | 6>     |       |           |        | 0000         |

| 4080                        | CHELRU                  | 15:0          |                                      |       |       |       |       |       |        | CHELR   | J<15:0>             |      | 0.    |            |        |       |           |        | 0000         |

|                             |                         | 31:16         |                                      |       |       |       |       |       |        |         |                     |      |       |            |        |       |           |        | xxxx         |

| 4090                        | CHEHIT                  | 15:0          |                                      |       |       |       |       |       |        | CHEHI   | <sup>-</sup> <31:0> |      |       |            |        |       |           |        | xxxx         |

|                             |                         | 31:16         |                                      |       |       |       |       |       |        |         |                     |      |       |            |        |       |           |        | xxxx         |

| 40A0                        | CHEMIS                  | 15:0          |                                      |       |       |       |       |       |        | CHEMIS  | 5<31:0>             |      |       |            |        |       |           |        | xxxx         |

| 4000                        | CHEPFABT                | 31:16         |                                      |       |       |       |       |       |        | CHEPFAI | OT -21-0-           |      |       |            |        |       |           |        | xxxx         |

| 4000                        | CHEFFABI                | 15:0          |                                      |       |       |       |       |       |        | UNEPFAI | 51<31.0>            |      |       |            |        |       |           |        | xxxx         |

Legend:

This register has corresponding CLR, SET and INV registers at its virtual address, plus an offset of 0x4, 0x8 and 0xC, respectively. See Section 12.1.1 "CLR, SET and INV Registers" for more information. Reset value is dependent on DEVCFGx configuration. 1:

2:

Note

## PIC32MX5XX/6XX/7XX

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |  |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|--|--|

| 21.24        | R/W-0             | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |  |  |

| 31:24        | CHEWEN            | —                 | _                 | —                 | —                 | -                 | —                | —                |  |  |

| 22.46        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |  |  |

| 23:16        | -                 | —                 |                   | —                 | —                 |                   | —                | —                |  |  |

| 15:8         | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |  |  |

| 15.0         |                   | —                 |                   | —                 | —                 |                   | —                | —                |  |  |

| 7.0          | U-0               | U-0               | U-0               | U-0               | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |

| 7:0          |                   |                   |                   | —                 |                   | CHEID             | X<3:0>           |                  |  |  |

#### REGISTER 9-2: CHEACC: CACHE ACCESS REGISTER

#### Legend:

| R = Readable bit  | W = Writable bit | U = Unimplemented bit | , read as '0'      |  |

|-------------------|------------------|-----------------------|--------------------|--|

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared  | x = Bit is unknown |  |

#### bit 31 CHEWEN: Cache Access Enable bits

- These bits apply to registers CHETAG, CHEMSK, CHEW0, CHEW1, CHEW2, and CHEW3.

- 1 = The cache line selected by CHEIDX<3:0> is writeable

- 0 = The cache line selected by CHEIDX<3:0> is not writeable

- bit 30-4 **Unimplemented:** Write '0'; ignore read

#### bit 3-0 CHEIDX<3:0>: Cache Line Index bits

The value selects the cache line for reading or writing.

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |  |  |  |  |  |  |  |  |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|--|--|--|--|--|--|--|--|--|

| 31:24        | R/W-x             | R/W-x             | R/W-x             | R/W-x             | R/W-x             | R/W-x             | R/W-x            | R/W-x            |  |  |  |  |  |  |  |  |  |

| 31:24        | CHEW1<31:24>      |                   |                   |                   |                   |                   |                  |                  |  |  |  |  |  |  |  |  |  |

| 00.40        | R/W-x             | R/W-x             | R/W-x             | R/W-x             | R/W-x             | R/W-x             | R/W-x            | R/W-x            |  |  |  |  |  |  |  |  |  |

| 23:16        | CHEW1<23:16>      |                   |                   |                   |                   |                   |                  |                  |  |  |  |  |  |  |  |  |  |

| 45.0         | R/W-x             | R/W-x             | R/W-x             | R/W-x             | R/W-x             | R/W-x             | R/W-x            | R/W-x            |  |  |  |  |  |  |  |  |  |

| 15:8         | CHEW1<15:8>       |                   |                   |                   |                   |                   |                  |                  |  |  |  |  |  |  |  |  |  |

| 7.0          | R/W-x             | R/W-x             | R/W-x             | R/W-x             | R/W-x             | R/W-x             | R/W-x            | R/W-x            |  |  |  |  |  |  |  |  |  |

| 7:0          |                   | •                 | •                 | CHEW1             | <7:0>             |                   |                  | CHEW1<7:0>       |  |  |  |  |  |  |  |  |  |

#### REGISTER 9-6: CHEW1: CACHE WORD 1

| Legend:           |                  |                           |                    |

|-------------------|------------------|---------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, re | ead as '0'         |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared      | x = Bit is unknown |

bit 31-0 **CHEW1<31:0>:** Word 1 of the cache line selected by CHEIDX<3:0> bits (CHEACC<3:0>) Readable only if the device is not code-protected.

#### REGISTER 9-7: CHEW2: CACHE WORD 2

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |  |  |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|--|--|--|

| 31:24        | R/W-x             | R/W-x             | R/W-x             | R/W-x             | R/W-x             | R/W-x             | R/W-x            | R/W-x            |  |  |  |

| 31:24        | CHEW2<31:24>      |                   |                   |                   |                   |                   |                  |                  |  |  |  |

| 00:40        | R/W-x             | R/W-x             | R/W-x             | R/W-x             | R/W-x             | R/W-x             | R/W-x            | R/W-x            |  |  |  |

| 23:16        | CHEW2<23:16>      |                   |                   |                   |                   |                   |                  |                  |  |  |  |

| 45.0         | R/W-x             | R/W-x             | R/W-x             | R/W-x             | R/W-x             | R/W-x             | R/W-x            | R/W-x            |  |  |  |

| 15:8         | CHEW2<15:8>       |                   |                   |                   |                   |                   |                  |                  |  |  |  |

| 7.0          | R/W-x             | R/W-x             | R/W-x             | R/W-x             | R/W-x             | R/W-x             | R/W-x            | R/W-x            |  |  |  |

| 7:0          |                   |                   |                   | CHEW2             | <7:0>             |                   |                  |                  |  |  |  |

| Legend:           |                  |                          |                    |

|-------------------|------------------|--------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, r | ead as '0'         |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared     | x = Bit is unknown |

bit 31-0 **CHEW2<31:0>:** Word 2 of the cache line selected by CHEIDX<3:0> bits (CHEACC<3:0>) Readable only if the device is not code-protected.

## PIC32MX5XX/6XX/7XX

#### REGISTER 11-12: U1ADDR: USB ADDRESS REGISTER

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |  |  |  |  |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|--|--|--|--|--|

| 31:24        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |  |  |  |  |  |

| 51.24        | _                 | _                 | -                 |                   | _                 | -                 |                  | —                |  |  |  |  |  |

| 22:46        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |  |  |  |  |  |

| 23:16        |                   | -                 |                   |                   |                   |                   |                  | —                |  |  |  |  |  |

| 15:8         | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |  |  |  |  |  |

| 15.6         | —                 | _                 |                   |                   | _                 |                   |                  | —                |  |  |  |  |  |

| 7:0          | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |  |  |  |

| 7.0          | LSPDEN            | DEVADDR<6:0>      |                   |                   |                   |                   |                  |                  |  |  |  |  |  |

#### Legend:

| R = Readable bit  | W = Writable bit | U = Unimplemented bit | , read as '0'      |  |

|-------------------|------------------|-----------------------|--------------------|--|

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared  | x = Bit is unknown |  |

#### bit 31-8 Unimplemented: Read as '0'

- bit 7 **LSPDEN:** Low-Speed Enable Indicator bit

- 1 = Next token command to be executed at low-speed

- 0 = Next token command to be executed at full-speed

- bit 6-0 DEVADDR<6:0>: 7-bit USB Device Address bits

#### REGISTER 11-13: U1FRML: USB FRAME NUMBER LOW REGISTER

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|--|

| 24.24        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |  |

| 31:24        | -                 | -                 |                   | —                 |                   |                   |                  | -                |  |

| 23:16        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |  |

| 23.10        | -                 | -                 |                   | —                 |                   |                   |                  | -                |  |

| 15.0         | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |  |

| 15:8         | _                 | _                 | _                 | —                 | -                 | _                 |                  | _                |  |

| 7.0          | R-0               | R-0               | R-0               | R-0               | R-0               | R-0               | R-0              | R-0              |  |

| 7:0          | FRML<7:0>         |                   |                   |                   |                   |                   |                  |                  |  |

| Legend:           |                  |                          |                    |

|-------------------|------------------|--------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, r | read as '0'        |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared     | x = Bit is unknown |

#### bit 31-8 Unimplemented: Read as '0'

bit 7-0 **FRML<7:0>:** 11-bit Frame Number Lower bits The register bits are updated with the current frame number whenever a SOF TOKEN is received.

# TABLE 12-9: PORTF REGISTER MAP FOR PIC32MX534F064H, PIC32MX564F064H, PIC32MX564F128H, PIC32MX575F512H, PIC32MX664F064H, PIC32MX664F128H, PIC32MX675F256H, PIC32MX675F512H, PIC32MX695F512H, PIC32MX775F512H, PIC32MX775F512H, PIC32MX775F512H, PIC32MX795F512H, DEVICES

| ess                         |                                 | e         |       |       |       |       |       |       |      | Bi   | its  |      |        |        |        |      |        |        |            |

|-----------------------------|---------------------------------|-----------|-------|-------|-------|-------|-------|-------|------|------|------|------|--------|--------|--------|------|--------|--------|------------|

| Virtual Address<br>(BF88_#) | Register<br>Name <sup>(1)</sup> | Bit Range | 31/15 | 30/14 | 29/13 | 28/12 | 27/11 | 26/10 | 25/9 | 24/8 | 23/7 | 22/6 | 21/5   | 20/4   | 19/3   | 18/2 | 17/1   | 16/0   | All Resets |

| 6140                        | TRISF                           | 31:16     | _     | —     | _     | —     | -     | —     | _    | _    | _    | —    | _      | —      | —      | _    | -      | —      | 0000       |

| 6140                        | IRIOF                           | 15:0      |       | _     | _     | _     | _     | _     | _    | _    | _    | _    | TRISF5 | TRISF4 | TRISF3 | _    | TRISF1 | TRISF0 | 003B       |

| 6150                        | PORTF                           | 31:16     | _     | _     |       | _     |       | _     |      |      |      |      | -      | _      | _      | _    |        |        | 0000       |

| 6150                        | PURIF                           | 15:0      |       | -     | -     | —     | —     | —     | -    | -    | -    | -    | RF5    | RF4    | RF3    |      | RF1    | RF0    | xxxx       |

| 6160                        | LATF                            | 31:16     |       | _     | _     | _     | _     | _     | _    | _    | _    | _    | -      | _      | _      | _    | _      | _      | 0000       |

| 6160                        | LAIF                            | 15:0      | -     | _     | —     | _     | _     | _     | _    | _    | _    | _    | LATF5  | LATF4  | LATF3  | —    | LATF1  | LATF0  | xxxx       |

| 6170                        | ODCF                            | 31:16     |       | _     | _     | _     | _     | _     | _    | _    | _    | _    | -      | _      | _      | _    | _      | _      | 0000       |

| 0170                        | ODCF                            | 15:0      | _     | _     | _     |       | -     |       |      |      |      |      | ODCF5  | ODCF4  | ODCF3  |      | ODCF1  | ODCF0  | 0000       |

Legend: x = unknown value on Reset; - = unimplemented, read as '0'. Reset values are shown in hexadecimal.

Note 1: All registers in this table have corresponding CLR, SET and INV registers at their virtual addresses, plus offsets of 0x4, 0x8 and 0xC, respectively. See Section 12.1.1 "CLR, SET and INV Registers" for more information.

# TABLE 12-10: PORTF REGISTER MAP PIC32MX534F064L, PIC32MX564F064L, PIC32MX564F128L, PIC32MX575F256L, PIC32MX575F512L, PIC32MX664F064L, PIC32MX664F128L, PIC32MX675F256L, PIC32MX675F512L, PIC32MX775F512L, PIC32MX7

| ess                         |                                 | Ċ,        |       |       |         |         |       |       |      | Bi     | ts   |      |        |        |        |        |        |        | - y       |

|-----------------------------|---------------------------------|-----------|-------|-------|---------|---------|-------|-------|------|--------|------|------|--------|--------|--------|--------|--------|--------|-----------|

| Virtual Address<br>(BF88_#) | Register<br>Name <sup>(1)</sup> | Bit Range | 31/15 | 30/14 | 29/13   | 28/12   | 27/11 | 26/10 | 25/9 | 24/8   | 23/7 | 22/6 | 21/5   | 20/4   | 19/3   | 18/2   | 17/1   | 16/0   | All Reset |

|                             | TDIOF                           | 31:16     | _     | _     | _       | _       | _     | _     | _    | _      | _    | _    | _      | _      | _      | _      | _      | _      | 0000      |

| 6140                        | TRISF                           | 15:0      | _     | _     | TRISF13 | TRISF12 | _     | _     | _    | TRISF8 | _    | _    | TRISF5 | TRISF4 | TRISF3 | TRISF2 | TRISF1 | TRISF0 | 313F      |

| 6150                        | PORTF                           | 31:16     | -     | _     | _       | _       | _     | -     | _    | _      | -    |      | -      |        | _      |        | _      | _      | 0000      |

| 0150                        | FUNIF                           | 15:0      | -     | —     | RF13    | RF12    | _     |       | _    | RF8    |      |      | RF5    | RF4    | RF3    | RF2    | RF1    | RF0    | xxxx      |

| 6160                        | LATF                            | 31:16     | —     | —     | _       |         | —     | _     | _    |        | -    | _    | _      | _      | _      | _      | —      | —      | 0000      |

| 0100                        | LAIF                            | 15:0      |       | —     | LATF13  | LATF12  |       | -     |      | LATF8  |      | -    | LATF5  | LATF4  | LATF3  | LATF2  | LATF1  | LATF0  | xxxx      |

| 6170                        | ODCF                            | 31:16     | —     | _     | _       | —       | _     |       | _    |        |      |      | _      |        | —      |        | -      | -      | 0000      |

| 0170                        | ODCF                            | 15:0      | _     | _     | ODCF13  | ODCF12  | _     | -     | —    | ODCF8  | _    | -    | ODCF5  | ODCF4  | ODCF3  | ODCF2  | ODCF1  | ODCF0  | 0000      |

Legend: x = unknown value on Reset; — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

Note 1: All registers in this table have corresponding CLR, SET and INV registers at their virtual addresses, plus offsets of 0x4, 0x8 and 0xC, respectively. See Section 12.1.1 "CLR, SET and INV Registers" for more information.

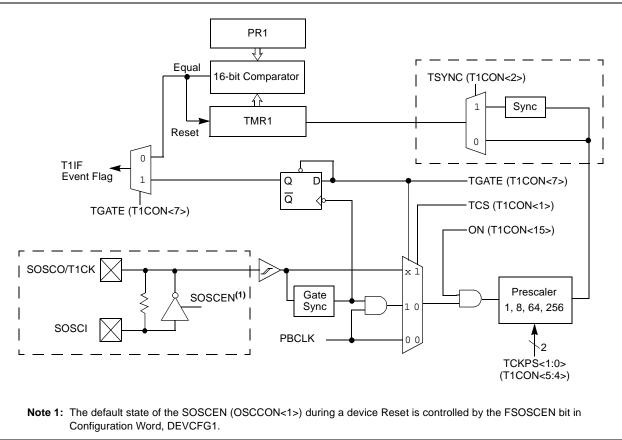

#### 13.0 TIMER1

Note: This data sheet summarizes the features of the PIC32MX5XX/6XX/7XX family of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to **Section 14. "Timers"** (DS60001105) in the *"PIC32 Family Reference Manual"*, which is available from the Microchip web site (www.microchip.com/PIC32).

This family of PIC32 devices features one synchronous/ asynchronous 16-bit timer that can operate as a free-running interval timer for various timing applications and counting external events. This timer can also be used with the low-power Secondary Oscillator (Sosc) for Real-Time Clock (RTC) applications. The following modes are supported:

- Synchronous Internal Timer

- Synchronous Internal Gated Timer

- Synchronous External Timer

- Asynchronous External Timer

#### FIGURE 13-1: TIMER1 BLOCK DIAGRAM

#### 13.1 Additional Supported Features

- Selectable clock prescaler

- Timer operation during Idle and Sleep mode

- Fast bit manipulation using CLR, SET and INV registers

- Asynchronous mode can be used with the Sosc to function as a Real-Time Clock (RTC)

A simplified block diagram of the Timer1 module is illustrated in Figure 13-1.

#### REGISTER 13-1: T1CON: TYPE A TIMER CONTROL REGISTER (CONTINUED)

- bit 3 Unimplemented: Read as '0'

bit 2 TSYNC: Timer External Clock Input Synchronization Selection bit When TCS = 1: 1 = External clock input is synchronized 0 = External clock input is not synchronized When TCS = 0: This bit is ignored.

bit 1 TCS: Timer Clock Source Select bit 1 = External clock from TxCKI pin 0 = Internal peripheral clock

- bit 0 Unimplemented: Read as '0'

- **Note 1:** When using the 1:1 PBCLK divisor, the user's software should not read/write the peripheral SFRs in the SYSCLK cycle immediately following the instruction that clears the module's ON bit.

#### 19.0 INTER-INTEGRATED CIRCUIT (I<sup>2</sup>C)

Note: This data sheet summarizes the features of the PIC32MX5XX/6XX/7XX family of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to Section 24. "Inter-Integrated Circuit (I<sup>2</sup>C)" (DS60001116) in the "*PIC32 Family Reference Manual*", which is available from the Microchip web site (www.microchip.com/PIC32). The  $l^2C$  module provides complete hardware support for both Slave and Multi-Master modes of the  $l^2C$  serial communication standard. Figure 19-1 illustrates the  $l^2C$  module block diagram.

Each  $I^2C$  module has a 2-pin interface: the SCLx pin is clock and the SDAx pin is data.

Each I<sup>2</sup>C module offers the following key features:

- I<sup>2</sup>C interface supporting both master and slave operation

- I<sup>2</sup>C Slave mode supports 7-bit and 10-bit addressing

- I<sup>2</sup>C Master mode supports 7-bit and 10-bit addressing

- I<sup>2</sup>C port allows bidirectional transfers between master and slaves

- Serial clock synchronization for the I<sup>2</sup>C port can be used as a handshake mechanism to suspend and resume serial transfer (SCLREL control)

- I<sup>2</sup>C supports multi-master operation; detects bus collision and arbitrates accordingly

- Provides support for address bit masking

#### 21.1 Control Registers

#### TABLE 21-1: PARALLEL MASTER PORT REGISTER MAP

|              |                                 |           |                                                                                                                                                 |           |       |       |         |        |        | Bi     | ts      |        |      |      |      |      |      |      |            |

|--------------|---------------------------------|-----------|-------------------------------------------------------------------------------------------------------------------------------------------------|-----------|-------|-------|---------|--------|--------|--------|---------|--------|------|------|------|------|------|------|------------|

| 7000 PMCON 3 | Register<br>Name <sup>(1)</sup> | Bit Range | 31/15                                                                                                                                           | 30/14     | 29/13 | 28/12 | 27/11   | 26/10  | 25/9   | 24/8   | 23/7    | 22/6   | 21/5 | 20/4 | 19/3 | 18/2 | 17/1 | 16/0 | All Resets |

| 7000 PM      |                                 | 31:16     | _                                                                                                                                               | _         | _     | _     | _       | _      | _      | _      |         | _      | _    | _    | —    | _    | —    | _    | 0000       |

| 7000 1 100   |                                 | 15:0      | ON                                                                                                                                              | —         | SIDL  | ADRMU | IX<1:0> | PMPTTL | PTWREN | PTRDEN | CSF     | <1:0>  | ALP  | CS2P | CS1P | —    | WRSP | RDSP | 0000       |

| 7010 PMM     | MODE                            | 31:16     | —                                                                                                                                               | —         | —     | —     | —       | —      | —      | —      | —       | —      | —    | —    | —    | —    | —    | —    | 0000       |

| 7010 Pivily  | NODE                            | 15:0      | 15:0         BUSY         IRQM<1:0>         INCM<1:0>         MODE16         MODE<1:0>         WAITB<1:0>         WAITM<3:0>         WAITE<1:0> |           |       |       |         |        | <1:0>  | 0000   |         |        |      |      |      |      |      |      |            |

| 7020 PMA     |                                 | 31:16     |                                                                                                                                                 | _         | _     | _     | _       | _      | _      |        | _       | -      | -    | _    | _    | _    | _    | _    | 0000       |

| 7020 PINA    | IADDR                           | 15:0      | CS2EN/A15                                                                                                                                       | CS1EN/A14 |       |       |         |        |        |        | ADDR    | <13:0> |      |      |      |      |      |      | 0000       |

| 7000 040     |                                 | 31:16     |                                                                                                                                                 |           |       |       |         |        |        | DATAOU | T 04.0  |        |      |      |      |      |      |      | 0000       |

| 7030 PMD     |                                 | 15:0      |                                                                                                                                                 |           |       |       |         |        |        | DATAOU | 1<31:0> |        |      |      |      |      |      |      | 0000       |

| 7040 DM      | MDIN                            | 31:16     |                                                                                                                                                 |           |       |       |         |        |        |        | .01.0   |        |      |      |      |      |      |      | 0000       |

| 7040 PM      |                                 | 15:0      |                                                                                                                                                 |           |       |       |         |        |        | DATAIN | <31:0>  |        |      |      |      |      |      |      | 0000       |

| 7050 014     | MAEN                            | 31:16     |                                                                                                                                                 | _         | _     | _     | _       | _      | _      |        | _       | -      | -    | _    | _    | _    | _    | _    | 0000       |

| 7050 PM/     | VIAEN                           | 15:0      |                                                                                                                                                 |           |       |       |         |        |        | PTEN<  | :15:0>  |        |      |      |      |      |      |      | 0000       |

| 7000 0140    | 10TAT                           | 31:16     | _                                                                                                                                               | _         | _     | _     | _       | _      | _      | _      | _       | _      | —    | _    | _    | _    | _    | _    | 0000       |

| 7060 PMS     | ISTAL                           | 15:0      | IBF                                                                                                                                             | IBOV      | _     | -     | IB3F    | IB2F   | IB1F   | IB0F   | OBE     | OBUF   | —    | -    | OB3E | OB2E | OB1E | OB0E | 008F       |

Legend: x = unknown value on Reset; — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

Note 1: All registers in this table have corresponding CLR, SET and INV registers at their virtual addresses, plus offsets of 0x4, 0x8 and 0xC, respectively. See Section 12.1.1 "CLR, SET and INV Registers" for more information.

| Bit<br>Range | Bit<br>31/23/15/7       | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3      | Bit<br>26/18/10/2 | Bit<br>25/17/9/1       | Bit<br>24/16/8/0 |  |  |  |  |  |

|--------------|-------------------------|-------------------|-------------------|-------------------|------------------------|-------------------|------------------------|------------------|--|--|--|--|--|

| 24.24        | U-0                     | U-0               | U-0               | U-0               | U-0                    | U-0               | R/W-0                  | R/W-0            |  |  |  |  |  |

| 31:24        | —                       | —                 | _                 | —                 | —                      | —                 | CAL<9                  | ):8>             |  |  |  |  |  |

| 23:16        | R/W-0                   | R/W-0             | R/W-0             | R/W-0             | R/W-0                  | R/W-0             | R/W-0                  | R/W-0            |  |  |  |  |  |

| 23.10        | CAL<7:0>                |                   |                   |                   |                        |                   |                        |                  |  |  |  |  |  |

| 15:8         | R/W-0                   | U-0               | R/W-0             | U-0               | U-0                    | U-0               | U-0                    | U-0              |  |  |  |  |  |

| 0.61         | ON <sup>(1,2)</sup>     |                   | SIDL              | —                 | —                      | -                 |                        | _                |  |  |  |  |  |

| 7.0          | R/W-0                   | R-0               | U-0               | U-0               | R/W-0                  | R-0               | R-0                    | R/W-0            |  |  |  |  |  |

| 7:0          | RTSECSEL <sup>(3)</sup> | RTCCLKON          | _                 | —                 | RTCWREN <sup>(4)</sup> | RTCSYNC           | HALFSEC <sup>(5)</sup> | RTCOE            |  |  |  |  |  |

|              |                         |                   |                   |                   |                        |                   |                        |                  |  |  |  |  |  |

#### REGISTER 22-1: RTCCON: RTC CONTROL REGISTER

#### Legend:

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, re | ad as '0'          |  |

|-------------------|------------------|---------------------------|--------------------|--|

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared      | x = Bit is unknown |  |

#### bit 31-26 Unimplemented: Read as '0'

bit 25-16 **CAL<9:0>:** RTC Drift Calibration bits, which contain a signed 10-bit integer value

| ~0 10    |                                                                                                          |

|----------|----------------------------------------------------------------------------------------------------------|

|          | 1111111111 = Minimum negative adjustment, subtracts 1 RTC clock pulse every one minute                   |

|          | •                                                                                                        |

|          | •                                                                                                        |

|          | •<br>1000000000 = Maximum negative adjustment, subtracts 512 clock pulses every one minute               |

|          | 0111111111 = Maximum positive adjustment, adds 511 RTC clock pulses every one minute                     |

|          | •                                                                                                        |

|          | •                                                                                                        |

|          | •                                                                                                        |

|          | 000000001 = Minimum positive adjustment, adds 1 RTC clock pulse every one minute                         |

|          | 000000000 = No adjustment                                                                                |

| bit 15   | ON: RTCC On bit <sup>(1,2)</sup>                                                                         |

|          | 1 = RTCC module is enabled                                                                               |

|          | 0 = RTCC module is disabled                                                                              |

| bit 14   | Unimplemented: Read as '0'                                                                               |

| bit 13   | SIDL: Stop in Idle Mode bit                                                                              |

|          | 1 = Disables the PBCLK to the RTCC when CPU enters in Idle mode                                          |

|          | 0 = Continue normal operation in Idle mode                                                               |

| bit 12-8 | Unimplemented: Read as '0'                                                                               |

| bit 7    | RTSECSEL: RTCC Seconds Clock Output Select bit <sup>(3)</sup>                                            |

|          | 1 = RTCC Seconds Clock is selected for the RTCC pin                                                      |

|          | 0 = RTCC Alarm Pulse is selected for the RTCC pin                                                        |

| bit 6    | RTCCLKON: RTCC Clock Enable Status bit                                                                   |

|          | 1 = RTCC Clock is actively running                                                                       |

|          | 0 = RTCC Clock is not running                                                                            |

| bit 5-4  | Unimplemented: Read as '0'                                                                               |

|          | •                                                                                                        |

| Note 1:  | The ON bit is only writable when RTCWREN = 1.                                                            |

| 2:       | When using the 1:1 PBCLK divisor, the user's software should not read/write the peripheral's SFRs in the |

|          | SYSCLK cycle immediately following the instruction that clears the module's ON bit.                      |

| 3:       | Requires $RTCOE = 1$ (RTCCON<0>) for the output to be active.                                            |

| 4:       | The RTCWREN bit can only be set when the write sequence is enabled.                                      |

| 5:       | This bit is read-only. It is cleared to '0' on a write to the seconds bit fields (RTCTIME<14:8>).        |

|          |                                                                                                          |

|          |                                                                                                          |

Note: This register is only reset on a Power-on Reset (POR).

© 2009-2016 Microchip Technology Inc.

#### REGISTER 24-20: CiFIFOCONn: CAN FIFO CONTROL REGISTER 'n' (n = 0 THROUGH 31)

- bit 6 TXABAT: Message Aborted bit<sup>(2)</sup> 1 = Message was aborted 0 = Message completed successfully bit 5 TXLARB: Message Lost Arbitration bit<sup>(3)</sup> 1 = Message lost arbitration while being sent 0 = Message did not lose arbitration while being sent TXERR: Error Detected During Transmission bit<sup>(3)</sup> bit 4 1 = A bus error occured while the message was being sent 0 = A bus error did not occur while the message was being sent bit 3 **TXREQ:** Message Send Request TXEN = 1: (FIFO configured as a Transmit FIFO) Setting this bit to '1' requests sending a message. The bit will automatically clear when all the messages queued in the FIFO are successfully sent. Clearing the bit to '0' while set ('1') will request a message abort. TXEN = 0: (FIFO configured as a receive FIFO) This bit has no effect. bit 2 RTREN: Auto RTR Enable bit 1 = When a remote transmit is received, TXREQ will be set 0 = When a remote transmit is received, TXREQ will be unaffected bit 1-0 TXPR<1:0>: Message Transmit Priority bits 11 = Highest message priority 10 = High intermediate message priority 01 = Low intermediate message priority 00 = Lowest message priority Note 1: These bits can only be modified when the CAN module is in Configuration mode (OPMOD<2:0> bits (CiCON<23:21>) = 100).

- 2: This bit is updated when a message completes (or aborts) or when the FIFO is reset.

- 3: This bit is reset on any read of this register or when the FIFO is reset.

#### REGISTER 25-14: ETHIRQ: ETHERNET CONTROLLER INTERRUPT REQUEST REGISTER

| bit 6 | PKTPEND: Packet Pending Interrupt bit                                                                                                                                                                                                               |

|-------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|       | 1 = RX packet pending in memory                                                                                                                                                                                                                     |

|       | 0 = RX packet is not pending in memory                                                                                                                                                                                                              |

|       | This bit is set when the BUFCNT counter has a value other than '0'. It is cleared by either a Reset or by writing the BUFCDEC bit to decrement the BUFCNT counter. Writing a '0' or a '1' has no effect.                                            |

| bit 5 | RXACT: Receive Activity Interrupt bit                                                                                                                                                                                                               |

|       | <ul><li>1 = RX packet data was successfully received</li><li>0 = No interrupt pending</li></ul>                                                                                                                                                     |

|       | This bit is set whenever RX packet data is stored in the RXBM FIFO. It is cleared by either a Reset or CPU write of a '1' to the CLR register.                                                                                                      |

| bit 4 | Unimplemented: Read as '0'                                                                                                                                                                                                                          |

| bit 3 | TXDONE: Transmit Done Interrupt bit                                                                                                                                                                                                                 |

|       | <ul><li>1 = TX packet was successfully sent</li><li>0 = No interrupt pending</li></ul>                                                                                                                                                              |

|       | This bit is set when the currently transmitted TX packet completes transmission, and the Transmit Status Vector is loaded into the first descriptor used for the packet. It is cleared by either a Reset or CPU write of a '1' to the CLR register. |

| bit 2 | TXABORT: Transmit Abort Condition Interrupt bit                                                                                                                                                                                                     |

|       | <ul><li>1 = TX abort condition occurred on the last TX packet</li><li>0 = No interrupt pending</li></ul>                                                                                                                                            |

|       | This bit is set when the MAC aborts the transmission of a TX packet for one of the following reasons:                                                                                                                                               |

|       | Jumbo TX packet abort                                                                                                                                                                                                                               |

|       | Underrun abort                                                                                                                                                                                                                                      |

|       | Excessive defer abort                                                                                                                                                                                                                               |

|       | Late collision abort                                                                                                                                                                                                                                |

|       | Excessive collisions abort                                                                                                                                                                                                                          |

|       | This bit is cleared by either a Reset or CPU write of a '1' to the CLR register.                                                                                                                                                                    |

| bit 1 | RXBUFNA: Receive Buffer Not Available Interrupt bit                                                                                                                                                                                                 |

|       | <ul> <li>1 = RX Buffer Descriptor Not Available condition has occurred</li> <li>0 = No interrupt pending</li> </ul>                                                                                                                                 |

|       | This bit is set by a RX Buffer Descriptor Overrun condition. It is cleared by either a Reset or a CPU write of a '1' to the CLR register.                                                                                                           |

| bit 0 | RXOVFLW: Receive FIFO Over Flow Error bit                                                                                                                                                                                                           |

|       | <ul><li>1 = RX FIFO Overflow Error condition has occurred</li><li>0 = No interrupt pending</li></ul>                                                                                                                                                |

|       | RXOVFLW is set by the RXBM Logic for an RX FIFO Overflow condition. It is cleared by either a Reset or CPU write of a '1' to the CLR register.                                                                                                      |

|       |                                                                                                                                                                                                                                                     |

**Note:** It is recommended to use the SET, CLR, or INV registers to set or clear any bit in this register. Setting or clearing any bits in this register should only be done for debug/test purposes.

| Bit<br>Range | Bit<br>31/23/15/7      | Bit<br>30/22/14/6     | Bit<br>29/21/13/5     | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |  |  |  |

|--------------|------------------------|-----------------------|-----------------------|-------------------|-------------------|-------------------|------------------|------------------|--|--|--|--|

| 31:24        | U-0                    | U-0                   | U-0                   | U-0               | U-0               | U-0               | U-0              | U-0              |  |  |  |  |

| 31.24        | —                      |                       | _                     | _                 | _                 | _                 | _                | _                |  |  |  |  |

| 23:16        | R/W-0                  | R/W-0                 | R/W-0                 | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |  |  |

| 23.10        | BUFCNT<7:0>            |                       |                       |                   |                   |                   |                  |                  |  |  |  |  |

| 15:8         | U-0                    | U-0                   | U-0                   | U-0               | U-0               | U-0               | U-0              | U-0              |  |  |  |  |

| 15.0         | —                      |                       | _                     | _                 | _                 | _                 | _                | _                |  |  |  |  |

| 7.0          | R/W-0                  | R/W-0                 | R/W-0                 | U-0               | U-0               | U-0               | U-0              | U-0              |  |  |  |  |

| 7:0          | ETHBUSY <sup>(1)</sup> | TXBUSY <sup>(2)</sup> | RXBUSY <sup>(2)</sup> | —                 |                   | _                 |                  | _                |  |  |  |  |

#### REGISTER 25-15: ETHSTAT: ETHERNET CONTROLLER STATUS REGISTER

### Legend:

| Legena.           |                  |                       |                    |

|-------------------|------------------|-----------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit | , read as '0'      |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared  | x = Bit is unknown |

#### bit 31-24 Unimplemented: Read as '0'

#### bit 23-16 **BUFCNT<7:0>:** Packet Buffer Count bits

Number of packet buffers received in memory. Once a packet has been successfully received, this register is incremented by hardware based on the number of descriptors used by the packet. Software decrements the counter (by writing to the BUFCDEC bit (ETHCON1<0>) for each descriptor used) after a packet has been read out of the buffer. The register does not roll over (0xFF to 0x00) when hardware tries to increment the register and the register is already at 0xFF. Conversely, the register does not roll under (0x00 to 0xFF) when software tries to decrement the register and the register is already at 0x000. When software attempts to decrement the same time that the hardware attempts to increment the counter, the counter value will remain unchanged.

When this register value reaches 0xFF, the RX logic will halt (only if automatic Flow Control is enabled) awaiting software to write the BUFCDEC bit in order to decrement the register below 0xFF.

If automatic Flow Control is disabled, the RXDMA will continue processing and the BUFCNT will saturate at a value of 0xFF.

When this register is non-zero, the PKTPEND status bit will be set and an interrupt may be generated, depending on the value of the ETHIEN bit <PKTPENDIE> register.

When the ETHRXST register is written, the BUFCNT counter is automatically cleared to 0x00.

- **Note:** BUFCNT will not be cleared when ON is set to '0'. This enables software to continue to utilize and decrement this count.

- bit 15-8 **Unimplemented:** Read as '0'

- bit 7 ETHBUSY: Ethernet Module busy bit<sup>(1)</sup>

1 = Ethernet logic has been turned on (ON (ETHCON1<15>) = 1) or is completing a transaction 0 = Ethernet logic is idle

This bit indicates that the module has been turned on or is completing a transaction after being turned off.

- bit 6 **TXBUSY:** Transmit Busy bit<sup>(2)</sup>

- 1 = TX logic is receiving data

- 0 = TX logic is idle

This bit indicates that a packet is currently being transmitted. A change in this status bit is not necessarily reflected by the TXDONE interrupt, as TX packets may be aborted or rejected by the MAC.

- **Note 1:** This bit will be *set* when the ON bit (ETHCON1<15>) = 1.

- **2:** This bit will be *cleared* when the ON bit (ETHCON1<15>) = 0.

#### TABLE 32-5: DC CHARACTERISTICS: OPERATING CURRENT (IDD) (CONTINUED)

| DC CHARACTERISTICS |                        |                          | $\begin{tabular}{lllllllllllllllllllllllllllllllllll$ |                              |                           |                           |                           |

|--------------------|------------------------|--------------------------|-------------------------------------------------------|------------------------------|---------------------------|---------------------------|---------------------------|

| Param.<br>No.      | Typical <sup>(3)</sup> | Max.                     | Units Conditions                                      |                              |                           |                           |                           |