Welcome to E-XFL.COM

### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

### Details

E·XFI

| Product Status             | Active                                                                          |

|----------------------------|---------------------------------------------------------------------------------|

| Core Processor             | MIPS32® M4K™                                                                    |

| Core Size                  | 32-Bit Single-Core                                                              |

| Speed                      | 80MHz                                                                           |

| Connectivity               | Ethernet, I <sup>2</sup> C, SPI, UART/USART, USB OTG                            |

| Peripherals                | Brown-out Detect/Reset, DMA, POR, PWM, WDT                                      |

| Number of I/O              | 85                                                                              |

| Program Memory Size        | 128KB (128K x 8)                                                                |

| Program Memory Type        | FLASH                                                                           |

| EEPROM Size                |                                                                                 |

| RAM Size                   | 32K x 8                                                                         |

| Voltage - Supply (Vcc/Vdd) | 2.3V ~ 3.6V                                                                     |

| Data Converters            | A/D 16x10b                                                                      |

| Oscillator Type            | Internal                                                                        |

| Operating Temperature      | -40°C ~ 105°C (TA)                                                              |

| Mounting Type              | Surface Mount                                                                   |

| Package / Case             | 100-TQFP                                                                        |

| Supplier Device Package    | 100-TQFP (12x12)                                                                |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic32mx664f128lt-v-pt |

|                            |                                                                                 |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

## **Referenced Sources**

This device data sheet is based on the following individual chapters of the *"PIC32 Family Reference Manual"*. These documents should be considered as the general reference for the operation of a particular module or device feature.

- Note 1: To access the documents listed below, browse to the documentation section of the PIC32MX795F512L product page on the Microchip web site (www.microchip.com) or select a family reference manual section from the following list. In addition to parameters, features, and other documentation, the resulting page provides links to the related family

- Section 1. "Introduction" (DS60001127)

- Section 2. "CPU" (DS60001113)

- Section 4. "Prefetch Cache" (DS60001119)

- Section 3. "Memory Organization" (DS60001115)

reference manual sections.

- Section 5. "Flash Program Memory" (DS60001121)

- Section 6. "Oscillator Configuration" (DS60001112)

- Section 7. "Resets" (DS60001118)

- Section 8. "Interrupt Controller" (DS60001108)

- Section 9. "Watchdog Timer and Power-up Timer (DS60001114)

- Section 10. "Power-Saving Features" (DS60001130)

- Section 12. "I/O Ports" (DS60001120)

- Section 13. "Parallel Master Port (PMP)" (DS60001128)

- Section 14. "Timers" (DS60001105)

- Section 15. "Input Capture" (DS60001122)

- Section 16. "Output Capture" (DS60001111)

- Section 17. "10-bit Analog-to-Digital Converter (ADC)" (DS60001104)

- Section 19. "Comparator" (DS60001110)

- Section 20. "Comparator Voltage Reference (CVREF)" (DS60001109)

- Section 21. "Universal Asynchronous Receiver Transmitter (UART)" (DS60001107)

- Section 23. "Serial Peripheral Interface (SPI)" (DS60001106)

- Section 24. "Inter-Integrated Circuit (I2C)" (DS60001116)

- Section 27. "USB On-The-Go (OTG)" (DS60001126)

- Section 29. "Real-Time Clock and Calendar (RTCC)" (DS60001125)

- Section 31. "Direct Memory Access (DMA) Controller" (DS60001117)

- Section 32. "Configuration" (DS60001124)

- Section 33. "Programming and Diagnostics" (DS60001129)

- Section 34. "Controller Area Network (CAN)" (DS60001154)

- Section 35. "Ethernet Controller" (DS60001155)

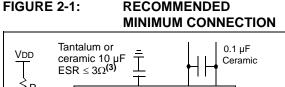

# Note 1: If the USB module is not used, this pin must be connected to VDD.

2: As an option, instead of a hard-wired connection, an inductor (L1) can be substituted between VDD and AVDD to improve ADC noise rejection. The inductor impedance should be less than  $3\Omega$  and the inductor capacity greater than 10 mA.

Where:

$$f = \frac{F_{CNV}}{2}$$

(i.e., ADC conversion rate/2)

$$f = \frac{1}{(2\pi\sqrt{LC})}$$

$$L = \left(\frac{1}{(2\pi f\sqrt{C})}\right)^2$$

3: Aluminum or electrolytic capacitors should not be used. ESR  $\leq 3\Omega$  from -40°C to 125°C @ SYSCLK frequency (i.e., MIPS).

# 2.2.1 BULK CAPACITORS

The use of a bulk capacitor is recommended to improve power supply stability. Typical values range from 4.7  $\mu F$  to 47  $\mu F$ . This capacitor should be located as close to the device as possible.

# 2.3 Capacitor on Internal Voltage Regulator (VCAP)

## 2.3.1 INTERNAL REGULATOR MODE

A low-ESR (1 ohm) capacitor is required on the VCAP pin, which is used to stabilize the internal voltage regulator output. The VCAP pin must not be connected to VDD, and must have a CEFC capacitor, with at least a 6V rating, connected to ground. The type can be ceramic or tantalum. Refer to **Section 32.0 "Electrical Characteristics"** for additional information on CEFC specifications.

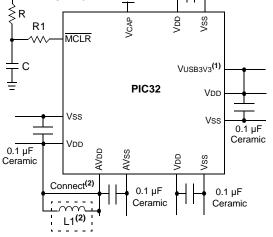

# 2.4 Master Clear (MCLR) Pin

The MCLR pin provides two specific device functions:

- Device Reset

- Device Programming and Debugging

Pulling The MCLR pin low generates a device Reset. Figure 2-2 illustrates a typical MCLR circuit. During device programming and debugging, the resistance and capacitance that can be added to the pin must be considered. Device programmers and debuggers drive the MCLR pin. Consequently, specific voltage levels (VIH and VIL) and fast signal transitions must not be adversely affected. Therefore, specific values of R and C will need to be adjusted based on the application and PCB requirements.

For example, as illustrated in Figure 2-2, it is recommended that the capacitor C, be isolated from the MCLR pin during programming and debugging operations.

Place the components illustrated in Figure 2-2 within one-quarter inch (6 mm) from the MCLR pin.

## FIGURE 2-2: EXAMPLE OF MCLR PIN CONNECTIONS

MCLR from the external capacitor C, in the event of MCLR pin breakdown, due to Electrostatic Discharge (ESD) or Electrical Overstress (EOS). Ensure that the MCLR pin VIH and VIL specifications are met without interfering with the Debug/Programmer tools.

- 2: The capacitor can be sized to prevent unintentional Resets from brief glitches or to extend the device Reset period during POR.

- **3:** No pull-ups or bypass capacitors are allowed on active debug/program PGECx/PGEDx pins.

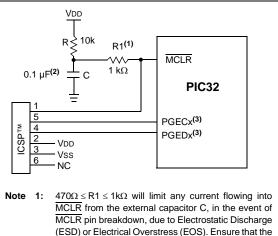

# 2.5 ICSP Pins

The PGECx and PGEDx pins are used for In-Circuit Serial Programming<sup>TM</sup> (ICSP<sup>TM</sup>) and debugging. It is recommended to keep the trace length between the ICSP connector and the ICSP pins on the device as short as possible. If the ICSP connector is expected to experience an ESD event, a series resistor is recommended, with the value in the range of a few tens of Ohms, not to exceed 100 Ohms.

Pull-up resistors, series diodes and capacitors on the PGECx and PGEDx pins are not recommended as they will interfere with the programmer/debugger communications to the device. If such discrete components are an application requirement, they should be removed from the circuit during programming and debugging. Alternatively, refer to the AC/DC characteristics and timing requirements information in the respective device Flash programming specification for information on capacitive loading limits and pin input voltage high (VIH) and input low (VIL) requirements.

Ensure that the "Communication Channel Select" (i.e., PGECx/PGEDx pins) programmed into the device matches the physical connections for the ICSP to MPLAB<sup>®</sup> ICD 3 or MPLAB<sup>®</sup> REAL ICE<sup>TM</sup>.

For more information on ICD 3 and REAL ICE connection requirements, refer to the following documents that are available on the Microchip web site.

- "Using MPLAB<sup>®</sup> ICD 3" (poster) (DS50001765)

- "MPLAB<sup>®</sup> ICD 3 Design Advisory" (DS50001764)

- "MPLAB<sup>®</sup> REAL ICE<sup>™</sup> In-Circuit Emulator User's Guide" (DS50001616)

- "Using MPLAB<sup>®</sup> REAL ICE™ Emulator" (poster) (DS50001749)

# 2.6 JTAG

The TMS, TDO, TDI and TCK pins are used for testing and debugging according to the Joint Test Action Group (JTAG) standard. It is recommended to keep the trace length between the JTAG connector and the JTAG pins on the device as short as possible. If the JTAG connector is expected to experience an ESD event, a series resistor is recommended, with the value in the range of a few tens of Ohms, not to exceed 100 Ohms.

Pull-up resistors, series diodes and capacitors on the TMS, TDO, TDI and TCK pins are not recommended as they will interfere with the programmer/debugger communications to the device. If such discrete components are an application requirement, they should be removed from the circuit during programming and debugging. Alternatively, refer to the AC/DC characteristics and timing requirements information in the respective device Flash programming specification for information on capacitive loading limits and pin input voltage high (VIH) and input low (VIL) requirements.

# 2.7 Trace

The trace pins can be connected to a hardware-traceenabled programmer to provide a compress real time instruction trace. When used for trace the TRD3, TRD2, TRD1, TRD0 and TRCLK pins should be dedicated for this use. The trace hardware requires a  $22\Omega$  series resistor between the trace pins and the trace connector.

# 2.8 External Oscillator Pins

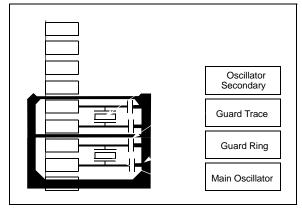

Many MCUs have options for at least two oscillators: a high-frequency primary oscillator and a low-frequency secondary oscillator. Refer to **Section 8.0 "Oscillator Configuration"** for details.

The oscillator circuit should be placed on the same side of the board as the device. Also, place the oscillator circuit close to the respective oscillator pins, not exceeding one-half inch (12 mm) distance between them. The load capacitors should be placed next to the oscillator itself, on the same side of the board. Use a grounded copper pour around the oscillator circuit to isolate them from surrounding circuits. The grounded copper pour should be routed directly to the MCU ground. Do not run any signal traces or power traces inside the ground pour. Also, if using a two-sided board, avoid any traces on the other side of the board where the crystal is placed. A suggested layout is illustrated in Figure 2-3.

### FIGURE 2-3: SUGGESTED OSCILLATOR CIRCUIT PLACEMENT

# 3.2 Architecture Overview

The MIPS32 M4K processor core contains several logic blocks working together in parallel, providing an efficient high-performance computing engine. The following blocks are included with the core:

- Execution Unit

- Multiply/Divide Unit (MDU)

- System Control Coprocessor (CP0)

- Fixed Mapping Translation (FMT)

- Dual Internal Bus interfaces

- Power Management

- MIPS16e<sup>®</sup> Support

- Enhanced JTAG (EJTAG) Controller

## 3.2.1 EXECUTION UNIT

The MIPS32 M4K processor core execution unit implements a load/store architecture with single-cycle ALU operations (logical, shift, add, subtract) and an autonomous multiply/divide unit. The core contains thirty-two 32-bit General Purpose Registers (GPRs) used for integer operations and address calculation. One additional register file shadow set (containing thirty-two registers) is added to minimize context switching overhead during interrupt/exception processing. The register file consists of two read ports and one write port and is fully bypassed to minimize operation latency in the pipeline.

The execution unit includes:

- 32-bit adder used for calculating the data address

- Address unit for calculating the next instruction address

- Logic for branch determination and branch target address calculation

- · Load aligner

- Bypass multiplexers used to avoid stalls when executing instruction streams where data producing instructions are followed closely by consumers of their results

- Leading Zero/One detect unit for implementing the CLZ and CLO instructions

- Arithmetic Logic Unit (ALU) for performing bit-wise logical operations

- Shifter and store aligner

## 3.2.2 MULTIPLY/DIVIDE UNIT (MDU)

MIPS32 M4K processor core includes a Multiply/Divide Unit (MDU) that contains a separate pipeline for multiply and divide operations. This pipeline operates in parallel with the Integer Unit (IU) pipeline and does not stall when the IU pipeline stalls. This allows MDU operations to be partially masked by system stalls and/or other integer unit instructions.

The high-performance MDU consists of a 32x16 booth recoded multiplier, result/accumulation registers (HI and LO), a divide state machine, and the necessary multiplexers and control logic. The first number shown ('32' of 32x16) represents the *rs* operand. The second number ('16' of 32x16) represents the *rt* operand. The PIC32 core only checks the value of the latter (*rt*) operand to determine how many times the operation must pass through the multiplier. The 16x16 and 32x16 operations pass through the multiplier once. A 32x32 operation passes through the multiplier twice.

The MDU supports execution of one 16x16 or 32x16 multiply operation every clock cycle; 32x32 multiply operations can be issued every other clock cycle. Appropriate interlocks are implemented to stall the issuance of back-to-back 32x32 multiply operations. The multiply operand size is automatically determined by logic built into the MDU.

Divide operations are implemented with a simple 1 bit per clock iterative algorithm. An early-in detection checks the sign extension of the dividend (*rs*) operand. If *rs* is 8 bits wide, 23 iterations are skipped. For a 16 bit wide *rs*, 15 iterations are skipped and for a 24 bit wide *rs*, 7 iterations are skipped. Any attempt to issue a subsequent MDU instruction while a divide is still active causes an IU pipeline stall until the divide operation is completed.

Table 3-1 lists the repeat rate (peak issue rate of cycles until the operation can be reissued) and latency (number of cycles until a result is available) for the PIC32 core multiply and divide instructions. The approximate latency and repeat rates are listed in terms of pipeline clocks.

| Opcode                  | Operand Size (mul rt) (div rs) | Latency | Repeat Rate |  |  |  |  |  |  |

|-------------------------|--------------------------------|---------|-------------|--|--|--|--|--|--|

| MULT/MULTU, MADD/MADDU, | 16 bits                        | 1       | 1           |  |  |  |  |  |  |

| MSUB/MSUBU              | 32 bits                        | 2       | 2           |  |  |  |  |  |  |

| MUL                     | 16 bits                        | 2       | 1           |  |  |  |  |  |  |

|                         | 32 bits                        | 3       | 2           |  |  |  |  |  |  |

| DIV/DIVU                | 8 bits                         | 12      | 11          |  |  |  |  |  |  |

|                         | 16 bits                        | 19      | 18          |  |  |  |  |  |  |

|                         | 24 bits                        | 26      | 25          |  |  |  |  |  |  |

|                         | 32 bits                        | 33      | 32          |  |  |  |  |  |  |

# TABLE 3-1:MIPS32<sup>®</sup> M4K<sup>®</sup> CORE HIGH-PERFORMANCE INTEGER MULTIPLY/DIVIDE UNIT<br/>LATENCIES AND REPEAT RATES

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |  |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|--|--|

| 04.04        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |  |  |

| 31:24        | _                 | _                 | _                 | —                 | _                 | —                 | —                | —                |  |  |

| 00.40        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |  |  |

| 23:16        | —                 | —                 | —                 | —                 | —                 | —                 | —                | —                |  |  |

| 45.0         | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R-0              | R-0              |  |  |

| 15:8         |                   | BMXDUDBA<15:8>    |                   |                   |                   |                   |                  |                  |  |  |

| 7.0          | R-0               | R-0               | R-0               | R-0               | R-0               | R-0               | R-0              | R-0              |  |  |

| 7:0          |                   |                   |                   | BMXDU             | DBA<7:0>          |                   |                  |                  |  |  |

### REGISTER 4-3: BMXDUDBA: DATA RAM USER DATA BASE ADDRESS REGISTER

# Legend:

| Legena:           |                  |                           |                    |

|-------------------|------------------|---------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, re | ad as '0'          |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared      | x = Bit is unknown |

bit 31-16 Unimplemented: Read as '0'

## bit 15-10 BMXDUDBA<15:10>: DRM User Data Base Address bits

When non-zero, the value selects the relative base address for User mode data space in RAM, the value must be greater than BMXDKPBA.

bit 9-0 BMXDUDBA<9:0>: DRM User Data Base Address Read-Only bits Value is always '0', which forces 1 KB increments

**Note 1:** At Reset, the value in this register is forced to zero, which causes all of the RAM to be allocated to Kernal mode data usage.

2: The value in this register must be less than or equal to BMXDRMSZ.

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0     |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|----------------------|

| 24.24        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0                  |

| 31:24        | —                 | _                 | _                 | —                 | _                 | _                 | -                | —                    |

| 22.16        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0                  |

| 23:16        | -                 | _                 | _                 | —                 | _                 | _                 | _                | —                    |

| 45.0         | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0                  |

| 15:8         | _                 | _                 | _                 | —                 | _                 | _                 | _                | —                    |

| 7.0          | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | W-0, HC              |

| 7:0          |                   | _                 | _                 | —                 | —                 |                   |                  | SWRST <sup>(1)</sup> |

## REGISTER 6-2: RSWRST: SOFTWARE RESET REGISTER

| Le   | gend:          | HC = Cleared by hardware |                                    |                    |  |  |

|------|----------------|--------------------------|------------------------------------|--------------------|--|--|

| R =  | = Readable bit | W = Writable bit         | U = Unimplemented bit, read as '0' |                    |  |  |

| -n : | = Value at POR | '1' = Bit is set         | '0' = Bit is cleared               | x = Bit is unknown |  |  |

bit 31-1 Unimplemented: Read as '0'

- bit 0 SWRST: Software Reset Trigger bit<sup>(1)</sup> 1 = Enable software Reset event 0 = No effect

- Note 1: The system unlock sequence must be performed before the SWRST bit can be written. Refer to Section 6. "Oscillator" (DS60001112) in the "PIC32 Family Reference Manual" for details.

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|

| 24.24        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 31:24        |                   |                   | _                 | —                 | -                 | _                 | _                | _                |

| 23:16        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | R/W-0            |

| 23.10        | —                 | —                 | —                 | —                 | _                 | —                 | —                | SS0              |

| 45.0         | U-0               | U-0               | U-0               | R/W-0             | U-0               | R/W-0             | R/W-0            | R/W-0            |

| 15:8         | _                 | —                 | —                 | MVEC              | _                 |                   | TPC<2:0>         |                  |

| 7.0          | U-0               | U-0               | U-0               | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |

| 7:0          |                   | _                 | _                 | INT4EP            | INT3EP            | INT2EP            | INT1EP           | INT0EP           |

### REGISTER 7-1: INTCON: INTERRUPT CONTROL REGISTER

### Legend:

| R = Readable bit W = Writable bit |                  | U = Unimplemented bit, read as '0' |                    |  |

|-----------------------------------|------------------|------------------------------------|--------------------|--|

| -n = Value at POR                 | '1' = Bit is set | '0' = Bit is cleared               | x = Bit is unknown |  |

### bit 31-17 Unimplemented: Read as '0'

- bit 16 **SS0:** Single Vector Shadow Register Set bit

- 1 = Single vector is presented with a shadow register set

- 0 = Single vector is not presented with a shadow register set

- bit 15-13 Unimplemented: Read as '0'

- bit 12 MVEC: Multiple Vector Configuration bit

- 1 = Interrupt controller configured for Multi-vector mode

- 0 = Interrupt controller configured for Single-vector mode

- bit 11 Unimplemented: Read as '0'

- bit 10-8 TPC<2:0>: Interrupt Proximity Timer Control bits

- 111 = Interrupts of group priority 7 or lower start the Interrupt Proximity timer 110 = Interrupts of group priority 6 or lower start the Interrupt Proximity timer 101 = Interrupts of group priority 5 or lower start the Interrupt Proximity timer 100 = Interrupts of group priority 4 or lower start the Interrupt Proximity timer 011 = Interrupts of group priority 3 or lower start the Interrupt Proximity timer

- 010 = Interrupts of group priority 2 or lower start the Interrupt Proximity timer

- 001 = Interrupts of group priority 1 start the Interrupt Proximity timer

- 000 = Disables Interrupt Proximity timer

- bit 7-5 Unimplemented: Read as '0'

- bit 4 INT4EP: External Interrupt 4 Edge Polarity Control bit

- 1 = Rising edge

- 0 = Falling edge

- bit 3 INT3EP: External Interrupt 3 Edge Polarity Control bit

- 1 = Rising edge

- 0 = Falling edge

- bit 2 INT2EP: External Interrupt 2 Edge Polarity Control bit

- 1 = Rising edge

- 0 = Falling edge

- bit 1 **INT1EP:** External Interrupt 1 Edge Polarity Control bit

- 1 = Rising edge

- 0 = Falling edge

- bit 0 INTOEP: External Interrupt 0 Edge Polarity Control bit

- 1 = Rising edge

- 0 = Falling edge

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5       | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1         | Bit<br>24/16/8/0 |  |

|--------------|-------------------|-------------------|-------------------------|-------------------|-------------------|-------------------|--------------------------|------------------|--|

| 31:24        | U-0               | U-0               | U-0                     | U-0               | U-0               | U-0               | U-0                      | U-0              |  |

| 31.24        |                   | _                 |                         |                   | _                 |                   | _                        |                  |  |

| 23:16        | U-0               | U-0               | U-0                     | U-0               | U-0               | U-0               | U-0                      | U-0              |  |

| 23.10        |                   | _                 | _                       | —                 | -                 | _                 | —                        | _                |  |

| 45.0         | U-0               | U-0               | U-0                     | U-0               | U-0               | R/W-0             | R/W-0                    | R/W-0            |  |

| 15:8         | —                 | —                 | —                       | —                 | _                 |                   | RIPL<2:0> <sup>(1)</sup> |                  |  |

| 7.0          | U-0               | U-0               | R/W-0                   | R/W-0             | R/W-0             | R/W-0             | R/W-0                    | R/W-0            |  |

| 7:0          |                   | —                 | VEC<5:0> <sup>(1)</sup> |                   |                   |                   |                          |                  |  |

### REGISTER 7-2: INTSTAT: INTERRUPT STATUS REGISTER

# Legend:

| Legena.           |                  |                           |                    |

|-------------------|------------------|---------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, re | ead as '0'         |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared      | x = Bit is unknown |

bit 31-11 Unimplemented: Read as '0'

- bit 10-8 **RIPL<2:0>:** Requested Priority Level bits<sup>(1)</sup> 111-000 = The priority level of the latest interrupt presented to the CPU

- bit 7-6 Unimplemented: Read as '0'

- bit 5-0 VEC<5:0>: Interrupt Vector bits<sup>(1)</sup> 11111-00000 = The interrupt vector that is presented to the CPU

- **Note 1:** This value should only be used when the interrupt controller is configured for Single-vector mode.

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |  |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|--|--|

|              | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |

| 31:24        |                   |                   |                   | TPTM              | R<31:24>          |                   |                  |                  |  |  |

| 22.46        | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |

| 23:16        | TPTMR<23:16>      |                   |                   |                   |                   |                   |                  |                  |  |  |

| 15.0         | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |

| 15:8         | TPTMR<15:8>       |                   |                   |                   |                   |                   |                  |                  |  |  |

| 7:0          | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |

|              |                   |                   |                   | TPTM              | 1R<7:0>           |                   |                  | •                |  |  |

### REGISTER 7-3: TPTMR: TEMPORAL PROXIMITY TIMER REGISTER

| Legend:                                                              |                  |                      |                    |  |

|----------------------------------------------------------------------|------------------|----------------------|--------------------|--|

| R = Readable bit W = Writable bit U = Unimplemented bit, read as '0' |                  |                      |                    |  |

| -n = Value at POR                                                    | '1' = Bit is set | '0' = Bit is cleared | x = Bit is unknown |  |

bit 31-0 TPTMR<31:0>: Temporal Proximity Timer Reload bits

Used by the Temporal Proximity Timer as a reload value when the Temporal Proximity timer is triggered by an interrupt event.

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |  |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|--|--|

| 04.04        | U-0               | U-0               | R/W-y             | R/W-y             | R/W-y             | R/W-0 R/W-0       |                  | R/W-1            |  |  |

| 31:24        | —                 | —                 | Р                 | LLODIV<2:0:       | > FRCDIV<2:0>     |                   |                  |                  |  |  |

| 00.40        | U-0 R-0           |                   | R-1               | R/W-y             | R/W-y             | R/W-y             | R/W-y            | R/W-y            |  |  |

| 23:16        | —                 | SOSCRDY           | PBDIVRDY          | PBDIV             | /<1:0>            | PLLMULT<2:0>      |                  |                  |  |  |

| 45.0         | U-0               | R-0               | R-0               | R-0               | U-0               | R/W-y             | R/W-y            | R/W-y            |  |  |

| 15:8         | —                 |                   | COSC<2:0>         |                   | —                 |                   | NOSC<2:0>        |                  |  |  |

| 7.0          | R/W-0             | R-0               | R-0               | R/W-0             | R/W-0             | R/W-0             | R/W-y            | R/W-0            |  |  |

| 7:0          | CLKLOCK           | ULOCK             | SLOCK             | SLPEN             | CF                | UFRCEN            | SOSCEN           | OSWEN            |  |  |

### REGISTER 8-1: OSCCON: OSCILLATOR CONTROL REGISTER

Legend:

y = Value set from Configuration bits on POR

- R = Readable bit -n = Value at POR

- W = Writable bit U = Unimplemented bit, read as '0'

- '1' = Bit is set

- 0' = Bit is cleared x = Bit is unknown

bit 31-30 Unimplemented: Read as '0'

bit 29-27 PLLODIV<2:0>: Output Divider for PLL

- 111 = PLL output divided by 256

- 110 = PLL output divided by 64

- 101 = PLL output divided by 32

- 100 = PLL output divided by 16

- 011 = PLL output divided by 8

- 010 = PLL output divided by 4

- 001 = PLL output divided by 2

- 000 = PLL output divided by 1

### bit 26-24 FRCDIV<2:0>: Internal Fast RC (FRC) Oscillator Clock Divider bits

- 111 = FRC divided by 256

- 110 = FRC divided by 64

- 101 = FRC divided by 32

- 100 = FRC divided by 16

- 011 = FRC divided by 8

- 010 = FRC divided by 4

- 001 = FRC divided by 2 (default setting)

- 000 = FRC divided by 1

- bit 23 Unimplemented: Read as '0'

- bit 22 SOSCRDY: Secondary Oscillator (Sosc) Ready Indicator bit

- 1 = Indicates that the Secondary Oscillator is running and is stable

- 0 = Secondary Oscillator is still warming up or is turned off

- bit 21 PBDIVRDY: Peripheral Bus Clock (PBCLK) Divisor Ready bit

- 1 = PBDIV<1:0> bits can be written

- 0 = PBDIV<1:0> bits cannot be written

- bit 20-19 **PBDIV<1:0>:** Peripheral Bus Clock (PBCLK) Divisor bits

- 11 = PBCLK is SYSCLK divided by 8 (default)

- 10 = PBCLK is SYSCLK divided by 4

- 01 = PBCLK is SYSCLK divided by 2

- 00 = PBCLK is SYSCLK divided by 1

**Note:** Writes to this register require an unlock sequence. Refer to **Section 6. "Oscillator"** (DS60001112) in the *"PIC32 Family Reference Manual"* for details.

#### **Control Registers** 10.1

## TABLE 10-1: DMA GLOBAL REGISTER MAP

| ess                         |                               | â         |               |                                                                               |       |         |         |       |      | Bi   | its  |      |      |      |      |      |           |      | s          |

|-----------------------------|-------------------------------|-----------|---------------|-------------------------------------------------------------------------------|-------|---------|---------|-------|------|------|------|------|------|------|------|------|-----------|------|------------|

| Virtual Address<br>(BF88_#) | Register<br>Name              | Bit Range | 31/15         | 30/14                                                                         | 29/13 | 28/12   | 27/11   | 26/10 | 25/9 | 24/8 | 23/7 | 22/6 | 21/5 | 20/4 | 19/3 | 18/2 | 17/1      | 16/0 | All Resets |

| 3000 DMACON                 |                               | 31:16     | _             | _                                                                             | -     | _       | _       |       | _    | _    | _    | _    | _    | _    | _    | _    | _         | _    | 0000       |

| 3000                        | DMACON                        | 15:0      | ON            | _                                                                             | _     | SUSPEND | DMABUSY | _     | _    | _    | _    | _    | _    | _    | _    | _    | _         | _    | 0000       |

| 2010                        | DMASTAT                       | 31:16     | _             | _                                                                             | _     | _       | —       | _     | _    | _    | _    | -    | _    | _    | —    | _    | _         | _    | 0000       |

| 3010                        | DIVIASTAT                     | 15:0      | _             | —                                                                             |       | —       | —       | —     |      |      |      | —    | _    | _    | RDWR | D    | MACH<2:0> | (2)  | 0000       |

| 2020                        | 0 DMAADDR 31:16 DMAADDR<31:0> |           |               |                                                                               |       |         |         |       |      |      | 0000 |      |      |      |      |      |           |      |            |

| 3020                        | DIVIAADDR                     | 15:0      | DMAADDR<31:0> |                                                                               |       |         |         |       |      |      |      |      |      |      | 0000 |      |           |      |            |

| Legen                       | <b>d</b> .                    | nknown    | value on R    | n Reset: — = unimplemented read as '0'. Reset values are shown in hexadecimal |       |         |         |       |      |      |      |      |      |      |      |      |           |      |            |

This register has corresponding CLR, SET and INV registers at its virtual address, plus an offset of 0x4, 0x8 and 0xC, respectively. See Section 12.1.1 "CLR, SET and INV Registers" for more information. Note 1:

DMACH<3> bit is not available on PIC32MX534/564/664/764 devices. 2:

# TABLE 10-2: DMA CRC REGISTER MAP<sup>(1)</sup>

| ess                         |                                 | 0         | Bits  |                |       |       |       |           |      |      |          |        |        |      |      |            | ú    |      |            |

|-----------------------------|---------------------------------|-----------|-------|----------------|-------|-------|-------|-----------|------|------|----------|--------|--------|------|------|------------|------|------|------------|

| Virtual Address<br>(BF88_#) | Register<br>Name <sup>(1)</sup> | Bit Range | 31/15 | 30/14          | 29/13 | 28/12 | 27/11 | 26/10     | 25/9 | 24/8 | 23/7     | 22/6   | 21/5   | 20/4 | 19/3 | 18/2       | 17/1 | 16/0 | All Resets |

| 2020                        | DCRCCON                         | 31:16     | _     | _              | BYTO  | <1:0> | WBO   | _         | —    | BITO | —        | _      |        | _    | _    | —          | —    | _    | 0000       |

| 3030                        | DURCUUN                         | 15:0      | —     | —              | —     |       |       | PLEN<4:0> |      |      | CRCEN    | CRCAPP | CRCTYP | _    | —    | CRCCH<2:0> |      |      |            |

| 3040                        | DCRCDATA                        | 31:16     |       |                |       |       |       |           |      |      | TA-31:05 |        |        |      |      |            |      |      | 0000       |

| 3040                        | DONODAIA                        | 15:0      |       | DCRCDATA<31:0> |       |       |       |           |      |      |          |        |        | 0000 |      |            |      |      |            |

| 3050                        | DCRCXOR                         | 31:16     |       | DCRCXOR<31:0>  |       |       |       |           |      |      |          |        | 0000   |      |      |            |      |      |            |

| 3030                        | DUNUAUK                         | 15:0      | )     |                |       |       |       |           |      |      |          |        | 0000   |      |      |            |      |      |            |

Legend: x = unknown value on Reset; — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

Note 1: All registers in this table have corresponding CLR, SET and INV registers at their virtual addresses, plus offsets of 0x4, 0x8 and 0xC, respectively. See Section 12.1.1 "CLR, SET and INV Registers" for more information.

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1                                      | Bit<br>24/16/8/0 |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------------------------------------------|------------------|

| 24.24        | U-0                                                   | U-0              |

| 31:24        | _                 | _                 | _                 | _                 | _                 | _                 | —                                                     | —                |

| 00.40        | U-0                                                   | U-0              |

| 23:16        | _                 | _                 | —                 | _                 |                   | _                 | 25/17/9/1         24/16/8/0           U-0         U-0 | _                |

| 45.0         | R/W-0             | U-0               | U-0               | R/W-0             | R/W-0             | U-0               | U-0                                                   | U-0              |

| 15:8         | 0N <sup>(1)</sup> | —                 | -                 | SUSPEND           | DMABUSY           | —                 | —                                                     | —                |

| 7.0          | U-0                                                   | U-0              |

| 7:0          |                   | _                 | _                 | _                 | _                 |                   | _                                                     | _                |

#### REGISTER 10-1: DMACON: DMA CONTROLLER CONTROL REGISTER

### Legend:

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, rea | d as '0'           |

|-------------------|------------------|----------------------------|--------------------|

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared       | x = Bit is unknown |

### bit 31-16 Unimplemented: Read as '0'

- ON: DMA On bit<sup>(1)</sup> bit 15

- 1 = DMA module is enabled

- 0 = DMA module is disabled

- bit 14-13 Unimplemented: Read as '0'

- bit 12 SUSPEND: DMA Suspend bit

- 1 = DMA transfers are suspended to allow CPU uninterrupted access to data bus

- 0 = DMA operates normally

- bit 11 DMABUSY: DMA Module Busy bit

- 1 = DMA module is active

- 0 = DMA module is disabled and not actively transferring data

- bit 10-0 Unimplemented: Read as '0'

- Note 1: When using the 1:1 PBCLK divisor, the user's software should not read/write the peripheral's SFRs in the SYSCLK cycle immediately following the instruction that clears the module's ON bit.

# PIC32MX5XX/6XX/7XX

| Bit<br>Range | Bit<br>31/23/15/7    | Bit<br>30/22/14/6 | Bit<br>29/21/13/5       | Bit<br>28/20/12/4 | Bit<br>27/19/11/3  | Bit<br>26/18/10/2 | Bit<br>25/17/9/1   | Bit<br>24/16/8/0 |

|--------------|----------------------|-------------------|-------------------------|-------------------|--------------------|-------------------|--------------------|------------------|

| 31:24        | U-0                  | U-0               | U-0                     | U-0               | U-0                | U-0               | U-0                | U-0              |

| 31.24        |                      |                   |                         |                   | _                  |                   |                    | —                |

| 23:16        | U-0                  | U-0               | U-0                     | U-0               | U-0                | U-0               | U-0                | U-0              |

| 23.10        | _                    | -                 | _                       | —                 | _                  | —                 | -                  | —                |

| 45.0         | R/W-0                | U-0               | R/W-0                   | U-0               | U-0                | U-0               | U-0                | U-0              |

| 15:8         | ON <sup>(1,3)</sup>  |                   | SIDL <sup>(4)</sup>     | _                 | -                  | _                 | _                  | —                |

| 7:0          | R/W-0                | R/W-0             | R/W-0                   | R/W-0             | R/W-0              | U-0               | R/W-0              | U-0              |

| 7:0          | TGATE <sup>(3)</sup> | Т                 | CKPS<2:0> <sup>(:</sup> | 3)                | T32 <sup>(2)</sup> | _                 | TCS <sup>(3)</sup> | _                |

## REGISTER 14-1: TXCON: TYPE B TIMER CONTROL REGISTER

### Legend:

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, | read as '0'        |  |

|-------------------|------------------|------------------------|--------------------|--|

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared   | x = Bit is unknown |  |

### bit 31-16 **Unimplemented:** Read as '0'

- bit 15 **ON:** Timer On bit<sup>(1,3)</sup>

- 1 = Module is enabled 0 = Module is disabled

- bit 14 Unimplemented: Read as '0'

- bit 13 SIDL: Stop in Idle Mode bit<sup>(4)</sup>

- 1 = Discontinue operation when device enters Idle mode0 = Continue operation when device is in Idle mode

- bit 12-8 Unimplemented: Read as '0'

- bit 7 **TGATE:** Timer Gated Time Accumulation Enable bit<sup>(3)</sup>

When TCS = 1:

This bit is ignored and is read as '0'.

### When TCS = 0:

1 =Gated time accumulation is enabled

0 = Gated time accumulation is disabled

### bit 6-4 TCKPS<2:0>: Timer Input Clock Prescale Select bits<sup>(3)</sup>

- 111 = 1:256 prescale value

- 110 = 1:64 prescale value

- 101 = 1:32 prescale value

- 100 = 1:16 prescale value

- 011 = 1:8 prescale value

- 010 = 1:4 prescale value

- 001 = 1:2 prescale value

- 000 = 1:1 prescale value

- **Note 1:** When using the 1:1 PBCLK divisor, the user's software should not read/write the peripheral SFRs in the SYSCLK cycle immediately following the instruction that clears the module's ON bit.

- **2:** This bit is only available on even numbered timers (Timer2 and Timer4).

- **3:** While operating in 32-bit mode, this bit has no effect for odd numbered timers (Timer1, Timer3, and Timer5). All timer functions are set through the even numbered timers.

- 4: While operating in 32-bit mode, this bit must be cleared on odd numbered timers to enable the 32-bit timer in Idle mode.

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |  |  |  |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|--|--|--|--|

| 31:24        | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |  |  |

|              | FLTEN7            | MSEL              | 7<1:0>            | FSEL7<4:0>        |                   |                   |                  |                  |  |  |  |  |

| 22:16        | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |  |  |

| 23:16        | FLTEN6            | MSEL              | 6<1:0>            |                   | FSEL6<4:0>        |                   |                  |                  |  |  |  |  |

| 15:8         | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |  |  |

| 10.0         | FLTEN5            | MSEL              | 5<1:0>            |                   | F                 | SEL5<4:0>         |                  |                  |  |  |  |  |

| 7.0          | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |  |  |

| 7:0          | FLTEN4            | MSEL              | 4<1:0>            | FSEL4<4:0>        |                   |                   |                  |                  |  |  |  |  |

## **REGISTER 24-11: CIFLTCON1: CAN FILTER CONTROL REGISTER 1**

### Legend:

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, r | ead as '0'         |

|-------------------|------------------|--------------------------|--------------------|

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared     | x = Bit is unknown |

| bit 31    | FLTEN7: Filter 7 Enable bit                                 |

|-----------|-------------------------------------------------------------|

|           | 1 = Filter is enabled                                       |

|           | 0 = Filter is disabled                                      |

| bit 30-29 | MSEL7<1:0>: Filter 7 Mask Select bits                       |

|           | 11 = Acceptance Mask 3 selected                             |

|           | 10 = Acceptance Mask 2 selected                             |

|           | 01 = Acceptance Mask 1 selected                             |

|           | 00 = Acceptance Mask 0 selected                             |

| bit 28-24 | FSEL7<4:0>: FIFO Selection bits                             |

|           | 11111 = Message matching filter is stored in FIFO buffer 31 |

|           | 11110 = Message matching filter is stored in FIFO buffer 30 |

|           | •                                                           |

|           | •                                                           |

|           | 00001 = Message matching filter is stored in FIFO buffer 1  |

|           | 00000 = Message matching filter is stored in FIFO buffer 0  |

| bit 23    | FLTEN6: Filter 6 Enable bit                                 |

|           | 1 = Filter is enabled                                       |

|           | 0 = Filter is disabled                                      |

| bit 22-21 | MSEL6<1:0>: Filter 6 Mask Select bits                       |

|           | 11 = Acceptance Mask 3 selected                             |

|           | 10 = Acceptance Mask 2 selected                             |

|           | 01 = Acceptance Mask 1 selected                             |

|           | 00 = Acceptance Mask 0 selected                             |

| bit 20-16 | FSEL6<4:0>: FIFO Selection bits                             |

|           | 11111 = Message matching filter is stored in FIFO buffer 31 |

|           | 11110 - Massage matching filter is stored in EIEO buffer 30 |

uffer 31 11110 = Message matching filter is stored in FIFO buffer 30

•

•

00001 = Message matching filter is stored in FIFO buffer 1 00000 = Message matching filter is stored in FIFO buffer 0

Note: The bits in this register can only be modified if the corresponding filter enable (FLTENn) bit is '0'.

## REGISTER 24-14: CIFLTCON4: CAN FILTER CONTROL REGISTER 4 (CONTINUED)

|           | (                                                           |

|-----------|-------------------------------------------------------------|

| bit 15    | FLTEN17: Filter 13 Enable bit                               |

|           | 1 = Filter is enabled                                       |

|           | 0 = Filter is disabled                                      |

| bit 14-13 | MSEL17<1:0>: Filter 17 Mask Select bits                     |

|           | 11 = Acceptance Mask 3 selected                             |

|           | 10 = Acceptance Mask 2 selected                             |

|           | 01 = Acceptance Mask 1 selected                             |

|           | 00 = Acceptance Mask 0 selected                             |

| bit 12-8  | FSEL17<4:0>: FIFO Selection bits                            |

|           | 11111 = Message matching filter is stored in FIFO buffer 31 |

|           | 11110 = Message matching filter is stored in FIFO buffer 30 |

|           | •                                                           |

|           |                                                             |

|           | 00001 = Message matching filter is stored in FIFO buffer 1  |

|           | 00000 = Message matching filter is stored in FIFO buffer 0  |

| bit 7     | FLTEN16: Filter 16 Enable bit                               |

|           | 1 = Filter is enabled                                       |

|           | 0 = Filter is disabled                                      |

| bit 6-5   | MSEL16<1:0>: Filter 16 Mask Select bits                     |

|           | 11 = Acceptance Mask 3 selected                             |

|           | 10 = Acceptance Mask 2 selected                             |

|           | 01 = Acceptance Mask 1 selected                             |

|           | 00 = Acceptance Mask 0 selected                             |

| bit 4-0   | FSEL16<4:0>: FIFO Selection bits                            |

|           | 11111 = Message matching filter is stored in FIFO buffer 31 |

|           | 11110 = Message matching filter is stored in FIFO buffer 30 |

|           | •                                                           |

|           | •                                                           |

|           | 00001 = Message matching filter is stored in FIFO buffer 1  |

|           | 00000 = Message matching filter is stored in FIFO buffer 0  |

| r         |                                                             |

Note: The bits in this register can only be modified if the corresponding filter enable (FLTENn) bit is '0'.

### TABLE 25-5: ETHERNET CONTROLLER REGISTER SUMMARY FOR PIC32MX664F064H, PIC32MX664F128H, PIC32MX664F064L, PIC32MX664F128L, PIC32MX675F256H, PIC32MX675F512H, PIC32MX695F512H, PIC32MX775F256H, PIC32MX775F512H, PIC32MX795F512H, PIC32MX695F512L, PIC32MX675F256L, PIC32MX675F512L, PIC32MX764F128H, PIC32MX764F128L, PIC32MX775F256L, PIC32MX775F512L AND PIC32MX795F512L DEVICES (CONTINUED)

| ess                         |                                 | 0                                         |               |                          |               |         |               |               |               | В             | its       |         |               |               |            |         |          |          | ŝ          |

|-----------------------------|---------------------------------|-------------------------------------------|---------------|--------------------------|---------------|---------|---------------|---------------|---------------|---------------|-----------|---------|---------------|---------------|------------|---------|----------|----------|------------|

| Virtual Address<br>(BF88_#) | Register<br>Name <sup>(1)</sup> | Bit Range                                 | 31/15         | 30/14                    | 29/13         | 28/12   | 27/11         | 26/10         | 25/9          | 24/8          | 23/7      | 22/6    | 21/5          | 20/4          | 19/3       | 18/2    | 17/1     | 16/0     | All Resets |

| 90E0                        | ETHSTAT                         | 31:16<br>15:0                             | _             |                          | _             | _       | _             |               |               | _             | BUSY      | TXBUSY  | RXBUSY        | BUFC          | NT<7:0>    | _       | _        | _        | 0000       |

|                             | ETH                             | 31:16                                     | _             |                          | _             | _       |               |               | _             |               | _         |         | _             |               | _          | _       | _        |          | 0000       |

| 9100                        | RXOVFLOW                        | 15:0                                      |               |                          |               |         |               |               |               | RXOVFLW       | CNT<15:0> |         |               |               |            |         |          |          | 0000       |

|                             | ETH                             | 31:16                                     | _             | _                        | _             | _       |               | _             | _             |               | _         | _       |               | _             |            |         |          | _        | 0000       |

| 9110                        | FRMTXOK                         |                                           |               |                          |               |         |               |               |               |               |           |         | 0000          |               |            |         |          |          |            |

| 9120                        | ETH                             | 31:16                                     | _             | -                        |               | _       | _             | -             | —             | -             | _         | _       | _             | -             |            | _       | _        | —        | 0000       |

| 9120                        | SCOLFRM                         | FRM         15:0         SCOLFRMCNT<15:0> |               |                          |               |         |               |               |               |               |           | 0000    |               |               |            |         |          |          |            |

| 9130                        | ETH                             | 31:16                                     | —             | _                        | _             | —       | _             | _             | —             | —             | —         | —       | _             | _             | —          | —       | —        | —        | 0000       |

|                             | MCOLFRM                         | 15:0                                      |               |                          |               |         |               |               |               | MCOLFRM       | CNT<15:0> |         |               |               |            |         |          |          | 0000       |

| 9140                        | ETH<br>FRMRXOK                  | 31:16                                     | —             | _                        | —             | —       | _             | _             | —             | -             | -         | —       | _             | —             | —          | _       | —        | —        | 0000       |

|                             |                                 | 15:0                                      |               |                          |               |         |               |               |               | FRMRXOK       |           |         |               |               |            |         |          | 0000     |            |

| 9150                        | ETH<br>FCSERR                   | 31:16<br>15:0                             | _             | —                        |               | —       | _             | —             | _             | FCSERRO       |           | _       |               | —             | —          | _       | —        | —        | 0000       |

|                             | ETH                             | 31:16                                     | _             | _                        | _             | _       | _             | _             | _             |               | _         | _       | _             | _             | _          | _       | _        | _        | 0000       |

| 9160                        | ALGNERR                         | 15:0                                      |               |                          |               |         |               |               |               | ALGNERR       | CNT<15:0> |         |               |               |            |         |          |          | 0000       |

|                             | 51404                           | 31:16                                     | _             | _                        | _             | _       | _             | _             | —             | _             | _         | —       | _             | _             | _          | _       | _        | _        | 0000       |

| 9200                        | EMAC1<br>CFG1                   | 15:0                                      | SOFT<br>RESET | SIM<br>RESET             | _             | _       | RESET<br>RMCS | RESET<br>RFUN | RESET<br>TMCS | RESET<br>TFUN | _         | _       | _             | LOOPBACK      | TXPAUSE    | RXPAUSE | PASSALL  | RXENABLE | 800D       |

|                             | EMAC1                           | 31:16                                     | _             |                          |               | —       |               | _             | —             |               | _         | _       |               | _             |            | —       | _        | —        | 0000       |

| 9210                        | CFG2                            | 15:0                                      | _             | EXCESS<br>DFR            | BP<br>NOBKOFF | NOBKOFF | —             |               | LONGPRE       | PUREPRE       | AUTOPAD   | VLANPAD | PAD<br>ENABLE | CRC<br>ENABLE | DELAYCRC   | HUGEFRM | LENGTHCK | FULLDPLX | 4082       |

| 9220                        | EMAC1                           | 31:16                                     | _             |                          | —             | _       | _             | _             | —             | _             | _         | _       | _             | _             | —          |         | _        | _        | 0000       |

| 3220                        | IPGT                            | 15:0                                      | —             | _                        | —             | —       | —             | _             | —             | _             | _         |         |               | B             | 2BIPKTGP<6 | :0>     |          | -        | 0012       |

| 9230                        | EMAC1                           | 31:16                                     | _             | _                        | —             | —       | _             | _             | —             | _             | _         | _       | —             | _             | —          | —       | _        | -        | 0000       |

|                             | IPGR                            | 15:0                                      | _             |                          |               | NB2     | BIPKTGP1<     | 6:0>          |               |               |           |         |               |               | 2BIPKTGP2< |         |          |          | 0C12       |

| 9240                        | EMAC1<br>CLRT                   | 31:16                                     | _             |                          | —             | -       | -             | -             | —             | _             | _         |         |               |               | —          |         | <u> </u> | -        | 0000       |

|                             |                                 | 15:0                                      | _             | - CWINDOW<5:0> RETX<3:0> |               |         |               |               |               |               |           | 370F    |               |               |            |         |          |          |            |

| 9250                        | EMAC1<br>MAXF                   | 31:16                                     |               |                          |               |         |               |               |               |               |           | 0000    |               |               |            |         |          |          |            |

|                             |                                 | 15:0                                      |               | MACMAXF<15:0> 05EE       |               |         |               |               |               |               |           |         |               |               |            |         |          |          |            |

PIC32MX5XX/6XX/7XX

x = unknown value on Reset; - = unimplemented, read as '0'. Reset values are shown in hexadecimal. Legend:

Note 1: All registers in this table (with the exception of ETHSTAT) have corresponding CLR, SET and INV registers at their virtual addresses, plus offsets of 0x4, 0x8 and 0xC, respectively. See Section 12.1.1 "CLR, SET and INV Registers" for more information.

Reset values default to the factory programmed value. 2:

DS60001156J-page 282

| REGISTER 25-23: | EMAC1CFG1: ETHERNET CONTROLLER MAC CONFIGURATION 1 REGISTER |

|-----------------|-------------------------------------------------------------|

|                 |                                                             |

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|

| 31:24        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 31.24        | —                 | —                 | —                 |                   | _                 | —                 | —                | —                |

| 23:16        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 23.10        |                   | —                 | —                 | _                 | _                 |                   |                  | —                |

|              | R/W-1             | R/W-0             | U-0               | U-0               | R/W-0             | R/W-0             | R/W-0            | R/W-0            |

| 15:8         | SOFT<br>RESET     | SIM<br>RESET      | —                 |                   | RESET<br>RMCS     | RESET<br>RFUN     | RESET<br>TMCS    | RESET<br>TFUN    |

|              | U-0               | U-0               | U-0               | R/W-0             | R/W-1             | R/W-1             | R/W-0            | R/W-1            |

| 7:0          |                   |                   | _                 | LOOPBACK          | TX<br>PAUSE       | RX<br>PAUSE       | PASSALL          | RX<br>ENABLE     |

| Logondy |

|---------|

| Legena. |

| Logona.           |                  |                           |                    |

|-------------------|------------------|---------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, re | ad as '0'          |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared      | x = Bit is unknown |

### bit 31-16 Unimplemented: Read as '0'

| bit 15    | SOFTRESET: Soft Reset bit                                                                               |

|-----------|---------------------------------------------------------------------------------------------------------|

|           | Setting this bit will put the MACMII in reset. Its default value is '1'.                                |

| bit 14    | SIMRESET: Simulation Reset bit                                                                          |

|           | Setting this bit will cause a reset to the random number generator within the Transmit Function.        |

| bit 13-12 | Unimplemented: Read as '0'                                                                              |

| bit 11    | RESETRMCS: Reset MCS/RX bit                                                                             |

|           | Setting this bit will put the MAC Control Sub-layer/Receive domain logic in reset.                      |

| bit 10    | RESETRFUN: Reset RX Function bit                                                                        |

|           | Setting this bit will put the MAC Receive function logic in reset.                                      |

| bit 9     | RESETTMCS: Reset MCS/TX bit                                                                             |

|           | Setting this bit will put the MAC Control Sub-layer/TX domain logic in reset.                           |

| bit 8     | RESETTFUN: Reset TX Function bit                                                                        |

|           | Setting this bit will put the MAC Transmit function logic in reset.                                     |

| bit 7-5   | Unimplemented: Read as '0'                                                                              |

| bit 4     | LOOPBACK: MAC Loopback mode bit                                                                         |

|           | 1 = MAC Transmit interface is loop backed to the MAC Receive interface                                  |

| bit 3     | 0 = MAC normal operation<br><b>TXPAUSE:</b> MAC TX Flow Control bit                                     |

| DILS      | 1 = PAUSE Flow Control frames are allowed to be transmitted                                             |

|           | 1 = PAUSE Flow Control frames are allowed to be transmitted $0 = PAUSE Flow Control frames are blocked$ |

| bit 2     | RXPAUSE: MAC RX Flow Control bit                                                                        |

|           | 1 = The MAC acts upon received PAUSE Flow Control frames                                                |

|           | 0 = Received PAUSE Flow Control frames are ignored                                                      |

| bit 1     | PASSALL: MAC Pass all Receive Frames bit                                                                |

|           | 1 = The MAC will accept all frames regardless of type (Normal vs. Control)                              |

|           | 0 = The received Control frames are ignored                                                             |

| bit 0     | RXENABLE: MAC Receive Enable bit                                                                        |

|           | 1 = Enable the MAC receiving of frames                                                                  |

|           |                                                                                                         |

0 = Disable the MAC receiving of frames

**Note:** Both 16-bit and 32-bit accesses are allowed to these registers (including the SET, CLR and INV registers). 8-bit accesses are not allowed and are ignored by the hardware.

# PIC32MX5XX/6XX/7XX

### REGISTER 25-28: EMAC1MAXF: ETHERNET CONTROLLER MAC MAXIMUM FRAME LENGTH REGISTER

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3     | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

|--------------|-------------------|-------------------|-------------------|-------------------|-----------------------|-------------------|------------------|------------------|

| 31:24        | U-0               | U-0               | U-0               | U-0               | U-0                   | U-0               | U-0              | U-0              |

| 31.24        |                   | —                 | _                 | _                 | —                     | —                 | _                | _                |

| 22:16        | U-0               | U-0               | U-0               | U-0               | U-0                   | U-0               | U-0              | U-0              |

| 23:16        | —                 | —                 | —                 | —                 | —                     | —                 | —                | —                |

| 15.0         | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0                 | R/W-1             | R/W-0            | R/W-1            |

| 15:8         |                   |                   |                   | MACMAXF<          | <15:8> <sup>(1)</sup> |                   |                  |                  |

| 7.0          | R/W-1             | R/W-1             | R/W-1             | R/W-0             | R/W-1                 | R/W-1             | R/W-1            | R/W-0            |

| 7:0          |                   |                   |                   | MACMAXF           | <7:0> <sup>(1)</sup>  |                   |                  |                  |

| Legend:           |                  |                          |                    |

|-------------------|------------------|--------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, r | ead as '0'         |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared     | x = Bit is unknown |

### bit 31-16 Unimplemented: Read as '0'

bit 15-0 MACMAXF<15:0>: Maximum Frame Length bits<sup>(1)</sup>

These bits reset to 0x05EE, which represents a maximum receive frame of 1518 octets. An untagged maximum size Ethernet frame is 1518 octets. A tagged frame adds four octets for a total of 1522 octets. If a shorter/longer maximum length restriction is desired, program this 16-bit field.

**Note 1:** If a proprietary header is allowed, this bit should be adjusted accordingly. For example, if 4-byte headers are prepended to frames, MACMAXF could be set to 1527 octets. This would allow the maximum VLAN tagged frame plus the 4-byte header.

**Note:** Both 16-bit and 32-bit accesses are allowed to these registers (including the SET, CLR and INV registers). 8-bit accesses are not allowed and are ignored by the hardware.

# PIC32MX5XX/6XX/7XX

NOTES:

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|

| 24.24        | r-1               | r-1               | r-1               | r-1               | r-1               | r-1               | r-1              | r-1              |

| 31:24        | —                 | —                 | —                 | _                 | —                 | _                 | _                | —                |

| 00.40        | R/P               | r-1               | r-1               | R/P               | R/P               | R/P               | R/P              | R/P              |

| 23:16        | FWDTEN            | —                 | —                 | WDTPS<4:0>        |                   |                   |                  |                  |

| 45.0         | R/P               | R/P               | R/P               | R/P               | r-1               | R/P               | R/P              | R/P              |

| 15:8         | FCKSM             | /<1:0>            | FPBDI             | /<1:0> —          |                   | OSCIOFNC          | POSCM            | OD<1:0>          |