Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFl

| Product Status             | Active                                                                            |

|----------------------------|-----------------------------------------------------------------------------------|

| Core Processor             | MIPS32® M4K™                                                                      |

| Core Size                  | 32-Bit Single-Core                                                                |

| Speed                      | 80MHz                                                                             |

| Connectivity               | Ethernet, I <sup>2</sup> C, SPI, UART/USART, USB OTG                              |

| Peripherals                | Brown-out Detect/Reset, DMA, POR, PWM, WDT                                        |

| Number of I/O              | 53                                                                                |

| Program Memory Size        | 256KB (256K x 8)                                                                  |

| Program Memory Type        | FLASH                                                                             |

| EEPROM Size                | -                                                                                 |

| RAM Size                   | 64K x 8                                                                           |

| Voltage - Supply (Vcc/Vdd) | 2.3V ~ 3.6V                                                                       |

| Data Converters            | A/D 16x10b                                                                        |

| Oscillator Type            | Internal                                                                          |

| Operating Temperature      | -40°C ~ 105°C (TA)                                                                |

| Mounting Type              | Surface Mount                                                                     |

| Package / Case             | 64-VFQFN Exposed Pad                                                              |

| Supplier Device Package    | 64-VQFN (9x9)                                                                     |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic32mx675f256ht-80v-mr |

|                            |                                                                                   |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

#### TABLE 11: PIN NAMES FOR USB AND ETHERNET DEVICES

| 1          | 21-PIN TFBGA (BOTTOM VIEW)                                                                  |          | L11                                                          |

|------------|---------------------------------------------------------------------------------------------|----------|--------------------------------------------------------------|

|            | PIC32MX664F064L<br>PIC32MX664F128L<br>PIC32MX675F256L<br>PIC32MX675F512L<br>PIC32MX695F512L |          | L1 A11                                                       |

|            | te: The TFBGA package skips from row "H                                                     |          |                                                              |

| Pin #      | Full Pin Name                                                                               | Pin #    | Full Pin Name                                                |

| A1         | PMD4/RE4                                                                                    | E2       | T4CK/RC3                                                     |

| A2         | PMD3/RE3                                                                                    | E3       | ECOL/SCK2/U6TX/U3RTS/PMA5/CN8/RG6                            |

| A3         | TRD0/RG13                                                                                   | E4       | T3CK/RC2                                                     |

| A4         | PMD0/RE0                                                                                    | E5       | VDD                                                          |

| A5         | PMD8/RG0                                                                                    | E6       | ETXERR/PMD9/RG1                                              |

| A6         | ETXD0/PMD10/RF1                                                                             | E7       | Vss                                                          |

| A7         | Vdd                                                                                         | E8       | AETXEN/SDA1/INT4/RA15                                        |

| A8         | Vss                                                                                         | E9       | RTCC/EMDIO/AEMDIO/IC1/RD8                                    |

| A9         | ETXD2/IC5/PMD12/RD12                                                                        | E10      | SS1/IC2/RD9                                                  |

| A10        | OC3/RD2                                                                                     | E11      | AETXCLK/SCL1/INT3/RA14                                       |

| A11        | OC2/RD1                                                                                     | F1       | MCLR                                                         |

| B1         | No Connect (NC)                                                                             | F2       | ERXDV/AERXDV/ECRSDV/AECRSDV//SCL4/SDO2/U3TX/PMA3/CN10/RG8    |

| B2         | AERXERR/RG15                                                                                | F3       | ERXCLK/AERXCLK/EREFCLK/AEREFCLK/SS2/U6RX/U3CTS/PMA2/CN11/RG9 |

| B3         | PMD2/RE2                                                                                    | F4       | ECRS/SDA4/SDI2/U3RX/PMA4/CN9/RG7                             |

| B4         | PMD1/RE1                                                                                    | F5       | Vss                                                          |

| B5         | TRD3/RA7                                                                                    | F6       | No Connect (NC)                                              |

| B6         | ETXD1/PMD11/RF0                                                                             | F7       | No Connect (NC)                                              |

| B7         | VCAP                                                                                        | F8       | VDD                                                          |

| B8         | PMRD/CN14/RD5                                                                               | F9       | OSC1/CLKI/RC12                                               |

| B9         | OC4/RD3                                                                                     | F10      | Vss                                                          |

| B10        | Vss                                                                                         | F11      | OSC2/CLKO/RC15                                               |

| B11        | SOSCO/T1CK/CN0/RC14                                                                         | G1       | AERXD0/INT1/RE8                                              |

| C1         | PMD6/RE6                                                                                    | G2       | AERXD1/INT2/RE9                                              |

| C2         | VDD                                                                                         | G3       | TMS/RA0                                                      |

| C3<br>C4   | TRD1/RG12<br>TRD2/RG14                                                                      | G4<br>G5 | No Connect (NC)<br>VDD                                       |

| C4         | TRCLK/RA6                                                                                   | G5<br>G6 | Vss                                                          |

|            | No Connect (NC)                                                                             | G0<br>G7 | Vss                                                          |

| C0<br>C7   | ETXCLK/PMD15/CN16/RD7                                                                       | G7<br>G8 | No Connect (NC)                                              |

| C8         | OC5/PMWR/CN13/RD4                                                                           | G9       | TDO/RA5                                                      |

| C9         | VDD                                                                                         | G10      | SDA2/RA3                                                     |

| C10        | SOSCI/CN1/RC13                                                                              | G11      | TDI/RA4                                                      |

| C11        | EMDC/AEMDC/IC4/PMCS1/PMA14/RD11                                                             | H1       | AN5/C1IN+/VBUSON/CN7/RB5                                     |

| D1         | T2CK/RC1                                                                                    | H2       | AN4/C1IN-/CN6/RB4                                            |

| D2         | PMD7/RE7                                                                                    | H3       | Vss                                                          |

| D3         | PMD5/RE5                                                                                    | H4       | VDD                                                          |

| D4         | Vss                                                                                         | H5       | No Connect (NC)                                              |

| D5         | Vss                                                                                         | H6       | VDD                                                          |

| D6         | No Connect (NC)                                                                             | H7       | No Connect (NC)                                              |

| D7         | ETXEN/PMD14/CN15/RD6                                                                        | H8       | VBUS                                                         |

| D8         | ETXD3/PMD13/CN19/RD13                                                                       | H9       | VUSB3V3                                                      |

| D9         | SDO1/OC1/INT0/RD0                                                                           | H10      | D+/RG2                                                       |

| D10        | No Connect (NC)                                                                             | H11      | SCL2/RA2                                                     |

| D11        | SCK1/IC3/PMCS2/PMA15/RD10                                                                   | J1       | AN3/C2IN+/CN5/RB3                                            |

| E1<br>Note | T5CK/SDI1/RC4<br>1: Shaded pins are 5V tolerant.                                            | J2       | AN2/C2IN-/CN4/RB2                                            |

The MIPS architecture defines that the result of a multiply or divide operation be placed in the HI and LO registers. Using the Move-From-HI (MFHI) and Move-From-LO (MFLO) instructions, these values can be transferred to the General Purpose Register file.

In addition to the HI/LO targeted operations, the MIPS32 architecture also defines a multiply instruction, MUL, which places the least significant results in the primary register file instead of the HI/LO register pair. By avoiding the explicit MFLO instruction required when using the LO register, and by supporting multiple destination registers, the throughput of multiply-intensive operations is increased.

Two other instructions, Multiply-Add (MADD) and Multiply-Subtract (MSUB), are used to perform the multiply-accumulate and multiply-subtract operations. The MADD instruction multiplies two numbers and then adds the product to the current contents of the HI and LO registers. Similarly, the MSUB instruction multiplies two operands and then subtracts the product from the HI and LO registers. The MADD and MSUB operations are commonly used in DSP algorithms.

#### 3.2.3 SYSTEM CONTROL COPROCESSOR (CP0)

In the MIPS architecture, CP0 is responsible for the virtual-to-physical address translation, the exception control system, the processor's diagnostics capability, the operating modes (Kernel, User and Debug) and whether interrupts are enabled or disabled. Configuration information, such as presence of options like MIPS16e, is also available by accessing the CP0 registers, listed in Table 3-2.

| Register<br>Number | Register<br>Name        | Function                                                                 |

|--------------------|-------------------------|--------------------------------------------------------------------------|

| 0-6                | Reserved                | Reserved.                                                                |

| 7                  | HWREna                  | Enables access via the RDHWR instruction to selected hardware registers. |

| 8                  | BadVAddr <sup>(1)</sup> | Reports the address for the most recent address-related exception.       |

| 9                  | Count <sup>(1)</sup>    | Processor cycle count.                                                   |

| 10                 | Reserved                | Reserved.                                                                |

| 11                 | Compare <sup>(1)</sup>  | Timer interrupt control.                                                 |

| 12                 | Status <sup>(1)</sup>   | Processor status and control.                                            |

| 12                 | IntCtl <sup>(1)</sup>   | Interrupt system status and control.                                     |

| 12                 | SRSCtl <sup>(1)</sup>   | Shadow register set status and control.                                  |

| 12                 | SRSMap <sup>(1)</sup>   | Provides mapping from vectored interrupt to a shadow set.                |

| 13                 | Cause <sup>(1)</sup>    | Cause of last general exception.                                         |

| 14                 | EPC <sup>(1)</sup>      | Program counter at last exception.                                       |

| 15                 | PRId                    | Processor identification and revision.                                   |

| 15                 | Ebase                   | Exception vector base register.                                          |

| 16                 | Config                  | Configuration register.                                                  |

| 16                 | Config1                 | Configuration Register 1.                                                |

| 16                 | Config2                 | Configuration Register 2.                                                |

| 16                 | Config3                 | Configuration Register 3.                                                |

| 17-22              | Reserved                | Reserved.                                                                |

| 23                 | Debug <sup>(2)</sup>    | Debug control and exception status.                                      |

| 24                 | DEPC <sup>(2)</sup>     | Program counter at last debug exception.                                 |

| 25-29              | Reserved                | Reserved.                                                                |

| 30                 | ErrorEPC <sup>(1)</sup> | Program counter at last error.                                           |

| 31                 | DESAVE <sup>(2)</sup>   | Debug handler scratchpad register.                                       |

|                    | <b>I</b>                |                                                                          |

TABLE 3-2: COPROCESSOR 0 REGISTERS

Note 1: Registers used in exception processing.

2: Registers used during debug.

Bit

Bit

Bit

| Bit<br>Range | Bit<br>31/23/15/7                                                                         | Bit<br>30/22/14/6 | Bit<br>29/21/13/5    | Bit<br>28/20/12/4     | Bit<br>27/19/11/3      | Bit<br>26/18/10/2 | Bit<br>25/17/9/1    | Bit<br>24/16/8/0 |  |  |  |  |

|--------------|-------------------------------------------------------------------------------------------|-------------------|----------------------|-----------------------|------------------------|-------------------|---------------------|------------------|--|--|--|--|

|              | U-0                                                                                       | U-0               | U-0                  | U-0                   | U-0                    | U-0               | U-0                 | U-0              |  |  |  |  |

| 31:24        |                                                                                           | _                 | —                    | _                     | _                      | —                 | —                   |                  |  |  |  |  |

| 00.40        | U-0                                                                                       | U-0               | U-0                  | U-0                   | U-0                    | U-0               | U-0                 | U-0              |  |  |  |  |

| 23:16        |                                                                                           | _                 | _                    |                       | —                      |                   |                     |                  |  |  |  |  |

| 45.0         | R/W-0, HC                                                                                 | R/W-0             | R-0, HS              | R-0, HS               | R-0, HSC               | U-0               | U-0                 | U-0              |  |  |  |  |

| 15:8         | WR                                                                                        | WREN              | WRERR <sup>(1)</sup> | LVDERR <sup>(1)</sup> | LVDSTAT <sup>(1)</sup> | —                 | —                   |                  |  |  |  |  |

| 7:0          | U-0                                                                                       | U-0               | U-0                  | U-0                   | R/W-0                  | R/W-0             | R/W-0               | R/W-0            |  |  |  |  |

| 7.0          | —                                                                                         | —                 | —                    | —                     |                        | NVMOF             | <b>P&lt;3:0&gt;</b> |                  |  |  |  |  |

| Legend:      |                                                                                           | U = Unimple       | emented bit, r       | ead as '0'            |                        | HSC = Set an      | d Cleared by        | hardware         |  |  |  |  |

| R = Reac     | lable bit                                                                                 | W = Writable      |                      | HS = Set by           | / hardware             | HC = Cleared      | -                   |                  |  |  |  |  |

| -n = Value   |                                                                                           | '1' = Bit is se   |                      | '0' = Bit is c        |                        | x = Bit is unkr   | •                   |                  |  |  |  |  |

|              |                                                                                           |                   |                      | 0 - Dit 10 0          |                        |                   |                     |                  |  |  |  |  |

| bit 31-16    | Unimpleme                                                                                 | nted: Read a      | <b>is</b> '0'        |                       |                        |                   |                     |                  |  |  |  |  |

| bit 15       | WR: Write C                                                                               |                   |                      |                       |                        |                   |                     |                  |  |  |  |  |

|              | This bit is w                                                                             | ritable when V    | VREN = 1 an          | d the unlock          | sequence is fo         | ollowed.          |                     |                  |  |  |  |  |

|              | 1 = Initiate a                                                                            | a Flash operat    | tion. Hardwar        | e clears this I       | bit when the o         | peration compl    | etes                |                  |  |  |  |  |

|              |                                                                                           | •                 |                      |                       |                        |                   |                     |                  |  |  |  |  |

| bit 14       | <ul><li>0 = Flash operation complete or inactive</li><li>WREN: Write Enable bit</li></ul> |                   |                      |                       |                        |                   |                     |                  |  |  |  |  |

|              | 1 = Enable writes to WR bit and enables LVD circuit                                       |                   |                      |                       |                        |                   |                     |                  |  |  |  |  |

|              | 0 = Disable writes to WR bit and disables LVD circuit                                     |                   |                      |                       |                        |                   |                     |                  |  |  |  |  |

|              | Note:                                                                                     | This is the on    | lv bit in this re    | aister that is        | reset by a dev         | vice Reset.       |                     |                  |  |  |  |  |

| bit 13       | WRERR: Write Error bit <sup>(1)</sup>                                                     |                   |                      |                       |                        |                   |                     |                  |  |  |  |  |

|              | This bit is read-only and is automatically set by hardware.                               |                   |                      |                       |                        |                   |                     |                  |  |  |  |  |

|              | 1 = Program or erase sequence did not complete successfully                               |                   |                      |                       |                        |                   |                     |                  |  |  |  |  |

|              | 0 = Program or erase sequence completed normally                                          |                   |                      |                       |                        |                   |                     |                  |  |  |  |  |

| bit 12       | LVDERR: Low-Voltage Detect Error bit (LVD circuit must be enabled) <sup>(1)</sup>         |                   |                      |                       |                        |                   |                     |                  |  |  |  |  |

|              | This bit is read-only and is automatically set by hardware.                               |                   |                      |                       |                        |                   |                     |                  |  |  |  |  |

|              | 1 = Low-voltage detected (possible data corruption, if WRERR is set)                      |                   |                      |                       |                        |                   |                     |                  |  |  |  |  |

|              | 0 = Voltage level is acceptable for programming                                           |                   |                      |                       |                        |                   |                     |                  |  |  |  |  |

| bit 11       | LVDSTAT: Low-Voltage Detect Status bit (LVD circuit must be enabled) <sup>(1)</sup>       |                   |                      |                       |                        |                   |                     |                  |  |  |  |  |

|              | This bit is read-only and is automatically set, and cleared, by hardware.                 |                   |                      |                       |                        |                   |                     |                  |  |  |  |  |

|              | 1 = Low-voltage event is active                                                           |                   |                      |                       |                        |                   |                     |                  |  |  |  |  |

|              | <ul> <li>Low-voltage event is active</li> <li>Low-voltage event is not active</li> </ul>  |                   |                      |                       |                        |                   |                     |                  |  |  |  |  |

| bit 10-4     |                                                                                           | nted: Read a      |                      |                       |                        |                   |                     |                  |  |  |  |  |

| bit 3-0      | -                                                                                         | 0>: NVM Ope       |                      |                       |                        |                   |                     |                  |  |  |  |  |

|              |                                                                                           | re writable wi    |                      | 0.                    |                        |                   |                     |                  |  |  |  |  |

|              | 1111 = Res                                                                                |                   |                      |                       |                        |                   |                     |                  |  |  |  |  |

|              | •                                                                                         | orrou             |                      |                       |                        |                   |                     |                  |  |  |  |  |

|              | •                                                                                         | •                 |                      |                       |                        |                   |                     |                  |  |  |  |  |

|              | •                                                                                         | a m ca d          |                      |                       |                        |                   |                     |                  |  |  |  |  |

|              | 0111 = Reserved<br>0110 = No operation                                                    |                   |                      |                       |                        |                   |                     |                  |  |  |  |  |

|              |                                                                                           | •                 | FM) erase or         | eration eras          | es PFM if all r        | bages are not v   | vrite-protected     | Ч                |  |  |  |  |

|              |                                                                                           |                   |                      |                       |                        | R if it is not wr |                     | 4                |  |  |  |  |

|              |                                                                                           |                   |                      |                       |                        | DDR if it is not  |                     | ed               |  |  |  |  |

|              | 0010 = No c                                                                               |                   | P9-                  |                       | ,                      |                   | - F                 | -                |  |  |  |  |

|              |                                                                                           |                   | eration: progr       | ams word se           | elected by NVM         | MADDR if it is r  | not write-prote     | ected            |  |  |  |  |

|              | 0000 = No o                                                                               | operation         |                      |                       | -                      |                   | -                   |                  |  |  |  |  |

|              |                                                                                           |                   |                      |                       |                        |                   |                     |                  |  |  |  |  |

#### **REGISTER 5-1:** NVMCON: PROGRAMMING CONTROL REGISTER

Bit

Bit

Bit

Bit

Bit

Bit

Note 1: This bit is cleared by setting NVMOP == 0000b, and initiating a Flash operation (i.e., WR).

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |  |  |  |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|--|--|--|--|

| 04.04        | W-0               | W-0               | W-0               | W-0               | W-0               | W-0               | W-0              | W-0              |  |  |  |  |

| 31:24        | NVMKEY<31:24>     |                   |                   |                   |                   |                   |                  |                  |  |  |  |  |

| 00.40        | W-0               | W-0               | W-0               | W-0               | W-0               | W-0               | W-0              | W-0              |  |  |  |  |

| 23:16        | NVMKEY<23:16>     |                   |                   |                   |                   |                   |                  |                  |  |  |  |  |

| 45.0         | W-0               | W-0               | W-0               | W-0               | W-0               | W-0               | W-0              | W-0              |  |  |  |  |

| 15:8         | NVMKEY<15:8>      |                   |                   |                   |                   |                   |                  |                  |  |  |  |  |

| 7.0          | W-0               | W-0               | W-0               | W-0               | W-0               | W-0               | W-0              | W-0              |  |  |  |  |

| 7:0          |                   |                   |                   | NVMK              | EY<7:0>           |                   |                  |                  |  |  |  |  |

#### REGISTER 5-2: NVMKEY: PROGRAMMING UNLOCK REGISTER

# Legend:R = Readable bitW = Writable bitU = Unimplemented bit, read as '0'-n = Value at POR'1' = Bit is set'0' = Bit is clearedx = Bit is unknown

#### bit 31-0 NVMKEY<31:0>: Unlock Register bits

These bits are write-only, and read as '0' on any read.

Note: This register is used as part of the unlock sequence to prevent inadvertent writes to the PFM.

#### REGISTER 5-3: NVMADDR: FLASH ADDRESS REGISTER

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |  |  |  |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|--|--|--|--|

| 24.24        | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |  |  |

| 31:24        | NVMADDR<31:24>    |                   |                   |                   |                   |                   |                  |                  |  |  |  |  |

| 00.40        | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |  |  |

| 23:16        | NVMADDR<23:16>    |                   |                   |                   |                   |                   |                  |                  |  |  |  |  |

| 45.0         | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |  |  |

| 15:8         | NVMADDR<15:8>     |                   |                   |                   |                   |                   |                  |                  |  |  |  |  |

| 7.0          | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |  |  |

| 7:0          |                   |                   |                   | NVMAE             | DDR<7:0>          |                   |                  |                  |  |  |  |  |

| Legend:           |                  |                                    |                    |  |  |  |

|-------------------|------------------|------------------------------------|--------------------|--|--|--|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read as '0' |                    |  |  |  |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared               | x = Bit is unknown |  |  |  |

bit 31-0 NVMADDR<31:0>: Flash Address bits Bulk/Chip/PFM Erase: Address is ignored. Page Erase: Address identifies the page to erase. Row Program: Address identifies the row to program. Word Program: Address identifies the word to program.

### 7.0 INTERRUPT CONTROLLER

Note: This data sheet summarizes the features of the PIC32MX5XX/6XX/7XX family of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to **Section 8. "Interrupts"** (DS60001108) in the *"PIC32 Family Reference Manual"*, which is available from the Microchip web site (www.microchip.com/PIC32).

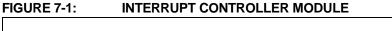

PIC32MX5XX/6XX/7XX devices generate interrupt requests in response to interrupt events from peripheral modules. The interrupt control module exists externally to the CPU logic and prioritizes the interrupt events before presenting them to the CPU.

The Interrupt Controller module includes the following features:

- Up to 96 interrupt sources

- Up to 64 interrupt vectors

- Single and multi-vector mode operations

- · Five external interrupts with edge polarity control

- Interrupt proximity timer

- Seven user-selectable priority levels for each vector

- Four user-selectable sub-priority levels within each priority

- Dedicated shadow set for user-selectable priority level

- Software can generate any interrupt

- User-configurable interrupt vector table location

- · User-configurable interrupt vector spacing

A simplified block diagram of the Interrupt Controller module is illustrated in Figure 7-1.

#### 7.1 **Control Registers**

#### **TABLE 7-2:** INTERRUPT REGISTER MAP FOR PIC32MX534F064H, PIC32MX564F064H, PIC32MX564F128H, PIC32MX575F256H AND PIC32MX575F512H DEVICES

|                             | 1                                                       |               | CJZIWIA |         |            |                               |                               |                             |                    |                  |                       |                       |                       |                       |               |            |        |               | 1             |      |      |

|-----------------------------|---------------------------------------------------------|---------------|---------|---------|------------|-------------------------------|-------------------------------|-----------------------------|--------------------|------------------|-----------------------|-----------------------|-----------------------|-----------------------|---------------|------------|--------|---------------|---------------|------|------|

| ess                         |                                                         |               |         |         |            |                               |                               |                             |                    | Bits             |                       |                       |                       |                       |               |            |        |               |               |      |      |

| Virtual Address<br>(BF88_#) | (BF88_#)<br>(BF88_#)<br>Register<br>Name <sup>(1)</sup> | Bit Range     | 31/15   | 30/14   | 29/13      | 28/12                         | 27/11                         | 26/10                       | 25/9               | 24/8             | 23/7                  | 22/6                  | 21/5                  | 20/4                  | 19/3          | 18/2       | 17/1   | 16/0          | All<br>Resets |      |      |

| 4000                        | INITOON                                                 | 31:16         | —       | _       | _          | _                             | _                             | —                           | -                  | _                | _                     | _                     |                       | _                     | —             | _          | _      | SS0           | 0000          |      |      |

| 1000                        | INTCON                                                  | 15:0          | —       | —       | _          | MVEC                          | —                             |                             | TPC<2:0>           |                  | —                     | —                     | _                     | INT4EP                | INT3EP        | INT2EP     | INT1EP | INT0EP        | 0000          |      |      |

| 1010                        | INTSTAT <sup>(3)</sup>                                  | 31:16         | _       | _       | _          | —                             | _                             | _                           | —                  | —                | —                     | _                     |                       |                       | —             | _          | _      | —             | 0000          |      |      |

| 1010                        | INTSTAT                                                 | 15:0          | —       | —       | —          | —                             | —                             |                             | SRIPL<2:0>         |                  | —                     | —                     |                       |                       | VEC<5:0       | )>         |        |               | 0000          |      |      |

| 1020                        | IPTMR                                                   | 31:16<br>15:0 |         |         |            |                               |                               |                             |                    | IPTMR<3          | 1:0>                  |                       |                       |                       |               |            |        |               | 0000          |      |      |

| 1030                        | IFS0                                                    |               | I2C1MIF | I2C1SIF | I2C1BIF    | U1TXIF<br>SPI3TXIF<br>I2C3MIF | U1RXIF<br>SPI3RXIF<br>I2C3SIF | U1EIF<br>SPI3EIF<br>I2C3BIF | _                  | _                | _                     | OC5IF                 | IC5IF                 | T5IF                  | INT4IF        | OC4IF      | IC4IF  | T4IF          | 0000          |      |      |

|                             |                                                         | 15:0          | INT3IF  | OC3IF   | IC3IF      | T3IF                          | INT2IF                        | OC2IF                       | IC2IF              | T2IF             | INT1IF                | OC1IF                 | IC1IF                 | T1IF                  | INT0IF        | CS1IF      | CS0IF  | CTIF          | 0000          |      |      |

|                             |                                                         | 31:16         | IC3EIF  | IC2EIF  | IC1EIF     | _                             | _                             | CAN1IF                      | USBIF              | FCEIF            | DMA7IF <sup>(2)</sup> | DMA6IF <sup>(2)</sup> | DMA5IF <sup>(2)</sup> | DMA4IF <sup>(2)</sup> | DMA3IF        | DMA2IF     | DMA1IF | DMA0IF        | 0000          |      |      |

| 1040                        | IFS1                                                    |               |         |         |            |                               |                               | U2TXIF                      | U2RXIF             | U2EIF            | <b>U3TXIF</b>         | <b>U3RXIF</b>         | <b>U3EIF</b>          |                       |               |            |        |               |               |      |      |

| 1040                        | 11 31                                                   | 15:0          | RTCCIF  | FSCMIF  | —          | -                             | —                             | SPI4TXIF                    | SPI4RXIF           | SPI4EIF          | SPI2TXIF              | SPI2RXIF              | SPI2EIF               | CMP2IF                | CMP1IF        | PMPIF      | AD1IF  | CNIF          | 0000          |      |      |

|                             |                                                         |               |         |         |            |                               |                               | I2C5MIF                     | I2C5SIF            | I2C5BIF          | I2C4MIF               | I2C4SIF               | I2C4BIF               |                       |               |            |        |               |               |      |      |

| 1050                        | IFS2                                                    | 31:16         | _       | —       | —          | —                             |                               | —                           | _                  | _                | —                     | —                     | _                     | _                     |               |            | —      | —             | 0000          |      |      |

|                             |                                                         | 15:0          | —       | —       | —          | —                             | U5TXIF                        | U5RXIF                      | U5EIF              | U6TXIF           | U6RXIF                | U6EIF                 | U4TXIF                | U4RXIF                | U4EIF         | PMPEIF     | IC5EIF | IC4EIF        | 0000          |      |      |

| 1060                        | IEC0                                                    | 31:16         | 31:16   | 31:16 I | I6 I2C1MIE | C1MIE I2C1SIE                 | I2C1BIE                       | U1TXIE<br>SPI3TXIE          | U1RXIE<br>SPI3RXIE | U1EIE<br>SPI3EIE | _                     | _                     | _                     | OC5IE                 | IC5IE         | T5IE INT4I | INT4IE | OC4IE         | IC4IE         | T4IE | 0000 |

| 1000                        | ILC0                                                    |               |         |         |            | I2C3MIE                       | I2C3SIE                       | I2C3BIE                     |                    |                  |                       |                       |                       |                       |               |            |        |               |               |      |      |

|                             |                                                         | 15:0          | INT3IE  | OC3IE   | IC3IE      | T3IE                          | INT2IE                        | OC2IE                       | IC2IE              | T2IE             | INT1IE                | OC1IE                 | IC1IE                 | T1IE                  | INT0IE        | CS1IE      | CS0IE  | CTIE          | 0000          |      |      |

|                             |                                                         | 31:16         | IC3EIE  | IC2EIE  | IC1EIE     | —                             | —                             | CAN1IE                      | USBIE              | FCEIE            | DMA7IE <sup>(2)</sup> | DMA6IE <sup>(2)</sup> | DMA5IE <sup>(2)</sup> | DMA4IE <sup>(2)</sup> | <b>DMA3IE</b> | DMA2IE     | DMA1IE | <b>DMA0IE</b> | 0000          |      |      |

| 1070                        | IEC1                                                    |               |         |         |            |                               |                               | U2TXIE                      | U2RXIE             | U2EIE            | <b>U3TXIE</b>         | U3RXIE                | U3EIE                 |                       |               |            |        |               |               |      |      |

| 1070                        | 1201                                                    | 15:0          | RTCCIE  | FSCMIE  | —          | —                             | —                             | SPI4TXIE                    | SPI4RXIE           | SPI4EIE          | SPI2TXIE              | SPI2RXIE              | SPI2EIE               | CMP2IE                | CMP1IE        | PMPIE      | AD1IE  | CNIE          | 0000          |      |      |

|                             |                                                         |               |         |         |            |                               |                               | I2C5MIE                     | I2C5SIE            | I2C5BIE          | I2C4MIE               | I2C4SIE               | I2C4BIE               |                       |               |            |        |               |               |      |      |

| 1080                        | IEC2                                                    | 31:16         | —       | —       | —          | _                             | —                             | —                           | —                  | —                | —                     | —                     | _                     | —                     | —             | —          | —      | —             | 0000          |      |      |

|                             |                                                         | 15:0          | —       | —       | —          | —                             | U5TXIE                        | U5RXIE                      | U5EIE              | U6TXIE           | U6RXIE                | U6EIE                 | U4TXIE                | U4RXIE                |               | PMPEIE     | IC5EIE | IC4EIE        | 0000          |      |      |

| 1090                        | IPC0                                                    | 31:16         | —       | —       | —          |                               | INT0IP<2:0>                   |                             | INTOIS             |                  | —                     | —                     | _                     |                       | S1IP<2:0>     |            | CS1IS  |               | 0000          |      |      |

|                             | 90 IFC0                                                 |               | —       | —       | —          |                               | CS0IP<2:0><br>s '0'. Reset v  |                             | CS0IS              |                  | —                     | —                     | —                     | C                     | CTIP<2:0>     |            | CTIS   | <1:0>         | 0000          |      |      |

Except where noted, all registers in this table have corresponding CLR, SET and INV registers at their virtual addresses, plus offsets of 0x4 0x8 and 0xC, respectively. See Section 12.1.1 "CLR, SET Note 1: and INV Registers" for more information.

These bits are not available on PIC32MX534/564/664/764 devices. 2:

This register does not have associated CLR, SET, and INV registers. 3:

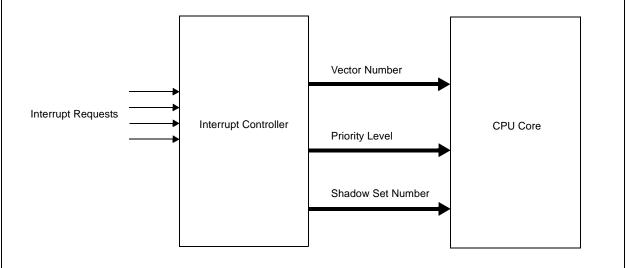

### 8.0 OSCILLATOR CONFIGURATION

Note: This data sheet summarizes the features of the PIC32MX5XX/6XX/7XX family of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to Section 6. "Oscillator" (DS60001112) in the "PIC32 Family Reference Manual", which is available from the Microchip web site (www.microchip.com/PIC32). The Oscillator module has the following features:

- A total of four external and internal oscillator options as clock sources

- On-chip PLL with user-selectable input divider, multiplier and output divider to boost operating frequency on select internal and external oscillator sources

- On-chip user-selectable divisor postscaler on select oscillator sources

- Software-controllable switching between various clock sources

- A Fail-Safe Clock Monitor (FSCM) that detects clock failure and permits safe application recovery or shutdown

- Dedicated On-Chip PLL for USB peripheral

Figure 8-1shows the Oscillator module block diagram.

| Bit<br>Range | Bit<br>31/23/15/7          | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |  |  |

|--------------|----------------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|--|--|--|

| 31:24        | U-0                        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |  |  |  |

| 31.24        | —                          |                   | _                 |                   | _                 | _                 | _                | —                |  |  |  |

| 22.16        | R/W-1                      | R/W-1             | R/W-1             | R/W-1             | R/W-1             | R/W-1             | R/W-1            | R/W-1            |  |  |  |

| 23:16        | CHAIRQ<7:0> <sup>(1)</sup> |                   |                   |                   |                   |                   |                  |                  |  |  |  |

| 15.0         | R/W-1                      | R/W-1             | R/W-1             | R/W-1             | R/W-1             | R/W-1             | R/W-1            | R/W-1            |  |  |  |

| 15:8         | CHSIRQ<7:0> <sup>(1)</sup> |                   |                   |                   |                   |                   |                  |                  |  |  |  |

| 7:0          | S-0                        | S-0               | R/W-0             | R/W-0             | R/W-0             | U-0               | U-0              | U-0              |  |  |  |

| 7.0          | CFORCE                     | CABORT            | PATEN             | SIRQEN            | AIRQEN            | _                 | _                | —                |  |  |  |

#### REGISTER 10-8: DCHxECON: DMA CHANNEL 'x' EVENT CONTROL REGISTER

| Legend:           | S = Settable bit |                      |                    |

|-------------------|------------------|----------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented b  | it, read as '0'    |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared | x = Bit is unknown |

#### bit 31-24 Unimplemented: Read as '0'

| bit 23-16 | CHAIRQ<7:0>: Channel Transfer Abort IRQ bits <sup>(1)</sup>                                                                                                                  |

|-----------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|           | 11111111 = Interrupt 255 will abort any transfers in progress and set CHAIF flag                                                                                             |

|           | •                                                                                                                                                                            |

|           | •                                                                                                                                                                            |

|           | •                                                                                                                                                                            |

|           | 00000001 = Interrupt 1 will abort any transfers in progress and set CHAIF flag<br>00000000 = Interrupt 0 will abort any transfers in progress and set CHAIF flag             |

| bit 15-8  | CHSIRQ<7:0>: Channel Transfer Start IRQ bits <sup>(1)</sup>                                                                                                                  |

|           | 11111111 = Interrupt 255 will initiate a DMA transfer                                                                                                                        |

|           | •                                                                                                                                                                            |

|           | •                                                                                                                                                                            |

|           | •                                                                                                                                                                            |

|           | 00000001 = Interrupt 1 will initiate a DMA transfer<br>00000000 = Interrupt 0 will initiate a DMA transfer                                                                   |

| bit 7     | CFORCE: DMA Forced Transfer bit                                                                                                                                              |

|           | <ul> <li>1 = A DMA transfer is forced to begin when this bit is written to a '1'</li> <li>0 = This bit always reads '0'</li> </ul>                                           |

| bit 6     | CABORT: DMA Abort Transfer bit                                                                                                                                               |

|           | <ul> <li>1 = A DMA transfer is aborted when this bit is written to a '1'</li> <li>0 = This bit always reads '0'</li> </ul>                                                   |

| bit 5     | PATEN: Channel Pattern Match Abort Enable bit                                                                                                                                |

|           | <ul><li>1 = Abort transfer and clear CHEN on pattern match</li><li>0 = Pattern match is disabled</li></ul>                                                                   |

| bit 4     | SIRQEN: Channel Start IRQ Enable bit                                                                                                                                         |

|           | <ul> <li>1 = Start channel cell transfer if an interrupt matching CHSIRQ occurs</li> <li>0 = Interrupt number CHSIRQ is ignored and does not start a transfer</li> </ul>     |

| bit 3     | AIRQEN: Channel Abort IRQ Enable bit                                                                                                                                         |

|           | <ul> <li>1 = Channel transfer is aborted if an interrupt matching CHAIRQ occurs</li> <li>0 = Interrupt number CHAIRQ is ignored and does not terminate a transfer</li> </ul> |

| bit 2-0   | Unimplemented: Read as '0'                                                                                                                                                   |

|           |                                                                                                                                                                              |

Note 1: See Table 7-1: "Interrupt IRQ, Vector and Bit Location" for the list of available interrupt IRQ sources.

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |  |  |  |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|--|--|--|--|

| 31:24        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |  |  |  |  |

| 31.24        | —                 | —                 | —                 | —                 | —                 | —                 |                  | —                |  |  |  |  |

| 23:16        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |  |  |  |  |

| 23.10        | —                 | —                 | —                 | —                 | —                 | —                 |                  | —                |  |  |  |  |

| 15.0         | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |  |  |

| 15:8         | CHCSIZ<15:8>      |                   |                   |                   |                   |                   |                  |                  |  |  |  |  |

| 7.0          | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |  |  |

| 7:0          |                   |                   |                   | CHCSIZ            | /<7:0>            |                   |                  |                  |  |  |  |  |

#### REGISTER 10-16: DCHxCSIZ: DMA CHANNEL 'x' CELL-SIZE REGISTER

#### Legend:

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read as '0' |                    |  |  |  |

|-------------------|------------------|------------------------------------|--------------------|--|--|--|

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared               | x = Bit is unknown |  |  |  |

#### bit 31-16 Unimplemented: Read as '0'

bit 15-0 CHCSIZ<15:0>: Channel Cell-Size bits

111111111111111 = 65,535 bytes transferred on an event

#### REGISTER 10-17: DCHxCPTR: DMA CHANNEL 'x' CELL POINTER REGISTER

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |  |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|--|--|

| 04.04        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |  |  |

| 31:24        | —                 | —                 | —                 | —                 | —                 | —                 | —                | —                |  |  |

| 00.40        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |  |  |

| 23:16        | —                 | —                 | —                 | —                 | —                 | —                 | —                | —                |  |  |

| 45.0         | R-0               | R-0               | R-0               | R-0               | R-0               | R-0               | R-0              | R-0              |  |  |

| 15:8         | CHCPTR<15:8>      |                   |                   |                   |                   |                   |                  |                  |  |  |

| 7.0          | R-0               | R-0               | R-0               | R-0               | R-0               | R-0               | R-0              | R-0              |  |  |

| 7:0          | CHCPTR<7:0>       |                   |                   |                   |                   |                   |                  |                  |  |  |

| Legend:           |                  |                      |                    |

|-------------------|------------------|----------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bi | it, read as '0'    |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared | x = Bit is unknown |

bit 31-16 Unimplemented: Read as '0'

**Note:** When in Pattern Detect mode, this register is reset on a pattern detect.

#### 12.1 Parallel I/O (PIO) Ports

All port pins have three registers (TRIS, LAT and PORT) that are directly associated with their operation.

TRIS is a Data Direction or Tri-State Control register that determines whether a digital pin is an input or an output. Setting a TRISx register bit = 1, configures the corresponding I/O pin as an input; setting a TRISx register bit = 0, configures the corresponding I/O pin as an output. All port I/O pins are defined as inputs after a device Reset. Certain I/O pins are shared with analog peripherals and default to analog inputs after a device Reset.

PORT is a register used to read the current state of the signal applied to the port I/O pins. Writing to a PORTx register performs a write to the port's latch, LATx register, latching the data to the port's I/O pins.

LAT is a register used to write data to the port I/O pins. The LATx Latch register holds the data written to either the LATx or PORTx registers. Reading the LATx Latch register reads the last value written to the corresponding PORT or Latch register.

Not all port I/O pins are implemented on some devices, therefore, the corresponding PORTx, LATx and TRISx register bits will read as zeros.

#### 12.1.1 CLR, SET AND INV REGISTERS

Every I/O module register has a corresponding Clear (CLR), Set (SET) and Invert (INV) register designed to provide fast atomic bit manipulations. As the name of the register implies, a value written to a SET, CLR or INV register effectively performs the implied operation, but only on the corresponding base register and only bits specified as '1' are modified. Bits specified as '0' are not modified.

Reading SET, CLR and INV registers returns undefined values. To see the affects of a write operation to a SET, CLR or INV register, the base register must be read.

| Note: | Using a PORTxINV register to toggle a bit |  |  |  |  |  |  |  |

|-------|-------------------------------------------|--|--|--|--|--|--|--|

|       | is recommended because the operation is   |  |  |  |  |  |  |  |

|       | performed in hardware atomically, using   |  |  |  |  |  |  |  |

|       | fewer instructions, as compared to the    |  |  |  |  |  |  |  |

|       | traditional read-modify-write method, as  |  |  |  |  |  |  |  |

|       | follows:                                  |  |  |  |  |  |  |  |

|       | PORTC $^{ = 0x0001:}$                     |  |  |  |  |  |  |  |

#### 12.1.2 DIGITAL INPUTS

Pins are configured as digital inputs by setting the corresponding TRIS register bits = 1. When configured as inputs, they are either TTL buffers or Schmitt Triggers. Several digital pins share functionality with analog inputs and default to the analog inputs at POR. Setting the corresponding bit in the AD1PCFG register = 1 enables the pin as a digital pin.

The maximum input voltage allowed on the input pins is the same as the maximum VIH specification. Refer to **Section 32.0 "Electrical Characteristics"** for VIH specification details.

| Note: | Analog levels on any pin that is defined as<br>a digital input (including the ANx pins)<br>may cause the input buffer to consume |

|-------|----------------------------------------------------------------------------------------------------------------------------------|

|       | current that exceeds the device specifications.                                                                                  |

#### 12.1.3 ANALOG INPUTS

Certain pins can be configured as analog inputs used by the ADC and comparator modules. Setting the corresponding bits in the AD1PCFG register = 0 enables the pin as an analog input pin and must have the corresponding TRIS bit set = 1 (input). If the TRIS bit is cleared = 0 (output), the digital output level (VOH or VOL) will be converted. Any time a port I/O pin is configured as analog, its digital input is disabled and the corresponding PORTx register bit will read '0'. The AD1PCFG register has a default value of 0x0000; therefore, all pins that share ANx functions are analog (not digital) by default.

#### 12.1.4 DIGITAL OUTPUTS

Pins are configured as digital outputs by setting the corresponding TRIS register bits = 0. When configured as digital outputs, these pins are CMOS drivers or can be configured as open-drain outputs by setting the corresponding bits in the Open-Drain Configuration (ODCx) register.

The open-drain feature allows generation of outputs higher than VDD (e.g., 5V) on any desired 5V tolerant pins by using external pull-up resistors. The maximum open-drain voltage allowed is the same as the maximum VIH specification.

See the **"Device Pin Tables"** section for the available pins and their functionality.

#### 12.1.5 ANALOG OUTPUTS

Certain pins can be configured as analog outputs, such as the CVREF output voltage used by the comparator module. Configuring the comparator reference module to provide this output will present the analog output voltage on the pin, independent of the TRIS register setting for the corresponding pin.

#### 12.1.6 INPUT CHANGE NOTIFICATION

The input change notification function of the I/O ports (CNx) allows devices to generate interrupt requests in response to change-of-state on selected pin.

Each CNx pin also has a weak pull-up, which acts as a current source connected to the pin. The pull-ups are enabled by setting the corresponding bit in the CNPUE register.

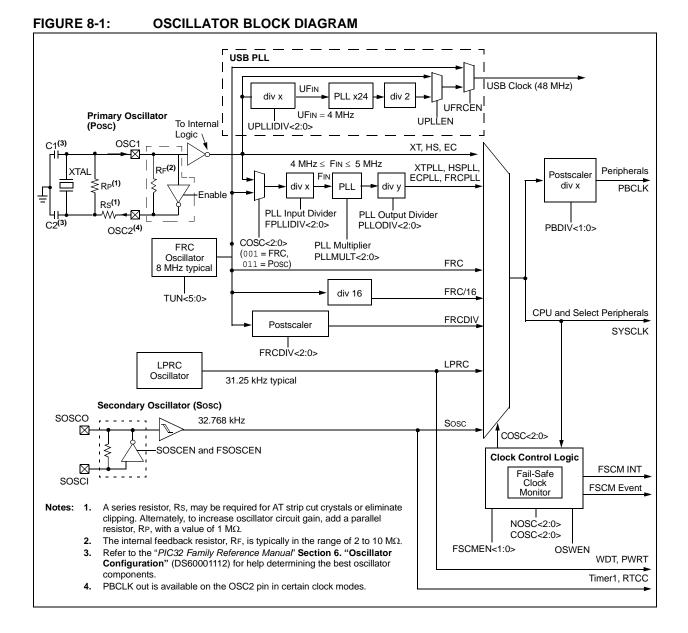

#### 13.0 TIMER1

Note: This data sheet summarizes the features of the PIC32MX5XX/6XX/7XX family of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to **Section 14. "Timers"** (DS60001105) in the *"PIC32 Family Reference Manual"*, which is available from the Microchip web site (www.microchip.com/PIC32).

This family of PIC32 devices features one synchronous/ asynchronous 16-bit timer that can operate as a free-running interval timer for various timing applications and counting external events. This timer can also be used with the low-power Secondary Oscillator (Sosc) for Real-Time Clock (RTC) applications. The following modes are supported:

- Synchronous Internal Timer

- Synchronous Internal Gated Timer

- Synchronous External Timer

- Asynchronous External Timer

#### FIGURE 13-1: TIMER1 BLOCK DIAGRAM

#### 13.1 Additional Supported Features

- Selectable clock prescaler

- Timer operation during Idle and Sleep mode

- Fast bit manipulation using CLR, SET and INV registers

- Asynchronous mode can be used with the Sosc to function as a Real-Time Clock (RTC)

A simplified block diagram of the Timer1 module is illustrated in Figure 13-1.

#### 20.1 Control Registers

#### TABLE 20-1: UART1 THROUGH UART6 REGISTER MAP

|                             |                              |           | Bits   |        |        |       |        |       |       |        |        |         |       |          |          |      |        |       |            |

|-----------------------------|------------------------------|-----------|--------|--------|--------|-------|--------|-------|-------|--------|--------|---------|-------|----------|----------|------|--------|-------|------------|

| Virtual Address<br>(BF80_#) | Register<br>Name             | Bit Range | 31/15  | 30/14  | 29/13  | 28/12 | 27/11  | 26/10 | 25/9  | 24/8   | 23/7   | 22/6    | 21/5  | 20/4     | 19/3     | 18/2 | 17/1   | 16/0  | All Resets |

| 6000                        | U1MODE <sup>(1)</sup>        | 31:16     |        |        | —      |       |        |       |       | _      |        | _       |       | _        |          |      |        |       | 0000       |

| 0000                        | UTWODE: /                    | 15:0      | ON     | _      | SIDL   | IREN  | RTSMD  | _     | UEN   | <1:0>  | WAKE   | LPBACK  | ABAUD | RXINV    | BRGH     | PDSE | _<1:0> | STSEL | 0000       |

| 6010                        | U1STA <sup>(1)</sup>         | 31:16     | _      |        |        |       | —      | _     |       | ADM_EN |        |         |       | ADDR     | <7:0>    |      |        | -     | 0000       |

| 0010                        | UIUIA                        | 15:0      | UTXISE | L<1:0> | UTXINV | URXEN | UTXBRK | UTXEN | UTXBF | TRMT   | URXISE | EL<1:0> | ADDEN | RIDLE    | PERR     | FERR | OERR   | URXDA | 0110       |

| 6020                        | U1TXREG                      | 31:16     | —      | —      | —      | _     | —      | —     | —     | —      | —      | —       | —     | —        | —        | —    | —      | —     | 0000       |

| 0020                        | OTIMALO                      | 15:0      | —      | —      | —      | _     | —      | —     | —     | TX8    |        |         |       | Transmit | Register |      |        |       | 0000       |

| 6030                        | U1RXREG                      | 31:16     |        | _      | _      | _     | —      | _     | _     | _      |        | —       | —     | —        | —        | —    | —      | _     | 0000       |

| 0000                        | OHOULEO                      | 15:0      |        | _      | _      | _     | —      | _     | _     | RX8    |        |         |       | Receive  | Register |      |        |       | 0000       |

| 6040                        | U1BRG <sup>(1)</sup>         | 31:16     | —      | _      | —      | —     | —      | —     | _     | —      | -      | _       | —     | _        | _        | —    | _      | —     | 0000       |

|                             |                              | 15:0      |        |        |        |       |        |       |       | BRG<   | 15:0>  |         |       |          |          |      |        |       | 0000       |

| 6200                        | U4MODE <sup>(1)</sup>        | 31:16     |        |        | _      | _     | _      | _     |       | —      |        | —       | _     |          | _        | —    | —      | —     | 0000       |

|                             |                              | 15:0      | ON     | _      | SIDL   | IREN  | _      | _     | _     | —      | WAKE   | LPBACK  | ABAUD | RXINV    | BRGH     | PDSE | _<1:0> | STSEL | 0000       |

| 6210                        | 10 U4STA <sup>(1)</sup> 31:1 |           |        | —      | _      | —     | —      | —     | —     | ADM_EN |        |         |       | ADDR     |          | 1    |        | r     | 0000       |

|                             |                              | 15:0      | UTXISE | L<1:0> | UTXINV | URXEN | UTXBRK | UTXEN | UTXBF | TRMT   | URXIS  | L<1:0>  | ADDEN | RIDLE    | PERR     | FERR | OERR   | URXDA | 0110       |

| 6220                        | U4TXREG                      | 31:16     | —      |        |        |       | _      | _     |       | —      |        |         | —     |          | —        | —    | —      | _     | 0000       |

|                             |                              | 15:0      | —      | —      | _      | —     | —      | —     | —     | TX8    |        |         |       | Transmit | Register |      |        |       | 0000       |

| 6230                        | U4RXREG                      | 31:16     | —      |        |        |       | _      | _     |       | —      |        |         | —     |          | —        | —    | —      | _     | 0000       |

|                             |                              | 15:0      | —      |        |        |       | _      | _     |       | RX8    |        |         |       | Receive  | Register |      |        |       | 0000       |

| 6240                        | U4BRG <sup>(1)</sup>         | 31:16     |        | —      | —      | —     | —      | —     | —     | —      |        |         | —     |          | —        | —    | —      | _     | 0000       |

|                             |                              | 15:0      |        |        |        |       | 1      |       |       | BRG<   | 15:0>  | 1       |       | 1        |          |      |        | 1     | 0000       |

| 6400                        | U3MODE <sup>(1)</sup>        | 31:16     | —      | _      | —      | —     | —      | —     | _     | —      | -      | —       | —     | _        | _        | -    | _      | —     | 0000       |

|                             |                              | 15:0      | ON     |        | SIDL   | IREN  | RTSMD  |       | UEN   |        | WAKE   | LPBACK  | ABAUD | RXINV    | BRGH     | PDSE | _<1:0> | STSEL | 0000       |

| 6410                        | U3STA <sup>(1)</sup>         | 31:16     | —      | _      | —      | —     | —      | —     | _     | ADM_EN |        |         |       | ADDR     |          | 1    |        | I.    | 0000       |

|                             |                              | 15:0      | UTXISE | L<1:0> | UTXINV | URXEN | UTXBRK | UTXEN | UTXBF | TRMT   | URXIS  | EL<1:0> | ADDEN | RIDLE    | PERR     | FERR | OERR   | URXDA | 0110       |

| 6420                        | U3TXREG                      | 31:16     | —      |        |        |       | _      | _     |       | —      |        |         | —     |          | —        | —    | —      | _     | 0000       |

|                             |                              | 15:0      | —      |        |        |       | _      | _     |       | TX8    |        |         |       | Transmit | Register |      |        |       | 0000       |

| 6430                        | <b>U3RXREG</b>               | 31:16     | _      | _      | -      | _     | —      | —     | _     | —      | -      | _       | —     | —        | _        | —    | _      | —     | 0000       |

|                             |                              | 15:0      | —      |        |        |       | _      | _     |       | RX8    |        |         |       | Receive  | Register |      |        |       | 0000       |