Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XE

| Details                    |                                                                                  |

|----------------------------|----------------------------------------------------------------------------------|

| Product Status             | Active                                                                           |

| Core Processor             | MIPS32® M4K™                                                                     |

| Core Size                  | 32-Bit Single-Core                                                               |

| Speed                      | 80MHz                                                                            |

| Connectivity               | Ethernet, I <sup>2</sup> C, SPI, UART/USART, USB OTG                             |

| Peripherals                | Brown-out Detect/Reset, DMA, POR, PWM, WDT                                       |

| Number of I/O              | 83                                                                               |

| Program Memory Size        | 256KB (256K x 8)                                                                 |

| Program Memory Type        | FLASH                                                                            |

| EEPROM Size                | -                                                                                |

| RAM Size                   | 64K × 8                                                                          |

| Voltage - Supply (Vcc/Vdd) | 2.3V ~ 3.6V                                                                      |

| Data Converters            | A/D 16x10b                                                                       |

| Oscillator Type            | Internal                                                                         |

| Operating Temperature      | -40°C ~ 105°C (TA)                                                               |

| Mounting Type              | Surface Mount                                                                    |

| Package / Case             | 121-TFBGA                                                                        |

| Supplier Device Package    | 121-TFBGA (10x10)                                                                |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic32mx675f256l-80v-bg |

|                            |                                                                                  |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

#### TABLE 7: **PIN NAMES FOR 100-PIN USB AND CAN DEVICES**

#### **100-PIN TQFP (TOP VIEW)**

#### PIC32MX534F064L PIC32MX564F064L PIC32MX564F128L PIC32MX575F512L PIC32MX575F256L

100

|       |                              |       | 1                              |

|-------|------------------------------|-------|--------------------------------|

| Pin # | Full Pin Name                | Pin # | Full Pin Name                  |

| 1     | RG15                         | 36    | Vss                            |

| 2     | VDD                          | 37    | Vdd                            |

| 3     | PMD5/RE5                     | 38    | TCK/RA1                        |

| 4     | PMD6/RE6                     | 39    | AC1TX/SCK4/U5TX/U2RTS/RF13     |

| 5     | PMD7/RE7                     | 40    | AC1RX/SS4/U5RX/U2CTS/RF12      |

| 6     | T2CK/RC1                     | 41    | AN12/PMA11/RB12                |

| 7     | T3CK/RC2                     | 42    | AN13/PMA10/RB13                |

| 8     | T4CK/RC3                     | 43    | AN14/PMALH/PMA1/RB14           |

| 9     | T5CK/SDI1/RC4                | 44    | AN15/OCFB/PMALL/PMA0/CN12/RB15 |

| 10    | SCK2/U6TX/U3RTS/PMA5/CN8/RG6 | 45    | Vss                            |

| 11    | SDA4/SDI2/U3RX/PMA4/CN9/RG7  | 46    | VDD                            |

| 12    | SCL4/SDO2/U3TX/PMA3/CN10/RG8 | 47    | SS3/U4RX/U1CTS/CN20/RD14       |

| 13    | MCLR                         | 48    | SCK3/U4TX/U1RTS/CN21/RD15      |

| 14    | SS2/U6RX/U3CTS/PMA2/CN11/RG9 | 49    | SDA5/SDI4/U2RX/PMA9/CN17/RF4   |

| 15    | Vss                          | 50    | SCL5/SDO4/U2TX/PMA8/CN18/RF5   |

| 16    | VDD                          | 51    | USBID/RF3                      |

| 17    | TMS/RA0                      | 52    | SDA3/SDI3/U1RX/RF2             |

| 18    | INT1/RE8                     | 53    | SCL3/SDO3/U1TX/RF8             |

| 19    | INT2/RE9                     | 54    | VBUS                           |

| 20    | AN5/C1IN+/VBUSON/CN7/RB5     | 55    | VUSB3V3                        |

| 21    | AN4/C1IN-/CN6/RB4            | 56    | D-/RG3                         |

| 22    | AN3/C2IN+/CN5/RB3            | 57    | D+/RG2                         |

| 23    | AN2/C2IN-/CN4/RB2            | 58    | SCL2/RA2                       |

| 24    | PGEC1/AN1/CN3/RB1            | 59    | SDA2/RA3                       |

| 25    | PGED1/AN0/CN2/RB0            | 60    | TDI/RA4                        |

| 26    | PGEC2/AN6/OCFA/RB6           | 61    | TDO/RA5                        |

| 27    | PGED2/AN7/RB7                | 62    | Vdd                            |

| 28    | VREF-/CVREF-/PMA7/RA9        | 63    | OSC1/CLKI/RC12                 |

| 29    | VREF+/CVREF+/PMA6/RA10       | 64    | OSC2/CLKO/RC15                 |

| 30    | AVDD                         | 65    | Vss                            |

| 31    | AVss                         | 66    | SCL1/INT3/RA14                 |

| 32    | AN8/C1OUT/RB8                | 67    | SDA1/INT4/RA15                 |

| 33    | AN9/C2OUT/RB9                | 68    | RTCC/IC1/RD8                   |

| 34    | AN10/CVREFOUT/PMA13/RB10     | 69    | SS1/IC2/RD9                    |

| 35    | AN11/PMA12/RB11              | 70    | SCK1/IC3/PMCS2/PMA15/RD10      |

Shaded pins are 5V tolerant. Note 1:

# PIC32MX5XX/6XX/7XX

#### REGISTER 10-14: DCHxSPTR: DMA CHANNEL 'x' SOURCE POINTER REGISTER

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |  |  |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|--|--|--|

| 31:24        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |  |  |  |

| 31.24        |                   | —                 | _                 |                   | _                 | _                 |                  |                  |  |  |  |

| 23:16        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |  |  |  |

| 23.10        |                   | —                 | _                 | _                 | _                 | _                 | —                | —                |  |  |  |

| 45.0         | R-0               | R-0               | R-0               | R-0               | R-0               | R-0               | R-0              | R-0              |  |  |  |

| 15:8         | CHSPTR<15:8>      |                   |                   |                   |                   |                   |                  |                  |  |  |  |

| 7.0          | R-0               | R-0               | R-0               | R-0               | R-0               | R-0               | R-0              | R-0              |  |  |  |

| 7:0          |                   |                   |                   | CHSPTF            | R<7:0>            |                   |                  |                  |  |  |  |

#### Legend:

| Logona.           |                  |                                    |                    |  |  |  |

|-------------------|------------------|------------------------------------|--------------------|--|--|--|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read as '0' |                    |  |  |  |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared               | x = Bit is unknown |  |  |  |

#### bit 31-16 Unimplemented: Read as '0'

bit 15-0 CHSPTR<15:0>: Channel Source Pointer bits

111111111111111 = Points to byte 65,535 of the source

Note: When in Pattern Detect mode, this register is reset on a pattern detect.

#### Bit Bit Bit Bit Bit Bit Bit Bit Bit Range 31/23/15/7 30/22/14/6 29/21/13/5 28/20/12/4 27/19/11/3 26/18/10/2 25/17/9/1 24/16/8/0 U-0 U-0 U-0 U-0 U-0 U-0 U-0 U-0 31:24 \_\_\_\_ \_\_\_ \_\_\_\_ \_\_\_\_ \_\_\_\_ \_\_\_\_ U-0 U-0 U-0 U-0 U-0 U-0 U-0 U-0 23:16 R-0 R-0 R-0 R-0 R-0 R-0 R-0 R-0 15:8 CHDPTR<15:8> R-0 R-0 R-0 R-0 R-0 R-0 R-0 R-0 7:0 CHDPTR<7:0>

#### **REGISTER 10-15: DCHxDPTR: DMA CHANNEL 'x' DESTINATION POINTER REGISTER**

#### Legend:

| 3                 |                  |                                    |                    |  |  |  |

|-------------------|------------------|------------------------------------|--------------------|--|--|--|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read as '0' |                    |  |  |  |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared               | x = Bit is unknown |  |  |  |

bit 31-16 Unimplemented: Read as '0'

bit 15-0 CHDPTR<15:0>: Channel Destination Pointer bits

111111111111111 = Points to byte 65,535 of the destination

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|--|

| 31:24        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |  |

| 31.24        |                   |                   |                   |                   | _                 | _                 |                  |                  |  |

| 22:46        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |  |

| 23:16        |                   |                   |                   |                   | _                 | _                 |                  | -                |  |

| 15:8         | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |  |

| 15.0         |                   |                   |                   |                   | _                 | _                 |                  | -                |  |

| 7:0          | U-0               | U-0               | U-0               | U-0               | U-0               | R-0               | R-0              | R-0              |  |

| 7:0          |                   | _                 | _                 | _                 | _                 |                   | FRMH<2:0>        |                  |  |

#### REGISTER 11-14: U1FRMH: USB FRAME NUMBER HIGH REGISTER

#### Legend:

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, r | ead as '0'         |  |

|-------------------|------------------|--------------------------|--------------------|--|

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared     | x = Bit is unknown |  |

bit 31-3 Unimplemented: Read as '0'

bit 2-0 **FRMH<2:0>:** Upper 3 bits of the Frame Numbers bits These register bits are updated with the current frame number whenever a SOF TOKEN is received.

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|--|

| 31:24        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |  |

| 31.24        |                   | _                 |                   | —                 |                   | _                 |                  | —                |  |

| 23:16        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |  |

| 23.10        | —                 | _                 | —                 | —                 | —                 | _                 | —                | —                |  |

| 15:8         | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |  |

| 15.6         | —                 | _                 | —                 | —                 | —                 | _                 | —                | —                |  |

| 7.0          | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |

| 7:0          |                   | PID<              | :3:0>             |                   | EP<3:0>           |                   |                  |                  |  |

#### REGISTER 11-15: U1TOK: USB TOKEN REGISTER

| Legend:           |                  |                      |                    |

|-------------------|------------------|----------------------|--------------------|

| R = Readable bit  | t, read as '0'   |                      |                    |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared | x = Bit is unknown |

bit 31-8 Unimplemented: Read as '0'

bit 7-4 PID<3:0>: Token Type Indicator bits<sup>(1)</sup> 1101 = SETUP (TX) token type transaction 1001 = IN (RX) token type transaction 0001 = OUT (TX) token type transaction Note: All other values not listed, are Reserved and must not be used.

#### bit 3-0 **EP<3:0>:** Token Command Endpoint Address bits The four bit value must specify a valid endpoint.

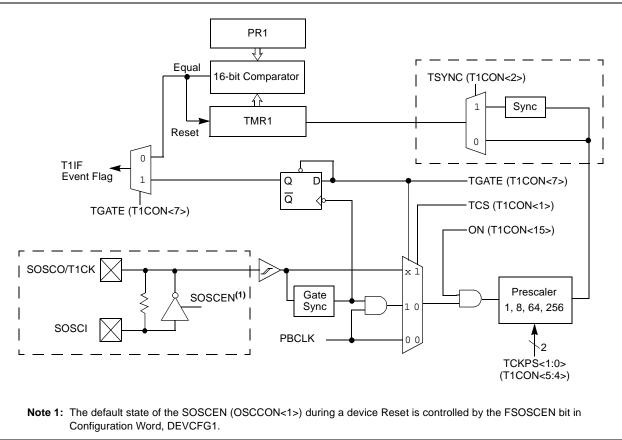

## 13.0 TIMER1

Note: This data sheet summarizes the features of the PIC32MX5XX/6XX/7XX family of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to **Section 14. "Timers"** (DS60001105) in the *"PIC32 Family Reference Manual"*, which is available from the Microchip web site (www.microchip.com/PIC32).

This family of PIC32 devices features one synchronous/ asynchronous 16-bit timer that can operate as a free-running interval timer for various timing applications and counting external events. This timer can also be used with the low-power Secondary Oscillator (Sosc) for Real-Time Clock (RTC) applications. The following modes are supported:

- Synchronous Internal Timer

- Synchronous Internal Gated Timer

- Synchronous External Timer

- Asynchronous External Timer

#### FIGURE 13-1: TIMER1 BLOCK DIAGRAM

#### 13.1 Additional Supported Features

- Selectable clock prescaler

- Timer operation during Idle and Sleep mode

- Fast bit manipulation using CLR, SET and INV registers

- Asynchronous mode can be used with the Sosc to function as a Real-Time Clock (RTC)

A simplified block diagram of the Timer1 module is illustrated in Figure 13-1.

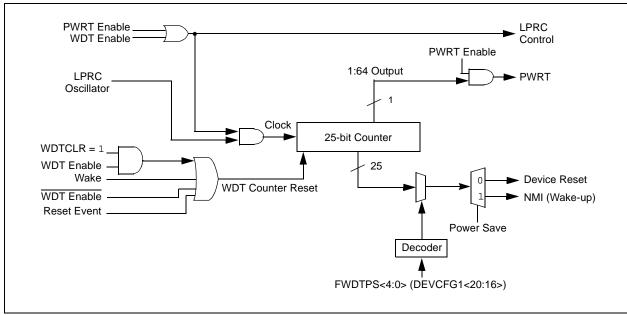

## 15.0 WATCHDOG TIMER (WDT)

Note: This data sheet summarizes the features of the PIC32MX5XX/6XX/7XX family of devices. However, it is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to Section 8. "Watchdog Timer and Power-up Timer" in the "PIC32 (DS60001114) Family Reference Manual", which is available from the Microchip web site (www.microchip.com/PIC32).

This section describes the operation of the WDT and Power-up Timer of the PIC32MX5XX/6XX/7XX.

The WDT, when enabled, operates from the internal Low-Power Oscillator (LPRC) clock source and can be used to detect system software malfunctions by resetting the device if the WDT is not cleared periodically in software. Various WDT time-out periods can be selected using the WDT postscaler. The WDT can also be used to wake the device from Sleep or Idle mode.

The following are key features of the WDT module:

- Configuration or software controlled

- User-configurable time-out period

- Can wake the device from Sleep or Idle mode

#### FIGURE 15-1: WATCHDOG TIMER AND POWER-UP TIMER BLOCK DIAGRAM

### 15.1 Control Registers

## TABLE 15-1: WATCHDOG TIMER REGISTER MAP

| ess                      |                                 |           |       | Bits  |       |       |       |       |      |      |      |      | (2)  |           |      |      |      |        |            |

|--------------------------|---------------------------------|-----------|-------|-------|-------|-------|-------|-------|------|------|------|------|------|-----------|------|------|------|--------|------------|

| Virtual Addr<br>(BF80_#) | Register<br>Name <sup>(1)</sup> | Bit Range | 31/15 | 30/14 | 29/13 | 28/12 | 27/11 | 26/10 | 25/9 | 24/8 | 23/7 | 22/6 | 21/5 | 20/4      | 19/3 | 18/2 | 17/1 | 16/0   | All Resets |

| 0000                     | WDTOON                          | 31:16     | _     | —     | —     | —     | _     | _     | _    | _    | _    | _    | —    | —         | _    | —    | _    | _      | 0000       |

| 0000                     | WDTCON                          | 15:0      | ON    | _     |       | _     | _     | _     | _    | _    | _    |      | S    | WDTPS<4:0 | )>   |      | _    | WDTCLR | 0000       |

Legend: x = unknown value on Reset; -- = unimplemented, read as '0'. Reset values are shown in hexadecimal.

Note 1: All registers in this table have corresponding CLR, SET and INV registers at their virtual addresses, plus offsets of 0x4, 0x8 and 0xC, respectively. See Section 12.1.1 "CLR, SET and INV Registers" for more information.

2: Reset values are dependent on the DEVCFGx Configuration bits and the type of Reset.

| Bit Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

|-----------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|

| 24.24     | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 31:24     | _                 | —                 |                   |                   | _                 |                   |                  |                  |

| 00.40     | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 23:16     | _                 | —                 | _                 | _                 | _                 | _                 | _                | _                |

| 45.0      | R/W-0             | U-0               | R/W-0             | U-0               | U-0               | U-0               | R/W-0            | R/W-0            |

| 15:8      | ON <sup>(1)</sup> | —                 | SIDL              | _                 | _                 | _                 | FEDGE            | C32              |

| 7:0       | R/W-0             | R/W-0             | R/W-0             | R-0               | R-0               | R/W-0             | R/W-0            | R/W-0            |

| 7:0       | ICTMR             | ICI<              | 1:0>              | ICOV              | ICBNE             |                   | ICM<2:0>         |                  |

#### REGISTER 16-1: ICxCON: INPUT CAPTURE 'x' CONTROL REGISTER

## Legend:

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read as '0' |                    |  |  |

|-------------------|------------------|------------------------------------|--------------------|--|--|

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared               | x = Bit is unknown |  |  |

| bit 31-16 | Unimplemented: Read as '0'                                                                                                                                |

|-----------|-----------------------------------------------------------------------------------------------------------------------------------------------------------|

| bit 15    | ON: Input Capture Module Enable bit <sup>(1)</sup>                                                                                                        |

|           | <ul> <li>1 = Module is enabled</li> <li>0 = Disable and reset module, disable clocks, disable interrupt generation and allow SFR modifications</li> </ul> |

| bit 14    | Unimplemented: Read as '0'                                                                                                                                |

| bit 13    | SIDL: Stop in Idle Control bit                                                                                                                            |

|           | <ul><li>1 = Halt in Idle mode</li><li>0 = Continue to operate in Idle mode</li></ul>                                                                      |

| bit 12-10 | Unimplemented: Read as '0'                                                                                                                                |

| bit 9     | FEDGE: First Capture Edge Select bit (only used in mode 6, ICM<2:0> = 110)                                                                                |

|           | <ul> <li>1 = Capture rising edge first</li> <li>0 = Capture falling edge first</li> </ul>                                                                 |

| bit 8     | C32: 32-bit Capture Select bit                                                                                                                            |

|           | <ul><li>1 = 32-bit timer resource capture</li><li>0 = 16-bit timer resource capture</li></ul>                                                             |

| bit 7     | ICTMR: Timer Select bit (Does not affect timer selection when C32 (ICxCON<8>) is '1')                                                                     |

|           | <ul> <li>1 = Timer2 is the counter source for capture</li> <li>0 = Timer3 is the counter source for capture</li> </ul>                                    |

| bit 6-5   | ICI<1:0>: Interrupt Control bits                                                                                                                          |

|           | 11 = Interrupt on every fourth capture event                                                                                                              |

|           | <ul> <li>10 = Interrupt on every third capture event</li> <li>01 = Interrupt on every second capture event</li> </ul>                                     |

|           | 00 = Interrupt on every capture event                                                                                                                     |

| bit 4     | ICOV: Input Capture Overflow Status Flag bit (read-only)                                                                                                  |

|           | <ul> <li>1 = Input capture overflow is occurred</li> <li>0 = No input capture overflow is occurred</li> </ul>                                             |

| bit 3     | ICBNE: Input Capture Buffer Not Empty Status bit (read-only)                                                                                              |

|           | <ul> <li>1 = Input capture buffer is not empty; at least one more capture value can be read</li> <li>0 = Input capture buffer is empty</li> </ul>         |

|           |                                                                                                                                                           |

**Note 1:** When using the 1:1 PBCLK divisor, the user's software should not read/write the peripheral's SFRs in the SYSCLK cycle immediately following the instruction that clears the module's ON bit.

| REGIST    | ER 18-1: SPIxCON: SPI CONTROL REGISTER (CONTINUED)                                                                                                                                              |

|-----------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| bit 15    | <b>ON:</b> SPI Peripheral On bit <sup>(1)</sup>                                                                                                                                                 |

|           | 1 = SPI Peripheral is enabled                                                                                                                                                                   |

| bit 11    | 0 = SPI Peripheral is disabled                                                                                                                                                                  |

| bit 14    | Unimplemented: Read as '0'                                                                                                                                                                      |

| bit 13    | SIDL: Stop in Idle Mode bit<br>1 = Discontinue operation when CPU enters in Idle mode                                                                                                           |

|           | 0 = Continue operation in Idle mode                                                                                                                                                             |

| bit 12    | <b>DISSDO:</b> Disable SDOx pin bit                                                                                                                                                             |

|           | 1 = SDOx pin is not used by the module (pin is controlled by associated PORT register)                                                                                                          |

|           | 0 = SDOx pin is controlled by the module                                                                                                                                                        |

| bit 11-10 | MODE<32,16>: 32/16-Bit Communication Select bits                                                                                                                                                |

|           | MODE32 MODE16 Communication                                                                                                                                                                     |

|           | 1 x 32-bit<br>0 1 16-bit                                                                                                                                                                        |

|           | 0 1 16-bit<br>0 0 8-bit                                                                                                                                                                         |

| bit 9     | SMP: SPI Data Input Sample Phase bit                                                                                                                                                            |

|           | Master mode (MSTEN = 1):                                                                                                                                                                        |

|           | 1 = Input data sampled at end of data output time                                                                                                                                               |

|           | 0 = Input data sampled at middle of data output time                                                                                                                                            |

|           | Slave mode (MSTEN = 0):                                                                                                                                                                         |

|           | SMP value is ignored when SPI is used in Slave mode. The module always uses SMP = 0.                                                                                                            |

| bit 8     | CKE: SPI Clock Edge Select bit <sup>(3)</sup>                                                                                                                                                   |

|           | 1 = Serial output data changes on transition from active clock state to Idle clock state (see CKP bit)                                                                                          |

| h:+ 7     | 0 = Serial output data changes on transition from Idle clock state to active clock state (see CKP bit)                                                                                          |

| bit 7     | SSEN: Slave Select Enable (Slave mode) bit<br>1 = SSx pin used for Slave mode                                                                                                                   |

|           | 0 = SSx pin not used for Slave mode (pin is controlled by port function)                                                                                                                        |

| bit 6     | <b>CKP:</b> Clock Polarity Select bit                                                                                                                                                           |

|           | 1 = Idle state for clock is a high level; active state is a low level                                                                                                                           |

|           | 0 = Idle state for clock is a low level; active state is a high level                                                                                                                           |

| bit 5     | MSTEN: Master Mode Enable bit                                                                                                                                                                   |

|           | 1 = Master mode<br>0 = Slave mode                                                                                                                                                               |

| bit 4     | Unimplemented: Read as '0'                                                                                                                                                                      |

| bit 3-2   | STXISEL<1:0>: SPI Transmit Buffer Empty Interrupt Mode bits                                                                                                                                     |

| Dit 0-2   | 11 = Interrupt is generated when the buffer is not full (has one or more empty elements)                                                                                                        |

|           | 10 = Interrupt is generated when the buffer is empty by one-half or more                                                                                                                        |

|           | 01 = Interrupt is generated when the buffer is completely empty                                                                                                                                 |

|           | 00 = Interrupt is generated when the last transfer is shifted out of SPISR and transmit operations are                                                                                          |

|           | complete                                                                                                                                                                                        |

| bit 1-0   | SRXISEL<1:0>: SPI Receive Buffer Full Interrupt Mode bits<br>11 = Interrupt is generated when the buffer is full                                                                                |

|           | 10 = Interrupt is generated when the buffer is full by one-half or more                                                                                                                         |

|           | 01 = Interrupt is generated when the buffer is not empty                                                                                                                                        |

|           | 00 = Interrupt is generated when the last word in the receive buffer is read (i.e., buffer is empty)                                                                                            |

|           | When using the 1.1 DPOLK divisor the user's activises should not used anywrite the mentation " OPP i                                                                                            |

| Note 1:   | When using the 1:1 PBCLK divisor, the user's software should not read or write the peripheral's SFRs in the SYSCLK cycle immediately following the instruction that clears the module's ON bit. |

| 2:        | This bit can only be written when the ON bit = $0$ .                                                                                                                                            |

| 3:        | This bit is not used in the Framed SPI mode. The user should program this bit to '0' for the Framed SPI                                                                                         |

| 0.        | mode (FRMEN = 1).                                                                                                                                                                               |

|           |                                                                                                                                                                                                 |

#### I2CxSTAT: I<sup>2</sup>C STATUS REGISTER (CONTINUED) REGISTER 19-2: **D\_A:** Data/Address bit (when operating as I<sup>2</sup>C slave) bit 5 This bit is cleared by hardware upon a device address match, and is set by hardware by reception of the slave byte. 1 = Indicates that the last byte received was data 0 = Indicates that the last byte received was device address bit 4 P: Stop bit This bit is set or cleared by hardware when a Start, Repeated Start, or Stop condition is detected. 1 = Indicates that a Stop bit has been detected last 0 = Stop bit was not detected last bit 3 S: Start bit This bit is set or cleared by hardware when a Start, Repeated Start, or Stop condition is detected. 1 = Indicates that a Start (or Repeated Start) bit has been detected last 0 = Start bit was not detected last **R\_W:** Read/Write Information bit (when operating as I<sup>2</sup>C slave) bit 2 This bit is set or cleared by hardware after reception of an I<sup>2</sup>C device address byte. 1 = Read – indicates data transfer is output from slave 0 = Write - indicates data transfer is input to slave **RBF:** Receive Buffer Full Status bit bit 1 This bit is set by hardware when the I2CxRCV register is written with a received byte, and is cleared by hardware when software reads I2CxRCV. 1 = Receive complete, I2CxRCV is full 0 = Receive not complete, I2CxRCV is empty bit 0 TBF: Transmit Buffer Full Status bit This bit is set by hardware when software writes to the I2CxTRN register, and is cleared by hardware upon completion of data transmission.

1 = Transmit in progress, I2CxTRN is full

0 = Transmit complete, I2CxTRN is empty

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6   | Bit<br>29/21/13/5  | Bit<br>28/20/12/4 | Bit<br>27/19/11/3   | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

|--------------|-------------------|---------------------|--------------------|-------------------|---------------------|-------------------|------------------|------------------|

| 24.24        | U-0               | U-0                 | U-0                | U-0               | U-0                 | U-0               | U-0              | U-0              |

| 31:24        |                   | _                   | _                  |                   | —                   | _                 |                  | —                |

| 00.40        | U-0               | U-0                 | U-0                | U-0               | U-0                 | U-0               | U-0              | U-0              |

| 23:16        | —                 | _                   | _                  | -                 | —                   | _                 | —                | —                |

| 45.0         | R/W-0             | U-0                 | R/W-0              | R/W-0             | R/W-0               | R/W-0             | R/W-0            | R/W-0            |

| 15:8         | 0N <sup>(1)</sup> | _                   | SIDL               | ADRML             | JX<1:0>             | PMPTTL            | PTWREN           | PTRDEN           |

| 7.0          | R/W-0             | R/W-0               | R/W-0              | U-0               | R/W-0               | U-0               | R/W-0            | R/W-0            |

| 7:0          | CSF<              | 1:0> <sup>(2)</sup> | ALP <sup>(2)</sup> | _                 | CS1P <sup>(2)</sup> |                   | WRSP             | RDSP             |

#### REGISTER 21-1: PMCON: PARALLEL PORT CONTROL REGISTER

#### Legend:

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, r | read as '0'        |

|-------------------|------------------|--------------------------|--------------------|

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared     | x = Bit is unknown |

#### bit 31-16 Unimplemented: Read as '0'

- bit 15 **ON:** Parallel Master Port Enable bit<sup>(1)</sup>

- 1 = PMP is enabled

- 0 = PMP is disabled, no off-chip access performed

- bit 14 Unimplemented: Read as '0'

- bit 13 **SIDL:** Stop in Idle Mode bit

- 1 = Discontinue module operation when device enters Idle mode

- 0 = Continue module operation when device enters Idle mode

#### bit 12-11 ADRMUX<1:0>: Address/Data Multiplexing Selection bits

- 11 = All 16 bits of address are multiplexed on PMD<15:0> pins

- 10 = All 16 bits of address are multiplexed on PMD<7:0> pins

- 01 = Lower 8 bits of address are multiplexed on PMD<7:0> pins, upper bits are on PMA<15:8>

- 00 = Address and data appear on separate pins

- bit 10 **PMPTTL:** PMP Module TTL Input Buffer Select bit

- 1 = PMP module uses TTL input buffers

- 0 = PMP module uses Schmitt Trigger input buffer

- bit 9 **PTWREN:** Write Enable Strobe Port Enable bit

- 1 = PMWR/PMENB port is enabled

- 0 = PMWR/PMENB port is disabled

- bit 8 **PTRDEN:** Read/Write Strobe Port Enable bit

- 1 = PMRD/PMWR port is enabled

- 0 = PMRD/PMWR port is disabled

- bit 7-6 CSF<1:0>: Chip Select Function bits<sup>(2)</sup>

- 11 = Reserved

- 10 = PMCS2 and PMCS1 function as Chip Select

- 01 = PMCS2 functions as Chip Select, PMCS1 functions as address bit 14

- 00 = PMCS2 and PMCS1 function as address bits 15 and  $14^{(2)}$

- bit 5 ALP: Address Latch Polarity bit<sup>(2)</sup>

- 1 = Active-high (PMALL and PMALH)

- $0 = \text{Active-low} (\overline{\text{PMALL}} \text{ and } \overline{\text{PMALH}})$

- bit 4 Unimplemented: Read as '0'

- **Note 1:** When using the 1:1 PBCLK divisor, the user's software should not read/write the peripheral's SFRs in the SYSCLK cycle immediately following the instruction that clears the module's ON control bit.

- 2: These bits have no effect when their corresponding pins are used as address lines.

## PIC32MX5XX/6XX/7XX

NOTES:

# PIC32MX5XX/6XX/7XX

|              |                   |                   |                   |                   |                   |                   |                  | ,                |  |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|--|

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |

| 31:24        | R/W-x             | R/W-x             | R/W-x             | R/W-x             | R/W-x             | R/W-x             | R/W-x            | R/W-x            |  |

| 31.24        |                   |                   |                   | SID<              | 10:3>             |                   |                  |                  |  |

| 22:46        | R/W-x             | R/W-x             | R/W-x             | U-0               | R/W-0             | U-0               | R/W-x            | R/W-x            |  |

| 23:16        |                   | SID<2:0>          |                   | —                 | EXID              | —                 | EID<1            | 7:16>            |  |

| 15.0         | R/W-x             | R/W-x             | R/W-x             | R/W-x             | R/W-x             | R/W-x             | R/W-x            | R/W-x            |  |

| 15:8         | EID<15:8>         |                   |                   |                   |                   |                   |                  |                  |  |

| 7:0          | R/W-x             | R/W-x             | R/W-x             | R/W-x             | R/W-x             | R/W-x             | R/W-x            | R/W-x            |  |

|              |                   |                   |                   | EID<              | :7:0>             |                   |                  |                  |  |

#### REGISTER 24-18: CIRXFn: CAN ACCEPTANCE FILTER 'n' REGISTER 7 (n = 0 THROUGH 31)

#### Legend:

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, r | ead as '0'         |

|-------------------|------------------|--------------------------|--------------------|

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared     | x = Bit is unknown |

bit 31-21 SID<10:0>: Standard Identifier bits

- 1 = Message address bit SIDx must be '1' to match filter

- 0 = Message address bit SIDx must be '0' to match filter

- bit 20 Unimplemented: Read as '0'

- bit 19 **EXID:** Extended Identifier Enable bits

- 1 = Match only messages with extended identifier addresses

- 0 = Match only messages with standard identifier addresses

- bit 18 Unimplemented: Read as '0'

- bit 17-0 EID<17:0>: Extended Identifier bits

- 1 = Message address bit EIDx must be '1' to match filter

- 0 = Message address bit EIDx must be '0' to match filter

**Note:** This register can only be modified when the filter is disabled (FLTENn = 0).

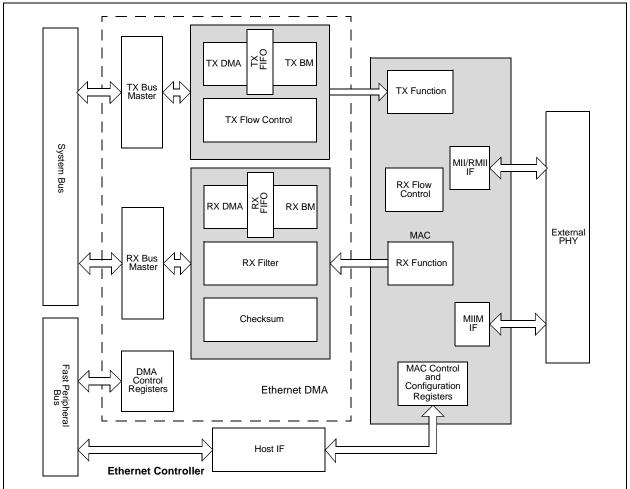

## 25.0 ETHERNET CONTROLLER

Note: This data sheet summarizes the features of the PIC32MX5XX/6XX/7XX family of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to Section 35. "Ethernet Controller" (DS60001155) in the "PIC32 Family Reference Manual", which is available from the Microchip web site (www.microchip.com/PIC32).

The Ethernet controller is a bus master module that interfaces with an off-chip Physical Layer (PHY) to implement a complete Ethernet node in a system.

Key features of the Ethernet Controller include:

- Supports 10/100 Mbps data transfer rates

- Supports full-duplex and half-duplex operation

- Supports RMII and MII PHY interface

- Supports MIIM PHY management interface

- Supports both manual and automatic Flow Control

- RAM descriptor-based DMA operation for both receive and transmit path

- · Fully configurable interrupts

- Configurable receive packet filtering

- CRC check

- 64-byte pattern match

- Broadcast, multicast and unicast packets

- Magic Packet™

- 64-bit hash table

- Runt packet

- Supports packet payload checksum calculation

- · Supports various hardware statistics counters

Figure 25-1 illustrates a block diagram of the Ethernet controller.

#### FIGURE 25-1: ETHERNET CONTROLLER BLOCK DIAGRAM

### 31.6 MPLAB X SIM Software Simulator

The MPLAB X SIM Software Simulator allows code development in a PC-hosted environment by simulating the PIC MCUs and dsPIC DSCs on an instruction level. On any given instruction, the data areas can be examined or modified and stimuli can be applied from a comprehensive stimulus controller. Registers can be logged to files for further run-time analysis. The trace buffer and logic analyzer display extend the power of the simulator to record and track program execution, actions on I/O, most peripherals and internal registers.

The MPLAB X SIM Software Simulator fully supports symbolic debugging using the MPLAB XC Compilers, and the MPASM and MPLAB Assemblers. The software simulator offers the flexibility to develop and debug code outside of the hardware laboratory environment, making it an excellent, economical software development tool.

#### 31.7 MPLAB REAL ICE In-Circuit Emulator System

The MPLAB REAL ICE In-Circuit Emulator System is Microchip's next generation high-speed emulator for Microchip Flash DSC and MCU devices. It debugs and programs all 8, 16 and 32-bit MCU, and DSC devices with the easy-to-use, powerful graphical user interface of the MPLAB X IDE.

The emulator is connected to the design engineer's PC using a high-speed USB 2.0 interface and is connected to the target with either a connector compatible with in-circuit debugger systems (RJ-11) or with the new high-speed, noise tolerant, Low-Voltage Differential Signal (LVDS) interconnection (CAT5).

The emulator is field upgradable through future firmware downloads in MPLAB X IDE. MPLAB REAL ICE offers significant advantages over competitive emulators including full-speed emulation, run-time variable watches, trace analysis, complex breakpoints, logic probes, a ruggedized probe interface and long (up to three meters) interconnection cables.

#### 31.8 MPLAB ICD 3 In-Circuit Debugger System

The MPLAB ICD 3 In-Circuit Debugger System is Microchip's most cost-effective, high-speed hardware debugger/programmer for Microchip Flash DSC and MCU devices. It debugs and programs PIC Flash microcontrollers and dsPIC DSCs with the powerful, yet easy-to-use graphical user interface of the MPLAB IDE.

The MPLAB ICD 3 In-Circuit Debugger probe is connected to the design engineer's PC using a highspeed USB 2.0 interface and is connected to the target with a connector compatible with the MPLAB ICD 2 or MPLAB REAL ICE systems (RJ-11). MPLAB ICD 3 supports all MPLAB ICD 2 headers.

## 31.9 PICkit 3 In-Circuit Debugger/ Programmer

The MPLAB PICkit 3 allows debugging and programming of PIC and dsPIC Flash microcontrollers at a most affordable price point using the powerful graphical user interface of the MPLAB IDE. The MPLAB PICkit 3 is connected to the design engineer's PC using a fullspeed USB interface and can be connected to the target via a Microchip debug (RJ-11) connector (compatible with MPLAB ICD 3 and MPLAB REAL ICE). The connector uses two device I/O pins and the Reset line to implement in-circuit debugging and In-Circuit Serial Programming<sup>™</sup> (ICSP<sup>™</sup>).

## 31.10 MPLAB PM3 Device Programmer

The MPLAB PM3 Device Programmer is a universal, CE compliant device programmer with programmable voltage verification at VDDMIN and VDDMAX for maximum reliability. It features a large LCD display (128 x 64) for menus and error messages, and a modular, detachable socket assembly to support various package types. The ICSP cable assembly is included as a standard item. In Stand-Alone mode, the MPLAB PM3 Device Programmer can read, verify and program PIC devices without a PC connection. It can also set code protection in this mode. The MPLAB PM3 connects to the host PC via an RS-232 or USB cable. The MPLAB PM3 has high-speed communications and optimized algorithms for quick programming of large memory devices, and incorporates an MMC card for file storage and data applications.

| DC CHARACTERISTICS |        |                                                                       | $\begin{array}{l} \mbox{Standard Operating Conditions: 2.3V to 3.6V} \\ \mbox{(unless otherwise stated)} \\ \mbox{Operating temperature} & -40^{\circ}C \leq TA \leq +85^{\circ}C \mbox{ for Industrial} \\ & -40^{\circ}C \leq TA \leq +105^{\circ}C \mbox{ for V-Temp} \end{array}$ |   |                          |          |                                                                                                                                                                         |  |

|--------------------|--------|-----------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---|--------------------------|----------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| Param.<br>No.      | Symbol | Characteristics                                                       | Min. Typical <sup>(1)</sup> Max. Units                                                                                                                                                                                                                                                |   |                          |          | Conditions                                                                                                                                                              |  |

| DI50               | lil    | Input Leakage Current <sup>(3)</sup><br>I/O Ports                     | _                                                                                                                                                                                                                                                                                     | _ | <u>+</u> 1               | μA       | Vss $\leq$ VPIN $\leq$ VDD,<br>Pin at high-impedance                                                                                                                    |  |

| DI51               |        | Analog Input Pins                                                     | —                                                                                                                                                                                                                                                                                     | — | <u>+</u> 1               | μΑ       | VSS $\leq$ VPIN $\leq$ VDD,<br>Pin at high-impedance                                                                                                                    |  |

| DI55<br>DI56       |        | MCLR <sup>(2)</sup><br>OSC1                                           | —                                                                                                                                                                                                                                                                                     | _ | <u>+</u> 1<br><u>+</u> 1 | μΑ<br>μΑ | $\label{eq:VSS} \begin{array}{l} \forall SS \leq VPIN \leq VDD \\ \forall SS \leq VPIN \leq VDD, \\ XT \text{ and } HS \text{ modes} \end{array}$                       |  |

| DI60a              | licl   | Input Low Injection<br>Current                                        | 0                                                                                                                                                                                                                                                                                     | _ | <sub>-5</sub> (7,10)     | mA       | This parameter applies<br>to all pins, with the<br>exception of RB10.<br>Maximum IICH current<br>for this exception is<br>0 mA.                                         |  |

| DI60b              | ІІСН   | Input High Injection<br>Current                                       | 0                                                                                                                                                                                                                                                                                     | _ | +5 <sup>(8,9,10)</sup>   | mA       | This parameter applies<br>to all pins, with the<br>exception of all 5V toler-<br>ant pins, SOSCI, and<br>RB10. Maximum IICH<br>current for these<br>exceptions is 0 mA. |  |

| DI60c              | ∑IICT  | Total Input Injection<br>Current (sum of all I/O<br>and control pins) | -20 <sup>(11)</sup>                                                                                                                                                                                                                                                                   | _ | +20 <sup>(11)</sup>      | mA       | Absolute instantaneous<br>sum of all $\pm$ input<br>injection currents from<br>all I/O pins<br>(   IICL +   IICH   ) $\leq \sum$ IICT                                   |  |

#### TABLE 32-8: DC CHARACTERISTICS: I/O PIN INPUT SPECIFICATIONS

Note 1: Data in "Typical" column is at 3.3V, 25°C unless otherwise stated. Parameters are for design guidance only and are not tested.

- 2: The leakage current on the MCLR pin is strongly dependent on the applied voltage level. The specified levels represent normal operating conditions. Higher leakage current may be measured at different input voltages.

- 3: Negative current is defined as current sourced by the pin.

- 4: This parameter is characterized, but not tested in manufacturing.

- 5: See the "Device Pin Tables" section for the 5V-tolerant pins.

- 6: The VIH specification is only in relation to externally applied inputs and not with respect to the user-selectable pull-ups. Externally applied high impedance or open drain input signals utilizing the PIC32 internal pullups are guaranteed to be recognized as a logic "high" internally to the PIC32 device, provided that the external load does not exceed the maximum value of ICNPU.

- 7: VIL source < (VSS 0.3). Characterized but not tested.

- 8: VIH source > (VDD + 0.3) for non-5V tolerant pins only.

- **9:** Digital 5V tolerant pins do not have an internal high side diode to VDD, and therefore, cannot tolerate any "positive" input injection current.

- **10:** Injection currents > | 0 | can affect the ADC results by approximately 4 to 6 counts (i.e., VIH Source > (VDD + 0.3) or VIL source < (VSS 0.3)).

- 11: Any number and/or combination of I/O pins not excluded under IICL or IICH conditions are permitted provided the "absolute instantaneous" sum of the input injection currents from all pins do not exceed the specified limit. If Note 7, IICL = (((Vss 0.3) VIL source) / Rs). If Note 8, IICH = ((IICH source (VDD + 0.3)) / RS). RS = Resistance between input source voltage and device pin. If (Vss 0.3) ≤ VSOURCE ≤ (VDD + 0.3), injection current = 0.

#### 32.2 AC Characteristics and Timing Parameters

The information contained in this section defines PIC32MX5XX/6XX/7XX AC characteristics and timing parameters.

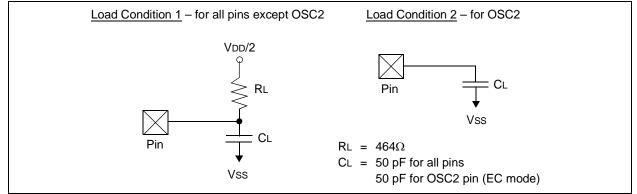

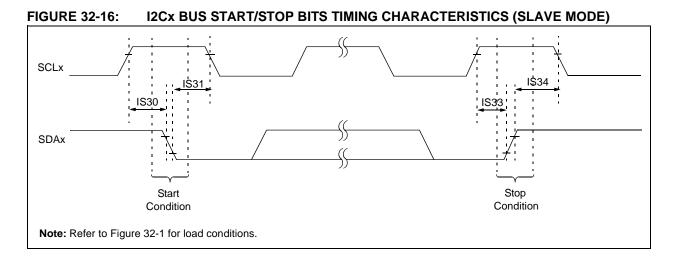

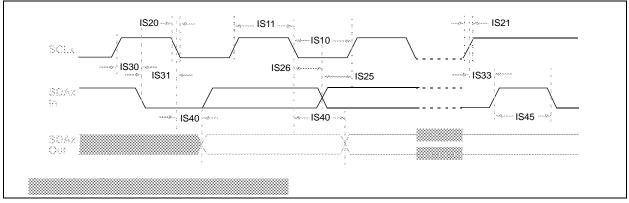

#### FIGURE 32-1: LOAD CONDITIONS FOR DEVICE TIMING SPECIFICATIONS

#### TABLE 32-16: CAPACITIVE LOADING REQUIREMENTS ON OUTPUT PINS

| AC CHARACTERISTICS |        |                       | (unles                                            | ard Operati<br>s otherwise<br>ting tempera | e stated | <b>l)</b><br>∙40°C ≤ | : <b>2.3V to 3.6V</b><br>TA ≤ +85°C for Industrial<br>TA ≤ +105°C for V-Temp |  |

|--------------------|--------|-----------------------|---------------------------------------------------|--------------------------------------------|----------|----------------------|------------------------------------------------------------------------------|--|

| Param.<br>No.      | Symbol | Characteristics       | Min. Typical <sup>(1)</sup> Max. Units Conditions |                                            |          |                      |                                                                              |  |

| DO50               | Cosco  | OSC2 pin              |                                                   | _                                          | 15       | pF                   | In XT and HS modes when an<br>external crystal is used to drive<br>OSC1      |  |

| DO56               | Сю     | All I/O pins and OSC2 |                                                   | —                                          | 50       | pF                   | In EC mode                                                                   |  |

| DO58               | Св     | SCLx, SDAx            |                                                   | —                                          | 400      | pF                   | In I <sup>2</sup> C mode                                                     |  |

Note 1: Data in "Typical" column is at 3.3V, 25°C unless otherwise stated. Parameters are for design guidance only and are not tested.

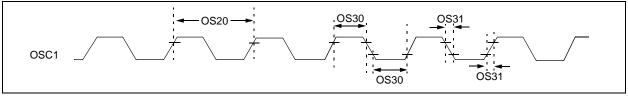

#### FIGURE 32-2: EXTERNAL CLOCK TIMING

#### TABLE 32-36: ADC MODULE SPECIFICATIONS (CONTINUED)

| AC CHARACTERISTICS |            |                                   | Standard Operating Conditions (see Note 5): 2.5V to 3.6V(unless otherwise stated)Operating temperature $-40^{\circ}C \le TA \le +85^{\circ}C$ for Industrial $-40^{\circ}C \le TA \le +105^{\circ}C$ for V-Temp |              |      |       |                                                         |  |

|--------------------|------------|-----------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------|------|-------|---------------------------------------------------------|--|

| Param.<br>No.      | Symbol     | Characteristics                   | Min.                                                                                                                                                                                                            | Typical      | Max. | Units | Conditions                                              |  |

| ADC Ac             | curacy – N | leasurements with Inter           | nal VREF+/VR                                                                                                                                                                                                    | EF-          |      |       |                                                         |  |

| AD20d              | Nr         | Resolution                        |                                                                                                                                                                                                                 | 10 data bits |      | bits  | (Note 3)                                                |  |

| AD21d              | INL        | Integral Nonlinearity             | > -1                                                                                                                                                                                                            | —            | < 1  | LSb   | VINL = AVSS = 0V,<br>AVDD = 2.5V to 3.6V<br>(Note 3)    |  |

| AD22d              | DNL        | Differential Nonlinearity         | > -1                                                                                                                                                                                                            |              | < 1  | LSb   | VINL = AVSS = 0V,<br>AVDD = 2.5V to 3.6V<br>(Notes 2,3) |  |

| AD23d              | Gerr       | Gain Error                        | > -4                                                                                                                                                                                                            | -            | < 4  | LSb   | VINL = AVSS = 0V,<br>AVDD = 2.5V to 3.6V<br>(Note 3)    |  |

| AD24d              | EOFF       | Offset Error                      | > -2                                                                                                                                                                                                            | -            | < 2  | LSb   | VINL = AVSS = 0V,<br>AVDD = 2.5V to 3.6V<br>(Note 3)    |  |

| AD25d              | —          | Monotonicity                      | —                                                                                                                                                                                                               | —            | _    | —     | Guaranteed                                              |  |

| Dynami             | c Performa | ance                              |                                                                                                                                                                                                                 |              |      |       |                                                         |  |

| AD31b              | SINAD      | Signal to Noise and<br>Distortion | 55                                                                                                                                                                                                              | 58.5         |      | dB    | (Notes 3,4)                                             |  |

| AD34b              | ENOB       | Effective Number of Bits          | 9.0                                                                                                                                                                                                             | 9.5          |      | bits  | (Notes 3,4)                                             |  |

**Note 1:** These parameters are not characterized or tested in manufacturing.

2: With no missing codes.

**3:** These parameters are characterized, but not tested in manufacturing.

4: Characterized with a 1 kHz sine wave.

**5:** The ADC module is functional at VBORMIN < VDD < 2.5V, but with degraded performance. Unless otherwise stated, module functionality is tested, but not characterized.

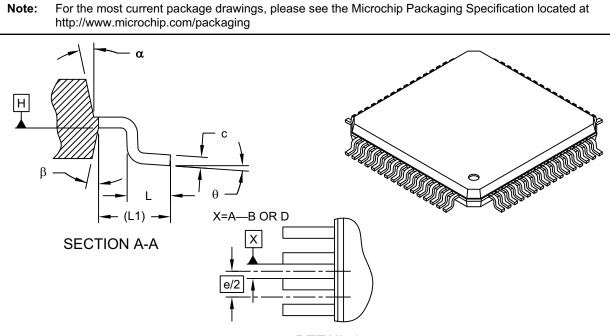

## 64-Lead Plastic Thin Quad Flatpack (PT)-10x10x1 mm Body, 2.00 mm Footprint [TQFP]

#### DETAIL 1

|                          | N   | ILLIMETER   | S         |      |  |  |

|--------------------------|-----|-------------|-----------|------|--|--|

| Dimension                | MIN | NOM         | MAX       |      |  |  |

| Number of Leads          | N   |             | 64        |      |  |  |

| Lead Pitch               | е   |             | 0.50 BSC  |      |  |  |

| Overall Height           | Α   | -           | -         | 1.20 |  |  |

| Molded Package Thickness | A2  | 0.95        | 1.00      | 1.05 |  |  |

| Standoff                 | A1  | 0.05        | -         | 0.15 |  |  |

| Foot Length              | L   | 0.45        | 0.60      | 0.75 |  |  |

| Footprint                | L1  | 1.00 REF    |           |      |  |  |

| Foot Angle               | ¢   | 0° 3.5° 7°  |           |      |  |  |

| Overall Width            | E   |             | 12.00 BSC |      |  |  |

| Overall Length           | D   |             | 12.00 BSC |      |  |  |

| Molded Package Width     | E1  |             | 10.00 BSC |      |  |  |

| Molded Package Length    | D1  |             | 10.00 BSC |      |  |  |

| Lead Thickness           | С   | 0.09 - 0.20 |           |      |  |  |

| Lead Width               | b   | 0.17        | 0.22      | 0.27 |  |  |

| Mold Draft Angle Top     | α   | 11° 12° 13° |           |      |  |  |

| Mold Draft Angle Bottom  | β   | 11°         | 12°       | 13°  |  |  |

Notes:

1. Pin 1 visual index feature may vary, but must be located within the hatched area.

2. Chamfers at corners are optional; size may vary.

3. Dimensions D1 and E1 do not include mold flash or protrusions. Mold flash or

protrusions shall not exceed 0.25mm per side. 4. Dimensioning and tolerancing per ASME Y14.5M

BSC: Basic Dimension. Theoretically exact value shown without tolerances.

REF: Reference Dimension, usually without tolerance, for information purposes only.

Microchip Technology Drawing C04-085C Sheet 2 of 2

## **Worldwide Sales and Service**

#### AMERICAS

Corporate Office 2355 West Chandler Blvd. Chandler, AZ 85224-6199 Tel: 480-792-7200 Fax: 480-792-7277 Technical Support: http://www.microchip.com/ support Web Address: www.microchip.com

Atlanta Duluth, GA Tel: 678-957-9614 Fax: 678-957-1455

Austin, TX Tel: 512-257-3370

**Boston** Westborough, MA Tel: 774-760-0087 Fax: 774-760-0088

**Chicago** Itasca, IL Tel: 630-285-0071 Fax: 630-285-0075

**Cleveland** Independence, OH Tel: 216-447-0464 Fax: 216-447-0643

**Dallas** Addison, TX Tel: 972-818-7423 Fax: 972-818-2924

Detroit Novi, MI Tel: 248-848-4000

Houston, TX Tel: 281-894-5983

Indianapolis Noblesville, IN Tel: 317-773-8323 Fax: 317-773-5453

Los Angeles Mission Viejo, CA Tel: 949-462-9523 Fax: 949-462-9608

New York, NY Tel: 631-435-6000

San Jose, CA Tel: 408-735-9110

**Canada - Toronto** Tel: 905-695-1980 Fax: 905-695-2078

#### ASIA/PACIFIC

Asia Pacific Office Suites 3707-14, 37th Floor Tower 6, The Gateway Harbour City, Kowloon

Hong Kong Tel: 852-2943-5100 Fax: 852-2401-3431

Australia - Sydney Tel: 61-2-9868-6733 Fax: 61-2-9868-6755

**China - Beijing** Tel: 86-10-8569-7000 Fax: 86-10-8528-2104

China - Chengdu Tel: 86-28-8665-5511 Fax: 86-28-8665-7889

China - Chongqing Tel: 86-23-8980-9588 Fax: 86-23-8980-9500

China - Dongguan Tel: 86-769-8702-9880

**China - Guangzhou** Tel: 86-20-8755-8029

China - Hangzhou Tel: 86-571-8792-8115 Fax: 86-571-8792-8116

**China - Hong Kong SAR** Tel: 852-2943-5100

**China - Nanjing** Tel: 86-25-8473-2460 Fax: 86-25-8473-2470

Fax: 852-2401-3431

**China - Qingdao** Tel: 86-532-8502-7355 Fax: 86-532-8502-7205

**China - Shanghai** Tel: 86-21-5407-5533 Fax: 86-21-5407-5066

China - Shenyang Tel: 86-24-2334-2829 Fax: 86-24-2334-2393

**China - Shenzhen** Tel: 86-755-8864-2200 Fax: 86-755-8203-1760

**China - Wuhan** Tel: 86-27-5980-5300 Fax: 86-27-5980-5118

**China - Xian** Tel: 86-29-8833-7252 Fax: 86-29-8833-7256

#### ASIA/PACIFIC

**China - Xiamen** Tel: 86-592-2388138 Fax: 86-592-2388130

**China - Zhuhai** Tel: 86-756-3210040 Fax: 86-756-3210049

India - Bangalore Tel: 91-80-3090-4444 Fax: 91-80-3090-4123

India - New Delhi Tel: 91-11-4160-8631 Fax: 91-11-4160-8632

India - Pune Tel: 91-20-3019-1500

**Japan - Osaka** Tel: 81-6-6152-7160 Fax: 81-6-6152-9310

**Japan - Tokyo** Tel: 81-3-6880- 3770 Fax: 81-3-6880-3771

**Korea - Daegu** Tel: 82-53-744-4301 Fax: 82-53-744-4302

Korea - Seoul Tel: 82-2-554-7200 Fax: 82-2-558-5932 or 82-2-558-5934

Malaysia - Kuala Lumpur Tel: 60-3-6201-9857 Fax: 60-3-6201-9859

Malaysia - Penang Tel: 60-4-227-8870 Fax: 60-4-227-4068

Philippines - Manila Tel: 63-2-634-9065 Fax: 63-2-634-9069

**Singapore** Tel: 65-6334-8870 Fax: 65-6334-8850

**Taiwan - Hsin Chu** Tel: 886-3-5778-366 Fax: 886-3-5770-955

**Taiwan - Kaohsiung** Tel: 886-7-213-7828

Taiwan - Taipei Tel: 886-2-2508-8600 Fax: 886-2-2508-0102

**Thailand - Bangkok** Tel: 66-2-694-1351 Fax: 66-2-694-1350

#### EUROPE

Austria - Wels Tel: 43-7242-2244-39 Fax: 43-7242-2244-393

**Denmark - Copenhagen** Tel: 45-4450-2828 Fax: 45-4485-2829

France - Paris Tel: 33-1-69-53-63-20 Fax: 33-1-69-30-90-79

Germany - Dusseldorf Tel: 49-2129-3766400

Germany - Karlsruhe Tel: 49-721-625370

**Germany - Munich** Tel: 49-89-627-144-0 Fax: 49-89-627-144-44

**Italy - Milan** Tel: 39-0331-742611 Fax: 39-0331-466781

Italy - Venice Tel: 39-049-7625286

**Netherlands - Drunen** Tel: 31-416-690399 Fax: 31-416-690340

**Poland - Warsaw** Tel: 48-22-3325737

**Spain - Madrid** Tel: 34-91-708-08-90 Fax: 34-91-708-08-91

Sweden - Stockholm Tel: 46-8-5090-4654

**UK - Wokingham** Tel: 44-118-921-5800 Fax: 44-118-921-5820