Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XE

| Product Status             | Active                                                                            |

|----------------------------|-----------------------------------------------------------------------------------|

| Core Processor             | MIPS32® M4K™                                                                      |

| Core Size                  | 32-Bit Single-Core                                                                |

| Speed                      | 80MHz                                                                             |

| Connectivity               | Ethernet, I <sup>2</sup> C, SPI, UART/USART, USB OTG                              |

| Peripherals                | Brown-out Detect/Reset, DMA, POR, PWM, WDT                                        |

| Number of I/O              | 85                                                                                |

| Program Memory Size        | 256КВ (256К х 8)                                                                  |

| Program Memory Type        | FLASH                                                                             |

| EEPROM Size                |                                                                                   |

| RAM Size                   | 64K x 8                                                                           |

| Voltage - Supply (Vcc/Vdd) | 2.3V ~ 3.6V                                                                       |

| Data Converters            | A/D 16x10b                                                                        |

| Oscillator Type            | Internal                                                                          |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                                 |

| Mounting Type              | Surface Mount                                                                     |

| Package / Case             | 100-TQFP                                                                          |

| Supplier Device Package    | 100-TQFP (12x12)                                                                  |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic32mx675f256lt-80i-pt |

|                            |                                                                                   |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

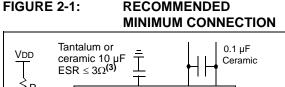

### Note 1: If the USB module is not used, this pin must be connected to VDD.

2: As an option, instead of a hard-wired connection, an inductor (L1) can be substituted between VDD and AVDD to improve ADC noise rejection. The inductor impedance should be less than  $3\Omega$  and the inductor capacity greater than 10 mA.

Where:

$$f = \frac{F_{CNV}}{2}$$

(i.e., ADC conversion rate/2)

$$f = \frac{1}{(2\pi\sqrt{LC})}$$

$$L = \left(\frac{1}{(2\pi f\sqrt{C})}\right)^2$$

3: Aluminum or electrolytic capacitors should not be used. ESR  $\leq 3\Omega$  from -40°C to 125°C @ SYSCLK frequency (i.e., MIPS).

### 2.2.1 BULK CAPACITORS

The use of a bulk capacitor is recommended to improve power supply stability. Typical values range from 4.7  $\mu F$  to 47  $\mu F$ . This capacitor should be located as close to the device as possible.

### 2.3 Capacitor on Internal Voltage Regulator (VCAP)

#### 2.3.1 INTERNAL REGULATOR MODE

A low-ESR (1 ohm) capacitor is required on the VCAP pin, which is used to stabilize the internal voltage regulator output. The VCAP pin must not be connected to VDD, and must have a CEFC capacitor, with at least a 6V rating, connected to ground. The type can be ceramic or tantalum. Refer to **Section 32.0 "Electrical Characteristics"** for additional information on CEFC specifications.

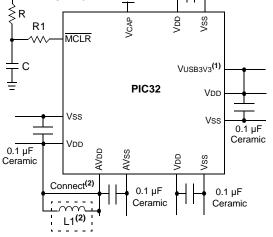

### 2.4 Master Clear (MCLR) Pin

The MCLR pin provides two specific device functions:

- Device Reset

- Device Programming and Debugging

Pulling The MCLR pin low generates a device Reset. Figure 2-2 illustrates a typical MCLR circuit. During device programming and debugging, the resistance and capacitance that can be added to the pin must be considered. Device programmers and debuggers drive the MCLR pin. Consequently, specific voltage levels (VIH and VIL) and fast signal transitions must not be adversely affected. Therefore, specific values of R and C will need to be adjusted based on the application and PCB requirements.

For example, as illustrated in Figure 2-2, it is recommended that the capacitor C, be isolated from the MCLR pin during programming and debugging operations.

Place the components illustrated in Figure 2-2 within one-quarter inch (6 mm) from the MCLR pin.

#### FIGURE 2-2: EXAMPLE OF MCLR PIN CONNECTIONS

MCLR from the external capacitor C, in the event of MCLR pin breakdown, due to Electrostatic Discharge (ESD) or Electrical Overstress (EOS). Ensure that the MCLR pin VIH and VIL specifications are met without interfering with the Debug/Programmer tools.

- 2: The capacitor can be sized to prevent unintentional Resets from brief glitches or to extend the device Reset period during POR.

- **3:** No pull-ups or bypass capacitors are allowed on active debug/program PGECx/PGEDx pins.

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |  |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|--|--|

| 31:24        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |  |  |

|              | _                 | _                 | _                 | —                 | _                 | —                 | —                | —                |  |  |

| 00.40        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |  |  |

| 23:16        | —                 | —                 | —                 | —                 | —                 | —                 | —                | —                |  |  |

| 45.0         | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R-0              | R-0              |  |  |

| 15:8         | BMXDUDBA<15:8>    |                   |                   |                   |                   |                   |                  |                  |  |  |

| 7.0          | R-0               | R-0               | R-0               | R-0               | R-0               | R-0               | R-0              | R-0              |  |  |

| 7:0          |                   |                   |                   | BMXDU             | DBA<7:0>          |                   |                  |                  |  |  |

#### REGISTER 4-3: BMXDUDBA: DATA RAM USER DATA BASE ADDRESS REGISTER

### Legend:

| Legena:           |                  |                                    |                    |  |  |  |

|-------------------|------------------|------------------------------------|--------------------|--|--|--|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read as '0' |                    |  |  |  |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared               | x = Bit is unknown |  |  |  |

bit 31-16 Unimplemented: Read as '0'

#### bit 15-10 BMXDUDBA<15:10>: DRM User Data Base Address bits

When non-zero, the value selects the relative base address for User mode data space in RAM, the value must be greater than BMXDKPBA.

bit 9-0 BMXDUDBA<9:0>: DRM User Data Base Address Read-Only bits Value is always '0', which forces 1 KB increments

**Note 1:** At Reset, the value in this register is forced to zero, which causes all of the RAM to be allocated to Kernal mode data usage.

2: The value in this register must be less than or equal to BMXDRMSZ.

#### **TABLE 7-7:** INTERRUPT REGISTER MAP FOR PIC32MX764F128L, PIC32MX775F256L, PIC32MX775F512L AND PIC32MX795F512L DEVICES (CONTINUED)

| ess                         |                                 |           |       |       |       |       |             |       |             | В                     | its  |             |      |                 |             |       |        |                      |             |       |        |        |

|-----------------------------|---------------------------------|-----------|-------|-------|-------|-------|-------------|-------|-------------|-----------------------|------|-------------|------|-----------------|-------------|-------|--------|----------------------|-------------|-------|--------|--------|

| Virtual Address<br>(BF88_#) | Register<br>Name <sup>(1)</sup> | Bit Range | 31/15 | 30/14 | 29/13 | 28/12 | 27/11       | 26/10 | 25/9        | 24/8                  | 23/7 | 22/6        | 21/5 | 20/4            | 19/3        | 18/2  | 17/1   | 16/0                 | All Resets  |       |        |        |

| 10D0                        | IPC4                            | 31:16     | _     | —     | -     |       | INT4IP<2:0> |       | INT4IS      | S<1:0>                | _    | _           | _    |                 | OC4IP<2:0>  |       | OC4IS  | 5<1:0>               | 0000        |       |        |        |

| TODO                        | IPC4                            | 15:0      | _     | _     | —     |       | IC4IP<2:0>  |       | IC4IS       | <1:0>                 | _    | _           | -    |                 | T4IP<2:0>   |       | T4IS-  | <1:0>                | 0000        |       |        |        |

| 10E0                        | IPC5                            | 31:16     | _     |       | —     |       | SPI1IP<2:0> | •     | SPI1IS      | S<1:0>                | _    | _           | _    |                 | OC5IP<2:0>  | •     | OC5IS  | 6<1:0>               | 0000        |       |        |        |

| IUEU                        | IPC5                            | 15:0      | —     | _     | _     |       | IC5IP<2:0>  |       | IC5IS       | <1:0>                 | _    | _           | _    |                 | T5IP<2:0>   |       | T5IS-  | <1:0>                | 0000        |       |        |        |

|                             |                                 | 31:16     | —     | _     | _     |       | AD1IP<2:0>  |       | AD1IS       | S<1:0>                | _    | _           | _    |                 | CNIP<2:0>   |       | CNIS   | <1:0>                | 0000        |       |        |        |

| 10F0                        | IPC6                            |           |       |       |       |       |             |       |             | I2C1IS<1:0>           |      |             |      |                 |             |       |        | U1IP<2:0>            |             | U1IS- | <1:0>  |        |

| 1000                        | IFCO                            | 15:0      | _     | -     | -     |       | I2C1IP<2:0> |       | I2C1IS<1:0> |                       |      | I2C1IS<1:0> |      | I2C1IS<1:0>     | —           | —     | —      |                      | SPI3IP<2:0> | •     | SPI3IS | S<1:0> |

|                             |                                 |           |       |       |       |       |             |       |             |                       |      |             |      |                 | 12C3IP<2:0> |       | 12C315 | 5<1:0>               |             |       |        |        |

|                             |                                 |           |       |       |       |       | U3IP<2:0>   |       | U3IS        | U3IS<1:0>             |      |             |      |                 |             |       |        |                      |             |       |        |        |

| 1100                        | IPC7                            | 31:16     | —     | —     | -     |       | SPI2IP<2:0> |       | SPI2IS      | S<1:0>                | —    | —           | -    | – CMP2IP<2:0> C |             | CMP2I | S<1:0> | 0000                 |             |       |        |        |

| 1100                        | 11 07                           |           |       |       |       |       | I2C4IP<2:0> |       | 12C418      | S<1:0>                |      |             |      |                 |             |       |        |                      |             |       |        |        |

|                             |                                 | 15:0      | _     |       |       | (     | CMP1IP<2:0  | >     | CMP1I       | S<1:0>                | —    | —           | —    | PMPIP<2:0>      |             | PMPIS | S<1:0> | 0000                 |             |       |        |        |

|                             |                                 | 31:16     | —     | —     | —     | F     | RTCCIP<2:0  | >     | RTCCI       | S<1:0>                | —    | —           | —    | I               | SCMIP<2:0   | >     | FSCMI  | S<1:0>               | 0000        |       |        |        |

| 1110                        | IPC8                            |           |       |       |       |       |             |       |             |                       |      |             |      |                 | U2IP<2:0>   |       | U2IS   | <1:0>                |             |       |        |        |

| 1110                        | 11 00                           | 15:0      | —     | —     | -     |       | I2C2IP<2:0> |       | 12C218      | S<1:0>                | —    | —           | —    |                 | SPI4IP<2:0> | •     | SPI4IS | S<1:0>               | 0000        |       |        |        |

|                             |                                 |           |       |       |       |       |             |       |             |                       |      |             |      |                 | I2C5IP<2:0> | •     | 12C515 | 5<1:0>               |             |       |        |        |

| 1120                        | IPC9                            | 31:16     | —     | —     | —     | [     | DMA3IP<2:0  | >     | DMA3I       | S<1:0>                | —    | —           | —    | I               | DMA2IP<2:0  | >     | DMA2I  | S<1:0>               | 0000        |       |        |        |

| 1120                        | IFC9                            | 15:0      | —     | -     | —     |       | DMA1IP<2:0  |       | DMA1I       | S<1:0>                | —    | —           | _    |                 | DMA0IP<2:0  |       | DMA0I  | S<1:0>               | 0000        |       |        |        |

| 1130                        | IPC10                           | 31:16     | —     | —     | —     | D     | MA7IP<2:0>  | (2)   | DMA7IS      | S<1:0> <sup>(2)</sup> | —    | —           | —    | D               | MA6IP<2:0>  | (2)   | DMA6IS | <1:0> <sup>(2)</sup> | 0000        |       |        |        |

| 1130                        | IFCIU                           | 15:0      | —     | _     | _     | D     | MA5IP<2:0>  | (2)   | DMA5IS      | S<1:0> <sup>(2)</sup> | _    | —           | _    | D               | MA4IP<2:0>  | (2)   | DMA4IS | <1:0> <sup>(2)</sup> | 0000        |       |        |        |

| 1140                        | IPC11                           | 31:16     |       | -     | —     | C     | AN2IP<2:0>  | (2)   | CAN2IS      | S<1:0> <sup>(2)</sup> | _    | _           | _    |                 | CAN1IP<2:0  | >     | CAN1   | S<1:0>               | 0000        |       |        |        |

| 1140                        | IFCII                           | 15:0      | —     | _     | —     |       | USBIP<2:0>  |       | USBIS       | S<1:0>                | _    | —           | _    |                 | FCEIP<2:0>  |       | FCEIS  | <1:0>                | 0000        |       |        |        |

| 1150                        | IPC12                           | 31:16     | _     | _     | —     |       | U5IP<2:0>   |       | U5IS        | <1:0>                 | —    | —           | —    |                 | U6IP<2:0>   |       | U6IS-  | <1:0>                | 0000        |       |        |        |

| 1150                        | IFC12                           | 15:0      |       | —     | _     |       | U4IP<2:0>   |       | U4IS        | <1:0>                 | —    | _           | —    |                 | ETHIP<2:0>  |       | ETHIS  | <1:0>                | 0000        |       |        |        |

DS60001156J-page 88

Legend: x = unknown value on Reset; — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

Except where noted, all registers in this table have corresponding CLR, SET and INV registers at their virtual addresses, plus offsets of 0x4, 0x8 and 0xC, respectively. See Section 12.1.1 "CLR, SET and INV Note 1: Registers" for more information.

2: This bit is unimplemented on PIC32MX764F128L device.

3: This register does not have associated CLR, SET, and INV registers.

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|

| 04.04        | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |

| 31:24        | IFS31             | IFS30             | IFS29             | IFS28             | IFS27             | IFS26             | IFS25            | IFS24            |

| 23:16        | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |

| 23.10        | IFS23             | IFS22             | IFS21             | IFS20             | IFS19             | IFS18             | IFS17            | IFS16            |

| 15:8         | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |

| 15.0         | IFS15             | IFS14             | IFS13             | IFS12             | IFS11             | IFS10             | IFS09            | IFS08            |

| 7.0          | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |

| 7:0          | IFS07             | IFS06             | IFS05             | IFS04             | IFS03             | IFS02             | IFS01            | IFS00            |

#### REGISTER 7-4: IFSx: INTERRUPT FLAG STATUS REGISTER

#### Legend:

| R = Readable bit  | = Readable bit W = Writable bit |                      | U = Unimplemented bit, read as '0' |  |  |  |

|-------------------|---------------------------------|----------------------|------------------------------------|--|--|--|

| -n = Value at POR | '1' = Bit is set                | '0' = Bit is cleared | x = Bit is unknown                 |  |  |  |

#### bit 31-0 IFS31-IFS00: Interrupt Flag Status bits

- 1 = Interrupt request has occurred

- 0 = Interrupt request has not occurred

**Note:** This register represents a generic definition of the IFSx register. Refer to Table 7-1 for the exact bit definitions.

#### REGISTER 7-5: IECx: INTERRUPT ENABLE CONTROL REGISTER

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|

| 24.24        | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |

| 31:24        | IEC31             | IEC30             | IEC29             | IEC28             | IEC27             | IEC26             | IEC25            | IEC24            |

| 23:16        | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |

| 23.10        | IEC23             | IEC22             | IEC21             | IEC20             | IEC19             | IEC18             | IEC17            | IEC16            |

| 15.0         | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |

| 15:8         | IEC15             | IEC14             | IEC13             | IEC12             | IEC11             | IEC10             | IEC09            | IEC08            |

| 7.0          | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |

| 7:0          | IEC07             | IEC06             | IEC05             | IEC04             | IEC03             | IEC02             | IEC01            | IEC00            |

### Legend:

| · J · · ·         |                  |                                    |                    |  |  |  |

|-------------------|------------------|------------------------------------|--------------------|--|--|--|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read as '0' |                    |  |  |  |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared               | x = Bit is unknown |  |  |  |

bit 31-0 IEC31-IEC00: Interrupt Enable bits

1 = Interrupt is enabled

0 = Interrupt is disabled

**Note:** This register represents a generic definition of the IECx register. Refer to Table 7-1 for the exact bit definitions.

| Bit Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |  |  |

|-----------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|--|--|--|

| 31:24     | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |  |

| 31:24     |                   | CHSSA<31:24>      |                   |                   |                   |                   |                  |                  |  |  |  |

| 00.40     | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |  |

| 23:16     | CHSSA<23:16>      |                   |                   |                   |                   |                   |                  |                  |  |  |  |

| 45.0      | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |  |

| 15:8      | CHSSA<15:8>       |                   |                   |                   |                   |                   |                  |                  |  |  |  |

| 7.0       | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |  |

| 7:0       |                   |                   |                   | CHSSA             | <7:0>             |                   |                  |                  |  |  |  |

#### REGISTER 10-10: DCHxSSA: DMA CHANNEL 'x' SOURCE START ADDRESS REGISTER

| Legend:           |                  |                        |                    |

|-------------------|------------------|------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, | read as '0'        |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared   | x = Bit is unknown |

bit 31-0 CHSSA<31:0> Channel Source Start Address bits Channel source start address. Note: This must be the physical address of the source.

#### REGISTER 10-11: DCHxDSA: DMA CHANNEL 'x' DESTINATION START ADDRESS REGISTER

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |  |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|--|--|

| 04.04        | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |

| 31:24        |                   | CHDSA<31:24>      |                   |                   |                   |                   |                  |                  |  |  |

| 00.40        | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |

| 23:16        | CHDSA<23:16>      |                   |                   |                   |                   |                   |                  |                  |  |  |

| 45.0         | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |

| 15:8         | CHDSA<15:8>       |                   |                   |                   |                   |                   |                  |                  |  |  |

| 7.0          | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |

| 7:0          |                   |                   |                   | CHDSA             | <7:0>             |                   |                  |                  |  |  |

| Legend:           |                  |                                    |                    |  |  |

|-------------------|------------------|------------------------------------|--------------------|--|--|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read as '0' |                    |  |  |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared               | x = Bit is unknown |  |  |

bit 31-0 CHDSA<31:0>: Channel Destination Start Address bits Channel destination start address.

Note: This must be the physical address of the destination.

#### REGISTER 11-7: U1IE: USB INTERRUPT ENABLE REGISTER

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1      | Bit<br>24/16/8/0        |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|-----------------------|-------------------------|

| 31:24        | U-0                   | U-0                     |

| 31.24        | —                 | —                 | —                 | —                 | _                 | —                 | _                     |                         |

| 23:16        | U-0                   | U-0                     |

| 23.10        | —                 | —                 | —                 | —                 | _                 | —                 | _                     |                         |

| 15:8         | U-0                   | U-0                     |

| 15.6         | —                 | —                 | —                 | —                 | _                 | —                 | _                     |                         |

|              | R/W-0                 | R/W-0                   |

| 7:0          | STALLIE           | ATTACHIE          | RESUMEIE          |                   | TRNIE             |                   | UERRIE <sup>(1)</sup> | URSTIE <sup>(2)</sup>   |

|              | STALLIE           | ATTACHIE          | RESUMEIE          | IDLEIE            |                   | SOFIE             | UERRIE'               | DETACHIE <sup>(3)</sup> |

#### Legend:

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, | read as '0'        |

|-------------------|------------------|------------------------|--------------------|

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared   | x = Bit is unknown |

#### bit 31-8 Unimplemented: Read as '0'

|       | •·····                                                          |

|-------|-----------------------------------------------------------------|

| bit 7 | STALLIE: STALL Handshake Interrupt Enable bit                   |

|       | 1 = STALL interrupt is enabled                                  |

|       | 0 = STALL interrupt is disabled                                 |

| bit 6 | ATTACHIE: ATTACH Interrupt Enable bit                           |

|       | 1 = ATTACH interrupt is enabled                                 |

|       | 0 = ATTACH interrupt is disabled                                |

| bit 5 | RESUMEIE: RESUME Interrupt Enable bit                           |

|       | 1 = RESUME interrupt is enabled                                 |

|       | 0 = RESUME interrupt is disabled                                |

| bit 4 | IDLEIE: Idle Detect Interrupt Enable bit                        |

|       | 1 = Idle interrupt is enabled                                   |

|       | 0 = Idle interrupt is disabled                                  |

| bit 3 | TRNIE: Token Processing Complete Interrupt Enable bit           |

|       | 1 = TRNIF interrupt is enabled                                  |

|       | 0 = TRNIF interrupt is disabled                                 |

| bit 2 | SOFIE: SOF Token Interrupt Enable bit                           |

|       | 1 = SOFIF interrupt is enabled                                  |

|       | 0 = SOFIF interrupt is disabled                                 |

| bit 1 | UERRIE: USB Error Interrupt Enable bit <sup>(1)</sup>           |

|       | 1 = USB Error interrupt is enabled                              |

|       | 0 = USB Error interrupt is disabled                             |

| bit 0 | URSTIE: USB Reset Interrupt Enable bit <sup>(2)</sup>           |

|       | 1 = URSTIF interrupt is enabled                                 |

|       | 0 = URSTIF interrupt is disabled                                |

|       | <b>DETACHIE:</b> USB Detach Interrupt Enable bit <sup>(3)</sup> |

|       | 1 = DATTCHIF interrupt is enabled                               |

|       | 0 = DATTCHIF interrupt is disabled                              |

|       |                                                                 |

**Note 1:** For an interrupt to propagate USBIF, the UERRIE bit (U1IE<1>) must be set.

- 2: Device mode.

- 3: Host mode.

### 22.1 Control Registers

#### TABLE 22-1: RTCC REGISTER MAP

| ess                         |                                 |           |              | Bits    |            |               |              |             |                   |       |          |          |        |      |         |                   |         |       |            |

|-----------------------------|---------------------------------|-----------|--------------|---------|------------|---------------|--------------|-------------|-------------------|-------|----------|----------|--------|------|---------|-------------------|---------|-------|------------|

| Virtual Address<br>(BF80_#) | Register<br>Name <sup>(1)</sup> | Bit Range | 31/15        | 30/14   | 29/13      | 28/12         | 27/11        | 26/10       | 25/9              | 24/8  | 23/7     | 22/6     | 21/5   | 20/4 | 19/3    | 18/2              | 17/1    | 16/0  | All Resets |

| 0200                        | RTCCON                          | 31:16     |              |         |            | —             |              |             |                   |       |          |          | CAL<   | 9:0> |         |                   |         |       | 0000       |

| 0200                        | RICCON                          | 15:0      | ON           | -       | SIDL       | —             | —            | —           |                   | _     | RTSECSEL | RTCCLKON | —      |      | RTCWREN | RTCSYNC           | HALFSEC | RTCOE | 0000       |

| 0210                        | RTCALRM                         | 31:16     | _            | -       | _          | —             | —            | —           |                   | _     | —        | _        | —      |      | _       | _                 | _       | —     | 0000       |

| 0210                        | RICALKI                         | 15:0      | ALRMEN       | CHIME   | PIV        | ALRMSYNC      |              | AMASI       | <b>&lt;</b> <3:0> |       |          |          |        | ARPT | <7:0>   |                   |         |       | 0000       |

| 0220                        | RTCTIME                         | 31:16     |              | HR10    | 0<3:0>     |               |              | HR01        | <3:0>             |       |          | MIN10<   | 3:0>   |      |         | MIN0 <sup>2</sup> | <3:0>   |       | xxxx       |

| 0220                        | RICTIVIE                        | 15:0      |              | SEC1    | 0<3:0>     |               |              | SEC01       | <3:0>             |       | _        | _        | —      | -    | _       | —                 | —       | —     | xx00       |

| 0000                        | DTODATE                         | 31:16     |              | YEAR'   | 10<3:0>    |               |              | YEAR0       | 1<3:0>            |       |          | MONTH1   | )<3:0> |      |         | MONTH             | 01<3:0> |       | xxxx       |

| 0230                        | RTCDATE                         | 15:0      |              | DAY1    | 0<3:0>     |               |              | DAY01       | l<3:0>            |       | -        | -        | _      | _    |         | WDAY(             | )1<3:0> |       | xx00       |

| 0040                        |                                 | 31:16     |              | HR10    | )<3:0>     |               |              | HR01        | <3:0>             |       |          | MIN10<   | 3:0>   |      |         | MIN0 <sup>2</sup> | <3:0>   |       | xxxx       |

| 0240                        | ALRMTIME                        | 15:0      |              | SEC1    | 0<3:0>     |               |              | SEC01       | <3:0>             |       | _        | —        | _      | _    | _       | _                 | _       | _     | xx00       |

| 0050                        |                                 | 31:16     | _            | _       | _          | —             | _            | _           | _                 | _     |          | MONTH1   | )<3:0> |      |         | MONTH             | 01<3:0> |       | 00xx       |

| 0250                        | ALRMDATE                        | 15:0      |              | DAY1    | 0<3:0>     |               |              | DAY01       | <3:0>             |       | _        | _        | _      | _    |         | WDAY              | )1<3:0> |       | xx0x       |

|                             | ، بام                           | unknow    | n voluo on D | aaati u | nimploment | 0' ac hear ha | , Depet volu | an ara ahau | un in hoved       | aimal |          |          |        |      | •       |                   |         |       |            |

PIC32MX5XX/6XX/7XX

Legend: x = unknown value on Reset; — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

Note 1: All registers in this table have corresponding CLR, SET and INV registers at its virtual address, plus an offset of 0x4, 0x8 and 0xC, respectively. See Section 12.1.1 "CLR, SET and INV Registers" for more information.

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3       | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------------|-------------------|------------------|------------------|

| 24.24        | U-0               | U-0               | U-0               | U-0               | U-0                     | U-0               | U-0              | U-0              |

| 31:24        | _                 | _                 | _                 | —                 | —                       |                   | _                | —                |

| 22:46        | U-0               | U-0               | U-0               | U-0               | U-0                     | U-0               | U-0              | U-0              |

| 23:16        | —                 | —                 | _                 | —                 | _                       | _                 | —                | —                |

| 15.0         | U-0               | U-0               | U-0               | R-0               | R-0                     | R-0               | R-0              | R-0              |

| 15:8         | —                 | _                 | _                 |                   |                         | FILHIT<4:0>       |                  |                  |

| 7.0          | U-0               | R-1               | R-0               | R-0               | R-0                     | R-0               | R-0              | R-0              |

| 7:0          | _                 |                   |                   | l                 | CODE<6:0> <sup>(1</sup> | )                 |                  |                  |

#### REGISTER 24-4: CiVEC: CAN INTERRUPT CODE REGISTER

#### Legend:

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, r | read as '0'        |

|-------------------|------------------|--------------------------|--------------------|

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared     | x = Bit is unknown |

#### bit 31-13 Unimplemented: Read as '0'

| bit 12-8 | FILHIT<4:0>: Filter Hit Number bit                  |

|----------|-----------------------------------------------------|

|          | 11111 = Filter 31                                   |

|          | 11110 = Filter 30                                   |

|          | •                                                   |

|          | •                                                   |

|          | 00001 = Filter 1                                    |

|          | 00000 = Filter 0                                    |

| bit 7    | Unimplemented: Read as '0'                          |

| bit 6-0  | ICODE<6:0>: Interrupt Flag Code bits <sup>(1)</sup> |

|          | 11111111 = Reserved                                 |

|          | •                                                   |

|          | •                                                   |

|          | •<br>1001001 = Reserved                             |

|          | 1001000 = Invalid message received (IVRIF)          |

|          | 1001111 = CAN module mode change (MODIF)            |

|          | 1000110 = CAN timestamp timer (CTMRIF)              |

|          | 1000101 = Bus bandwidth error (SERRIF)              |

|          | 1000100 = Address error interrupt (SERRIF)          |

|          | 1000011 = Receive FIFO overflow interrupt (RBOVIF)  |

|          | 1000010 = Wake-up interrupt (WAKIF)                 |

|          | 1000001 = Error Interrupt (CERRIF)                  |

|          | 1000000 = No interrupt                              |

|          | 0111111 = Reserved                                  |

|          | •                                                   |

|          | •                                                   |

|          | 0100000 = Reserved                                  |

|          | 0011111 = FIFO31 Interrupt (CiFSTAT<31> set)        |

|          | 0011110 = FIFO30 Interrupt (CiFSTAT<30> set)        |

|          | •                                                   |

|          | •                                                   |

|          | 0000001 = FIFO1 Interrupt (CiFSTAT<1> set)          |

|          | 0000000 = FIFO0 Interrupt (CiFSTAT<0> set)          |

|          |                                                     |

Note 1: These bits are only updated for enabled interrupts.

#### **REGISTER 25-13: ETHIEN: ETHERNET CONTROLLER INTERRUPT ENABLE REGISTER**

| Bit<br>Range | Bit<br>31/23/15/7       | Bit<br>30/22/14/6        | Bit<br>29/21/13/5       | Bit<br>28/20/12/4 | Bit<br>27/19/11/3       | Bit<br>26/18/10/2        | Bit<br>25/17/9/1         | Bit<br>24/16/8/0         |

|--------------|-------------------------|--------------------------|-------------------------|-------------------|-------------------------|--------------------------|--------------------------|--------------------------|

| 31:24        | U-0                     | U-0                      | U-0                     | U-0               | U-0                     | U-0                      | U-0                      | U-0                      |

| 31:24        |                         | —                        |                         | —                 |                         |                          |                          | —                        |

| 23:16        | U-0                     | U-0                      | U-0                     | U-0               | U-0                     | U-0                      | U-0                      | U-0                      |

| 23.10        | _                       | —                        | _                       | —                 |                         | _                        | —                        | —                        |

| 15:8         | U-0                     | R/W-0                    | R/W-0                   | U-0               | U-0                     | U-0                      | R/W-0                    | R/W-0                    |

| 10.0         | —                       | TXBUSEIE <sup>(1)</sup>  | RXBUSEIE <sup>(2)</sup> | _                 | _                       | —                        | EWMARKIE <sup>(2)</sup>  | FWMARKIE <sup>(2)</sup>  |

| 7:0          | R/W-0                   | R/W-0                    | R/W-0                   | U-0               | R/W-0                   | R/W-0                    | R/W-0                    | R/W-0                    |

| 7:0          | RXDONEIE <sup>(2)</sup> | PKTPENDIE <sup>(2)</sup> | RXACTIE <sup>(2)</sup>  |                   | TXDONEIE <sup>(1)</sup> | TXABORTIE <sup>(1)</sup> | RXBUFNAIE <sup>(2)</sup> | RXOVFLWIE <sup>(2)</sup> |

#### Legend:

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, r | ead as '0'         |

|-------------------|------------------|--------------------------|--------------------|

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared     | x = Bit is unknown |

bit 31-15 Unimplemented: Read as '0'

- bit 14 **TXBUSEIE:** Transmit BVCI Bus Error Interrupt Enable bit<sup>(1)</sup>

- 1 = Enable TXBUS Error Interrupt

- 0 = Disable TXBUS Error Interrupt

- bit 13 **RXBUSEIE:** Receive BVCI Bus Error Interrupt Enable bit<sup>(2)</sup>

- 1 = Enable RXBUS Error Interrupt 0 = Disable RXBUS Error Interrupt

- 0 = Disable RABOS Efformetry

- bit 12-10 Unimplemented: Read as '0'

| bit 9 | <b>EWMARKIE:</b> Empty Watermark Interrupt Enable bit <sup>(2)</sup><br>1 = Enable EWMARK Interrupt<br>0 = Disable EWMARK Interrupt                 |

|-------|-----------------------------------------------------------------------------------------------------------------------------------------------------|

| bit 8 | <b>FWMARKIE:</b> Full Watermark Interrupt Enable bit <sup>(2)</sup><br>1 = Enable FWMARK Interrupt<br>0 = Disable FWMARK Interrupt                  |

| bit 7 | <b>RXDONEIE:</b> Receiver Done Interrupt Enable bit <sup>(2)</sup><br>1 = Enable RXDONE Interrupt<br>0 = Disable RXDONE Interrupt                   |

| bit 6 | PKTPENDIE: Packet Pending Interrupt Enable bit <sup>(2)</sup><br>1 = Enable PKTPEND Interrupt<br>0 = Disable PKTPEND Interrupt                      |

| bit 5 | <b>RXACTIE:</b> RX Activity Interrupt Enable bit<br>1 = Enable RXACT Interrupt<br>0 = Disable RXACT Interrupt                                       |

| bit 4 | Unimplemented: Read as '0'                                                                                                                          |

| bit 3 | <b>TXDONEIE:</b> Transmitter Done Interrupt Enable bit <sup>(1)</sup><br>1 = Enable TXDONE Interrupt<br>0 = Disable TXDONE Interrupt                |

| bit 2 | <b>TXABORTIE:</b> Transmitter Abort Interrupt Enable bit <sup>(1)</sup><br>1 = Enable TXABORT Interrupt<br>0 = Disable TXABORT Interrupt            |

| bit 1 | <b>RXBUFNAIE:</b> Receive Buffer Not Available Interrupt Enable bit <sup>(2)</sup><br>1 = Enable RXBUFNA Interrupt<br>0 = Disable RXBUFNA Interrupt |

| bit 0 | <b>RXOVFLWIE:</b> Receive FIFO Overflow Interrupt Enable bit <sup>(2)</sup><br>1 = Enable RXOVFLW Interrupt<br>0 = Disable RXOVFLW Interrupt        |

- **Note 1:** This bit is only used for TX operations.

- **2:** This bit is only used for RX operations.

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |  |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|--|--|

| 31:24        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |  |  |

| 31.24        | —                 | —                 |                   | —                 | —                 | —                 |                  | —                |  |  |

| 22:46        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |  |  |

| 23:16        |                   | -                 |                   | —                 | —                 |                   |                  | —                |  |  |

| 15:8         | U-0               | U-0               | R/W-0             | U-0               | U-0               | U-0               | U-0              | U-0              |  |  |

| 15.6         | —                 | —                 | SIDL              | —                 | —                 | —                 |                  | —                |  |  |

| 7:0          | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | R-0              | R-0              |  |  |

| 7:0          | —                 | —                 | —                 | —                 |                   | —                 | C2OUT            | C1OUT            |  |  |

#### REGISTER 26-2: CMSTAT: COMPARATOR STATUS REGISTER

| -   | -    |  |

|-----|------|--|

|     | ond  |  |

| Leu | ena: |  |

|     |      |  |

| zogonan           |                      |                      |                    |  |

|-------------------|----------------------|----------------------|--------------------|--|

| R = Readable bit  | bit W = Writable bit |                      | ead as '0'         |  |

| -n = Value at POR | '1' = Bit is set     | '0' = Bit is cleared | x = Bit is unknown |  |

#### bit 31-14 Unimplemented: Read as '0'

bit 13 SIDL: Stop in Idle Control bit

1 = All Comparator modules are disabled while in Idle mode

0 = All Comparator modules continue to operate while in Idle mode

#### bit 12-2 Unimplemented: Read as '0'

- bit 1 **C2OUT:** Comparator Output bit

- 1 = Output of Comparator 2 is a '1'

- 0 = Output of Comparator 2 is a '0'

#### bit 0 C1OUT: Comparator Output bit

- 1 = Output of Comparator 1 is a '1'

- 0 = Output of Comparator 1 is a '0'

#### 31.11 Demonstration/Development Boards, Evaluation Kits, and Starter Kits

A wide variety of demonstration, development and evaluation boards for various PIC MCUs and dsPIC DSCs allows quick application development on fully functional systems. Most boards include prototyping areas for adding custom circuitry and provide application firmware and source code for examination and modification.

The boards support a variety of features, including LEDs, temperature sensors, switches, speakers, RS-232 interfaces, LCD displays, potentiometers and additional EEPROM memory.

The demonstration and development boards can be used in teaching environments, for prototyping custom circuits and for learning about various microcontroller applications.

In addition to the PICDEM<sup>™</sup> and dsPICDEM<sup>™</sup> demonstration/development board series of circuits, Microchip has a line of evaluation kits and demonstration software for analog filter design, KEELOQ<sup>®</sup> security ICs, CAN, IrDA<sup>®</sup>, PowerSmart battery management, SEEVAL<sup>®</sup> evaluation system, Sigma-Delta ADC, flow rate sensing, plus many more.

Also available are starter kits that contain everything needed to experience the specified device. This usually includes a single application and debug capability, all on one board.

Check the Microchip web page (www.microchip.com) for the complete list of demonstration, development and evaluation kits.

### 31.12 Third-Party Development Tools

Microchip also offers a great collection of tools from third-party vendors. These tools are carefully selected to offer good value and unique functionality.

- Device Programmers and Gang Programmers from companies, such as SoftLog and CCS

- Software Tools from companies, such as Gimpel and Trace Systems

- Protocol Analyzers from companies, such as Saleae and Total Phase

- Demonstration Boards from companies, such as MikroElektronika, Digilent<sup>®</sup> and Olimex

- Embedded Ethernet Solutions from companies, such as EZ Web Lynx, WIZnet and IPLogika<sup>®</sup>

| DC CHARACTERISTICS |                        |                                     | $\begin{array}{llllllllllllllllllllllllllllllllllll$ |                              |                           |      |               |  |

|--------------------|------------------------|-------------------------------------|------------------------------------------------------|------------------------------|---------------------------|------|---------------|--|

| Param.<br>No.      | Typical <sup>(3)</sup> | Max.                                | Units                                                | Units Conditions             |                           |      |               |  |

| Operatir           | ng Current (I          | DD) <sup>(1,2,4)</sup> f <b>O</b> I | PIC32MX5                                             | 575/675/695/775/795 Family D | )evices                   |      |               |  |

| DC20               | 6                      | 9                                   | mA                                                   | Code executing from Flash    | -40ºC,<br>+25ºC,<br>+85ºC |      | 4 MHz         |  |

| DC20b              | 7                      | 10                                  |                                                      |                              | +105⁰C                    |      |               |  |

| DC20a              | 4                      |                                     |                                                      | Code executing from SRAM     | _                         |      |               |  |

| DC21               | 37                     | 40                                  | mA                                                   | Code executing from Flash    |                           |      | 25 MHz        |  |

| DC21a              | 25                     |                                     | IIIA                                                 | Code executing from SRAM     | _                         | _    | 23 10112      |  |

| DC22               | 64                     | 70                                  | mA                                                   | Code executing from Flash    |                           |      | 60 MH-        |  |

| DC22a              | 61                     | _                                   | IIIA                                                 | Code executing from SRAM     |                           | _    | 60 MHz        |  |

| DC23               | 85                     | 98                                  | mA                                                   | Code executing from Flash    | -40ºC,<br>+25ºC,<br>+85ºC | _    | 80 MHz        |  |

| DC23b              | 90                     | 120                                 | ]                                                    |                              | +105⁰C                    |      |               |  |

| DC23a              | 85                     |                                     | ]                                                    | Code executing from SRAM     | —                         |      |               |  |

| DC25a              | 125                    | 150                                 | μA                                                   | —                            | +25°C                     | 3.3V | LPRC (31 kHz) |  |

#### TABLE 32-5: DC CHARACTERISTICS: OPERATING CURRENT (IDD)

**Note 1:** A device's IDD supply current is mainly a function of the operating voltage and frequency. Other factors, such as PBCLK (Peripheral Bus Clock) frequency, number of peripheral modules enabled, internal code execution pattern, execution from Program Flash memory vs. SRAM, I/O pin loading and switching rate, oscillator type, as well as temperature, can have an impact on the current consumption.

- 2: The test conditions for IDD measurements are as follows:

- Oscillator mode is EC (for 8 MHz and below) and EC+PLL (for above 8 MHz) with OSC1 driven by external square wave from rail-to-rail, (OSC1 input clock input over/undershoot < 100 mV required)</li>

- OSC2/CLKO is configured as an I/O input pin

- USB PLL oscillator is disabled if the USB module is implemented, PBCLK divisor = 1:8

- CPU, program Flash, and SRAM data memory are operational, program Flash memory Wait states = 111, Program Cache and Prefetch are disabled and SRAM data memory Wait states = 1

- No peripheral modules are operating, (ON bit = 0)

- WDT, Clock Switching, Fail-Safe Clock Monitor, and Secondary Oscillator are disabled

- All I/O pins are configured as inputs and pulled to Vss

- MCLR = VDD

- CPU executing while(1) statement from Flash

- RTCC and JTAG are disabled

- **3:** Data in "Typical" column is at 3.3V, 25°C at specified operating frequency unless otherwise stated. Parameters are for design guidance only and are not tested.

- **4:** All parameters are characterized, but only those parameters listed for 4 MHz and 80 MHz are tested at 3.3V in manufacturing.

#### TABLE 32-6: DC CHARACTERISTICS: IDLE CURRENT (IIDLE) (CONTINUED)

| DC CHARACTERISTICS                                                            |                        |      | $\begin{tabular}{lllllllllllllllllllllllllllllllllll$ |                     |            |                           |  |  |  |

|-------------------------------------------------------------------------------|------------------------|------|-------------------------------------------------------|---------------------|------------|---------------------------|--|--|--|

| Parameter<br>No.                                                              | Typical <sup>(2)</sup> | Max. | Units                                                 |                     | Conditions |                           |  |  |  |

| Idle Current (IIDLE) <sup>(1)</sup> for PIC32MX534/564/664/764 Family Devices |                        |      |                                                       |                     |            |                           |  |  |  |

| DC30a                                                                         | 1.5                    | 5    |                                                       | -40°C, +25°C, +85°C |            | 4 MHz                     |  |  |  |

| DC30c                                                                         | 3.5                    | 6    | mA                                                    | +105⁰C              | —          | 4 10172                   |  |  |  |

| DC31a                                                                         | 7                      | 11   |                                                       | -40°C, +25°C, +85°C | —          | 25 MHz (Note 3)           |  |  |  |

| DC32a                                                                         | 13                     | 20   | mA                                                    | -40°C, +25°C, +85°C | —          | 60 MHz (Note 3)           |  |  |  |

| DC33a                                                                         | 17                     | 25   | mA                                                    | -40°C, +25°C, +85°C |            | 80 MHz                    |  |  |  |

| DC33c                                                                         | 20                     | 27   | IIIA                                                  | +105°C              | —          | 00 1011 12                |  |  |  |

| DC34c                                                                         |                        | 40   |                                                       | -40°C               |            |                           |  |  |  |

| DC34d                                                                         |                        | 75   |                                                       | +25°C               | 2.3V       |                           |  |  |  |

| DC34e                                                                         |                        | 800  | μA                                                    | +85°C               | 2.3V       |                           |  |  |  |

| DC34f                                                                         |                        | 1000 |                                                       | +105°C              |            |                           |  |  |  |

| DC35c                                                                         | 30                     |      |                                                       | -40°C               |            |                           |  |  |  |

| DC35d                                                                         | 55                     |      |                                                       | +25°C               | 2.21/      | LPRC (31 kHz)<br>(Note 3) |  |  |  |

| DC35e                                                                         | 230                    | _    | μA                                                    | +85°C               | 3.3V       |                           |  |  |  |

| DC35f                                                                         | 800                    |      |                                                       | +105°C              |            |                           |  |  |  |

| DC36c                                                                         |                        | 43   |                                                       | -40°C               |            | 1                         |  |  |  |

| DC36d                                                                         |                        | 106  | <b>.</b>                                              | +25°C               | 2.01/      |                           |  |  |  |

| DC36e                                                                         |                        | 800  | μA                                                    | +85°C               | 3.6V       |                           |  |  |  |

| DC36f                                                                         |                        | 1000 | 1                                                     | +105°C              |            |                           |  |  |  |

Note 1: The test conditions for IIDLE current measurements are as follows:

- Oscillator mode is EC (for 8 MHz and below) and EC+PLL (for above 8 MHz) with OSC1 driven by external square wave from rail-to-rail, (OSC1 input clock input over/undershoot < 100 mV required)</li>

- OSC2/CLKO is configured as an I/O input pin

- USB PLL oscillator is disabled if the USB module is implemented, PBCLK divisor = 1:8

- CPU is in Idle mode, program Flash memory Wait states = 111, Program Cache and Prefetch are disabled and SRAM data memory Wait states = 1

- No peripheral modules are operating, (ON bit = 0)

- WDT, Clock Switching, Fail-Safe Clock Monitor, and Secondary Oscillator are disabled

- All I/O pins are configured as inputs and pulled to Vss

- MCLR = VDD

- RTCC and JTAG are disabled

- 2: Data in "Typical" column is at 3.3V, 25°C unless otherwise stated. Parameters are for design guidance only and are not tested.

- 3: This parameter is characterized, but not tested in manufacturing.

- **4:** All parameters are characterized, but only those parameters listed for 4 MHz and 80 MHz are tested at 3.3V in manufacturing.

| DC CHARACTERISTICS |        |                                                                       | $\begin{tabular}{lllllllllllllllllllllllllllllllllll$ |                        |                          |          |                                                                                                                                                                         |  |

|--------------------|--------|-----------------------------------------------------------------------|-------------------------------------------------------|------------------------|--------------------------|----------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| Param.<br>No.      | Symbol | Characteristics                                                       | Min.                                                  | Typical <sup>(1)</sup> | Max.                     | Units    | Conditions                                                                                                                                                              |  |

| DI50               | lil    | Input Leakage Current <sup>(3)</sup><br>I/O Ports                     | _                                                     | _                      | <u>+</u> 1               | μA       | Vss $\leq$ VPIN $\leq$ VDD,<br>Pin at high-impedance                                                                                                                    |  |

| DI51               |        | Analog Input Pins                                                     | —                                                     | —                      | <u>+</u> 1               | μΑ       | VSS $\leq$ VPIN $\leq$ VDD,<br>Pin at high-impedance                                                                                                                    |  |

| DI55<br>DI56       |        | MCLR <sup>(2)</sup><br>OSC1                                           | —                                                     | _                      | <u>+</u> 1<br><u>+</u> 1 | μΑ<br>μΑ | $\label{eq:VSS} \begin{array}{l} \forall SS \leq VPIN \leq VDD \\ \forall SS \leq VPIN \leq VDD, \\ XT \text{ and } HS \text{ modes} \end{array}$                       |  |

| DI60a              | licl   | Input Low Injection<br>Current                                        | 0                                                     | _                      | <sub>-5</sub> (7,10)     | mA       | This parameter applies<br>to all pins, with the<br>exception of RB10.<br>Maximum IICH current<br>for this exception is<br>0 mA.                                         |  |

| DI60b              | ІІСН   | Input High Injection<br>Current                                       | 0                                                     | _                      | +5 <sup>(8,9,10)</sup>   | mA       | This parameter applies<br>to all pins, with the<br>exception of all 5V toler-<br>ant pins, SOSCI, and<br>RB10. Maximum IICH<br>current for these<br>exceptions is 0 mA. |  |

| DI60c              | ∑IICT  | Total Input Injection<br>Current (sum of all I/O<br>and control pins) | -20 <sup>(11)</sup>                                   | _                      | +20 <sup>(11)</sup>      | mA       | Absolute instantaneous<br>sum of all $\pm$ input<br>injection currents from<br>all I/O pins<br>(   IICL +   IICH   ) $\leq \sum$ IICT                                   |  |

#### TABLE 32-8: DC CHARACTERISTICS: I/O PIN INPUT SPECIFICATIONS

Note 1: Data in "Typical" column is at 3.3V, 25°C unless otherwise stated. Parameters are for design guidance only and are not tested.

- 2: The leakage current on the MCLR pin is strongly dependent on the applied voltage level. The specified levels represent normal operating conditions. Higher leakage current may be measured at different input voltages.

- 3: Negative current is defined as current sourced by the pin.

- 4: This parameter is characterized, but not tested in manufacturing.

- 5: See the "Device Pin Tables" section for the 5V-tolerant pins.

- 6: The VIH specification is only in relation to externally applied inputs and not with respect to the user-selectable pull-ups. Externally applied high impedance or open drain input signals utilizing the PIC32 internal pullups are guaranteed to be recognized as a logic "high" internally to the PIC32 device, provided that the external load does not exceed the maximum value of ICNPU.

- 7: VIL source < (VSS 0.3). Characterized but not tested.

- 8: VIH source > (VDD + 0.3) for non-5V tolerant pins only.

- **9:** Digital 5V tolerant pins do not have an internal high side diode to VDD, and therefore, cannot tolerate any "positive" input injection current.

- **10:** Injection currents > | 0 | can affect the ADC results by approximately 4 to 6 counts (i.e., VIH Source > (VDD + 0.3) or VIL source < (VSS 0.3)).

- 11: Any number and/or combination of I/O pins not excluded under IICL or IICH conditions are permitted provided the "absolute instantaneous" sum of the input injection currents from all pins do not exceed the specified limit. If Note 7, IICL = (((Vss 0.3) VIL source) / Rs). If Note 8, IICH = ((IICH source (VDD + 0.3)) / RS). RS = Resistance between input source voltage and device pin. If (Vss 0.3) ≤ VSOURCE ≤ (VDD + 0.3), injection current = 0.

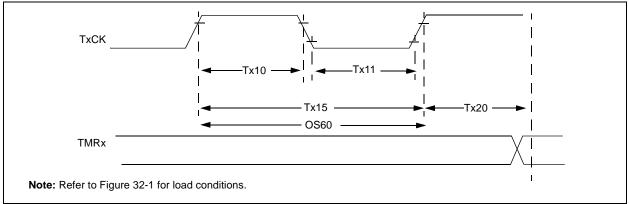

#### FIGURE 32-6: TIMER1, 2, 3, 4, 5 EXTERNAL CLOCK TIMING CHARACTERISTICS

### TABLE 32-23: TIMER1 EXTERNAL CLOCK TIMING REQUIREMENTS<sup>(1)</sup>

| AC CHA        |           | TICS                                                         |                                                                                                     | (unl |                                            | ions: 2.3<br>°C ≤ Ta ≤<br>°C ≤ Ta ≤ | +85°C                                      | for Ind |                                  |    |            |

|---------------|-----------|--------------------------------------------------------------|-----------------------------------------------------------------------------------------------------|------|--------------------------------------------|-------------------------------------|--------------------------------------------|---------|----------------------------------|----|------------|

| Param.<br>No. | Symbol    | Charac                                                       | teristics <sup>(2)</sup>                                                                            |      | Min.                                       | Typical                             | Max.                                       | Units   | Conditions                       |    |            |

| TA10          | T⊤xH      | TxCK<br>High Time                                            | Synchrono<br>with presca                                                                            |      | [(12.5 ns or 1 ТРВ)/N]<br>+ 25 ns          | —                                   | —                                          | ns      | Must also meet parameter TA15    |    |            |

|               |           |                                                              | Asynchron<br>with presca                                                                            |      | 10                                         |                                     | —                                          | ns      | —                                |    |            |

| TA11          | T⊤xL      | TxCK<br>Low Time                                             | Synchrono<br>with presca                                                                            |      | [(12.5 ns or 1 Трв)/N]<br>+ 25 ns          | _                                   | _                                          | ns      | Must also meet<br>parameter TA15 |    |            |

|               |           |                                                              | Asynchronous,<br>with prescaler                                                                     |      | 10                                         | _                                   | —                                          | ns      | _                                |    |            |

| TA15          | ΤτχΡ      | TxCK<br>Input Period                                         | Synchronous,<br>d with prescaler                                                                    |      |                                            |                                     | [(Greater of 25 ns or<br>2 TPB)/N] + 30 ns |         | _                                | ns | VDD > 2.7V |

|               |           |                                                              |                                                                                                     |      | [(Greater of 25 ns or<br>2 TPB)/N] + 50 ns | —                                   | _                                          | ns      | Vdd < 2.7V                       |    |            |

|               |           |                                                              | Asynchron<br>with presca                                                                            |      | 20                                         | —                                   | _                                          | ns      | VDD > 2.7V<br>(Note 3)           |    |            |

|               |           |                                                              |                                                                                                     |      | 50                                         | —                                   | _                                          | ns      | VDD < 2.7V<br>(Note 3)           |    |            |

| OS60          | FT1       | Input Freque<br>(oscillator en                               | OSC1/T1CK Oscillator<br>nput Frequency Range<br>oscillator enabled by setting<br>CS bit (T1CON<1>)) |      | 32                                         | —                                   | 100                                        | kHz     | _                                |    |            |

| TA20          | TCKEXTMRL | Delay from External TxCK<br>Clock Edge to Timer<br>Increment |                                                                                                     | ĸ    | —                                          | —                                   | 1                                          | Трв     | —                                |    |            |

Note 1: Timer1 is a Type A.

2: This parameter is characterized, but not tested in manufacturing.

**3:** N = Prescale Value (1, 8, 64, 256).

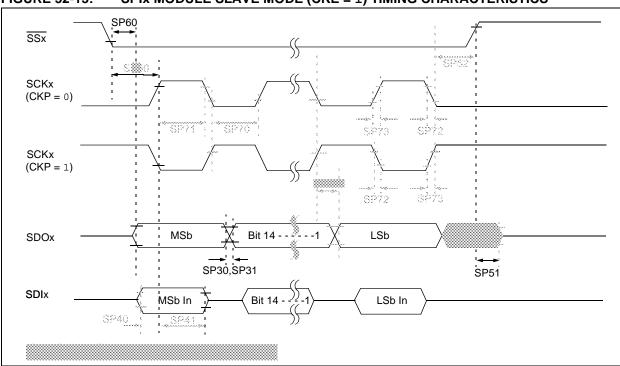

#### FIGURE 32-13: SPIX MODULE SLAVE MODE (CKE = 1) TIMING CHARACTERISTICS

#### TABLE 32-31: SPIX MODULE SLAVE MODE (CKE = 1) TIMING REQUIREMENTS

| AC CHA        |                       | (unless o                                                                 | d Operating<br>otherwise st<br>g temperatur | t <b>ated)</b><br>e -40° | °C ≤ TA ≤ | <b>3V to 3.6V</b><br>≤ +85°C for Industrial<br>≤ +105°C for V-Temp |                    |

|---------------|-----------------------|---------------------------------------------------------------------------|---------------------------------------------|--------------------------|-----------|--------------------------------------------------------------------|--------------------|

| Param.<br>No. | Symbol                | Characteristics <sup>(1)</sup>                                            | Min.                                        | Typical <sup>(2)</sup>   | Max.      | Units                                                              | Conditions         |

| SP70          | TscL                  | SCKx Input Low Time <sup>(3)</sup>                                        | Tsck/2                                      |                          | —         | ns                                                                 | —                  |

| SP71          | TscH                  | SCKx Input High Time <sup>(3)</sup>                                       | Tsck/2                                      | —                        | _         | ns                                                                 | —                  |

| SP72          | TscF                  | SCKx Input Fall Time                                                      | _                                           | 5                        | 10        | ns                                                                 | —                  |

| SP73          | TscR                  | SCKx Input Rise Time                                                      |                                             | 5                        | 10        | ns                                                                 | —                  |

| SP30          | TDOF                  | SDOx Data Output Fall Time <sup>(4)</sup>                                 | —                                           | —                        | _         | ns                                                                 | See parameter DO32 |

| SP31          | TDOR                  | SDOx Data Output Rise Time <sup>(4)</sup>                                 |                                             | —                        | _         | ns                                                                 | See parameter DO31 |

| SP35          | TscH2doV,             | SDOx Data Output Valid after                                              |                                             | _                        | 20        | ns                                                                 | VDD > 2.7V         |

|               | TscL2doV              | SCKx Edge                                                                 |                                             | _                        | 30        | ns                                                                 | VDD < 2.7V         |