Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFl

| Details                    |                                                                                   |

|----------------------------|-----------------------------------------------------------------------------------|

| Product Status             | Active                                                                            |

| Core Processor             | MIPS32® M4K™                                                                      |

| Core Size                  | 32-Bit Single-Core                                                                |

| Speed                      | 80MHz                                                                             |

| Connectivity               | Ethernet, I <sup>2</sup> C, SPI, UART/USART, USB OTG                              |

| Peripherals                | Brown-out Detect/Reset, DMA, POR, PWM, WDT                                        |

| Number of I/O              | 83                                                                                |

| Program Memory Size        | 256KB (256K x 8)                                                                  |

| Program Memory Type        | FLASH                                                                             |

| EEPROM Size                | -                                                                                 |

| RAM Size                   | 64K x 8                                                                           |

| Voltage - Supply (Vcc/Vdd) | 2.3V ~ 3.6V                                                                       |

| Data Converters            | A/D 16x10b                                                                        |

| Oscillator Type            | Internal                                                                          |

| Operating Temperature      | -40°C ~ 105°C (TA)                                                                |

| Mounting Type              | Surface Mount                                                                     |

| Package / Case             | 121-TFBGA                                                                         |

| Supplier Device Package    | 121-TFBGA (10x10)                                                                 |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic32mx675f256lt-80v-bg |

|                            |                                                                                   |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

1

#### TABLE 9: PIN NAMES FOR 100-PIN USB, ETHERNET, AND CAN DEVICES (CONTINUED)

#### **100-PIN TQFP (TOP VIEW)**

PIC32MX764F128L PIC32MX775F256L PIC32MX775F512L PIC32MX795F512L

100

| Pin # | Full Pin Name                   | Pin # | Full Pin Name                        |

|-------|---------------------------------|-------|--------------------------------------|

| 71    | EMDC/AEMDC/IC4/PMCS1/PMA14/RD11 | 86    | VDD                                  |

| 72    | SDO1/OC1/INT0/RD0               | 87    | C1RX/ETXD1/PMD11/RF0                 |

| 73    | SOSCI/CN1/RC13                  | 88    | C1TX/ETXD0/PMD10/RF1                 |

| 74    | SOSCO/T1CK/CN0/RC14             | 89    | C2TX <sup>(1)</sup> /ETXERR/PMD9/RG1 |

| 75    | Vss                             | 90    | C2RX <sup>(1)</sup> /PMD8/RG0        |

| 76    | OC2/RD1                         | 91    | TRCLK/RA6                            |

| 77    | OC3/RD2                         | 92    | TRD3/RA7                             |

| 78    | OC4/RD3                         | 93    | PMD0/RE0                             |

| 79    | ETXD2/IC5/PMD12/RD12            | 94    | PMD1/RE1                             |

| 80    | ETXD3/PMD13/CN19/RD13           | 95    | TRD2/RG14                            |

| 81    | OC5/PMWR/CN13/RD4               | 96    | TRD1/RG12                            |

| 82    | PMRD/CN14/RD5                   | 97    | TRD0/RG13                            |

| 83    | ETXEN/PMD14/CN15/RD6            | 98    | PMD2/RE2                             |

| 84    | ETXCLK/PMD15/CN16/RD7           | 99    | PMD3/RE3                             |

| 85    | VCAP/VDDCORE                    | 100   | PMD4/RE4                             |

Note 1: This pin is not available on PIC32MX764F128L devices.

2: Shaded pins are 5V tolerant.

### TABLE 10: PIN NAMES FOR USB AND CAN DEVICES

| 121        | PIN TFBGA (BOTTOM VIEW)                                                                     |       | L11                              |     |

|------------|---------------------------------------------------------------------------------------------|-------|----------------------------------|-----|

|            | PIC32MX534F064L<br>PIC32MX564F064L<br>PIC32MX564F128L<br>PIC32MX575F256L<br>PIC32MX575F512L | L1    |                                  | A11 |

|            | The TFBGA package skips from row "H" to                                                     |       |                                  |     |

| Pin #      | Full Pin Name                                                                               | Pin # | Full Pin Name                    |     |

| A1         | PMD4/RE4                                                                                    | E2    | T4CK/RC3                         |     |

| A2         | PMD3/RE3                                                                                    | E3    | SCK2/U6TXU6TX/U3RTS/PMA5/CN8/RG6 |     |

| A3         | TRD0/RG13                                                                                   | E4    | T3CK/RC2                         |     |

| A4         | PMD0/RE0                                                                                    | E5    | Vdd                              |     |

| A5         | PMD8/RG0                                                                                    | E6    | PMD9/RG1                         |     |

| A6         | C1TX/PMD10/RF1                                                                              | E7    | Vss                              |     |

| A7         | Vdd                                                                                         | E8    | SDA1/INT4/RA15                   |     |

| A8         | Vss                                                                                         | E9    | RTCC/IC1/RD8                     |     |

| A9         | IC5/PMD12/RD12                                                                              | E10   | SS1/IC2/RD9                      |     |

| A10        | OC3/RD2                                                                                     | E11   | SCL1/INT3/RA14                   |     |

| A11        | OC2/RD1                                                                                     | F1    | MCLR                             |     |

| B1         | No Connect (NC)                                                                             | F2    | SCL4/SDO2/U3TX/PMA3/CN10/RG8     |     |

| B2         | RG15                                                                                        | F3    | SS2/U6RX/U3CTS/PMA2/CN11/RG9     |     |

| B3         | PMD2/RE2                                                                                    | F4    | SDA4/SDI2/U3RX/PMA4/CN9/RG7      |     |

| B3<br>B4   | PMD1/RE1                                                                                    | F5    | Vss                              |     |

| B5         | TRD3/RA7                                                                                    | F6    | No Connect (NC)                  |     |

| B6         | C1RX/PMD11/RF0                                                                              | F7    | No Connect (NC)                  |     |

| B7         | VCAP                                                                                        | F8    | VDD                              |     |

| B8         | PMRD/CN14/RD5                                                                               | F9    | OSC1/CLKI/RC12                   |     |

| B9         | OC4/RD3                                                                                     |       | Vss                              |     |

| B10        | Vss                                                                                         | F11   | OSC2/CLKO/RC15                   |     |

| B10<br>B11 | SOSCO/T1CK/CN0/RC14                                                                         | G1    | INT1/RE8                         |     |

| C1         | PMD6/RE6                                                                                    | G2    | INT2/RE9                         |     |

| C2         | VDD                                                                                         | G3    | TMS/RA0                          |     |

| C3         | TRD1/RG12                                                                                   | G4    | No Connect (NC)                  |     |

| C4         | TRD2/RG14                                                                                   | G5    | VDD                              |     |

| C5         | TRCLK/RA6                                                                                   | G6    | Vss                              |     |

| C6         | No Connect (NC)                                                                             | G7    | Vss                              |     |

| C7         | PMD15/CN16/RD7                                                                              | G8    | No Connect (NC)                  |     |

| C8         | OC5/PMWR/CN13/RD4                                                                           | G9    | TDO/RA5                          |     |

| C9         | VDD                                                                                         | G10   | SDA2/RA3                         |     |

| C10        | SOSCI/CN1/RC13                                                                              | G11   | TDI/RA4                          |     |

| C11        | IC4/PMCS1/PMA14/RD11                                                                        | H1    | AN5/C1IN+/VBUSON/CN7/RB5         |     |

| D1         | T2CK/RC1                                                                                    | H2    | AN4/C1IN-/CN6/RB4                |     |

| D2         | PMD7/RE7                                                                                    | H3    | Vss                              |     |

| D3         | PMD5/RE5                                                                                    | H4    | VDD                              |     |

| D4         | Vss                                                                                         | H5    | No Connect (NC)                  |     |

| D5         | Vss                                                                                         | H6    | VDD                              |     |

| D6         | No Connect (NC)                                                                             | H7    | No Connect (NC)                  |     |

| D7         | PMD14/CN15/RD6                                                                              | H8    | VBUS                             |     |

| D8         | PMD13/CN19/RD13                                                                             | H9    | VUSB3V3                          |     |

| D9         | SDO1/OC1/INT0/RD0                                                                           | H10   | D+/RG2                           |     |

| D10        | No Connect (NC)                                                                             | H11   | SCL2/RA2                         |     |

| D11        | SCK1/IC3/PMCS2/PMA15/RD10                                                                   | J1    | AN3/C2IN+/CN5/RB3                |     |

|            |                                                                                             | 51    |                                  |     |

## 1.0 DEVICE OVERVIEW

**Note:** This data sheet summarizes the features of the PIC32MX5XX/6XX/7XX family of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to the documents listed in the *Documentation* > *Reference Manual* section of the Microchip PIC32 web site (www.microchip.com/pic32).

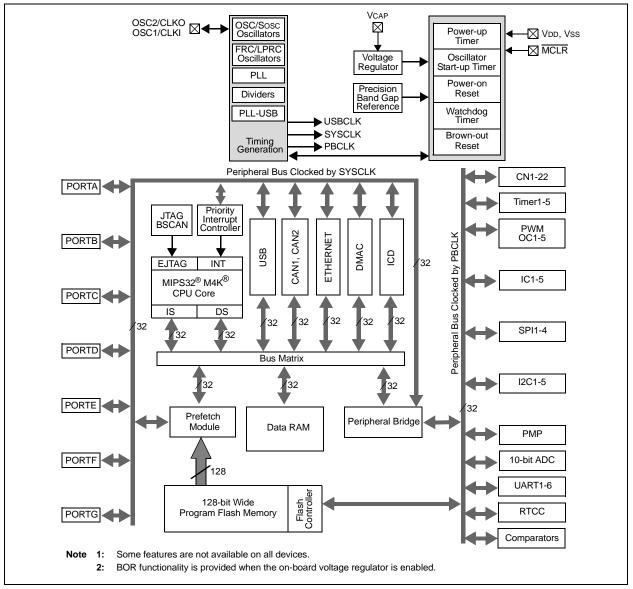

FIGURE 1-1: BLOCK DIAGRAM<sup>(1,2)</sup>

This document contains device-specific information for PIC32MX5XX/6XX/7XX devices.

Figure 1-1 illustrates a general block diagram of the core and peripheral modules in the PIC32MX5XX/6XX/7XX family of devices.

Table 1-1 lists the functions of the various pins shown in the pinout diagrams.

### 2.0 GUIDELINES FOR GETTING STARTED WITH 32-BIT MCUS

**Note:** This data sheet summarizes the features of the PIC32MX5XX/6XX/7XX family of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to the related section of the *"PIC32 Family Reference Manual"*, which is available from the Microchip web site (www.microchip.com/PIC32).

### 2.1 Basic Connection Requirements

Getting started with the PIC32MX5XX/6XX/7XX family of 32-bit Microcontrollers (MCUs) requires attention to a minimal set of device pin connections before proceeding with development. The following is a list of pin names, which must always be connected:

- All VDD and Vss pins (see 2.2 "Decoupling Capacitors")

- All AVDD and AVss pins even if the ADC module is not used (see 2.2 "Decoupling Capacitors")

- VCAP pin (see 2.3 "Capacitor on Internal Voltage Regulator (VCAP)")

- MCLR pin (see 2.4 "Master Clear (MCLR) Pin")

- PGECx/PGEDx pins used for In-Circuit Serial Programming<sup>™</sup> (ICSP<sup>™</sup>) and debugging purposes (see **2.5** "ICSP Pins")

- OSC1 and OSC2 pins when external oscillator source is used (see 2.8 "External Oscillator Pins")

The following pin may be required, as well: VREF+/ VREF- pins used when external voltage reference for ADC module is implemented.

**Note:** The AVDD and AVSS pins must be connected, regardless of the ADC use and the ADC voltage reference source.

### 2.2 Decoupling Capacitors

The use of decoupling capacitors on power supply pins, such as VDD, VSS, AVDD and AVSS is required. See Figure 2-1.

Consider the following criteria when using decoupling capacitors:

- Value and type of capacitor: A value of 0.1  $\mu$ F (100 nF), 10-20V is recommended. The capacitor should be a low Equivalent Series Resistance (low-ESR) capacitor and have resonance frequency in the range of 20 MHz and higher. It is further recommended to use ceramic capacitors.

- Placement on the printed circuit board: The decoupling capacitors should be placed as close to the pins as possible. It is recommended that the capacitors be placed on the same side of the board as the device. If space is constricted, the capacitor can be placed on another layer on the PCB using a via; however, ensure that the trace length from the pin to the capacitor is within one-quarter inch (6 mm) in length.

- Handling high frequency noise: If the board is experiencing high frequency noise, upward of tens of MHz, add a second ceramic-type capacitor in parallel to the above described decoupling capacitor. The value of the second capacitor can be in the range of 0.01  $\mu$ F to 0.001  $\mu$ F. Place this second capacitor next to the primary decoupling capacitor. In high-speed circuit designs, consider implementing a decade pair of capacitances as close to the power and ground pins as possible. For example, 0.1  $\mu$ F in parallel with 0.001  $\mu$ F.

- Maximizing performance: On the board layout from the power supply circuit, run the power and return traces to the decoupling capacitors first, and then to the device pins. This ensures that the decoupling capacitors are first in the power chain. Equally important is to keep the trace length between the capacitor and the power pins to a minimum, thereby reducing PCB track inductance.

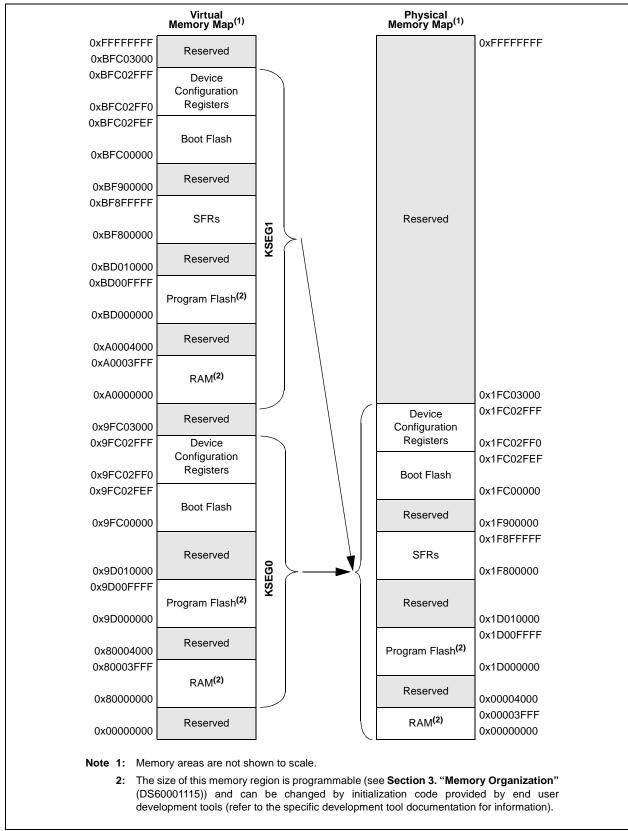

# FIGURE 4-2: MEMORY MAP ON RESET FOR PIC32MX534F064H AND PIC32MX534F064L DEVICES

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |  |  |  |  |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|--|--|--|--|--|

| 04.04        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |  |  |  |  |  |

| 31:24        | -                 | _                 | _                 | —                 | _                 | —                 | —                | —                |  |  |  |  |  |

| 00.40        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |  |  |  |  |  |

| 23:16        | -                 | —                 | —                 | —                 | —                 | —                 | —                | —                |  |  |  |  |  |

| 45.0         | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R-0              | R-0              |  |  |  |  |  |

| 15:8         |                   |                   |                   | BMXDU             | DBA<15:8>         |                   |                  |                  |  |  |  |  |  |

| 7.0          | R-0               | R-0               | R-0               | R-0               | R-0               | R-0               | R-0              | R-0              |  |  |  |  |  |

| 7:0          | BMXDUDBA<7:0>     |                   |                   |                   |                   |                   |                  |                  |  |  |  |  |  |

#### REGISTER 4-3: BMXDUDBA: DATA RAM USER DATA BASE ADDRESS REGISTER

### Legend:

| Legena:           |                  |                           |                    |

|-------------------|------------------|---------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, re | ad as '0'          |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared      | x = Bit is unknown |

bit 31-16 Unimplemented: Read as '0'

#### bit 15-10 BMXDUDBA<15:10>: DRM User Data Base Address bits

When non-zero, the value selects the relative base address for User mode data space in RAM, the value must be greater than BMXDKPBA.

bit 9-0 BMXDUDBA<9:0>: DRM User Data Base Address Read-Only bits Value is always '0', which forces 1 KB increments

**Note 1:** At Reset, the value in this register is forced to zero, which causes all of the RAM to be allocated to Kernal mode data usage.

2: The value in this register must be less than or equal to BMXDRMSZ.

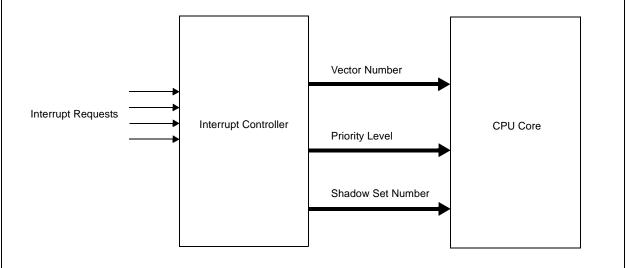

# 7.0 INTERRUPT CONTROLLER

Note: This data sheet summarizes the features of the PIC32MX5XX/6XX/7XX family of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to **Section 8. "Interrupts"** (DS60001108) in the *"PIC32 Family Reference Manual"*, which is available from the Microchip web site (www.microchip.com/PIC32).

PIC32MX5XX/6XX/7XX devices generate interrupt requests in response to interrupt events from peripheral modules. The interrupt control module exists externally to the CPU logic and prioritizes the interrupt events before presenting them to the CPU.

The Interrupt Controller module includes the following features:

- Up to 96 interrupt sources

- Up to 64 interrupt vectors

- Single and multi-vector mode operations

- · Five external interrupts with edge polarity control

- Interrupt proximity timer

- Seven user-selectable priority levels for each vector

- Four user-selectable sub-priority levels within each priority

- Dedicated shadow set for user-selectable priority level

- Software can generate any interrupt

- User-configurable interrupt vector table location

- · User-configurable interrupt vector spacing

A simplified block diagram of the Interrupt Controller module is illustrated in Figure 7-1.

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|

| 21.24        | R/W-0             | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 31:24        | CHEWEN            | —                 | _                 | —                 | —                 | -                 | —                | —                |

| 22:16        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 23:16        | -                 | —                 |                   | —                 | —                 |                   | —                | —                |

| 15:8         | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 15.0         |                   | —                 |                   | —                 | —                 |                   | —                | —                |

| 7.0          | U-0               | U-0               | U-0               | U-0               | R/W-0             | R/W-0             | R/W-0            | R/W-0            |

| 7:0          |                   |                   |                   | —                 |                   | CHEID             | X<3:0>           |                  |

#### REGISTER 9-2: CHEACC: CACHE ACCESS REGISTER

#### Legend:

| R = Readable bit  | W = Writable bit | U = Unimplemented bit | , read as '0'      |  |

|-------------------|------------------|-----------------------|--------------------|--|

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared  | x = Bit is unknown |  |

#### bit 31 CHEWEN: Cache Access Enable bits

- These bits apply to registers CHETAG, CHEMSK, CHEW0, CHEW1, CHEW2, and CHEW3.

- 1 = The cache line selected by CHEIDX<3:0> is writeable

- 0 = The cache line selected by CHEIDX<3:0> is not writeable

- bit 30-4 **Unimplemented:** Write '0'; ignore read

#### bit 3-0 CHEIDX<3:0>: Cache Line Index bits

The value selects the cache line for reading or writing.

# 11.0 USB ON-THE-GO (OTG)

Note: This data sheet summarizes the features of the PIC32MX5XX/6XX/7XX family of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to Section 27. "USB On-The-Go (OTG)" (DS60001126) in the "PIC32 Family Reference Manual", which is available from the Microchip web site (www.microchip.com/PIC32).

The Universal Serial Bus (USB) module contains analog and digital components to provide a USB 2.0 full-speed and low-speed embedded Host, full-speed Device or OTG implementation with a minimum of external components. This module in Host mode is intended for use as an embedded host and therefore does not implement a UHCI or OHCI controller.

The USB module consists of the clock generator, the USB voltage comparators, the transceiver, the Serial Interface Engine (SIE), a dedicated USB DMA controller, pull-up and pull-down resistors, and the register interface. A block diagram of the PIC32 USB OTG module is presented in Figure 11-1.

The clock generator provides the 48 MHz clock required for USB full-speed and low-speed communication. The voltage comparators monitor the voltage on the VBUS pin to determine the state of the bus. The transceiver provides the analog translation between the USB bus and the digital logic. The SIE is a state machine that transfers data to and from the endpoint buffers and generates the hardware protocol for data transfers. The USB DMA controller transfers data between the data buffers in RAM and the SIE. The integrated pull-up and pull-down resistors eliminate the need for external signaling components. The register interface allows the CPU to configure and communicate with the module.

The USB module includes the following features:

- USB Full-speed support for host and device

- Low-speed host support

- USB OTG support

- Integrated signaling resistors

- Integrated analog comparators for VBUS monitoring

- Integrated USB transceiver

- Transaction handshaking performed by hardware

- Endpoint buffering anywhere in system RAM

- Integrated DMA to access system RAM and Flash

- The implementation and use of the USB Note: specifications, as well as other third party may specifications or technologies, require licensing; including, but not limited to, USB Implementers Forum, Inc. (also referred to as USB-IF). The user is fully responsible for investigating and satisfying any applicable licensing obligations.

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|

| 31:24        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 31.24        | _                 | _                 |                   | _                 |                   |                   | —                | —                |

| 23:16        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 23.10        | _                 | -                 | _                 | _                 |                   | _                 | —                | _                |

| 15:8         | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 15.0         | _                 | -                 | _                 | _                 |                   | _                 | —                | _                |

| 7:0          | R-0               | U-0               | U-0               | R/W-0             | R/W-0             | U-0               | R/W-0            | R/W-0            |

| 7.0          | UACTPND           | _                 |                   | USLPGRD           | USBBUSY           |                   | USUSPEND         | USBPWR           |

#### REGISTER 11-5: U1PWRC: USB POWER CONTROL REGISTER

### Legend:

| Logona.           |                  |                            |                    |

|-------------------|------------------|----------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, rea | id as '0'          |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared       | x = Bit is unknown |

#### bit 31-8 Unimplemented: Read as '0'

- bit 7 UACTPND: USB Activity Pending bit

- 1 = USB bus activity has been detected; but an interrupt is pending, it has not been generated yet

- 0 = An interrupt is not pending

#### bit 6-5 Unimplemented: Read as '0'

- bit 4 USLPGRD: USB Sleep Entry Guard bit

- 1 = Sleep entry is blocked if USB bus activity is detected or if a notification is pending

- 0 = USB module does not block Sleep entry

#### bit 3 USBBUSY: USB Module Busy bit

- 1 = USB module is active or disabled, but not ready to be enabled

- 0 = USB module is not active and is ready to be enabled

- **Note:** When USBPWR = 0 and USBBUSY = 1, status from all other registers is invalid and writes to all USB module registers produce undefined results.

#### bit 2 Unimplemented: Read as '0'

#### bit 1 USUSPEND: USB Suspend Mode bit

- 1 = USB module is placed in Suspend mode

- (The 48 MHz USB clock will be gated off. The transceiver is placed in a low-power state.)

- 0 = USB module operates normally

- bit 0 USBPWR: USB Operation Enable bit

- 1 = USB module is turned on

- 0 = USB module is disabled

(Outputs held inactive, device pins not used by USB, analog features are shut down to reduce power consumption.)

#### TABLE 12-3: PORTC REGISTER MAP FOR PIC32MX534F064H, PIC32MX564F064H, PIC32MX564F128H, PIC32MX575F256H, PIC32MX575F512H, PIC32MX664F064H, PIC32MX664F128H, PIC32MX675F256H, PIC32MX675F512H, PIC32MX695F512H, PIC32MX764F128H, PIC32MX775F256H, PIC32MX775F512H AND PIC32MX795F512H DEVICES

| ess                         |                                 | n         |         |          |            |             |             |             |            | Bi      | ts   |      |      |      |      |      |      |      | ő          |

|-----------------------------|---------------------------------|-----------|---------|----------|------------|-------------|-------------|-------------|------------|---------|------|------|------|------|------|------|------|------|------------|

| Virtual Address<br>(BF88_#) | Register<br>Name <sup>(1)</sup> | Bit Range | 31/15   | 30/14    | 29/13      | 28/12       | 27/11       | 26/10       | 25/9       | 24/8    | 23/7 | 22/6 | 21/5 | 20/4 | 19/3 | 18/2 | 17/1 | 16/0 | All Resets |

| 6080                        | TRISC                           | 31:16     | —       | _        | -          | —           | _           | -           | —          | _       | -    | -    | -    | _    | _    | _    | _    | -    | 0000       |

| 6060                        | IRISC                           | 15:0      | TRISC15 | TRISC14  | TRISC13    | TRISC12     | _           | _           | _          | _       | _    | _    | _    | _    | _    | _    | _    | _    | F000       |

| 6000                        | PORTC                           | 31:16     | —       | -        |            | —           | —           |             | -          |         |      | _    |      | _    | _    | -    | _    |      | 0000       |

| 6090                        | PURIC                           | 15:0      | RC15    | RC14     | RC13       | RC12        | _           | -           | —          | -       | -    | -    | -    | -    |      | -    |      | -    | xxxx       |

| 60A0                        | LATC                            | 31:16     | _       | _        | _          | _           | _           | _           | _          | _       | _    | _    | _    | _    | _    | _    | _    | _    | 0000       |

| 60A0                        | LAIC                            | 15:0      | LATC15  | LATC14   | LATC13     | LATC12      | _           | _           | -          | —       | _    | —    | _    | —    | _    | _    | _    | _    | xxxx       |

| 60B0                        | ODCC                            | 31:16     | _       | _        | _          | _           | _           | _           | _          | _       | _    | _    | _    | _    | _    | _    | _    | _    | 0000       |

| 00B0                        | ODCC                            | 15:0      | ODCC15  | ODCC14   | ODCC13     | ODCC12      | _           | _           | —          | _       | _    | _    | _    | _    | _    | _    | _    | _    | 0000       |

| Logon                       | 4                               | - unkno   |         | Pocot: - | unimplomon | ted read as | '0' Poset v | luce are ch | we in hove | locimol |      |      |      |      |      |      |      |      |            |

Legend: x = unknown value on Reset; — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

Note 1: All registers in this table have corresponding CLR, SET and INV registers at their virtual addresses, plus offsets of 0x4, 0x8 and 0xC, respectively. See Section 12.1.1 "CLR, SET and INV Registers" for more information.

#### TABLE 12-4: PORTC REGISTER MAP FOR PIC32MX534F064L, PIC32MX564F064L, PIC32MX564F128L, PIC32MX575F256L, PIC32MX575F512L, PIC32MX664F064L, PIC32MX664F128L, PIC32MX675F256L, PIC32MX675F512L, PIC32MX695F512L, PIC32MX764F128L. PIC32MX775F256L. PIC32MX775F512L AND PIC32MX795F512L DEVICES

| ess                         |                                 | 0         |         |         |         |         |       |       |      | Bi   | ts   |      |      |        |        |        |        |      | ú          |

|-----------------------------|---------------------------------|-----------|---------|---------|---------|---------|-------|-------|------|------|------|------|------|--------|--------|--------|--------|------|------------|

| Virtual Address<br>(BF88_#) | Register<br>Name <sup>(1)</sup> | Bit Range | 31/15   | 30/14   | 29/13   | 28/12   | 27/11 | 26/10 | 25/9 | 24/8 | 23/7 | 22/6 | 21/5 | 20/4   | 19/3   | 18/2   | 17/1   | 16/0 | All Resets |

| 6080                        | TRISC                           | 31:16     |         | _       | _       | _       | _     | _     | _    | _    | _    | _    | _    | _      | _      | _      | _      | _    | 0000       |

| 6060                        | TRISC                           | 15:0      | TRISC15 | TRISC14 | TRISC13 | TRISC12 | _     | _     | _    | _    | _    | _    | _    | TRISC4 | TRISC3 | TRISC2 | TRISC1 | _    | FOOF       |

| 6000                        | PORTC                           | 31:16     | _       | —       | —       | —       | —     | —     | —    | —    | _    | —    | —    | —      | —      | —      | —      | —    | 0000       |

| 6090                        | PURIC                           | 15:0      | RC15    | RC14    | RC13    | RC12    | _     | _     | —    | —    | _    | —    | —    | RC4    | RC3    | RC2    | RC1    | —    | xxxx       |

| 60A0                        | LATC                            | 31:16     | _       | _       | _       | _       | _     | _     | _    | _    | _    | _    | _    | _      | _      | _      | _      | _    | 0000       |

| 60A0                        | LAIC                            | 15:0      | LATC15  | LATC14  | LATC13  | LATC12  | _     | _     | —    | —    | _    | —    | —    | LATC4  | LATC3  | LATC2  | LATC1  | —    | xxxx       |

| 60B0                        | ODCC                            | 31:16     | —       | _       | _       | —       | _     | _     | _    | _    | _    | _    | _    | _      | _      | _      | _      | _    | 0000       |

| 00B0                        | ODCC                            | 15:0      | ODCC15  | ODCC14  | ODCC13  | ODCC12  | _     | _     | _    | _    | _    | _    | _    | ODCC4  | ODCC3  | ODCC2  | ODCC1  | _    | 0000       |

Legend: x = unknown value on Reset; --- = unimplemented, read as '0'. Reset values are shown in hexadecimal.

Note 1: All registers in this table have corresponding CLR, SET and INV registers at their virtual addresses, plus offsets of 0x4, 0x8 and 0xC, respectively. See Section 12.1.1 "CLR, SET and INV Registers" for more information

| Bit<br>Range | Bit<br>31/23/15/7   | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

|--------------|---------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|

| 04.04        | U-0                 | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 31:24        |                     |                   |                   |                   | _                 |                   | _                | —                |

| 00.40        | U-0                 | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 23:16        | _                   | _                 | _                 |                   | _                 | —                 | _                | —                |

| 45.0         | R/W-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 15:8         | ON <sup>(1,2)</sup> |                   | _                 | —                 | —                 | —                 | —                | —                |

| 7.0          | U-0                 | R-y               | R-y               | R-y               | R-y               | R-y               | R/W-0            | R/W-0            |

| 7:0          | _                   |                   | S                 |                   | WDTWINEN          | WDTCLR            |                  |                  |

#### REGISTER 15-1: WDTCON: WATCHDOG TIMER CONTROL REGISTER

| Legend:           | y = Values set from Configuration bits on POR |                                    |                    |  |  |  |

|-------------------|-----------------------------------------------|------------------------------------|--------------------|--|--|--|

| R = Readable bit  | W = Writable bit                              | U = Unimplemented bit, read as '0' |                    |  |  |  |

| -n = Value at POR | '1' = Bit is set                              | '0' = Bit is cleared               | x = Bit is unknown |  |  |  |

bit 31-16 Unimplemented: Read as '0'

bit 0

- bit 15 **ON:** Watchdog Timer Enable bit<sup>(1,2)</sup>

- 1 = Enables the WDT if it is not enabled by the device configuration 0 = Disable the WDT if it was enabled in software

- bit 14-7 **Unimplemented:** Read as '0'

- bit 6-2 **SWDTPS<4:0>:** Shadow Copy of Watchdog Timer Postscaler Value from Device Configuration bits On reset, these bits are set to the values of the WDTPS <4:0> Configuration bits.

- bit 1 WDTWINEN: Watchdog Timer Window Enable bit

- 1 = Enable windowed Watchdog Timer

- 0 = Disable windowed Watchdog Timer

- WDTCLR: Watchdog Timer Reset bit

- 1 = Writing a '1' will clear the WDT

- 0 = Software cannot force this bit to a '0'

- Note 1: A read of this bit results in a '1' if the Watchdog Timer is enabled by the device configuration or software.

- 2: When using the 1:1 PBCLK divisor, the user's software should not read or write the peripheral's SFRs in the SYSCLK cycle immediately following the instruction that clears the module's ON bit.

#### I2CxSTAT: I<sup>2</sup>C STATUS REGISTER (CONTINUED) REGISTER 19-2: **D\_A:** Data/Address bit (when operating as I<sup>2</sup>C slave) bit 5 This bit is cleared by hardware upon a device address match, and is set by hardware by reception of the slave byte. 1 = Indicates that the last byte received was data 0 = Indicates that the last byte received was device address bit 4 P: Stop bit This bit is set or cleared by hardware when a Start, Repeated Start, or Stop condition is detected. 1 = Indicates that a Stop bit has been detected last 0 = Stop bit was not detected last bit 3 S: Start bit This bit is set or cleared by hardware when a Start, Repeated Start, or Stop condition is detected. 1 = Indicates that a Start (or Repeated Start) bit has been detected last 0 = Start bit was not detected last **R\_W:** Read/Write Information bit (when operating as I<sup>2</sup>C slave) bit 2 This bit is set or cleared by hardware after reception of an I<sup>2</sup>C device address byte. 1 = Read – indicates data transfer is output from slave 0 = Write - indicates data transfer is input to slave **RBF:** Receive Buffer Full Status bit bit 1 This bit is set by hardware when the I2CxRCV register is written with a received byte, and is cleared by hardware when software reads I2CxRCV. 1 = Receive complete, I2CxRCV is full 0 = Receive not complete, I2CxRCV is empty bit 0 TBF: Transmit Buffer Full Status bit This bit is set by hardware when software writes to the I2CxTRN register, and is cleared by hardware upon completion of data transmission.

1 = Transmit in progress, I2CxTRN is full

0 = Transmit complete, I2CxTRN is empty

#### REGISTER 21-1: PMCON: PARALLEL PORT CONTROL REGISTER (CONTINUED)

- bit 3 **CS1P:** Chip Select 0 Polarity bit<sup>(2)</sup>

- 1 = Active-high (PMCS1)

- $0 = \text{Active-low}(\overline{\text{PMCS1}})$

- bit 2 Unimplemented: Read as '0'

- bit 1 WRSP: Write Strobe Polarity bit

- For Slave Modes and Master mode 2 (PMMODE<9:8> = 00,01,10):

- 1 = Write strobe active-high (PMWR)

- $0 = Write strobe active-low (\overline{PMWR})$

For Master mode 1 (PMMODE<9:8> = 11):

- 1 = Enable strobe active-high (PMENB)

- 0 = Enable strobe active-low (PMENB)

- bit 0 RDSP: Read Strobe Polarity bit

- For Slave modes and Master mode 2 (PMMODE<9:8> = 00,01,10):

- 1 = Read Strobe active-high (PMRD)

- $0 = \text{Read Strobe active-low } (\overline{\text{PMRD}})$

For Master mode 1 (PMMODE<9:8> = 11):

- 1 = Read/write strobe active-high (PMRD/ $\overline{PMWR}$ )

- 0 = Read/write strobe active-low (PMRD/PMWR)

- **Note 1:** When using the 1:1 PBCLK divisor, the user's software should not read/write the peripheral's SFRs in the SYSCLK cycle immediately following the instruction that clears the module's ON control bit.

- 2: These bits have no effect when their corresponding pins are used as address lines.

|              |                   |                   |                   |                   |                   |                   |                  | ,                |  |  |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|--|--|

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |  |

| 31:24        | R/W-x             | R/W-x             | R/W-x             | R/W-x             | R/W-x             | R/W-x             | R/W-x            | R/W-x            |  |  |

| 31.24        | SID<10:3>         |                   |                   |                   |                   |                   |                  |                  |  |  |

| 22:46        | R/W-x             | R/W-x             | R/W-x             | U-0               | R/W-0             | U-0               | R/W-x            | R/W-x            |  |  |

| 23:16        |                   | SID<2:0>          |                   | —                 | EXID              | — EID<17:16>      |                  |                  |  |  |

| 15.0         | R/W-x             | R/W-x             | R/W-x             | R/W-x             | R/W-x             | R/W-x             | R/W-x            | R/W-x            |  |  |

| 15:8         | EID<15:8>         |                   |                   |                   |                   |                   |                  |                  |  |  |

| 7.0          | R/W-x             | R/W-x             | R/W-x             | R/W-x             | R/W-x             | R/W-x             | R/W-x            | R/W-x            |  |  |

| 7:0          |                   |                   |                   | EID<              | :7:0>             |                   |                  |                  |  |  |

#### REGISTER 24-18: CIRXFn: CAN ACCEPTANCE FILTER 'n' REGISTER 7 (n = 0 THROUGH 31)

#### Legend:

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read as '0' |                    |  |  |

|-------------------|------------------|------------------------------------|--------------------|--|--|

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared               | x = Bit is unknown |  |  |

bit 31-21 SID<10:0>: Standard Identifier bits

- 1 = Message address bit SIDx must be '1' to match filter

- 0 = Message address bit SIDx must be '0' to match filter

- bit 20 Unimplemented: Read as '0'

- bit 19 **EXID:** Extended Identifier Enable bits

- 1 = Match only messages with extended identifier addresses

- 0 = Match only messages with standard identifier addresses

- bit 18 Unimplemented: Read as '0'

- bit 17-0 EID<17:0>: Extended Identifier bits

- 1 = Message address bit EIDx must be '1' to match filter

- 0 = Message address bit EIDx must be '0' to match filter

**Note:** This register can only be modified when the filter is disabled (FLTENn = 0).

|              |                   |                   |                   |                   |                   | •                 |                    | ,                  |  |  |  |  |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|--------------------|--------------------|--|--|--|--|

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1   | Bit<br>24/16/8/0   |  |  |  |  |

| 31:24        | R-x                | R-x                |  |  |  |  |

| 31.24        |                   | CiFIFOUAn<31:24>  |                   |                   |                   |                   |                    |                    |  |  |  |  |

| 23:16        | R-x                | R-x                |  |  |  |  |

| 23.10        | CiFIFOUAn<23:16>  |                   |                   |                   |                   |                   |                    |                    |  |  |  |  |

| 45.0         | R-x                | R-x                |  |  |  |  |

| 15:8         | CiFIFOUAn<15:8>   |                   |                   |                   |                   |                   |                    |                    |  |  |  |  |

| 7.0          | R-x               | R-x               | R-x               | R-x               | R-x               | R-x               | R-0 <sup>(1)</sup> | R-0 <sup>(1)</sup> |  |  |  |  |

| 7:0          |                   |                   |                   | CiFIFOU           | IAn<7:0>          |                   |                    |                    |  |  |  |  |

#### REGISTER 24-22: CiFIFOUAn: CAN FIFO USER ADDRESS REGISTER 'n' (n = 0 THROUGH 31)

#### Legend:

| 3                 |                  |                        |                                    |  |  |  |

|-------------------|------------------|------------------------|------------------------------------|--|--|--|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, | U = Unimplemented bit, read as '0' |  |  |  |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared   | x = Bit is unknown                 |  |  |  |

bit 31-0 CiFIFOUAn<31:0>: CAN FIFO User Address bits

TXEN = 1: (FIFO configured as a transmit buffer)

A read of this register will return the address where the next message is to be written (FIFO head).

TXEN = 0: (FIFO configured as a receive buffer)

A read of this register will return the address where the next message is to be read (FIFO tail).

**Note 1:** This bit will always read '0', which forces byte-alignment of messages.

**Note:** This register is not guaranteed to read correctly in Configuration mode, and should only be accessed when the module is not in Configuration mode.

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|

| 31:24        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 31.24        | —                 | —                 | —                 | —                 | —                 | —                 | —                | —                |

| 23:16        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 23.10        | _                 | _                 | _                 | _                 | _                 | —                 |                  | —                |

| 15:8         | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 15.0         | —                 | —                 | —                 | —                 | —                 | —                 | —                | —                |

| 7:0          | U-0               | U-0               | U-0               | R-0               | R-0               | R-0               | R-0              | R-0              |

| 7.0          | _                 | _                 | _                 |                   | (                 | CiFIFOCI<4:0:     | >                |                  |

#### **REGISTER 24-23:** CiFIFOCIN: CAN MODULE MESSAGE INDEX REGISTER 'n' (n = 0 THROUGH 31)

#### Legend:

| 0                 |                               |                      |                                    |  |  |  |  |  |

|-------------------|-------------------------------|----------------------|------------------------------------|--|--|--|--|--|

| R = Readable bit  | Readable bit W = Writable bit |                      | U = Unimplemented bit, read as '0' |  |  |  |  |  |

| -n = Value at POR | '1' = Bit is set              | '0' = Bit is cleared | x = Bit is unknown                 |  |  |  |  |  |

bit 31-5 Unimplemented: Read as '0'

bit 4-0 CiFIFOCIn<4:0>: CAN Side FIFO Message Index bits

TXEN = 1: (FIFO configured as a transmit buffer)

A read of this register will return an index to the message that the FIFO will next attempt to transmit.

TXEN = 0: (FIFO configured as a receive buffer)

A read of this register will return an index to the message that the FIFO will use to save the next message.

#### TABLE 32-20: INTERNAL RC ACCURACY

| AC CHA                          | RACTERISTICS    | (unless | $\begin{array}{llllllllllllllllllllllllllllllllllll$ |      |       |            |  |  |  |  |

|---------------------------------|-----------------|---------|------------------------------------------------------|------|-------|------------|--|--|--|--|

| Param.<br>No.                   | Characteristics | Min.    | Typical                                              | Max. | Units | Conditions |  |  |  |  |

| LPRC @ 31.25 kHz <sup>(1)</sup> |                 |         |                                                      |      |       |            |  |  |  |  |

| F21                             | 1 LPRC          |         | _                                                    | +15  | %     | —          |  |  |  |  |

**Note 1:** Change of LPRC frequency as VDD changes.

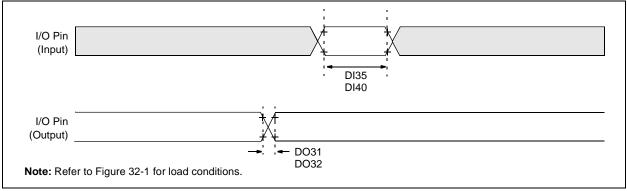

#### FIGURE 32-3: I/O TIMING CHARACTERISTICS

#### TABLE 32-21: I/O TIMING REQUIREMENTS

| AC CHARACTERISTICS |        |                      | Standard Ope<br>(unless other<br>Operating tem | wise state             |      | ≤ +85°C fc | or Industria |            |

|--------------------|--------|----------------------|------------------------------------------------|------------------------|------|------------|--------------|------------|

| Param.<br>No.      | Symbol | Characteris          | Min.                                           | Typical <sup>(1)</sup> | Max. | Units      | Conditions   |            |

| DO31               | TIOR   | Port Output Rise Tin | ne                                             | _                      | 5    | 15         | ns           | Vdd < 2.5V |

|                    |        |                      |                                                | —                      | 5    | 10         | ns           | Vdd > 2.5V |

| DO32               | TIOF   | Port Output Fall Tim | е                                              | _                      | 5    | 15         | ns           | Vdd < 2.5V |

|                    |        |                      |                                                | —                      | 5    | 10         | ns           | VDD > 2.5V |

| DI35               | TINP   | INTx Pin High or Lov | 10                                             | —                      | —    | ns         | —            |            |

| DI40               | Trbp   | CNx High or Low Tir  | 2                                              | _                      | _    | TSYSCLK    | _            |            |

**Note 1:** Data in "Typical" column is at 3.3V, 25°C unless otherwise stated.

2: This parameter is characterized, but not tested in manufacturing.

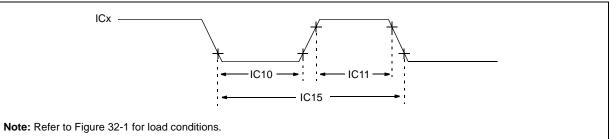

### FIGURE 32-7: INPUT CAPTURE (CAPx) TIMING CHARACTERISTICS

#### TABLE 32-25: INPUT CAPTURE MODULE TIMING REQUIREMENTS

| AC CHARACTERISTICS |        |                                    |             | perating Conditions: 2.3V<br>erwise stated)<br>mperature $-40^{\circ}C \le TA \le +$<br>$-40^{\circ}C \le TA \le +$ | 85°C for |       |                                         |                                  |

|--------------------|--------|------------------------------------|-------------|---------------------------------------------------------------------------------------------------------------------|----------|-------|-----------------------------------------|----------------------------------|

| Param.<br>No.      | Symbol | bol Characteristics <sup>(1)</sup> |             | Min.                                                                                                                | Max.     | Units | Con                                     | ditions                          |

| IC10               | TccL   | ICx Input                          | t Low Time  | [(12.5 ns or 1 ТРВ)/N]<br>+ 25 ns                                                                                   | -        | ns    | Must also<br>meet<br>parameter<br>IC15. | N = prescale<br>value (1, 4, 16) |

| IC11               | ТссН   | ICx Input                          | t High Time | [(12.5 ns or 1 ТРВ)/N]<br>+ 25 ns                                                                                   |          | ns    | Must also<br>meet<br>parameter<br>IC15. |                                  |

| IC15               | TCCP   | ICx Input                          | t Period    | [(25 ns or 2 Трв)/N]<br>+ 50 ns                                                                                     | —        | ns    | —                                       |                                  |

Note 1: These parameters are characterized, but not tested in manufacturing.

#### FIGURE 32-8: OUTPUT COMPARE MODULE (OCx) TIMING CHARACTERISTICS

#### TABLE 32-26: OUTPUT COMPARE MODULE TIMING REQUIREMENTS

| AC CHA        | AC CHARACTERISTICS |                                |      | $\begin{array}{l} \mbox{Standard Operating Conditions: 2.3V to 3.6V} \\ \mbox{(unless otherwise stated)} \\ \mbox{Operating temperature} & -40^{\circ}C \leq TA \leq +85^{\circ}C \mbox{ for Industrial} \\ & -40^{\circ}C \leq TA \leq +105^{\circ}C \mbox{ for V-Temp} \end{array}$ |      |       |                    |  |  |

|---------------|--------------------|--------------------------------|------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|-------|--------------------|--|--|

| Param.<br>No. | Symbol             | Characteristics <sup>(1)</sup> | Min. | Typical <sup>(2)</sup>                                                                                                                                                                                                                                                                | Max. | Units | Conditions         |  |  |

| OC10          | TCCF               | OCx Output Fall Time           | —    | _                                                                                                                                                                                                                                                                                     | _    | ns    | See parameter DO32 |  |  |

| OC11          | TCCR               | OCx Output Rise Time           |      | —                                                                                                                                                                                                                                                                                     |      | ns    | See parameter DO31 |  |  |

Note 1: These parameters are characterized, but not tested in manufacturing.

2: Data in "Typical" column is at 3.3V, 25°C unless otherwise stated. Parameters are for design guidance only and are not tested.

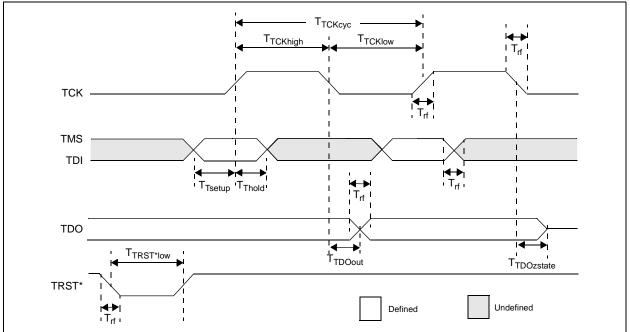

#### FIGURE 32-28: EJTAG TIMING CHARACTERISTICS

#### TABLE 32-43: EJTAG TIMING REQUIREMENTS

| AC CHA        | AC CHARACTERISTICS |                                                  |      | $\begin{array}{llllllllllllllllllllllllllllllllllll$ |       |            |  |  |  |

|---------------|--------------------|--------------------------------------------------|------|------------------------------------------------------|-------|------------|--|--|--|

| Param.<br>No. | Symbol             | Description <sup>(1)</sup>                       | Min. | Max.                                                 | Units | Conditions |  |  |  |

| EJ1           | Ттсксүс            | TCK Cycle Time                                   | 25   | _                                                    | ns    |            |  |  |  |

| EJ2           | Ттскнідн           | TCK High Time                                    | 10   |                                                      | ns    | —          |  |  |  |

| EJ3           | TTCKLOW            | TCK Low Time                                     | 10   |                                                      | ns    | —          |  |  |  |

| EJ4           | TTSETUP            | TAP Signals Setup Time Before<br>Rising TCK      | 5    | —                                                    | ns    | _          |  |  |  |

| EJ5           | TTHOLD             | TAP Signals Hold Time After<br>Rising TCK        | 3    | —                                                    | ns    | _          |  |  |  |

| EJ6           | Ττροουτ            | TDO Output Delay Time from<br>Falling TCK        | —    | 5                                                    | ns    | _          |  |  |  |

| EJ7           | TTDOZSTATE         | TDO 3-State Delay Time from<br>Falling TCK       | -    | 5                                                    | ns    | —          |  |  |  |

| EJ8           | TTRSTLOW           | TRST Low Time                                    | 25   | _                                                    | ns    | —          |  |  |  |

| EJ9           | Trf                | TAP Signals Rise/Fall Time, All Input and Output | —    | —                                                    | ns    | _          |  |  |  |

Note 1: These parameters are characterized, but not tested in manufacturing.

#### Note the following details of the code protection feature on Microchip devices:

- Microchip products meet the specification contained in their particular Microchip Data Sheet.

- Microchip believes that its family of products is one of the most secure families of its kind on the market today, when used in the intended manner and under normal conditions.

- There are dishonest and possibly illegal methods used to breach the code protection feature. All of these methods, to our knowledge, require using the Microchip products in a manner outside the operating specifications contained in Microchip's Data Sheets. Most likely, the person doing so is engaged in theft of intellectual property.

- Microchip is willing to work with the customer who is concerned about the integrity of their code.

- Neither Microchip nor any other semiconductor manufacturer can guarantee the security of their code. Code protection does not mean that we are guaranteeing the product as "unbreakable."

Code protection is constantly evolving. We at Microchip are committed to continuously improving the code protection features of our products. Attempts to break Microchip's code protection feature may be a violation of the Digital Millennium Copyright Act. If such acts allow unauthorized access to your software or other copyrighted work, you may have a right to sue for relief under that Act.

Information contained in this publication regarding device applications and the like is provided only for your convenience and may be superseded by updates. It is your responsibility to ensure that your application meets with your specifications. MICROCHIP MAKES NO REPRESENTATIONS OR WARRANTIES OF ANY KIND WHETHER EXPRESS OR IMPLIED, WRITTEN OR ORAL, STATUTORY OR OTHERWISE, RELATED TO THE INFORMATION, INCLUDING BUT NOT LIMITED TO ITS CONDITION, QUALITY, PERFORMANCE, MERCHANTABILITY OR FITNESS FOR PURPOSE. Microchip disclaims all liability arising from this information and its use. Use of Microchip devices in life support and/or safety applications is entirely at the buyer's risk, and the buyer agrees to defend, indemnify and hold harmless Microchip from any and all damages, claims, suits, or expenses resulting from such use. No licenses are conveyed, implicitly or otherwise, under any Microchip intellectual property rights unless otherwise stated.

Microchip received ISO/TS-16949:2009 certification for its worldwide headquarters, design and wafer fabrication facilities in Chandler and Tempe, Arizona; Gresham, Oregon and design centers in California and India. The Company's quality system processes and procedures are for its PIC® MCUs and dsPIC® DSCs, KEELoQ® code hopping devices, Serial EEPROMs, microperipherals, nonvolatile memory and analog products. In addition, Microchip's quality system for the design and manufacture of development systems is ISO 9001:2000 certified.

# QUALITY MANAGEMENT SYSTEM CERTIFIED BY DNV = ISO/TS 16949=

#### Trademarks

The Microchip name and logo, the Microchip logo, AnyRate, dsPIC, FlashFlex, flexPWR, Heldo, JukeBlox, KeeLoq, KeeLoq logo, Kleer, LANCheck, LINK MD, MediaLB, MOST, MOST logo, MPLAB, OptoLyzer, PIC, PICSTART, PIC32 logo, RightTouch, SpyNIC, SST, SST Logo, SuperFlash and UNI/O are registered trademarks of Microchip Technology Incorporated in the U.S.A. and other countries.

ClockWorks, The Embedded Control Solutions Company, ETHERSYNCH, Hyper Speed Control, HyperLight Load, IntelliMOS, mTouch, Precision Edge, and QUIET-WIRE are registered trademarks of Microchip Technology Incorporated in the U.S.A.

Analog-for-the-Digital Age, Any Capacitor, AnyIn, AnyOut, BodyCom, chipKIT, chipKIT logo, CodeGuard, dsPICDEM, dsPICDEM.net, Dynamic Average Matching, DAM, ECAN, EtherGREEN, In-Circuit Serial Programming, ICSP, Inter-Chip Connectivity, JitterBlocker, KleerNet, KleerNet logo, MiWi, motorBench, MPASM, MPF, MPLAB Certified logo, MPLIB, MPLINK, MultiTRAK, NetDetach, Omniscient Code Generation, PICDEM, PICDEM.net, PICkit, PICtail, PureSilicon, RightTouch logo, REAL ICE, Ripple Blocker, Serial Quad I/O, SQI, SuperSwitcher, SuperSwitcher II, Total Endurance, TSHARC, USBCheck, VariSense, ViewSpan, WiperLock, Wireless DNA, and ZENA are trademarks of Microchip Technology Incorporated in the U.S.A. and other countries.

$\ensuremath{\mathsf{SQTP}}$  is a service mark of Microchip Technology Incorporated in the U.S.A.

Silicon Storage Technology is a registered trademark of Microchip Technology Inc. in other countries.

GestIC is a registered trademarks of Microchip Technology Germany II GmbH & Co. KG, a subsidiary of Microchip Technology Inc., in other countries.

All other trademarks mentioned herein are property of their respective companies.

© 2009-2016, Microchip Technology Incorporated, Printed in the U.S.A., All Rights Reserved.

ISBN: 978-1-5224-0958-8