Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

-·XEI

| 2 0 14110                  |                                                                                  |

|----------------------------|----------------------------------------------------------------------------------|

| Product Status             | Active                                                                           |

| Core Processor             | MIPS32® M4K™                                                                     |

| Core Size                  | 32-Bit Single-Core                                                               |

| Speed                      | 80MHz                                                                            |

| Connectivity               | Ethernet, I <sup>2</sup> C, SPI, UART/USART, USB OTG                             |

| Peripherals                | Brown-out Detect/Reset, DMA, POR, PWM, WDT                                       |

| Number of I/O              | 53                                                                               |

| Program Memory Size        | 512KB (512K x 8)                                                                 |

| Program Memory Type        | FLASH                                                                            |

| EEPROM Size                | -                                                                                |

| RAM Size                   | 64K x 8                                                                          |

| Voltage - Supply (Vcc/Vdd) | 2.3V ~ 3.6V                                                                      |

| Data Converters            | A/D 16x10b                                                                       |

| Oscillator Type            | Internal                                                                         |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                                |

| Mounting Type              | Surface Mount                                                                    |

| Package / Case             | 64-VFQFN Exposed Pad                                                             |

| Supplier Device Package    | 64-VQFN (9x9)                                                                    |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic32mx675f512h-80i-mr |

|                            |                                                                                  |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

PIC32MX795F512L

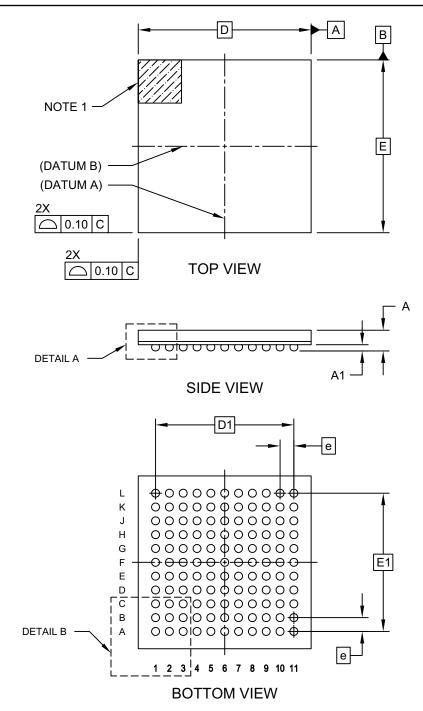

#### **TABLE 12:** PIN NAMES FOR USB, ETHERNET, AND CAN DEVICES

| 121-PIN TFBGA (BOTTOM VIEW)                           |    | L11 |

|-------------------------------------------------------|----|-----|

| PIC32MX764F128L<br>PIC32MX775F256L<br>PIC32MX775F512L | L1 | A11 |

A1

Note: The TFBGA package skips from row "H" to row "J" and has no "I" row.

| Pin #      | Full Pin Name                                               | Pin # | Full Pin Name                                                |

|------------|-------------------------------------------------------------|-------|--------------------------------------------------------------|

| A1         | PMD4/RE4                                                    | E2    | T4CK/AC2RX <sup>(1)</sup> /RC3                               |

| A2         | PMD3/RE3                                                    | E3    | ECOL/SCK2/U6TX/U3RTS/PMA5/CN8/RG6                            |

| A3         | TRD0/RG13                                                   | E4    | T3CK/AC2TX <sup>(1)</sup> /RC2                               |

| A4         | PMD0/RE0                                                    | E5    | Vdd                                                          |

| A5         | C2RX <sup>(1)</sup> /PMD8/RG0                               | E6    | C2TX <sup>(1)</sup> /ETXERR/PMD9/RG1                         |

| A6         | C1TX/ETXD0/PMD10/RF1                                        | E7    | Vss                                                          |

| A7         | VDD                                                         | E8    | AETXEN/SDA1/INT4/RA15                                        |

| A8         | Vss                                                         | E9    | RTCC/EMDIO/AEMDIO/IC1/RD8                                    |

| A9         | ETXD2/IC5/PMD12/RD12                                        | E10   | SS1/IC2/RD9                                                  |

| A10        | OC3/RD2                                                     | E11   | AETXCLK/SCL1/INT3/RA14                                       |

| A11        | OC2/RD1                                                     | F1    | MCLR                                                         |

| B1         | No Connect (NC)                                             | F2    | ERXDV/AERXDV/ECRSDV/AECRSDV/SCL4/SDO2/U3TX/PMA3/CN10/RG8     |

| B2         | AERXERR/RG15                                                | F3    | ERXCLK/AERXCLK/EREFCLK/AEREFCLK/SS2/U6RX/U3CTS/PMA2/CN11/RG9 |

| B3         | PMD2/RE2                                                    | F4    | ECRS/SDA4/SDI2/U3RX/PMA4/CN9/RG7                             |

| B4         | PMD1/RE1                                                    | F5    | Vss                                                          |

| B5         | TRD3/RA7                                                    | F6    | No Connect (NC)                                              |

| B6         | C1RX/ETXD1/PMD11/RF0                                        | F7    | No Connect (NC)                                              |

| B7         | VCAP                                                        | F8    | Vdd                                                          |

| B8         | PMRD/CN14/RD5                                               | F9    | OSC1/CLKI/RC12                                               |

| B9         | OC4/RD3                                                     | F10   | Vss                                                          |

| B10        | Vss                                                         | F11   | OSC2/CLKO/RC15                                               |

| B11        | SOSCO/T1CK/CN0/RC14                                         | G1    | AERXD0/INT1/RE8                                              |

| C1         | PMD6/RE6                                                    | G2    | AERXD1/INT2/RE9                                              |

| C2         | VDD                                                         | G3    | TMS/RA0                                                      |

| C3         | TRD1/RG12                                                   | G4    | No Connect (NC)                                              |

| C4         | TRD2/RG14                                                   | G5    | Vdd                                                          |

| C5         | TRCLK/RA6                                                   | G6    | Vss                                                          |

| C6         | No Connect (NC)                                             | G7    | Vss                                                          |

| C7         | ETXCLK/PMD15/CN16/RD7                                       | G8    | No Connect (NC)                                              |

| C8         | OC5/PMWR/CN13/RD4                                           | G9    | TDO/RA5                                                      |

| C9         | VDD                                                         | G10   | SDA2/RA3                                                     |

| C10        | SOSCI/CN1/RC13                                              | G11   | TDI/RA4                                                      |

| C11        | EMDC/AEMDC/IC4/PMCS1/PMA14/RD11                             | H1    | AN5/C1IN+/VBUSON/CN7/RB5                                     |

| D1         | T2CK/RC1                                                    | H2    | AN4/C1IN-/CN6/RB4                                            |

| D2         | PMD7/RE7                                                    | H3    | Vss                                                          |

| D3         | PMD5/RE5                                                    | H4    | VDD                                                          |

| D4         | Vss                                                         | H5    | No Connect (NC)                                              |

| D5         | Vss                                                         | H6    | VDD                                                          |

| D6         |                                                             | H7    | No Connect (NC)                                              |

| D7         | ETXEN/PMD14/CN15/RD6                                        | H8    | VBUS                                                         |

| D8         | ETXD3/PMD13/CN19/RD13                                       | H9    | VUSB3V3                                                      |

| D9         | SD01/0C1/INT0/RD0                                           | H10   | D+/RG2                                                       |

| D10        | No Connect (NC)<br>SCK1/IC3/PMCS2/PMA15/RD10                | H11   | SCL2/RA2<br>AN3/C2IN+/CN5/RB3                                |

| D11        |                                                             | J1    |                                                              |

| E1<br>Note | T5CK/SDI1/RC4<br>1: This pin is not available on PIC32MX764 | J2    | AN2/C2IN-/CN4/RB2                                            |

2: Shaded pins are 5V tolerant.

NOTES:

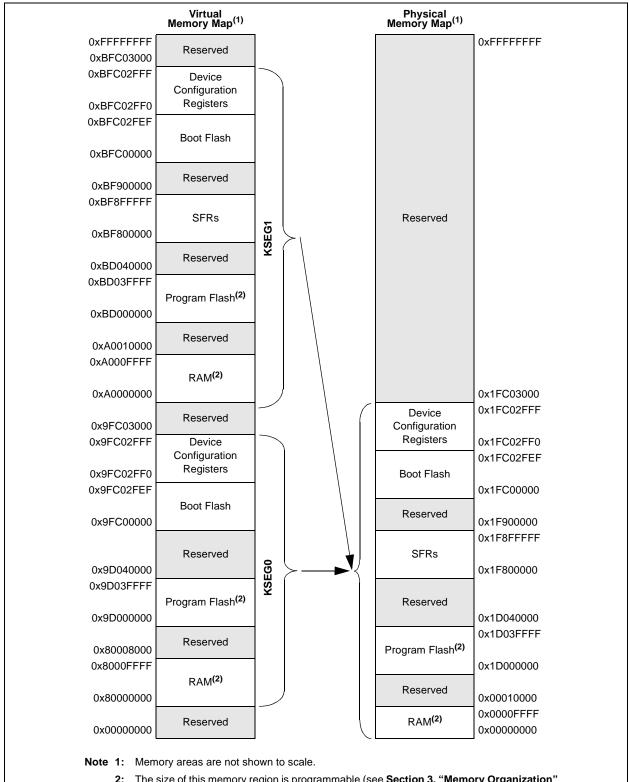

# FIGURE 4-4: MEMORY MAP ON RESET FOR PIC32MX575F256H, PIC32MX575F256L, PIC32MX675F256H, PIC32MX675F256L, PIC32MX775F256H AND PIC32MX775F256L DEVICES

2: The size of this memory region is programmable (see Section 3. "Memory Organization" (DS60001115)) and can be changed by initialization code provided by end user development tools (refer to the specific development tool documentation for information).

# TABLE 7-1: INTERRUPT IRQ, VECTOR AND BIT LOCATION

| Interment Course(1)              | IRQ    | Vector      |               | Interru  | pt Bit Location |              |

|----------------------------------|--------|-------------|---------------|----------|-----------------|--------------|

| Interrupt Source <sup>(1)</sup>  | Number | Number      | Flag          | Enable   | Priority        | Sub-Priority |

|                                  | Highe  | est Natural | Order Priorit | y        |                 |              |

| CT – Core Timer Interrupt        | 0      | 0           | IFS0<0>       | IEC0<0>  | IPC0<4:2>       | IPC0<1:0>    |

| CS0 – Core Software Interrupt 0  | 1      | 1           | IFS0<1>       | IEC0<1>  | IPC0<12:10>     | IPC0<9:8>    |

| CS1 – Core Software Interrupt 1  | 2      | 2           | IFS0<2>       | IEC0<2>  | IPC0<20:18>     | IPC0<17:16>  |

| INT0 – External Interrupt 0      | 3      | 3           | IFS0<3>       | IEC0<3>  | IPC0<28:26>     | IPC0<25:24>  |

| T1 – Timer1                      | 4      | 4           | IFS0<4>       | IEC0<4>  | IPC1<4:2>       | IPC1<1:0>    |

| IC1 – Input Capture 1            | 5      | 5           | IFS0<5>       | IEC0<5>  | IPC1<12:10>     | IPC1<9:8>    |

| OC1 – Output Compare 1           | 6      | 6           | IFS0<6>       | IEC0<6>  | IPC1<20:18>     | IPC1<17:16>  |

| INT1 – External Interrupt 1      | 7      | 7           | IFS0<7>       | IEC0<7>  | IPC1<28:26>     | IPC1<25:24>  |

| T2 – Timer2                      | 8      | 8           | IFS0<8>       | IEC0<8>  | IPC2<4:2>       | IPC2<1:0>    |

| IC2 – Input Capture 2            | 9      | 9           | IFS0<9>       | IEC0<9>  | IPC2<12:10>     | IPC2<9:8>    |

| OC2 – Output Compare 2           | 10     | 10          | IFS0<10>      | IEC0<10> | IPC2<20:18>     | IPC2<17:16>  |

| INT2 – External Interrupt 2      | 11     | 11          | IFS0<11>      | IEC0<11> | IPC2<28:26>     | IPC2<25:24>  |

| T3 – Timer3                      | 12     | 12          | IFS0<12>      | IEC0<12> | IPC3<4:2>       | IPC3<1:0>    |

| IC3 – Input Capture 3            | 13     | 13          | IFS0<13>      | IEC0<13> | IPC3<12:10>     | IPC3<9:8>    |

| OC3 – Output Compare 3           | 14     | 14          | IFS0<14>      | IEC0<14> | IPC3<20:18>     | IPC3<17:16>  |

| INT3 – External Interrupt 3      | 15     | 15          | IFS0<15>      | IEC0<15> | IPC3<28:26>     | IPC3<25:24>  |

| T4 – Timer4                      | 16     | 16          | IFS0<16>      | IEC0<16> | IPC4<4:2>       | IPC4<1:0>    |

| IC4 – Input Capture 4            | 17     | 17          | IFS0<17>      | IEC0<17> | IPC4<12:10>     | IPC4<9:8>    |

| OC4 – Output Compare 4           | 18     | 18          | IFS0<18>      | IEC0<18> | IPC4<20:18>     | IPC4<17:16>  |

| INT4 – External Interrupt 4      | 19     | 19          | IFS0<19>      | IEC0<19> | IPC4<28:26>     | IPC4<25:24>  |

| T5 – Timer5                      | 20     | 20          | IFS0<20>      | IEC0<20> | IPC5<4:2>       | IPC5<1:0>    |

| IC5 – Input Capture 5            | 21     | 21          | IFS0<21>      | IEC0<21> | IPC5<12:10>     | IPC5<9:8>    |

| OC5 – Output Compare 5           | 22     | 22          | IFS0<22>      | IEC0<22> | IPC5<20:18>     | IPC5<17:16>  |

| SPI1E – SPI1 Fault               | 23     | 23          | IFS0<23>      | IEC0<23> | IPC5<28:26>     | IPC5<25:24>  |

| SPI1RX – SPI1 Receive Done       | 24     | 23          | IFS0<24>      | IEC0<24> | IPC5<28:26>     | IPC5<25:24>  |

| SPI1TX – SPI1 Transfer Done      | 25     | 23          | IFS0<25>      | IEC0<25> | IPC5<28:26>     | IPC5<25:24>  |

| U1E – UART1 Error                |        |             |               |          |                 |              |

| SPI3E – SPI3 Fault               | 26     | 24          | IFS0<26>      | IEC0<26> | IPC6<4:2>       | IPC6<1:0>    |

| I2C3B – I2C3 Bus Collision Event |        |             |               |          |                 |              |

| U1RX – UART1 Receiver            |        |             |               |          |                 |              |

| SPI3RX – SPI3 Receive Done       | 27     | 24          | IFS0<27>      | IEC0<27> | IPC6<4:2>       | IPC6<1:0>    |

| I2C3S - I2C3 Slave Event         |        |             |               |          |                 |              |

| U1TX – UART1 Transmitter         |        |             |               |          |                 |              |

| SPI3TX – SPI3 Transfer Done      | 28     | 24          | IFS0<28>      | IEC0<28> | IPC6<4:2>       | IPC6<1:0>    |

| I2C3M – I2C3 Master Event        | 1      |             |               |          |                 |              |

| I2C1B – I2C1 Bus Collision Event | 29     | 25          | IFS0<29>      | IEC0<29> | IPC6<12:10>     | IPC6<9:8>    |

| I2C1S – I2C1 Slave Event         | 30     | 25          | IFS0<30>      | IEC0<30> | IPC6<12:10>     | IPC6<9:8>    |

| I2C1M – I2C1 Master Event        | 31     | 25          | IFS0<31>      | IEC0<31> | IPC6<12:10>     | IPC6<9:8>    |

| CN – Input Change Interrupt      | 32     | 26          | IFS1<0>       | IEC1<0>  | IPC6<20:18>     | IPC6<17:16>  |

Note 1: Not all interrupt sources are available on all devices. See TABLE 1: "PIC32MX5XX USB and CAN Features", TABLE 2: "PIC32MX6XX USB and Ethernet Features" and TABLE 3: "PIC32MX7XX USB, Ethernet, and CAN Features" for the list of available peripherals.

# TABLE 10-3: DMA CHANNELS 0-7 REGISTER MAP (CONTINUED)

| ess                         |                                 |               |        |       |       |               |        |       |      | Bi     | ts       |        |        |        |         |        |        |         |            |

|-----------------------------|---------------------------------|---------------|--------|-------|-------|---------------|--------|-------|------|--------|----------|--------|--------|--------|---------|--------|--------|---------|------------|

| Virtual Address<br>(BF88_#) | Register<br>Name <sup>(1)</sup> | Bit Range     | 31/15  | 30/14 | 29/13 | 28/12         | 27/11  | 26/10 | 25/9 | 24/8   | 23/7     | 22/6   | 21/5   | 20/4   | 19/3    | 18/2   | 17/1   | 16/0    | All Resets |

| 3180                        | DCH1DSIZ                        | 31:16         | _      | -     | —     | _             | -      | -     | _    | —      | _        | _      | _      | _      | —       | _      | _      | _       | 0000       |

| 5100                        |                                 | 15:0          |        |       |       | -             |        |       | -    | CHDSIZ | <15:0>   |        |        | -      | -       |        |        |         | 0000       |

| 3190                        | DCH1SPTR                        | 31:16         | —      | —     | —     | —             | —      | —     | _    | —      | —        | —      | —      | —      | —       | —      | —      | —       | 0000       |

| 5150                        | Donnor IIX                      | 15:0          |        |       |       |               |        |       |      | CHSPTI | R<15:0>  |        |        |        |         |        |        |         | 0000       |

| 31A0                        | DCH1DPTR                        | 31:16         | —      | —     | —     | —             | —      | —     | —    | —      | —        | —      | —      | —      | —       | —      | —      | —       | 0000       |

| 5170                        |                                 | 15:0          |        |       |       |               |        |       |      | CHDPTI | R<15:0>  |        |        |        |         |        |        |         | 0000       |

| 31B0                        | DCH1CSIZ                        | 31:16         | —      | —     | —     | —             | —      | —     | _    | —      | —        | —      | —      | —      | —       | —      | —      | —       | 0000       |

| 0100                        |                                 | 15:0          |        |       |       |               |        |       |      | CHCSIZ | 2<15:0>  |        |        |        |         |        |        |         | 0000       |

| 31C0                        | DCH1CPTR                        | 31:16         | _      | —     | —     | _             | —      | —     | —    | —      | _        | —      | —      | —      | —       | —      | —      | —       | 0000       |

| 0100                        |                                 | 15:0          |        |       |       |               |        |       |      | CHCPTI | R<15:0>  |        |        |        |         | -      | -      | -       | 0000       |

| 31D0                        | DCH1DAT                         | 31:16         | _      | _     | —     | _             | _      | _     | _    | —      | —        | —      | —      | —      | _       | —      | —      | —       | 0000       |

| 0120                        | Bonnbra                         | 15:0          | _      | _     | —     | _             | _      | _     | _    | —      |          |        |        | CHPDA  | \T<7:0> | -      | -      | -       | 0000       |

| 31E0                        | DCH2CON                         | 31:16         | —      | —     | —     | —             | —      | —     |      | —      | —        | —      | —      | —      | —       | —      | —      | —       | 0000       |

| 0120                        | DONZOON                         | 15:0          | CHBUSY | _     | —     | —             | _      | _     |      | CHCHNS | CHEN     | CHAED  | CHCHN  | CHAEN  | _       | CHEDET | CHPR   | :l<1:0> | 0000       |

| 31E0                        | DCH2ECON                        | 31:16         | —      | —     | —     | —             | —      | —     | _    | —      |          | -      |        | CHAIR  |         |        |        |         | OOFF       |

| 511.0                       | DONZEOON                        | 15:0          |        |       |       | CHSIR         | Q<7:0> |       |      |        | CFORCE   | CABORT | PATEN  | SIRQEN | AIRQEN  | —      | —      | —       | FF00       |

| 3200                        | DCH2INT                         | 31:16         | _      | _     | —     | —             | _      | _     |      | —      | CHSDIE   | CHSHIE | CHDDIE | CHDHIE | CHBCIE  | CHCCIE | CHTAIE | CHERIE  | 0000       |

| 5200                        | DONZINI                         | 15:0          | —      | —     | —     | —             | —      | —     | _    | —      | CHSDIF   | CHSHIF | CHDDIF | CHDHIF | CHBCIF  | CHCCIF | CHTAIF | CHERIF  | 0000       |

| 3210                        | DCH2SSA                         | 31:16<br>15:0 |        |       |       |               |        |       |      | CHSSA  | <31:0>   |        |        |        |         |        |        |         | 0000       |

| 3220                        | DCH2DSA                         | 31:16<br>15:0 |        |       |       |               |        |       |      | CHDSA  | <31:0>   |        |        |        |         |        |        |         | 0000       |

|                             |                                 | 31:16         |        | _     | _     | _             | _      | _     | _    |        | _        | _      | _      | _      |         |        | _      |         | 0000       |

| 3230                        | DCH2SSIZ                        | 15:0          |        |       |       |               |        |       |      | CHSSIZ |          |        |        |        |         |        |        |         | 0000       |

|                             |                                 | 31:16         | _      | _     | _     | _             | _      | _     | _    | _      | _        | _      | _      | _      |         | _      | _      | _       | 0000       |

| 3240                        | DCH2DSIZ                        | 15:0          |        |       |       |               |        |       |      | CHDSIZ |          |        |        |        |         |        |        |         | 0000       |

|                             |                                 | 31:16         | _      | _     | _     | _             | _      | _     | _    | _      | _        | _      | _      | _      | _       | _      | _      | _       | 0000       |

| 3250                        | DCH2SPTR                        | 15:0          |        |       |       |               |        |       |      | CHSPTI |          |        |        |        |         |        |        |         | 0000       |

| <u> </u>                    |                                 | 31:16         | _      | _     | _     | _             | _      | _     | _    | _      |          | _      | _      | _      |         |        | _      |         | 0000       |

| 3260                        | DCH2DPTR                        | 15:0          |        |       |       |               |        |       |      | CHDPTI | 8<15.0>  |        |        |        |         |        |        |         | 0000       |

| <u> </u>                    |                                 | 31:16         | _      |       |       |               |        |       | _    |        |          | _      |        | _      | _       |        | _      | _       | 0000       |

| 3270                        | DCH2CSIZ                        | 15:0          |        |       |       |               |        |       |      |        |          |        |        |        |         |        |        |         |            |

|                             |                                 |               |        |       |       |               |        |       |      | 010312 | .< 10.02 |        |        |        |         |        |        |         |            |

| 3280                        | DCH2CPTR                        | 31:16         | _      | _     | —     | —             | _      | _     | _    | —      | _        | —      | —      | —      | —       | _      | _      | _       | 0000       |

|                             |                                 | 15:0          |        |       |       | n, tead as ,0 |        |       |      | CHCPTI | ۲<15:0>  |        |        |        |         |        |        |         | 0000       |

Legend: x = unknown value on Reset; - = unimplemented, read as '0'. Reset values are shown in hexadecimal.

Note 1: All registers in this table have corresponding CLR, SET and INV registers at their virtual addresses, plus offsets of 0x4, 0x8 and 0xC, respectively. See Section 12.1.1 "CLR, SET and INV Registers" for more information.

2: DMA channels 4-7 are not available on PIC32MX534/564/664/764 devices.

# 11.0 USB ON-THE-GO (OTG)

Note: This data sheet summarizes the features of the PIC32MX5XX/6XX/7XX family of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to Section 27. "USB On-The-Go (OTG)" (DS60001126) in the "PIC32 Family Reference Manual", which is available from the Microchip web site (www.microchip.com/PIC32).

The Universal Serial Bus (USB) module contains analog and digital components to provide a USB 2.0 full-speed and low-speed embedded Host, full-speed Device or OTG implementation with a minimum of external components. This module in Host mode is intended for use as an embedded host and therefore does not implement a UHCI or OHCI controller.

The USB module consists of the clock generator, the USB voltage comparators, the transceiver, the Serial Interface Engine (SIE), a dedicated USB DMA controller, pull-up and pull-down resistors, and the register interface. A block diagram of the PIC32 USB OTG module is presented in Figure 11-1.

The clock generator provides the 48 MHz clock required for USB full-speed and low-speed communication. The voltage comparators monitor the voltage on the VBUS pin to determine the state of the bus. The transceiver provides the analog translation between the USB bus and the digital logic. The SIE is a state machine that transfers data to and from the endpoint buffers and generates the hardware protocol for data transfers. The USB DMA controller transfers data between the data buffers in RAM and the SIE. The integrated pull-up and pull-down resistors eliminate the need for external signaling components. The register interface allows the CPU to configure and communicate with the module.

The USB module includes the following features:

- USB Full-speed support for host and device

- Low-speed host support

- USB OTG support

- Integrated signaling resistors

- Integrated analog comparators for VBUS monitoring

- Integrated USB transceiver

- Transaction handshaking performed by hardware

- Endpoint buffering anywhere in system RAM

- Integrated DMA to access system RAM and Flash

- The implementation and use of the USB Note: specifications, as well as other third party may specifications or technologies, require licensing; including, but not limited to, USB Implementers Forum, Inc. (also referred to as USB-IF). The user is fully responsible for investigating and satisfying any applicable licensing obligations.

# REGISTER 14-1: TXCON: TYPE B TIMER CONTROL REGISTER (CONTINUED)

- bit 3 T32: 32-Bit Timer Mode Select bit<sup>(2)</sup>

- 1 = Odd numbered and even numbered timers form a 32-bit timer

- 0 = Odd numbered and even numbered timers form a separate 16-bit timer

### bit 2 Unimplemented: Read as '0'

- bit 1 **TCS:** Timer Clock Source Select bit<sup>(3)</sup> 1 = External clock from TxCK pin 0 = Internal peripheral clock

- bit 0 Unimplemented: Read as '0'

- **Note 1:** When using the 1:1 PBCLK divisor, the user's software should not read/write the peripheral SFRs in the SYSCLK cycle immediately following the instruction that clears the module's ON bit.

- 2: This bit is only available on even numbered timers (Timer2 and Timer4).

- **3:** While operating in 32-bit mode, this bit has no effect for odd numbered timers (Timer1, Timer3, and Timer5). All timer functions are set through the even numbered timers.

- 4: While operating in 32-bit mode, this bit must be cleared on odd numbered timers to enable the 32-bit timer in Idle mode.

NOTES:

# TABLE 20-1: UART1 THROUGH UART6 REGISTER MAP (CONTINUED)

| ess                         |                       |           |        |        |        |               |        |       |       | Bi     | ts     |         |       |          |          |      |        |       |            |

|-----------------------------|-----------------------|-----------|--------|--------|--------|---------------|--------|-------|-------|--------|--------|---------|-------|----------|----------|------|--------|-------|------------|

| Virtual Address<br>(BF80_#) | Register<br>Name      | Bit Range | 31/15  | 30/14  | 29/13  | 28/12         | 27/11  | 26/10 | 25/9  | 24/8   | 23/7   | 22/6    | 21/5  | 20/4     | 19/3     | 18/2 | 17/1   | 16/0  | All Resets |

| 6620                        | U6TXREG               | 31:16     | _      | _      | —      | —             |        |       | —     | —      |        | —       | _     |          | —        | —    | —      | —     | 0000       |

| 0020                        |                       |           | _      | _      | _      | —             | _      | _     | _     | TX8    |        |         |       | Transmit | Register | -    |        | -     | 0000       |

| 6630                        | U6RXREG               | 31:16     | _      | -      | _      | —             | _      | _     | _     |        | _      | —       | _     |          | _        | _    | —      | _     | 0000       |

| 0030                        | UUKAREG               | 15:0      | _      | _      | —      | —             | —      | —     | —     | RX8    |        |         |       | Receive  | Register |      |        |       | 0000       |

| 6640                        | U6BRG <sup>(1)</sup>  | 31:16     | _      | _      | —      | —             | —      | —     | —     | —      | _      | —       | —     | —        | —        | _    | —      | _     | 0000       |

| 0040                        | OODING                | 15:0      |        |        | -      | -             |        |       |       | BRG<   | 15:0>  |         |       |          | -        | -    |        | -     | 0000       |

| 6800                        | U2MODE <sup>(1)</sup> | 31:16     | _      | _      | _      | —             | _      | _     | _     | —      | _      | -       | —     | _        | _        | —    | -      | _     | 0000       |

| 0000                        | OZIVIODE              | 15:0      | ON     | _      | SIDL   | IREN          | RTSMD  | _     | UEN   | <1:0>  | WAKE   | LPBACK  | ABAUD | RXINV    | BRGH     | PDSE | L<1:0> | STSEL | 0000       |

| 6810                        | U2STA <sup>(1)</sup>  | 31:16     | -      | _      |        | —             | —      | —     | _     | ADM_EN |        |         |       | ADDR     | R<7:0>   | -    |        | -     | 0000       |

| 0010                        | 0251A.                |           | UTXISE | L<1:0> | UTXINV | URXEN         | UTXBRK | UTXEN | UTXBF | TRMT   | URXISI | EL<1:0> | ADDEN | RIDLE    | PERR     | FERR | OERR   | URXDA | 0110       |

| 6820                        | U2TXREG               | 31:16     | _      | _      | _      | —             | _      | _     | _     | —      | _      | -       | —     | _        | —        | —    | -      | —     | 0000       |

| 0020                        | OZTARLO               | 15:0      | -      | _      |        | _             | —      | —     | _     | TX8    |        |         |       | Transmit | Register | -    |        | -     | 0000       |

| 6830                        | U2RXREG               | 31:16     | -      | _      |        | _             | —      | —     | _     | —      | _      | -       | —     | _        | _        | _    | -      | _     | 0000       |

| 0000                        | OZIVAREO              | 15:0      | -      | _      |        | _             | _      | —     | _     | RX8    |        |         |       | Receive  | Register | -    |        | -     | 0000       |

| 6840                        | U2BRG <sup>(1)</sup>  | 31:16     | —      | —      | —      | —             | —      | —     | —     | —      | —      | —       | —     | —        | —        | —    | —      | —     | 0000       |

| 0010                        |                       | 15:0      |        |        |        |               |        |       |       | BRG<   | 15:0>  |         |       |          |          |      |        |       | 0000       |

| 6A00                        | U5MODE <sup>(1)</sup> | 31:16     | —      | —      | —      | —             | —      | —     | —     | —      | —      | —       | —     | —        | —        | —    | —      | —     | 0000       |

| 0/100                       |                       | 15:0      | ON     | _      | SIDL   | IREN          | _      | —     | _     | —      | WAKE   | LPBACK  | ABAUD | RXINV    | BRGH     | PDSE | L<1:0> | STSEL | 0000       |

| 6A10                        | U5STA <sup>(1)</sup>  | 31:16     | —      | —      | —      | —             | _      | —     | —     | ADM_EN |        |         |       | ADDR     |          | -    |        | -     | 0000       |

| 0,110                       |                       | 15:0      | UTXISE | L<1:0> | UTXINV | URXEN         | UTXBRK | UTXEN | UTXBF | TRMT   | URXISI | EL<1:0> | ADDEN | RIDLE    | PERR     | FERR | OERR   | URXDA | 0110       |

| 6A20                        | U5TXREG               | 31:16     | -      | _      | _      | _             | _      | _     |       | —      | _      | -       | —     | _        |          |      | -      |       | 0000       |

|                             |                       | 15:0      | —      | _      | _      | —             | _      | _     |       | TX8    |        |         | 1     | Transmit | Register | 1    |        | 1     | 0000       |

| 6A30                        | U5RXREG               | 31:16     | -      | _      | _      | _             | _      | _     |       | —      | _      | -       | —     | _        |          |      | -      |       | 0000       |

|                             |                       | 15:0      | —      | —      | —      | —             | —      | —     | —     | RX8    |        |         |       | Receive  | Register |      |        |       | 0000       |

| 6A40                        | U5BRG <sup>(1)</sup>  | 31:16     | —      | —      |        | —             | —      | —     | —     | —      | —      | —       | —     | _        |          |      | —      |       | 0000       |

| Legen                       |                       | 15:0      |        |        |        | d, read as '0 |        |       |       | BRG<   | 15:0>  |         |       |          |          |      |        |       | 0000       |

DS60001156J-page 206

This register has corresponding CLR, SET and INV registers at its virtual address, plus an offset of 0x4, 0x8 and 0xC, respectively. See Section 12.1.1 "CLR, SET and INV Registers" for more information. Note 1:

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|

| 04.04        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | R/W-0            |

| 31:24        |                   | —                 | _                 | _                 | —                 | —                 | —                | ADM_EN           |

| 00.40        | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |

| 23:16        |                   |                   |                   | ADDR<             | <7:0>             |                   |                  |                  |

| 45.0         | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0, HC         | R/W-0             | R-0              | R-1              |

| 15:8         | UTXISE            | L<1:0>            | UTXINV            | URXEN             | UTXBRK            | UTXEN             | UTXBF            | TRMT             |

| 7.0          | R/W-0             | R/W-0             | R/W-0             | R-1               | R-0               | R-0               | R/W-0, HS        | R-0              |

| 7:0          | URXISE            | L<1:0>            | ADDEN             | RIDLE             | PERR              | FERR              | OERR             | URXDA            |

# REGISTER 20-2: UxSTA: UARTx STATUS AND CONTROL REGISTER

| Legend:           | HS = Set by hardware | HC = Cleared by hardwar  | re                 |

|-------------------|----------------------|--------------------------|--------------------|

| R = Readable bit  | W = Writable bit     | U = Unimplemented bit, r | ead as '0'         |

| -n = Value at POR | '1' = Bit is set     | '0' = Bit is cleared     | x = Bit is unknown |

bit 31-25 Unimplemented: Read as '0'

- bit 24 ADM\_EN: Automatic Address Detect Mode Enable bit

- 1 = Automatic Address Detect mode is enabled

- 0 = Automatic Address Detect mode is disabled

- bit 23-16 ADDR<7:0>: Automatic Address Mask bits

When the ADM\_EN bit is '1', this value defines the address character to use for automatic address detection.

- bit 15-14 UTXISEL<1:0>: TX Interrupt Mode Selection bits

- 11 = Reserved, do not use

- 10 = Interrupt is generated and asserted while the transmit buffer is empty

- 01 = Interrupt is generated and asserted when all characters have been transmitted

- 00 = Interrupt is generated and asserted while the transmit buffer contains at least one empty space

- bit 13 UTXINV: Transmit Polarity Inversion bit

- If IrDA mode is disabled (i.e., IREN (UxMODE<12>) is '0'):

- 1 = UxTX Idle state is '0'

- 0 = UxTX Idle state is '1'

If IrDA mode is enabled (i.e., IREN (UxMODE<12>) is '1'):

- 1 = IrDA encoded UxTX Idle state is '1'

- 0 = IrDA encoded UxTX Idle state is '0'

- bit 12 URXEN: Receiver Enable bit

- 1 = UARTx receiver is enabled. UxRX pin is controlled by UARTx (if ON = 1)

- 0 = UARTx receiver is disabled. UxRX pin is ignored by the UARTx module. UxRX pin is controlled by port.

- bit 11 UTXBRK: Transmit Break bit

- 1 = Send Break on next transmission. Start bit followed by twelve '0' bits, followed by Stop bit; cleared by hardware upon completion.

- 0 = Break transmission is disabled or completed

- bit 10 UTXEN: Transmit Enable bit

- 1 = UARTx transmitter is enabled. UxTX pin is controlled by UARTx (if ON = 1)

- 0 = UARTx transmitter is disabled. Any pending transmission is aborted and buffer is reset. UxTX pin is controlled by port.

- bit 9 UTXBF: Transmit Buffer Full Status bit (read-only)

- 1 = Transmit buffer is full

- 0 = Transmit buffer is not full, at least one more character can be written

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|

| 24.24        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 31:24        | —                 | _                 | _                 | —                 | _                 | _                 | _                | _                |

| 00.40        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 23:16        | —                 | _                 | _                 | —                 | _                 | _                 | _                | —                |

| 45.0         | U-0               | R/W-0             | U-0               | U-0               | U-0               | R/W-0             | R/W-0            | R/W-0            |

| 15:8         | —                 | PTEN14            | _                 | —                 | _                 |                   | PTEN<10:8>       |                  |

| 7.0          | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |

| 7:0          |                   |                   |                   | PTEN              | <7:0>             |                   |                  |                  |

# REGISTER 21-4: PMAEN: PARALLEL PORT PIN ENABLE REGISTER

# Legend:

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, re | ead as '0'         |  |

|-------------------|------------------|---------------------------|--------------------|--|

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared      | x = Bit is unknown |  |

- bit 31-15 **Unimplemented:** Read as '0'

- bit 15-14 **PTEN14:** PMCS1 Strobe Enable bits

- 1 = PMA14 functions as either PMA14 or PMCS1<sup>(1)</sup>

- 0 = PMA14 functions as port I/O

- bit 13-11 Unimplemented: Read as '0'

- bit 10-2 PTEN<10:2>: PMP Address Port Enable bits

- 1 = PMA<10:2> function as PMP address lines

- 0 = PMA<10:2> function as port I/O

- bit 1-0 **PTEN<1:0>:** PMALH/PMALL Strobe Enable bits

- 1 = PMA1 and PMA0 function as either PMA<1:0> or PMALH and PMALL<sup>(2)</sup>

- 0 = PMA1 and PMA0 pads function as port I/O

- **Note 1:** The use of this pin as PMA14 or CS1 is selected by the CSF<1:0> bits in the PMCON register.

- 2: The use of these pins as PMA1/PMA0 or PMALH/PMALL depends on the Address/Data Multiplex mode selected by bits ADRMUX<1:0> in the PMCON register.

| Bit Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |  |

|-----------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|--|--|

| 31:24     | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |

| 31.24     | FLTEN3            | MSEL:             | 3<1:0>            |                   | F                 | SEL3<4:0>         |                  |                  |  |  |

| 22.46     | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |

| 23:16     | FLTEN2            | MSEL              | 2<1:0>            | FSEL2<4:0>        |                   |                   |                  |                  |  |  |

| 15.0      | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |

| 15:8      | FLTEN1            | MSEL              | 1<1:0>            |                   | F                 | SEL1<4:0>         |                  |                  |  |  |

| 7.0       | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |

| 7:0       | FLTEN0 MSEL0<1:0> |                   |                   | F                 | SEL0<4:0>         |                   |                  |                  |  |  |

# REGISTER 24-10: CIFLTCON0: CAN FILTER CONTROL REGISTER 0

### Legend:

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, r | ead as '0'         |

|-------------------|------------------|--------------------------|--------------------|

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared     | x = Bit is unknown |

| bit 31    | FLTEN3: Filter 3 Enable bit                                 |

|-----------|-------------------------------------------------------------|

|           | 1 = Filter is enabled                                       |

|           | 0 = Filter is disabled                                      |

| bit 30-29 | MSEL3<1:0>: Filter 3 Mask Select bits                       |

|           | 11 = Acceptance Mask 3 selected                             |

|           | 10 = Acceptance Mask 2 selected                             |

|           | 01 = Acceptance Mask 1 selected                             |

|           | 00 = Acceptance Mask 0 selected                             |

| bit 28-24 | FSEL3<4:0>: FIFO Selection bits                             |

|           | 11111 = Message matching filter is stored in FIFO buffer 31 |

|           | 11110 = Message matching filter is stored in FIFO buffer 30 |

|           | •                                                           |

|           |                                                             |

|           | 00001 = Message matching filter is stored in FIFO buffer 1  |

|           | 00000 = Message matching filter is stored in FIFO buffer 0  |

| bit 23    | FLTEN2: Filter 2 Enable bit                                 |

|           | 1 = Filter is enabled                                       |

|           | 0 = Filter is disabled                                      |

| bit 22-21 | MSEL2<1:0>: Filter 2 Mask Select bits                       |

|           | 11 = Acceptance Mask 3 selected                             |

|           | 10 = Acceptance Mask 2 selected                             |

|           | 01 = Acceptance Mask 1 selected                             |

|           | 00 = Acceptance Mask 0 selected                             |

| bit 20-16 | FSEL2<4:0>: FIFO Selection bits                             |

|           | 11111 = Message matching filter is stored in FIFO buffer 31 |

|           | 11110 = Message matching filter is stored in FIFO buffer 30 |

|           | •                                                           |

|           | •                                                           |

|           | 00001 = Message matching filter is stored in FIFO buffer 1  |

|           | 00000 = Message matching filter is stored in FIFO buffer 0  |

|           |                                                             |

Note: The bits in this register can only be modified if the corresponding filter enable (FLTENn) bit is '0'.

# REGISTER 24-12: CIFLTCON2: CAN FILTER CONTROL REGISTER 2 (CONTINUED)

| bit 15    | FLTEN9: Filter 9 Enable bit<br>1 = Filter is enabled<br>0 = Filter is disabled                                                                                                    |

|-----------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| bit 14-13 | MSEL9<1:0>: Filter 9 Mask Select bits<br>11 = Acceptance Mask 3 selected<br>10 = Acceptance Mask 2 selected<br>01 = Acceptance Mask 1 selected<br>00 = Acceptance Mask 0 selected |

| bit 12-8  | FSEL9<4:0>: FIFO Selection bits<br>11111 = Message matching filter is stored in FIFO buffer 31<br>11110 = Message matching filter is stored in FIFO buffer 30                     |

|           | 00001 = Message matching filter is stored in FIFO buffer 1<br>00000 = Message matching filter is stored in FIFO buffer 0                                                          |

| bit 7     | FLTEN8: Filter 8 Enable bit<br>1 = Filter is enabled<br>0 = Filter is disabled                                                                                                    |

| bit 6-5   | MSEL8<1:0>: Filter 8 Mask Select bits<br>11 = Acceptance Mask 3 selected<br>10 = Acceptance Mask 2 selected<br>01 = Acceptance Mask 1 selected<br>00 = Acceptance Mask 0 selected |

| bit 4-0   | <pre>FSEL8&lt;4:0&gt;: FIFO Selection bits 11111 = Message matching filter is stored in FIFO buffer 31 11110 = Message matching filter is stored in FIFO buffer 30</pre>          |

Note: The bits in this register can only be modified if the corresponding filter enable (FLTENn) bit is '0'.

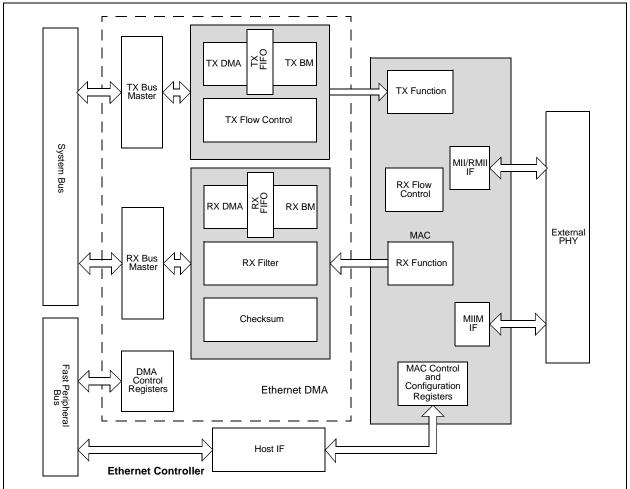

# 25.0 ETHERNET CONTROLLER

Note: This data sheet summarizes the features of the PIC32MX5XX/6XX/7XX family of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to Section 35. "Ethernet Controller" (DS60001155) in the "PIC32 Family Reference Manual", which is available from the Microchip web site (www.microchip.com/PIC32).

The Ethernet controller is a bus master module that interfaces with an off-chip Physical Layer (PHY) to implement a complete Ethernet node in a system.

Key features of the Ethernet Controller include:

- Supports 10/100 Mbps data transfer rates

- Supports full-duplex and half-duplex operation

- Supports RMII and MII PHY interface

- Supports MIIM PHY management interface

- Supports both manual and automatic Flow Control

- RAM descriptor-based DMA operation for both receive and transmit path

- · Fully configurable interrupts

- Configurable receive packet filtering

- CRC check

- 64-byte pattern match

- Broadcast, multicast and unicast packets

- Magic Packet™

- 64-bit hash table

- Runt packet

- Supports packet payload checksum calculation

- · Supports various hardware statistics counters

Figure 25-1 illustrates a block diagram of the Ethernet controller.

# FIGURE 25-1: ETHERNET CONTROLLER BLOCK DIAGRAM

| Bit Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |

|-----------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|--|

| 31:24     | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |

| 31.24     |                   |                   |                   | PMM<              | 31:24>            |                   |                  |                  |  |

| 23:16     | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |

| 23.10     | PMM<23:16>        |                   |                   |                   |                   |                   |                  |                  |  |

| 15:8      | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |

| 15.0      | PMM<15:8>         |                   |                   |                   |                   |                   |                  |                  |  |

| 7:0       | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |

|           |                   |                   |                   | PMM               | <7:0>             |                   |                  |                  |  |

### REGISTER 25-7: ETHPMM0: ETHERNET CONTROLLER PATTERN MATCH MASK 0 REGISTER

# Legend:

| 9                 |                  |                        |                    |

|-------------------|------------------|------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, | read as '0'        |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared   | x = Bit is unknown |

| bit 31-24 | PMM<31:24>: Pattern Match Mask 3 bits |

|-----------|---------------------------------------|

| hit 23-16 | PMM-23-16- Pattern Match Mask 2 hits  |

- bit 23-16 PMM<23:16>: Pattern Match Mask 2 bits

- bit 15-8 **PMM<15:8>:** Pattern Match Mask 1 bits

- bit 7-0 PMM<7:0>: Pattern Match Mask 0 bits

- Note 1: This register is only used for RX operations.

2: The bits in this register may only be changed while the RXEN bit (ETHCON1<8>) = 0 or the PMMODE bit (ETHRXFC<11:8>) = 0.

# REGISTER 25-8: ETHPMM1: ETHERNET CONTROLLER PATTERN MATCH MASK 1 REGISTER

| Bit Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |

|-----------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|--|

| 31:24     | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |

| 31.24     |                   |                   |                   | PMM<              | 63:56>            |                   |                  |                  |  |

| 23:16     | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |

| 23.10     | PMM<55:48>        |                   |                   |                   |                   |                   |                  |                  |  |

| 15:8      | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |

| 15.6      | PMM<47:40>        |                   |                   |                   |                   |                   |                  |                  |  |

| 7:0       | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |

| 7.0       |                   |                   |                   | PMM<              | 39:32>            |                   |                  |                  |  |

| Legend:           |                  |                      |                    |

|-------------------|------------------|----------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented b  | vit, read as '0'   |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared | x = Bit is unknown |

|                   |                  |                      |                    |

| bit 31-24 | PMM<63:56>: Pattern Match Mask 7 bits |

|-----------|---------------------------------------|

| bit 23-16 | PMM<55:48>: Pattern Match Mask 6 bits |

| bit 15-8  | PMM<47:40>: Pattern Match Mask 5 bits |

| bit 7-0   | PMM<39:32>: Pattern Match Mask 4 bits |

# Note 1: This register is only used for RX operations. 2: The bits in this register may only be changed while the RXEN bit (ETHCON1<8>) = 0 or the PMMODE bit (ETHRXFC<11:8>) = 0.

### REGISTER 25-33: EMAC1MADR: ETHERNET CONTROLLER MAC MII MANAGEMENT ADDRESS REGISTER

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|

| 31:24        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 31.24        |                   | _                 |                   | —                 | _                 | —                 | -                | —                |

| 23:16        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 23.10        | —                 | _                 | —                 | —                 | _                 | —                 | _                | —                |

| 15:8         | U-0               | U-0               | U-0               | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-1            |

| 10.0         | —                 | _                 | —                 | PHYADDR<4:0>      |                   |                   |                  |                  |

| 7.0          | U-0               | U-0               | U-0               | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |

| 7:0          |                   | _                 |                   | REGADDR<4:0>      |                   |                   |                  |                  |

# Legend:

| 0                 |                  |                        |                    |

|-------------------|------------------|------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, | read as '0'        |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared   | x = Bit is unknown |

### bit 31-13 Unimplemented: Read as '0'

- bit 12-8 **PHYADDR<4:0>:** MII Management PHY Address bits This field represents the 5-bit PHY Address field of Management cycles. Up to 31 PHYs can be addressed (0 is reserved).

- bit 7-5 Unimplemented: Read as '0'

- bit 4-0 **REGADDR<4:0>:** MII Management Register Address bits This field represents the 5-bit Register Address field of Management cycles. Up to 32 registers can be accessed.

**Note:** Both 16-bit and 32-bit accesses are allowed to these registers (including the SET, CLR and INV registers). 8-bit accesses are not allowed and are ignored by the hardware.

| DC CHARACTERISTICS |                              |            | $\begin{array}{l} \mbox{Standard Operating Conditions: 2.3V to 3.6V} \\ \mbox{(unless otherwise stated)} \\ \mbox{Operating temperature} & -40^\circ C \leq TA \leq +85^\circ C \mbox{ for Industrial} \\ & -40^\circ C \leq TA \leq +105^\circ C \mbox{ for V-Temp} \end{array}$ |                     |       |               |  |  |

|--------------------|------------------------------|------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------|-------|---------------|--|--|

| Parameter<br>No.   | Typical <sup>(2)</sup>       | Max.       | Units                                                                                                                                                                                                                                                                             | Units Conditions    |       |               |  |  |

| Idle Current (I    | IDLE) <sup>(1,3)</sup> for P | PIC32MX575 | /675/695/775                                                                                                                                                                                                                                                                      | 795 Family Devices  |       |               |  |  |

| DC30               | 4.5                          | 6.5        | mA                                                                                                                                                                                                                                                                                | -40°C, +25°C, +85°C |       | 4 MHz         |  |  |

| DC30b              | 5                            | 7          | mA                                                                                                                                                                                                                                                                                | +105°C              | —     | 4 IVITIZ      |  |  |

| DC31               | 13                           | 15         | mA                                                                                                                                                                                                                                                                                | -40°C, +25°C, +85°C | —     | 25 MHz        |  |  |

| DC32               | 28                           | 30         | mA                                                                                                                                                                                                                                                                                | -40°C, +25°C, +85°C | —     | 60 MHz        |  |  |

| DC33               | 36                           | 42         | mA                                                                                                                                                                                                                                                                                | -40°C, +25°C, +85°C |       | 80 MHz        |  |  |

| DC33b              | 39                           | 45         | mA                                                                                                                                                                                                                                                                                | +105°C              | —     |               |  |  |

| DC34               |                              | 40         |                                                                                                                                                                                                                                                                                   | -40°C               |       |               |  |  |

| DC34a              |                              | 75         | μΑ                                                                                                                                                                                                                                                                                | +25°C               | 2.3V  |               |  |  |

| DC34b              |                              | 800        |                                                                                                                                                                                                                                                                                   | +85°C               |       |               |  |  |

| DC34c              |                              | 1000       |                                                                                                                                                                                                                                                                                   | +105°C              |       |               |  |  |

| DC35               | 35                           |            |                                                                                                                                                                                                                                                                                   | -40°C               |       |               |  |  |

| DC35a              | 65                           |            |                                                                                                                                                                                                                                                                                   | +25°C               | 2 2\/ |               |  |  |

| DC35b              | 600                          | _          | μA                                                                                                                                                                                                                                                                                | +85°C               | 3.3V  | LPRC (31 kHz) |  |  |

| DC35c              | 800                          |            |                                                                                                                                                                                                                                                                                   | +105°C              |       |               |  |  |

| DC36               |                              | 43         |                                                                                                                                                                                                                                                                                   | -40°C               |       |               |  |  |

| DC36a              |                              | 106        |                                                                                                                                                                                                                                                                                   | +25°C               | 3.6V  |               |  |  |

| DC36b              |                              | 800        | μA                                                                                                                                                                                                                                                                                | +85°C               | 3.0V  |               |  |  |

| DC36c              |                              | 1000       |                                                                                                                                                                                                                                                                                   | +105°C              |       |               |  |  |

# TABLE 32-6: DC CHARACTERISTICS: IDLE CURRENT (IIDLE)

Note 1: The test conditions for IIDLE current measurements are as follows:

- Oscillator mode is EC (for 8 MHz and below) and EC+PLL (for above 8 MHz) with OSC1 driven by external square wave from rail-to-rail, (OSC1 input clock input over/undershoot < 100 mV required)</li>

- OSC2/CLKO is configured as an I/O input pin

- USB PLL oscillator is disabled if the USB module is implemented, PBCLK divisor = 1:8

- CPU is in Idle mode, program Flash memory Wait states = 111, Program Cache and Prefetch are disabled and SRAM data memory Wait states = 1

- No peripheral modules are operating, (ON bit = 0)

- WDT, Clock Switching, Fail-Safe Clock Monitor, and Secondary Oscillator are disabled

- All I/O pins are configured as inputs and pulled to Vss

- MCLR = VDD

- RTCC and JTAG are disabled

- 2: Data in "Typical" column is at 3.3V, 25°C unless otherwise stated. Parameters are for design guidance only and are not tested.

- 3: This parameter is characterized, but not tested in manufacturing.

- **4:** All parameters are characterized, but only those parameters listed for 4 MHz and 80 MHz are tested at 3.3V in manufacturing.

# TABLE 32-6: DC CHARACTERISTICS: IDLE CURRENT (IIDLE) (CONTINUED)

| DC CHARACTERISTICS                                                            |                        |          | Standard Operating Conditions: 2.3V to 3.6V(unless otherwise stated)Operating temperature $-40^{\circ}C \le T_A \le +85^{\circ}C$ for Industrial $-40^{\circ}C \le T_A \le +105^{\circ}C$ for V-Temp |                     |            |                                  |  |  |

|-------------------------------------------------------------------------------|------------------------|----------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------|------------|----------------------------------|--|--|

| Parameter<br>No.                                                              | Typical <sup>(2)</sup> | Max.     | Units                                                                                                                                                                                                |                     | Conditions |                                  |  |  |

| Idle Current (IIDLE) <sup>(1)</sup> for PIC32MX534/564/664/764 Family Devices |                        |          |                                                                                                                                                                                                      |                     |            |                                  |  |  |

| DC30a                                                                         | 1.5                    | 5        |                                                                                                                                                                                                      | -40°C, +25°C, +85°C |            | 4 MHz                            |  |  |

| DC30c                                                                         | 3.5                    | 6        | mA                                                                                                                                                                                                   | +105⁰C              | —          | 4 10172                          |  |  |

| DC31a                                                                         | 7                      | 11       |                                                                                                                                                                                                      | -40°C, +25°C, +85°C | —          | 25 MHz (Note 3)                  |  |  |

| DC32a                                                                         | 13                     | 20       | mA                                                                                                                                                                                                   | -40°C, +25°C, +85°C | —          | 60 MHz (Note 3)                  |  |  |

| DC33a                                                                         | 17                     | 25       | - mA                                                                                                                                                                                                 | -40°C, +25°C, +85°C |            | 80 MHz                           |  |  |

| DC33c                                                                         | 20                     | 27       | mA                                                                                                                                                                                                   | +105°C              | —          |                                  |  |  |

| DC34c                                                                         |                        | 40       |                                                                                                                                                                                                      | -40°C               |            |                                  |  |  |

| DC34d                                                                         |                        | 75 +25°C | 2.3V                                                                                                                                                                                                 |                     |            |                                  |  |  |

| DC34e                                                                         |                        | 800      | μA 800                                                                                                                                                                                               | +85°C               | 2.3V       |                                  |  |  |

| DC34f                                                                         |                        | 1000     |                                                                                                                                                                                                      | +105°C              |            |                                  |  |  |

| DC35c                                                                         | 30                     |          |                                                                                                                                                                                                      | -40°C               |            |                                  |  |  |

| DC35d                                                                         | 55                     |          |                                                                                                                                                                                                      | +25°C               | 2.21/      | LPRC (31 kHz)<br><b>(Note 3)</b> |  |  |

| DC35e                                                                         | 230                    | _        | μA                                                                                                                                                                                                   | +85°C               | 3.3V       |                                  |  |  |

| DC35f                                                                         | 800                    |          |                                                                                                                                                                                                      | +105°C              |            |                                  |  |  |

| DC36c                                                                         |                        | 43       |                                                                                                                                                                                                      | -40°C               |            | 1                                |  |  |

| DC36d                                                                         |                        | 106      |                                                                                                                                                                                                      | +25°C               | 2.01/      |                                  |  |  |