Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFI

| Details                    |                                                                                  |

|----------------------------|----------------------------------------------------------------------------------|

| Product Status             | Active                                                                           |

| Core Processor             | MIPS32® M4K™                                                                     |

| Core Size                  | 32-Bit Single-Core                                                               |

| Speed                      | 80MHz                                                                            |

| Connectivity               | Ethernet, I <sup>2</sup> C, SPI, UART/USART, USB OTG                             |

| Peripherals                | Brown-out Detect/Reset, DMA, POR, PWM, WDT                                       |

| Number of I/O              | 53                                                                               |

| Program Memory Size        | 512KB (512K x 8)                                                                 |

| Program Memory Type        | FLASH                                                                            |

| EEPROM Size                | -                                                                                |

| RAM Size                   | 64K × 8                                                                          |

| Voltage - Supply (Vcc/Vdd) | 2.3V ~ 3.6V                                                                      |

| Data Converters            | A/D 16x10b                                                                       |

| Oscillator Type            | Internal                                                                         |

| Operating Temperature      | -40°C ~ 105°C (TA)                                                               |

| Mounting Type              | Surface Mount                                                                    |

| Package / Case             | 64-TQFP                                                                          |

| Supplier Device Package    | 64-TQFP (10x10)                                                                  |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic32mx675f512h-80v-pt |

|                            |                                                                                  |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

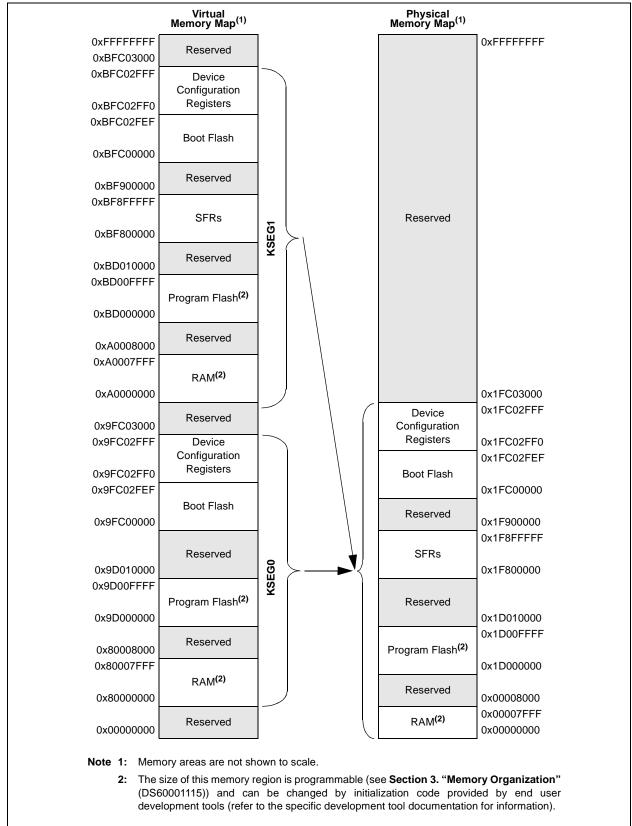

# FIGURE 4-1: MEMORY MAP ON RESET FOR PIC32MX564F064H, PIC32MX564F064L, PIC32MX664F064H AND PIC32MX664F064L DEVICES

NOTES:

# 5.0 FLASH PROGRAM MEMORY

Note: This data sheet summarizes the features of the PIC32MX5XX/6XX/7XX family of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to Section 5. "Flash Program Memory" (DS60001121) in the "PIC32 Family Reference Manual", which is available from the Microchip web site (www.microchip.com/PIC32). PIC32MX5XX/6XX/7XX devices contain an internal Flash program memory for executing user code. There are three methods by which the user can program this memory:

- Run-Time Self-Programming (RTSP)

- EJTAG Programming

- In-Circuit Serial Programming<sup>™</sup> (ICSP<sup>™</sup>)

RTSP is performed by software executing from either Flash or RAM memory. Information about RTSP techniques is available in **Section 5. "Flash Program Memory"** (DS60001121) in the *"PIC32 Family Reference Manual"*.

EJTAG is performed using the EJTAG port of the device and an EJTAG capable programmer.

ICSP is performed using a serial data connection to the device and allows much faster programming times than RTSP.

The EJTAG and ICSP methods are described in the "*PIC32 Flash Programming Specification*" (DS60001145), which can be downloaded from the Microchip web site.

Note: For PIC32MX5XX/6XX/7XX devices, the Flash page size is 4 KB and the row size is 512 bytes (1024 IW and 128 IW, respectively).

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0     |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|----------------------|

| 24.24        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0                  |

| 31:24        | —                 | _                 | _                 | —                 | _                 | _                 | -                | —                    |

| 22.16        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0                  |

| 23:16        | -                 | _                 | _                 | —                 | _                 | _                 | _                | —                    |

| 45.0         | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0                  |

| 15:8         | _                 | _                 | _                 | —                 | _                 | _                 | _                | —                    |

| 7.0          | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | W-0, HC              |

| 7:0          |                   | _                 | _                 | —                 | —                 |                   |                  | SWRST <sup>(1)</sup> |

## REGISTER 6-2: RSWRST: SOFTWARE RESET REGISTER

| Le   | gend:          | HC = Cleared by hardwar | e                         |                    |

|------|----------------|-------------------------|---------------------------|--------------------|

| R =  | = Readable bit | W = Writable bit        | U = Unimplemented bit, re | ead as '0'         |

| -n : | = Value at POR | '1' = Bit is set        | '0' = Bit is cleared      | x = Bit is unknown |

bit 31-1 Unimplemented: Read as '0'

- bit 0 SWRST: Software Reset Trigger bit<sup>(1)</sup> 1 = Enable software Reset event 0 = No effect

- Note 1: The system unlock sequence must be performed before the SWRST bit can be written. Refer to Section 6. "Oscillator" (DS60001112) in the "PIC32 Family Reference Manual" for details.

#### **TABLE 7-2:** INTERRUPT REGISTER MAP FOR PIC32MX534F064H, PIC32MX564F064H, PIC32MX564F128H, PIC32MX575F256H AND PIC32MX575F512H DEVICES (CONTINUED)

| ess                         |                                 | 0         |       |       |       |       |             |       |         | Bits                 |      |      |      |      |            |             |        |                       |               |

|-----------------------------|---------------------------------|-----------|-------|-------|-------|-------|-------------|-------|---------|----------------------|------|------|------|------|------------|-------------|--------|-----------------------|---------------|

| Virtual Address<br>(BF88_#) | Register<br>Name <sup>(1)</sup> | Bit Range | 31/15 | 30/14 | 29/13 | 28/12 | 27/11       | 26/10 | 25/9    | 24/8                 | 23/7 | 22/6 | 21/5 | 20/4 | 19/3       | 18/2        | 17/1   | 16/0                  | All<br>Resets |

| 10A0                        | IPC1                            | 31:16     | _     | —     | —     |       | INT1IP<2:0> |       | INT1IS  | <1:0>                | -    | _    | _    | C    | C1IP<2:0>  | >           | OC1IS  | S<1:0>                | 0000          |

| TUAU                        | IFCI                            | 15:0      |       | _     | _     |       | IC1IP<2:0>  |       | IC1IS<  | <1:0>                | _    | _    |      | -    | T1IP<2:0>  |             | T1IS   | <1:0>                 | 0000          |

| 10B0                        | IPC2                            | 31:16     |       | —     | —     |       | INT2IP<2:0> |       | INT2IS  | <1:0>                | —    | _    | -    | C    | C2IP<2:0>  | >           | OC2IS  | S<1:0>                | 0000          |

| тово                        | IF 02                           | 15:0      |       | _     | _     |       | IC2IP<2:0>  |       | IC2IS<  | <1:0>                | _    | -    |      | -    | T2IP<2:0>  |             | T2IS   | <1:0>                 | 0000          |

| 10C0                        | IPC3                            | 31:16     |       | _     | _     |       | INT3IP<2:0> |       | INT3IS  | <1:0>                | —    | _    |      | C    | C3IP<2:0>  | >           | OC3IS  | S<1:0>                | 0000          |

| 1000                        | 11 00                           | 15:0      | —     | —     | —     |       | IC3IP<2:0>  |       | IC3IS<  | <1:0>                | —    | —    | —    | -    | T3IP<2:0>  |             | T3IS   | <1:0>                 | 0000          |

| 10D0                        | IPC4                            | 31:16     | —     | —     | —     |       | INT4IP<2:0> |       | INT4IS  | <1:0>                | —    | —    | —    | C    | C4IP<2:0>  | <b>&gt;</b> | OC4IS  | S<1:0>                | 0000          |

| TODO                        | 11 04                           | 15:0      | —     | —     | —     |       | IC4IP<2:0>  |       | IC4IS<  | <1:0>                | —    | —    | —    | -    | T4IP<2:0>  |             | T4IS   | <1:0>                 | 0000          |

| 10E0                        | IPC5                            | 31:16     | —     | —     | —     |       | —           | —     | —       | —                    | —    | —    | _    | -    | C5IP<2:0>  | >           | OC5IS  | S<1:0>                | 0000          |

| IOLO                        | 1 00                            | 15:0      | —     | —     | —     |       | IC5IP<2:0>  |       | IC5IS<  | <1:0>                | —    | —    | —    |      | T5IP<2:0>  |             | T5IS   |                       | 0000          |

|                             |                                 | 31:16     | —     | —     | —     |       | AD1IP<2:0>  |       | AD1IS-  | <1:0>                | —    | —    | —    | (    | CNIP<2:0>  |             | CNIS   | -                     | 0000          |

| 10F0                        | IPC6                            |           |       |       |       |       |             |       |         |                      |      |      |      | l    | J1IP<2:0>  |             | U1IS   | <1:0>                 |               |

| 101.0                       | 1 00                            | 15:0      | —     | —     | —     |       | I2C1IP<2:0> |       | I2C1IS  | <1:0>                | —    | —    | —    | S    | PI3IP<2:0: | >           | SPI3IS | S<1:0>                | 0000          |

|                             |                                 |           |       |       |       |       |             |       |         |                      |      |      |      | 12   | 2C3IP<2:0> | >           | 12C31  | S<1:0>                |               |

|                             |                                 |           |       |       |       |       | U3IP<2:0>   |       | U3IS<   | :1:0>                |      |      |      |      |            |             |        |                       |               |

| 1100                        | IPC7                            | 31:16     | —     | —     | —     |       | SPI2IP<2:0> |       | SPI2IS  | <1:0>                | —    | —    | —    | C    | MP2IP<2:0  | >           | CMP2I  | S<1:0>                | 0000          |

| 1100                        | 11 07                           |           |       |       |       |       | I2C4IP<2:0> |       | I2C4IS  | -                    |      |      |      |      |            |             |        |                       |               |

|                             |                                 | 15:0      | —     | —     | —     | (     | CMP1IP<2:0> | •     | CMP1IS  |                      | —    | —    | _    |      | MPIP<2:0   |             | PMPIS  | S<1:0>                | 0000          |

|                             |                                 | 31:16     | —     | —     | —     | F     | RTCCIP<2:0> | •     | RTCCIS  | S<1:0>               | —    | —    | _    |      | SCMIP<2:0  | >           |        | S<1:0>                | 0000          |

| 1110                        | IPC8                            |           |       |       |       |       |             |       |         |                      |      |      |      |      | J2IP<2:0>  |             | U2IS   |                       |               |

|                             | 11 00                           | 15:0      | —     | —     | —     | —     | —           | —     | —       | —                    | —    | —    | —    | S    | PI4IP<2:0; | >           | SPI4IS | S<1:0>                | 0000          |

|                             |                                 |           |       |       |       |       |             |       |         |                      |      |      |      |      | 2C5IP<2:0> |             | 12C518 |                       |               |

| 1120                        | IPC9                            | 31:16     | _     | —     | —     |       | DMA3IP<2:0> |       | DMA3IS  |                      | _    | —    | _    |      | MA2IP<2:0  |             | DMA2I  |                       | 0000          |

| 1120                        | 11 00                           | 15:0      | _     | —     | —     |       | DMA1IP<2:0> |       | DMA1IS  |                      | _    | —    | _    |      | MA0IP<2:0  |             | DMA0I  |                       | 0000          |

| 1130                        | IPC10                           | 31:16     | —     | —     | —     |       | MA7IP<2:0>( |       | DMA7IS- | -                    | —    | —    | —    |      | A6IP<2:0>  |             |        | S<1:0> <sup>(2)</sup> | 0000          |

| 1100                        | 1 010                           | 15:0      | —     | —     | —     | D     | MA5IP<2:0>( | 2)    | DMA5IS- | <1:0> <sup>(2)</sup> | —    | —    | —    | DM   | IA4IP<2:0> | (2)         | DMA4IS | S<1:0> <sup>(2)</sup> | 0000          |

| 1140                        | IPC11                           | 31:16     | _     | _     | _     | _     | —           | _     | _       | _                    | —    | _    | _    | -    | AN1IP<2:0  |             | CAN1I  | S<1:0>                | 0000          |

| 1140                        |                                 | 15:0      | —     | —     | —     |       | USBIP<2:0>  |       | USBIS   | <1:0>                | —    | —    | _    | F    | CEIP<2:0>  | •           | FCEIS  | 6<1:0>                | 0000          |

| 1150                        | IPC12                           | 31:16     | _     | —     | —     |       | U5IP<2:0>   |       | U5IS<   | :1:0>                | —    | —    | —    | l    | J6IP<2:0>  |             | U6IS   | <1:0>                 | 0000          |

| 1100                        | 1 012                           | 15:0      | —     | —     | —     |       | U4IP<2:0>   |       | U4IS<   | :1:0>                | —    | —    | _    | —    | —          | -           | -      | —                     | 0000          |

PIC32MX5XX/6XX/7XX

x = unknown value on Reset; --- = unimplemented, read as '0'. Reset values are shown in hexadecimal. Legend:

Except where noted, all registers in this table have corresponding CLR, SET and INV registers at their virtual addresses, plus offsets of 0x4 0x8 and 0xC, respectively. See Section 12.1.1 "CLR, SET Note 1: and INV Registers" for more information.

These bits are not available on PIC32MX534/564/664/764 devices. 2:

This register does not have associated CLR, SET, and INV registers. 3:

|                             |                                 | P             | IC32M)  | <b>(795F5</b> 1 | 12L DEV | /ICES                         |                               |                               |                               |                             |                               |                               |                             |                       |                         |        |               |        |            |

|-----------------------------|---------------------------------|---------------|---------|-----------------|---------|-------------------------------|-------------------------------|-------------------------------|-------------------------------|-----------------------------|-------------------------------|-------------------------------|-----------------------------|-----------------------|-------------------------|--------|---------------|--------|------------|

| SS                          |                                 |               |         |                 |         |                               |                               |                               |                               | В                           | its                           |                               |                             |                       |                         |        |               |        |            |

| Virtual Address<br>(BF88_#) | Register<br>Name <sup>(1)</sup> | Bit Range     | 31/15   | 30/14           | 29/13   | 28/12                         | 27/11                         | 26/10                         | 25/9                          | 24/8                        | 23/7                          | 22/6                          | 21/5                        | 20/4                  | 19/3                    | 18/2   | 17/1          | 16/0   | All Resets |

| 1000                        | INTCON                          | 31:16         | _       | _               | —       | _                             | _                             | -                             | —                             | _                           | _                             | —                             | —                           | _                     |                         | —      | —             | SS0    | 0000       |

| 1000                        | INTCON                          | 15:0          | _       | -               | _       | MVEC                          | _                             |                               | TPC<2:0>                      |                             | _                             | —                             | _                           | INT4EP                | INT3EP                  | INT2EP | INT1EP        | INT0EP | 0000       |

| 1010                        | INTSTAT <sup>(3)</sup>          | 31:16         |         | —               | _       | —                             | _                             | _                             | —                             | —                           | _                             | _                             | —                           |                       | —                       | —      | —             |        | 0000       |

|                             |                                 | 15:0          | _       | _               | —       | —                             | —                             |                               | SRIPL<2:0>                    |                             | —                             | —                             |                             |                       | VEC                     | <5:0>  |               |        | 0000       |

| 1020                        | IPTMR                           | 31:16<br>15:0 |         |                 |         |                               |                               |                               |                               | IPTMR                       | <31:0>                        |                               |                             |                       |                         |        |               |        | 0000       |

| 1030                        | IFS0                            | 31:16         | I2C1MIF | I2C1SIF         | I2C1BIF | U1TXIF<br>SPI3TXIF<br>I2C3MIF | U1RXIF<br>SPI3RXIF<br>I2C3SIF | U1EIF<br>SPI3EIF<br>I2C3BIF   | SPI1TXIF                      | SPI1RXIF                    | SPI1EIF                       | OC5IF                         | IC5IF                       | T5IF                  | INT4IF                  | OC4IF  | IC4IF         | T4IF   | 0000       |

|                             |                                 | 15:0          | INT3IF  | OC3IF           | IC3IF   | T3IF                          | INT2IF                        | OC2IF                         | IC2IF                         | T2IF                        | INT1IF                        | OC1IF                         | IC1IF                       | T1IF                  | INT0IF                  | CS1IF  | CS0IF         | CTIF   | 0000       |

|                             |                                 | 31:16         | IC3EIF  | IC2EIF          | IC1EIF  | ETHIF                         | CAN2IF <sup>(2)</sup>         | CAN1IF                        | USBIF                         | FCEIF                       | DMA7IF <sup>(2)</sup>         | DMA6IF <sup>(2)</sup>         | DMA5IF <sup>(2)</sup>       | DMA4IF <sup>(2)</sup> | DMA3IF                  | DMA2IF | DMA1IF        | DMA0IF | 0000       |

| 1040                        | IFS1                            | 15:0          | RTCCIF  | FSCMIF          | I2C2MIF | I2C2SIF                       | I2C2BIF                       | U2TXIF<br>SPI4TXIF<br>I2C5MIF | U2RXIF<br>SPI4RXIF<br>I2C5SIF | U2EIF<br>SPI4EIF<br>I2C5BIF | U3TXIF<br>SPI2TXIF<br>I2C4MIF | U3RXIF<br>SPI2RXIF<br>I2C4SIF | U3EIF<br>SPI2EIF<br>I2C4BIF | CMP2IF                | CMP1IF                  | PMPIF  | AD1IF         | CNIF   | 0000       |

|                             |                                 | 31:16         | _       | _               | _       | _                             | _                             | _                             | _                             | _                           | _                             | _                             | _                           | _                     | _                       | _      | _             | _      | 0000       |

| 1050                        | IFS2                            | 15:0          |         | _               | _       | _                             | U5TXIF                        | U5RXIF                        | U5EIF                         | U6TXIF                      | U6RXIF                        | U6EIF                         | U4TXIF                      | U4RXIF                | U4EIF                   | PMPEIF | IC5EIF        | IC4EIF | 0000       |

| 1060                        | IEC0                            | 31:16         | I2C1MIE | I2C1SIE         | I2C1BIE | U1TXIE<br>SPI3TXIE<br>I2C3MIE | U1RXIE<br>SPI3RXIE<br>I2C3SIE | U1EIE<br>SPI3EIE<br>I2C3BIE   | SPI1TXIE                      | SPI1RXIE                    | SPI1EIE                       | OC5IE                         | IC5IE                       | T5IE                  | INT4IE                  | OC4IE  | IC4IE         | T4IE   | 0000       |

|                             |                                 | 15:0          | INT3IE  | OC3IE           | IC3IE   | T3IE                          | INT2IE                        | OC2IE                         | IC2IE                         | T2IE                        | INT1IE                        | OC1IE                         | IC1IE                       | T1IE                  | INT0IE                  | CS1IE  | CS0IE         | CTIE   | 0000       |

|                             |                                 | 31:16         | IC3EIE  | IC2EIE          | IC1EIE  | ETHIE                         | CAN2IE <sup>(2)</sup>         | CAN1IE                        | USBIE                         | FCEIE                       | DMA7IE <sup>(2)</sup>         | DMA6IE <sup>(2)</sup>         | DMA5IE <sup>(2)</sup>       | DMA4IE <sup>(2)</sup> | DMA3IE                  | DMA2IE | DMA1IE        | DMA0IE | 0000       |

| 1070                        | IEC1                            | 15:0          | RTCCIE  | FSCMIE          | I2C2MIE | I2C2SIE                       | I2C2BIE                       | U2TXIE<br>SPI4TXIE<br>I2C5MIE | U2RXIE<br>SPI4RXIE<br>I2C5SIE | U2EIE<br>SPI4EIE<br>I2C5BIE | U3TXIE<br>SPI2TXIE<br>I2C4MIE | U3RXIE<br>SPI2RXIE<br>I2C4SIE | U3EIE<br>SPI2EIE<br>I2C4BIE | CMP2IE                | CMP1IE                  | PMPIE  | AD1IE         | CNIE   | 0000       |

|                             | 1500                            | 31:16         | _       | _               | _       | _                             | _                             | _                             | _                             | _                           | _                             | _                             | _                           | _                     | _                       | _      | _             | _      | 0000       |

| 1080                        | IEC2                            | 15:0          | _       | —               | _       | _                             | U5TXIE                        | U5RXIE                        | U5EIE                         | U6TXIE                      | U6RXIE                        | U6EIE                         | U4TXIE                      | U4RXIE                | U4EIE                   | PMPEIE | IC5EIE        | IC4EIE | 0000       |

| 1090                        | IPC0                            | 31:16         |         | _               | —       |                               | INT0IP<2:0>                   |                               | INTOIS                        | S<1:0>                      | _                             | —                             | —                           |                       | CS1IP<2:0>              | >      | CS1IS         | S<1:0> | 0000       |

| 1090                        | IFCU                            | 15:0          | —       | —               | —       |                               | CS0IP<2:0>                    |                               | CSOIS                         | 5<1:0>                      | —                             | —                             | —                           |                       | CTIP<2:0>               |        | CTIS          | <1:0>  | 0000       |

| 10A0                        | IPC1                            | 31:16         |         | —               |         |                               | INT1IP<2:0>                   |                               | INT1IS                        |                             | —                             |                               | —                           |                       | OC1IP<2:0>              | >      | OC1IS         |        | 0000       |

|                             |                                 | 15:0          |         | —               | —       |                               | IC1IP<2:0>                    |                               | IC1IS                         |                             | _                             | —                             | —                           |                       | T1IP<2:0>               |        | T1IS          |        | 0000       |

| 10B0                        | IPC2                            | 31:16         |         | —               |         |                               | INT2IP<2:0>                   |                               | INT2IS                        |                             | _                             |                               | —                           |                       | OC2IP<2:0>              | >      | OC2IS         |        | 0000       |

|                             |                                 | 15:0          | _       | _               | _       |                               | IC2IP<2:0>                    |                               | IC2IS                         |                             | _                             | _                             | _                           |                       | T2IP<2:0>               |        | T2IS          |        | 0000       |

| 10C0                        | IPC3                            | 31:16<br>15:0 |         |                 | _       |                               | INT3IP<2:0><br>IC3IP<2:0>     |                               | INT3IS<br>IC3IS               |                             |                               |                               |                             |                       | OC3IP<2:0><br>T3IP<2:0> | >      | OC3IS<br>T3IS |        | 0000       |

| í                           |                                 | 15.0          |         |                 |         |                               | 10315 <2.0>                   |                               | 10313                         | <1.U2                       |                               |                               | _                           |                       | 1015 <2.0>              |        | 1313          | <1.02  | 0000       |

# TABLE 7-7:INTERRUPT REGISTER MAP FOR PIC32MX764F128L, PIC32MX775F256L, PIC32MX775F512L AND<br/>PIC32MX795F512L DEVICES

**d:** x = unknown value on Reset; — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

Note 1: Except where noted, all registers in this table have corresponding CLR, SET and INV registers at their virtual addresses, plus offsets of 0x4, 0x8 and 0xC, respectively. See Section 12.1.1 "CLR, SET and INV Registers" for more information.

PIC32MX5XX/6XX/7XX

2: This bit is unimplemented on PIC32MX764F128L device.

3: This register does not have associated CLR, SET, and INV registers.

# PIC32MX5XX/6XX/7XX

NOTES:

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6     | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3  | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

|--------------|-------------------|-----------------------|-------------------|-------------------|--------------------|-------------------|------------------|------------------|

| 04.04        | U-0               | U-0                   | R/W-0             | R/W-0             | R/W-0              | U-0               | U-0              | R/W-0            |

| 31:24        |                   | _                     | BYTO              | <1:0>             | WBO <sup>(1)</sup> | _                 | _                | BITO             |

| 00.40        | U-0               | U-0                   | U-0               | U-0               | U-0                | U-0               | U-0              | U-0              |

| 23:16        | —                 | —                     | _                 | —                 | —                  | _                 | _                | _                |

| 45.0         | U-0               | U-0                   | U-0               | R/W-0             | R/W-0              | R/W-0             | R/W-0            | R/W-0            |

| 15:8         | —                 | —                     | _                 |                   |                    | PLEN<4:0>         |                  |                  |

| 7.0          | R/W-0             | R/W-0                 | R/W-0             | U-0               | U-0                | R/W-0             | R/W-0            | R/W-0            |

| 7:0          | CRCEN             | CRCAPP <sup>(1)</sup> | CRCTYP            | _                 | —                  | (                 | CRCCH<2:0>       | ,                |

## REGISTER 10-4: DCRCCON: DMA CRC CONTROL REGISTER

## Legend:

| 0                 |                  |                        |                    |

|-------------------|------------------|------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, | read as '0'        |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared   | x = Bit is unknown |

#### bit 31-30 **Unimplemented:** Read as '0'

- bit 29-28 BYTO<1:0>: CRC Byte Order Selection bits

- 11 = Endian byte swap on half-word boundaries (source half-word order with reverse source byte order per half-word)

- 10 = Swap half-words on word boundaries (reverse source half-word order with source byte order per half-word)

- 01 = Endian byte swap on word boundaries (reverse source byte order)

- 00 = No swapping (source byte order)

- bit 27 **WBO:** CRC Write Byte Order Selection bit<sup>(1)</sup>

- 1 = Source data is written to the destination re-ordered as defined by BYTO<1:0>

- 0 = Source data is written to the destination unaltered

- bit 26-25 Unimplemented: Read as '0'

- bit 24 BITO: CRC Bit Order Selection bit

When CRCTYP (DCRCCON<15>) = 1 (CRC module is in IP Header mode):

- 1 = The IP header checksum is calculated Least Significant bit (LSb) first (reflected)

- 0 = The IP header checksum is calculated Most Significant bit (MSb) first (not reflected)

<u>When CRCTYP (DCRCCON<15>) = 0</u> (CRC module is in LFSR mode):

- 1 = The LFSR CRC is calculated Least Significant bit first (reflected)

- 0 = The LFSR CRC is calculated Most Significant bit first (not reflected)

- bit 23-13 Unimplemented: Read as '0'

- bit 12-8 **PLEN<4:0>:** Polynomial Length bits<sup>(1)</sup>

<u>When CRCTYP (DCRCCON<15>) = 1</u> (CRC module is in IP Header mode): These bits are unused.

<u>When CRCTYP (DCRCCON<15>) = 0</u> (CRC module is in LFSR mode): Denotes the length of the polynomial -1.

- bit 7 CRCEN: CRC Enable bit

- 1 = CRC module is enabled and channel transfers are routed through the CRC module

- 0 = CRC module is disabled and channel transfers proceed normally

- **Note 1:** When WBO = 1, unaligned transfers are not supported and the CRCAPP bit cannot be set.

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|

| 31:24        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 31.24        |                   |                   |                   | _                 |                   |                   | _                | _                |

| 22.10        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 23:16        |                   |                   |                   | _                 |                   |                   | -                |                  |

| 15:8         | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 15.0         |                   |                   |                   | _                 |                   |                   | -                |                  |

| 7:0          | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |

| 7.0          | DPPULUP           | DMPULUP           | DPPULDWN          | DMPULDWN          | VBUSON            | OTGEN             | VBUSCHG          | VBUSDIS          |

### REGISTER 11-4: U10TGCON: USB OTG CONTROL REGISTER

#### Legend:

bit 7

| •                 |                  |                        |                    |

|-------------------|------------------|------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, | read as '0'        |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared   | x = Bit is unknown |

#### bit 31-8 Unimplemented: Read as '0'

**DPPULUP:** D+ Pull-Up Enable bit 1 = D+ data line pull-up resistor is enabled 0 = D+ data line pull-up resistor is disabled

#### bit 6 **DMPULUP:** D- Pull-Up Enable bit

- 1 = D- data line pull-up resistor is enabled

0 = D- data line pull-up resistor is disabled

- bit 5 **DPPULDWN:** D+ Pull-Down Enable bit

- 1 = D+ data line pull-down resistor is enabled

- 0 = D+ data line pull-down resistor is disabled

### bit 4 DMPULDWN: D- Pull-Down Enable bit

- 1 = D- data line pull-down resistor is enabled

- 0 = D- data line pull-down resistor is disabled

#### bit 3 VBUSON: VBUS Power-on bit

- 1 = VBUS line is powered

- 0 = VBUS line is not powered

- bit 2 **OTGEN:** OTG Functionality Enable bit

- 1 = DPPULUP, DMPULUP, DPPULDWN and DMPULDWN bits are under software control

- 0 = DPPULUP, DMPULUP, DPPULDWN and DMPULDWN bits are under USB hardware control

### bit 1 VBUSCHG: VBUS Charge Enable bit

- 1 = VBUS line is charged through a pull-up resistor

- 0 = VBUS line is not charged through a resistor

### bit 0 VBUSDIS: VBUS Discharge Enable bit

- 1 = VBUS line is discharged through a pull-down resistor

- 0 = VBUS line is not discharged through a resistor

| REGIST    | ER 18-1: SPIxCON: SPI CONTROL REGISTER (CONTINUED)                                                                                                                                              |

|-----------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| bit 15    | <b>ON:</b> SPI Peripheral On bit <sup>(1)</sup>                                                                                                                                                 |

|           | 1 = SPI Peripheral is enabled                                                                                                                                                                   |

| bit 11    | 0 = SPI Peripheral is disabled                                                                                                                                                                  |

| bit 14    | Unimplemented: Read as '0'                                                                                                                                                                      |

| bit 13    | SIDL: Stop in Idle Mode bit<br>1 = Discontinue operation when CPU enters in Idle mode                                                                                                           |

|           | 0 = Continue operation in Idle mode                                                                                                                                                             |

| bit 12    | <b>DISSDO:</b> Disable SDOx pin bit                                                                                                                                                             |

|           | 1 = SDOx pin is not used by the module (pin is controlled by associated PORT register)                                                                                                          |

|           | 0 = SDOx pin is controlled by the module                                                                                                                                                        |

| bit 11-10 | MODE<32,16>: 32/16-Bit Communication Select bits                                                                                                                                                |

|           | MODE32 MODE16 Communication                                                                                                                                                                     |

|           | 1 x 32-bit<br>0 1 16-bit                                                                                                                                                                        |

|           | 0 1 16-bit<br>0 0 8-bit                                                                                                                                                                         |

| bit 9     | SMP: SPI Data Input Sample Phase bit                                                                                                                                                            |

|           | Master mode (MSTEN = 1):                                                                                                                                                                        |

|           | 1 = Input data sampled at end of data output time                                                                                                                                               |

|           | 0 = Input data sampled at middle of data output time                                                                                                                                            |

|           | Slave mode (MSTEN = 0):                                                                                                                                                                         |

|           | SMP value is ignored when SPI is used in Slave mode. The module always uses SMP = 0.                                                                                                            |

| bit 8     | CKE: SPI Clock Edge Select bit <sup>(3)</sup>                                                                                                                                                   |

|           | 1 = Serial output data changes on transition from active clock state to Idle clock state (see CKP bit)                                                                                          |

| h:+ 7     | 0 = Serial output data changes on transition from Idle clock state to active clock state (see CKP bit)                                                                                          |

| bit 7     | SSEN: Slave Select Enable (Slave mode) bit<br>1 = SSx pin used for Slave mode                                                                                                                   |

|           | 0 = SSx pin not used for Slave mode (pin is controlled by port function)                                                                                                                        |

| bit 6     | CKP: Clock Polarity Select bit                                                                                                                                                                  |

|           | 1 = Idle state for clock is a high level; active state is a low level                                                                                                                           |

|           | 0 = Idle state for clock is a low level; active state is a high level                                                                                                                           |

| bit 5     | MSTEN: Master Mode Enable bit                                                                                                                                                                   |

|           | 1 = Master mode<br>0 = Slave mode                                                                                                                                                               |

| bit 4     | Unimplemented: Read as '0'                                                                                                                                                                      |

| bit 3-2   | STXISEL<1:0>: SPI Transmit Buffer Empty Interrupt Mode bits                                                                                                                                     |

| Dit 0-2   | 11 = Interrupt is generated when the buffer is not full (has one or more empty elements)                                                                                                        |

|           | 10 = Interrupt is generated when the buffer is empty by one-half or more                                                                                                                        |

|           | 01 = Interrupt is generated when the buffer is completely empty                                                                                                                                 |

|           | 00 = Interrupt is generated when the last transfer is shifted out of SPISR and transmit operations are                                                                                          |

|           | complete                                                                                                                                                                                        |

| bit 1-0   | SRXISEL<1:0>: SPI Receive Buffer Full Interrupt Mode bits<br>11 = Interrupt is generated when the buffer is full                                                                                |

|           | 10 = Interrupt is generated when the buffer is full by one-half or more                                                                                                                         |

|           | 01 = Interrupt is generated when the buffer is not empty                                                                                                                                        |

|           | 00 = Interrupt is generated when the last word in the receive buffer is read (i.e., buffer is empty)                                                                                            |

|           | When using the 1.1 DPOLK divisor the user's activises should not used anywrite the mentation " OPP i                                                                                            |

| Note 1:   | When using the 1:1 PBCLK divisor, the user's software should not read or write the peripheral's SFRs in the SYSCLK cycle immediately following the instruction that clears the module's ON bit. |

| 2:        | This bit can only be written when the ON bit = $0$ .                                                                                                                                            |

| 3:        | This bit is not used in the Framed SPI mode. The user should program this bit to '0' for the Framed SPI                                                                                         |

| 0.        | mode (FRMEN = 1).                                                                                                                                                                               |

|           |                                                                                                                                                                                                 |

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3                  | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |

|--------------|-------------------|-------------------|-------------------|-------------------|------------------------------------|-------------------|------------------|------------------|--|

| 04-04        | R/W-x             | R/W-x             | R/W-x             | R/W-x             | R/W-x                              | R/W-x             | R/W-x            | R/W-x            |  |

| 31:24        |                   | YEAR1             | 0<3:0>            |                   |                                    | YEAR0             | 1<3:0>           |                  |  |

| 00.40        | R/W-x             | R/W-x             | R/W-x             | R/W-x             | R/W-x                              | R/W-x             | R/W-x            | R/W-x            |  |

| 23:16        |                   | MONTH             | 10<3:0>           |                   | MONTH01<3:0>                       |                   |                  |                  |  |

| 45.0         | R/W-x             | R/W-x             | R/W-x             | R/W-x             | R/W-x                              | R/W-x             | R/W-x            | R/W-x            |  |

| 15:8         |                   | DAY10             | <3:0>             |                   | DAY01<3:0>                         |                   |                  |                  |  |

| 7.0          | U-0               | U-0               | U-0               | U-0               | R/W-x                              | R/W-x             | R/W-x            | R/W-x            |  |

| 7:0          | —                 | —                 | _                 | _                 |                                    | WDAYC             | )1<3:0>          |                  |  |

|              |                   |                   |                   |                   |                                    |                   |                  |                  |  |

| Legend:      |                   |                   |                   |                   |                                    |                   |                  |                  |  |

| R = Read     | able bit          |                   | W = Writable      | e bit             | U = Unimplemented bit, read as '0' |                   |                  |                  |  |

0' = Bit is cleared

## REGISTER 22-4: RTCDATE: RTC DATE VALUE REGISTER

bit 31-28 YEAR10<3:0>: Binary-Coded Decimal Value of Years bits, 10 digits

'1' = Bit is set

bit 27-24 YEAR01<3:0>: Binary-Coded Decimal Value of Years bits, 1 digit

bit 23-20 MONTH10<3:0>: Binary-Coded Decimal Value of Months bits, 10 digits; contains a value from 0 to 1

bit 19-16 MONTH01<3:0>: Binary-Coded Decimal Value of Months bits, 1 digit; contains a value from 0 to 9

bit 15-12 DAY10<3:0>: Binary-Coded Decimal Value of Days bits, 10 digits; contains a value from 0 to 3

bit 11-8 DAY01<3:0>: Binary-Coded Decimal Value of Days bits, 1 digit; contains a value from 0 to 9

bit 7-4 Unimplemented: Read as '0'

-n = Value at POR

bit 3-0 WDAY01<3:0>: Binary-Coded Decimal Value of Weekdays bits,1 digit; contains a value from 0 to 6

**Note:** This register is only writable when RTCWREN = 1 (RTCCON<3>).

x = Bit is unknown

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1    | Bit<br>24/16/8/0    |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|---------------------|---------------------|

| 04.04        | U-0                 | U-0                 |

| 31:24        | —                 | —                 | —                 |                   | _                 | —                 | —                   | _                   |

| 00.40        | U-0                 | U-0                 |

| 23:16        | —                 | —                 | —                 | _                 | —                 | —                 | —                   | _                   |

| 45.0         | R/W-0             | U-0               | R/W-0             | U-0               | U-0               | R/W-0             | R/W-0               | R/W-0               |

| 15:8         | ON <sup>(1)</sup> | —                 | SIDL              | _                 | —                 | F                 | ORM<2:0>            |                     |

| 7.0          | R/W-0             | R/W-0             | R/W-0             | R/W-0             | U-0               | R/W-0             | R/W-0, HSC          | R/C-0, HSC          |

| 7:0          |                   | SSRC<2:0>         |                   | CLRASAM           | —                 | ASAM              | SAMP <sup>(2)</sup> | DONE <sup>(3)</sup> |

### REGISTER 23-1: AD1CON1: ADC CONTROL REGISTER 1

#### Legend:

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, re | ad as '0'          |

|-------------------|------------------|---------------------------|--------------------|

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared      | x = Bit is unknown |

#### bit 31-16 Unimplemented: Read as '0'

- bit 15 **ON:** ADC Operating Mode bit<sup>(1)</sup>

- 1 = ADC module is operating

- 0 = ADC module is not operating

- bit 14 Unimplemented: Read as '0'

- bit 13 **SIDL:** Stop in Idle Mode bit

- 1 = Discontinue module operation when device enters Idle mode

- 0 = Continue module operation in Idle mode

- bit 12-11 Unimplemented: Read as '0'

#### bit 10-8 **FORM<2:0>:** Data Output Format bits

- 111 = Signed Fractional 32-bit (DOUT = sddd dddd dd00 0000 0000 0000 0000)

- 110 = Fractional 32-bit (DOUT = dddd dddd dd00 0000 0000 0000 0000)

- 101 = Signed Integer 32-bit (DOUT = ssss ssss ssss ssss ssss dddd dddd)

- 100 = Integer 32-bit (DOUT = 0000 0000 0000 0000 0000 00dd dddd dddd)

- 011 = Signed Fractional 16-bit (DOUT = 0000 0000 0000 0000 sddd dddd dd00 0000)

- 010 = Fractional 16-bit (DOUT = 0000 0000 0000 0000 dddd dddd dd00 0000)

- 000 = Integer 16-bit (DOUT = 0000 0000 0000 0000 0000 00dd dddd dddd)

#### bit 7-5 SSRC<2:0>: Conversion Trigger Source Select bits

- 111 = Internal counter ends sampling and starts conversion (auto convert)

- 110 = Reserved

- 101 = Reserved

- 100 = Reserved

- 011 = CTMU ends sampling and starts conversion

- 010 = Timer 3 period match ends sampling and starts conversion

- 001 = Active transition on INT0 pin ends sampling and starts conversion

- 000 = Clearing the SAMP bit ends sampling and starts conversion

- **Note 1:** When using the 1:1 PBCLK divisor, the user's software should not read/write the peripheral's SFRs in the SYSCLK cycle immediately following the instruction that clears the module's ON bit.

- 2: If ASAM = 0, software can write a '1' to start sampling. This bit is automatically set by hardware if ASAM = 1. If SSRC<2:0> = 000, software can write a '0' to end sampling and start conversion. If SSRC<2:0> ≠ '000', this bit is automatically cleared by hardware to end sampling and start conversion.

- **3:** This bit is automatically set by hardware when analog-to-digital conversion is complete. Software can write a '0' to clear this bit (a write of '1' is not allowed). Clearing this bit does not affect any operation already in progress. This bit is automatically cleared by hardware at the start of a new conversion.

| Bit<br>Range |     |     | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |

|--------------|-----|-----|-------------------|-------------------|-------------------|-------------------|------------------|------------------|--|

| 31:24        | U-0 | U-0 | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |  |

| 31.24        | —   | —   | _                 | _                 | —                 | _                 | —                | —                |  |

| 23:16        | U-0 | U-0 | R-0               | R-0               | R-0               | R-0               | R-0              | R-0              |  |

| 23.10        | —   | —   | ТХВО              | TXBP              | RXBP              | TXWARN            | RXWARN           | EWARN            |  |

| 15:8         | R-0 | R-0 | R-0               | R-0 R-0           |                   | R-0               | R-0              | R-0              |  |

| 10.6         |     |     |                   | TERRCI            | NT<7:0>           |                   |                  |                  |  |

| 7.0          | R-0 | R-0 | R-0               | R-0               | R-0               | R-0               | R-0              | R-0              |  |

| 7:0          |     |     |                   | RERRC             | NT<7:0>           |                   |                  |                  |  |

## REGISTER 24-5: CITREC: CAN TRANSMIT/RECEIVE ERROR COUNT REGISTER

### Legend:

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, r | ead as '0'         |

|-------------------|------------------|--------------------------|--------------------|

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared     | x = Bit is unknown |

### bit 31-22 Unimplemented: Read as '0'

bit 21 **TXBO:** Transmitter in Error State Bus OFF (TERRCNT  $\geq$  256)

- bit 20 **TXBP:** Transmitter in Error State Bus Passive (TERRCNT  $\geq$  128)

- bit 19 **RXBP:** Receiver in Error State Bus Passive (RERRCNT  $\geq$  128)

- bit 18 **TXWARN:** Transmitter in Error State Warning (128 > TERRCNT ≥ 96)

- bit 17 **RXWARN:** Receiver in Error State Warning  $(128 > \text{RERRCNT} \ge 96)$

- bit 16 EWARN: Transmitter or Receiver is in Error State Warning

- bit 15-8 TERRCNT<7:0>: Transmit Error Counter

- bit 7-0 RERRCNT<7:0>: Receive Error Counter

### REGISTER 24-6: CIFSTAT: CAN FIFO STATUS REGISTER

|       |          | Bit<br>30/22/14/6 |          |          | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

|-------|----------|-------------------|----------|----------|-------------------|-------------------|------------------|------------------|

| 04.04 | R-0      | R-0               | R-0      | R-0      | R-0               | R-0               | R-0              | R-0              |

| 31:24 | FIFOIP31 | FIFOIP30          | FIFOIP29 | FIFOIP28 | FIFOIP27          | FIFOIP26          | FIFOIP25         | FIFOIP24         |

| 23:16 | R-0      | R-0               | R-0      | R-0      | R-0               | R-0               | R-0              | R-0              |

| 23.10 | FIFOIP23 | FIFOIP22          | FIFOIP21 | FIFOIP20 | FIFOIP19          | FIFOIP18          | FIFOIP17         | FIFOIP16         |

| 15.0  | R-0      | R-0               | R-0      | R-0      | R-0               | R-0               | R-0              | R-0              |

| 15:8  | FIFOIP15 | FIFOIP14          | FIFOIP13 | FIFOIP12 | FIFOIP11          | FIFOIP10          | FIFOIP9          | FIFOIP8          |

| 7.0   | R-0      | R-0               | R-0      | R-0      | R-0               | R-0               | R-0              | R-0              |

| 7:0   | FIFOIP7  | FIFOIP6           | FIFOIP5  | FIFOIP4  | FIFOIP3           | FIFOIP2           | FIFOIP1          | FIFOIP0          |

## Legend:

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, re | ad as '0'          |

|-------------------|------------------|---------------------------|--------------------|

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared      | x = Bit is unknown |

bit 31-0 FIFOIP<31:0>: FIFOn Interrupt Pending bits

1 = One or more enabled FIFO interrupts are pending

0 = No FIFO interrupts are pending

### REGISTER 25-26: EMAC1IPGR: ETHERNET CONTROLLER MAC NON-BACK-TO-BACK INTERPACKET GAP REGISTER

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |  |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|--|--|

| 31:24        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |  |  |

| 31.24        |                   | —                 |                   |                   |                   |                   | —                | —                |  |  |

| 23:16        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |  |  |

| 23.10        |                   | —                 |                   |                   |                   |                   | —                | —                |  |  |

| 15:8         | U-0               | R/W-0             | R/W-0             | R/W-0             | R/W-1             | R/W-1             | R/W-0            | R/W-0            |  |  |

| 10.0         | —                 | NB2BIPKTGP1<6:0>  |                   |                   |                   |                   |                  |                  |  |  |

| 7:0          | U-0               | R/W-0             | R/W-0             | R/W-1             | R/W-0             | R/W-0             | R/W-1            | R/W-0            |  |  |

| 7.0          |                   |                   |                   | NB2E              | BIPKTGP2<6:       | 0>                |                  |                  |  |  |

| Legend:           |                  |                                    |                    |  |  |  |

|-------------------|------------------|------------------------------------|--------------------|--|--|--|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read as '0' |                    |  |  |  |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared               | x = Bit is unknown |  |  |  |

#### bit 31-15 Unimplemented: Read as '0'

### bit 14-8 NB2BIPKTGP1<6:0>: Non-Back-to-Back Interpacket Gap Part 1 bits

This is a programmable field representing the optional carrierSense window referenced in section 4.2.3.2.1 "Deference" of the IEEE 80.23 Specification. If the carrier is detected during the timing of IPGR1, the MAC defers to the carrier. If, however, the carrier comes after IPGR1, the MAC continues timing IPGR2 and transmits, knowingly causing a collision, thus ensuring fair access to the medium. Its range of values is 0x0 to IPGR2. Its recommend value is 0xC (12d).

#### bit 7 Unimplemented: Read as '0'

# bit 6-0 NB2BIPKTGP2<6:0>: Non-Back-to-Back Interpacket Gap Part 2 bits

This is a programmable field representing the non-back-to-back Inter-Packet-Gap. Its recommended value is 0x12 (18d), which represents the minimum IPG of 0.96  $\mu$ s (in 100 Mbps) or 9.6  $\mu$ s (in 10 Mbps).

**Note:** Both 16-bit and 32-bit accesses are allowed to these registers (including the SET, CLR and INV registers). 8-bit accesses are not allowed and are ignored by the hardware.

# PIC32MX5XX/6XX/7XX

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |  |  |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|--|--|--|

| 31:24        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |  |  |  |

| 31.24        |                   | —                 | _                 | _                 | _                 | _                 | —                | —                |  |  |  |

| 22.16        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |  |  |  |

| 23:16        | _                 | —                 | —                 | _                 | _                 | —                 | _                | —                |  |  |  |

| 45.0         | R/W-P             | R/W-P             | R/W-P             | R/W-P             | R/W-P             | R/W-P             | R/W-P            | R/W-P            |  |  |  |

| 15:8         | STNADDR2<7:0>     |                   |                   |                   |                   |                   |                  |                  |  |  |  |

| 7.0          | R/W-P             | R/W-P             | R/W-P             | R/W-P             | R/W-P             | R/W-P             | R/W-P            | R/W-P            |  |  |  |

| 7:0          |                   |                   |                   | STNADDR           | 1<7:0>            |                   |                  |                  |  |  |  |

## REGISTER 25-39: EMAC1SA2: ETHERNET CONTROLLER MAC STATION ADDRESS 2 REGISTER

| Legend:           | P = Programmable bit               |                      |                    |  |  |  |

|-------------------|------------------------------------|----------------------|--------------------|--|--|--|

| R = Readable bit  | U = Unimplemented bit, read as '0' |                      |                    |  |  |  |

| -n = Value at POR | '1' = Bit is set                   | '0' = Bit is cleared | x = Bit is unknown |  |  |  |

- bit 31-16 Reserved: Maintain as '0'; ignore read

- bit 15-8 **STNADDR2<7:0>:** Station Address Octet 2 bits These bits hold the second transmitted octet of the station address.

- bit 7-0 **STNADDR1<7:0>:** Station Address Octet 1 bits These bits hold the most significant (first transmitted) octet of the station address.

Note 1: Both 16-bit and 32-bit accesses are allowed to these registers (including the SET, CLR and INV registers). 8-bit accesses are not allowed and are ignored by the hardware.

2: This register is loaded at reset from the factory preprogrammed station address.

# 27.1 Control Register

# TABLE 27-1: COMPARATOR VOLTAGE REFERENCE REGISTER MAP

| lress<br>¢)              |                                 | e         |       | Bits  |       |       |       |                        |       |                      |      |       |      |       |      |      |      |      |           |

|--------------------------|---------------------------------|-----------|-------|-------|-------|-------|-------|------------------------|-------|----------------------|------|-------|------|-------|------|------|------|------|-----------|

| Virtual Addr<br>(BF80_#) | Register<br>Name <sup>(1)</sup> | Bit Range | 31/15 | 30/14 | 29/13 | 28/12 | 27/11 | 26/10                  | 25/9  | 24/8                 | 23/7 | 22/6  | 21/5 | 20/4  | 19/3 | 18/2 | 17/1 | 16/0 | All Reset |

| 0000                     | CVRCON                          | 31:16     |       |       | —     | —     | —     | -                      | —     | _                    | _    | _     | -    | _     |      | —    |      | —    | 0000      |

| 9800                     | CVRCON                          | 15:0      | ON    | -     | _     | —     | _     | VREFSEL <sup>(2)</sup> | BGSEL | <1:0> <sup>(2)</sup> | _    | CVROE | CVRR | CVRSS |      | CVR< | 3:0> |      | 0100      |

Legend: x = unknown value on Reset; — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

Note 1: All registers in this table have corresponding CLR, SET and INV registers at their virtual addresses, plus offsets of 0x4, 0x8 and 0xC, respectively. See Section 12.1.1 "CLR, SET and INV Registers" for more information.

2: These bits are not available on PIC32MX575/675/695/775/795 devices. On these devices, reset value for CVRCON is '0000'.

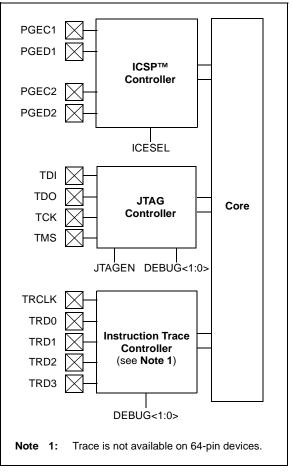

## REGISTER 29-1: DEVCFG0: DEVICE CONFIGURATION WORD 0 (CONTINUED)

- bit 3 ICESEL: In-Circuit Emulator/Debugger Communication Channel Select bit

- 1 = PGEC2/PGED2 pair is used

- 0 = PGEC1/PGED1 pair is used

- bit 2 Reserved: Write '1'

- bit 1-0 DEBUG<1:0>: Background Debugger Enable bits (forced to '11' if code-protect is enabled)

- 11 = Debugger is disabled

- 10 = Debugger is enabled

- 01 = Reserved (same as '11' setting)

- 00 = Reserved (same as '11' setting)

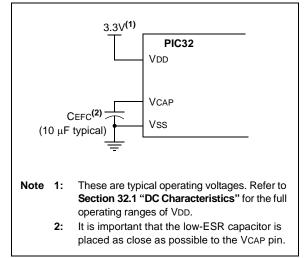

# 29.2 On-Chip Voltage Regulator

All PIC32MX5XX/6XX/7XX devices' core and digital logic are designed to operate at a nominal 1.8V. To simplify system designs, most devices in the PIC32MX-5XX/6XX/7XX family incorporate an on-chip regulator providing the required core logic voltage from VDD.

A low-ESR capacitor (such as tantalum) must be connected to the VCAP pin (see Figure 29-1). This helps to maintain the stability of the regulator. The recommended value for the filter capacitor is provided in **Section 32.1 "DC Characteristics"**.

Note: It is important that the low-ESR capacitor is placed as close as possible to the VCAP pin.

# 29.2.1 ON-CHIP REGULATOR AND POR

It takes a fixed delay for the on-chip regulator to generate an output. During this time, designated as TPU, code execution is disabled. TPU is applied every time the device resumes operation after any power-down, including Sleep mode.

## 29.2.2 ON-CHIP REGULATOR AND BOR

PIC32MX5XX/6XX/7XX devices also have a simple brown-out capability. If the voltage supplied to the regulator is inadequate to maintain a regulated level, the regulator Reset circuitry will generate a Brown-out Reset (BOR). This event is captured by the BOR flag bit (RCON<1>). The brown-out voltage levels are specified in **Section 32.1 "DC Characteristics"**.

# FIGURE 29-1: CONNECTIONS FOR THE ON-CHIP REGULATOR

## 29.3 **Programming and Diagnostics**

PIC32MX5XX/6XX/7XX devices provide a complete range of programming and diagnostic features that can increase the flexibility of any application using them. These features allow system designers to include:

- Simplified field programmability using two-wire In-Circuit Serial Programming<sup>™</sup> (ICSP<sup>™</sup>) interfaces

- Debugging using ICSP

- Programming and debugging capabilities using the EJTAG extension of JTAG

- JTAG boundary scan testing for device and board diagnostics

PIC32 devices incorporate two programming and diagnostic modules, and a trace controller, that provide a range of functions to the application developer.

FIGURE 29-2:

PROGRAMMING, DEBUGGING, AND TRACE PORTS BLOCK DIAGRAM

## 31.11 Demonstration/Development Boards, Evaluation Kits, and Starter Kits

A wide variety of demonstration, development and evaluation boards for various PIC MCUs and dsPIC DSCs allows quick application development on fully functional systems. Most boards include prototyping areas for adding custom circuitry and provide application firmware and source code for examination and modification.

The boards support a variety of features, including LEDs, temperature sensors, switches, speakers, RS-232 interfaces, LCD displays, potentiometers and additional EEPROM memory.

The demonstration and development boards can be used in teaching environments, for prototyping custom circuits and for learning about various microcontroller applications.

In addition to the PICDEM<sup>™</sup> and dsPICDEM<sup>™</sup> demonstration/development board series of circuits, Microchip has a line of evaluation kits and demonstration software for analog filter design, KEELOQ<sup>®</sup> security ICs, CAN, IrDA<sup>®</sup>, PowerSmart battery management, SEEVAL<sup>®</sup> evaluation system, Sigma-Delta ADC, flow rate sensing, plus many more.

Also available are starter kits that contain everything needed to experience the specified device. This usually includes a single application and debug capability, all on one board.

Check the Microchip web page (www.microchip.com) for the complete list of demonstration, development and evaluation kits.

# 31.12 Third-Party Development Tools

Microchip also offers a great collection of tools from third-party vendors. These tools are carefully selected to offer good value and unique functionality.

- Device Programmers and Gang Programmers from companies, such as SoftLog and CCS

- Software Tools from companies, such as Gimpel and Trace Systems

- Protocol Analyzers from companies, such as Saleae and Total Phase

- Demonstration Boards from companies, such as MikroElektronika, Digilent<sup>®</sup> and Olimex

- Embedded Ethernet Solutions from companies, such as EZ Web Lynx, WIZnet and IPLogika<sup>®</sup>

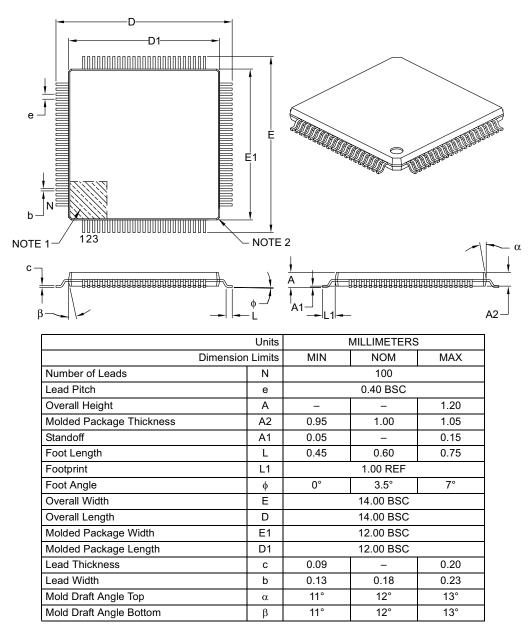

# 100-Lead Plastic Thin Quad Flatpack (PT) – 12x12x1 mm Body, 2.00 mm [TQFP]

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

#### Notes:

- 1. Pin 1 visual index feature may vary, but must be located within the hatched area.

- 2. Chamfers at corners are optional; size may vary.

- 3. Dimensions D1 and E1 do not include mold flash or protrusions. Mold flash or protrusions shall not exceed 0.25 mm per side.

- 4. Dimensioning and tolerancing per ASME Y14.5M.

- BSC: Basic Dimension. Theoretically exact value shown without tolerances.

REF: Reference Dimension, usually without tolerance, for information purposes only.

Microchip Technology Drawing C04-100B