Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFl

| Product Status             | Active                                                                            |

|----------------------------|-----------------------------------------------------------------------------------|

| Core Processor             | MIPS32 ® M4K™                                                                     |

| Core Size                  | 32-Bit Single-Core                                                                |

| Speed                      | 80MHz                                                                             |

| Connectivity               | Ethernet, I <sup>2</sup> C, SPI, UART/USART, USB OTG                              |

| Peripherals                | Brown-out Detect/Reset, DMA, POR, PWM, WDT                                        |

| Number of I/O              | 53                                                                                |

| Program Memory Size        | 512KB (512K x 8)                                                                  |

| Program Memory Type        | FLASH                                                                             |

| EEPROM Size                | -                                                                                 |

| RAM Size                   | 64K x 8                                                                           |

| Voltage - Supply (Vcc/Vdd) | 2.3V ~ 3.6V                                                                       |

| Data Converters            | A/D 16x10b                                                                        |

| Oscillator Type            | Internal                                                                          |

| Operating Temperature      | -40°C ~ 105°C (TA)                                                                |

| Mounting Type              | Surface Mount                                                                     |

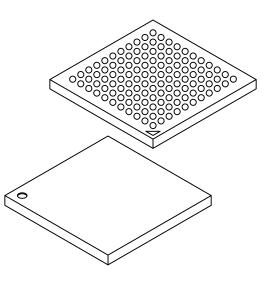

| Package / Case             | 64-VFQFN Exposed Pad                                                              |

| Supplier Device Package    | 64-VQFN (9x9)                                                                     |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic32mx675f512ht-80v-mr |

|                            |                                                                                   |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

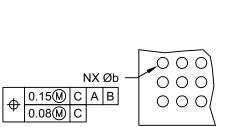

|                |                                            | Pin Nun                    | nber <sup>(1)</sup> |                 |             | <b>D</b> "     |                                       |

|----------------|--------------------------------------------|----------------------------|---------------------|-----------------|-------------|----------------|---------------------------------------|

| Pin Name       | 64-Pin<br>QFN/TQFP                         | 100-Pin<br>TQFP            | 121-Pin<br>TFBGA    | 124-pin<br>VTLA | Pin<br>Type | Buffer<br>Type | Description                           |

| CN0            | 48                                         | 74                         | B11                 | B40             | I           | ST             | Change notification inputs. Can be    |

| CN1            | 47                                         | 73                         | C10                 | A47             | I           | ST             | software programmed for internal weak |

| CN2            | 16                                         | 25                         | K2                  | B14             | I           | ST             | pull-ups on all inputs.               |

| CN3            | 15                                         | 24                         | K1                  | A15             | I           | ST             |                                       |

| CN4            | 14                                         | 23                         | J2                  | B13             | I           | ST             |                                       |

| CN5            | 13                                         | 22                         | J1                  | A13             | I           | ST             |                                       |

| CN6            | 12                                         | 21                         | H2                  | B11             | I           | ST             |                                       |

| CN7            | 11                                         | 20                         | H1                  | A12             | I           | ST             |                                       |

| CN8            | 4                                          | 10                         | E3                  | A7              | I           | ST             |                                       |

| CN9            | 5                                          | 11                         | F4                  | B6              | I           | ST             |                                       |

| CN10           | 6                                          | 12                         | F2                  | A8              | I           | ST             |                                       |

| CN11           | 8                                          | 14                         | F3                  | A9              | I           | ST             |                                       |

| CN12           | 30                                         | 44                         | L8                  | A29             | I           | ST             |                                       |

| CN13           | 52                                         | 81                         | C8                  | B44             | I           | ST             |                                       |

| CN14           | 53                                         | 82                         | B8                  | A55             | I           | ST             |                                       |

| CN15           | 54                                         | 83                         | D7                  | B45             | I           | ST             |                                       |

| CN16           | 55                                         | 84                         | C7                  | A56             | I           | ST             |                                       |

| CN17           | 31                                         | 49                         | L10                 | B27             | I           | ST             |                                       |

| CN18           | 32                                         | 50                         | L11                 | A32             | I           | ST             |                                       |

| CN19           | —                                          | 80                         | D8                  | A54             | I           | ST             |                                       |

| CN20           | —                                          | 47                         | L9                  | B26             | I           | ST             |                                       |

| CN21           | —                                          | 48                         | K9                  | A31             | I           | ST             |                                       |

| IC1            | 42                                         | 68                         | E9                  | B37             | I           | ST             | Capture Inputs 1-5                    |

| IC2            | 43                                         | 69                         | E10                 | A45             | I           | ST             |                                       |

| IC3            | 44                                         | 70                         | D11                 | B38             | I           | ST             | -                                     |

| IC4            | 45                                         | 71                         | C11                 | A46             | I           | ST             | -                                     |

| IC5            | 52                                         | 79                         | A9                  | A60             | I           | ST             | -                                     |

| OCFA           | 17                                         | 26                         | L1                  | A20             | I           | ST             | Output Compare Fault A Input          |

| OC1            | 46                                         | 72                         | D9                  | B39             | 0           | _              | Output Compare Output 1               |

| OC2            | 49                                         | 76                         | A11                 | A52             | 0           |                | Output Compare Output 2               |

| OC3            | 50                                         | 77                         | A10                 | B42             | 0           |                | Output Compare Output 3               |

| OC4            | 51                                         | 78                         | B9                  | A53             | 0           | _              | Output Compare Output 4               |

| OC5            | 52                                         | 81                         | C8                  | B44             | 0           |                | Output Compare Output 5               |

| OCFB           | 30                                         | 44                         | L8                  | A29             | I           | ST             | Output Compare Fault B Input          |

| INT0           | 46                                         | 72                         | D9                  | B39             | I           | ST             | External Interrupt 0                  |

| INT1           | 42                                         | 18                         | G1                  | A11             | I           | ST             | External Interrupt 1                  |

| INT2           | 43                                         | 19                         | G2                  | B10             | I           | ST             | External Interrupt 2                  |

| INT3           | 44                                         | 66                         | E11                 | B36             | 1           | ST             | External Interrupt 3                  |

| INT4           | 45                                         | 67                         | E8                  | A44             | 1           | ST             | External Interrupt 4                  |

| Legend: C<br>S | MOS = CMO<br>T = Schmitt T<br>TL = TTL inp | S compatib<br>rigger input | le input or c       | output          | A           |                | Analog input P = Power                |

TABLE 1-1: PINOUT I/O DESCRIPTIONS (CONTINUED)

Note 1: Pin numbers are only provided for reference. See the "Device Pin Tables" section for device pin availability.

2: See 25.0 "Ethernet Controller" for more information.

#### 2.0 GUIDELINES FOR GETTING STARTED WITH 32-BIT MCUS

**Note:** This data sheet summarizes the features of the PIC32MX5XX/6XX/7XX family of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to the related section of the *"PIC32 Family Reference Manual"*, which is available from the Microchip web site (www.microchip.com/PIC32).

#### 2.1 Basic Connection Requirements

Getting started with the PIC32MX5XX/6XX/7XX family of 32-bit Microcontrollers (MCUs) requires attention to a minimal set of device pin connections before proceeding with development. The following is a list of pin names, which must always be connected:

- All VDD and Vss pins (see 2.2 "Decoupling Capacitors")

- All AVDD and AVss pins even if the ADC module is not used (see 2.2 "Decoupling Capacitors")

- VCAP pin (see 2.3 "Capacitor on Internal Voltage Regulator (VCAP)")

- MCLR pin (see 2.4 "Master Clear (MCLR) Pin")

- PGECx/PGEDx pins used for In-Circuit Serial Programming<sup>™</sup> (ICSP<sup>™</sup>) and debugging purposes (see **2.5** "ICSP Pins")

- OSC1 and OSC2 pins when external oscillator source is used (see 2.8 "External Oscillator Pins")

The following pin may be required, as well: VREF+/ VREF- pins used when external voltage reference for ADC module is implemented.

**Note:** The AVDD and AVSS pins must be connected, regardless of the ADC use and the ADC voltage reference source.

#### 2.2 Decoupling Capacitors

The use of decoupling capacitors on power supply pins, such as VDD, VSS, AVDD and AVSS is required. See Figure 2-1.

Consider the following criteria when using decoupling capacitors:

- Value and type of capacitor: A value of 0.1  $\mu$ F (100 nF), 10-20V is recommended. The capacitor should be a low Equivalent Series Resistance (low-ESR) capacitor and have resonance frequency in the range of 20 MHz and higher. It is further recommended to use ceramic capacitors.

- Placement on the printed circuit board: The decoupling capacitors should be placed as close to the pins as possible. It is recommended that the capacitors be placed on the same side of the board as the device. If space is constricted, the capacitor can be placed on another layer on the PCB using a via; however, ensure that the trace length from the pin to the capacitor is within one-quarter inch (6 mm) in length.

- Handling high frequency noise: If the board is experiencing high frequency noise, upward of tens of MHz, add a second ceramic-type capacitor in parallel to the above described decoupling capacitor. The value of the second capacitor can be in the range of 0.01  $\mu$ F to 0.001  $\mu$ F. Place this second capacitor next to the primary decoupling capacitor. In high-speed circuit designs, consider implementing a decade pair of capacitances as close to the power and ground pins as possible. For example, 0.1  $\mu$ F in parallel with 0.001  $\mu$ F.

- Maximizing performance: On the board layout from the power supply circuit, run the power and return traces to the decoupling capacitors first, and then to the device pins. This ensures that the decoupling capacitors are first in the power chain. Equally important is to keep the trace length between the capacitor and the power pins to a minimum, thereby reducing PCB track inductance.

### PIC32MX5XX/6XX/7XX

NOTES:

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |  |  |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|--|--|--|

| 04.04        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |  |  |  |

| 31:24        | -                 | _                 | _                 | —                 | _                 | —                 | —                | —                |  |  |  |

| 00.40        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |  |  |  |

| 23:16        | —                 | —                 | —                 | —                 | —                 | —                 | —                | —                |  |  |  |

| 45.0         | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R-0              | R-0              |  |  |  |

| 15:8         |                   |                   |                   | BMXDU             | DBA<15:8>         |                   |                  |                  |  |  |  |

| 7.0          | R-0               | R-0               | R-0               | R-0               | R-0               | R-0               | R-0              | R-0              |  |  |  |

| 7:0          | BMXDUDBA<7:0>     |                   |                   |                   |                   |                   |                  |                  |  |  |  |

#### REGISTER 4-3: BMXDUDBA: DATA RAM USER DATA BASE ADDRESS REGISTER

#### Legend:

| Legena:           |                  |                           |                    |

|-------------------|------------------|---------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, re | ad as '0'          |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared      | x = Bit is unknown |

bit 31-16 Unimplemented: Read as '0'

#### bit 15-10 BMXDUDBA<15:10>: DRM User Data Base Address bits

When non-zero, the value selects the relative base address for User mode data space in RAM, the value must be greater than BMXDKPBA.

bit 9-0 BMXDUDBA<9:0>: DRM User Data Base Address Read-Only bits Value is always '0', which forces 1 KB increments

**Note 1:** At Reset, the value in this register is forced to zero, which causes all of the RAM to be allocated to Kernal mode data usage.

2: The value in this register must be less than or equal to BMXDRMSZ.

# TABLE 12-5: PORTD REGISTER MAP FOR PIC32MX534F064H, PIC32MX564F064H, PIC32MX564F128H, PIC32MX575F512H, PIC32MX575F512H, PIC32MX664F064H, PIC32MX664F128H, PIC32MX675F256H, PIC32MX675F512H, PIC32MX695F512H, PIC32MX775F512H, PIC32MX775F512H, AND PIC32MX795F512H DEVICES

| ess                         |                                 |           |       |       |       |       |         |         |        | Bi     | ts     |        |        |        |        |        |        |        | ú          |

|-----------------------------|---------------------------------|-----------|-------|-------|-------|-------|---------|---------|--------|--------|--------|--------|--------|--------|--------|--------|--------|--------|------------|

| Virtual Address<br>(BF88_#) | Register<br>Name <sup>(1)</sup> | Bit Range | 31/15 | 30/14 | 29/13 | 28/12 | 27/11   | 26/10   | 25/9   | 24/8   | 23/7   | 22/6   | 21/5   | 20/4   | 19/3   | 18/2   | 17/1   | 16/0   | All Resets |

| 60C0                        | TRISD                           | 31:16     | -     | -     | -     | _     | _       | -       | —      | —      | —      | —      | —      | -      | _      | -      | -      | —      | 0000       |

| 6000                        | TRISD                           | 15:0      | _     | _     | _     | -     | TRISD11 | TRISD10 | TRISD9 | TRISD8 | TRISD7 | TRISD6 | TRISD5 | TRISD4 | TRISD3 | TRISD2 | TRISD1 | TRISD0 | OFFF       |

| 6000                        | PORTD                           | 31:16     | _     |       |       | _     | _       |         | -      |        |        |        |        | _      | _      |        | _      | _      | 0000       |

| 6000                        | PORID                           | 15:0      | -     | -     | _     | _     | RD11    | RD10    | RD9    | RD8    | RD7    | RD6    | RD5    | RD4    | RD3    | RD2    | RD1    | RD0    | xxxx       |

| 60E0                        | LATD                            | 31:16     | _     | _     | _     | -     | _       | -       | _      | _      | _      | _      | _      | _      | -      | _      | _      | _      | 0000       |

| 60E0                        | LAID                            | 15:0      | _     | _     | _     | -     | LATD11  | LATD10  | LATD9  | LATD8  | LATD7  | LATD6  | LATD5  | LATD4  | LATD3  | LATD2  | LATD1  | LATD0  | xxxx       |

| 60F0                        | ODCD                            | 31:16     | _     | -     | _     | _     | _       | —       | -      | -      | -      |        |        | —      | _      | _      | _      | -      | 0000       |

| OUFU                        | ODCD                            | 15:0      |       | _     | —     | _     | ODCD11  | ODCD10  | ODCD9  | ODCD8  | ODCD7  | ODCD6  | ODCD5  | ODCD4  | ODCD3  | ODCD2  | ODCD1  | ODCD0  | 0000       |

Legend: x = unknown value on Reset; - = unimplemented, read as '0'. Reset values are shown in hexadecimal.

Note 1: All registers in this table have corresponding CLR, SET and INV registers at their virtual addresses, plus offsets of 0x4, 0x8 and 0xC, respectively. See Section 12.1.1 "CLR, SET and INV Registers" for more information.

# TABLE 12-6: PORTD REGISTER MAP FOR PIC32MX534F064L, PIC32MX564F064L, PIC32MX564F128L, PIC32MX575F512L, PIC32MX664F064L, PIC32MX664F128L, PIC32MX675F256L, PIC32MX675F512L, PIC32MX695F512L, PIC32MX764F128L, PIC32MX775F512L, AND PIC32MX795F512L DEVICES

| ess                         |       | Ċ,        |         |         |         |         |         |         |        | Bi     | ts     |        |        |        |        |        |        |        | 6         |

|-----------------------------|-------|-----------|---------|---------|---------|---------|---------|---------|--------|--------|--------|--------|--------|--------|--------|--------|--------|--------|-----------|

| Virtual Address<br>(BF88_#) |       | Bit Range | 31/15   | 30/14   | 29/13   | 28/12   | 27/11   | 26/10   | 25/9   | 24/8   | 23/7   | 22/6   | 21/5   | 20/4   | 19/3   | 18/2   | 17/1   | 16/0   | All Reset |

| 60C0                        | TRISD | 31:16     | _       | _       | _       | -       | -       | _       |        | _      | -      | -      | _      |        | -      | -      | —      | —      | 0000      |

| 6000                        | TRISD | 15:0      | TRISD15 | TRISD14 | TRISD13 | TRISD12 | TRISD11 | TRISD10 | TRISD9 | TRISD8 | TRISD7 | TRISD6 | TRISD5 | TRISD4 | TRISD3 | TRISD2 | TRISD1 | TRISD0 | FFFF      |

| 60D0                        | PORTD | 31:16     | _       | _       |         |         |         | -       |        |        |        |        | -      |        |        |        | _      | _      | 0000      |

| 0000                        | FORID | 15:0      | RD15    | RD14    | RD13    | RD12    | RD11    | RD10    | RD9    | RD8    | RD7    | RD6    | RD5    | RD4    | RD3    | RD2    | RD1    | RD0    | xxxx      |

| 60E0                        | LATD  | 31:16     | —       | _       | _       | _       | _       | _       | _      | _      | -      | _      | _      | _      | _      | _      | —      | —      | 0000      |

| OUEU                        | LAID  | 15:0      | LAT15   | LAT14   | LAT13   | LAT12   | LATD11  | LATD10  | LATD9  | LATD8  | LATD7  | LATD6  | LATD5  | LATD4  | LATD3  | LATD2  | LATD1  | LATD0  | xxxx      |

| 60F0                        | ODCD  | 31:16     | _       | _       |         |         |         | _       | -      |        |        |        | _      | -      |        |        | _      | -      | 0000      |

| OUFU                        | ODCD  | 15:0      | ODCD15  | ODCD14  | ODCD13  | ODCD12  | ODCD11  | ODCD10  | ODCD9  | ODCD8  | ODCD7  | ODCD6  | ODCD5  | ODCD4  | ODCD3  | ODCD2  | ODCD1  | ODCD0  | 0000      |

Ļ

Legend: x = unknown value on Reset; — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

Note 1: All registers in this table have corresponding CLR, SET and INV registers at their virtual addresses, plus offsets of 0x4, 0x8 and 0xC, respectively. See Section 12.1.1 "CLR, SET and INV Registers" for more information.

#### 14.2 Control Registers

| TABLE 14-1: | TIMER2 THROUGH TIMER5 REGISTER MAP |

|-------------|------------------------------------|

|             |                                    |

|                             |                                 | ••            |                                                         |       |       |       |       |       |      |          |            |      |                |          |      |      |                         |      |            |

|-----------------------------|---------------------------------|---------------|---------------------------------------------------------|-------|-------|-------|-------|-------|------|----------|------------|------|----------------|----------|------|------|-------------------------|------|------------|

| ess                         |                                 |               |                                                         |       |       |       |       |       |      | В        | ts         |      |                |          |      |      |                         |      |            |

| Virtual Address<br>(BF80_#) | Register<br>Name <sup>(1)</sup> | Bit Range     | 31/15                                                   | 30/14 | 29/13 | 28/12 | 27/11 | 26/10 | 25/9 | 24/8     | 23/7       | 22/6 | 21/5           | 20/4     | 19/3 | 18/2 | 17/1                    | 16/0 | All Resets |

| 0800                        | T2CON                           | 31:16         | —                                                       | _     | —     | —     |       | —     |      |          | —          | —    | —              |          | —    | -    | —                       |      | 0000       |

| 0800                        | 12001                           | 15:0          | ) ON - SIDL TGATE TCKPS<2:0> T32 - TCS <sup>(2)</sup> - |       |       |       |       |       |      |          | 0000       |      |                |          |      |      |                         |      |            |

| 0810                        | TMR2                            | 31:16         |                                                         |       |       |       |       |       |      |          |            | 0000 |                |          |      |      |                         |      |            |

| 0010                        | T IVIT VZ                       | 15:0          |                                                         |       |       |       |       |       |      |          |            |      | 0000           |          |      |      |                         |      |            |

| 0820                        | PR2                             | 31:16         | —                                                       |       |       |       |       |       |      |          |            | 0000 |                |          |      |      |                         |      |            |

| 0020                        | 1112                            | 15:0          |                                                         |       |       |       |       |       |      | PR2<     | 15:0>      |      | •              |          |      |      |                         |      | FFFF       |

| 0A00                        | T3CON                           | 31:16         | —                                                       | —     | —     | —     | —     | —     | —    | _        | —          | —    | —              | —        | —    | —    | —                       | —    | 0000       |

| 0,100                       | 100011                          | 15:0          | ON                                                      | —     | SIDL  | _     | _     | —     | _    | _        | TGATE      |      | TCKPS<2:0>     | <b>`</b> | —    | —    | TCS <sup>(2)</sup>      | _    | 0000       |

| 0A10                        | TMR3                            | 31:16         | —                                                       | —     | —     | _     | —     | —     | —    | —        | —          | —    | —              | —        | —    | —    | —                       | —    | 0000       |

|                             |                                 | 15:0          |                                                         |       | 1     |       |       |       |      | TMR3     | <15:0>     |      |                |          |      |      |                         |      | 0000       |

| 0A20                        | PR3                             | 31:16         | —                                                       | —     | —     | —     | —     | —     | —    | —        | —          | —    | —              | —        | —    | —    | —                       | —    | 0000       |

|                             | -                               | 15:0          |                                                         |       |       |       |       |       |      | PR3<     | 15:0>      |      | -              |          |      |      |                         |      | FFFF       |

| 0C00                        | T4CON                           | 31:16         | _                                                       | —     | —     | —     | —     | —     | —    | —        | —          | —    | —              | —        |      | —    |                         | —    | 0000       |

|                             |                                 | 15:0          | ON                                                      | _     | SIDL  | —     | _     | _     |      | _        | TGATE      |      | TCKPS<2:0>     | >        | T32  | _    | TCS <sup>(2)</sup>      | _    | 0000       |

| 0C10                        | TMR4                            | 31:16         | —                                                       | —     |       | —     | —     | —     | _    |          |            | —    | —              | —        |      | _    | —                       | _    | 0000       |

|                             |                                 | 15:0          |                                                         |       |       |       |       |       |      | TMR4     |            |      |                |          |      |      |                         |      | 0000       |

| 0C20                        | PR4                             | 31:16         | -                                                       | —     | —     | —     | _     | _     | _    | -        | -          | _    | —              | _        | —    | _    | _                       | —    | 0000       |

|                             |                                 | 15:0          | _                                                       |       |       | _     |       |       |      | PR4<     |            |      |                | _        |      | _    | _                       | _    | FFFF       |

| 0E00                        | T5CON                           | 31:16<br>15:0 | ON                                                      |       |       |       |       |       |      |          | —<br>TGATE |      | <br>TCKPS<2:0> |          |      |      | —<br>TCS <sup>(2)</sup> |      | 0000       |

| <u> </u>                    |                                 | 31:16         | - UN                                                    |       | SIDL  |       |       |       |      | _        | IGATE      | _    |                | ,<br>    | _    |      | -                       | _    | 0000       |

| 0E10                        | TMR5                            | 15:0          | _                                                       |       | _     | _     |       | —     |      | <br>TMR5 |            | _    | _              |          | _    | _    |                         | _    | 0000       |

|                             |                                 | 31:16         | _                                                       | _     |       | _     | _     | _     | _    | —        |            | _    | _              | _        | _    | _    | _                       | _    | 0000       |

| 0E20                        | PR5                             | 15:0          |                                                         |       |       |       |       |       |      |          |            |      |                |          |      |      |                         |      |            |

|                             |                                 | 13.0          | PR5<15:0> FFFF                                          |       |       |       |       |       |      |          |            |      |                |          |      |      |                         |      |            |

Legend: x = unknown value on Reset; — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

Note 1: All registers in this table have corresponding CLR, SET and INV registers at their virtual addresses, plus offsets of 0x4, 0x8 and 0xC, respectively. See Section 12.1.1 "CLR, SET and INV Registers" for more information.

2: These bits are not available on 64-pin devices.

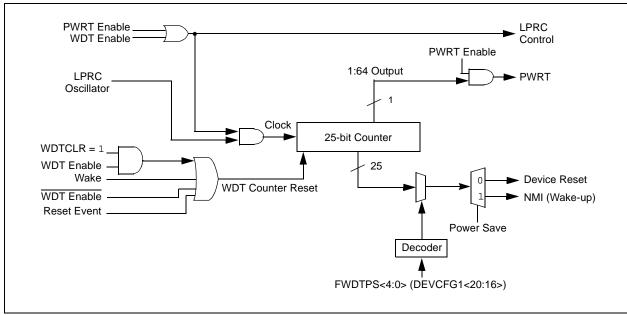

### 15.0 WATCHDOG TIMER (WDT)

Note: This data sheet summarizes the features of the PIC32MX5XX/6XX/7XX family of devices. However, it is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to Section 8. "Watchdog Timer and Power-up Timer" in the "PIC32 (DS60001114) Family Reference Manual", which is available from the Microchip web site (www.microchip.com/PIC32).

This section describes the operation of the WDT and Power-up Timer of the PIC32MX5XX/6XX/7XX.

The WDT, when enabled, operates from the internal Low-Power Oscillator (LPRC) clock source and can be used to detect system software malfunctions by resetting the device if the WDT is not cleared periodically in software. Various WDT time-out periods can be selected using the WDT postscaler. The WDT can also be used to wake the device from Sleep or Idle mode.

The following are key features of the WDT module:

- Configuration or software controlled

- User-configurable time-out period

- Can wake the device from Sleep or Idle mode

#### FIGURE 15-1: WATCHDOG TIMER AND POWER-UP TIMER BLOCK DIAGRAM

| Bit Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

|-----------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|

| 24.24     | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 31:24     | _                 | —                 |                   |                   | _                 |                   |                  |                  |

| 00.40     | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 23:16     | _                 | —                 | _                 | _                 | _                 | _                 | _                | _                |

| 45.0      | R/W-0             | U-0               | R/W-0             | U-0               | U-0               | U-0               | R/W-0            | R/W-0            |

| 15:8      | ON <sup>(1)</sup> | —                 | SIDL              | _                 | _                 | _                 | FEDGE            | C32              |

| 7.0       | R/W-0             | R/W-0             | R/W-0             | R-0               | R-0               | R/W-0             | R/W-0            | R/W-0            |

| 7:0       | ICTMR ICI<        |                   | 1:0>              | ICOV              | ICBNE             |                   | ICM<2:0>         |                  |

#### REGISTER 16-1: ICxCON: INPUT CAPTURE 'x' CONTROL REGISTER

#### Legend:

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, | read as '0'        |

|-------------------|------------------|------------------------|--------------------|

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared   | x = Bit is unknown |

| bit 31-16 | Unimplemented: Read as '0'                                                                                                                                |

|-----------|-----------------------------------------------------------------------------------------------------------------------------------------------------------|

| bit 15    | ON: Input Capture Module Enable bit <sup>(1)</sup>                                                                                                        |

|           | <ul> <li>1 = Module is enabled</li> <li>0 = Disable and reset module, disable clocks, disable interrupt generation and allow SFR modifications</li> </ul> |

| bit 14    | Unimplemented: Read as '0'                                                                                                                                |

| bit 13    | SIDL: Stop in Idle Control bit                                                                                                                            |

|           | <ul><li>1 = Halt in Idle mode</li><li>0 = Continue to operate in Idle mode</li></ul>                                                                      |

| bit 12-10 | Unimplemented: Read as '0'                                                                                                                                |

| bit 9     | FEDGE: First Capture Edge Select bit (only used in mode 6, ICM<2:0> = 110)                                                                                |

|           | <ul> <li>1 = Capture rising edge first</li> <li>0 = Capture falling edge first</li> </ul>                                                                 |

| bit 8     | C32: 32-bit Capture Select bit                                                                                                                            |

|           | <ul><li>1 = 32-bit timer resource capture</li><li>0 = 16-bit timer resource capture</li></ul>                                                             |

| bit 7     | ICTMR: Timer Select bit (Does not affect timer selection when C32 (ICxCON<8>) is '1')                                                                     |

|           | <ul> <li>1 = Timer2 is the counter source for capture</li> <li>0 = Timer3 is the counter source for capture</li> </ul>                                    |

| bit 6-5   | ICI<1:0>: Interrupt Control bits                                                                                                                          |

|           | 11 = Interrupt on every fourth capture event                                                                                                              |

|           | <ul> <li>10 = Interrupt on every third capture event</li> <li>01 = Interrupt on every second capture event</li> </ul>                                     |

|           | 00 = Interrupt on every capture event                                                                                                                     |

| bit 4     | ICOV: Input Capture Overflow Status Flag bit (read-only)                                                                                                  |

|           | <ul> <li>1 = Input capture overflow is occurred</li> <li>0 = No input capture overflow is occurred</li> </ul>                                             |

| bit 3     | ICBNE: Input Capture Buffer Not Empty Status bit (read-only)                                                                                              |

|           | <ul> <li>1 = Input capture buffer is not empty; at least one more capture value can be read</li> <li>0 = Input capture buffer is empty</li> </ul>         |

|           |                                                                                                                                                           |

**Note 1:** When using the 1:1 PBCLK divisor, the user's software should not read/write the peripheral's SFRs in the SYSCLK cycle immediately following the instruction that clears the module's ON bit.

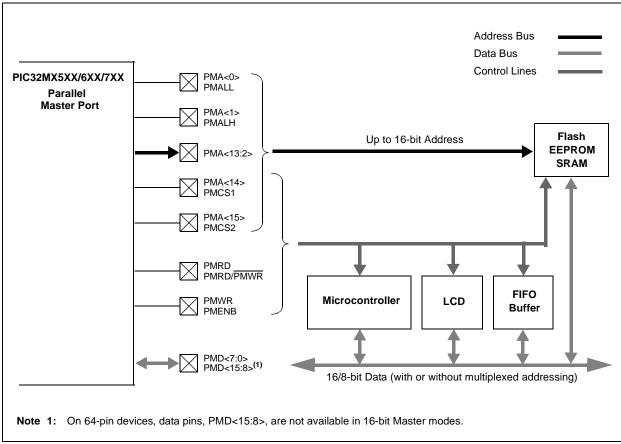

#### 21.0 PARALLEL MASTER PORT (PMP)

Note: This data sheet summarizes the features of the PIC32MX5XX/6XX/7XX family of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to Section 13. "Parallel Master Port (PMP)" (DS60001128) in the "PIC32 Family Reference Manual", which is available from the Microchip web site (www.microchip.com/PIC32).

The PMP is a parallel 8-bit/16-bit input/output module specifically designed to communicate with a wide variety of parallel devices, such as communications peripherals, LCDs, external memory devices and microcontrollers. Because the interface to parallel peripherals varies significantly, the PMP module is highly configurable. Figure 21-1 shows the PMP module pinout and its connections to external devices.

**FIGURE 21-1:**

The following are key features of the PMP module:

- 8-bit and 16-bit interface

- Up to 16 programmable address lines

- Up to two Chip Select lines

- Programmable strobe options

- Individual read and write strobes, or

- Read/Write strobe with enable strobe

- · Address auto-increment/auto-decrement

- · Programmable address/data multiplexing

- Programmable polarity on control signals

- · Parallel Slave Port support

- Legacy addressable

- Address support

- 4-byte deep auto-incrementing buffer

- · Programmable wait states

- · Operates during Sleep and Idle modes

- Fast bit manipulation using CLR, SET and INV registers

Note: On 64-pin devices, the PMD<15:8> data pins are not available.

PMP MODULE PINOUT AND CONNECTIONS TO EXTERNAL DEVICES

#### REGISTER 21-1: PMCON: PARALLEL PORT CONTROL REGISTER (CONTINUED)

- bit 3 **CS1P:** Chip Select 0 Polarity bit<sup>(2)</sup>

- 1 = Active-high (PMCS1)

- $0 = \text{Active-low}(\overline{\text{PMCS1}})$

- bit 2 Unimplemented: Read as '0'

- bit 1 WRSP: Write Strobe Polarity bit

- For Slave Modes and Master mode 2 (PMMODE<9:8> = 00,01,10):

- 1 = Write strobe active-high (PMWR)

- $0 = Write strobe active-low (\overline{PMWR})$

For Master mode 1 (PMMODE<9:8> = 11):

- 1 = Enable strobe active-high (PMENB)

- 0 = Enable strobe active-low (PMENB)

- bit 0 RDSP: Read Strobe Polarity bit

- For Slave modes and Master mode 2 (PMMODE<9:8> = 00,01,10):

- 1 = Read Strobe active-high (PMRD)

- 0 = Read Strobe active-low (PMRD)

For Master mode 1 (PMMODE<9:8> = 11):

- 1 = Read/write strobe active-high (PMRD/ $\overline{PMWR}$ )

- 0 = Read/write strobe active-low (PMRD/PMWR)

- **Note 1:** When using the 1:1 PBCLK divisor, the user's software should not read/write the peripheral's SFRs in the SYSCLK cycle immediately following the instruction that clears the module's ON control bit.

- 2: These bits have no effect when their corresponding pins are used as address lines.

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |  |  |  |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|--|--|--|--|

| 31:24        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |  |  |  |  |

| 31.24        | —                 | —                 | _                 | _                 | —                 | _                 | —                | —                |  |  |  |  |

| 23:16        | U-0               | U-0               | R-0               | R-0               | R-0               | R-0               | R-0              | R-0              |  |  |  |  |

| 23.10        | —                 | —                 | ТХВО              | TXBP              | RXBP              | TXWARN            | RXWARN           | EWARN            |  |  |  |  |

| 15:8         | R-0               | R-0               | R-0               | R-0               | R-0               | R-0               | R-0              | R-0              |  |  |  |  |

| 10.6         |                   |                   |                   | TERRCI            | NT<7:0>           |                   |                  |                  |  |  |  |  |

| 7.0          | R-0               | R-0               | R-0               | R-0               | R-0               | R-0               | R-0              | R-0              |  |  |  |  |

| 7:0          | RERRCNT<7:0>      |                   |                   |                   |                   |                   |                  |                  |  |  |  |  |

#### REGISTER 24-5: CITREC: CAN TRANSMIT/RECEIVE ERROR COUNT REGISTER

#### Legend:

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read as '0' |                    |  |  |

|-------------------|------------------|------------------------------------|--------------------|--|--|

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared               | x = Bit is unknown |  |  |

#### bit 31-22 Unimplemented: Read as '0'

bit 21 **TXBO:** Transmitter in Error State Bus OFF (TERRCNT  $\geq$  256)

- bit 20 **TXBP:** Transmitter in Error State Bus Passive (TERRCNT  $\geq$  128)

- bit 19 **RXBP:** Receiver in Error State Bus Passive (RERRCNT  $\geq$  128)

- bit 18 **TXWARN:** Transmitter in Error State Warning (128 > TERRCNT ≥ 96)

- bit 17 **RXWARN:** Receiver in Error State Warning  $(128 > \text{RERRCNT} \ge 96)$

- bit 16 EWARN: Transmitter or Receiver is in Error State Warning

- bit 15-8 TERRCNT<7:0>: Transmit Error Counter

- bit 7-0 RERRCNT<7:0>: Receive Error Counter

#### REGISTER 24-6: CIFSTAT: CAN FIFO STATUS REGISTER

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|

| 31:24        | R-0               | R-0               | R-0               | R-0               | R-0               | R-0               | R-0              | R-0              |

| 31.24        | FIFOIP31          | FIFOIP30          | FIFOIP29          | FIFOIP28          | FIFOIP27          | FIFOIP26          | FIFOIP25         | FIFOIP24         |

| 23:16        | R-0               | R-0               | R-0               | R-0               | R-0               | R-0               | R-0              | R-0              |

| 23.10        | FIFOIP23          | FIFOIP22          | FIFOIP21          | FIFOIP20          | FIFOIP19          | FIFOIP18          | FIFOIP17         | FIFOIP16         |

| 15.0         | R-0               | R-0               | R-0               | R-0               | R-0               | R-0               | R-0              | R-0              |

| 15:8         | FIFOIP15          | FIFOIP14          | FIFOIP13          | FIFOIP12          | FIFOIP11          | FIFOIP10          | FIFOIP9          | FIFOIP8          |

| 7.0          | R-0               | R-0               | R-0               | R-0               | R-0               | R-0               | R-0              | R-0              |

| 7:0          | FIFOIP7           | FIFOIP6           | FIFOIP5           | FIFOIP4           | FIFOIP3           | FIFOIP2           | FIFOIP1          | FIFOIP0          |

#### Legend:

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read as '0' |                    |  |

|-------------------|------------------|------------------------------------|--------------------|--|

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared               | x = Bit is unknown |  |

bit 31-0 FIFOIP<31:0>: FIFOn Interrupt Pending bits

1 = One or more enabled FIFO interrupts are pending

0 = No FIFO interrupts are pending

## PIC32MX5XX/6XX/7XX

#### REGISTER 25-17: ETHFRMTXOK: ETHERNET CONTROLLER FRAMES TRANSMITTED OK STATISTICS REGISTER

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |  |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|--|--|

| 31:24        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |  |  |

| 31.24        | —                 | —                 | _                 | _                 | _                 | _                 | —                | —                |  |  |

| 22:46        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |  |  |

| 23:16        | —                 | —                 | _                 | _                 | _                 | _                 | —                | —                |  |  |

| 15.0         | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |

| 15:8         |                   |                   |                   | FRMTXOK           | CNT<15:8>         |                   |                  |                  |  |  |

| 7.0          | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |

| 7:0          | FRMTXOKCNT<7:0>   |                   |                   |                   |                   |                   |                  |                  |  |  |

#### Legend:

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, r | read as '0'        |  |

|-------------------|------------------|--------------------------|--------------------|--|

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared     | x = Bit is unknown |  |

#### bit 31-16 Unimplemented: Read as '0'

bit 15-0 **FRMTXOKCNT<15:0>:** Frame Transmitted OK Count bits Increment counter for frames successfully transmitted.

Note 1: This register is only used for TX operations.

2: This register is automatically cleared by hardware after a read operation, unless the byte enables for bytes 0/1 are '0'.

**3:** It is recommended to use the SET, CLR, or INV registers to set or clear any bit in this register. Setting or clearing any bits in this register should only be done for debug/test purposes.

| DC CHA        | RACTERIS               | Standard Operating Conditions: 2.3V to 3.6V<br>(unless otherwise stated)<br>Operating temperature $-40^{\circ}C \le TA \le +85^{\circ}C$ for Industrial<br>$-40^{\circ}C \le TA \le +105^{\circ}C$ for V-Temp |           |             |                              |                                                    |  |  |  |

|---------------|------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------|-------------|------------------------------|----------------------------------------------------|--|--|--|

| Param.<br>No. | Typical <sup>(2)</sup> | Max.                                                                                                                                                                                                          | Units     |             | Conditions                   |                                                    |  |  |  |

| Power-D       | Oown Curre             | nt (IPD) <sup>(1)</sup> f                                                                                                                                                                                     | or PIC32  | AX534/564/  | /664/764                     | Family Devices                                     |  |  |  |

| DC40g         | 12                     | 40                                                                                                                                                                                                            |           | -40°C       |                              |                                                    |  |  |  |

| DC40h         | 20                     | 120                                                                                                                                                                                                           |           | +25°C       | 2.3V                         | Base Power-Down Current (Note 6)                   |  |  |  |

| DC40i         | 210                    | 600                                                                                                                                                                                                           |           | +85°C       | 2.30                         | Base Power-Down Current (Note 6)                   |  |  |  |

| DC40o         | 400                    | 1000                                                                                                                                                                                                          |           | +105°C      |                              |                                                    |  |  |  |

| DC40j         | 20                     | 120                                                                                                                                                                                                           |           | +25°C       | 3.3V Base Power-Down Current |                                                    |  |  |  |

| DC40k         | 15                     | 80                                                                                                                                                                                                            | μA        | -40°C       |                              |                                                    |  |  |  |

| DC40I         | 20                     | 120                                                                                                                                                                                                           |           | +25°C       |                              |                                                    |  |  |  |

| DC40m         | 113                    | 350 <sup>(5)</sup>                                                                                                                                                                                            |           | +70°C       | 3.6V                         | Base Power-Down Current                            |  |  |  |

| DC40n         | 220                    | 650                                                                                                                                                                                                           |           | +85°C       |                              |                                                    |  |  |  |

| DC40p         | 500                    | 1000                                                                                                                                                                                                          |           | +105°C      |                              |                                                    |  |  |  |

| Module        | Differential           | Current fo                                                                                                                                                                                                    | or PIC32N | IX534/564/0 | 664/764                      | Family Devices                                     |  |  |  |

| DC41c         | _                      | 10                                                                                                                                                                                                            |           |             | 2.5V                         | Watchdog Timer Current: AIWDT (Notes 3,6)          |  |  |  |

| DC41d         | 5                      |                                                                                                                                                                                                               | μA        | —           | 3.3V                         | Watchdog Timer Current: AIWDT (Note 3)             |  |  |  |

| DC41e         | _                      | 20                                                                                                                                                                                                            |           |             | 3.6V                         | Watchdog Timer Current: AIWDT (Note 3)             |  |  |  |

| DC42c         | —                      | 40                                                                                                                                                                                                            |           |             | 2.5V                         | RTCC + Timer1 w/32 kHz Crystal: ΔIRTCC (Notes 3,6) |  |  |  |

| DC42d         | 23                     | _                                                                                                                                                                                                             | μA        | —           | 3.3V                         | RTCC + Timer1 w/32 kHz Crystal: ΔIRTCC (Note 3)    |  |  |  |

| DC42e         | —                      | 50                                                                                                                                                                                                            |           |             | 3.6V                         | RTCC + Timer1 w/32 kHz Crystal: ΔIRTCC (Note 3)    |  |  |  |

| DC43c         | —                      | 1300                                                                                                                                                                                                          |           |             | 2.5V                         | ADC: ΔIADC (Notes 3,4,6)                           |  |  |  |

| DC43d         | 1100                   |                                                                                                                                                                                                               | μA        | —           | 3.3V ADC: △IADC (Notes 3,4)  |                                                    |  |  |  |

| DC43e         | _                      | 1300                                                                                                                                                                                                          |           |             | 3.6V                         | ADC: ΔIADC (Notes 3,4)                             |  |  |  |

#### TABLE 32-7: DC CHARACTERISTICS: POWER-DOWN CURRENT (IPD) (CONTINUED)

Note 1: The test conditions for IPD current measurements are as follows:

- Oscillator mode is EC (for 8 MHz and below) and EC+PLL (for above 8 MHz) with OSC1 driven by external square wave from rail-to-rail, (OSC1 input clock input over/undershoot < 100 mV required)</li>

- OSC2/CLKO is configured as an I/O input pin

- USB PLL oscillator is disabled if the USB module is implemented, PBCLK divisor = 1:8

- CPU is in Sleep mode, program Flash memory Wait states = 111, Program Cache and Prefetch are disabled and SRAM data memory Wait states = 1

- No peripheral modules are operating, (ON bit = 0)

- WDT, Clock Switching, Fail-Safe Clock Monitor, and Secondary Oscillator are disabled

- All I/O pins are configured as inputs and pulled to Vss

- $\overline{\text{MCLR}} = \text{VDD}$

- RTCC and JTAG are disabled

- 2: Data in the "Typical" column is at 3.3V, 25°C unless otherwise stated. Parameters are for design guidance only and are not tested.

- 3: The  $\Delta$  current is the additional current consumed when the module is enabled. This current should be added to the base IPD current.

- 4: Test conditions for ADC module differential current are as follows: Internal ADC RC oscillator enabled.

- 5: Data is characterized at +70°C and not tested. Parameter is for design guidance only.

- 6: This parameter is characterized, but not tested in manufacturing.

| DC CHA        | RACTER | ISTICS                                                  | Standard Operating Conditions: 2.3V to 3.6V(unless otherwise stated)Operating temperature $-40^{\circ}C \le TA \le +85^{\circ}C$ for Industrial $-40^{\circ}C \le TA \le +105^{\circ}C$ for V-Temp |                        |          |       |                                                   |

|---------------|--------|---------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------|----------|-------|---------------------------------------------------|

| Param.<br>No. | Symbol | Characteristics                                         | Min.                                                                                                                                                                                               | Typical <sup>(1)</sup> | Max.     | Units | Conditions                                        |

|               | VIL    | Input Low Voltage                                       |                                                                                                                                                                                                    |                        |          |       |                                                   |

| DI10          |        | I/O Pins:                                               |                                                                                                                                                                                                    |                        |          |       |                                                   |

|               |        | with TTL Buffer                                         | Vss                                                                                                                                                                                                | —                      | 0.15 Vdd | V     |                                                   |

|               |        | with Schmitt Trigger Buffer                             | Vss                                                                                                                                                                                                | —                      | 0.2 Vdd  | V     |                                                   |

| DI15          |        | MCLR <sup>(2)</sup>                                     | Vss                                                                                                                                                                                                | —                      | 0.2 Vdd  | V     |                                                   |

| DI16          |        | OSC1 (XT mode)                                          | Vss                                                                                                                                                                                                | —                      | 0.2 Vdd  | V     | (Note 4)                                          |

| DI17          |        | OSC1 (HS mode)                                          | Vss                                                                                                                                                                                                | —                      | 0.2 Vdd  | V     | (Note 4)                                          |

| DI18          |        | SDAx, SCLx                                              | Vss                                                                                                                                                                                                | _                      | 0.3 Vdd  | V     | SMBus disabled<br>(Note 4)                        |

| DI19          |        | SDAx, SCLx                                              | Vss                                                                                                                                                                                                | —                      | 0.8      | V     | SMBus enabled<br>(Note 4)                         |

|               | Vih    | Input High Voltage                                      |                                                                                                                                                                                                    |                        |          |       |                                                   |

| DI20          |        | I/O Pins not 5V-tolerant <sup>(5)</sup>                 | 0.65 VDD                                                                                                                                                                                           | —                      | Vdd      | V     | (Note 4,6)                                        |

|               |        | I/O Pins 5V-tolerant with<br>PMP <sup>(5)</sup>         | 0.25 VDD + 0.8V                                                                                                                                                                                    | _                      | 5.5      | V     | (Note 4,6)                                        |

|               |        | I/O Pins 5V-tolerant <sup>(5)</sup>                     | 0.65 Vdd                                                                                                                                                                                           | _                      | 5.5      | V     |                                                   |

| DI28          |        | SDAx, SCLx                                              | 0.65 Vdd                                                                                                                                                                                           | —                      | 5.5      | V     | SMBus disabled (Note 4,6)                         |

| DI29          |        | SDAx, SCLx                                              | 2.1                                                                                                                                                                                                | _                      | 5.5      | V     | SMBus enabled,<br>2.3V ≤ VPIN ≤ 5.5<br>(Note 4,6) |

| DI30          | ICNPU  | Change Notification Pull-up Current                     | —                                                                                                                                                                                                  | —                      | -50      | μA    | VDD = 3.3V, VPIN = VSS<br>(Note 3,6)              |

| DI31          | ICNPD  | Change Notification<br>Pull-down Current <sup>(4)</sup> | —                                                                                                                                                                                                  | 50                     | _        | μA    | VDD = 3.3V, VPIN = VDD                            |

#### TABLE 32-8: DC CHARACTERISTICS: I/O PIN INPUT SPECIFICATIONS

**Note 1:** Data in "Typical" column is at 3.3V, 25°C unless otherwise stated. Parameters are for design guidance only and are not tested.

- 2: The leakage current on the MCLR pin is strongly dependent on the applied voltage level. The specified levels represent normal operating conditions. Higher leakage current may be measured at different input voltages.

- **3:** Negative current is defined as current sourced by the pin.

- 4: This parameter is characterized, but not tested in manufacturing.

- 5: See the "Device Pin Tables" section for the 5V-tolerant pins.

- 6: The VIH specification is only in relation to externally applied inputs and not with respect to the user-selectable pull-ups. Externally applied high impedance or open drain input signals utilizing the PIC32 internal pullups are guaranteed to be recognized as a logic "high" internally to the PIC32 device, provided that the external load does not exceed the maximum value of ICNPU.

- 7: VIL source < (VSS 0.3). Characterized but not tested.

- 8: VIH source > (VDD + 0.3) for non-5V tolerant pins only.

- **9:** Digital 5V tolerant pins do not have an internal high side diode to VDD, and therefore, cannot tolerate any "positive" input injection current.

- 10: Injection currents > | 0 | can affect the ADC results by approximately 4 to 6 counts (i.e., VIH Source > (VDD + 0.3) or VIL source < (VSS 0.3)).</p>

- 11: Any number and/or combination of I/O pins not excluded under IICL or IICH conditions are permitted provided the "absolute instantaneous" sum of the input injection currents from all pins do not exceed the specified limit. If Note 7, IICL = (((Vss 0.3) VIL source) / Rs). If Note 8, IICH = ((IICH source (VDD + 0.3)) / RS). RS = Resistance between input source voltage and device pin. If (Vss 0.3) ≤ VSOURCE ≤ (VDD + 0.3), injection current = 0.

### PIC32MX5XX/6XX/7XX

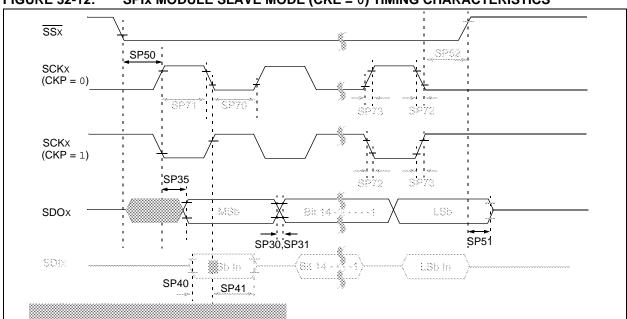

#### FIGURE 32-12: SPIX MODULE SLAVE MODE (CKE = 0) TIMING CHARACTERISTICS

#### TABLE 32-30: SPIX MODULE SLAVE MODE (CKE = 0) TIMING REQUIREMENTS

| АС СНА        | ARACTERIS             | Standard<br>(unless o<br>Operating                                 | therwise  | e stated            | <b>)</b><br>40°C ≤ T | <b>2.3V to 3.6V</b><br>$\overline{A} \le +85^{\circ}C$ for Industrial $\overline{A} \le +105^{\circ}C$ for V-Temp |                    |

|---------------|-----------------------|--------------------------------------------------------------------|-----------|---------------------|----------------------|-------------------------------------------------------------------------------------------------------------------|--------------------|

| Param.<br>No. | Symbol                | Characteristics <sup>(1)</sup>                                     | Min.      | Тур. <sup>(2)</sup> | Max.                 | Units                                                                                                             | Conditions         |

| SP70          | TscL                  | SCKx Input Low Time <sup>(3)</sup>                                 | Tsck/2    | _                   |                      | ns                                                                                                                | —                  |

| SP71          | TscH                  | SCKx Input High Time <sup>(3)</sup>                                | Tsck/2    | _                   |                      | ns                                                                                                                | —                  |

| SP72          | TscF                  | SCKx Input Fall Time                                               | —         | —                   | _                    | ns                                                                                                                | See parameter DO32 |

| SP73          | TscR                  | SCKx Input Rise Time                                               | —         | —                   | _                    | ns                                                                                                                | See parameter DO31 |

| SP30          | TDOF                  | SDOx Data Output Fall Time <sup>(4)</sup>                          | —         | _                   | _                    | ns                                                                                                                | See parameter DO32 |

| SP31          | TdoR                  | SDOx Data Output Rise Time <sup>(4)</sup>                          | —         | _                   | _                    | ns                                                                                                                | See parameter DO31 |

| SP35          | TscH2doV,             | SDOx Data Output Valid after                                       | —         | —                   | 15                   | ns                                                                                                                | VDD > 2.7V         |

|               | TscL2doV              | SCKx Edge                                                          | —         | _                   | 20                   | ns                                                                                                                | VDD < 2.7V         |

| SP40          | TDIV2SCH,<br>TDIV2SCL | Setup Time of SDIx Data Input to SCKx Edge                         | 10        |                     |                      | ns                                                                                                                |                    |

| SP41          | TscH2diL,<br>TscL2diL | Hold Time of SDIx Data Input to SCKx Edge                          | 10        | —                   | _                    | ns                                                                                                                | —                  |

| SP50          | TssL2scH,<br>TssL2scL | $\overline{\text{SSx}}\downarrow$ to SCKx $\uparrow$ or SCKx Input | 175       |                     |                      | ns                                                                                                                | —                  |

| SP51          | TssH2doZ              | SSx ↑ to SDOx Output<br>High-Impedance <sup>(3)</sup>              | 5         | —                   | 25                   | ns                                                                                                                | —                  |

| SP52          | TscH2ssH<br>TscL2ssH  | SSx after SCKx Edge                                                | Тѕск + 20 | _                   |                      | ns                                                                                                                | _                  |

Note 1: These parameters are characterized, but not tested in manufacturing.

2: Data in "Typical" column is at 3.3V, 25°C unless otherwise stated. Parameters are for design guidance only and are not tested.

**3:** The minimum clock period for SCKx is 40 ns.

4: Assumes 50 pF load on all SPIx pins.

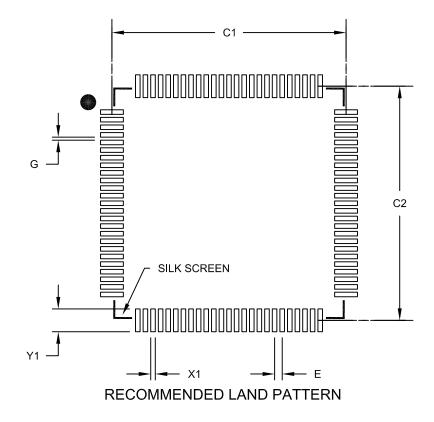

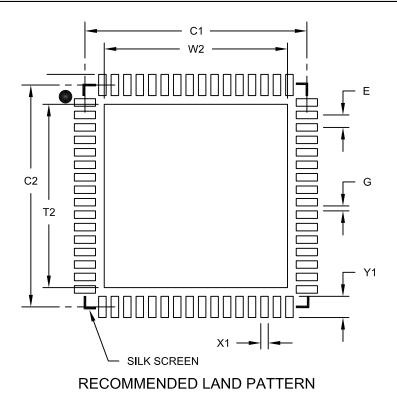

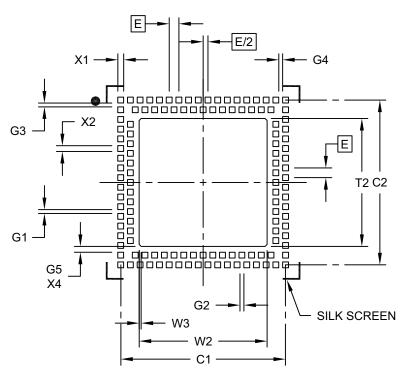

100-Lead Plastic Thin Quad Flatpack (PF) - 14x14x1 mm Body 2.00 mm Footprint [TQFP]

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

|                           | Units    |          |       | S    |

|---------------------------|----------|----------|-------|------|

| Dimensior                 | l Limits | MIN      | NOM   | MAX  |

| Contact Pitch             | E        | 0.50 BSC |       |      |

| Contact Pad Spacing       | C1       |          | 15.40 |      |

| Contact Pad Spacing       | C2       |          | 15.40 |      |

| Contact Pad Width (X100)  | X1       |          |       | 0.30 |