Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFl

| Details                    |                                                                                  |

|----------------------------|----------------------------------------------------------------------------------|

| Product Status             | Active                                                                           |

| Core Processor             | MIPS32® M4K™                                                                     |

| Core Size                  | 32-Bit Single-Core                                                               |

| Speed                      | 80MHz                                                                            |

| Connectivity               | Ethernet, I <sup>2</sup> C, SPI, UART/USART, USB OTG                             |

| Peripherals                | Brown-out Detect/Reset, DMA, POR, PWM, WDT                                       |

| Number of I/O              | 83                                                                               |

| Program Memory Size        | 512KB (512K x 8)                                                                 |

| Program Memory Type        | FLASH                                                                            |

| EEPROM Size                | -                                                                                |

| RAM Size                   | 64K x 8                                                                          |

| Voltage - Supply (Vcc/Vdd) | 2.3V ~ 3.6V                                                                      |

| Data Converters            | A/D 16x10b                                                                       |

| Oscillator Type            | Internal                                                                         |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                                |

| Mounting Type              | Surface Mount                                                                    |

| Package / Case             | 121-TFBGA                                                                        |

| Supplier Device Package    | 121-TFBGA (10x10)                                                                |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic32mx675f512l-80i-bg |

|                            |                                                                                  |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

|                  |                                                                 |                         |                  |     | USB      | , Ethe | ernet, a               | nd CA                                    | N                     |                    |                                 |                              |             |         |      |       |                         |

|------------------|-----------------------------------------------------------------|-------------------------|------------------|-----|----------|--------|------------------------|------------------------------------------|-----------------------|--------------------|---------------------------------|------------------------------|-------------|---------|------|-------|-------------------------|

| Device           | Pins                                                            | Program Memory (KB)     | Data Memory (KB) | USB | Ethernet | CAN    | Timers/Capture/Compare | DMA Channels<br>(Programmable/Dedicated) | UART <sup>(2,3)</sup> | SPI <sup>(3)</sup> | I <sup>2</sup> C <sup>(3)</sup> | 10-bit 1 Msps ADC (Channels) | Comparators | dSd/dMd | JTAG | Trace | Packages <sup>(4)</sup> |

| PIC32MX764F128H  | 64                                                              | 128 + 12 <sup>(1)</sup> | 32               | 1   | 1        | 1      | 5/5/5                  | 4/8                                      | 6                     | 3                  | 4                               | 16                           | 2           | Yes     | Yes  | No    | PT,<br>MR               |

| PIC32MX775F256H  | 64                                                              | 256 + 12 <sup>(1)</sup> | 64               | 1   | 1        | 2      | 5/5/5                  | 8/8                                      | 6                     | 3                  | 4                               | 16                           | 2           | Yes     | Yes  | No    | PT,<br>MR               |

| PIC32MX775F512H  | 64                                                              | 512 + 12 <sup>(1)</sup> | 64               | 1   | 1        | 2      | 5/5/5                  | 8/8                                      | 6                     | 3                  | 4                               | 16                           | 2           | Yes     | Yes  | No    | PT,<br>MR               |

| PIC32MX795F512H  | 64                                                              | 512 + 12 <sup>(1)</sup> | 128              | 1   | 1        | 2      | 5/5/5                  | 8/8                                      | 6                     | 3                  | 4                               | 16                           | 2           | Yes     | Yes  | No    | PT,<br>MR               |

| PIC32MX764F128L  | 100                                                             | 128 + 12 <sup>(1)</sup> | 32               | 1   | 1        | 1      | 5/5/5                  | 4/6                                      | 6                     | 4                  | 5                               | 16                           | 2           | Yes     | Yes  | Yes   | PT, PF,<br>BG           |

| PIC32MX775F256L  | 100                                                             | 256 + 12 <sup>(1)</sup> | 64               | 1   | 1        | 2      | 5/5/5                  | 8/8                                      | 6                     | 4                  | 5                               | 16                           | 2           | Yes     | Yes  | Yes   | PT, PF,<br>BG           |

| PIC32MX775F512L  | 100                                                             | 512 + 12 <sup>(1)</sup> | 64               | 1   | 1        | 2      | 5/5/5                  | 8/8                                      | 6                     | 4                  | 5                               | 16                           | 2           | Yes     | Yes  | Yes   | PT, PF,<br>BG           |

| PIC32MX795F512L  | 100                                                             | 512 + 12 <sup>(1)</sup> | 128              | 1   | 1        | 2      | 5/5/5                  | 8/8                                      | 6                     | 4                  | 5                               | 16                           | 2           | Yes     | Yes  | Yes   | PT, PF,<br>BG, TL       |

| Legend: PF, PT = | end: PF, PT = TQFP MR = QFN BG = TFBGA TL = VTLA <sup>(5)</sup> |                         |                  |     |          |        |                        |                                          |                       |                    |                                 |                              |             |         |      |       |                         |

### TABLE 3: PIC32MX7XX USB, ETHERNET, AND CAN FEATURES

Note 1: This device features 12 KB boot Flash memory.

2: CTS and RTS pins may not be available for all UART modules. Refer to the "Device Pin Tables" section for more information.

3: Some pins between the UART, SPI and I<sup>2</sup>C modules may be shared. Refer to the "Device Pin Tables" section for more information.

4: Refer to Section 34.0 "Packaging Information" for more information.

5: 100-pin devices other than those listed here are available in the VTLA package upon request. Please contact your local Microchip Sales Office for details.

| TABLE 1- | <u>I: PINOU</u>                               | T I/O DES       | CRIPTION            | NS (CONT        | INUED | )                    |                                                   |  |  |

|----------|-----------------------------------------------|-----------------|---------------------|-----------------|-------|----------------------|---------------------------------------------------|--|--|

|          |                                               | Pin Nur         | nber <sup>(1)</sup> |                 | Pin   | Buffer               |                                                   |  |  |

| Pin Name | 64-Pin<br>QFN/TQFP                            | 100-Pin<br>TQFP | 121-Pin<br>TFBGA    | 124-pin<br>VTLA | Туре  | Туре                 | Description                                       |  |  |

| SDI1     | —                                             | 9               | E1                  | B5              | I     | ST                   | SPI1 data in                                      |  |  |

| SDO1     | —                                             | 72              | D9                  | B39             | 0     | _                    | SPI1 data out                                     |  |  |

| SS1      | _                                             | 69              | E10                 | A45             | I/O   | ST                   | SPI1 slave synchronization or frame pulse I/O     |  |  |

| SCK3     | 49                                            | 48              | K9                  | A31             | I/O   | ST                   | Synchronous serial clock input/output<br>for SPI3 |  |  |

| SDI3     | 50                                            | 52              | K11                 | A36             | I     | ST                   | SPI3 data in                                      |  |  |

| SDO3     | 51                                            | 53              | J10                 | B29             | 0     |                      | SPI3 data out                                     |  |  |

| SS3      | 43                                            | 47              | L9                  | B26             | I/O   | ST                   | SPI3 slave synchronization or frame pulse I/O     |  |  |

| SCK2     | 4                                             | 10              | E3                  | A7              | I/O   | ST                   | Synchronous serial clock input/output<br>for SPI2 |  |  |

| SDI2     | 5                                             | 11              | F4                  | B6              | I     | ST                   | SPI2 data in                                      |  |  |

| SDO2     | 6                                             | 12              | F2                  | A8              | 0     |                      | SPI2 data out                                     |  |  |

| SS2      | 8                                             | 14              | F3                  | A9              | I/O   | ST                   | SPI2 slave synchronization or frame pulse I/O     |  |  |

| SCK4     | 29                                            | 39              | L6                  | B22             | I/O   | ST                   | Synchronous serial clock input/ou<br>for SPI4     |  |  |

| SDI4     | 31                                            | 49              | L10                 | B27             | I     | ST                   | SPI4 data in                                      |  |  |

| SDO4     | 32                                            | 50              | L11                 | A32             | 0     |                      | SPI4 data out                                     |  |  |

| SS4      | 21                                            | 40              | K6                  | A27             | I/O   | ST                   | SPI4 slave synchronization or frame pulse I/O     |  |  |

| SCL1     | 44                                            | 66              | E11                 | B36             | I/O   | ST                   | Synchronous serial clock input/output<br>for I2C1 |  |  |

| SDA1     | 43                                            | 67              | E8                  | A44             | I/O   | ST                   | Synchronous serial data input/output for I2C1     |  |  |

| SCL3     | 51                                            | 53              | J10                 | B29             | I/O   | ST                   | Synchronous serial clock input/output<br>for I2C3 |  |  |

| SDA3     | 50                                            | 52              | K11                 | A36             | I/O   | ST                   | Synchronous serial data input/output for I2C3     |  |  |

| SCL2     | _                                             | 58              | H11                 | A39             | I/O   | ST                   | Synchronous serial clock input/output<br>for I2C2 |  |  |

| SDA2     | _                                             | 59              | G10                 | B32             | I/O   | ST                   | Synchronous serial data input/output<br>for I2C2  |  |  |

| SCL4     | 6                                             | 12              | F2                  | A8              | I/O   | ST                   | Synchronous serial clock input/outpu<br>for I2C4  |  |  |

| SDA4     | 5                                             | 11              | F4                  | B6              | I/O   | ST                   | Synchronous serial data input/output<br>for I2C4  |  |  |

| SCL5     | 32                                            | 50              | L11                 | A32             | I/O   | ST                   | Synchronous serial clock input/outpu<br>for I2C5  |  |  |

| SDA5     | 31                                            | 49              | L10                 | B27             | I/O   | ST                   | Synchronous serial data input/output<br>for I2C5  |  |  |

| -        | CMOS = CMO<br>ST = Schmitt 1<br>TTL = TTL inp | Frigger input   |                     |                 |       | nalog = A<br>= Outpu | Analog input P = Power<br>t I = Input             |  |  |

TABLE 1-1: PINOUT I/O DESCRIPTIONS (CONTINUED)

Note 1: Pin numbers are only provided for reference. See the "Device Pin Tables" section for device pin availability.

2: See 25.0 "Ethernet Controller" for more information.

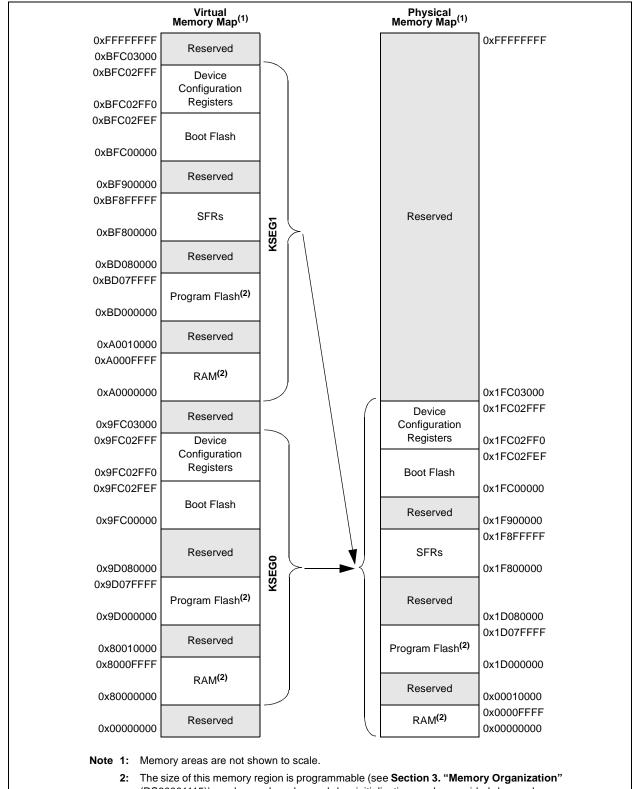

### FIGURE 4-5: MEMORY MAP ON RESET FOR PIC32MX575F512H, PIC32MX575F512L, PIC32MX675F512H, PIC32MX675F512L, PIC32MX775F512H AND PIC32MX775F512L DEVICES

(DS60001115)) and can be changed by initialization code provided by end user development tools (refer to the specific development tool documentation for information).

## 4.2 Control Registers

Register 4-1 through Register 4-8 are used for setting the RAM and Flash memory partitions for data and code.

### TABLE 4-2:BUS MATRIX REGISTER MAP

| ress                        | L                       | e         |       |                     |       |       |       |           |      |      |       | Bits       |      |           |           |           |            |          |               |

|-----------------------------|-------------------------|-----------|-------|---------------------|-------|-------|-------|-----------|------|------|-------|------------|------|-----------|-----------|-----------|------------|----------|---------------|

| Virtual Address<br>(BF88_#) | Register<br>Name        | Bit Range | 31/15 | 30/14               | 29/13 | 28/12 | 27/11 | 26/10     | 25/9 | 24/8 | 23/7  | 22/6       | 21/5 | 20/4      | 19/3      | 18/2      | 17/1       | 16/0     | All<br>Resets |

| 0000                        |                         | 31:16     | —     |                     | —     | —     |       | BMXCHEDMA | —    | _    |       | —          | —    | BMXERRIXI | BMXERRICD | BMXERRDMA | BMXERRDS   | BMXERRIS | 001F          |

| 2000                        | BINIXCON                | 15:0      | —     | -                   | _     | _     |       | _         | _    | _    | _     | BMXWSDRM   | _    | _         | _         | В         | MXARB<2:0> |          | 0041          |

| 2010                        | BMXDKPBA <sup>(1)</sup> | 31:16     | —     | -                   | -     | _     | _     | _         | —    | -    | _     | —          | —    | —         | _         | —         | _          | —        | 0000          |

| 2010                        | DIVINDINF DAV /         | 15:0      |       | BMXDKPBA<15:0> 0000 |       |       |       |           |      |      |       |            |      |           |           |           |            |          |               |

| 2020                        | BMXDUDBA <sup>(1)</sup> | 31:16     | —     | —                   | —     | —     | —     |           | —    | —    | —     | _          | —    | -         | —         | —         | —          | —        | 0000          |

| 2020                        | DWIXDODDI               | 15:0      |       |                     |       |       |       |           |      |      | BMXDL | JDBA<15:0> |      | •         |           |           |            | T        | 0000          |

| 2030                        | BMXDUPBA <sup>(1)</sup> | 31:16     | _     | —                   | —     |       | _     | —         | _    | _    | _     | —          | _    | —         | —         | —         | —          | —        | 0000          |

| 2000                        |                         | 15:0      |       |                     |       |       |       |           |      |      | BMXDL | JPBA<15:0> |      |           |           |           |            |          | 0000          |

| 2040                        | BMXDRMSZ                | 31:16     |       |                     |       |       |       |           |      |      | BMXDF | RMSZ<31:0> |      |           |           |           |            |          | xxxx          |

|                             |                         | 15:0      |       |                     |       |       |       |           |      |      |       |            |      |           |           |           |            |          | xxxx          |

| 2050                        | BMXPUPBA <sup>(1)</sup> | 31:16     | —     | —                   | -     |       | —     | —         | _    |      | —     | _          | —    | —         |           | BMXPUPB   | A<19:16>   |          | 0000          |

|                             |                         | 15:0      |       |                     |       |       |       |           |      |      | BMXPL | JPBA<15:0> |      |           |           |           |            |          | 0000          |

| 2060                        | BMXPFMSZ                | 31:16     |       |                     |       |       |       |           |      |      | BMXPF | MSZ<31:0>  |      |           |           |           |            |          | xxxx          |

|                             |                         | 15:0      |       |                     |       |       |       |           |      |      |       |            |      |           |           |           |            |          | xxxx          |

| 2070                        | BMXBOOTSZ               | 31:16     |       |                     |       |       |       |           |      |      | вмхво | OTSZ<31:0> |      |           |           |           |            |          | 0000          |

|                             |                         | 15:0      |       |                     |       |       |       |           |      |      |       |            |      |           |           |           |            |          | 3000          |

Legend: x = unknown value on Reset; - = unimplemented, read as '0'. Reset values are shown in hexadecimal.

Note 1: This register has corresponding CLR, SET and INV registers at its virtual address, plus an offset of 0x4, 0x8 and 0xC, respectively. See Section 12.1.1 "CLR, SET and INV Registers" for more information.

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|

| 04.04        | U-0               | U-0               | R/W-y             | R/W-y             | R/W-y             | R/W-0             | R/W-0            | R/W-1            |

| 31:24        | —                 | —                 | Р                 | LLODIV<2:0:       | >                 | F                 | RCDIV<2:0>       |                  |

| 00.40        | U-0               | R-0               | R-1               | R/W-y             | R/W-y             | R/W-y             | R/W-y            | R/W-y            |

| 23:16        | —                 | SOSCRDY           | PBDIVRDY          | PBDIV             | /<1:0>            | Р                 | LLMULT<2:0>      | •                |

| 45.0         | U-0               | R-0               | R-0               | R-0               | U-0               | R/W-y             | R/W-y            | R/W-y            |

| 15:8         | —                 |                   | COSC<2:0>         |                   | —                 |                   | NOSC<2:0>        |                  |

| 7.0          | R/W-0             | R-0               | R-0               | R/W-0             | R/W-0             | R/W-0             | R/W-y            | R/W-0            |

| 7:0          | CLKLOCK           | ULOCK             | SLOCK             | SLPEN             | CF                | UFRCEN            | SOSCEN           | OSWEN            |

### REGISTER 8-1: OSCCON: OSCILLATOR CONTROL REGISTER

Legend:

y = Value set from Configuration bits on POR

- R = Readable bit -n = Value at POR

- W = Writable bit U = Unimplemented bit, read as '0'

- '1' = Bit is set

- 0' = Bit is cleared x = Bit is unknown

bit 31-30 Unimplemented: Read as '0'

bit 29-27 PLLODIV<2:0>: Output Divider for PLL

- 111 = PLL output divided by 256

- 110 = PLL output divided by 64

- 101 = PLL output divided by 32

- 100 = PLL output divided by 16

- 011 = PLL output divided by 8

- 010 = PLL output divided by 4

- 001 = PLL output divided by 2

- 000 = PLL output divided by 1

#### bit 26-24 FRCDIV<2:0>: Internal Fast RC (FRC) Oscillator Clock Divider bits

- 111 = FRC divided by 256

- 110 = FRC divided by 64

- 101 = FRC divided by 32

- 100 = FRC divided by 16

- 011 = FRC divided by 8

- 010 = FRC divided by 4

- 001 = FRC divided by 2 (default setting)

- 000 = FRC divided by 1

- bit 23 Unimplemented: Read as '0'

- bit 22 SOSCRDY: Secondary Oscillator (Sosc) Ready Indicator bit

- 1 = Indicates that the Secondary Oscillator is running and is stable

- 0 = Secondary Oscillator is still warming up or is turned off

- bit 21 PBDIVRDY: Peripheral Bus Clock (PBCLK) Divisor Ready bit

- 1 = PBDIV<1:0> bits can be written

- 0 = PBDIV<1:0> bits cannot be written

- bit 20-19 **PBDIV<1:0>:** Peripheral Bus Clock (PBCLK) Divisor bits

- 11 = PBCLK is SYSCLK divided by 8 (default)

- 10 = PBCLK is SYSCLK divided by 4

- 01 = PBCLK is SYSCLK divided by 2

- 00 = PBCLK is SYSCLK divided by 1

**Note:** Writes to this register require an unlock sequence. Refer to **Section 6. "Oscillator"** (DS60001112) in the *"PIC32 Family Reference Manual"* for details.

### REGISTER 10-9: DCHxINT: DMA CHANNEL 'x' INTERRUPT CONTROL REGISTER (CONTINUED)

- bit 5 **CHDDIF:** Channel Destination Done Interrupt Flag bit

- 1 = Channel Destination Pointer has reached end of destination (CHDPTR = CHDSIZ)

- 0 = No interrupt is pending

- bit 4 CHDHIF: Channel Destination Half Full Interrupt Flag bit

- 1 = Channel Destination Pointer has reached midpoint of destination (CHDPTR = CHDSIZ/2)

0 = No interrupt is pending

#### bit 3 CHBCIF: Channel Block Transfer Complete Interrupt Flag bit

- 1 = A block transfer has been completed (the larger of CHSSIZ/CHDSIZ bytes has been transferred), or a pattern match event occurs

- 0 = No interrupt is pending

### bit 2 CHCCIF: Channel Cell Transfer Complete Interrupt Flag bit

- 1 = A cell transfer has been completed (CHCSIZ bytes have been transferred)

- 0 = No interrupt is pending

- bit 1 CHTAIF: Channel Transfer Abort Interrupt Flag bit

- 1 = An interrupt matching CHAIRQ has been detected and the DMA transfer has been aborted

- 0 = No interrupt is pending

### bit 0 CHERIF: Channel Address Error Interrupt Flag bit

- 1 = A channel address error has been detected (either the source or the destination address is invalid)

- 0 = No interrupt is pending

# TABLE 12-9: PORTF REGISTER MAP FOR PIC32MX534F064H, PIC32MX564F064H, PIC32MX564F128H, PIC32MX575F512H, PIC32MX664F064H, PIC32MX664F128H, PIC32MX675F256H, PIC32MX675F512H, PIC32MX695F512H, PIC32MX775F512H, PIC32MX775F512H, PIC32MX775F512H, PIC32MX795F512H, DEVICES

| ess                         |                                 | e         |       |       |       |       |       |       |      | Bi   | its  |      |        |        |        |      |        |        |            |

|-----------------------------|---------------------------------|-----------|-------|-------|-------|-------|-------|-------|------|------|------|------|--------|--------|--------|------|--------|--------|------------|

| Virtual Address<br>(BF88_#) | Register<br>Name <sup>(1)</sup> | Bit Range | 31/15 | 30/14 | 29/13 | 28/12 | 27/11 | 26/10 | 25/9 | 24/8 | 23/7 | 22/6 | 21/5   | 20/4   | 19/3   | 18/2 | 17/1   | 16/0   | All Resets |

| 6140                        | TRISF                           | 31:16     | _     | —     | _     | —     | -     | —     | —    | —    | _    | —    | _      | —      | —      | _    | -      | —      | 0000       |

| 6140                        | IRIOF                           | 15:0      |       | _     | _     | _     | _     | _     | _    | _    | _    | _    | TRISF5 | TRISF4 | TRISF3 | _    | TRISF1 | TRISF0 | 003B       |

| 6150                        | PORTF                           | 31:16     | _     | _     |       | _     |       | _     |      |      |      |      | -      | _      | _      | _    |        |        | 0000       |

| 6150                        | PURIF                           | 15:0      |       | -     | -     | —     | —     | —     | -    | -    | -    | -    | RF5    | RF4    | RF3    |      | RF1    | RF0    | xxxx       |

| 6160                        | LATF                            | 31:16     |       | _     | _     | _     | _     | _     | _    | _    | _    | _    | -      | _      | _      | _    | _      | _      | 0000       |

| 6160                        | LAIF                            | 15:0      | -     | _     | —     | _     | _     | _     | _    | _    | _    | _    | LATF5  | LATF4  | LATF3  | —    | LATF1  | LATF0  | xxxx       |

| 6170                        | ODCF                            | 31:16     |       | _     | _     | _     | _     | _     | _    | _    | _    | _    | -      | _      | _      | _    | _      | _      | 0000       |

| 0170                        | ODCF                            | 15:0      | _     | _     | _     |       | -     |       |      |      |      |      | ODCF5  | ODCF4  | ODCF3  |      | ODCF1  | ODCF0  | 0000       |

Legend: x = unknown value on Reset; - = unimplemented, read as '0'. Reset values are shown in hexadecimal.

Note 1: All registers in this table have corresponding CLR, SET and INV registers at their virtual addresses, plus offsets of 0x4, 0x8 and 0xC, respectively. See Section 12.1.1 "CLR, SET and INV Registers" for more information.

# TABLE 12-10: PORTF REGISTER MAP PIC32MX534F064L, PIC32MX564F064L, PIC32MX564F128L, PIC32MX575F256L, PIC32MX575F512L, PIC32MX664F064L, PIC32MX664F128L, PIC32MX675F256L, PIC32MX675F512L, PIC32MX775F512L, PIC32MX7

| ess                         |                                 | Ċ,        |       |       |         |         |       |       |      | Bi     | ts   |      |        |        |        |        |        |        | - y       |

|-----------------------------|---------------------------------|-----------|-------|-------|---------|---------|-------|-------|------|--------|------|------|--------|--------|--------|--------|--------|--------|-----------|

| Virtual Address<br>(BF88_#) | Register<br>Name <sup>(1)</sup> | Bit Range | 31/15 | 30/14 | 29/13   | 28/12   | 27/11 | 26/10 | 25/9 | 24/8   | 23/7 | 22/6 | 21/5   | 20/4   | 19/3   | 18/2   | 17/1   | 16/0   | All Reset |

|                             | TDIOF                           | 31:16     | _     | _     | _       | _       | _     | _     | _    | _      | _    | _    | _      | _      | _      | _      | _      | _      | 0000      |

| 6140                        | TRISF                           | 15:0      | _     | _     | TRISF13 | TRISF12 | _     | _     | _    | TRISF8 | _    | _    | TRISF5 | TRISF4 | TRISF3 | TRISF2 | TRISF1 | TRISF0 | 313F      |

| 6150                        | PORTF                           | 31:16     | -     | _     | _       | _       | _     | -     | _    | _      | -    |      | -      |        | _      |        | _      | _      | 0000      |

| 0150                        | FUNIF                           | 15:0      | -     | —     | RF13    | RF12    | _     |       | _    | RF8    |      |      | RF5    | RF4    | RF3    | RF2    | RF1    | RF0    | xxxx      |

| 6160                        | LATF                            | 31:16     | —     | —     | _       |         | —     | _     | _    |        | -    | _    | _      | _      | _      | _      | —      | —      | 0000      |

| 0100                        | LAIF                            | 15:0      |       | —     | LATF13  | LATF12  |       | -     |      | LATF8  |      | -    | LATF5  | LATF4  | LATF3  | LATF2  | LATF1  | LATF0  | xxxx      |

| 6170                        | ODCF                            | 31:16     | —     | _     | _       | —       | _     |       | _    |        |      |      | _      |        | —      |        |        |        | 0000      |

| 0170                        | ODCF                            | 15:0      | _     | _     | ODCF13  | ODCF12  | _     | -     | —    | ODCF8  | _    | -    | ODCF5  | ODCF4  | ODCF3  | ODCF2  | ODCF1  | ODCF0  | 0000      |

Legend: x = unknown value on Reset; — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

Note 1: All registers in this table have corresponding CLR, SET and INV registers at their virtual addresses, plus offsets of 0x4, 0x8 and 0xC, respectively. See Section 12.1.1 "CLR, SET and INV Registers" for more information.

# 16.1 Control Registers

| ess                         |                       |               |       |       |       |       |       |       |       | Bi      | ts      |      |      |      |        |      |            |      |              |

|-----------------------------|-----------------------|---------------|-------|-------|-------|-------|-------|-------|-------|---------|---------|------|------|------|--------|------|------------|------|--------------|

| Virtual Address<br>(BF80_#) | Register<br>Name      | Bit Range     | 31/15 | 30/14 | 29/13 | 28/12 | 27/11 | 26/10 | 25/9  | 24/8    | 23/7    | 22/6 | 21/5 | 20/4 | 19/3   | 18/2 | 17/1       | 16/0 | All Resets   |

| 2000                        | IC1CON <sup>(1)</sup> | 31:16         |       | —     | —     | —     | _     | —     | _     | _       | _       | —    | —    | _    | —      | —    | _          | _    | 0000         |

| 2000                        | IC ICON.              | 15:0          | ON    | _     | SIDL  | _     | _     | _     | FEDGE | C32     | ICTMR   | ICI< | 1:0> | ICOV | ICBNE  |      | ICM<2:0>   |      | 0000         |

| 2010                        | IC1BUF                | 31:16         |       |       |       |       |       |       |       | IC1BUF  | ~31.0>  |      |      |      |        |      |            |      | xxxx         |

| 2010                        |                       | 15:0          |       |       |       |       |       |       |       |         |         |      |      |      | xxxx   |      |            |      |              |

| 2200                        | IC2CON <sup>(1)</sup> | 31:16         |       | _     | —     | —     | _     | _     | —     | _       | _       | _    | _    | —    | —      |      | —          | —    | 0000         |

| 2200                        | .0200.1               | 15:0          | ON    | —     | SIDL  | —     | —     | —     | FEDGE | C32     | ICTMR   | ICI< | 1:0> | ICOV | ICBNE  |      | ICM<2:0>   |      | 0000         |

| 2210                        | IC2BUF                | 31:16         |       |       |       |       |       |       |       | IC2BUF  | <31:0>  |      |      |      |        |      |            |      | xxxx         |

|                             |                       | 15:0          |       |       | -     |       |       |       |       |         |         |      |      |      | -      |      |            |      | xxxx         |

| 2400                        | IC3CON <sup>(1)</sup> | 31:16         | -     | _     | —     | _     | _     | —     | _     | _       | -       | -    | —    | —    | —      |      | -          |      | 0000         |

|                             |                       | 15:0          | ON    | —     | SIDL  | —     | —     | —     | FEDGE | C32     | ICTMR   | ICI< | 1:0> | ICOV | ICBNE  |      | ICM<2:0>   |      | 0000         |

| 2410                        | IC3BUF                | 31:16         |       |       |       |       |       |       |       | IC3BUF  | <31:0>  |      |      |      |        |      |            |      | XXXX         |

|                             |                       | 15:0          |       |       | 1     |       |       |       |       |         |         |      |      |      | 1      |      |            |      | XXXX         |

| 2600                        | IC4CON <sup>(1)</sup> | 31:16         | -     |       | -     | _     |       |       | -     | -       | -       | -    |      | -    |        | —    | -          | _    | 0000         |

|                             |                       | 15:0          | ON    | _     | SIDL  | —     | —     | —     | FEDGE | C32     | ICTMR   | ICI< | 1:0> | ICOV | ICBNE  |      | ICM<2:0>   |      | 0000         |

| 2610                        | IC4BUF                | 31:16<br>15:0 |       |       |       |       |       |       |       | IC4BUF  | <31:0>  |      |      |      |        |      |            |      | XXXX         |

|                             |                       | 31:16         |       | _     | _     | _     | _     |       | _     | _       | _       | _    |      |      | _      |      | _          | _    | xxxx<br>0000 |

| 2800                        | IC5CON <sup>(1)</sup> | 15:0          | ON    | _     |       | _     |       |       | FEDGE | <br>C32 | ICTMR   | ICI< |      | ICOV | ICBNE  |      | ICM<2:0>   |      |              |

|                             |                       | 31:16         | UN    |       | SIDL  | —     | _     |       | FEDGE | 632     | ICTIVIK |      | 1.0> | 1000 | ICDINE | l    | 10101<2.0> |      | 0000         |

| 2810                        | IC5BUF                | 15:0          |       |       |       |       |       |       |       | IC5BUF  | <31:0>  |      |      |      |        |      |            |      | XXXX         |

|                             |                       | 15.0          |       |       |       |       |       |       |       |         |         |      |      |      |        |      |            |      | XXXX         |

# TABLE 16-1: INPUT CAPTURE 1-INPUT CAPTURE 5 REGISTER MAP

Legend: x = unknown value on Reset; — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

Note 1: This register has corresponding CLR, SET and INV registers at its virtual address, plus an offset of 0x4, 0x8 and 0xC, respectively. See Section 12.1.1 "CLR, SET and INV Registers" for more information.

### TABLE 20-1: UART1 THROUGH UART6 REGISTER MAP (CONTINUED)

| ess                         |                              |           |        |        |        |               |        |       |       | Bi     | ts     |         |       |          |          |      |        |       |            |

|-----------------------------|------------------------------|-----------|--------|--------|--------|---------------|--------|-------|-------|--------|--------|---------|-------|----------|----------|------|--------|-------|------------|

| Virtual Address<br>(BF80_#) | Register<br>Name             | Bit Range | 31/15  | 30/14  | 29/13  | 28/12         | 27/11  | 26/10 | 25/9  | 24/8   | 23/7   | 22/6    | 21/5  | 20/4     | 19/3     | 18/2 | 17/1   | 16/0  | All Resets |

| 6620                        | U6TXREG                      | 31:16     | _      | _      | —      | —             |        |       | —     | —      |        | —       | _     |          | —        | —    | —      | —     | 0000       |

| 0020                        | UUTAREG                      | 15:0      | _      | _      | _      | —             | _      | _     | _     | TX8    |        |         |       | Transmit | Register | -    |        | -     | 0000       |

| 6630                        | U6RXREG                      | 31:16     | _      | _      | _      | —             | _      | —     | _     |        | _      | —       | _     |          | _        | _    | —      | _     | 0000       |

| 0030                        | UUKAREG                      | 15:0      | _      | _      | —      | —             | —      | —     | _     | RX8    |        |         |       | Receive  | Register |      |        |       | 0000       |

| 6640                        | U6BRG <sup>(1)</sup>         | 31:16     | _      | _      | —      | —             | —      | —     | —     | —      | _      | —       | —     | —        | —        | _    | —      | _     | 0000       |

| 0040                        | OODING                       | 15:0      |        |        | -      |               |        |       |       | BRG<   | 15:0>  |         |       |          | -        | -    |        | -     | 0000       |

| 6800                        | U2MODE <sup>(1)</sup>        | 31:16     | _      | _      | _      | —             | _      | _     | _     | —      | _      | -       | —     | _        | _        | —    | -      | _     | 0000       |

| 0000                        | OZIVIODE                     | 15:0      | ON     | _      | SIDL   | IREN          | RTSMD  | _     | UEN   | <1:0>  | WAKE   | LPBACK  | ABAUD | RXINV    | BRGH     | PDSE | L<1:0> | STSEL | 0000       |

| 6810                        | ) U2STA <sup>(1)</sup> 31:16 | 31:16     | -      | _      |        | _             | —      | —     | _     | ADM_EN |        |         |       | ADDR     | R<7:0>   | -    |        | -     | 0000       |

| 0010                        | 02017                        | 15:0      | UTXISE | L<1:0> | UTXINV | URXEN         | UTXBRK | UTXEN | UTXBF | TRMT   | URXISI | EL<1:0> | ADDEN | RIDLE    | PERR     | FERR | OERR   | URXDA | 0110       |

| 6820                        | U2TXREG                      | 31:16     | _      | _      | _      | —             | _      | _     | _     | —      | _      | -       | —     | _        | —        | —    | -      | —     | 0000       |

| 0020                        | OZTARLO                      | 15:0      | -      | _      |        | _             | _      | —     | _     | TX8    |        |         |       | Transmit | Register | -    |        | -     | 0000       |

| 6830                        | U2RXREG                      | 31:16     | -      | _      |        | —             | _      | —     | _     | —      | _      | -       | —     | _        | _        | _    | -      | -     | 0000       |

| 0000                        | OZIVAREO                     | 15:0      | -      | _      |        | —             | _      | —     | _     | RX8    |        |         |       | Receive  | Register | -    |        | -     | 0000       |

| 6840                        | U2BRG <sup>(1)</sup>         | 31:16     | —      | —      | —      | —             | —      | —     | —     | —      | —      | —       | —     | —        | —        | —    | —      | —     | 0000       |

| 0010                        |                              | 15:0      |        |        |        |               |        |       |       | BRG<   | 15:0>  |         |       |          |          |      |        |       | 0000       |

| 6A00                        | U5MODE <sup>(1)</sup>        | 31:16     | —      | —      | —      | —             | —      | —     | —     | —      | —      | —       | —     | —        | —        | —    | —      | —     | 0000       |

| 0/100                       |                              | 15:0      | ON     | _      | SIDL   | IREN          | _      | —     | _     | —      | WAKE   | LPBACK  | ABAUD | RXINV    | BRGH     | PDSE | L<1:0> | STSEL | 0000       |

| 6A10                        | U5STA <sup>(1)</sup>         | 31:16     | —      | —      | —      | —             | _      | —     | —     | ADM_EN |        |         |       | ADDR     |          | -    |        | -     | 0000       |

| 0,110                       |                              | 15:0      | UTXISE | L<1:0> | UTXINV | URXEN         | UTXBRK | UTXEN | UTXBF | TRMT   | URXISI | EL<1:0> | ADDEN | RIDLE    | PERR     | FERR | OERR   | URXDA | 0110       |

| 6A20                        | U5TXREG                      | 31:16     | -      | _      | _      | _             | _      | _     |       | —      | _      | -       | —     | _        |          |      | -      |       | 0000       |

|                             |                              | 15:0      | —      | _      | _      | _             | _      | _     |       | TX8    |        |         | 1     | Transmit | Register | 1    |        | 1     | 0000       |

| 6A30                        | U5RXREG                      | 31:16     | -      | _      | _      | _             | _      | _     |       | —      | _      | -       | —     | _        |          |      | -      |       | 0000       |

|                             |                              | 15:0      | —      | —      | —      | —             | —      | —     | —     | RX8    |        |         |       | Receive  | Register |      |        |       | 0000       |

| 6A40                        | U5BRG <sup>(1)</sup>         | 31:16     | —      | —      |        | —             | —      | —     | —     | —      | —      | —       | —     | _        |          |      | —      |       | 0000       |

| Legen                       |                              | 15:0      |        |        |        | d, read as '0 |        |       |       | BRG<   | 15:0>  |         |       |          |          |      |        |       | 0000       |

DS60001156J-page 206

This register has corresponding CLR, SET and INV registers at its virtual address, plus an offset of 0x4, 0x8 and 0xC, respectively. See Section 12.1.1 "CLR, SET and INV Registers" for more information. Note 1:

### REGISTER 24-2: CiCFG: CAN BAUD RATE CONFIGURATION REGISTER (CONTINUED)

```

bit 10-8 PRSEG<2:0>: Propagation Time Segment bits<sup>(4)</sup>

111 = \text{Length is 8 x Tq}

000 = \text{Length is } 1 \times TQ

SJW<1:0>: Synchronization Jump Width bits<sup>(3)</sup>

bit 7-6

11 = \text{Length is } 4 \times \text{Tq}

10 = Length is 3 x TQ

01 = Length is 2 x TQ

00 = \text{Length is } 1 \times TQ

BRP<5:0>: Baud Rate Prescaler bits

bit 5-0

111111 = TQ = (2 x 64)/FSYS

111110 = TQ = (2 x 63)/FSYS

000001 = TQ = (2 \times 2)/FSYS

000000 = TQ = (2 \times 1)/FSYS

Note 1: SEG2PH \leq SEG1PH. If SEG2PHTS is clear, SEG2PH will be set automatically.

2: 3 Time bit sampling is not allowed for BRP < 2.

```

- $\textbf{3:} \quad SJW \leq SEG2PH.$

- **4:** The Time Quanta per bit must be greater than 7 (that is, TQBIT > 7).

Note: This register can only be modified when the CAN module is in Configuration mode (OPMOD<2:0> (CiCON<23:21>) = 100).

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|

| 31:24        | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |

| 31.24        | FLTEN7            | MSEL              | 7<1:0>            |                   | F                 | SEL7<4:0>         |                  |                  |

| 22:16        | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |

| 23:16        | FLTEN6            | MSEL              | 6<1:0>            |                   | F                 | SEL6<4:0>         |                  |                  |

| 15:8         | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |

| 10.0         | FLTEN5            | MSEL              | 5<1:0>            |                   | F                 | SEL5<4:0>         |                  |                  |

| 7.0          | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |

| 7:0          | FLTEN4            | MSEL              | 4<1:0>            |                   | F                 | SEL4<4:0>         |                  |                  |

### REGISTER 24-11: CIFLTCON1: CAN FILTER CONTROL REGISTER 1

### Legend:

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, re | ead as '0'         |

|-------------------|------------------|---------------------------|--------------------|

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared      | x = Bit is unknown |

| bit 31    | FLTEN7: Filter 7 Enable bit                                        |

|-----------|--------------------------------------------------------------------|

|           | 1 = Filter is enabled                                              |

|           | 0 = Filter is disabled                                             |

| bit 30-29 | MSEL7<1:0>: Filter 7 Mask Select bits                              |

|           | 11 = Acceptance Mask 3 selected                                    |

|           | 10 = Acceptance Mask 2 selected                                    |

|           | 01 = Acceptance Mask 1 selected<br>00 = Acceptance Mask 0 selected |

| hit 20 24 | FSEL7<4:0>: FIFO Selection bits                                    |

| DIL 20-24 |                                                                    |

|           | 11111 = Message matching filter is stored in FIFO buffer 31        |

|           | 11110 = Message matching filter is stored in FIFO buffer 30        |

|           | •                                                                  |

|           | •                                                                  |

|           | 00001 = Message matching filter is stored in FIFO buffer 1         |

|           | 00000 = Message matching filter is stored in FIFO buffer 0         |

| bit 23    | FLTEN6: Filter 6 Enable bit                                        |

|           | 1 = Filter is enabled                                              |

|           | 0 = Filter is disabled                                             |

| bit 22-21 | MSEL6<1:0>: Filter 6 Mask Select bits                              |

|           | 11 = Acceptance Mask 3 selected                                    |

|           | 10 = Acceptance Mask 2 selected                                    |

|           | 01 = Acceptance Mask 1 selected                                    |

|           | 00 = Acceptance Mask 0 selected                                    |

| bit 20-16 | FSEL6<4:0>: FIFO Selection bits                                    |

|           | 11111 = Message matching filter is stored in FIFO buffer 31        |

|           | 11110 - Massage matching filter is stored in EIEO buffer 20        |

11110 = Message matching filter is stored in FIFO buffer 30

•

00001 = Message matching filter is stored in FIFO buffer 1

00000 = Message matching filter is stored in FIFO buffer 0

Note: The bits in this register can only be modified if the corresponding filter enable (FLTENn) bit is '0'.

•

### REGISTER 24-12: CIFLTCON2: CAN FILTER CONTROL REGISTER 2 (CONTINUED)

| bit 15    | FLTEN9: Filter 9 Enable bit<br>1 = Filter is enabled<br>0 = Filter is disabled                                                                                                    |

|-----------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| bit 14-13 | MSEL9<1:0>: Filter 9 Mask Select bits<br>11 = Acceptance Mask 3 selected<br>10 = Acceptance Mask 2 selected<br>01 = Acceptance Mask 1 selected<br>00 = Acceptance Mask 0 selected |

| bit 12-8  | FSEL9<4:0>: FIFO Selection bits<br>11111 = Message matching filter is stored in FIFO buffer 31<br>11110 = Message matching filter is stored in FIFO buffer 30                     |

|           | 00001 = Message matching filter is stored in FIFO buffer 1<br>00000 = Message matching filter is stored in FIFO buffer 0                                                          |

| bit 7     | FLTEN8: Filter 8 Enable bit<br>1 = Filter is enabled<br>0 = Filter is disabled                                                                                                    |

| bit 6-5   | MSEL8<1:0>: Filter 8 Mask Select bits<br>11 = Acceptance Mask 3 selected<br>10 = Acceptance Mask 2 selected<br>01 = Acceptance Mask 1 selected<br>00 = Acceptance Mask 0 selected |

| bit 4-0   | <pre>FSEL8&lt;4:0&gt;: FIFO Selection bits 11111 = Message matching filter is stored in FIFO buffer 31 11110 = Message matching filter is stored in FIFO buffer 30</pre>          |

Note: The bits in this register can only be modified if the corresponding filter enable (FLTENn) bit is '0'.

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |  |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|--|--|

| 31:24        | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |

| 31.24        | FLTEN23           | MSEL2             | 3<1:0>            |                   | FSEL23<4:0>       |                   |                  |                  |  |  |

| 22:16        | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |

| 23:16        | FLTEN22           | MSEL22<1:0>       |                   | FSEL22<4:0>       |                   |                   |                  |                  |  |  |

| 15:8         | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |

| 10.0         | FLTEN21           | MSEL2             | 21<1:0>           |                   | F                 | SEL21<4:0>        | •                |                  |  |  |

| 7.0          | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |

| 7:0          | FLTEN20           | MSEL20<1:0>       |                   | FSEL20<4:0>       |                   |                   |                  |                  |  |  |

### REGISTER 24-15: CIFLTCON5: CAN FILTER CONTROL REGISTER 5

### Legend:

| R = Readable bit W = Writable bit |                  | U = Unimplemented bit, read as '0' |                    |  |  |  |

|-----------------------------------|------------------|------------------------------------|--------------------|--|--|--|

| -n = Value at POR                 | '1' = Bit is set | '0' = Bit is cleared               | x = Bit is unknown |  |  |  |

| bit ( | 31    | FLTEN23: Filter 23 Enable bit<br>1 = Filter is enabled<br>0 = Filter is disabled                                                                                                                                                                                                           |

|-------|-------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| bit ( | 30-29 | MSEL23<1:0>: Filter 23 Mask Select bits<br>11 = Acceptance Mask 3 selected<br>10 = Acceptance Mask 2 selected<br>01 = Acceptance Mask 1 selected<br>00 = Acceptance Mask 0 selected                                                                                                        |

| bit 2 | 28-24 | <pre>FSEL23&lt;4:0&gt;: FIFO Selection bits 11111 = Message matching filter is stored in FIFO buffer 31 11110 = Message matching filter is stored in FIFO buffer 30 00001 = Message matching filter is stored in FIFO buffer 1</pre>                                                       |

| bit 2 | 23    | 00000 = Message matching filter is stored in FIFO buffer 0<br><b>FLTEN22:</b> Filter 22 Enable bit<br>1 = Filter is enabled<br>0 = Filter is disabled                                                                                                                                      |

| bit 2 | 22-21 | MSEL22<1:0>: Filter 22 Mask Select bits<br>11 = Acceptance Mask 3 selected<br>10 = Acceptance Mask 2 selected<br>01 = Acceptance Mask 1 selected<br>00 = Acceptance Mask 0 selected                                                                                                        |

| bit 2 | 20-16 | FSEL22<4:0>: FIFO Selection bits<br>11111 = Message matching filter is stored in FIFO buffer 31<br>11110 = Message matching filter is stored in FIFO buffer 30<br>00001 = Message matching filter is stored in FIFO buffer 1<br>00000 = Message matching filter is stored in FIFO buffer 0 |

|       | otor  | The hite in this register can only be madified if the correspond                                                                                                                                                                                                                           |

Note: The bits in this register can only be modified if the corresponding filter enable (FLTENn) bit is '0'.

| REGISTER 24-21: CIFIFOINTn: CAN FIFO INTERRUPT REGISTER 'n' (n = 0 THROUGH 31) |            |            |            |            |            |            |           |           |  |  |

|--------------------------------------------------------------------------------|------------|------------|------------|------------|------------|------------|-----------|-----------|--|--|

| Bit                                                                            | Bit        | Bit        | Bit        | Bit        | Bit        | Bit        | Bit       | Bit       |  |  |

| Range                                                                          | 31/23/15/7 | 30/22/14/6 | 29/21/13/5 | 28/20/12/4 | 27/19/11/3 | 26/18/10/2 | 25/17/9/1 | 24/16/8/0 |  |  |

| Range | 31/23/15/7 | 30/22/14/6 | 29/21/13/5 | 28/20/12/4 | 27/19/11/3 | 26/18/10/2               | 25/17/9/1               | 24/16/8/0                 |

|-------|------------|------------|------------|------------|------------|--------------------------|-------------------------|---------------------------|

| 24.24 | U-0        | U-0        | U-0        | U-0        | U-0        | R/W-0                    | R/W-0                   | R/W-0                     |

| 31:24 | —          | _          |            |            |            | TXNFULLIE                | TXHALFIE                | TXEMPTYIE                 |

| 00.40 | U-0        | U-0        | U-0        | U-0        | R/W-0      | R/W-0                    | R/W-0                   | R/W-0                     |

| 23:16 | —          | —          | —          | _          | RXOVFLIE   | RXFULLIE                 | RXHALFIE                | RXNEMPTYIE                |

| 15.0  | U-0        | U-0        | U-0        | U-0        | U-0        | R-0                      | R-0                     | R-0                       |

| 15:8  | —          | —          |            |            | _          | TXNFULLIF <sup>(1)</sup> | TXHALFIF                | TXEMPTYIF <sup>(1)</sup>  |

| 7.0   | U-0        | U-0        | U-0        | U-0        | R/W-0      | R-0                      | R-0                     | R-0                       |

| 7:0   | _          | _          | _          | _          | RXOVFLIF   | RXFULLIF <sup>(1)</sup>  | RXHALFIF <sup>(1)</sup> | RXNEMPTYIF <sup>(1)</sup> |

# Legend:

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read as '0' |                    |  |  |

|-------------------|------------------|------------------------------------|--------------------|--|--|

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared               | x = Bit is unknown |  |  |

### bit 31-27 Unimplemented: Read as '0'

| bit 26    | <b>TXNFULLIE:</b> Transmit FIFO Not Full Interrupt Enable bit<br>1 = Interrupt enabled for FIFO not full<br>0 = Interrupt disabled for FIFO not full   |

|-----------|--------------------------------------------------------------------------------------------------------------------------------------------------------|

| bit 25    | <b>TXHALFIE:</b> Transmit FIFO Half Full Interrupt Enable bit<br>1 = Interrupt enabled for FIFO half full<br>0 = Interrupt disabled for FIFO half full |

| bit 24    | <b>TXEMPTYIE:</b> Transmit FIFO Empty Interrupt Enable bit<br>1 = Interrupt enabled for FIFO empty<br>0 = Interrupt disabled for FIFO empty            |

| bit 23-20 | Unimplemented: Read as '0'                                                                                                                             |

| bit 19    | RXOVFLIE: Overflow Interrupt Enable bit                                                                                                                |

|           | <ul><li>1 = Interrupt enabled for overflow event</li><li>0 = Interrupt disabled for overflow event</li></ul>                                           |

| bit 18    | RXFULLIE: Full Interrupt Enable bit                                                                                                                    |

|           | <ol> <li>1 = Interrupt enabled for FIFO full</li> <li>0 = Interrupt disabled for FIFO full</li> </ol>                                                  |

| bit 17    | RXHALFIE: FIFO Half Full Interrupt Enable bit                                                                                                          |

|           | <ul><li>1 = Interrupt enabled for FIFO half full</li><li>0 = Interrupt disabled for FIFO half full</li></ul>                                           |

| bit 16    | <b>RXNEMPTYIE:</b> Empty Interrupt Enable bit                                                                                                          |

|           | <ul><li>1 = Interrupt enabled for FIFO not empty</li><li>0 = Interrupt disabled for FIFO not empty</li></ul>                                           |

| bit 15-11 | Unimplemented: Read as '0'                                                                                                                             |

| bit 10    | TXNFULLIF: Transmit FIFO Not Full Interrupt Flag bit <sup>(1)</sup>                                                                                    |

|           | <u>TXEN = 1:</u> (FIFO configured as a transmit buffer)<br>1 = FIFO is not full<br>0 = FIFO is full                                                    |

|           | <u>TXEN = 0:</u> (FIFO configured as a receive buffer)<br>Unused, reads '0'                                                                            |

**Note 1:** This bit is read-only and reflects the status of the FIFO.

| Bit Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

|-----------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|

| 31:24     | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 31.24     |                   |                   |                   | —                 |                   | -                 |                  | _                |

| 23:16     | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 23.10     |                   |                   |                   | —                 |                   | -                 |                  | _                |

| 15:8      | U-0               | U-0               | U-0               | U-0               | U-0               | R/W-0             | R/W-0            | R/W-0            |

| 10.0      | _                 | _                 | _                 | —                 | _                 | R                 | XBUFSZ<6:        | 4>               |

| 7:0       | R/W-0             | R/W-0             | R/W-0             | R/W-0             | U-0               | U-0               | U-0              | U-0              |

| 7.0       |                   | RXBUFS            | SZ<3:0>           |                   |                   | _                 |                  |                  |

### REGISTER 25-2: ETHCON2: ETHERNET CONTROLLER CONTROL REGISTER 2

## Legend:

| Logona.           |                            |                      |                                    |  |  |

|-------------------|----------------------------|----------------------|------------------------------------|--|--|

| R = Readable bit  | ble bit W = Writable bit U |                      | U = Unimplemented bit, read as '0' |  |  |

| -n = Value at POR | '1' = Bit is set           | '0' = Bit is cleared | x = Bit is unknown                 |  |  |

### bit 31-11 Unimplemented: Read as '0'

bit 10-4 RXBUFSZ<6:0>: RX Data Buffer Size for All RX Descriptors (in 16-byte increments) bits

111111 = RX data Buffer size for descriptors is 2032 bytes

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

Note 1: This register is only used for RX operations.

2: The bits in this register may only be changed while the RXEN bit (ETHCON1<8>) = 0.

# 28.0 POWER-SAVING FEATURES

Note: This data sheet summarizes the features of the PIC32MX5XX/6XX/7XX family of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to Section 10. "Power-Saving Features" (DS60001130) in the "PIC32 Family Reference Manual", which is available from the Microchip web site (www.microchip.com/PIC32).

This section describes power-saving features for the PIC32MX5XX/6XX/7XX family of devices. These devices offer a total of nine methods and modes, organized into two categories, that allow the user to balance power consumption with device performance. In all of the methods and modes described in this section, power-saving is controlled by software.

### 28.1 Power-Saving with CPU Running

When the CPU is running, power consumption can be controlled by reducing the CPU clock frequency, lowering the Peripheral Bus Clock (PBCLK) and by individually disabling modules. These methods are grouped into the following categories:

- FRC Run mode: the CPU is clocked from the FRC clock source with or without postscalers.

- LPRC Run mode: the CPU is clocked from the LPRC clock source.

- Sosc Run mode: the CPU is clocked from the Sosc clock source.

In addition, the Peripheral Bus Scaling mode is available where peripherals are clocked at the programmable fraction of the CPU clock (SYSCLK).

### 28.2 CPU Halted Methods

The device supports two power-saving modes, Sleep and Idle, both of which Halt the clock to the CPU. These modes operate with all clock sources, as listed below:

- **Posc Idle mode:** the system clock is derived from the Posc. The system clock source continues to operate. Peripherals continue to operate, but can optionally be individually disabled.

- FRC Idle mode: the system clock is derived from the FRC with or without postscalers. Peripherals continue to operate, but can optionally be individually disabled.

- **Sosc Idle mode:** the system clock is derived from the Sosc. Peripherals continue to operate, but can optionally be individually disabled.

- LPRC Idle mode: the system clock is derived from the LPRC. Peripherals continue to operate, but can optionally be individually disabled. This is the lowest power mode for the device with a clock running.

- Sleep mode: the CPU, the system clock source and any peripherals that operate from the system clock source are Halted. Some peripherals can operate in Sleep using specific clock sources. This is the lowest power mode for the device.

# 28.3 Power-Saving Operation

Peripherals and the CPU can be halted or disabled to further reduce power consumption.

### 28.3.1 SLEEP MODE

Sleep mode has the lowest power consumption of the device power-saving operating modes. The CPU and most peripherals are halted. Select peripherals can continue to operate in Sleep mode and can be used to wake the device from Sleep. See the individual peripheral module sections for descriptions of behavior in Sleep.

Sleep mode includes the following characteristics:

- The CPU is halted

- The system clock source is typically shutdown. See Section 28.3.3 "Peripheral Bus Scaling Method" for specific information.

- There can be a wake-up delay based on the oscillator selection

- The Fail-Safe Clock Monitor (FSCM) does not operate during Sleep mode

- The BOR circuit, if enabled, remains operative during Sleep mode

- The WDT, if enabled, is not automatically cleared prior to entering Sleep mode

- Some peripherals can continue to operate at limited functionality in Sleep mode. These peripherals include I/O pins that detect a change in the input signal, WDT, ADC, UART and peripherals that use an external clock input or the internal LPRC oscillator (e.g., RTCC, Timer1 and Input Capture).

- I/O pins continue to sink or source current in the same manner as they do when the device is not in Sleep

- Modules can be individually disabled by software prior to entering Sleep in order to further reduce consumption

| DC CHARACTERISTICS |                                            |                                                         | $\begin{array}{ll} \mbox{Standard Operating Conditions: 2.3V to 3.6V} \\ \mbox{(unless otherwise stated)} \\ \mbox{Operating temperature} & -40^{\circ}C \leq TA \leq +85^{\circ}C \mbox{ for Industrial} \\ & -40^{\circ}C \leq TA \leq +105^{\circ}C \mbox{ for V-Temp} \end{array}$ |            |          |    |                                                   |  |  |

|--------------------|--------------------------------------------|---------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------|----------|----|---------------------------------------------------|--|--|

| Param.<br>No.      | Sympoli Characteristics Mun (Vnical)// Max |                                                         | Units                                                                                                                                                                                                                                                                                  | Conditions |          |    |                                                   |  |  |

|                    | VIL                                        | Input Low Voltage                                       |                                                                                                                                                                                                                                                                                        |            |          |    |                                                   |  |  |

| DI10               |                                            | I/O Pins:                                               |                                                                                                                                                                                                                                                                                        |            |          |    |                                                   |  |  |

|                    |                                            | with TTL Buffer                                         | Vss                                                                                                                                                                                                                                                                                    | —          | 0.15 Vdd | V  |                                                   |  |  |

|                    |                                            | with Schmitt Trigger Buffer                             | Vss                                                                                                                                                                                                                                                                                    | —          | 0.2 Vdd  | V  |                                                   |  |  |

| DI15               |                                            | MCLR <sup>(2)</sup>                                     | Vss                                                                                                                                                                                                                                                                                    | —          | 0.2 Vdd  | V  |                                                   |  |  |

| DI16               |                                            | OSC1 (XT mode)                                          | Vss                                                                                                                                                                                                                                                                                    | —          | 0.2 Vdd  | V  | (Note 4)                                          |  |  |

| DI17               |                                            | OSC1 (HS mode)                                          | Vss                                                                                                                                                                                                                                                                                    | —          | 0.2 Vdd  | V  | (Note 4)                                          |  |  |

| DI18               |                                            | SDAx, SCLx                                              | Vss                                                                                                                                                                                                                                                                                    | _          | 0.3 Vdd  | V  | SMBus disabled<br>(Note 4)                        |  |  |

| DI19               |                                            | SDAx, SCLx                                              | Vss                                                                                                                                                                                                                                                                                    | —          | 0.8      | V  | SMBus enabled<br>(Note 4)                         |  |  |

|                    | Vih                                        | Input High Voltage                                      |                                                                                                                                                                                                                                                                                        |            |          |    |                                                   |  |  |

| DI20               |                                            | I/O Pins not 5V-tolerant <sup>(5)</sup>                 | 0.65 VDD                                                                                                                                                                                                                                                                               | —          | Vdd      | V  | (Note 4,6)                                        |  |  |

|                    |                                            | I/O Pins 5V-tolerant with<br>PMP <sup>(5)</sup>         | 0.25 VDD + 0.8V                                                                                                                                                                                                                                                                        | _          | 5.5      | V  | (Note 4,6)                                        |  |  |