Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XE

| Details                    |                                                                                  |

|----------------------------|----------------------------------------------------------------------------------|

| Product Status             | Active                                                                           |

| Core Processor             | MIPS32® M4K™                                                                     |

| Core Size                  | 32-Bit Single-Core                                                               |

| Speed                      | 80MHz                                                                            |

| Connectivity               | Ethernet, I <sup>2</sup> C, SPI, UART/USART, USB OTG                             |

| Peripherals                | Brown-out Detect/Reset, DMA, POR, PWM, WDT                                       |

| Number of I/O              | 83                                                                               |

| Program Memory Size        | 512KB (512K x 8)                                                                 |

| Program Memory Type        | FLASH                                                                            |

| EEPROM Size                | -                                                                                |

| RAM Size                   | 64K x 8                                                                          |

| Voltage - Supply (Vcc/Vdd) | 2.3V ~ 3.6V                                                                      |

| Data Converters            | A/D 16x10b                                                                       |

| Oscillator Type            | Internal                                                                         |

| Operating Temperature      | -40°C ~ 105°C (TA)                                                               |

| Mounting Type              | Surface Mount                                                                    |

| Package / Case             | 121-TFBGA                                                                        |

| Supplier Device Package    | 121-TFBGA (10x10)                                                                |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic32mx675f512l-80v-bg |

|                            |                                                                                  |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

#### **Referenced Sources**

This device data sheet is based on the following individual chapters of the *"PIC32 Family Reference Manual"*. These documents should be considered as the general reference for the operation of a particular module or device feature.

- Note 1: To access the documents listed below, browse to the documentation section of the PIC32MX795F512L product page on the Microchip web site (www.microchip.com) or select a family reference manual section from the following list. In addition to parameters, features, and other documentation, the resulting page provides links to the related family

- Section 1. "Introduction" (DS60001127)

- Section 2. "CPU" (DS60001113)

- Section 4. "Prefetch Cache" (DS60001119)

- Section 3. "Memory Organization" (DS60001115)

reference manual sections.

- Section 5. "Flash Program Memory" (DS60001121)

- Section 6. "Oscillator Configuration" (DS60001112)

- Section 7. "Resets" (DS60001118)

- Section 8. "Interrupt Controller" (DS60001108)

- Section 9. "Watchdog Timer and Power-up Timer (DS60001114)

- Section 10. "Power-Saving Features" (DS60001130)

- Section 12. "I/O Ports" (DS60001120)

- Section 13. "Parallel Master Port (PMP)" (DS60001128)

- Section 14. "Timers" (DS60001105)

- Section 15. "Input Capture" (DS60001122)

- Section 16. "Output Capture" (DS60001111)

- Section 17. "10-bit Analog-to-Digital Converter (ADC)" (DS60001104)

- Section 19. "Comparator" (DS60001110)

- Section 20. "Comparator Voltage Reference (CVREF)" (DS60001109)

- Section 21. "Universal Asynchronous Receiver Transmitter (UART)" (DS60001107)

- Section 23. "Serial Peripheral Interface (SPI)" (DS60001106)

- Section 24. "Inter-Integrated Circuit (I2C)" (DS60001116)

- Section 27. "USB On-The-Go (OTG)" (DS60001126)

- Section 29. "Real-Time Clock and Calendar (RTCC)" (DS60001125)

- Section 31. "Direct Memory Access (DMA) Controller" (DS60001117)

- Section 32. "Configuration" (DS60001124)

- Section 33. "Programming and Diagnostics" (DS60001129)

- Section 34. "Controller Area Network (CAN)" (DS60001154)

- Section 35. "Ethernet Controller" (DS60001155)

| Pin Name |                      | Pin Nur         | nber <sup>(1)</sup> |                 | D:          | <b>D</b> ((    |                                   |  |

|----------|----------------------|-----------------|---------------------|-----------------|-------------|----------------|-----------------------------------|--|

|          | e 64-Pin<br>QFN/TQFP | 100-Pin<br>TQFP | 121-Pin<br>TFBGA    | 124-pin<br>VTLA | Pin<br>Type | Buffer<br>Type | Description                       |  |

| RA0      | _                    | 17              | G3                  | B9              | I/O         | ST             | PORTA is a bidirectional I/O port |  |

| RA1      | —                    | 38              | J6                  | A26             | I/O         | ST             |                                   |  |

| RA2      | —                    | 58              | H11                 | A39             | I/O         | ST             |                                   |  |

| RA3      | —                    | 59              | G10                 | B32             | I/O         | ST             |                                   |  |

| RA4      | —                    | 60              | G11                 | A40             | I/O         | ST             |                                   |  |

| RA5      | —                    | 61              | G9                  | B33             | I/O         | ST             |                                   |  |

| RA6      | —                    | 91              | C5                  | B51             | I/O         | ST             |                                   |  |

| RA7      | —                    | 92              | B5                  | A62             | I/O         | ST             |                                   |  |

| RA9      | —                    | 28              | L2                  | A21             | I/O         | ST             |                                   |  |

| RA10     |                      | 29              | K3                  | B17             | I/O         | ST             | ]                                 |  |

| RA14     |                      | 66              | E11                 | B36             | I/O         | ST             | ]                                 |  |

| RA15     | —                    | 67              | E8                  | A44             | I/O         | ST             |                                   |  |

| RB0      | 16                   | 25              | K2                  | B14             | I/O         | ST             | PORTB is a bidirectional I/O port |  |

| RB1      | 15                   | 24              | K1                  | A15             | I/O         | ST             |                                   |  |

| RB2      | 14                   | 23              | J2                  | B13             | I/O         | ST             |                                   |  |

| RB3      | 13                   | 22              | J1                  | A13             | I/O         | ST             |                                   |  |

| RB4      | 12                   | 21              | H2                  | B11             | I/O         | ST             |                                   |  |

| RB5      | 11                   | 20              | H1                  | A12             | I/O         | ST             |                                   |  |

| RB6      | 17                   | 26              | L1                  | A20             | I/O         | ST             |                                   |  |

| RB7      | 18                   | 27              | J3                  | B16             | I/O         | ST             |                                   |  |

| RB8      | 21                   | 32              | K4                  | A23             | I/O         | ST             |                                   |  |

| RB9      | 22                   | 33              | L4                  | B19             | I/O         | ST             |                                   |  |

| RB10     | 23                   | 34              | L5                  | A24             | I/O         | ST             | 1                                 |  |

| RB11     | 24                   | 35              | J5                  | B20             | I/O         | ST             | ]                                 |  |

| RB12     | 27                   | 41              | J7                  | B23             | I/O         | ST             | ]                                 |  |

| RB13     | 28                   | 42              | L7                  | A28             | I/O         | ST             | ]                                 |  |

| RB14     | 29                   | 43              | K7                  | B24             | I/O         | ST             |                                   |  |

| RB15     | 30                   | 44              | L8                  | A29             | I/O         | ST             |                                   |  |

| RC1      | —                    | 6               | D1                  | A5              | I/O         | ST             | PORTC is a bidirectional I/O port |  |

| RC2      | —                    | 7               | E4                  | B4              | I/O         | ST             |                                   |  |

| RC3      | —                    | 8               | E2                  | A6              | I/O         | ST             |                                   |  |

| RC4      |                      | 9               | E1                  | B5              | I/O         | ST             | ]                                 |  |

| RC12     | 39                   | 63              | F9                  | B34             | I/O         | ST             | ]                                 |  |

| RC13     | 47                   | 73              | C10                 | A47             | I/O         | ST             | ]                                 |  |

| RC14     | 48                   | 74              | B11                 | B40             | I/O         | ST             | ]                                 |  |

|          | -                    | 64              | F11                 | A42             | I/O         | ST             | 1                                 |  |

TTL = TTL input buffer

Note 1: Pin numbers are only provided for reference. See the "Device Pin Tables" section for device pin availability.

2: See 25.0 "Ethernet Controller" for more information.

#### TABLE 1-1: PINOUT I/O DESCRIPTIONS (CONTINUED)

|          |                                              | nber <sup>(1)</sup> |                  | Pin             | Duffer      |                      |                                                                                                |  |

|----------|----------------------------------------------|---------------------|------------------|-----------------|-------------|----------------------|------------------------------------------------------------------------------------------------|--|

| Pin Name | 64-Pin<br>QFN/TQFP                           | 100-Pin<br>TQFP     | 121-Pin<br>TFBGA | 124-pin<br>VTLA | Ріп<br>Туре | Buffer<br>Type       | Description                                                                                    |  |

| TMS      | 23                                           | 17                  | G3               | B9              | I           | ST                   | JTAG Test mode select pin                                                                      |  |

| ТСК      | 27                                           | 38                  | J6               | A26             | I           | ST                   | JTAG test clock input pin                                                                      |  |

| TDI      | 28                                           | 60                  | G11              | A40             | I           | ST                   | JTAG test data input pin                                                                       |  |

| TDO      | 24                                           | 61                  | G9               | B33             | 0           |                      | JTAG test data output pin                                                                      |  |

| RTCC     | 42                                           | 68                  | E9               | B37             | 0           |                      | Real-Time Clock alarm output                                                                   |  |

| CVREF-   | 15                                           | 28                  | L2               | A21             | I           | Analog               | Comparator Voltage Reference (low)                                                             |  |

| CVREF+   | 16                                           | 29                  | K3               | B17             | I           | Analog               | Comparator Voltage Reference (high)                                                            |  |

| CVREFOUT | 23                                           | 34                  | L5               | A24             | 0           | Analog               | Comparator Voltage Reference output                                                            |  |

| C1IN-    | 12                                           | 21                  | H2               | B11             | I           | Analog               | Comparator 1 negative input                                                                    |  |

| C1IN+    | 11                                           | 20                  | H1               | A12             | I           | Analog               | Comparator 1 positive input                                                                    |  |

| C1OUT    | 21                                           | 32                  | K4               | A23             | 0           |                      | Comparator 1 output                                                                            |  |

| C2IN-    | 14                                           | 23                  | J2               | B13             | I           | Analog               | Comparator 2 negative input                                                                    |  |

| C2IN+    | 13                                           | 22                  | J1               | A13             | I           | Analog               | Comparator 2 positive input                                                                    |  |

| C2OUT    | 22                                           | 33                  | L4               | B19             | 0           |                      | Comparator 2 output                                                                            |  |

| PMA0     | 30                                           | 44                  | L8               | A29             | I/O         | TTL/ST               | Parallel Master Port Address bit 0 inpu<br>(Buffered Slave modes) and output<br>(Master modes) |  |

| PMA1     | 29                                           | 43                  | K7               | B24             | I/O         | TTL/ST               | Parallel Master Port Address bit 1 in<br>(Buffered Slave modes) and output<br>(Master modes)   |  |

| PMA2     | 8                                            | 14                  | F3               | A9              | 0           | _                    | Parallel Master Port address                                                                   |  |

| PMA3     | 6                                            | 12                  | F2               | A8              | 0           |                      | (Demultiplexed Master modes)                                                                   |  |

| PMA4     | 5                                            | 11                  | F4               | B6              | 0           | _                    |                                                                                                |  |

| PMA5     | 4                                            | 10                  | E3               | A7              | 0           | _                    |                                                                                                |  |

| PMA6     | 16                                           | 29                  | K3               | B17             | 0           | —                    |                                                                                                |  |

| PMA7     | 22                                           | 28                  | L2               | A21             | 0           | —                    |                                                                                                |  |

| PMA8     | 32                                           | 50                  | L11              | A32             | 0           | _                    |                                                                                                |  |

| PMA9     | 31                                           | 49                  | L10              | B27             | 0           | _                    |                                                                                                |  |

| PMA10    | 28                                           | 42                  | L7               | A28             | 0           | _                    |                                                                                                |  |

| PMA11    | 27                                           | 41                  | J7               | B23             | 0           |                      |                                                                                                |  |

| PMA12    | 24                                           | 35                  | J5               | B20             | 0           |                      |                                                                                                |  |

| PMA13    | 23                                           | 34                  | L5               | A24             | 0           | _                    | 1                                                                                              |  |

| PMA14    | 45                                           | 71                  | C11              | A46             | 0           | _                    | 1                                                                                              |  |

| PMA15    | 44                                           | 70                  | D11              | B38             | 0           | _                    | 1                                                                                              |  |

| PMCS1    | 45                                           | 71                  | C11              | A46             | 0           |                      | Parallel Master Port Chip Select 1<br>strobe                                                   |  |

| PMCS2    | 44                                           | 70                  | D11              | B38             | 0           | _                    | Parallel Master Port Chip Select 2 strobe                                                      |  |

| 5        | CMOS = CMO<br>ST = Schmitt 1<br>TL = TTL inp | rigger input        |                  |                 |             | nalog = A<br>= Outpu | Analog input P = Power<br>t I = Input                                                          |  |

Note 1: Pin numbers are only provided for reference. See the "Device Pin Tables" section for device pin availability.

2: See 25.0 "Ethernet Controller" for more information.

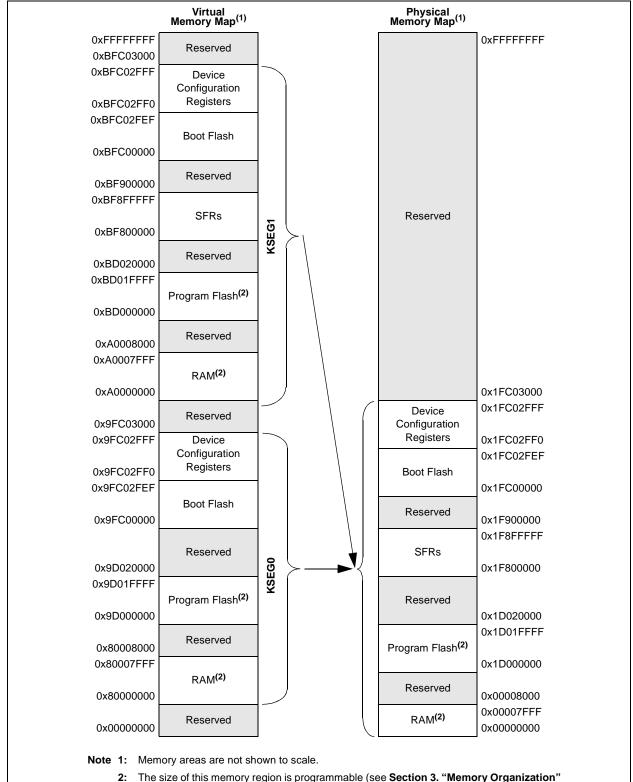

# FIGURE 4-3: MEMORY MAP ON RESET FOR PIC32MX564F128H, PIC32MX564F128L, PIC32MX664F128H, PIC32MX664F128L, PIC32MX764F128H AND PIC32MX764F128L DEVICES

(DS60001115)) and can be changed by initialization code provided by end user development tools (refer to the specific development tool documentation for information).

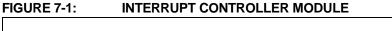

#### 7.0 INTERRUPT CONTROLLER

Note: This data sheet summarizes the features of the PIC32MX5XX/6XX/7XX family of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to **Section 8. "Interrupts"** (DS60001108) in the *"PIC32 Family Reference Manual"*, which is available from the Microchip web site (www.microchip.com/PIC32).

PIC32MX5XX/6XX/7XX devices generate interrupt requests in response to interrupt events from peripheral modules. The interrupt control module exists externally to the CPU logic and prioritizes the interrupt events before presenting them to the CPU.

The Interrupt Controller module includes the following features:

- Up to 96 interrupt sources

- Up to 64 interrupt vectors

- Single and multi-vector mode operations

- · Five external interrupts with edge polarity control

- Interrupt proximity timer

- Seven user-selectable priority levels for each vector

- Four user-selectable sub-priority levels within each priority

- Dedicated shadow set for user-selectable priority level

- Software can generate any interrupt

- User-configurable interrupt vector table location

- · User-configurable interrupt vector spacing

A simplified block diagram of the Interrupt Controller module is illustrated in Figure 7-1.

| Bit<br>Range | Bit<br>31/23/15/7          | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |

|--------------|----------------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|--|

| 31:24        | U-0                        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |  |

| 31.24        | —                          |                   | _                 |                   | _                 | _                 | _                | —                |  |

| 22.16        | R/W-1                      | R/W-1             | R/W-1             | R/W-1             | R/W-1             | R/W-1             | R/W-1            | R/W-1            |  |

| 23:16        | CHAIRQ<7:0> <sup>(1)</sup> |                   |                   |                   |                   |                   |                  |                  |  |

| 15.0         | R/W-1                      | R/W-1             | R/W-1             | R/W-1             | R/W-1             | R/W-1             | R/W-1            | R/W-1            |  |

| 15:8         | CHSIRQ<7:0> <sup>(1)</sup> |                   |                   |                   |                   |                   |                  |                  |  |

| 7:0          | S-0                        | S-0               | R/W-0             | R/W-0             | R/W-0             | U-0               | U-0              | U-0              |  |

| 7.0          | CFORCE                     | CABORT            | PATEN             | SIRQEN            | AIRQEN            | _                 | _                | —                |  |

#### REGISTER 10-8: DCHxECON: DMA CHANNEL 'x' EVENT CONTROL REGISTER

| Legend:           | S = Settable bit |                      |                    |

|-------------------|------------------|----------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented b  | it, read as '0'    |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared | x = Bit is unknown |

#### bit 31-24 Unimplemented: Read as '0'

| bit 23-16 | CHAIRQ<7:0>: Channel Transfer Abort IRQ bits <sup>(1)</sup>                                                                                                                  |

|-----------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|           | 11111111 = Interrupt 255 will abort any transfers in progress and set CHAIF flag                                                                                             |

|           | •                                                                                                                                                                            |

|           | •                                                                                                                                                                            |

|           | •                                                                                                                                                                            |

|           | 00000001 = Interrupt 1 will abort any transfers in progress and set CHAIF flag<br>00000000 = Interrupt 0 will abort any transfers in progress and set CHAIF flag             |

| bit 15-8  | CHSIRQ<7:0>: Channel Transfer Start IRQ bits <sup>(1)</sup>                                                                                                                  |

|           | 11111111 = Interrupt 255 will initiate a DMA transfer                                                                                                                        |

|           | •                                                                                                                                                                            |

|           | •                                                                                                                                                                            |

|           | •                                                                                                                                                                            |

|           | 00000001 = Interrupt 1 will initiate a DMA transfer<br>00000000 = Interrupt 0 will initiate a DMA transfer                                                                   |

| bit 7     | CFORCE: DMA Forced Transfer bit                                                                                                                                              |

|           | <ul> <li>1 = A DMA transfer is forced to begin when this bit is written to a '1'</li> <li>0 = This bit always reads '0'</li> </ul>                                           |

| bit 6     | CABORT: DMA Abort Transfer bit                                                                                                                                               |

|           | <ul> <li>1 = A DMA transfer is aborted when this bit is written to a '1'</li> <li>0 = This bit always reads '0'</li> </ul>                                                   |

| bit 5     | PATEN: Channel Pattern Match Abort Enable bit                                                                                                                                |

|           | <ul><li>1 = Abort transfer and clear CHEN on pattern match</li><li>0 = Pattern match is disabled</li></ul>                                                                   |

| bit 4     | SIRQEN: Channel Start IRQ Enable bit                                                                                                                                         |

|           | <ul> <li>1 = Start channel cell transfer if an interrupt matching CHSIRQ occurs</li> <li>0 = Interrupt number CHSIRQ is ignored and does not start a transfer</li> </ul>     |

| bit 3     | AIRQEN: Channel Abort IRQ Enable bit                                                                                                                                         |

|           | <ul> <li>1 = Channel transfer is aborted if an interrupt matching CHAIRQ occurs</li> <li>0 = Interrupt number CHAIRQ is ignored and does not terminate a transfer</li> </ul> |

| bit 2-0   | Unimplemented: Read as '0'                                                                                                                                                   |

|           |                                                                                                                                                                              |

Note 1: See Table 7-1: "Interrupt IRQ, Vector and Bit Location" for the list of available interrupt IRQ sources.

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|

| 04.04        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 31:24        | —                 | —                 | —                 | _                 | —                 | —                 | _                | _                |

| 00.40        | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |

| 23:16        | CHSDIE            | CHSHIE            | CHDDIE            | CHDHIE            | CHBCIE            | CHCCIE            | CHTAIE           | CHERIE           |

| 45.0         | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 15:8         | —                 | —                 | —                 | _                 | —                 | —                 | _                | _                |

| 7.0          | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |

| 7:0          | CHSDIF            | CHSHIF            | CHDDIF            | CHDHIF            | CHBCIF            | CHCCIF            | CHTAIF           | CHERIF           |

#### REGISTER 10-9: DCHxINT: DMA CHANNEL 'x' INTERRUPT CONTROL REGISTER

#### Legend:

| 0                                 |                  |                                    |                    |  |

|-----------------------------------|------------------|------------------------------------|--------------------|--|

| R = Readable bit W = Writable bit |                  | U = Unimplemented bit, read as '0' |                    |  |

| -n = Value at POR                 | '1' = Bit is set | '0' = Bit is cleared               | x = Bit is unknown |  |

#### bit 31-24 Unimplemented: Read as '0'

| bit 23   | CHSDIE: Channel Source Done Interrupt Enable bit                              |

|----------|-------------------------------------------------------------------------------|

|          | 1 = Interrupt is enabled                                                      |

|          | 0 = Interrupt is disabled                                                     |

| bit 22   | CHSHIE: Channel Source Half Empty Interrupt Enable bit                        |

|          | 1 = Interrupt is enabled                                                      |

|          | 0 = Interrupt is disabled                                                     |

| bit 21   | CHDDIE: Channel Destination Done Interrupt Enable bit                         |

|          | 1 = Interrupt is enabled                                                      |

|          | 0 = Interrupt is disabled                                                     |

| bit 20   | CHDHIE: Channel Destination Half Full Interrupt Enable bit                    |

|          | 1 = Interrupt is enabled                                                      |

|          | 0 = Interrupt is disabled                                                     |

| bit 19   | CHBCIE: Channel Block Transfer Complete Interrupt Enable bit                  |

|          | 1 = Interrupt is enabled                                                      |

|          | 0 = Interrupt is disabled                                                     |

| bit 18   | CHCCIE: Channel Cell Transfer Complete Interrupt Enable bit                   |

|          | 1 = Interrupt is enabled                                                      |

|          | 0 = Interrupt is disabled                                                     |

| bit 17   | CHTAIE: Channel Transfer Abort Interrupt Enable bit                           |

|          | 1 = Interrupt is enabled                                                      |

|          | 0 = Interrupt is disabled                                                     |

| bit 16   | CHERIE: Channel Address Error Interrupt Enable bit                            |

|          | 1 = Interrupt is enabled                                                      |

|          | 0 = Interrupt is disabled                                                     |

| bit 15-8 | Unimplemented: Read as '0'                                                    |

| bit 7    | CHSDIF: Channel Source Done Interrupt Flag bit                                |

|          | 1 = Channel Source Pointer has reached end of source (CHSPTR = CHSSIZ)        |

|          | 0 = No interrupt is pending                                                   |

| bit 6    | CHSHIF: Channel Source Half Empty Interrupt Flag bit                          |

|          | 1 = Channel Source Pointer has reached midpoint of source (CHSPTR = CHSSIZ/2) |

|          | 0 = No interrupt is pending                                                   |

|          |                                                                               |

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|

| 31:24        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 31.24        | _                 | _                 |                   | —                 |                   |                   |                  | —                |

| 00.40        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 23:16        | _                 | _                 |                   | —                 |                   |                   |                  | —                |

| 15:8         | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 10.0         | —                 | _                 | —                 | —                 | —                 | -                 | —                | —                |

| 7.0          | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |

| 7:0          |                   |                   |                   | BDTPTR            | H<23:16>          |                   |                  |                  |

#### REGISTER 11-18: U1BDTP2: USB BUFFER DESCRIPTOR TABLE PAGE 2 REGISTER

#### Legend:

| 0                 |                                 |                      |                    |

|-------------------|---------------------------------|----------------------|--------------------|

| R = Readable bit  | = Readable bit W = Writable bit |                      | ead as '0'         |

| -n = Value at POR | '1' = Bit is set                | '0' = Bit is cleared | x = Bit is unknown |

#### bit 31-8 Unimplemented: Read as '0'

#### bit 7-0 BDTPTRH<23:16>: BDT Base Address bits

This 8-bit value provides address bits 23 through 16 of the BDT base address, which defines the starting location of the BDT in system memory.

The 32-bit BDT base address is 512-byte aligned.

#### REGISTER 11-19: U1BDTP3: USB BUFFER DESCRIPTOR TABLE PAGE 3 REGISTER

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|

| 31:24        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 31.24        |                   | —                 |                   | —                 |                   |                   | —                | —                |

| 22:16        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 23:16        |                   | —                 |                   | —                 |                   |                   | —                | —                |

| 15:8         | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 10.0         |                   | —                 |                   | —                 |                   |                   | —                | —                |

| 7.0          | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |

| 7:0          |                   |                   |                   | BDTPTR            | U<31:24>          |                   |                  |                  |

| Legend:           |                  |                           |                    |

|-------------------|------------------|---------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, re | ead as '0'         |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared      | x = Bit is unknown |

#### bit 31-8 Unimplemented: Read as '0'

#### bit 7-0 BDTPTRU<31:24>: BDT Base Address bits

This 8-bit value provides address bits 31 through 24 of the BDT base address, defines the starting location of the BDT in system memory.

The 32-bit BDT base address is 512-byte aligned.

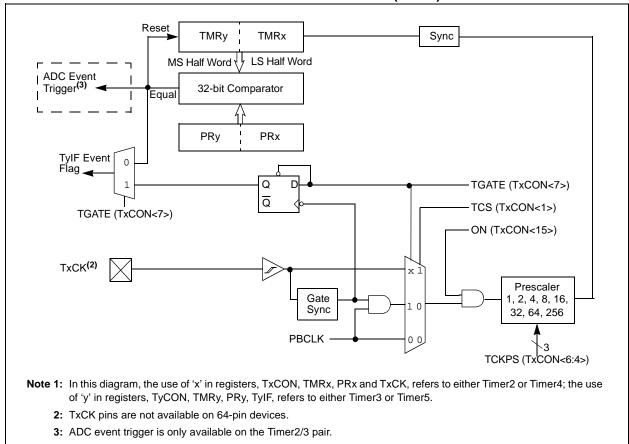

#### FIGURE 14-2: TIMER2/3 AND TIMER4/5 BLOCK DIAGRAM (32-BIT)

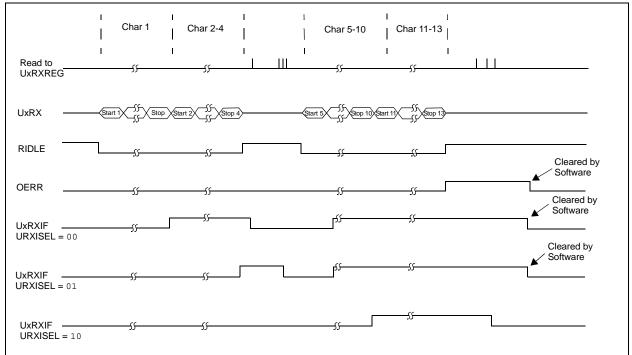

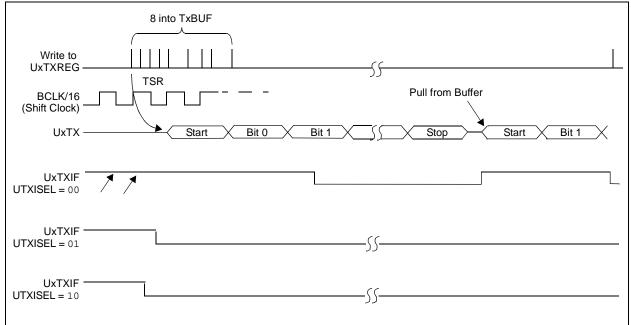

Figure 20-2 and Figure 20-3 illustrate typical receive and transmit timing for the UART module.

#### FIGURE 20-2: UART RECEPTION

#### FIGURE 20-3: TRANSMISSION (8-BIT OR 9-BIT DATA)

#### REGISTER 20-1: UXMODE: UARTX MODE REGISTER (CONTINUED)

- bit 5 **ABAUD:** Auto-Baud Enable bit 1 = Enable baud rate measurement on the next character – requires reception of Sync character (0x55);

- cleared by hardware upon completion 0 = Baud rate measurement disabled or completed

- bit 4 **RXINV:** Receive Polarity Inversion bit

- 1 = UxRX Idle state is '0'

- 0 = UxRX Idle state is '1'

- bit 3 BRGH: High Baud Rate Enable bit

- 1 = High-Speed mode 4x baud clock enabled

- 0 = Standard Speed mode 16x baud clock enabled

- bit 2-1 **PDSEL<1:0>:** Parity and Data Selection bits

- 11 = 9-bit data, no parity

- 10 = 8-bit data, odd parity

- 01 = 8-bit data, even parity

- 00 = 8-bit data, no parity

- bit 0 STSEL: Stop Selection bit

- 1 = 2 Stop bits

- 0 = 1 Stop bit

- **Note 1:** When using the 1:1 PBCLK divisor, the user software should not read/write the peripheral SFRs in the SYSCLK cycle immediately following the instruction that clears the module's ON bit.

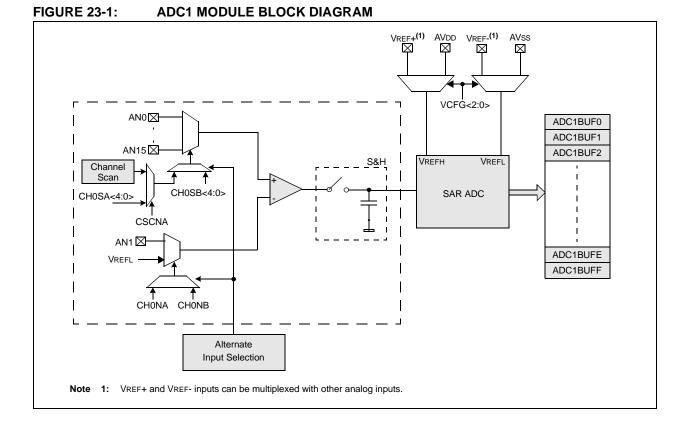

#### 23.0 10-BIT ANALOG-TO-DIGITAL CONVERTER (ADC)

Note: This data sheet summarizes the features of the PIC32MX5XX/6XX/7XX family of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to Section 17. "10-bit Analog-to-Digital Converter (ADC)" (DS60001104) in the "PIC32 Family Reference Manual", which is available from Microchip web the site (www.microchip.com/PIC32).

The PIC32MX5XX/6XX/7XX 10-bit Analog-to-Digital Converter (ADC) includes the following features:

- Successive Approximation Register (SAR) conversion

- Up to 1 Msps conversion speed

- Up to 16 analog input pins

- External voltage reference input pins

- One unipolar, differential Sample and Hold (S&H) circuit

- Automatic Channel Scan mode

- Selectable conversion trigger source

- 16-word conversion result buffer

- · Selectable buffer fill modes

- Eight conversion result format options

- · Operation during Sleep and Idle modes

A block diagram of the 10-bit ADC is illustrated in Figure 23-1. The 10-bit ADC has up to 16 analog input pins, designated AN0-AN15. In addition, there are two analog input pins for external voltage reference connections. These voltage reference inputs may be shared with other analog input pins and may be common to other analog module references.

The analog inputs are connected through two multiplexers to one S&H. The analog input multiplexers can be switched between two sets of analog inputs between conversions. Unipolar differential conversions are possible on all channels, other than the pin used as the reference, using a reference input pin (see Figure 23-1).

The Analog Input Scan mode sequentially converts user-specified channels. A control register specifies which analog input channels will be included in the scanning sequence.

The 10-bit ADC is connected to a 16-word result buffer. Each 10-bit result is converted to one of eight 32-bit output formats when it is read from the result buffer.

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|--|

| 31:24        | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |

| 31.24        | FLTEN27           | MSEL2             | 27<1:0>           |                   |                   | FSEL27<4:0>       |                  |                  |  |

| 22:16        | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |

| 23:16        | FLTEN26           | MSEL2             | 26<1:0>           | FSEL26<4:0>       |                   |                   |                  |                  |  |

| 15.0         | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |

| 15:8         | FLTEN25           | MSEL2             | 25<1:0>           |                   |                   | FSEL25<4:0>       |                  |                  |  |

| 7.0          | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |

| 7:0          | FLTEN24           | MSEL24<1:0>       |                   | FSEL24<4:0>       |                   |                   |                  |                  |  |

#### REGISTER 24-16: CIFLTCON6: CAN FILTER CONTROL REGISTER 6

#### Legend:

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, r | read as '0'        |

|-------------------|------------------|--------------------------|--------------------|

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared     | x = Bit is unknown |

| bit 31    | <b>FLTEN27:</b> Filter 27 Enable bit<br>1 = Filter is enabled<br>0 = Filter is disabled                                                                                             |

|-----------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| bit 30-29 | MSEL27<1:0>: Filter 27 Mask Select bits<br>11 = Acceptance Mask 3 selected<br>10 = Acceptance Mask 2 selected<br>01 = Acceptance Mask 1 selected<br>00 = Acceptance Mask 0 selected |

| bit 28-24 | FSEL27<4:0>: FIFO Selection bits<br>11111 = Message matching filter is stored in FIFO buffer 31<br>11110 = Message matching filter is stored in FIFO buffer 30                      |

|           | 00001 = Message matching filter is stored in FIFO buffer 1<br>00000 = Message matching filter is stored in FIFO buffer 0                                                            |

| bit 23    | FLTEN26: Filter 26 Enable bit<br>1 = Filter is enabled<br>0 = Filter is disabled                                                                                                    |

| bit 22-21 | MSEL26<1:0>: Filter 26 Mask Select bits<br>11 = Acceptance Mask 3 selected<br>10 = Acceptance Mask 2 selected<br>01 = Acceptance Mask 1 selected<br>00 = Acceptance Mask 0 selected |

| bit 20-16 | <pre>FSEL26&lt;4:0&gt;: FIFO Selection bits 11111 = Message matching filter is stored in FIFO buffer 31 11110 = Message matching filter is stored in FIFO buffer 30</pre>           |

|           |                                                                                                                                                                                     |

Note: The bits in this register can only be modified if the corresponding filter enable (FLTENn) bit is '0'.

#### **REGISTER 24-21:** CiFIFOINTn: CAN FIFO INTERRUPT REGISTER 'n' (n = 0 THROUGH 31)

- bit 9 TXHALFIF: FIFO Transmit FIFO Half Empty Interrupt Flag bit<sup>(1)</sup> TXEN = 1: (FIFO configured as a transmit buffer) 1 = FIFO is  $\leq$  half full 0 = FIFO is > half full TXEN = 0: (FIFO configured as a receive buffer) Unused, reads '0' bit 8 **TXEMPTYIF:** Transmit FIFO Empty Interrupt Flag bit<sup>(1)</sup> TXEN = 1: (FIFO configured as a transmit buffer) 1 = FIFO is empty 0 = FIFO is not empty, at least 1 message queued to be transmitted TXEN = 0: (FIFO configured as a receive buffer) Unused, reads '0' bit 7-4 Unimplemented: Read as '0' bit 3 **RXOVFLIF:** Receive FIFO Overflow Interrupt Flag bit TXEN = 1: (FIFO configured as a transmit buffer) Unused, reads '0' TXEN = 0: (FIFO configured as a receive buffer) 1 = Overflow event has occurred 0 = No overflow event occured bit 2 **RXFULLIF:** Receive FIFO Full Interrupt Flag bit<sup>(1)</sup> TXEN = 1: (FIFO configured as a transmit buffer) Unused, reads '0' TXEN = 0: (FIFO configured as a receive buffer) 1 = FIFO is full 0 = FIFO is not full RXHALFIF: Receive FIFO Half Full Interrupt Flag bit<sup>(1)</sup> bit 1 TXEN = 1: (FIFO configured as a transmit buffer) Unused, reads '0' TXEN = 0: (FIFO configured as a receive buffer) 1 = FIFO is  $\geq$  half full 0 = FIFO is < half full bit 0 **RXNEMPTYIF:** Receive Buffer Not Empty Interrupt Flag bit<sup>(1)</sup> TXEN = 1: (FIFO configured as a transmit buffer) Unused, reads '0' TXEN = 0: (FIFO configured as a receive buffer) 1 = FIFO is not empty, has at least 1 message 0 = FIFO is empty

- Note 1: This bit is read-only and reflects the status of the FIFO.

#### 27.1 Control Register

#### TABLE 27-1: COMPARATOR VOLTAGE REFERENCE REGISTER MAP

| lress<br>¢)              |                                 | e         |       |       |       |       |       |                        |       | Bits                 |      |       |      |       |      |      |      |      |           |

|--------------------------|---------------------------------|-----------|-------|-------|-------|-------|-------|------------------------|-------|----------------------|------|-------|------|-------|------|------|------|------|-----------|

| Virtual Addr<br>(BF80_#) | Register<br>Name <sup>(1)</sup> | Bit Range | 31/15 | 30/14 | 29/13 | 28/12 | 27/11 | 26/10                  | 25/9  | 24/8                 | 23/7 | 22/6  | 21/5 | 20/4  | 19/3 | 18/2 | 17/1 | 16/0 | All Reset |

| 0000                     | CVRCON                          | 31:16     |       |       | —     | —     | —     | -                      | —     | _                    | _    | _     |      | _     |      | —    |      | —    | 0000      |

| 9800                     | CVRCON                          | 15:0      | ON    | -     | _     | —     | _     | VREFSEL <sup>(2)</sup> | BGSEL | <1:0> <sup>(2)</sup> | _    | CVROE | CVRR | CVRSS |      | CVR< | 3:0> |      | 0100      |

Legend: x = unknown value on Reset; — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

Note 1: All registers in this table have corresponding CLR, SET and INV registers at their virtual addresses, plus offsets of 0x4, 0x8 and 0xC, respectively. See Section 12.1.1 "CLR, SET and INV Registers" for more information.

2: These bits are not available on PIC32MX575/675/695/775/795 devices. On these devices, reset value for CVRCON is '0000'.

| DC CHARACT       | ERISTICS                     |            | Standard Operating Conditions: 2.3V to 3.6V(unless otherwise stated)Operating temperature $-40^{\circ}C \le TA \le +85^{\circ}C$ for Industrial $-40^{\circ}C \le TA \le +105^{\circ}C$ for V-Temp |                     |            |               |  |  |  |

|------------------|------------------------------|------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------|------------|---------------|--|--|--|

| Parameter<br>No. | Typical <sup>(2)</sup>       | Max.       | Units                                                                                                                                                                                              |                     | Conditions |               |  |  |  |

| Idle Current (I  | IDLE) <sup>(1,3)</sup> for P | PIC32MX575 | /675/695/775                                                                                                                                                                                       | 795 Family Devices  |            |               |  |  |  |

| DC30             | 4.5                          | 6.5        | mA                                                                                                                                                                                                 | -40°C, +25°C, +85°C |            | 4 MHz         |  |  |  |

| DC30b            | 5                            | 7          | mA                                                                                                                                                                                                 | +105°C              | —          | 4 MHZ         |  |  |  |

| DC31             | 13                           | 15         | mA                                                                                                                                                                                                 | -40°C, +25°C, +85°C | —          | 25 MHz        |  |  |  |

| DC32             | 28                           | 30         | mA                                                                                                                                                                                                 | -40°C, +25°C, +85°C | —          | 60 MHz        |  |  |  |

| DC33             | 36                           | 42         | mA                                                                                                                                                                                                 | -40°C, +25°C, +85°C |            | 80 MHz        |  |  |  |

| DC33b            | 39                           | 45         | mA                                                                                                                                                                                                 | +105°C              | —          |               |  |  |  |

| DC34             |                              | 40         |                                                                                                                                                                                                    | -40°C               |            |               |  |  |  |

| DC34a            |                              | 75         |                                                                                                                                                                                                    | +25°C               | 2.3V       |               |  |  |  |

| DC34b            |                              | 800        | μA                                                                                                                                                                                                 | +85°C               | 2.3V       |               |  |  |  |

| DC34c            |                              | 1000       |                                                                                                                                                                                                    | +105°C              |            |               |  |  |  |

| DC35             | 35                           |            |                                                                                                                                                                                                    | -40°C               |            |               |  |  |  |

| DC35a            | 65                           |            |                                                                                                                                                                                                    | +25°C               | 3.3V       |               |  |  |  |

| DC35b            | 600                          | _          | μΑ                                                                                                                                                                                                 | +85°C               | 3.3V       | LPRC (31 kHz) |  |  |  |

| DC35c            | 800                          |            |                                                                                                                                                                                                    | +105°C              |            |               |  |  |  |

| DC36             |                              | 43         |                                                                                                                                                                                                    | -40°C               |            |               |  |  |  |

| DC36a            |                              | 106        |                                                                                                                                                                                                    | +25°C               | 3.6V       |               |  |  |  |

| DC36b            |                              | 800        | μA                                                                                                                                                                                                 | +85°C               | 3.0V       |               |  |  |  |

| DC36c            |                              | 1000       |                                                                                                                                                                                                    | +105°C              |            |               |  |  |  |

#### TABLE 32-6: DC CHARACTERISTICS: IDLE CURRENT (IIDLE)

Note 1: The test conditions for IIDLE current measurements are as follows:

- Oscillator mode is EC (for 8 MHz and below) and EC+PLL (for above 8 MHz) with OSC1 driven by external square wave from rail-to-rail, (OSC1 input clock input over/undershoot < 100 mV required)</li>

- OSC2/CLKO is configured as an I/O input pin

- USB PLL oscillator is disabled if the USB module is implemented, PBCLK divisor = 1:8

- CPU is in Idle mode, program Flash memory Wait states = 111, Program Cache and Prefetch are disabled and SRAM data memory Wait states = 1

- No peripheral modules are operating, (ON bit = 0)

- WDT, Clock Switching, Fail-Safe Clock Monitor, and Secondary Oscillator are disabled

- All I/O pins are configured as inputs and pulled to Vss

- MCLR = VDD

- RTCC and JTAG are disabled

- 2: Data in "Typical" column is at 3.3V, 25°C unless otherwise stated. Parameters are for design guidance only and are not tested.

- 3: This parameter is characterized, but not tested in manufacturing.

- **4:** All parameters are characterized, but only those parameters listed for 4 MHz and 80 MHz are tested at 3.3V in manufacturing.

#### 32.2 AC Characteristics and Timing Parameters

The information contained in this section defines PIC32MX5XX/6XX/7XX AC characteristics and timing parameters.

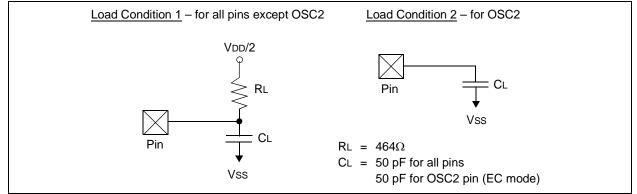

#### FIGURE 32-1: LOAD CONDITIONS FOR DEVICE TIMING SPECIFICATIONS

#### TABLE 32-16: CAPACITIVE LOADING REQUIREMENTS ON OUTPUT PINS

| AC CHARACTERISTICS |        |                       |      | $\begin{array}{llllllllllllllllllllllllllllllllllll$ |     |    |                                                                         |  |  |  |  |

|--------------------|--------|-----------------------|------|------------------------------------------------------|-----|----|-------------------------------------------------------------------------|--|--|--|--|

| Param.<br>No.      | Symbol | Characteristics       | Min. | Min. Typical <sup>(1)</sup> Max. Units Conditions    |     |    |                                                                         |  |  |  |  |

| DO50               | Cosco  | OSC2 pin              |      | _                                                    | 15  | pF | In XT and HS modes when an<br>external crystal is used to drive<br>OSC1 |  |  |  |  |

| DO56               | Сю     | All I/O pins and OSC2 |      | —                                                    | 50  | pF | oF In EC mode                                                           |  |  |  |  |

| DO58 CB SCLx, SDAx |        |                       |      | —                                                    | 400 | pF | In I <sup>2</sup> C mode                                                |  |  |  |  |

Note 1: Data in "Typical" column is at 3.3V, 25°C unless otherwise stated. Parameters are for design guidance only and are not tested.

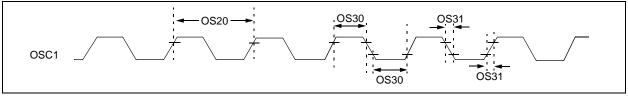

#### FIGURE 32-2: EXTERNAL CLOCK TIMING

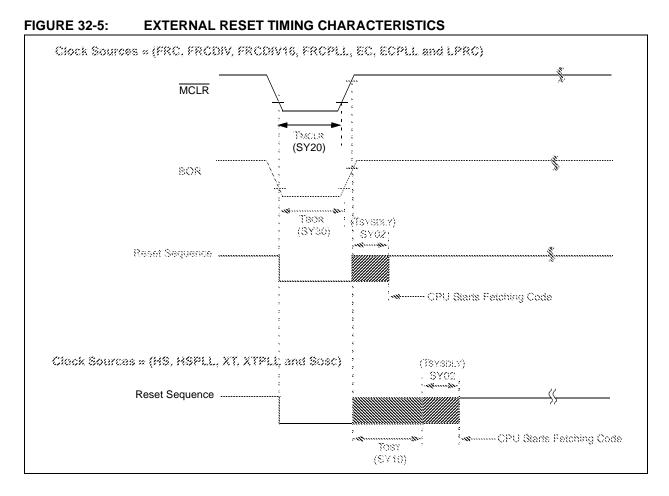

#### TABLE 32-22: RESETS TIMING

| AC CHARACTERISTICS |         |                                                                                                                                            |      | $\begin{tabular}{lllllllllllllllllllllllllllllllllll$ |      |       |                |  |  |  |  |

|--------------------|---------|--------------------------------------------------------------------------------------------------------------------------------------------|------|-------------------------------------------------------|------|-------|----------------|--|--|--|--|

| Param.<br>No.      | Symbol  | Characteristics <sup>(1)</sup>                                                                                                             | Min. | Typical <sup>(2)</sup>                                | Max. | Units | Conditions     |  |  |  |  |

| SY00               | Τρυ     | Power-up Period<br>Internal Voltage Regulator Enabled                                                                                      | _    | 400                                                   | 600  | μS    | -40°C to +85°C |  |  |  |  |

| SY02               | TSYSDLY | System Delay Period:<br>Time Required to Reload Device<br>Configuration Fuses plus SYSCLK<br>Delay before First instruction is<br>Fetched. |      | 1 μs +<br>8 SYSCLK<br>cycles                          | _    | _     | -40°C to +85°C |  |  |  |  |

| SY20               | TMCLR   | MCLR Pulse Width (low)                                                                                                                     | —    | 2                                                     | _    | μS    | -40°C to +85°C |  |  |  |  |

| SY30               | TBOR    | BOR Pulse Width (low)                                                                                                                      | —    | 1                                                     |      | μS    | -40°C to +85°C |  |  |  |  |

**Note 1:** These parameters are characterized, but not tested in manufacturing.

2: Data in "Typ" column is at 3.3V, 25°C unless otherwise stated. Characterized by design but not tested.

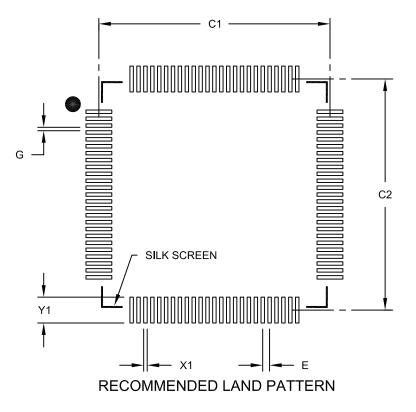

100-Lead Plastic Thin Quad Flatpack (PT)-12x12x1mm Body, 2.00 mm Footprint [TQFP]

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

|                           | Units    |      |          |      |  |  |

|---------------------------|----------|------|----------|------|--|--|

| Dimensior                 | n Limits | MIN  | NOM      | MAX  |  |  |

| Contact Pitch             | E        |      | 0.40 BSC |      |  |  |

| Contact Pad Spacing       | C1       |      | 13.40    |      |  |  |

| Contact Pad Spacing       | C2       |      | 13.40    |      |  |  |

| Contact Pad Width (X100)  | X1       |      |          | 0.20 |  |  |

| Contact Pad Length (X100) | Y1       |      |          | 1.50 |  |  |

| Distance Between Pads     | G        | 0.20 |          |      |  |  |

Notes:

1. Dimensioning and tolerancing per ASME Y14.5M

BSC: Basic Dimension. Theoretically exact value shown without tolerances.

Microchip Technology Drawing No. C04-2100B

### **Worldwide Sales and Service**

#### AMERICAS

Corporate Office 2355 West Chandler Blvd. Chandler, AZ 85224-6199 Tel: 480-792-7200 Fax: 480-792-7277 Technical Support: http://www.microchip.com/ support Web Address: www.microchip.com

Atlanta Duluth, GA Tel: 678-957-9614 Fax: 678-957-1455

Austin, TX Tel: 512-257-3370

**Boston** Westborough, MA Tel: 774-760-0087 Fax: 774-760-0088

**Chicago** Itasca, IL Tel: 630-285-0071 Fax: 630-285-0075

**Cleveland** Independence, OH Tel: 216-447-0464 Fax: 216-447-0643

**Dallas** Addison, TX Tel: 972-818-7423 Fax: 972-818-2924

Detroit Novi, MI Tel: 248-848-4000

Houston, TX Tel: 281-894-5983

Indianapolis Noblesville, IN Tel: 317-773-8323 Fax: 317-773-5453

Los Angeles Mission Viejo, CA Tel: 949-462-9523 Fax: 949-462-9608

New York, NY Tel: 631-435-6000

San Jose, CA Tel: 408-735-9110

**Canada - Toronto** Tel: 905-695-1980 Fax: 905-695-2078

#### ASIA/PACIFIC

Asia Pacific Office Suites 3707-14, 37th Floor Tower 6, The Gateway Harbour City, Kowloon

Hong Kong Tel: 852-2943-5100 Fax: 852-2401-3431

Australia - Sydney Tel: 61-2-9868-6733 Fax: 61-2-9868-6755

**China - Beijing** Tel: 86-10-8569-7000 Fax: 86-10-8528-2104

China - Chengdu Tel: 86-28-8665-5511 Fax: 86-28-8665-7889

China - Chongqing Tel: 86-23-8980-9588 Fax: 86-23-8980-9500

China - Dongguan Tel: 86-769-8702-9880

**China - Guangzhou** Tel: 86-20-8755-8029

China - Hangzhou Tel: 86-571-8792-8115 Fax: 86-571-8792-8116

**China - Hong Kong SAR** Tel: 852-2943-5100

**China - Nanjing** Tel: 86-25-8473-2460 Fax: 86-25-8473-2470

Fax: 852-2401-3431

**China - Qingdao** Tel: 86-532-8502-7355 Fax: 86-532-8502-7205

**China - Shanghai** Tel: 86-21-5407-5533 Fax: 86-21-5407-5066

China - Shenyang Tel: 86-24-2334-2829 Fax: 86-24-2334-2393

**China - Shenzhen** Tel: 86-755-8864-2200 Fax: 86-755-8203-1760

**China - Wuhan** Tel: 86-27-5980-5300 Fax: 86-27-5980-5118

**China - Xian** Tel: 86-29-8833-7252 Fax: 86-29-8833-7256

#### ASIA/PACIFIC

**China - Xiamen** Tel: 86-592-2388138 Fax: 86-592-2388130

**China - Zhuhai** Tel: 86-756-3210040 Fax: 86-756-3210049

India - Bangalore Tel: 91-80-3090-4444 Fax: 91-80-3090-4123

India - New Delhi Tel: 91-11-4160-8631 Fax: 91-11-4160-8632

India - Pune Tel: 91-20-3019-1500

**Japan - Osaka** Tel: 81-6-6152-7160 Fax: 81-6-6152-9310

**Japan - Tokyo** Tel: 81-3-6880- 3770 Fax: 81-3-6880-3771

**Korea - Daegu** Tel: 82-53-744-4301 Fax: 82-53-744-4302

Korea - Seoul Tel: 82-2-554-7200 Fax: 82-2-558-5932 or 82-2-558-5934

Malaysia - Kuala Lumpur Tel: 60-3-6201-9857 Fax: 60-3-6201-9859

Malaysia - Penang Tel: 60-4-227-8870 Fax: 60-4-227-4068

Philippines - Manila Tel: 63-2-634-9065 Fax: 63-2-634-9069

**Singapore** Tel: 65-6334-8870 Fax: 65-6334-8850

**Taiwan - Hsin Chu** Tel: 886-3-5778-366 Fax: 886-3-5770-955

**Taiwan - Kaohsiung** Tel: 886-7-213-7828

Taiwan - Taipei Tel: 886-2-2508-8600 Fax: 886-2-2508-0102

**Thailand - Bangkok** Tel: 66-2-694-1351 Fax: 66-2-694-1350

#### EUROPE

Austria - Wels Tel: 43-7242-2244-39 Fax: 43-7242-2244-393

**Denmark - Copenhagen** Tel: 45-4450-2828 Fax: 45-4485-2829

France - Paris Tel: 33-1-69-53-63-20 Fax: 33-1-69-30-90-79

Germany - Dusseldorf Tel: 49-2129-3766400

Germany - Karlsruhe Tel: 49-721-625370

**Germany - Munich** Tel: 49-89-627-144-0 Fax: 49-89-627-144-44

**Italy - Milan** Tel: 39-0331-742611 Fax: 39-0331-466781

Italy - Venice Tel: 39-049-7625286

**Netherlands - Drunen** Tel: 31-416-690399 Fax: 31-416-690340

**Poland - Warsaw** Tel: 48-22-3325737

**Spain - Madrid** Tel: 34-91-708-08-90 Fax: 34-91-708-08-91

Sweden - Stockholm Tel: 46-8-5090-4654

**UK - Wokingham** Tel: 44-118-921-5800 Fax: 44-118-921-5820