Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFI

| Product Status             | Active                                                                           |

|----------------------------|----------------------------------------------------------------------------------|

| Core Processor             | MIPS32® M4K™                                                                     |

| Core Size                  | 32-Bit Single-Core                                                               |

| Speed                      | 80MHz                                                                            |

| Connectivity               | Ethernet, I <sup>2</sup> C, SPI, UART/USART, USB OTG                             |

| Peripherals                | Brown-out Detect/Reset, DMA, POR, PWM, WDT                                       |

| Number of I/O              | 85                                                                               |

| Program Memory Size        | 512KB (512K x 8)                                                                 |

| Program Memory Type        | FLASH                                                                            |

| EEPROM Size                |                                                                                  |

| RAM Size                   | 64K x 8                                                                          |

| Voltage - Supply (Vcc/Vdd) | 2.3V ~ 3.6V                                                                      |

| Data Converters            | A/D 16x10b                                                                       |

| Oscillator Type            | Internal                                                                         |

| Operating Temperature      | -40°C ~ 105°C (TA)                                                               |

| Mounting Type              | Surface Mount                                                                    |

| Package / Case             | 100-TQFP                                                                         |

| Supplier Device Package    | 100-TQFP (12x12)                                                                 |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic32mx675f512l-80v-pt |

|                            |                                                                                  |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# TABLE 11: PIN NAMES FOR USB AND ETHERNET DEVICES (CONTINUED)

| 1     | 21-PIN TFBGA (BOTTOM VIEW                                                                   | /)         | L11                                         |    |

|-------|---------------------------------------------------------------------------------------------|------------|---------------------------------------------|----|

|       | PIC32MX664F064L<br>PIC32MX664F128L<br>PIC32MX675F256L<br>PIC32MX675F512L<br>PIC32MX695F512L |            |                                             | 11 |

| No    | te: The TFBGA package skips from row                                                        | / "H" to r | ow "J" and has no "I" row. A1               |    |

| Pin # | Full Pin Name                                                                               | Pin #      | Full Pin Name                               |    |

| J3    | PGED2/AN7/RB7                                                                               | K8         | VDD                                         |    |

| J4    | AVDD                                                                                        | K9         | AETXD1/SCK3/U4TX/U1RTS/CN21/RD15            |    |

| J5    | AN11/ERXERR/AETXERR/PMA12/RB11                                                              | K10        | USBID/RF3                                   |    |

| J6    | TCK/RA1                                                                                     | K11        | SDA3/SDI3/U1RX/RF2                          |    |

| J7    | AN12/ERXD0/AECRS/PMA11/RB12                                                                 | L1         | PGEC2/AN6/OCFA/RB6                          |    |

| J8    | No Connect (NC)                                                                             | L2         | VREF-/CVREF-/AERXD2/PMA7/RA9                |    |

| J9    | No Connect (NC)                                                                             | L3         | AVss                                        |    |

| J10   | SCL3/SDO3/U1TX/RF8                                                                          | L4         | AN9/C2OUT/RB9                               |    |

| J11   | D-/RG3                                                                                      | L5         | AN10/CVREFOUT/PMA13/RB10                    |    |

| K1    | PGEC1/AN1/CN3/RB1                                                                           | L6         | SCK4/U5TX/U2RTS/RF13                        |    |

| K2    | PGED1/AN0/CN2/RB0                                                                           | L7         | AN13/ERXD1/AECOL/PMA10/RB13                 |    |

| K3    | VREF+/CVREF+/AERXD3/PMA6/RA10                                                               | L8         | AN15/ERXD3/AETXD2/OCFB/PMALL/PMA0/CN12/RB15 |    |

| K4    | AN8/C1OUT/RB8                                                                               | L9         | AETXD0/SS3/U4RX/U1CTS/CN20/RD14             |    |

| K5    | No Connect (NC)                                                                             | L10        | SDA5/SDI4/U2RX/PMA9/CN17/RF4                |    |

| K6    | SS4/U5RX/U2CTS/RF12                                                                         | L11        | SCL5/SDO4/U2TX/PMA8/CN18/RF5                |    |

| K7    | AN14/ERXD2/AETXD3/PMALH/PMA1/RB14                                                           |            |                                             |    |

Note 1: Shaded pins are 5V tolerant.

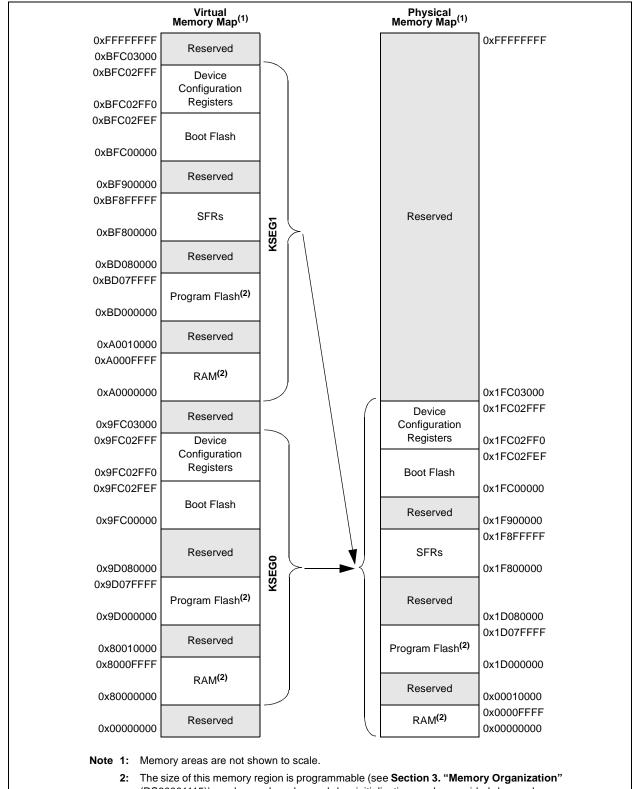

### FIGURE 4-5: MEMORY MAP ON RESET FOR PIC32MX575F512H, PIC32MX575F512L, PIC32MX675F512H, PIC32MX675F512L, PIC32MX775F512H AND PIC32MX775F512L DEVICES

(DS60001115)) and can be changed by initialization code provided by end user development tools (refer to the specific development tool documentation for information).

| Bit Bit<br>Range 31/23/15/7 30 |           | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1   | Bit<br>24/16/8/0   |

|--------------------------------|-----------|-------------------|-------------------|-------------------|-------------------|-------------------|--------------------|--------------------|

| 21.24                          | U-0       | U-0               | U-0               | U-0               | U-0               | U-0               | U-0                | U-0                |

| 31:24                          |           | _                 | -                 | —                 | _                 | —                 |                    | —                  |

| 23:16                          | U-0       | U-0               | U-0               | U-0               | U-0               | U-0               | U-0                | U-0                |

| 23.10                          | _         | _                 | _                 | —                 | _                 | —                 |                    | —                  |

| 45.0                           | U-0       | U-0               | U-0               | U-0               | U-0               | U-0               | R/W-0, HS          | R/W-0              |

| 15:8                           | —         | _                 | —                 | —                 | _                 | —                 | CMR                | VREGS              |

| 7.0                            | R/W-0, HS | R/W-0, HS         | U-0               | R/W-0, HS         | R/W-0, HS         | R/W-0, HS         | R/W-1, HS          | R/W-1, HS          |

| 7:0                            | EXTR      | SWR               | _                 | WDTO              | SLEEP             | IDLE              | BOR <sup>(1)</sup> | POR <sup>(1)</sup> |

### REGISTER 6-1: RCON: RESET CONTROL REGISTER

| Legend:           | HS = Set by hardware |                           |                    |  |  |  |  |  |

|-------------------|----------------------|---------------------------|--------------------|--|--|--|--|--|

| R = Readable bit  | W = Writable bit     | U = Unimplemented bit, re | ad as '0'          |  |  |  |  |  |

| -n = Value at POR | '1' = Bit is set     | '0' = Bit is cleared      | x = Bit is unknown |  |  |  |  |  |

| bit 31-10 | Unimplemented: Read as '0 | n' |

|-----------|---------------------------|----|

|           | eninplemented. Read as    |    |

| bit 9 | CMR: Configuration Mismatch Reset Flag bit                                   |

|-------|------------------------------------------------------------------------------|

|       | 1 = Configuration mismatch Reset has occurred                                |

|       | 0 = Configuration mismatch Reset has not occurred                            |

| bit 8 | VREGS: Voltage Regulator Standby Enable bit                                  |

|       | $\ensuremath{\mathtt{l}}$ = Regulator is enabled and is on during Sleep mode |

|       | 0 = Regulator is set to Stand-by Tracking mode                               |

| bit 7 | EXTR: External Reset (MCLR) Pin Flag bit                                     |

|       | 1 = Master Clear (pin) Reset has occurred                                    |

|       | 0 = Master Clear (pin) Reset has not occurred                                |

| bit 6 | SWR: Software Reset Flag bit                                                 |

|       | 1 = Software Reset was executed                                              |

|       | 0 = Software Reset was not executed                                          |

| bit 5 | Unimplemented: Read as '0'                                                   |

| bit 4 | WDTO: Watchdog Timer Time-out Flag bit                                       |

|       | 1 = WDT Time-out has occurred                                                |

|       | 0 = WDT Time-out has not occurred                                            |

| bit 3 | SLEEP: Wake From Sleep Flag bit                                              |

|       | 1 = Device was in Sleep mode                                                 |

|       | 0 = Device was not in Sleep mode                                             |

| bit 2 | IDLE: Wake From Idle Flag bit                                                |

|       | 1 = Device was in Idle mode                                                  |

|       | 0 = Device was not in Idle mode                                              |

| bit 1 | BOR: Brown-out Reset Flag bit <sup>(1)</sup>                                 |

|       | 1 = Brown-out Reset has occurred                                             |

|       | 0 = Brown-out Reset has not occurred                                         |

| bit 0 | <b>POR:</b> Power-on Reset Flag bit <sup>(1)</sup>                           |

|       | 1 = Power-on Reset has occurred                                              |

|       | 0 = Power-on Reset has not occurred                                          |

|       |                                                                              |

Note 1: User software must clear this bit to view the next detection.

|                             |                        | P             | IC32M)        | <b>(695F5</b> 1 | 12L DE      | /ICES                         |                               |                             |                    |                  |                       |                       |                       |                       |                         |        |                         |        |            |

|-----------------------------|------------------------|---------------|---------------|-----------------|-------------|-------------------------------|-------------------------------|-----------------------------|--------------------|------------------|-----------------------|-----------------------|-----------------------|-----------------------|-------------------------|--------|-------------------------|--------|------------|

| SS                          |                        |               |               |                 |             |                               |                               |                             |                    | Bi               | its                   |                       |                       |                       |                         |        |                         |        |            |

| Virtual Address<br>(BF88_#) |                        | Bit Range     | 31/15         | 30/14           | 29/13       | 28/12                         | 27/11                         | 26/10                       | 25/9               | 24/8             | 23/7                  | 22/6                  | 21/5                  | 20/4                  | 19/3                    | 18/2   | 17/1                    | 16/0   | All Resets |

| 1000                        | INTCON                 | 31:16         | _             | _               | —           | —                             | _                             |                             | —                  | —                | —                     | —                     | _                     | _                     | —                       | —      | —                       | SS0    | 0000       |

| 1000                        | introom                | 15:0          | —             | —               | —           | MVEC                          | —                             |                             | TPC<2:0>           | -                | —                     | —                     | —                     | INT4EP                | INT3EP                  | INT2EP | INT1EP                  | INT0EP | 0000       |

| 1010                        | INTSTAT <sup>(3)</sup> | 31:16         | —             | _               |             |                               | _                             | —                           | —                  | —                |                       |                       | _                     | _                     | _                       | —      | —                       | _      | 0000       |

|                             |                        | 15:0          |               |                 | —           | —                             | _                             |                             | SRIPL<2:0>         | •                | —                     | —                     |                       |                       | VEC                     | <5:0>  |                         |        | 0000       |

| 1020                        | IPTMR                  | 31:16<br>15:0 |               |                 |             |                               |                               |                             |                    | IPTMR            | <31:0>                |                       |                       |                       |                         |        |                         |        | 0000       |

| 1030                        | IFS0                   | 31:16         | I2C1MIF       | I2C1SIF         | I2C1BIF     | U1TXIF<br>SPI3TXIF<br>I2C3MIF | U1RXIF<br>SPI3RXIF<br>I2C3SIF | U1EIF<br>SPI3EIF<br>I2C3BIF | SPI1TXIF           | SPI1RXIF         | SPI1EIF               | OC5IF                 | IC5IF                 | T5IF                  | INT4IF                  | OC4IF  | IC4IF                   | T4IF   | 0000       |

|                             |                        | 15:0          | INT3IF        | OC3IF           | IC3IF       | T3IF                          | INT2IF                        | OC2IF                       | IC2IF              | T2IF             | INT1IF                | OC1IF                 | IC1IF                 | T1IF                  | INTOIF                  | CS1IF  | CS0IF                   | CTIF   | 0000       |

|                             |                        | 31:16         | IC3EIF        | IC2EIF          | IC1EIF      | ETHIF                         | —                             | _                           | USBIF              | FCEIF            | DMA7IF <sup>(2)</sup> | DMA6IF <sup>(2)</sup> | DMA5IF <sup>(2)</sup> | DMA4IF <sup>(2)</sup> | DMA3IF                  | DMA2IF | DMA1IF                  | DMA0IF | 0000       |

| 1040                        | IFS1                   | 15:0          | RTCCIF        | FSCMIF          | I2C2MIF     | I2C2SIF                       | I2C2BIF                       | U2TXIF<br>SPI4TXIF          | U2RXIF<br>SPI4RXIF | U2EIF<br>SPI4EIF | U3TXIF<br>SPI2TXIF    | U3RXIF<br>SPI2RXIF    | U3EIF<br>SPI2EIF      | CMP2IF                | CMP1IF                  | PMPIF  | AD1IF                   | CNIF   | 0000       |

|                             |                        |               |               |                 |             |                               |                               | I2C5MIF                     | I2C5SIF            | I2C5BIF          | I2C4MIF               | I2C4SIF               | I2C4BIF               |                       |                         |        |                         |        |            |

| 1050                        | IFS2                   | 31:16         | _             |                 | _           | _                             |                               | —                           | _                  | —                | —                     | _                     | _                     | —                     | —                       | —      | _                       | —      | 0000       |

|                             |                        | 15:0          | _             | _               | _           | -                             | U5TXIF                        | U5RXIF                      | U5EIF              | U6TXIF           | U6RXIF                | U6EIF                 | U4TXIF                | U4RXIF                | U4EIF                   | PMPEIF | IC5EIF                  | IC4EIF | 0000       |

| 1060                        | IEC0                   | 31:16         | I2C1MIE       | I2C1SIE         | I2C1BIE     | U1TXIE<br>SPI3TXIE<br>I2C3MIE | U1RXIE<br>SPI3RXIE<br>I2C3SIE | U1EIE<br>SPI3EIE<br>I2C3BIE | SPI1TXIE           | SPI1RXIE         | SPI1EIE               | OC5IE                 | IC5IE                 | T5IE                  | INT4IE                  | OC4IE  | IC4IE                   | T4IE   | 0000       |

|                             |                        | 15:0          | INT3IE        | OC3IE           | IC3IE       | T3IE                          | INT2IE                        | OC2IE                       | IC2IE              | T2IE             | INT1IE                | OC1IE                 | IC1IE                 | T1IE                  | INT0IE                  | CS1IE  | CS0IE                   | CTIE   | 0000       |

|                             |                        | 31:16         | <b>IC3EIE</b> | IC2EIE          | IC1EIE      | ETHIE                         | _                             | -                           | USBIE              | FCEIE            | DMA7IE <sup>(2)</sup> | DMA6IE(2)             | DMA5IE <sup>(2)</sup> | DMA4IE <sup>(2)</sup> | DMA3IE                  | DMA2IE | DMA1IE                  | DMA0IE | 0000       |

| 1070                        | IEC1                   | 15:0          | RTCCIE        | FSCMIE          | I2C2MIE     | I2C2SIE                       | I2C2BIE                       | U2TXIE<br>SPI4TXIE          | U2RXIE<br>SPI4RXIE | U2EIE<br>SPI4EIE | U3TXIE<br>SPI2TXIE    | U3RXIE<br>SPI2RXIE    | U3EIE<br>SPI2EIE      | CMP2IE                | CMP1IE                  | PMPIE  | AD1IE                   | CNIE   | 0000       |

|                             |                        |               |               |                 |             |                               |                               | I2C5MIE                     | I2C5SIE            | I2C5BIE          | I2C4MIE               | I2C4SIE               | I2C4BIE               |                       |                         |        |                         |        |            |

| 1080                        | IEC2                   | 31:16         | —             | _               | —           | —                             | —                             | -                           | —                  | —                | —                     | —                     | —                     | —                     | —                       | —      | —                       | —      | 0000       |

| 1000                        | 1202                   | 15:0          | —             |                 | —           | _                             | U5TXIE                        | U5RXIE                      | U5EIE              | U6TXIE           | U6RXIE                | U6EIE                 | U4TXIE                | U4RXIE                | U4EIE                   | PMPEIE | IC5EIE                  | IC4EIE | 0000       |

| 1090                        | IPC0                   | 31:16         | -             | _               |             |                               | INT0IP<2:0>                   |                             |                    | S<1:0>           |                       |                       | _                     |                       | CS1IP<2:0>              |        | CS1IS                   |        | 0000       |

|                             |                        | 15:0          | —             | —               | —           |                               | CS0IP<2:0>                    |                             |                    | S<1:0>           | —                     | —                     | —                     |                       | CTIP<2:0>               |        | CTIS                    |        | 0000       |

| 10A0                        | IPC1                   | 31:16         | _             |                 | _           |                               | INT1IP<2:0>                   |                             |                    | S<1:0>           | _                     | _                     | _                     |                       | OC1IP<2:0>              | •      | OC1IS                   |        | 0000       |

|                             |                        | 15:0          | _             | _               | _           |                               | IC1IP<2:0>                    |                             |                    | <1:0>            | _                     | _                     | _                     |                       | T1IP<2:0>               |        | T1IS-                   |        | 0000       |

| 10B0                        | IPC2                   | 31:16         | _             | _               | —           |                               | INT2IP<2:0>                   |                             |                    | S<1:0>           | —                     | _                     | _                     | OC2IP<2:0>            |                         |        | OC2IS<1:0>              |        | 0000       |

|                             |                        | 15:0          | _             |                 |             |                               | IC2IP<2:0><br>INT3IP<2:0>     |                             |                    | <1:0><br>S<1:0>  |                       |                       |                       | T2IP<2:0>             |                         |        | T2IS<1:0><br>OC3IS<1:0> |        | 0000       |

| 10C0                        | IPC3                   | 31:16<br>15:0 | _             |                 |             |                               | IC3IP<2:0>                    |                             |                    | <1:0>            | _                     |                       |                       |                       | OC3IP<2:0><br>T3IP<2:0> | •      | T3IS-                   |        | 0000       |

| Legend                      | d: x=                  |               | n value on F  | Reset; — = u    | Inimplement | ed, read as '                 |                               | ues are sho                 |                    |                  | I                     | I                     |                       | 1                     | .011 \2.02              |        | 1010                    |        | 0000       |

#### **TABLE 7-6:** INTERRUPT REGISTER MAP FOR PIC32MX664F064L, PIC32MX664F128L, PIC32MX675F256L, PIC32MX675F512L AND

Except where noted, all registers in this table have corresponding CLR, SET and INV registers at their virtual addresses, plus offsets of 0x4, 0x8 and 0xC, respectively. See Section 12.1.1 "CLR, SET and INV Note 1: Registers" for more information.

These bits are not available on PIC32MX664 devices. 2:

This register does note have associated CLR, SET, and INV registers. 3:

| Bit Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |  |  |  |  |

|-----------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|--|--|--|--|--|

| 04-04     | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |  |  |  |

| 31:24     |                   |                   |                   | CHSSA<            | 31:24>            |                   |                  |                  |  |  |  |  |  |

| 00.40     | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |  |  |  |

| 23:16     | CHSSA<23:16>      |                   |                   |                   |                   |                   |                  |                  |  |  |  |  |  |

| 45.0      | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |  |  |  |

| 15:8      | CHSSA<15:8>       |                   |                   |                   |                   |                   |                  |                  |  |  |  |  |  |

| 7.0       | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |  |  |  |

| 7:0       |                   |                   |                   | CHSSA             | <7:0>             |                   |                  |                  |  |  |  |  |  |

# REGISTER 10-10: DCHxSSA: DMA CHANNEL 'x' SOURCE START ADDRESS REGISTER

| Legend:           |                  |                        |                    |

|-------------------|------------------|------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, | read as '0'        |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared   | x = Bit is unknown |

bit 31-0 CHSSA<31:0> Channel Source Start Address bits Channel source start address. Note: This must be the physical address of the source.

# REGISTER 10-11: DCHxDSA: DMA CHANNEL 'x' DESTINATION START ADDRESS REGISTER

| Bit<br>Range | Bit<br>31/23/15/7 | 23/15/7 30/22/14/6 |       | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |  |  |  |  |  |

|--------------|-------------------|--------------------|-------|-------------------|-------------------|-------------------|------------------|------------------|--|--|--|--|--|--|

| 04.04        | R/W-0             | R/W-0              | R/W-0 | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |  |  |  |  |

| 31:24        | CHDSA<31:24>      |                    |       |                   |                   |                   |                  |                  |  |  |  |  |  |  |

| 00.40        | R/W-0             | R/W-0              | R/W-0 | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |  |  |  |  |

| 23:16        | CHDSA<23:16>      |                    |       |                   |                   |                   |                  |                  |  |  |  |  |  |  |

| 45.0         | R/W-0             | R/W-0              | R/W-0 | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |  |  |  |  |

| 15:8         | CHDSA<15:8>       |                    |       |                   |                   |                   |                  |                  |  |  |  |  |  |  |

| 7.0          | R/W-0             | R/W-0              | R/W-0 | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |  |  |  |  |

| 7:0          |                   |                    |       | CHDSA             | <7:0>             |                   |                  |                  |  |  |  |  |  |  |

| Legend:           |                  |                           |                    |

|-------------------|------------------|---------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, re | ead as '0'         |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared      | x = Bit is unknown |

bit 31-0 CHDSA<31:0>: Channel Destination Start Address bits Channel destination start address.

Note: This must be the physical address of the destination.

# TABLE 11-1: USB REGISTER MAP (CONTINUED)

| ess                         |                                 |           |       |       | · · · |       |       |       |      |      | Bits  |          |       |          |        |        |           |          |            |

|-----------------------------|---------------------------------|-----------|-------|-------|-------|-------|-------|-------|------|------|-------|----------|-------|----------|--------|--------|-----------|----------|------------|

| Virtual Address<br>(BF88_#) | Register<br>Name <sup>(1)</sup> | Bit Range | 31/15 | 30/14 | 29/13 | 28/12 | 27/11 | 26/10 | 25/9 | 24/8 | 23/7  | 22/6     | 21/5  | 20/4     | 19/3   | 18/2   | 17/1      | 16/0     | All Resets |

| 5280                        | U1FRML <sup>(3)</sup>           | 31:16     |       | —     | —     | —     | —     | —     | —    | —    | _     | —        | _     | —        | —      | —      | _         | —        | 0000       |

| 5200                        | OTTRIME                         | 15:0      | —     |       | —     | —     | —     | —     | —    | —    |       |          |       | FRML<    | 7:0>   |        |           |          | 0000       |

| 5290                        | U1FRMH <sup>(3)</sup>           | 31:16     | —     | —     | —     | —     | —     | —     | —    | —    | —     | —        | —     | —        | —      | —      | —         | —        | 0000       |

| 0200                        | 01110                           | 15:0      | —     | —     | —     | —     | —     | —     | —    | —    | _     | —        | _     | -        | —      |        | FRMH<2:0> | •        | 0000       |

| 52A0                        | U1TOK                           | 31:16     | —     | —     | —     | —     | —     | —     | —    | —    | —     | —        | —     | —        | —      | —      | —         | —        | 0000       |

| 02/10                       | orron                           | 15:0      | —     | —     | —     | —     | —     | —     | —    | —    |       | PID      | <3:0> |          |        | EP     | <3:0>     |          | 0000       |

| 52B0                        | U1SOF                           | 31:16     | —     | —     | —     | —     | —     | —     | —    | —    | _     | —        | _     | —        | —      | —      | _         | —        | 0000       |

| 5260                        | 0130F                           | 15:0      | —     | _     | _     | —     | _     | _     | _    |      |       |          |       | CNT<7    | 7:0>   |        |           |          | 0000       |

| 52C0                        | U1BDTP2                         | 31:16     | —     | -     | —     | —     | _     | _     | -    |      | —     | —        |       | —        | —      | _      |           | _        | 0000       |

| 5200                        | OIBDIF2                         | 15:0      | —     | —     | —     | —     | —     | —     | —    | —    |       |          |       | BDTPTRH  | H<7:0> |        |           |          | 0000       |

| 52D0                        | U1BDTP3                         | 31:16     | —     | _     | _     | —     | _     | _     | _    |      | —     | _        |       | —        | _      | _      |           | _        | 0000       |

| 5200                        | UIBDIF3                         | 15:0      | —     | _     | _     | _     | _     | _     | -    |      |       |          |       | BDTPTRU  | J<7:0> |        |           |          | 0000       |

| 52E0                        | U1CNFG1                         | 31:16     | —     | _     | _     | —     | _     | _     | _    |      | —     | _        |       | —        | _      | _      |           | _        | 0000       |

| 52E0                        | UTCINFGT                        | 15:0      | —     | _     | _     | —     | _     | _     | _    |      | UTEYE | UOEMON   |       | USBSIDL  | —      | _      |           | UASUSPND | 0001       |

| 5300                        | U1EP0                           | 31:16     | —     | _     | _     | _     | _     | _     | -    |      | —     | _        |       | —        | _      | _      |           | _        | 0000       |

| 5300                        | UIEPU                           | 15:0      | —     | _     | _     | —     | _     | _     | _    |      | LSPD  | RETRYDIS |       | EPCONDIS | EPRXEN | EPTXEN | EPSTALL   | EPHSHK   | 0000       |

| 5310                        | U1EP1                           | 31:16     | —     | _     | _     | —     | _     | _     | _    |      | —     | _        |       | —        | _      | _      |           | _        | 0000       |

| 5310                        | UIEPI                           | 15:0      | —     | _     | _     | _     | _     | _     | _    | _    | —     | _        | -     | EPCONDIS | EPRXEN | EPTXEN | EPSTALL   | EPHSHK   | 0000       |

| 5320                        | U1EP2                           | 31:16     | —     | _     | _     | —     | _     | _     | _    |      | —     | _        |       | —        | _      | _      |           | _        | 0000       |

| 5520                        | UIEFZ                           | 15:0      | _     | _     | _     | _     | _     | _     | _    |      | —     | _        | -     | EPCONDIS | EPRXEN | EPTXEN | EPSTALL   | EPHSHK   | 0000       |

| 5330                        | U1EP3                           | 31:16     | —     | _     | _     | _     | _     | _     | _    | _    | —     | _        | -     | —        | _      | -      |           | _        | 0000       |

| 5330                        | UIEP3                           | 15:0      | —     | _     | _     | —     | _     | _     | _    |      | —     | _        |       | EPCONDIS | EPRXEN | EPTXEN | EPSTALL   | EPHSHK   | 0000       |

| 5340                        | U1EP4                           | 31:16     | _     | _     | -     | -     | -     | -     | -    | _    | _     | _        | _     | —        | -      | _      | _         | _        | 0000       |

| 5540                        | UTEP4                           | 15:0      | —     | _     | _     | _     | _     | _     | _    | _    | —     | _        | -     | EPCONDIS | EPRXEN | EPTXEN | EPSTALL   | EPHSHK   | 0000       |

| 5350                        | U1EP5                           | 31:16     | _     | _     | -     | -     | -     | -     | -    | _    | _     | _        | _     | —        | -      | _      | _         | _        | 0000       |

| 5350                        | UIEP5                           | 15:0      | _     | _     | -     | -     | -     | -     | -    | _    | _     | _        | _     | EPCONDIS | EPRXEN | EPTXEN | EPSTALL   | EPHSHK   | 0000       |

| 5260                        | U1EP6                           | 31:16     |       |       | _     | —     | _     |       | _    | _    | —     |          |       | —        | _      | —      |           |          | 0000       |

| 5360                        | UTEP6                           | 15:0      | _     | _     | -     | -     | -     | -     | -    | _    | _     | _        | _     | EPCONDIS | EPRXEN | EPTXEN | EPSTALL   | EPHSHK   | 0000       |

| 5270                        | U1EP7                           | 31:16     | _     | _     | _     | _     | _     | _     | _    | —    | _     | _        | _     | —        | _      | _      | -         | _        | 0000       |

| 5370                        | UTEP7                           | 15:0      |       |       | _     | _     | _     |       | _    | _    | —     |          |       | EPCONDIS | EPRXEN | EPTXEN | EPSTALL   | EPHSHK   | 0000       |

| 5200                        |                                 | 31:16     | _     | _     | _     | _     | _     | _     | _    | —    | -     | —        | _     | —        | _      | —      | _         | _        | 0000       |

| 5380                        | U1EP8                           | 15:0      | —     | _     | —     | —     | _     | _     | —    | _    | _     | _        | -     | EPCONDIS | EPRXEN | EPTXEN | EPSTALL   | EPHSHK   | 0000       |

| 5000                        |                                 | 31:16     | _     | —     | _     | _     | _     | _     | —    | —    | _     | _        | _     | —        | —      | —      | —         | —        | 0000       |

| 5390                        | U1EP9                           | 15:0      | _     | —     | _     | _     | _     | _     | _    | _    | _     | _        | _     | EPCONDIS | EPRXEN | EPTXEN | EPSTALL   | EPHSHK   | 0000       |

5390

U1EP9

Legend:

x =

Note

1:

All n

end: x = unknown value on Reset; — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

1: All registers in this table (except as noted) have corresponding CLR, SET and INV registers at its virtual address, plus an offset of 0x4, 0x8 and 0xC respectively. See Section 12.1.1 "CLR, SET and INV Registers" for more information.

2: This register does not have associated SET and INV registers.

3: This register does not have associated CLR, SET and INV registers.

4: Reset value for this bit is undefined.

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1      | Bit<br>24/16/8/0 |  |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|-----------------------|------------------|--|

| 24.24        | U-0                   | U-0              |  |

| 31:24        |                   | _                 | _                 | _                 | —                 | —                 | _                     | —                |  |

| 22.10        | U-0                   | U-0              |  |

| 23:16        | _                 | _                 | _                 | _                 | _                 | —                 | _                     | —                |  |

| 15:8         | U-0                   | U-0              |  |

| 10.0         |                   | _                 | _                 | _                 | —                 | —                 | _                     | —                |  |

|              | R/W-0                 | R/W-0            |  |

| 7:0          | BTSEE             | BMXEE             | DMAEE             | BTOEE             | DFN8EE            | CRC16EE           | CRC5EE <sup>(1)</sup> |                  |  |

|              | DISEE             | DIVIXEE           | DIVIAEE           | DIVEE             | DENGEE            | URUIDEE           | EOFEE <sup>(2)</sup>  | PIDEE            |  |

# REGISTER 11-9: U1EIE: USB ERROR INTERRUPT ENABLE REGISTER

### Legend:

| 5                 |                  |                          |                    |

|-------------------|------------------|--------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, r | ead as '0'         |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared     | x = Bit is unknown |

| bit 31-8 | Unimplemented: Read as '0'                                                               |

|----------|------------------------------------------------------------------------------------------|

| bit 7    | BTSEE: Bit Stuff Error Interrupt Enable bit                                              |

|          | <ul><li>1 = BTSEF interrupt is enabled</li><li>0 = BTSEF interrupt is disabled</li></ul> |

| bit 6    | BMXEE: Bus Matrix Error Interrupt Enable bit                                             |

|          | 1 = BMXEF interrupt is enabled                                                           |

|          | 0 = BMXEF interrupt is disabled                                                          |

| bit 5    | DMAEE: DMA Error Interrupt Enable bit                                                    |

|          | <ul><li>1 = DMAEF interrupt is enabled</li><li>0 = DMAEF interrupt is disabled</li></ul> |

| bit 4    | BTOEE: Bus Turnaround Time-out Error Interrupt Enable bit                                |

|          | 1 = BTOEF interrupt is enabled                                                           |

- 0 = BTOEF interrupt is disabled

- bit 3 DFN8EE: Data Field Size Error Interrupt Enable bit

- 1 = DFN8EF interrupt is enabled

- 0 = DFN8EF interrupt is disabled

- bit 2 CRC16EE: CRC16 Failure Interrupt Enable bit

- 1 = CRC16EF interrupt is enabled

- 0 = CRC16EF interrupt is disabled

- CRC5EE: CRC5 Host Error Interrupt Enable bit<sup>(1)</sup> bit 1

- 1 = CRC5EF interrupt is enabled

- 0 = CRC5EF interrupt is disabled

- EOFEE: EOF Error Interrupt Enable bit<sup>(2)</sup>

- 1 = EOF interrupt is enabled

- 0 = EOF interrupt is disabled

- bit 0 PIDEE: PID Check Failure Interrupt Enable bit

- 1 = PIDEF interrupt is enabled

- 0 = PIDEF interrupt is disabled

- Note 1: Device mode.

- 2: Host mode.

Note: For an interrupt to propagate USBIF, the UERRIE bit (U1IE<1>) must be set.

# REGISTER 11-20: U1CNFG1: USB CONFIGURATION 1 REGISTER

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|

| 31:24        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 31.24        |                   | —                 |                   |                   |                   |                   |                  | _                |

| 23:16        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 23.10        |                   | —                 |                   |                   |                   |                   |                  |                  |

| 15:8         | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 15.6         |                   | —                 |                   |                   |                   |                   |                  | —                |

| 7.0          | R/W-0             | R/W-0             | U-0               | R/W-0             | U-0               | U-0               | U-0              | R/W-0            |

| 7:0          | UTEYE             | UOEMON            |                   | USBSIDL           |                   |                   |                  | UASUSPND         |

#### Legend:

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, I | read as '0'        |

|-------------------|------------------|--------------------------|--------------------|

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared     | x = Bit is unknown |

#### bit 31-8 Unimplemented: Read as '0'

- bit 7 UTEYE: USB Eye-Pattern Test Enable bit

- 1 = Eye-Pattern Test is enabled

- 0 = Eye-Pattern Test is disabled

- bit 6 **UOEMON:** USB OE Monitor Enable bit

- $1 = \overline{OE}$  signal is active; it indicates intervals during which the D+/D- lines are driving

- $0 = \overline{OE}$  signal is inactive

- bit 5 Unimplemented: Read as '0'

- bit 4 USBSIDL: Stop in Idle Mode bit

- 1 = Discontinue module operation when device enters Idle mode

- 0 = Continue module operation in Idle mode

- bit 3-1 Unimplemented: Read as '0'

### bit 0 UASUSPND: Automatic Suspend Enable bit

- 1 = USB module automatically suspends upon entry to Sleep mode. See the USUSPEND bit (U1PWRC<1>) in Register 11-5.

- 0 = USB module does not automatically suspend upon entry to Sleep mode. Software must use the USUSPEND bit (U1PWRC<1>) to suspend the module, including the USB 48 MHz clock.

#### TABLE 12-3: PORTC REGISTER MAP FOR PIC32MX534F064H, PIC32MX564F064H, PIC32MX564F128H, PIC32MX575F256H, PIC32MX575F512H, PIC32MX664F064H, PIC32MX664F128H, PIC32MX675F256H, PIC32MX675F512H, PIC32MX695F512H, PIC32MX764F128H, PIC32MX775F256H, PIC32MX775F512H AND PIC32MX795F512H DEVICES

| ess                         |                                 | n         |         |          |            |             |             |             |            | Bi      | ts   |      |      |      |      |      |      |      | ő          |

|-----------------------------|---------------------------------|-----------|---------|----------|------------|-------------|-------------|-------------|------------|---------|------|------|------|------|------|------|------|------|------------|

| Virtual Address<br>(BF88_#) | Register<br>Name <sup>(1)</sup> | Bit Range | 31/15   | 30/14    | 29/13      | 28/12       | 27/11       | 26/10       | 25/9       | 24/8    | 23/7 | 22/6 | 21/5 | 20/4 | 19/3 | 18/2 | 17/1 | 16/0 | All Resets |

| 6080                        | TRISC                           | 31:16     | —       | _        | -          | —           | _           | -           | —          | _       | -    | -    | -    | _    | _    | _    | _    | -    | 0000       |

| 6060                        | IRISC                           | 15:0      | TRISC15 | TRISC14  | TRISC13    | TRISC12     | _           | _           | _          | _       | _    | _    | _    | _    | _    | _    | _    | _    | F000       |

| 6000                        | PORTC                           | 31:16     | —       | -        |            | —           | —           |             | -          |         |      | _    |      | _    | _    | -    | _    |      | 0000       |

| 6090                        | PURIC                           | 15:0      | RC15    | RC14     | RC13       | RC12        | _           | -           | —          | -       | -    | -    | -    | -    |      | -    |      | -    | xxxx       |

| 60A0                        | LATC                            | 31:16     | _       | _        | _          | _           | _           | _           | _          | _       | _    | _    | _    | _    | _    | _    | _    | _    | 0000       |

| 60A0                        | LAIC                            | 15:0      | LATC15  | LATC14   | LATC13     | LATC12      | _           | _           | -          | —       | _    | —    | _    | _    | _    | _    | _    | _    | xxxx       |

| 60B0                        | ODCC                            | 31:16     | _       | _        | _          | _           | _           | _           | _          | _       | _    | _    | _    | _    | _    | _    | _    | _    | 0000       |

| 00B0                        | ODCC                            | 15:0      | ODCC15  | ODCC14   | ODCC13     | ODCC12      | _           | _           | —          | _       | _    | _    | _    | _    | _    | _    | _    | _    | 0000       |

| Logon                       | 4                               | - unkno   |         | Pocot: - | unimplomon | ted read as | '0' Poset v | luce are ch | we in hove | locimol |      |      |      |      |      |      |      |      |            |

Legend: x = unknown value on Reset; — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

Note 1: All registers in this table have corresponding CLR, SET and INV registers at their virtual addresses, plus offsets of 0x4, 0x8 and 0xC, respectively. See Section 12.1.1 "CLR, SET and INV Registers" for more information.

### TABLE 12-4: PORTC REGISTER MAP FOR PIC32MX534F064L, PIC32MX564F064L, PIC32MX564F128L, PIC32MX575F256L, PIC32MX575F512L, PIC32MX664F064L, PIC32MX664F128L, PIC32MX675F256L, PIC32MX675F512L, PIC32MX695F512L, PIC32MX764F128L. PIC32MX775F256L. PIC32MX775F512L AND PIC32MX795F512L DEVICES

| ess                         |                                 | 0         |         |         |         |         |       |       |      | Bi   | ts   |      |      |        |        |        |        |      | ú          |

|-----------------------------|---------------------------------|-----------|---------|---------|---------|---------|-------|-------|------|------|------|------|------|--------|--------|--------|--------|------|------------|

| Virtual Address<br>(BF88_#) | Register<br>Name <sup>(1)</sup> | Bit Range | 31/15   | 30/14   | 29/13   | 28/12   | 27/11 | 26/10 | 25/9 | 24/8 | 23/7 | 22/6 | 21/5 | 20/4   | 19/3   | 18/2   | 17/1   | 16/0 | All Resets |

| 6080                        | TRISC                           | 31:16     |         | _       | —       | _       | _     | _     | _    | _    | _    | _    | _    | _      | _      | _      | _      | _    | 0000       |

| 6060                        | TRISC                           | 15:0      | TRISC15 | TRISC14 | TRISC13 | TRISC12 | _     | _     | _    | _    | _    | _    | _    | TRISC4 | TRISC3 | TRISC2 | TRISC1 | _    | FOOF       |

| 6000                        | PORTC                           | 31:16     | _       | —       | —       | —       | —     | —     | —    | —    | _    | —    | —    | —      | —      | —      | —      | —    | 0000       |

| 6090                        | PURIC                           | 15:0      | RC15    | RC14    | RC13    | RC12    | _     | _     | —    | —    | _    | —    | —    | RC4    | RC3    | RC2    | RC1    | —    | xxxx       |

| 60A0                        | LATC                            | 31:16     | _       | _       | _       | _       | _     | _     | _    | _    | _    | _    | _    | _      | _      | _      | _      | _    | 0000       |

| 60A0                        | LAIC                            | 15:0      | LATC15  | LATC14  | LATC13  | LATC12  | _     | _     | —    | —    | _    | —    | —    | LATC4  | LATC3  | LATC2  | LATC1  | —    | xxxx       |

| 60B0                        | ODCC                            | 31:16     | —       | _       | _       | —       | _     | —     | _    | _    | _    | _    | _    | —      | _      | _      | _      | _    | 0000       |

| 00B0                        | ODCC                            | 15:0      | ODCC15  | ODCC14  | ODCC13  | ODCC12  | _     | _     | _    | _    | _    | _    | _    | ODCC4  | ODCC3  | ODCC2  | ODCC1  | _    | 0000       |

Legend: x = unknown value on Reset; --- = unimplemented, read as '0'. Reset values are shown in hexadecimal.

Note 1: All registers in this table have corresponding CLR, SET and INV registers at their virtual addresses, plus offsets of 0x4, 0x8 and 0xC, respectively. See Section 12.1.1 "CLR, SET and INV Registers" for more information

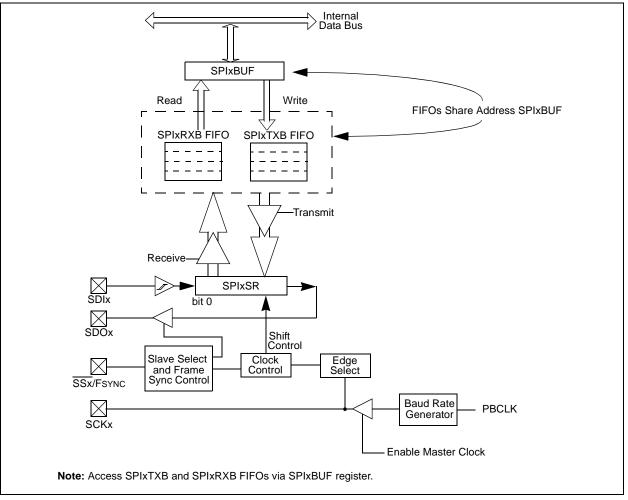

# 18.0 SERIAL PERIPHERAL INTERFACE (SPI)

Note: This data sheet summarizes the features of the PIC32MX5XX/6XX/7XX family of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to Section 23. "Serial Peripheral Interface (SPI)" (DS60001106) in the "PIC32 Family Reference Manual", which is available from the Microchip web site (www.microchip.com/PIC32).

The SPI module is a synchronous serial interface that is useful for communicating with external peripherals and other microcontroller devices. These peripheral devices may be Serial EEPROMs, Shift registers, display drivers, Analog-to-Digital Converters, etc. The PIC32 SPI module is compatible with Motorola<sup>®</sup> SPI and SIOP interfaces. The following are some of the key features of the SPI module:

- Master mode and Slave mode support

- · Four different clock formats

- Enhanced Framed SPI protocol support

- User-configurable 8-bit, 16-bit and 32-bit data width

- Separate SPI FIFO buffers for receive and transmit

FIFO buffers act as 4/8/16-level deep FIFOs

- based on 32/16/8-bit data width

Programmable interrupt event on every 8-bit, 16-bit and 32-bit data transfer

- Operation during Sleep and Idle modes

- Fast bit manipulation using CLR, SET and INV registers

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0      |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|-----------------------|

| 24.24        | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0                 |

| 31:24        | FRMEN             | FRMSYNC           | FRMPOL            | MSSEN             | FRMSYPW           | F                 | RMCNT<2:0        | >                     |

| 00.40        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | R/W-0            | R/W-0                 |

| 23:16        | _                 | —                 | _                 | —                 | —                 |                   | SPIFE            | ENHBUF <sup>(2)</sup> |

| 15.0         | R/W-0             | U-0               | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0                 |

| 15:8         | 0N <sup>(1)</sup> | —                 | SIDL              | DISSDO            | MODE32            | MODE16            | SMP              | CKE <sup>(3)</sup>    |

| 7.0          | R/W-0             | R/W-0             | R/W-0             | U-0               | R/W-0             | R/W-0             | R/W-0            | R/W-0                 |

| 7:0          | SSEN              | CKP               | MSTEN             | _                 | STXISE            | L<1:0>            | SRXIS            | EL<1:0>               |

## REGISTER 18-1: SPIxCON: SPI CONTROL REGISTER

#### Legend:

| F  | R = Readable bit | W = Writable bit | U = Unimplemented bit, re | ad as '0'          |

|----|------------------|------------------|---------------------------|--------------------|

| -1 | n = Value at POR | '1' = Bit is set | '0' = Bit is cleared      | x = Bit is unknown |

| bit 31 | FRMEN: Framed SPI Support | bit |

|--------|---------------------------|-----|

|        |                           | Dir |

- 1 = Framed SPI support is enabled (SSx pin used as FSYNC input/output)

- 0 = Framed SPI support is disabled

- bit 30 **FRMSYNC:** Frame Sync Pulse Direction Control on SSx pin bit (only Framed SPI mode) 1 = Frame sync pulse input (Slave mode)

- 0 = Frame sync pulse output (Master mode)

- bit 29 **FRMPOL:** Frame Sync Polarity bit (only Framed SPI mode)

- 1 = Frame pulse is active-high

- 0 = Frame pulse is active-low

- bit 28 MSSEN: Master Mode Slave Select Enable bit

- 1 = Slave select SPI support enabled. The SS pin is automatically driven during transmission in Master mode. Polarity is determined by the FRMPOL bit.

- 0 = Slave select SPI support is disabled.

- bit 27 FRMSYPW: Frame Sync Pulse Width bit

- 1 = Frame sync pulse is one character wide

- 0 = Frame sync pulse is one clock wide

- bit 26-24 **FRMCNT<2:0>:** Frame Sync Pulse Counter bits. Controls the number of data characters transmitted per pulse. This bit is only valid in Framed Sync mode.

- 111 = Reserved

- 110 = Reserved

- 101 = Generate a frame sync pulse on every 32 data characters

- 100 = Generate a frame sync pulse on every 16 data characters

- 011 = Generate a frame sync pulse on every 8 data characters

- 010 = Generate a frame sync pulse on every 4 data characters

- 001 = Generate a frame sync pulse on every 2 data characters

- 000 = Generate a frame sync pulse on every data character

- bit 23-18 Unimplemented: Read as '0'

- bit 17 SPIFE: Frame Sync Pulse Edge Select bit (only Framed SPI mode)

- 1 = Frame synchronization pulse coincides with the first bit clock

- 0 = Frame synchronization pulse precedes the first bit clock

- bit 16 ENHBUF: Enhanced Buffer Enable bit<sup>(2)</sup>

- 1 = Enhanced Buffer mode is enabled

- 0 = Enhanced Buffer mode is disabled

- **Note 1:** When using the 1:1 PBCLK divisor, the user's software should not read or write the peripheral's SFRs in the SYSCLK cycle immediately following the instruction that clears the module's ON bit.

- **2:** This bit can only be written when the ON bit = 0.

- **3:** This bit is not used in the Framed SPI mode. The user should program this bit to '0' for the Framed SPI mode (FRMEN = 1).

# REGISTER 18-2: SPIxSTAT: SPI STATUS REGISTER

- bit 1 SPITBF: SPI Transmit Buffer Full Status bit

- 1 = Transmit not yet started, SPITXB is full

- 0 = Transmit buffer is not full

#### Standard Buffer Mode:

Automatically set in hardware when the core writes to the SPIBUF location, loading SPITXB. Automatically cleared in hardware when the SPI module transfers data from SPITXB to SPISR.

### Enhanced Buffer Mode:

Set when CWPTR + 1 = SRPTR; cleared otherwise

SPIRBF: SPI Receive Buffer Full Status bit

1 = Receive buffer, SPIxRXB is full

0 = Receive buffer, SPIxRXB is not full

Standard Buffer Mode:

bit 0

Automatically set in hardware when the SPI module transfers data from SPIxSR to SPIxRXB. Automatically cleared in hardware when SPIxBUF is read from, reading SPIxRXB.

Enhanced Buffer Mode:

Set when SWPTR + 1 = CRPTR; cleared otherwise

# REGISTER 20-2: UxSTA: UARTx STATUS AND CONTROL REGISTER (CONTINUED)

- bit 8 **TRMT:** Transmit Shift Register is Empty bit (read-only) 1 = Transmit shift register is empty and transmit buffer is empty (the last transmission has completed) 0 = Transmit shift register is not empty, a transmission is in progress or queued in the transmit buffer bit 7-6 URXISEL<1:0>: Receive Interrupt Mode Selection bit 11 = Reserved 10 = Interrupt flag bit is asserted while receive buffer is 3/4 or more full (has 6 or more data characters) 01 = Interrupt flag bit is asserted while receive buffer is 1/2 or more full (has 4 or more data characters) 00 = Interrupt flag bit is asserted while receive buffer is not empty (has at least 1 data character) **ADDEN:** Address Character Detect bit (bit 8 of received data = 1) bit 5 1 = Address Detect mode is enabled. If 9-bit mode is not selected, this control bit has no effect. 0 = Address Detect mode is disabled bit 4 **RIDLE:** Receiver Idle bit (read-only) 1 =Receiver is idle 0 = Data is being received bit 3 PERR: Parity Error Status bit (read-only) 1 = Parity error has been detected for the current character 0 = Parity error has not been detected FERR: Framing Error Status bit (read-only) bit 2 1 = Framing error has been detected for the current character 0 = Framing error has not been detected bit 1 **OERR:** Receive Buffer Overrun Error Status bit. This bit is set in hardware and can only be cleared (= 0) in software. Clearing a previously set OERR bit resets the receiver buffer and RSR to an empty state.

- 1 = Receive buffer has overflowed

- 0 = Receive buffer has not overflowed

- bit 0 **URXDA:** Receive Buffer Data Available bit (read-only)

- 1 = Receive buffer has data, at least one more character can be read

- 0 = Receive buffer is empty

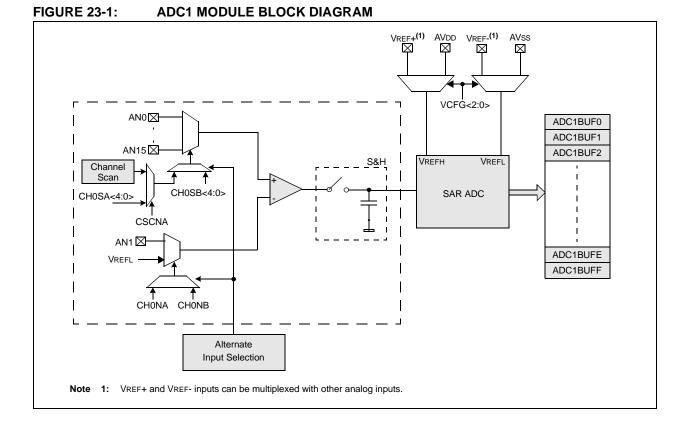

# 23.0 10-BIT ANALOG-TO-DIGITAL CONVERTER (ADC)

Note: This data sheet summarizes the features of the PIC32MX5XX/6XX/7XX family of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to Section 17. "10-bit Analog-to-Digital Converter (ADC)" (DS60001104) in the "PIC32 Family Reference Manual", which is available from Microchip web the site (www.microchip.com/PIC32).

The PIC32MX5XX/6XX/7XX 10-bit Analog-to-Digital Converter (ADC) includes the following features:

- Successive Approximation Register (SAR) conversion

- Up to 1 Msps conversion speed

- Up to 16 analog input pins

- External voltage reference input pins

- One unipolar, differential Sample and Hold (S&H) circuit

- Automatic Channel Scan mode

- Selectable conversion trigger source

- 16-word conversion result buffer

- · Selectable buffer fill modes

- Eight conversion result format options

- · Operation during Sleep and Idle modes

A block diagram of the 10-bit ADC is illustrated in Figure 23-1. The 10-bit ADC has up to 16 analog input pins, designated AN0-AN15. In addition, there are two analog input pins for external voltage reference connections. These voltage reference inputs may be shared with other analog input pins and may be common to other analog module references.

The analog inputs are connected through two multiplexers to one S&H. The analog input multiplexers can be switched between two sets of analog inputs between conversions. Unipolar differential conversions are possible on all channels, other than the pin used as the reference, using a reference input pin (see Figure 23-1).

The Analog Input Scan mode sequentially converts user-specified channels. A control register specifies which analog input channels will be included in the scanning sequence.

The 10-bit ADC is connected to a 16-word result buffer. Each 10-bit result is converted to one of eight 32-bit output formats when it is read from the result buffer.

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4     | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

|--------------|-------------------|-------------------|-------------------|-----------------------|-------------------|-------------------|------------------|------------------|

| 31:24        | R/W-0             | R/W-0             | R/W-0             | R/W-0                 | R/W-0             | U-0               | U-0              | U-0              |

| 31.24        | IVRIE             | WAKIE             | CERRIE            | SERRIE                | RBOVIE            | _                 | —                | —                |

| 23:16        | U-0               | U-0               | U-0               | U-0                   | R/W-0             | R/W-0             | R/W-0            | R/W-0            |

| 23.10        | _                 | —                 | _                 | _                     | MODIE             | CTMRIE            | RBIE             | TBIE             |

| 15.0         | R/W-0             | R/W-0             | R/W-0             | R/W-0                 | R/W-0             | U-0               | U-0              | U-0              |

| 15:8         | IVRIF             | WAKIF             | CERRIF            | SERRIF <sup>(1)</sup> | RBOVIF            | _                 | —                | —                |

| 7.0          | U-0               | U-0               | U-0               | U-0                   | R/W-0             | R/W-0             | R/W-0            | R/W-0            |

| 7:0          |                   |                   |                   |                       | MODIF             | CTMRIF            | RBIF             | TBIF             |

# REGISTER 24-3: CIINT: CAN INTERRUPT REGISTER

# Legend:

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read as '0' |                    |  |  |  |  |

|-------------------|------------------|------------------------------------|--------------------|--|--|--|--|

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared               | x = Bit is unknown |  |  |  |  |

| bit 31    | IVRIE: Invalid Message Received Interrupt Enable bit<br>1 = Interrupt request is enabled<br>0 = Interrupt request is not enabled                                 |

|-----------|------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| bit 30    | <b>WAKIE:</b> CAN Bus Activity Wake-up Interrupt Enable bit<br>1 = Interrupt request is enabled<br>0 = Interrupt request is not enabled                          |

| bit 29    | <b>CERRIE:</b> CAN Bus Error Interrupt Enable bit<br>1 = Interrupt request is enabled<br>0 = Interrupt request is not enabled                                    |

| bit 28    | SERRIE: System Error Interrupt Enable bit<br>1 = Interrupt request is enabled<br>0 = Interrupt request is not enabled                                            |

| bit 27    | <b>RBOVIE:</b> Receive Buffer Overflow Interrupt Enable bit<br>1 = Interrupt request is enabled<br>0 = Interrupt request is not enabled                          |

| bit 26-20 | Unimplemented: Read as '0'                                                                                                                                       |

| bit 19    | <b>MODIE:</b> Mode Change Interrupt Enable bit<br>1 = Interrupt request is enabled<br>0 = Interrupt request is not enabled                                       |

| bit 18    | <b>CTMRIE:</b> CAN Timestamp Timer Interrupt Enable bit<br>1 = Interrupt request is enabled<br>0 = Interrupt request is not enabled                              |

| bit 17    | <b>RBIE:</b> Receive Buffer Interrupt Enable bit<br>1 = Interrupt request is enabled<br>0 = Interrupt request is not enabled                                     |

| bit 16    | <b>TBIE:</b> Transmit Buffer Interrupt Enable bit<br>1 = Interrupt request is enabled<br>0 = Interrupt request is not enabled                                    |

| bit 15    | <b>IVRIF:</b> Invalid Message Received Interrupt Flag bit<br>1 = An invalid messages interrupt has occurred<br>0 = An invalid message interrupt has not occurred |

| Note 1:   | This bit can only be cleared by turning the CAN module Off and On by                                                                                             |

**Note 1:** This bit can only be cleared by turning the CAN module Off and On by clearing or setting the ON bit (CiCON<15>).

| Bit Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0    |  |  |

|-----------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|---------------------|--|--|

| 24.24     | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0               |  |  |

| 31:24     | PTV<15:8>         |                   |                   |                   |                   |                   |                  |                     |  |  |

| 00.40     | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0               |  |  |

| 23:16     | PTV<7:0>          |                   |                   |                   |                   |                   |                  |                     |  |  |

| 45.0      | R/W-0             | U-0               | R/W-0             | U-0               | U-0               | U-0               | R/W-0            | R/W-0               |  |  |

| 15:8      | ON                | —                 | SIDL              | _                 | _                 | _                 | TXRTS            | RXEN <sup>(1)</sup> |  |  |

| 7:0       | R/W-0             | U-0               | U-0               | R/W-0             | U-0               | U-0               | U-0              | R/W-0               |  |  |

|           | AUTOFC            |                   | _                 | MANFC             | _                 |                   |                  | BUFCDEC             |  |  |

# REGISTER 25-1: ETHCON1: ETHERNET CONTROLLER CONTROL REGISTER 1

# Legend:

| Legenu.           |                  |                          |                    |

|-------------------|------------------|--------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, I | read as '0'        |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared     | x = Bit is unknown |

bit 31-16 PTV<15:0>: PAUSE Timer Value bits PAUSE Timer Value used for Flow Control. This register should only be written when RXEN (ETHCON1<8>) is not set. These bits are only used for Flow Control operations. bit 15 **ON:** Ethernet ON bit 1 = Ethernet module is enabled 0 = Ethernet module is disabled bit 14 Unimplemented: Read as '0' bit 13 SIDL: Ethernet Stop in Idle Mode bit 1 = Ethernet module transfers are paused during Idle mode 0 = Ethernet module transfers continue during Idle mode bit 12-10 Unimplemented: Read as '0' bit 9 TXRTS: Transmit Request to Send bit 1 = Activate the TX logic and send the packet(s) defined in the TX EDT 0 = Stop transmit (when cleared by software) or transmit done (when cleared by hardware)

After the bit is written with a '1', it will clear to a '0' whenever the transmit logic has finished transmitting the requested packets in the Ethernet Descriptor Table (EDT). If a '0' is written by the CPU, the transmit logic finishes the current packet's transmission and then stops any further.

This bit only affects TX operations.

### bit 8 **RXEN:** Receive Enable bit<sup>(1)</sup>

- 1 = Enable RX logic, packets are received and stored in the RX buffer as controlled by the filter configuration

- 0 = Disable RX logic, no packets are received in the RX buffer

This bit only affects RX operations.

**Note 1:** It is not recommended to clear the RXEN bit and then make changes to any RX related field/register. The Ethernet Controller must be reinitialized (ON cleared to '0'), and then the RX changes applied.

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5   | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

|--------------|-------------------|-------------------|---------------------|-------------------|-------------------|-------------------|------------------|------------------|

| 31:24        | U-0               | U-0               | U-0                 | U-0               | U-0               | U-0               | U-0              | U-0              |

| 31.24        |                   | —                 |                     | _                 | _                 | _                 | _                | _                |

| 23:16        | U-0               | U-0               | U-0                 | U-0               | U-0               | U-0               | U-0              | U-0              |

| 23.10        | —                 | —                 | —                   | -                 | —                 | —                 | —                | —                |

| 15.0         | R/W-0             | R/W-0             | R/W-0               | U-0               | U-0               | U-0               | U-0              | R-0              |

| 15:8         | 0N <sup>(1)</sup> | COE               | CPOL <sup>(2)</sup> | -                 | —                 | —                 | —                | COUT             |

| 7:0          | R/W-1             | R/W-1             | U-0                 | R/W-0             | U-0               | U-0               | R/W-1            | R/W-1            |

|              | EVPOL             | _<1:0>            |                     | CREF              | _                 |                   | CCH              | <1:0>            |

## REGISTER 26-1: CMxCON: COMPARATOR 'x' CONTROL REGISTER

#### Legend:

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, re | ead as '0'         |

|-------------------|------------------|---------------------------|--------------------|

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared      | x = Bit is unknown |

#### bit 31-16 Unimplemented: Read as '0'

bit 15 ON: Comparator ON bit<sup>(1)</sup>

Clearing this bit does not affect the other bits in this register.

- 1 = Module is enabled. Setting this bit does not affect the other bits in this register

- 0 = Module is disabled and does not consume current.

- bit 14 COE: Comparator Output Enable bit

- 1 = Comparator output is driven on the output CxOUT pin

- 0 = Comparator output is not driven on the output CxOUT pin

- bit 13 **CPOL:** Comparator Output Inversion bit<sup>(2)</sup>

- 1 = Output is inverted

- 0 = Output is not inverted

### bit 12-9 Unimplemented: Read as '0'

- bit 8 COUT: Comparator Output bit

- 1 =Output of the Comparator is a '1'

- 0 = Output of the Comparator is a '0'

- bit 7-6 EVPOL<1:0>: Interrupt Event Polarity Select bits

- 11 = Comparator interrupt is generated on a low-to-high or high-to-low transition of the comparator output

- 10 = Comparator interrupt is generated on a high-to-low transition of the comparator output

- 01 = Comparator interrupt is generated on a low-to-high transition of the comparator output

- 00 = Comparator interrupt generation is disabled

#### bit 5 Unimplemented: Read as '0'

- bit 4 **CREF:** Comparator Positive Input Configure bit

- 1 = Comparator non-inverting input is connected to the internal CVREF

- 0 = Comparator non-inverting input is connected to the CxIN+ pin

- bit 3-2 Unimplemented: Read as '0'

- bit 1-0 **CCH<1:0>:** Comparator Negative Input Select bits for Comparator

- 11 = Comparator inverting input is connected to the IVREF

- 10 = Comparator inverting input is connected to the C2IN+ pin for C1 and C1IN+ pin for C2

- 01 = Comparator inverting input is connected to the C1IN+ pin for C1 and C2IN+ pin for C2

- 00 = Comparator inverting input is connected to the C1IN- pin for C1 and C2IN- pin for C2

- **Note 1:** When using the 1:1 PBCLK divisor, the user's software should not read/write the peripheral's SFRs in the SYSCLK cycle immediately following the instruction that clears the module's ON bit.