Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XE

| Details                    |                                                                                   |

|----------------------------|-----------------------------------------------------------------------------------|

| Product Status             | Active                                                                            |

| Core Processor             | MIPS32® M4K™                                                                      |

| Core Size                  | 32-Bit Single-Core                                                                |

| Speed                      | 80MHz                                                                             |

| Connectivity               | Ethernet, I <sup>2</sup> C, SPI, UART/USART, USB OTG                              |

| Peripherals                | Brown-out Detect/Reset, DMA, POR, PWM, WDT                                        |

| Number of I/O              | 83                                                                                |

| Program Memory Size        | 512KB (512K x 8)                                                                  |

| Program Memory Type        | FLASH                                                                             |

| EEPROM Size                | -                                                                                 |

| RAM Size                   | 64K x 8                                                                           |

| Voltage - Supply (Vcc/Vdd) | 2.3V ~ 3.6V                                                                       |

| Data Converters            | A/D 16x10b                                                                        |

| Oscillator Type            | Internal                                                                          |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                                 |

| Mounting Type              | Surface Mount                                                                     |

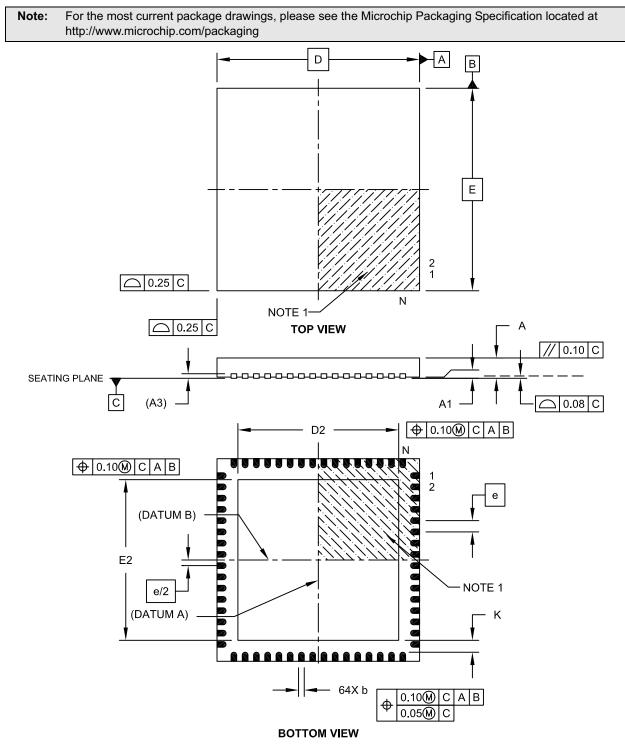

| Package / Case             | 121-TFBGA                                                                         |

| Supplier Device Package    | 121-TFBGA (10x10)                                                                 |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic32mx675f512lt-80i-bg |

|                            |                                                                                   |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

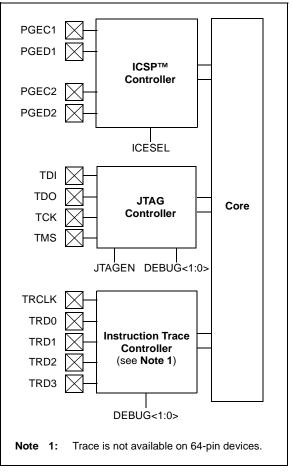

# 2.5 ICSP Pins

The PGECx and PGEDx pins are used for In-Circuit Serial Programming<sup>TM</sup> (ICSP<sup>TM</sup>) and debugging. It is recommended to keep the trace length between the ICSP connector and the ICSP pins on the device as short as possible. If the ICSP connector is expected to experience an ESD event, a series resistor is recommended, with the value in the range of a few tens of Ohms, not to exceed 100 Ohms.

Pull-up resistors, series diodes and capacitors on the PGECx and PGEDx pins are not recommended as they will interfere with the programmer/debugger communications to the device. If such discrete components are an application requirement, they should be removed from the circuit during programming and debugging. Alternatively, refer to the AC/DC characteristics and timing requirements information in the respective device Flash programming specification for information on capacitive loading limits and pin input voltage high (VIH) and input low (VIL) requirements.

Ensure that the "Communication Channel Select" (i.e., PGECx/PGEDx pins) programmed into the device matches the physical connections for the ICSP to MPLAB<sup>®</sup> ICD 3 or MPLAB<sup>®</sup> REAL ICE<sup>TM</sup>.

For more information on ICD 3 and REAL ICE connection requirements, refer to the following documents that are available on the Microchip web site.

- "Using MPLAB<sup>®</sup> ICD 3" (poster) (DS50001765)

- "MPLAB<sup>®</sup> ICD 3 Design Advisory" (DS50001764)

- "MPLAB<sup>®</sup> REAL ICE<sup>™</sup> In-Circuit Emulator User's Guide" (DS50001616)

- "Using MPLAB<sup>®</sup> REAL ICE™ Emulator" (poster) (DS50001749)

# 2.6 JTAG

The TMS, TDO, TDI and TCK pins are used for testing and debugging according to the Joint Test Action Group (JTAG) standard. It is recommended to keep the trace length between the JTAG connector and the JTAG pins on the device as short as possible. If the JTAG connector is expected to experience an ESD event, a series resistor is recommended, with the value in the range of a few tens of Ohms, not to exceed 100 Ohms.

Pull-up resistors, series diodes and capacitors on the TMS, TDO, TDI and TCK pins are not recommended as they will interfere with the programmer/debugger communications to the device. If such discrete components are an application requirement, they should be removed from the circuit during programming and debugging. Alternatively, refer to the AC/DC characteristics and timing requirements information in the respective device Flash programming specification for information on capacitive loading limits and pin input voltage high (VIH) and input low (VIL) requirements.

# 2.7 Trace

The trace pins can be connected to a hardware-traceenabled programmer to provide a compress real time instruction trace. When used for trace the TRD3, TRD2, TRD1, TRD0 and TRCLK pins should be dedicated for this use. The trace hardware requires a  $22\Omega$  series resistor between the trace pins and the trace connector.

# 2.8 External Oscillator Pins

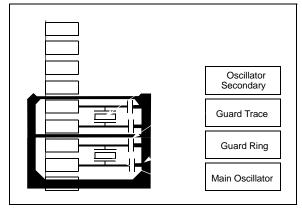

Many MCUs have options for at least two oscillators: a high-frequency primary oscillator and a low-frequency secondary oscillator. Refer to **Section 8.0 "Oscillator Configuration"** for details.

The oscillator circuit should be placed on the same side of the board as the device. Also, place the oscillator circuit close to the respective oscillator pins, not exceeding one-half inch (12 mm) distance between them. The load capacitors should be placed next to the oscillator itself, on the same side of the board. Use a grounded copper pour around the oscillator circuit to isolate them from surrounding circuits. The grounded copper pour should be routed directly to the MCU ground. Do not run any signal traces or power traces inside the ground pour. Also, if using a two-sided board, avoid any traces on the other side of the board where the crystal is placed. A suggested layout is illustrated in Figure 2-3.

#### FIGURE 2-3: SUGGESTED OSCILLATOR CIRCUIT PLACEMENT

### TABLE 4-1: SFR MEMORY MAP

|                        | Virtual A | Address         |

|------------------------|-----------|-----------------|

| Peripheral             | Base      | Offset<br>Start |

| Watchdog Timer         |           | 0x0000          |

| RTCC                   |           | 0x0200          |

| Timer1-Timer5          |           | 0x0600          |

| Input Capture 1-5      |           | 0x2000          |

| Output Compare 1-5     |           | 0x3000          |

| I2C1-I2C5              |           | 0x5000          |

| SPI1-SPI4              |           | 0x5800          |

| UART1-UART6            | 0xBF80    | 0x6000          |

| PMP                    | UXBFOU    | 0x7000          |

| ADC                    |           | 0x9000          |

| CVREF                  |           | 0x9800          |

| Comparator             |           | 0xA000          |

| Oscillator             |           | 0xF000          |

| Device and Revision ID |           | 0xF200          |

| Flash Controller       |           | 0xF400          |

| Reset                  |           | 0xF600          |

| Interrupts             |           | 0x1000          |

| Bus Matrix             |           | 0x2000          |

| DMA                    |           | 0x3000          |

| Prefetch               | 0xBF88    | 0x4000          |

| USB                    |           | 0x5040          |

| PORTA-PORTG            |           | 0x6000          |

| Ethernet               |           | 0x9000          |

| Configuration          | 0xBFC0    | 0x2FF0          |

| Interrupt Source <sup>(1)</sup>   | IRQ    | Vector        | Interrupt Bit Location |          |              |              |  |  |

|-----------------------------------|--------|---------------|------------------------|----------|--------------|--------------|--|--|

| Interrupt Source                  | Number | Number        | Flag                   | Enable   | Priority     | Sub-Priority |  |  |

| IC3E – Input Capture 3 Error      | 63     | 13            | IFS1<31>               | IEC1<31> | IPC3<12:10>  | IPC3<9:8>    |  |  |

| IC4E – Input Capture 4 Error      | 64     | 17            | IFS2<0>                | IEC2<0>  | IPC4<12:10>  | IPC4<9:8>    |  |  |

| IC5E – Input Capture 5 Error      | 65     | 21            | IFS2<1>                | IEC2<1>  | IPC5<12:10>  | IPC5<9:8>    |  |  |

| PMPE – Parallel Master Port Error | 66     | 28            | IFS2<2>                | IEC2<2>  | IPC7<4:2>    | IPC7<1:0>    |  |  |

| U4E – UART4 Error                 | 67     | 49            | IFS2<3>                | IEC2<3>  | IPC12<12:10> | IPC12<9:8>   |  |  |

| U4RX – UART4 Receiver             | 68     | 49            | IFS2<4>                | IEC2<4>  | IPC12<12:10> | IPC12<9:8>   |  |  |

| U4TX – UART4 Transmitter          | 69     | 49            | IFS2<5>                | IEC2<5>  | IPC12<12:10> | IPC12<9:8>   |  |  |

| U6E – UART6 Error                 | 70     | 50            | IFS2<6>                | IEC2<6>  | IPC12<20:18> | IPC12<17:16> |  |  |

| U6RX – UART6 Receiver             | 71     | 50            | IFS2<7>                | IEC2<7>  | IPC12<20:18> | IPC12<17:16> |  |  |

| U6TX – UART6 Transmitter          | 72     | 50            | IFS2<8>                | IEC2<8>  | IPC12<20:18> | IPC12<17:16> |  |  |

| U5E – UART5 Error                 | 73     | 51            | IFS2<9>                | IEC2<9>  | IPC12<28:26> | IPC12<25:24> |  |  |

| U5RX – UART5 Receiver             | 74     | 51            | IFS2<10>               | IEC2<10> | IPC12<28:26> | IPC12<25:24> |  |  |

| U5TX – UART5 Transmitter          | 75     | 51            | IFS2<11>               | IEC2<11> | IPC12<28:26> | IPC12<25:24> |  |  |

| (Reserved)                        | —      | —             | —                      | —        | <u> </u>     |              |  |  |

|                                   | Lowe   | est Natural ( | Order Priority         | /        |              |              |  |  |

Note 1: Not all interrupt sources are available on all devices. See TABLE 1: "PIC32MX5XX USB and CAN Features", TABLE 2: "PIC32MX6XX USB and Ethernet Features" and TABLE 3: "PIC32MX7XX USB, Ethernet, and CAN Features" for the list of available peripherals.

|                             |                                 | P             | IC32M)  | <b>(795F5</b> 1                                | 12L DEV | /ICES                         |                               |                               |                               |                             |                               |                               |                             |                       |            |        |        |        |            |

|-----------------------------|---------------------------------|---------------|---------|------------------------------------------------|---------|-------------------------------|-------------------------------|-------------------------------|-------------------------------|-----------------------------|-------------------------------|-------------------------------|-----------------------------|-----------------------|------------|--------|--------|--------|------------|

| SS                          |                                 |               |         |                                                |         |                               |                               |                               |                               | В                           | its                           |                               |                             |                       |            |        |        |        |            |

| Virtual Address<br>(BF88_#) | Register<br>Name <sup>(1)</sup> | Bit Range     | 31/15   | 30/14                                          | 29/13   | 28/12                         | 27/11                         | 26/10                         | 25/9                          | 24/8                        | 23/7                          | 22/6                          | 21/5                        | 20/4                  | 19/3       | 18/2   | 17/1   | 16/0   | All Resets |

| 1000                        | INTCON                          | 31:16         | _       | _                                              | —       | _                             | _                             | -                             | —                             | _                           | _                             | —                             | —                           | _                     |            | —      | —      | SS0    | 0000       |

| 1000                        | INTCON                          | 15:0          | _       | -                                              | —       | MVEC                          | _                             |                               | TPC<2:0>                      |                             | _                             | —                             | _                           | INT4EP                | INT3EP     | INT2EP | INT1EP | INT0EP | 0000       |

| 1010                        | INTSTAT <sup>(3)</sup>          | 31:16         |         | —                                              | _       | —                             | —                             | _                             | —                             | —                           | _                             | _                             | —                           |                       | —          | —      | —      |        | 0000       |

|                             |                                 | 15:0          | _       | _                                              | —       | —                             | —                             |                               | SRIPL<2:0>                    |                             | —                             | —                             |                             |                       | VEC        | <5:0>  |        |        | 0000       |

| 1020                        | IPTMR                           | 31:16<br>15:0 |         |                                                |         |                               | IPIMR<31:0>                   |                               |                               |                             |                               |                               |                             | 0000                  |            |        |        |        |            |

| 1030                        | IFS0                            | 31:16         | I2C1MIF | I2C1SIF                                        | I2C1BIF | U1TXIF<br>SPI3TXIF<br>I2C3MIF | U1RXIF<br>SPI3RXIF<br>I2C3SIF | U1EIF<br>SPI3EIF<br>I2C3BIF   | SPI1TXIF                      | SPI1RXIF                    | SPI1EIF                       | OC5IF                         | IC5IF                       | T5IF                  | INT4IF     | OC4IF  | IC4IF  | T4IF   | 0000       |

|                             |                                 | 15:0          | INT3IF  | OC3IF                                          | IC3IF   | T3IF                          | INT2IF                        | OC2IF                         | IC2IF                         | T2IF                        | INT1IF                        | OC1IF                         | IC1IF                       | T1IF                  | INT0IF     | CS1IF  | CS0IF  | CTIF   | 0000       |

|                             |                                 | 31:16         | IC3EIF  | IC2EIF                                         | IC1EIF  | ETHIF                         | CAN2IF <sup>(2)</sup>         | CAN1IF                        | USBIF                         | FCEIF                       | DMA7IF <sup>(2)</sup>         | DMA6IF <sup>(2)</sup>         | DMA5IF <sup>(2)</sup>       | DMA4IF <sup>(2)</sup> | DMA3IF     | DMA2IF | DMA1IF | DMA0IF | 0000       |

| 1040                        | IFS1                            | 15:0          | RTCCIF  | FSCMIF                                         | I2C2MIF | I2C2SIF                       | I2C2BIF                       | U2TXIF<br>SPI4TXIF<br>I2C5MIF | U2RXIF<br>SPI4RXIF<br>I2C5SIF | U2EIF<br>SPI4EIF<br>I2C5BIF | U3TXIF<br>SPI2TXIF<br>I2C4MIF | U3RXIF<br>SPI2RXIF<br>I2C4SIF | U3EIF<br>SPI2EIF<br>I2C4BIF | CMP2IF                | CMP1IF     | PMPIF  | AD1IF  | CNIF   | 0000       |

|                             |                                 | 31:16         | _       | _                                              | _       | _                             | _                             | _                             | _                             | _                           | _                             | _                             | _                           | _                     | _          | _      | _      | _      | 0000       |

| 1050                        | IFS2                            | 15:0          |         | _                                              | _       | _                             | U5TXIF                        | U5RXIF                        | U5EIF                         | U6TXIF                      | U6RXIF                        | U6EIF                         | U4TXIF                      | U4RXIF                | U4EIF      | PMPEIF | IC5EIF | IC4EIF | 0000       |

| 1060                        | IEC0                            | 31:16         | I2C1MIE | I2C1SIE                                        | I2C1BIE | U1TXIE<br>SPI3TXIE<br>I2C3MIE | U1RXIE<br>SPI3RXIE<br>I2C3SIE | U1EIE<br>SPI3EIE<br>I2C3BIE   | SPI1TXIE                      | SPI1RXIE                    | SPI1EIE                       | OC5IE                         | IC5IE                       | T5IE                  | INT4IE     | OC4IE  | IC4IE  | T4IE   | 0000       |

|                             |                                 | 15:0          | INT3IE  | OC3IE                                          | IC3IE   | T3IE                          | INT2IE                        | OC2IE                         | IC2IE                         | T2IE                        | INT1IE                        | OC1IE                         | IC1IE                       | T1IE                  | INT0IE     | CS1IE  | CS0IE  | CTIE   | 0000       |

|                             |                                 | 31:16         | IC3EIE  | IC2EIE                                         | IC1EIE  | ETHIE                         | CAN2IE <sup>(2)</sup>         | CAN1IE                        | USBIE                         | FCEIE                       | DMA7IE <sup>(2)</sup>         | DMA6IE <sup>(2)</sup>         | DMA5IE <sup>(2)</sup>       | DMA4IE <sup>(2)</sup> | DMA3IE     | DMA2IE | DMA1IE | DMA0IE | 0000       |

| 1070                        | IEC1                            | 15:0          | RTCCIE  | FSCMIE                                         | I2C2MIE | I2C2SIE                       | I2C2BIE                       | U2TXIE<br>SPI4TXIE<br>I2C5MIE | U2RXIE<br>SPI4RXIE<br>I2C5SIE | U2EIE<br>SPI4EIE<br>I2C5BIE | U3TXIE<br>SPI2TXIE<br>I2C4MIE | U3RXIE<br>SPI2RXIE<br>I2C4SIE | U3EIE<br>SPI2EIE<br>I2C4BIE | CMP2IE                | CMP1IE     | PMPIE  | AD1IE  | CNIE   | 0000       |

|                             | 1500                            | 31:16         | _       | _                                              | _       | _                             | _                             | _                             | _                             | _                           | _                             | _                             | _                           | _                     | _          | _      | _      | _      | 0000       |

| 1080                        | IEC2                            | 15:0          | _       | —                                              | _       | _                             | U5TXIE                        | U5RXIE                        | U5EIE                         | U6TXIE                      | U6RXIE                        | U6EIE                         | U4TXIE                      | U4RXIE                | U4EIE      | PMPEIE | IC5EIE | IC4EIE | 0000       |

| 1090                        | IPC0                            | 31:16         |         | _                                              | —       |                               | INT0IP<2:0>                   |                               | INTOIS                        | S<1:0>                      | _                             | —                             | —                           |                       | CS1IP<2:0> | >      | CS1IS  | S<1:0> | 0000       |

| 1090                        | IFCU                            | 15:0          | —       | —                                              | —       |                               | CS0IP<2:0>                    |                               | CSOIS                         | 5<1:0>                      | —                             | —                             | —                           |                       | CTIP<2:0>  |        | CTIS   | <1:0>  | 0000       |

| 10A0                        | IPC1                            | 31:16         |         | —                                              |         |                               | INT1IP<2:0>                   |                               | INT1IS                        |                             | —                             |                               | —                           |                       | OC1IP<2:0> | >      | OC1IS  |        | 0000       |

|                             |                                 | 15:0          |         | —                                              | —       |                               | IC1IP<2:0>                    |                               | IC1IS                         |                             | _                             | —                             | —                           |                       | T1IP<2:0>  |        | T1IS   |        | 0000       |

| 10B0                        | IPC2                            | 31:16         |         | —                                              |         |                               | INT2IP<2:0>                   |                               | INT2IS                        |                             | _                             |                               | —                           |                       | OC2IP<2:0> | >      | OC2IS  |        | 0000       |

|                             |                                 | 15:0          | _       | _                                              | _       |                               | IC2IP<2:0>                    |                               | IC2IS                         |                             | _                             | _                             | _                           |                       | T2IP<2:0>  |        | T2IS   |        | 0000       |

| 10C0                        | IPC3                            | 31:16<br>15:0 |         |                                                | _       |                               | INT3IP<2:0>                   |                               | INT3IS                        |                             |                               |                               | _                           |                       | OC3IP<2:0> | >      | OC315  |        | 0000       |

| í                           |                                 | 15.0          |         | IC3IP<2:0> IC3IS<1:0> T3IP<2:0> T3IS<1:0> 0000 |         |                               |                               |                               |                               |                             |                               |                               |                             |                       |            |        |        |        |            |

# TABLE 7-7:INTERRUPT REGISTER MAP FOR PIC32MX764F128L, PIC32MX775F256L, PIC32MX775F512L AND<br/>PIC32MX795F512L DEVICES

**d:** x = unknown value on Reset; — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

Note 1: Except where noted, all registers in this table have corresponding CLR, SET and INV registers at their virtual addresses, plus offsets of 0x4, 0x8 and 0xC, respectively. See Section 12.1.1 "CLR, SET and INV Registers" for more information.

PIC32MX5XX/6XX/7XX

2: This bit is unimplemented on PIC32MX764F128L device.

3: This register does not have associated CLR, SET, and INV registers.

## REGISTER 8-1: OSCCON: OSCILLATOR CONTROL REGISTER (CONTINUED)

bit 18-16 PLLMULT<2:0>: Phase-Locked Loop (PLL) Multiplier bits

- 111 = Clock is multiplied by 24

- 110 =Clock is multiplied by 21

- 101 = Clock is multiplied by 20

- 100 = Clock is multiplied by 19

- 011 = Clock is multiplied by 18

- 010 =Clock is multiplied by 17

- 001 =Clock is multiplied by 16

- 000 =Clock is multiplied by 15

- bit 15 Unimplemented: Read as '0'

- bit 14-12 COSC<2:0>: Current Oscillator Selection bits

- 111 = Internal Fast RC (FRC) Oscillator divided by OSCCON<FRCDIV> bits

- 110 = Internal Fast RC (FRC) Oscillator divided by 16

- 101 = Internal Low-Power RC (LPRC) Oscillator

- 100 = Secondary Oscillator (Sosc)

- 011 = Primary Oscillator (Posc) with PLL module (XTPLL, HSPLL or ECPLL)

- 010 = Primary Oscillator (Posc) (XT, HS or EC)

- 001 = Internal Fast RC Oscillator with PLL module via Postscaler (FRCPLL)

- 000 = Internal Fast RC (FRC) Oscillator

- bit 11 Unimplemented: Read as '0'

- bit 10-8 NOSC<2:0>: New Oscillator Selection bits

- 111 = Internal Fast RC Oscillator (FRC) divided by OSCCON<FRCDIV> bits

- 110 = Internal Fast RC Oscillator (FRC) divided by 16

- 101 = Internal Low-Power RC (LPRC) Oscillator

- 100 = Secondary Oscillator (Sosc)

- 011 = Primary Oscillator with PLL module (XTPLL, HSPLL or ECPLL)

- 010 = Primary Oscillator (XT, HS or EC)

- 001 = Internal Fast Internal RC Oscillator with PLL module via Postscaler (FRCPLL)

- 000 = Internal Fast Internal RC Oscillator (FRC)

- On Reset, these bits are set to the value of the FNOSC Configuration bits (DEVCFG1<2:0>).

- bit 7 CLKLOCK: Clock Selection Lock Enable bit

If clock switching and monitoring is disabled (FCKSM<1:0> = 1x):

- 1 = Clock and PLL selections are locked

- 0 = Clock and PLL selections are not locked and may be modified

If clock switching and monitoring is enabled (FCKSM<1:0> = 0x):

Clock and PLL selections are never locked and may be modified.

- bit 6 ULOCK: USB PLL Lock Status bit

- 1 = Indicates that the USB PLL module is in lock or USB PLL module start-up timer is satisfied

- 0 = Indicates that the USB PLL module is out of lock or USB PLL module start-up timer is in progress or USB PLL is disabled

- bit 5 SLOCK: PLL Lock Status bit

- 1 = PLL module is in lock or PLL module start-up timer is satisfied

- 0 = PLL module is out of lock, PLL start-up timer is running or PLL is disabled

- bit 4 SLPEN: Sleep Mode Enable bit

- 1 = Device will enter Sleep mode when a WAIT instruction is executed

- 0 = Device will enter Idle mode when a WAIT instruction is executed

- bit 3 **CF:** Clock Fail Detect bit

- 1 = FSCM has detected a clock failure

- 0 = No clock failure has been detected

Note: Writes to this register require an unlock sequence. Refer to **Section 6.** "Oscillator" (DS60001112) in the "PIC32 Family Reference Manual" for details.

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |  |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|--|--|

| 31:24        | R/W-x             | R/W-x             | R/W-x             | R/W-x             | R/W-x             | R/W-x             | R/W-x            | R/W-x            |  |  |

| 31:24        |                   |                   |                   | CHEW3<            | :31:24>           |                   |                  |                  |  |  |

| 00.40        | R/W-x             | R/W-x             | R/W-x             | R/W-x             | R/W-x             | R/W-x             | R/W-x            | R/W-x            |  |  |

| 23:16        | CHEW3<23:16>      |                   |                   |                   |                   |                   |                  |                  |  |  |

| 45.0         | R/W-x             | R/W-x             | R/W-x             | R/W-x             | R/W-x             | R/W-x             | R/W-x            | R/W-x            |  |  |

| 15:8         | CHEW3<15:8>       |                   |                   |                   |                   |                   |                  |                  |  |  |

| 7.0          | R/W-x             | R/W-x             | R/W-x             | R/W-x             | R/W-x             | R/W-x             | R/W-x            | R/W-x            |  |  |

| 7:0          | CHEW3<7:0>        |                   |                   |                   |                   |                   |                  |                  |  |  |

## REGISTER 9-8: CHEW3: CACHE WORD 3

| Legend:           |                  |                      |                    |

|-------------------|------------------|----------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bi | t, read as '0'     |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared | x = Bit is unknown |

bit 31-0 **CHEW3<31:0>:** Word 3 of the cache line selected by CHEIDX<3:0> bits (CHEACC<3:0>) Readable only if the device is not code-protected.

Note: This register is a window into the cache data array and is only readable if the device is not code-protected.

#### REGISTER 9-9: CHELRU: CACHE LRU REGISTER

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |  |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|--|--|

| 31:24        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | R-0              |  |  |

|              | —                 | —                 | _                 | —                 | —                 | _                 | —                | CHELRU<24>       |  |  |

| 22:16        | R-0               | R-0               | R-0               | R-0               | R-0               | R-0               | R-0              | R-0              |  |  |

| 23:16        |                   |                   |                   | CHELRI            | J<23:16>          |                   |                  |                  |  |  |

| 45.0         | R-0               | R-0               | R-0               | R-0               | R-0               | R-0               | R-0              | R-0              |  |  |

| 15:8         | CHELRU<15:8>      |                   |                   |                   |                   |                   |                  |                  |  |  |

| 7:0          | R-0               | R-0               | R-0               | R-0               | R-0               | R-0               | R-0              | R-0              |  |  |

| 7.0          | CHELRU<7:0>       |                   |                   |                   |                   |                   |                  |                  |  |  |

| Legend:           |                  |                        |                    |

|-------------------|------------------|------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, | read as '0'        |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared   | x = Bit is unknown |

bit 31-25 Unimplemented: Write '0'; ignore read

bit 24-0 **CHELRU<24:0>:** Cache Least Recently Used State Encoding bits Indicates the pseudo-LRU state of the cache.

# PIC32MX5XX/6XX/7XX

| Bit<br>Range | Bit<br>31/23/15/7    | Bit<br>30/22/14/6 | Bit<br>29/21/13/5       | Bit<br>28/20/12/4 | Bit<br>27/19/11/3  | Bit<br>26/18/10/2 | Bit<br>25/17/9/1   | Bit<br>24/16/8/0 |

|--------------|----------------------|-------------------|-------------------------|-------------------|--------------------|-------------------|--------------------|------------------|

| 21.24        | U-0                  | U-0               | U-0                     | U-0               | U-0                | U-0               | U-0                | U-0              |

| 31:24        |                      |                   |                         |                   | _                  |                   |                    | —                |

| 23:16        | U-0                  | U-0               | U-0                     | U-0               | U-0                | U-0               | U-0                | U-0              |

| 23.10        | _                    | -                 | _                       | —                 | _                  | —                 | -                  | —                |

| 45.0         | R/W-0                | U-0               | R/W-0                   | U-0               | U-0                | U-0               | U-0                | U-0              |

| 15:8         | ON <sup>(1,3)</sup>  |                   | SIDL <sup>(4)</sup>     | _                 | -                  | _                 | _                  | —                |

| 7:0          | R/W-0                | R/W-0             | R/W-0                   | R/W-0             | R/W-0              | U-0               | R/W-0              | U-0              |

| 7:0          | TGATE <sup>(3)</sup> | Т                 | CKPS<2:0> <sup>(:</sup> | 3)                | T32 <sup>(2)</sup> | _                 | TCS <sup>(3)</sup> | _                |

## REGISTER 14-1: TXCON: TYPE B TIMER CONTROL REGISTER

#### Legend:

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, | read as '0'        |  |

|-------------------|------------------|------------------------|--------------------|--|

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared   | x = Bit is unknown |  |

### bit 31-16 **Unimplemented:** Read as '0'

- bit 15 **ON:** Timer On bit<sup>(1,3)</sup>

- 1 = Module is enabled 0 = Module is disabled

- bit 14 Unimplemented: Read as '0'

- bit 13 SIDL: Stop in Idle Mode bit<sup>(4)</sup>

- 1 = Discontinue operation when device enters Idle mode0 = Continue operation when device is in Idle mode

- bit 12-8 Unimplemented: Read as '0'

- bit 7 **TGATE:** Timer Gated Time Accumulation Enable bit<sup>(3)</sup>

When TCS = 1:

This bit is ignored and is read as '0'.

#### When TCS = 0:

1 =Gated time accumulation is enabled

0 = Gated time accumulation is disabled

#### bit 6-4 TCKPS<2:0>: Timer Input Clock Prescale Select bits<sup>(3)</sup>

- 111 = 1:256 prescale value

- 110 = 1:64 prescale value

- 101 = 1:32 prescale value

- 100 = 1:16 prescale value

- 011 = 1:8 prescale value

- 010 = 1:4 prescale value

- 001 = 1:2 prescale value

- 000 = 1:1 prescale value

- **Note 1:** When using the 1:1 PBCLK divisor, the user's software should not read/write the peripheral SFRs in the SYSCLK cycle immediately following the instruction that clears the module's ON bit.

- **2:** This bit is only available on even numbered timers (Timer2 and Timer4).

- **3:** While operating in 32-bit mode, this bit has no effect for odd numbered timers (Timer1, Timer3, and Timer5). All timer functions are set through the even numbered timers.

- 4: While operating in 32-bit mode, this bit must be cleared on odd numbered timers to enable the 32-bit timer in Idle mode.

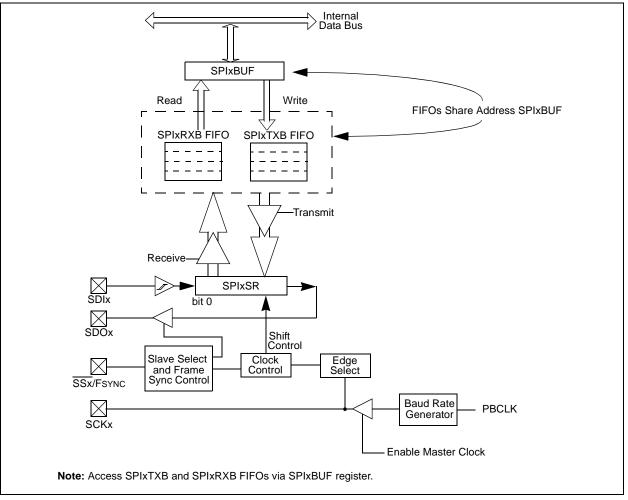

# 18.0 SERIAL PERIPHERAL INTERFACE (SPI)

Note: This data sheet summarizes the features of the PIC32MX5XX/6XX/7XX family of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to Section 23. "Serial Peripheral Interface (SPI)" (DS60001106) in the "PIC32 Family Reference Manual", which is available from the Microchip web site (www.microchip.com/PIC32).

The SPI module is a synchronous serial interface that is useful for communicating with external peripherals and other microcontroller devices. These peripheral devices may be Serial EEPROMs, Shift registers, display drivers, Analog-to-Digital Converters, etc. The PIC32 SPI module is compatible with Motorola<sup>®</sup> SPI and SIOP interfaces. The following are some of the key features of the SPI module:

- Master mode and Slave mode support

- · Four different clock formats

- Enhanced Framed SPI protocol support

- User-configurable 8-bit, 16-bit and 32-bit data width

- Separate SPI FIFO buffers for receive and transmit

FIFO buffers act as 4/8/16-level deep FIFOs

- based on 32/16/8-bit data width

Programmable interrupt event on every 8-bit, 16-bit and 32-bit data transfer

- Operation during Sleep and Idle modes

- Fast bit manipulation using CLR, SET and INV registers

# PIC32MX5XX/6XX/7XX

### REGISTER 25-19: ETHMCOLFRM: ETHERNET CONTROLLER MULTIPLE COLLISION FRAMES STATISTICS REGISTER

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |  |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|--|--|

| 21.24        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |  |  |

| 31:24        | —                 | —                 | _                 | _                 | —                 | —                 | _                | —                |  |  |

| 23:16        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |  |  |

| 23.10        | —                 | —                 | _                 | _                 | —                 | —                 | _                | —                |  |  |

| 15:8         | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |

| 10.0         |                   | MCOLFRMCNT<15:8>  |                   |                   |                   |                   |                  |                  |  |  |

| 7.0          | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |

| 7:0          | MCOLFRMCNT<7:0>   |                   |                   |                   |                   |                   |                  |                  |  |  |

| Legend:           |                                                             |                      |                    |  |

|-------------------|-------------------------------------------------------------|----------------------|--------------------|--|

| R = Readable bit  | ble bit W = Writable bit U = Unimplemented bit, read as '0' |                      |                    |  |

| -n = Value at POR | '1' = Bit is set                                            | '0' = Bit is cleared | x = Bit is unknown |  |

#### bit 31-16 Unimplemented: Read as '0'

bit 15-0 **MCOLFRMCNT<15:0>:** Multiple Collision Frame Count bits Increment count for frames that were successfully transmitted after there was more than one collision.

**Note 1:** This register is only used for TX operations.

2: This register is automatically cleared by hardware after a read operation, unless the byte enables for bytes 0/1 are '0'.

**3:** It is recommended to use the SET, CLR, or INV registers to set or clear any bit in this register. Setting or clearing any bits in this register should only be done for debug/test purposes.

#### REGISTER 25-20: ETHFRMRXOK: ETHERNET CONTROLLER FRAMES RECEIVED OK STATISTICS REGISTER

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |  |  |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|--|--|--|

| 24.24        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |  |  |  |

| 31:24        | _                 | _                 | _                 | _                 | _                 | _                 | _                | —                |  |  |  |

| 00.40        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |  |  |  |

| 23:16        | _                 | _                 | _                 | _                 | _                 | _                 | _                | —                |  |  |  |

| 45.0         | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |  |

| 15:8         |                   | FRMRXOKCNT<15:8>  |                   |                   |                   |                   |                  |                  |  |  |  |

| 7.0          | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |  |

| 7:0          | FRMRXOKCNT<7:0>   |                   |                   |                   |                   |                   |                  |                  |  |  |  |

## Legend:

| 3                 |                  |                        |                    |  |

|-------------------|------------------|------------------------|--------------------|--|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, | read as '0'        |  |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared   | x = Bit is unknown |  |

#### bit 31-16 Unimplemented: Read as '0'

bit 15-0 FRMRXOKCNT<15:0>: Frames Received OK Count bits

Increment count for frames received successfully by the RX Filter. This count will not be incremented if there is a Frame Check Sequence (FCS) or Alignment error.

Note 1: This register is only used for RX operations.

- 2: This register is automatically cleared by hardware after a read operation, unless the byte enables for bytes 0/1 are '0'.

- **3:** It is recommended to use the SET, CLR, or INV registers to set or clear any bit in this register. Setting or clearing any bits in this register should only be done for debug/test purposes.

### REGISTER 25-25: EMAC1IPGT: ETHERNET CONTROLLER MAC BACK-TO-BACK INTERPACKET GAP REGISTER

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|

| 31:24        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 31.24        | —                 | —                 | _                 | _                 | _                 | —                 | —                | _                |

| 22:16        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 23:16        | —                 | —                 | —                 | _                 | _                 | —                 | _                | —                |

| 45.0         | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 15:8         |                   | _                 | _                 | _                 | _                 | —                 | _                | _                |

| 7.0          | U-0               | R/W-0             | R/W-0             | R/W-1             | R/W-0             | R/W-0             | R/W-1            | R/W-0            |

| 7:0          | _                 |                   |                   | B2                | BIPKTGP<6:(       | )>                |                  |                  |

#### Legend:

| Logona.           |                  |                        |                          |  |  |

|-------------------|------------------|------------------------|--------------------------|--|--|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, | emented bit, read as '0' |  |  |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared   | x = Bit is unknown       |  |  |

#### bit 31-7 Unimplemented: Read as '0'

#### bit 6-0 B2BIPKTGP<6:0>: Back-to-Back Interpacket Gap bits

This is a programmable field representing the nibble time offset of the minimum possible period between the end of any transmitted packet, to the beginning of the next. In Full-Duplex mode, the register value should be the desired period in nibble times minus 3. In Half-Duplex mode, the register value should be the desired period in nibble times minus 6. In Full-Duplex the recommended setting is 0x15 (21d), which represents the minimum IPG of 0.96  $\mu$ s (in 100 Mbps) or 9.6  $\mu$ s (in 10 Mbps). In Half-Duplex mode, the recommended setting is 0x12 (18d), which also represents the minimum IPG of 0.96  $\mu$ s (in 100 Mbps) or 9.6  $\mu$ s (in 100 Mbps) (in 100 Mbps) or 9.6  $\mu$ s (in 100 Mbps) (in 100 Mbps) (in 100 Mbps) or 9.6  $\mu$ s (in 100 Mbps) (in

**Note:** Both 16-bit and 32-bit accesses are allowed to these registers (including the SET, CLR and INV registers). 8-bit accesses are not allowed and are ignored by the hardware.

## REGISTER 29-3: DEVCFG2: DEVICE CONFIGURATION WORD 2 (CONTINUED)

- bit 2-0 **FPLLIDIV<2:0>:** PLL Input Divider bits

- 111 = 12x divider

- 110 = 10x divider

- 101 = 6x divider

- 100 = 5x divider

- 011 = 4x divider

- 010 = 3x divider

- 001 = 2x divider

- 000 = 1x divider

| REGISTE | ER 29-4: D | DEVCFG3: DE | EVICE CON | FIGURATIO | N WORD 3 |  |

|---------|------------|-------------|-----------|-----------|----------|--|

|         |            |             |           |           |          |  |

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2     | Bit<br>25/17/9/1      | Bit<br>24/16/8/0      |  |  |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-----------------------|-----------------------|-----------------------|--|--|

| 04-04        | R/P               | R/P               | r-1               | r-1               | r-1               | R/P                   | R/P                   | R/P                   |  |  |

| 31:24        | FVBUSONIO         | FUSBIDIO          | _                 | —                 | —                 | FCANIO <sup>(1)</sup> | FETHIO <sup>(2)</sup> | FMIIEN <sup>(2)</sup> |  |  |

| 23:16        | r-1               | r-1               | r-1               | r-1               | r-1               | R/P                   | R/P                   | R/P                   |  |  |

| 23.10        | —                 | —                 | —                 | —                 | —                 | FSRSSEL<2:0>          |                       |                       |  |  |

| 45.0         | R/P               | R/P               | R/P               | R/P               | R/P               | R/P                   | R/P                   | R/P                   |  |  |

| 15:8         | USERID<15:8>      |                   |                   |                   |                   |                       |                       |                       |  |  |

| 7.0          | R/P               | R/P               | R/P               | R/P               | R/P               | R/P                   | R/P                   | R/P                   |  |  |

| 7:0          | USERID<7:0>       |                   |                   |                   |                   |                       |                       |                       |  |  |

| Legend:           | r = Reserved bit | P = Programmable bit                   |  |  |

|-------------------|------------------|----------------------------------------|--|--|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read as '0'     |  |  |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared x = Bit is unknow |  |  |

1 = VBUSON pin is controlled by the USB module 0 = VBUSON pin is controlled by the port function

bit 30

FUSBIDIO: USB USBID Selection bit 1 = USBID pin is controlled by the USB module 0 = USBID pin is controlled by the port function

bit 29-27

Reserved: Write '1'

bit 26

FCANIO: CAN I/O Pin Selection bit<sup>(1)</sup> 1 = Default CAN I/O Pins 0 = Alternate CAN I/O Pins

bit 25

FETHIO: Ethernet I/O Pins

1 = Default Ethernet I/O Pins

FVBUSONIO: USB VBUSON Selection bit

- 0 =Alternate Ethernet I/O Pins

- bit 24 FMIIEN: Ethernet MII Enable bit<sup>(2)</sup>

- 1 = MII is enabled

- 0 = RMII is enabled

- bit 23-19 Reserved: Write '1'

- bit 18-16 FSRSSEL<2:0>: SRS Select bits

- 111 = Assign Interrupt Priority 7 to a shadow register set

- 110 = Assign Interrupt Priority 6 to a shadow register set

- •

bit 31

- 001 = Assign Interrupt Priority 1 to a shadow register set

000 = All interrupt priorities are assigned to a shadow register set

- bit 15-0 **USERID<15:0>:** User ID bits This is a 16-bit value that is user-defined and is readable via ICSP<sup>™</sup> and JTAG.

- Note 1: This bit is Reserved and reads '1' on PIC32MX664/675/695 devices.

- 2: This bit is Reserved and reads '1' on PIC32MX534/564/575 devices.

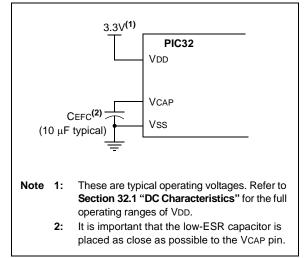

# 29.2 On-Chip Voltage Regulator

All PIC32MX5XX/6XX/7XX devices' core and digital logic are designed to operate at a nominal 1.8V. To simplify system designs, most devices in the PIC32MX-5XX/6XX/7XX family incorporate an on-chip regulator providing the required core logic voltage from VDD.

A low-ESR capacitor (such as tantalum) must be connected to the VCAP pin (see Figure 29-1). This helps to maintain the stability of the regulator. The recommended value for the filter capacitor is provided in **Section 32.1 "DC Characteristics"**.

Note: It is important that the low-ESR capacitor is placed as close as possible to the VCAP pin.

# 29.2.1 ON-CHIP REGULATOR AND POR

It takes a fixed delay for the on-chip regulator to generate an output. During this time, designated as TPU, code execution is disabled. TPU is applied every time the device resumes operation after any power-down, including Sleep mode.

## 29.2.2 ON-CHIP REGULATOR AND BOR

PIC32MX5XX/6XX/7XX devices also have a simple brown-out capability. If the voltage supplied to the regulator is inadequate to maintain a regulated level, the regulator Reset circuitry will generate a Brown-out Reset (BOR). This event is captured by the BOR flag bit (RCON<1>). The brown-out voltage levels are specified in **Section 32.1 "DC Characteristics"**.

# FIGURE 29-1: CONNECTIONS FOR THE ON-CHIP REGULATOR

## 29.3 **Programming and Diagnostics**

PIC32MX5XX/6XX/7XX devices provide a complete range of programming and diagnostic features that can increase the flexibility of any application using them. These features allow system designers to include:

- Simplified field programmability using two-wire In-Circuit Serial Programming<sup>™</sup> (ICSP<sup>™</sup>) interfaces

- Debugging using ICSP

- Programming and debugging capabilities using the EJTAG extension of JTAG

- JTAG boundary scan testing for device and board diagnostics

PIC32 devices incorporate two programming and diagnostic modules, and a trace controller, that provide a range of functions to the application developer.

FIGURE 29-2:

PROGRAMMING, DEBUGGING, AND TRACE PORTS BLOCK DIAGRAM

| DC CHA        | RACTER | ISTICS                                                  | $\begin{array}{l} \mbox{Standard Operating Conditions: 2.3V to 3.6V} \\ \mbox{(unless otherwise stated)} \\ \mbox{Operating temperature} & -40^\circ C \leq TA \leq +85^\circ C \mbox{ for Industrial} \\ -40^\circ C \leq TA \leq +105^\circ C \mbox{ for V-Temp} \end{array}$ |                        |          |       |                                                   |

|---------------|--------|---------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------|----------|-------|---------------------------------------------------|

| Param.<br>No. | Symbol | Characteristics                                         | Min.                                                                                                                                                                                                                                                                            | Typical <sup>(1)</sup> | Max.     | Units | Conditions                                        |

|               | VIL    | Input Low Voltage                                       |                                                                                                                                                                                                                                                                                 |                        |          |       |                                                   |

| DI10          |        | I/O Pins:                                               |                                                                                                                                                                                                                                                                                 |                        |          |       |                                                   |

|               |        | with TTL Buffer                                         | Vss                                                                                                                                                                                                                                                                             | —                      | 0.15 Vdd | V     |                                                   |

|               |        | with Schmitt Trigger Buffer                             | Vss                                                                                                                                                                                                                                                                             | —                      | 0.2 Vdd  | V     |                                                   |

| DI15          |        | MCLR <sup>(2)</sup>                                     | Vss                                                                                                                                                                                                                                                                             | —                      | 0.2 Vdd  | V     |                                                   |

| DI16          |        | OSC1 (XT mode)                                          | Vss                                                                                                                                                                                                                                                                             | —                      | 0.2 Vdd  | V     | (Note 4)                                          |

| DI17          |        | OSC1 (HS mode)                                          | Vss                                                                                                                                                                                                                                                                             | —                      | 0.2 Vdd  | V     | (Note 4)                                          |

| DI18          |        | SDAx, SCLx                                              | Vss                                                                                                                                                                                                                                                                             | _                      | 0.3 Vdd  | V     | SMBus disabled<br>(Note 4)                        |

| DI19          |        | SDAx, SCLx                                              | Vss                                                                                                                                                                                                                                                                             | —                      | 0.8      | V     | SMBus enabled<br>(Note 4)                         |

|               | Vih    | Input High Voltage                                      |                                                                                                                                                                                                                                                                                 |                        |          |       |                                                   |

| DI20          |        | I/O Pins not 5V-tolerant <sup>(5)</sup>                 | 0.65 VDD                                                                                                                                                                                                                                                                        | —                      | Vdd      | V     | (Note 4,6)                                        |

|               |        | I/O Pins 5V-tolerant with<br>PMP <sup>(5)</sup>         | 0.25 VDD + 0.8V                                                                                                                                                                                                                                                                 | _                      | 5.5      | V     | (Note 4,6)                                        |

|               |        | I/O Pins 5V-tolerant <sup>(5)</sup>                     | 0.65 Vdd                                                                                                                                                                                                                                                                        | _                      | 5.5      | V     |                                                   |

| DI28          |        | SDAx, SCLx                                              | 0.65 Vdd                                                                                                                                                                                                                                                                        | —                      | 5.5      | V     | SMBus disabled (Note 4,6)                         |

| DI29          |        | SDAx, SCLx                                              | 2.1                                                                                                                                                                                                                                                                             | _                      | 5.5      | V     | SMBus enabled,<br>2.3V ≤ VPIN ≤ 5.5<br>(Note 4,6) |

| DI30          | ICNPU  | Change Notification Pull-up Current                     | —                                                                                                                                                                                                                                                                               | —                      | -50      | μA    | VDD = 3.3V, VPIN = VSS<br>(Note 3,6)              |

| DI31          | ICNPD  | Change Notification<br>Pull-down Current <sup>(4)</sup> | —                                                                                                                                                                                                                                                                               | 50                     | _        | μA    | VDD = 3.3V, VPIN = VDD                            |

### TABLE 32-8: DC CHARACTERISTICS: I/O PIN INPUT SPECIFICATIONS

**Note 1:** Data in "Typical" column is at 3.3V, 25°C unless otherwise stated. Parameters are for design guidance only and are not tested.

- 2: The leakage current on the MCLR pin is strongly dependent on the applied voltage level. The specified levels represent normal operating conditions. Higher leakage current may be measured at different input voltages.

- **3:** Negative current is defined as current sourced by the pin.

- 4: This parameter is characterized, but not tested in manufacturing.

- 5: See the "Device Pin Tables" section for the 5V-tolerant pins.

- 6: The VIH specification is only in relation to externally applied inputs and not with respect to the user-selectable pull-ups. Externally applied high impedance or open drain input signals utilizing the PIC32 internal pullups are guaranteed to be recognized as a logic "high" internally to the PIC32 device, provided that the external load does not exceed the maximum value of ICNPU.

- 7: VIL source < (VSS 0.3). Characterized but not tested.

- 8: VIH source > (VDD + 0.3) for non-5V tolerant pins only.

- **9:** Digital 5V tolerant pins do not have an internal high side diode to VDD, and therefore, cannot tolerate any "positive" input injection current.

- 10: Injection currents > | 0 | can affect the ADC results by approximately 4 to 6 counts (i.e., VIH Source > (VDD + 0.3) or VIL source < (VSS 0.3)).</p>

- 11: Any number and/or combination of I/O pins not excluded under IICL or IICH conditions are permitted provided the "absolute instantaneous" sum of the input injection currents from all pins do not exceed the specified limit. If Note 7, IICL = (((Vss 0.3) VIL source) / Rs). If Note 8, IICH = ((IICH source (VDD + 0.3)) / RS). RS = Resistance between input source voltage and device pin. If (Vss 0.3) ≤ VSOURCE ≤ (VDD + 0.3), injection current = 0.

## TABLE 32-13: COMPARATOR SPECIFICATIONS

| DC CHA        |        | STICS                                 | $ \begin{array}{ l l l l l l l l l l l l l l l l l l l$ |         |      |       |                                                                                        |

|---------------|--------|---------------------------------------|---------------------------------------------------------|---------|------|-------|----------------------------------------------------------------------------------------|

| Param.<br>No. | Symbol | Characteristics                       | Min.                                                    | Typical | Max. | Units | Comments                                                                               |

| D300          | Vioff  | Input Offset Voltage                  | —                                                       | ±7.5    | ±25  | mV    | Avdd = Vdd,<br>Avss = Vss                                                              |

| D301          | VICM   | Input Common Mode Voltage             | 0                                                       | _       | Vdd  | V     | Avdd = Vdd,<br>Avss = Vss<br>(Note 2)                                                  |

| D302          | CMRR   | Common Mode Rejection Ratio           | 55                                                      | —       | _    | dB    | Max VICM = (VDD - 1)V<br>(Note 2)                                                      |

| D303          | Tresp  | Response Time                         | —                                                       | 150     | 400  | ns    | AVDD = VDD,<br>AVss = Vss<br>(Notes 1, 2)                                              |

| D304          | ON2ov  | Comparator Enabled to Output<br>Valid | —                                                       |         | 10   | μs    | Comparator module is<br>configured before setting<br>the comparator ON bit<br>(Note 2) |

| D305          | IVref  | Internal Voltage Reference            | 0.57                                                    | 0.6     | 0.63 | V     | For devices without<br>BGSEL<1:0>                                                      |

|               |        |                                       | 1.14                                                    | 1.2     | 1.26 | V     | BGSEL<1:0> = 00                                                                        |

|               |        |                                       | 0.57                                                    | 0.6     | 0.63 | V     | BGSEL<1:0> = 01                                                                        |

**Note 1:** Response time measured with one comparator input at (VDD – 1.5)/2, while the other input transitions from Vss to VDD.

2: These parameters are characterized but not tested.

**3:** The Comparator module is functional at VBORMIN < VDD < VDDMIN, but with degraded performance. Unless otherwise stated, module functionality is tested, but not characterized.

# PIC32MX5XX/6XX/7XX

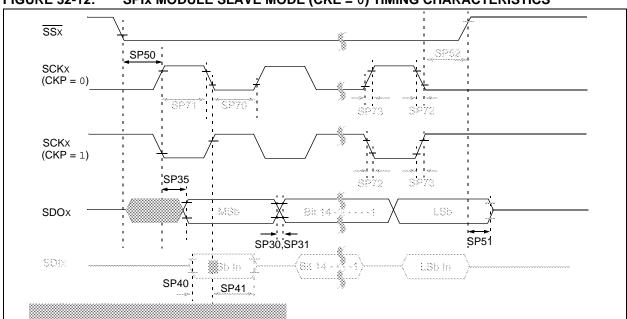

#### FIGURE 32-12: SPIX MODULE SLAVE MODE (CKE = 0) TIMING CHARACTERISTICS

#### TABLE 32-30: SPIX MODULE SLAVE MODE (CKE = 0) TIMING REQUIREMENTS

| АС СНА        | ARACTERIS             | STICS                                                               | $\begin{tabular}{lllllllllllllllllllllllllllllllllll$ |                     |      |       |                    |

|---------------|-----------------------|---------------------------------------------------------------------|-------------------------------------------------------|---------------------|------|-------|--------------------|

| Param.<br>No. | Symbol                | Characteristics <sup>(1)</sup>                                      | Min.                                                  | Тур. <sup>(2)</sup> | Max. | Units | Conditions         |

| SP70          | TscL                  | SCKx Input Low Time <sup>(3)</sup>                                  | Тѕск/2                                                | _                   |      | ns    | —                  |

| SP71          | TscH                  | SCKx Input High Time <sup>(3)</sup>                                 | Tsck/2                                                | _                   |      | ns    | —                  |

| SP72          | TscF                  | SCKx Input Fall Time                                                | —                                                     | —                   | _    | ns    | See parameter DO32 |

| SP73          | TscR                  | SCKx Input Rise Time                                                | —                                                     | —                   | _    | ns    | See parameter DO31 |

| SP30          | TDOF                  | SDOx Data Output Fall Time <sup>(4)</sup>                           | —                                                     | _                   | _    | ns    | See parameter DO32 |

| SP31          | TdoR                  | SDOx Data Output Rise Time <sup>(4)</sup>                           | —                                                     | _                   | _    | ns    | See parameter DO31 |

| SP35          | TscH2doV,             | SDOx Data Output Valid after                                        | —                                                     | —                   | 15   | ns    | VDD > 2.7V         |

|               | TscL2doV              | SCKx Edge                                                           | —                                                     | _                   | 20   | ns    | VDD < 2.7V         |

| SP40          | TDIV2SCH,<br>TDIV2SCL | Setup Time of SDIx Data Input to SCKx Edge                          | 10                                                    |                     |      | ns    |                    |

| SP41          | TscH2diL,<br>TscL2diL | Hold Time of SDIx Data Input to SCKx Edge                           | 10                                                    | —                   | _    | ns    | —                  |

| SP50          | TssL2scH,<br>TssL2scL | $\overline{\text{SSx}} \downarrow$ to SCKx $\uparrow$ or SCKx Input | 175                                                   |                     |      | ns    | —                  |

| SP51          | TssH2doZ              | SSx ↑ to SDOx Output<br>High-Impedance <sup>(3)</sup>               | 5                                                     | —                   | 25   | ns    | —                  |

| SP52          | TscH2ssH<br>TscL2ssH  | SSx after SCKx Edge                                                 | Тѕск + 20                                             | _                   |      | ns    | _                  |

Note 1: These parameters are characterized, but not tested in manufacturing.

2: Data in "Typical" column is at 3.3V, 25°C unless otherwise stated. Parameters are for design guidance only and are not tested.

**3:** The minimum clock period for SCKx is 40 ns.

4: Assumes 50 pF load on all SPIx pins.

# PIC32MX5XX/6XX/7XX

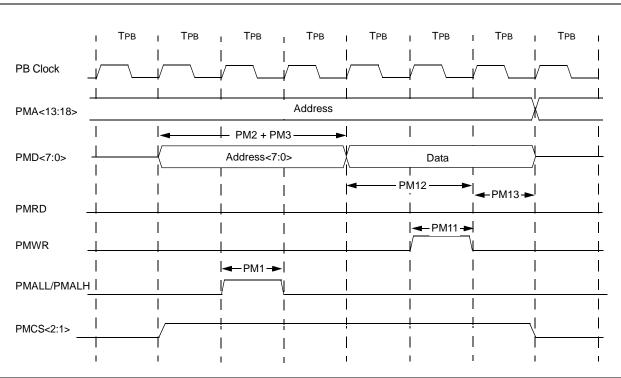

## FIGURE 32-27: PARALLEL MASTER PORT WRITE TIMING DIAGRAM

# TABLE 32-41: PARALLEL MASTER PORT WRITE TIMING REQUIREMENTS

| AC CHARACTERISTICS |         |                                                                           | $\begin{array}{l} \mbox{Standard Operating Conditions: 2.3V to 3.6V} \\ \mbox{(unless otherwise stated)} \\ \mbox{Operating temperature} & -40^\circ C \leq TA \leq +85^\circ C \mbox{ for Industrial} \\ & -40^\circ C \leq TA \leq +105^\circ C \mbox{ for V-Temp} \end{array}$ |         |      |       |            |

|--------------------|---------|---------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------|------|-------|------------|

| Param.<br>No.      | Symbol  | Characteristics <sup>(1)</sup>                                            | Min.                                                                                                                                                                                                                                                                              | Typical | Max. | Units | Conditions |

| PM11               | Twr     | PMWR Pulse Width                                                          | _                                                                                                                                                                                                                                                                                 | 1 Трв   |      | —     | _          |

| PM12               | TDVSU   | Data Out Valid before PMWR or<br>PMENB goes Inactive (data setup<br>time) | —                                                                                                                                                                                                                                                                                 | 2 Трв   | _    | —     | _          |

| PM13               | TDVHOLD | PMWR or PMEMB Invalid to Data<br>Out Invalid (data hold time)             | —                                                                                                                                                                                                                                                                                 | 1 Трв   |      | —     | —          |

**Note 1:** These parameters are characterized, but not tested in manufacturing.

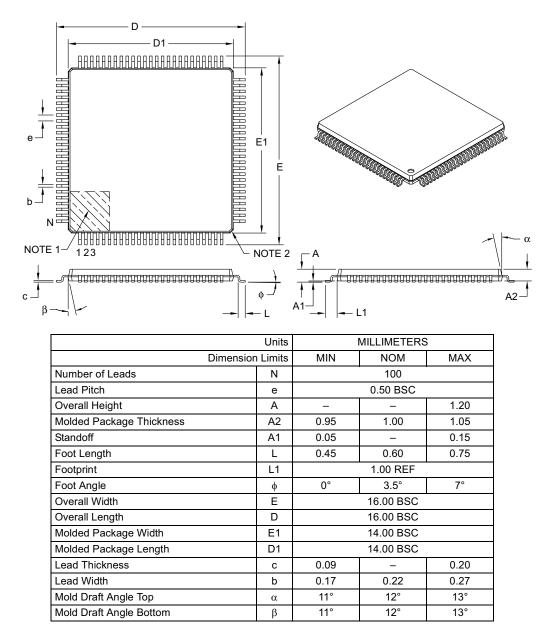

## 100-Lead Plastic Thin Quad Flatpack (PF) – 14x14x1 mm Body, 2.00 mm [TQFP]

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

#### Notes:

- 1. Pin 1 visual index feature may vary, but must be located within the hatched area.

- 2. Chamfers at corners are optional; size may vary.

- 3. Dimensions D1 and E1 do not include mold flash or protrusions. Mold flash or protrusions shall not exceed 0.25 mm per side.

- 4. Dimensioning and tolerancing per ASME Y14.5M.

- BSC: Basic Dimension. Theoretically exact value shown without tolerances.

REF: Reference Dimension, usually without tolerance, for information purposes only.

Microchip Technology Drawing C04-110B

# 64-Lead Plastic Quad Flat, No Lead Package (MR) – 9x9x0.9 mm Body [QFN] With 7.15 x 7.15 Exposed Pad [QFN]

Microchip Technology Drawing C04-149C Sheet 1 of 2