Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XE

| Product Status             | Active                                                                            |

|----------------------------|-----------------------------------------------------------------------------------|

| Core Processor             | MIPS32® M4K™                                                                      |

| Core Size                  | 32-Bit Single-Core                                                                |

| Speed                      | 80MHz                                                                             |

| Connectivity               | Ethernet, I <sup>2</sup> C, SPI, UART/USART, USB OTG                              |

| Peripherals                | Brown-out Detect/Reset, DMA, POR, PWM, WDT                                        |

| Number of I/O              | 85                                                                                |

| Program Memory Size        | 512KB (512K x 8)                                                                  |

| Program Memory Type        | FLASH                                                                             |

| EEPROM Size                | -                                                                                 |

| RAM Size                   | 64K x 8                                                                           |

| Voltage - Supply (Vcc/Vdd) | 2.3V ~ 3.6V                                                                       |

| Data Converters            | A/D 16x10b                                                                        |

| Oscillator Type            | Internal                                                                          |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                                 |

| Mounting Type              | Surface Mount                                                                     |

| Package / Case             | 100-TQFP                                                                          |

| Supplier Device Package    | 100-TQFP (12x12)                                                                  |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic32mx675f512lt-80i-pt |

|                            |                                                                                   |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

#### **Referenced Sources**

This device data sheet is based on the following individual chapters of the *"PIC32 Family Reference Manual"*. These documents should be considered as the general reference for the operation of a particular module or device feature.

- Note 1: To access the documents listed below, browse to the documentation section of the PIC32MX795F512L product page on the Microchip web site (www.microchip.com) or select a family reference manual section from the following list. In addition to parameters, features, and other documentation, the resulting page provides links to the related family

- Section 1. "Introduction" (DS60001127)

- Section 2. "CPU" (DS60001113)

- Section 4. "Prefetch Cache" (DS60001119)

- Section 3. "Memory Organization" (DS60001115)

reference manual sections.

- Section 5. "Flash Program Memory" (DS60001121)

- Section 6. "Oscillator Configuration" (DS60001112)

- Section 7. "Resets" (DS60001118)

- Section 8. "Interrupt Controller" (DS60001108)

- Section 9. "Watchdog Timer and Power-up Timer (DS60001114)

- Section 10. "Power-Saving Features" (DS60001130)

- Section 12. "I/O Ports" (DS60001120)

- Section 13. "Parallel Master Port (PMP)" (DS60001128)

- Section 14. "Timers" (DS60001105)

- Section 15. "Input Capture" (DS60001122)

- Section 16. "Output Capture" (DS60001111)

- Section 17. "10-bit Analog-to-Digital Converter (ADC)" (DS60001104)

- Section 19. "Comparator" (DS60001110)

- Section 20. "Comparator Voltage Reference (CVREF)" (DS60001109)

- Section 21. "Universal Asynchronous Receiver Transmitter (UART)" (DS60001107)

- Section 23. "Serial Peripheral Interface (SPI)" (DS60001106)

- Section 24. "Inter-Integrated Circuit (I2C)" (DS60001116)

- Section 27. "USB On-The-Go (OTG)" (DS60001126)

- Section 29. "Real-Time Clock and Calendar (RTCC)" (DS60001125)

- Section 31. "Direct Memory Access (DMA) Controller" (DS60001117)

- Section 32. "Configuration" (DS60001124)

- Section 33. "Programming and Diagnostics" (DS60001129)

- Section 34. "Controller Area Network (CAN)" (DS60001154)

- Section 35. "Ethernet Controller" (DS60001155)

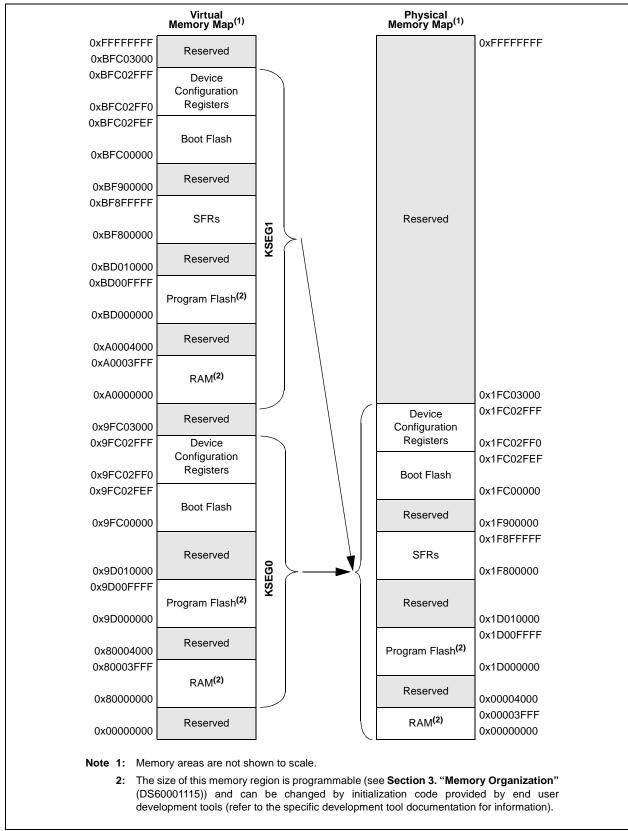

# FIGURE 4-2: MEMORY MAP ON RESET FOR PIC32MX534F064H AND PIC32MX534F064L DEVICES

# TABLE 7-6: INTERRUPT REGISTER MAP FOR PIC32MX664F064L, PIC32MX664F128L, PIC32MX675F256L, PIC32MX675F512L AND PIC32MX695F512L DEVICES (CONTINUED)

| ess                         |                                 |           |       |       |       |       |             |       |             | Bi                    | its  |      |      |             |             |             |             |                      |            |       |       |      |

|-----------------------------|---------------------------------|-----------|-------|-------|-------|-------|-------------|-------|-------------|-----------------------|------|------|------|-------------|-------------|-------------|-------------|----------------------|------------|-------|-------|------|

| Virtual Address<br>(BF88_#) | Register<br>Name <sup>(1)</sup> | Bit Range | 31/15 | 30/14 | 29/13 | 28/12 | 27/11       | 26/10 | 25/9        | 24/8                  | 23/7 | 22/6 | 21/5 | 20/4        | 19/3        | 18/2        | 17/1        | 16/0                 | All Resets |       |       |      |

| 10D0                        | IPC4                            | 31:16     | _     | —     | -     |       | INT4IP<2:0> |       | INT4IS<1:0> |                       | _    | —    | -    |             | OC4IP<2:0>  |             | OC4IS       | 6<1:0>               | 0000       |       |       |      |

| 1000                        | IPC4                            | 15:0      | _     | _     | _     |       | IC4IP<2:0>  |       | IC4IS       | <1:0>                 | _    | _    | _    |             | T4IP<2:0>   |             | T4IS-       | <1:0>                | 0000       |       |       |      |

| 4050                        | IPC5                            | 31:16     | —     | _     | _     |       | SPI1IP<2:0> |       | SPI1IS      | 6<1:0>                | _    | _    | _    |             | OC5IP<2:0>  |             | OC5IS       | S<1:0>               | 0000       |       |       |      |

| 10E0                        | IPC5                            | 15:0      | _     | _     | _     |       | IC5IP<2:0>  |       | IC5IS       | <1:0>                 | -    |      | _    |             | T5IP<2:0>   |             | T5IS-       | <1:0>                | 0000       |       |       |      |

|                             |                                 | 31:16     | _     | _     | _     |       | AD1IP<2:0>  |       | AD1IS       | S<1:0>                | _    | _    | _    |             | CNIP<2:0>   |             | CNIS        | <1:0>                | 0000       |       |       |      |

| 10F0                        | IPC6                            |           |       |       |       |       |             |       |             |                       |      |      |      |             | U1IP<2:0>   |             | U1IS-       | <1:0>                |            |       |       |      |

| IUFU                        | IFCO                            | 15:0      | —     | —     | —     |       | I2C1IP<2:0> |       | 12C115      | S<1:0>                | —    | —    | —    | SPI3IP<2:0> |             | SPI3IS      | S<1:0>      | 0000                 |            |       |       |      |

|                             |                                 |           |       |       |       |       |             |       |             |                       |      |      |      | I2C3IP<2:0> |             | I2C3IS<1:0> |             |                      |            |       |       |      |

|                             |                                 |           |       |       |       |       | U3IP<2:0>   |       | U3IS        | <1:0>                 |      |      |      |             |             |             |             |                      |            |       |       |      |

| 1100                        | IPC7                            | 31:16     | —     | —     | —     |       | SPI2IP<2:0> |       | SPI2IS      | S<1:0>                | —    | -    | —    | (           | CMP2IP<2:0  | >           | CMP2IS<1:0> |                      | 0000       |       |       |      |

| 1100                        | 11 07                           |           |       |       |       |       | I2C4IP<2:0> |       | 12C415      | S<1:0>                |      |      |      |             |             |             |             |                      |            |       |       |      |

|                             |                                 | 15:0      | _     |       |       | (     | CMP1IP<2:0  | >     | CMP1I       | S<1:0>                | _    | _    |      | PMPIP<2:0>  |             | PMPIS<1:0>  |             | 0000                 |            |       |       |      |

|                             |                                 | 31:16     | _     |       |       | F     | RTCCIP<2:0  | >     | RTCCIS<1:0> |                       | _    | _    |      | I           | FSCMIP<2:0  | >           | FSCMI       | S<1:0>               | 0000       |       |       |      |

| 1110                        | IPC8                            |           |       |       |       |       |             |       |             |                       |      |      |      |             | U2IP<2:0>   |             | U2IS-       | <1:0>                |            |       |       |      |

| 1110                        | 11 00                           | 15:0      | —     | —     | —     |       | I2C2IP<2:0> |       | 12C215      | 6<1:0>                | —    | —    | —    |             | SPI4IP<2:0> |             | SPI4IS      | S<1:0>               | 0000       |       |       |      |

|                             |                                 |           |       |       |       |       |             |       |             |                       |      |      |      |             | I2C5IP<2:0> |             | 12C515      | S<1:0>               |            |       |       |      |

| 1120                        | IPC9                            | 31:16     | _     | _     |       |       | DMA3IP<2:0  |       | DMA3I       | S<1:0>                | _    |      |      |             | DMA2IP<2:0  |             | DMA2I       | S<1:0>               | 0000       |       |       |      |

| 1120                        | 11 03                           | 15:0      | _     | _     |       |       | DMA1IP<2:0  |       | DMA1I       |                       | _    |      |      |             | DMA0IP<2:0  |             | DMA0I       | S<1:0>               | 0000       |       |       |      |

| 1130                        | IPC10                           | 31:16     | —     | —     | —     | DI    | MA7IP<2:0>  | (2)   | DMA7IS      | i<1:0> <sup>(2)</sup> | —    | _    | —    | D           | MA6IP<2:0>  | (2)         | DMA6IS      | <1:0> <sup>(2)</sup> | 0000       |       |       |      |

| 1130                        | 11 010                          | 15:0      | —     | —     | —     | DI    | MA5IP<2:0>  | (2)   | DMA5IS      | i<1:0> <sup>(2)</sup> | _    | _    | —    | D           | MA4IP<2:0>  | (2)         | DMA4IS      | <1:0> <sup>(2)</sup> | 0000       |       |       |      |

| 1140                        | IPC11                           | 31:16     | —     | -     | _     | _     | _           |       | _           |                       |      |      | _    |             |             | —           |             | 0000                 |            |       |       |      |

| 1140                        | IFCII                           | 15:0      | —     | —     | —     |       | USBIP<2:0>  |       | USBIS       | S<1:0>                | _    | _    | —    | FCEIP<2:0>  |             | FCEIS       | <1:0>       | 0000                 |            |       |       |      |

| 1150                        | IPC12                           | 31:16     | _     | _     | -     |       | U5IP<2:0>   |       | U5IS-       | <1:0>                 | _    |      | -    | U6IP<2:0>   |             | U6IP<2:0>   |             | U6IP<2:0>            |            | U6IS- | <1:0> | 0000 |

| 1150                        | IFUIZ                           | 15:0      | _     | -     | -     |       | U4IP<2:0>   |       | U4IS-       | <1:0>                 |      |      |      |             | ETHIP<2:0>  |             | ETHIS       | i<1:0>               | 0000       |       |       |      |

Legend: x = unknown value on Reset; -- = unimplemented, read as '0'. Reset values are shown in hexadecimal.

Note 1: Except where noted, all registers in this table have corresponding CLR, SET and INV registers at their virtual addresses, plus offsets of 0x4, 0x8 and 0xC, respectively. See Section 12.1.1 "CLR, SET and INV Registers" for more information.

2: These bits are not available on PIC32MX664 devices.

3: This register does note have associated CLR, SET, and INV registers.

# PIC32MX5XX/6XX/7XX

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|

| 21.24        | R/W-0             | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 31:24        | CHEWEN            | —                 | _                 | —                 | —                 | -                 | —                | —                |

| 22:16        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 23:16        | -                 | —                 |                   | —                 | —                 |                   | —                | —                |

| 15:8         | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 15.0         |                   | —                 |                   | —                 | —                 |                   | —                | —                |

| 7.0          | U-0               | U-0               | U-0               | U-0               | R/W-0             | R/W-0             | R/W-0            | R/W-0            |

| 7:0          |                   |                   |                   | —                 |                   | CHEID             | X<3:0>           |                  |

#### REGISTER 9-2: CHEACC: CACHE ACCESS REGISTER

#### Legend:

| R = Readable bit  | W = Writable bit | U = Unimplemented bit | , read as '0'      |  |

|-------------------|------------------|-----------------------|--------------------|--|

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared  | x = Bit is unknown |  |

#### bit 31 CHEWEN: Cache Access Enable bits

- These bits apply to registers CHETAG, CHEMSK, CHEW0, CHEW1, CHEW2, and CHEW3.

- 1 = The cache line selected by CHEIDX<3:0> is writeable

- 0 = The cache line selected by CHEIDX<3:0> is not writeable

- bit 30-4 **Unimplemented:** Write '0'; ignore read

#### bit 3-0 CHEIDX<3:0>: Cache Line Index bits

The value selects the cache line for reading or writing.

#### TABLE 10-3: DMA CHANNELS 0-7 REGISTER MAP (CONTINUED)

| ess                         |                                 |               |        |       |       |               |        |       |      | Bi     | ts       |        |        |        |         |        |        |        |            |

|-----------------------------|---------------------------------|---------------|--------|-------|-------|---------------|--------|-------|------|--------|----------|--------|--------|--------|---------|--------|--------|--------|------------|

| Virtual Address<br>(BF88_#) | Register<br>Name <sup>(1)</sup> | Bit Range     | 31/15  | 30/14 | 29/13 | 28/12         | 27/11  | 26/10 | 25/9 | 24/8   | 23/7     | 22/6   | 21/5   | 20/4   | 19/3    | 18/2   | 17/1   | 16/0   | All Resets |

| 3180                        | DCH1DSIZ                        | 31:16         | _      | -     | —     | _             | -      | -     | _    | —      | _        | _      | _      | —      | —       | _      | _      | _      | 0000       |

| 5100                        |                                 | 15:0          |        |       |       | -             |        |       | -    | CHDSIZ | <15:0>   |        |        | -      | -       |        |        |        | 0000       |

| 3190                        | DCH1SPTR                        | 31:16         | —      | —     | —     | —             | —      | —     | _    | —      | —        | —      | —      | —      | —       | —      | —      | —      | 0000       |

| 5150                        | Donnor IIX                      | 15:0          |        |       |       |               |        |       |      | CHSPTI | R<15:0>  |        |        |        |         |        |        |        | 0000       |

| 31A0                        | DCH1DPTR                        | 31:16         | —      | —     | —     | —             | —      | —     | —    | —      | —        | —      | —      | —      | —       | —      | —      | —      | 0000       |

| 5170                        |                                 |               |        |       |       |               |        |       |      | 0000   |          |        |        |        |         |        |        |        |            |

| 31B0                        | DCH1CSIZ                        | 31:16         | —      | —     | —     | —             | —      | —     | _    | —      | —        | —      | —      | —      | —       | —      | —      | —      | 0000       |

| 0100                        |                                 | 15:0          |        |       |       |               |        |       |      | CHCSIZ | 2<15:0>  |        |        |        |         |        |        |        | 0000       |

| 31C0                        | DCH1CPTR                        | 31:16         | _      | —     | —     | _             | —      | —     | —    | —      | _        | —      | —      | —      | —       | —      | —      | —      | 0000       |

| 0100                        |                                 | 15:0          |        |       |       |               |        |       |      | CHCPTI | R<15:0>  |        |        |        |         | -      | -      | -      | 0000       |

| 31D0                        | DCH1DAT                         | 31:16         | _      | _     | —     | _             | _      | _     | _    | —      | —        | —      | —      | —      | _       | —      | —      | —      | 0000       |

| 0120                        | Bonnbra                         | 15:0          | _      | _     | —     | _             | _      | _     | _    | —      |          |        |        | CHPDA  | \T<7:0> | -      | -      | -      | 0000       |

| 31E0                        | DCH2CON                         | 31:16         | —      | —     | —     | —             | —      | —     |      | —      | —        | —      | —      | —      | —       | —      | —      | —      | 0000       |

| 0120                        |                                 | 15:0          | CHBUSY | _     | —     | —             | _      | _     |      | CHCHNS | CHEN     | CHAED  | CHCHN  | CHAEN  | _       | CHEDET | CHPR   | l<1:0> | 0000       |

| 31E0                        | 31F0 DCH2ECON 31:16 CHAIRQ<7:0> |               |        |       |       |               |        | OOFF  |      |        |          |        |        |        |         |        |        |        |            |

| 511.0                       | DONZEOON                        | 15:0          |        |       |       | CHSIR         | Q<7:0> |       |      |        | CFORCE   | CABORT | PATEN  | SIRQEN | AIRQEN  | —      | —      | —      | FF00       |

| 3200                        | DCH2INT                         | 31:16         | _      | _     | —     | —             | _      | _     |      | —      | CHSDIE   | CHSHIE | CHDDIE | CHDHIE | CHBCIE  | CHCCIE | CHTAIE | CHERIE | 0000       |

| 5200                        | DONZINI                         | 15:0          | —      | —     | —     | —             | —      | —     | _    | —      | CHSDIF   | CHSHIF | CHDDIF | CHDHIF | CHBCIF  | CHCCIF | CHTAIF | CHERIF | 0000       |

| 3210                        | DCH2SSA                         | 31:16<br>15:0 |        |       |       |               |        |       |      | CHSSA  | <31:0>   |        |        |        |         |        |        |        | 0000       |

| 3220                        | DCH2DSA                         | 31:16<br>15:0 |        |       |       |               |        |       |      | CHDSA  | <31:0>   |        |        |        |         |        |        |        | 0000       |

|                             |                                 | 31:16         |        | _     | _     | _             | _      | _     | _    |        | _        | _      | _      | _      |         |        | _      |        | 0000       |

| 3230                        | DCH2SSIZ                        | 15:0          |        |       |       |               |        |       |      | CHSSIZ |          |        |        |        |         |        |        |        | 0000       |

|                             |                                 | 31:16         | _      | _     | _     | _             | _      | _     | _    | _      | _        | _      | _      | _      |         | _      | _      | _      | 0000       |

| 3240                        | DCH2DSIZ                        | 15:0          |        |       |       |               |        |       |      | CHDSIZ |          |        |        |        |         |        |        |        | 0000       |

|                             |                                 | 31:16         | _      | _     | _     | _             | _      | _     | _    | _      | _        | _      | _      | _      | _       | _      | _      | _      | 0000       |

| 3250                        | DCH2SPTR                        | 15:0          |        |       |       |               |        |       |      | CHSPTI |          |        |        |        |         |        |        |        | 0000       |

| <u> </u>                    |                                 | 31:16         | _      | _     | _     | _             | _      | _     | _    | _      |          | _      | _      | _      |         |        | _      |        | 0000       |

| 3260                        | DCH2DPTR                        | 15:0          |        |       |       |               |        |       |      | CHDPTI | 8<15.0>  |        |        |        |         |        |        |        | 0000       |

|                             |                                 | 31:16         | _      |       |       |               |        |       | _    |        |          | _      |        | _      | _       |        | _      | _      | 0000       |

| 3270                        | DCH2CSIZ                        | 15:0          |        |       |       |               |        |       |      | CHCSIZ |          |        |        |        |         |        |        |        | 0000       |

|                             |                                 |               |        |       |       |               |        |       |      | 010312 | .< 10.02 |        |        |        |         |        |        |        |            |

| 3280                        | DCH2CPTR                        | 31:16         | _      | _     | —     | —             | _      | _     | _    | —      | _        | —      | —      | —      | —       | _      | _      | _      | 0000       |

|                             |                                 | 15:0          |        |       |       | n, tead as ,0 |        |       |      | CHCPTI | ۲<15:0>  |        |        |        |         |        |        |        | 0000       |

Legend: x = unknown value on Reset; - = unimplemented, read as '0'. Reset values are shown in hexadecimal.

Note 1: All registers in this table have corresponding CLR, SET and INV registers at their virtual addresses, plus offsets of 0x4, 0x8 and 0xC, respectively. See Section 12.1.1 "CLR, SET and INV Registers" for more information.

2: DMA channels 4-7 are not available on PIC32MX534/564/664/764 devices.

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5    | Bit<br>28/20/12/4    | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1       | Bit<br>24/16/8/0 |

|--------------|-------------------|-------------------|----------------------|----------------------|-------------------|-------------------|------------------------|------------------|

| 31:24        | U-0               | U-0               | U-0                  | U-0                  | U-0               | U-0               | U-0                    | U-0              |

| 31.24        |                   |                   | —                    |                      | —                 | —                 | —                      | —                |

| 23:16        | U-0               | U-0               | U-0                  | U-0                  | U-0               | U-0               | U-0                    | U-0              |

| 23.10        |                   |                   | —                    |                      | —                 | —                 | —                      | —                |

| 15:8         | U-0               | U-0               | U-0                  | U-0                  | U-0               | U-0               | U-0                    | U-0              |

| 15.0         | _                 | _                 | —                    | _                    | _                 |                   | —                      | _                |

|              | R/WC-0, HS        | R/WC-0, HS        | R/WC-0, HS           | R/WC-0, HS           | R/WC-0, HS        | R/WC-0, HS        | R/WC-0, HS             | R/WC-0, HS       |

| 7:0          | BTSEF             | BMXEF             | DMAEF <sup>(1)</sup> | BTOEF <sup>(2)</sup> | DFN8EF            | CRC16EF           | CRC5EF <sup>(4)</sup>  | PIDEF            |

|              | DIGLI             | DIVIALI           |                      | DIOLIN               |                   | ONCIULI           | EOFEF <sup>(3,5)</sup> | TIDLI            |

#### REGISTER 11-8: U1EIR: USB ERROR INTERRUPT STATUS REGISTER

| Legend:           | WC = Write '1' to clear | HS = Hardware Settable bit |                    |  |  |  |

|-------------------|-------------------------|----------------------------|--------------------|--|--|--|

| R = Readable bit  | W = Writable bit        | U = Unimplemented bit, re  | ead as '0'         |  |  |  |

| -n = Value at POR | '1' = Bit is set        | '0' = Bit is cleared       | x = Bit is unknown |  |  |  |

- bit 31-8 Unimplemented: Read as '0'

bit 7 BTSEF: Bit Stuff Error Flag bit 1 = Packet is rejected due to bit stuff error 0 = Packet is accepted

bit 6 BMXEF: Bus Matrix Error Flag bit 1 = Invalid base address of the BDT, or the address of an individual buffer pointed to by a BDT entry 0 = No address error

bit 5 DMAEF: DMA Error Flag bit<sup>(1)</sup> 1 = USB DMA error condition detected 0 = No DMA error

- bit 4 **BTOEF:** Bus Turnaround Time-Out Error Flag bit<sup>(2)</sup> 1 = Bus turnaround time-out has occurred

- 0 = No bus turnaround time-out

- bit 3 DFN8EF: Data Field Size Error Flag bit

1 = Data field received is not an integral number of bytes

0 = Data field received is an integral number of bytes

- bit 2 CRC16EF: CRC16 Failure Flag bit

- 1 = Data packet is rejected due to CRC16 error

0 = Data packet is accepted

- bit 1 CRC5EF: CRC5 Host Error Flag bit<sup>(4)</sup> 1 = Token packet is rejected due to CRC5 error 0 = Token packet is accepted EOFEF: EOF Error Flag bit<sup>(3,5)</sup> 1 = EOF error condition is detected

- 0 = No EOF error condition

- bit 0 PIDEF: PID Check Failure Flag bit

- 1 = PID check is failed

- 0 = PID check is passed

- **Note 1:** This type of error occurs when the module's request for the DMA bus is not granted in time to service the module's demand for memory, resulting in an overflow or underflow condition, and/or the allocated buffer size is not sufficient to store the received data packet causing it to be truncated.

- 2: This type of error occurs when more than 16-bit-times of Idle from the previous End-of-Packet (EOP) has elapsed.

- **3:** This type of error occurs when the module is transmitting or receiving data and the SOF counter has reached zero.

- 4: Device mode.

- 5: Host mode.

#### I2CxSTAT: I<sup>2</sup>C STATUS REGISTER (CONTINUED) REGISTER 19-2: **D\_A:** Data/Address bit (when operating as I<sup>2</sup>C slave) bit 5 This bit is cleared by hardware upon a device address match, and is set by hardware by reception of the slave byte. 1 = Indicates that the last byte received was data 0 = Indicates that the last byte received was device address bit 4 P: Stop bit This bit is set or cleared by hardware when a Start, Repeated Start, or Stop condition is detected. 1 = Indicates that a Stop bit has been detected last 0 = Stop bit was not detected last bit 3 S: Start bit This bit is set or cleared by hardware when a Start, Repeated Start, or Stop condition is detected. 1 = Indicates that a Start (or Repeated Start) bit has been detected last 0 = Start bit was not detected last **R\_W:** Read/Write Information bit (when operating as I<sup>2</sup>C slave) bit 2 This bit is set or cleared by hardware after reception of an I<sup>2</sup>C device address byte. 1 = Read – indicates data transfer is output from slave 0 = Write - indicates data transfer is input to slave **RBF:** Receive Buffer Full Status bit bit 1 This bit is set by hardware when the I2CxRCV register is written with a received byte, and is cleared by hardware when software reads I2CxRCV. 1 = Receive complete, I2CxRCV is full 0 = Receive not complete, I2CxRCV is empty bit 0 TBF: Transmit Buffer Full Status bit This bit is set by hardware when software writes to the I2CxTRN register, and is cleared by hardware upon completion of data transmission.

1 = Transmit in progress, I2CxTRN is full

0 = Transmit complete, I2CxTRN is empty

### TABLE 23-1: ADC REGISTER MAP (CONTINUED)

| ess                         |                  |               |       |                                    |       |       |       |       |        | Bi          | ts        |          |      |      |      |      |      |      |            |

|-----------------------------|------------------|---------------|-------|------------------------------------|-------|-------|-------|-------|--------|-------------|-----------|----------|------|------|------|------|------|------|------------|

| Virtual Address<br>(BF80_#) | Register<br>Name | Bit Range     | 31/15 | 30/14                              | 29/13 | 28/12 | 27/11 | 26/10 | 25/9   | 24/8        | 23/7      | 22/6     | 21/5 | 20/4 | 19/3 | 18/2 | 17/1 | 16/0 | All Resets |

| 9120                        | ADC1BUFB         | 31:16<br>15:0 |       | ADC Result Word B (ADC1BUFB<31:0>) |       |       |       |       |        |             |           |          |      | 0000 |      |      |      |      |            |

| 9130                        | ADC1BUFC         | 31:16<br>15:0 |       | ADC Result Word C (ADC1BUFC<31:0>) |       |       |       |       |        |             |           |          |      | 0000 |      |      |      |      |            |

| 9140                        | ADC1BUFD         | 31:16<br>15:0 |       |                                    |       |       |       |       | ADC Re | sult Word D | (ADC1BUFE | 0<31:0>) |      |      |      |      |      |      | 0000       |

| 9150                        | ADC1BUFE         | 31:16<br>15:0 |       | ADC Result Word E (ADC1BUFE<31:0>) |       |       |       |       |        |             |           |          | 0000 |      |      |      |      |      |            |

| 9160                        | ADC1BUFF         | 31:16<br>15:0 |       | ADC Result Word F (ADC1BUFF<31:0>) |       |       |       |       |        |             |           |          |      |      |      |      |      |      |            |

= unimplemented, read as '0'. Reset values are shown in hexadecimal. Legend: x = unknown value on Reset

This register has corresponding CLR, SET and INV registers at their virtual addresses, plus offsets of 0x4, 0x8 and 0xC, respectively. See Section 12.1.1 "CLR, SET and INV Registers" for more information. Note 1:

#### REGISTER 24-3: CIINT: CAN INTERRUPT REGISTER (CONTINUED)

- bit 14 WAKIF: CAN Bus Activity Wake-up Interrupt Flag bit 1 = A bus wake-up activity interrupt has occurred 0 = A bus wake-up activity interrupt has not occurred CERRIF: CAN Bus Error Interrupt Flag bit bit 13 1 = A CAN bus error has occurred 0 = A CAN bus error has not occurred bit 12 SERRIF: System Error Interrupt Flag bit 1 = A system error occurred (typically an illegal address was presented to the system bus) 0 = A system error has not occurred bit 11 **RBOVIF:** Receive Buffer Overflow Interrupt Flag bit 1 = A receive buffer overflow has occurred 0 = A receive buffer overflow has not occurred bit 10-4 Unimplemented: Read as '0' MODIF: CAN Mode Change Interrupt Flag bit bit 3 1 = A CAN module mode change has occurred (OPMOD<2:0> has changed to reflect REQOP) 0 = A CAN module mode change has not occurred bit 2 CTMRIF: CAN Timer Overflow Interrupt Flag bit 1 = A CAN timer (CANTMR) overflow has occurred 0 = A CAN timer (CANTMR) overflow has not occurred bit 1 **RBIF:** Receive Buffer Interrupt Flag bit 1 = A receive buffer interrupt is pending 0 = A receive buffer interrupt is not pending bit 0 TBIF: Transmit Buffer Interrupt Flag bit 1 = A transmit buffer interrupt is pending

- 1 = A transmit buffer interrupt is pending

0 = A transmit buffer interrupt is not pending

- **Note 1:** This bit can only be cleared by turning the CAN module Off and On by clearing or setting the ON bit (CiCON<15>).

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |  |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|--|--|

| 31:24        | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |

| 31.24        | FLTEN7            | MSEL              | 7<1:0>            |                   | F                 | SEL7<4:0>         |                  |                  |  |  |

| 22:16        | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |

| 23:16        | FLTEN6            | MSEL              | 6<1:0>            | FSEL6<4:0>        |                   |                   |                  |                  |  |  |

| 15:8         | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |

| 10.0         | FLTEN5            | MSEL              | 5<1:0>            | FSEL5<4:0>        |                   |                   |                  |                  |  |  |

| 7.0          | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |

| 7:0          | FLTEN4            | MSEL              | 4<1:0>            |                   | F                 | SEL4<4:0>         |                  |                  |  |  |

#### REGISTER 24-11: CIFLTCON1: CAN FILTER CONTROL REGISTER 1

#### Legend:

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read as '0' |                    |  |  |  |  |

|-------------------|------------------|------------------------------------|--------------------|--|--|--|--|

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared               | x = Bit is unknown |  |  |  |  |

| bit 31    | FLTEN7: Filter 7 Enable bit                                        |

|-----------|--------------------------------------------------------------------|

|           | 1 = Filter is enabled                                              |

|           | 0 = Filter is disabled                                             |

| bit 30-29 | MSEL7<1:0>: Filter 7 Mask Select bits                              |

|           | 11 = Acceptance Mask 3 selected                                    |

|           | 10 = Acceptance Mask 2 selected                                    |

|           | 01 = Acceptance Mask 1 selected<br>00 = Acceptance Mask 0 selected |

| hit 20 24 | FSEL7<4:0>: FIFO Selection bits                                    |

| DIL 20-24 |                                                                    |

|           | 11111 = Message matching filter is stored in FIFO buffer 31        |

|           | 11110 = Message matching filter is stored in FIFO buffer 30        |

|           | •                                                                  |

|           | •                                                                  |

|           | 00001 = Message matching filter is stored in FIFO buffer 1         |

|           | 00000 = Message matching filter is stored in FIFO buffer 0         |

| bit 23    | FLTEN6: Filter 6 Enable bit                                        |

|           | 1 = Filter is enabled                                              |

|           | 0 = Filter is disabled                                             |

| bit 22-21 | MSEL6<1:0>: Filter 6 Mask Select bits                              |

|           | 11 = Acceptance Mask 3 selected                                    |

|           | 10 = Acceptance Mask 2 selected                                    |

|           | 01 = Acceptance Mask 1 selected                                    |

|           | 00 = Acceptance Mask 0 selected                                    |

| bit 20-16 | FSEL6<4:0>: FIFO Selection bits                                    |

|           | 11111 = Message matching filter is stored in FIFO buffer 31        |

|           | 11110 - Massage matching filter is stored in EIEO buffer 20        |

11110 = Message matching filter is stored in FIFO buffer 30

•

00001 = Message matching filter is stored in FIFO buffer 1

00000 = Message matching filter is stored in FIFO buffer 0

Note: The bits in this register can only be modified if the corresponding filter enable (FLTENn) bit is '0'.

•

#### REGISTER 24-16: CIFLTCON6: CAN FILTER CONTROL REGISTER 6 (CONTINUED)

| bit 15    | FLTEN25: Filter 25 Enable bit                                                                          |

|-----------|--------------------------------------------------------------------------------------------------------|

|           | 1 = Filter is enabled                                                                                  |

|           | 0 = Filter is disabled                                                                                 |

| bit 14-13 | MSEL25<1:0>: Filter 25 Mask Select bits                                                                |

|           | 11 = Acceptance Mask 3 selected                                                                        |

|           | 10 = Acceptance Mask 2 selected                                                                        |

|           | 01 = Acceptance Mask 1 selected                                                                        |

|           | 00 = Acceptance Mask 0 selected                                                                        |

| bit 12-8  | FSEL25<4:0>: FIFO Selection bits                                                                       |

|           | 11111 = Message matching filter is stored in FIFO buffer 31                                            |

|           | 11110 = Message matching filter is stored in FIFO buffer 30                                            |

|           | •                                                                                                      |

|           | •                                                                                                      |

|           | 00001 = Message matching filter is stored in FIFO buffer 1                                             |

|           | 00000 = Message matching filter is stored in FIFO buffer 0                                             |

| bit 7     | FLTEN24: Filter 24 Enable bit                                                                          |

|           | 1 = Filter is enabled                                                                                  |

|           | 0 = Filter is disabled                                                                                 |

| bit 6-5   | MSEL24<1:0>: Filter 24 Mask Select bits                                                                |

|           | 11 = Acceptance Mask 3 selected                                                                        |

|           | 10 = Acceptance Mask 2 selected                                                                        |

|           | 01 = Acceptance Mask 1 selected                                                                        |

|           | 00 = Acceptance Mask 0 selected                                                                        |

| bit 4-0   | FSEL24<4:0>: FIFO Selection bits                                                                       |

|           | 11111 = Message matching filter is stored in FIFO buffer 31                                            |

|           | 11110 = Message matching filter is stored in FIFO buffer 30                                            |

|           |                                                                                                        |

|           | •                                                                                                      |

|           | 00001 = Message matching filter is stored in FIFO buffer 1                                             |

|           | 00000 = Message matching filter is stored in FIFO buffer 0                                             |

| Note:     | The bits in this register can only be modified if the corresponding filter enable (FLTENn) bit is '0'. |

| Bit Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0    |  |  |  |

|-----------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|---------------------|--|--|--|

| 24.24     | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0               |  |  |  |

| 31:24     | PTV<15:8>         |                   |                   |                   |                   |                   |                  |                     |  |  |  |

| 00.40     | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0               |  |  |  |

| 23:16     | PTV<7:0>          |                   |                   |                   |                   |                   |                  |                     |  |  |  |

| 45.0      | R/W-0             | U-0               | R/W-0             | U-0               | U-0               | U-0               | R/W-0            | R/W-0               |  |  |  |

| 15:8      | ON                | —                 | SIDL              | _                 | _                 | _                 | TXRTS            | RXEN <sup>(1)</sup> |  |  |  |

| 7:0       | R/W-0             | U-0               | U-0               | R/W-0             | U-0               | U-0               | U-0              | R/W-0               |  |  |  |

| 7:0       | AUTOFC            |                   | _                 | MANFC             | _                 |                   |                  | BUFCDEC             |  |  |  |

#### REGISTER 25-1: ETHCON1: ETHERNET CONTROLLER CONTROL REGISTER 1

#### Legend:

| Legenu.           |                  |                          |                    |

|-------------------|------------------|--------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, I | read as '0'        |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared     | x = Bit is unknown |

bit 31-16 PTV<15:0>: PAUSE Timer Value bits PAUSE Timer Value used for Flow Control. This register should only be written when RXEN (ETHCON1<8>) is not set. These bits are only used for Flow Control operations. bit 15 **ON:** Ethernet ON bit 1 = Ethernet module is enabled 0 = Ethernet module is disabled bit 14 Unimplemented: Read as '0' bit 13 SIDL: Ethernet Stop in Idle Mode bit 1 = Ethernet module transfers are paused during Idle mode 0 = Ethernet module transfers continue during Idle mode bit 12-10 Unimplemented: Read as '0' bit 9 TXRTS: Transmit Request to Send bit 1 = Activate the TX logic and send the packet(s) defined in the TX EDT 0 = Stop transmit (when cleared by software) or transmit done (when cleared by hardware)

After the bit is written with a '1', it will clear to a '0' whenever the transmit logic has finished transmitting the requested packets in the Ethernet Descriptor Table (EDT). If a '0' is written by the CPU, the transmit logic finishes the current packet's transmission and then stops any further.

This bit only affects TX operations.

#### bit 8 **RXEN:** Receive Enable bit<sup>(1)</sup>

- 1 = Enable RX logic, packets are received and stored in the RX buffer as controlled by the filter configuration

- 0 = Disable RX logic, no packets are received in the RX buffer

This bit only affects RX operations.

**Note 1:** It is not recommended to clear the RXEN bit and then make changes to any RX related field/register. The Ethernet Controller must be reinitialized (ON cleared to '0'), and then the RX changes applied.

#### **REGISTER 25-15: ETHSTAT: ETHERNET CONTROLLER STATUS REGISTER (CONTINUED)**

- bit 5 **RXBUSY:** Receive Busy bit<sup>(2)</sup> 1 = RX logic is receiving data

- 0 = RX logic is idle

This bit indicates that a packet is currently being received. A change in this status bit is not necessarily reflected by the RXDONE interrupt, as RX packets may be aborted or rejected by the RX filter.

- bit 4-0 Unimplemented: Read as '0'

- **Note 1:** This bit will be *set* when the ON bit (ETHCON1<15>) = 1.

- **2:** This bit will be *cleared* when the ON bit (ETHCON1<15>) = 0.

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |  |  |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|--|--|--|

| 31:24        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |  |  |  |

|              |                   | —                 |                   |                   | —                 |                   | —                | —                |  |  |  |

| 22:46        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |  |  |  |

| 23:16        | —                 | —                 | _                 | _                 | —                 | _                 | _                | —                |  |  |  |

| 15.0         | R/W-P             | R/W-P             | R/W-P             | R/W-P             | R/W-P             | R/W-P             | R/W-P            | R/W-P            |  |  |  |

| 15:8         | STNADDR4<7:0>     |                   |                   |                   |                   |                   |                  |                  |  |  |  |

| 7.0          | R/W-P             | R/W-P             | R/W-P             | R/W-P             | R/W-P             | R/W-P             | R/W-P            | R/W-P            |  |  |  |

| 7:0          |                   |                   |                   | STNADD            | R3<7:0>           |                   |                  |                  |  |  |  |

#### REGISTER 25-38: EMAC1SA1: ETHERNET CONTROLLER MAC STATION ADDRESS 1 REGISTER

| Legend:           |                  | P = Programmable bit     |                    |

|-------------------|------------------|--------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, r | ead as '0'         |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared     | x = Bit is unknown |

bit 31-16 Unimplemented: Read as '0'

- bit 15-8 **STNADDR4<7:0>:** Station Address Octet 4 bits These bits hold the fourth transmitted octet of the station address.

- bit 7-0 **STNADDR3<7:0>:** Station Address Octet 3 bits These bits hold the third transmitted octet of the station address.

Note 1: Both 16-bit and 32-bit accesses are allowed to these registers (including the SET, CLR and INV registers). 8-bit accesses are not allowed and are ignored by the hardware.

2: This register is loaded at reset from the factory preprogrammed station address.

#### 26.1 Control Registers

#### TABLE 26-1: COMPARATOR REGISTER MAP

| ess                         |                                 | 6         |       |       |       |       |       |       |      | Bi   | ts   |        |      |      |      |      |       |       | 6          |

|-----------------------------|---------------------------------|-----------|-------|-------|-------|-------|-------|-------|------|------|------|--------|------|------|------|------|-------|-------|------------|

| Virtual Address<br>(BF80_#) | Register<br>Name <sup>(1)</sup> | Bit Range | 31/15 | 30/14 | 29/13 | 28/12 | 27/11 | 26/10 | 25/9 | 24/8 | 23/7 | 22/6   | 21/5 | 20/4 | 19/3 | 18/2 | 17/1  | 16/0  | All Resets |

| 4.000                       |                                 | 31:16     | _     | _     |       | —     |       | _     |      |      |      | —      |      |      | —    | -    | —     | -     | 0000       |

| A000                        | CM1CON                          | 15:0      | ON    | COE   | CPOL  | —     | _     | _     | _    | COUT | EVPO | L<1:0> | _    | CREF | —    | _    | CCH   | <1:0> | 00C3       |

| A010                        | CM2CON                          | 31:16     | _     | _     | _     | _     | _     | _     |      | _    | _    | —      | _    |      | _    |      | —     | _     | 0000       |

| AUTU                        | CIVIZCON                        | 15:0      | ON    | COE   | CPOL  | -     | -     | -     |      | COUT | EVPO | L<1:0> | -    | CREF |      |      | CCH   | <1:0> | 00C3       |

| A060                        | CMSTAT                          | 31:16     |       | -     | —     | —     | —     | —     | —    | —    | —    | —      | —    | —    | _    | —    | —     | —     | 0000       |

| A060                        | CIVISTAT                        | 15:0      |       | _     | SIDL  | -     |       | _     |      |      |      | _      |      |      | _    |      | C2OUT | C10UT | 0000       |

Legend: x = unknown value on Reset; - = unimplemented, read as '0'. Reset values are shown in hexadecimal.

Note 1: All registers in this table have corresponding CLR, SET and INV registers at their virtual addresses, plus offsets of 0x4, 0x8 and 0xC, respectively. See Section 12.1.1 "CLR, SET and INV Registers" for more information.

| Bit<br>Range | Bit<br>31/23/15/7           | Bit<br>30/22/14/6 | Bit<br>29/21/13/5  | Bit<br>28/20/12/4 | Bit<br>27/19/11/3   | Bit<br>26/18/10/2 | Bit<br>25/17/9/1      | Bit<br>24/16/8/0 |  |  |  |

|--------------|-----------------------------|-------------------|--------------------|-------------------|---------------------|-------------------|-----------------------|------------------|--|--|--|

| 04.04        | R                           | R                 | R                  | R                 | R                   | R                 | R                     | R                |  |  |  |

| 31:24        |                             | VER<3             | :0> <sup>(1)</sup> |                   |                     | DEVID<2           | 27:24> <sup>(1)</sup> |                  |  |  |  |

| 00.40        | R                           | R                 | R                  | R                 | R                   | R                 | R                     | R                |  |  |  |

| 23:16        | DEVID<23:16> <sup>(1)</sup> |                   |                    |                   |                     |                   |                       |                  |  |  |  |

| 45.0         | R                           | R                 | R                  | R                 | R                   | R                 | R                     | R                |  |  |  |

| 15:8         | DEVID<15:8> <sup>(1)</sup>  |                   |                    |                   |                     |                   |                       |                  |  |  |  |

| 7.0          | R                           | R                 | R                  | R                 | R                   | R                 | R                     | R                |  |  |  |

| 7:0          |                             |                   |                    | DEVID<            | 7:0> <sup>(1)</sup> |                   |                       |                  |  |  |  |

#### REGISTER 29-5: DEVID: DEVICE AND REVISION ID REGISTER

## Legend:

| Legena.                         |                  |                          |                    |

|---------------------------------|------------------|--------------------------|--------------------|

| = Readable bit W = Writable bit |                  | U = Unimplemented bit, r | ead as '0'         |

| -n = Value at POR               | '1' = Bit is set | '0' = Bit is cleared     | x = Bit is unknown |

bit 31-28 VER<3:0>: Revision Identifier bits<sup>(1)</sup>

bit 27-0 DEVID<27:0>: Device ID bits<sup>(1)</sup>

Note 1: See the "PIC32 Flash Programming Specification" (DS60001145) for a list of Revision and Device ID values.

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|

| 31:24        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 31.24        |                   | _                 |                   |                   |                   |                   | _                | —                |

| 00.40        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 23:16        | _                 | _                 | _                 | _                 | _                 | _                 | _                | —                |

| 45.0         | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 15:8         | _                 | _                 | _                 | _                 | _                 | _                 | _                | —                |

| 7.0          | U-0               | U-0               | U-0               | U-0               | R/W-1             | R/W-0             | U-0              | R/W-0            |

| 7:0          | _                 | _                 | _                 | _                 | JTAGEN            | TROEN             |                  | TDOEN            |

#### REGISTER 29-6: DDPCON: DEBUG DATA PORT CONTROL REGISTER

| Legend:           |                  |                      |                    |

|-------------------|------------------|----------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bi | it, read as '0'    |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared | x = Bit is unknown |

#### bit 31-4 Unimplemented: Read as '0'

- bit 3 JTAGEN: JTAG Port Enable bit

- 1 = Enable the JTAG port

- 0 = Disable the JTAG port

- bit 2 **TROEN:** Trace Output Enable bit

- 1 = Enable the trace port

- 0 = Disable the trace port

- bit 1 Unimplemented: Read as '0'

- bit 0 TDOEN: TDO Enable for 2-Wire JTAG

- 1 = 2-wire JTAG protocol uses TDO

- 0 = 2-wire JTAG protocol does not use TDO

## 31.0 DEVELOPMENT SUPPORT

The PIC<sup>®</sup> microcontrollers (MCU) and dsPIC<sup>®</sup> digital signal controllers (DSC) are supported with a full range of software and hardware development tools:

- Integrated Development Environment

- MPLAB<sup>®</sup> X IDE Software

- Compilers/Assemblers/Linkers

- MPLAB XC Compiler

- MPASM<sup>™</sup> Assembler

- MPLINK<sup>™</sup> Object Linker/ MPLIB<sup>™</sup> Object Librarian

- MPLAB Assembler/Linker/Librarian for Various Device Families

- Simulators

- MPLAB X SIM Software Simulator

- Emulators

- MPLAB REAL ICE™ In-Circuit Emulator

- In-Circuit Debuggers/Programmers

- MPLAB ICD 3

- PICkit™ 3

- Device Programmers

- MPLAB PM3 Device Programmer

- Low-Cost Demonstration/Development Boards, Evaluation Kits and Starter Kits

- Third-party development tools

#### 31.1 MPLAB X Integrated Development Environment Software

The MPLAB X IDE is a single, unified graphical user interface for Microchip and third-party software, and hardware development tool that runs on Windows<sup>®</sup>, Linux and Mac OS<sup>®</sup> X. Based on the NetBeans IDE, MPLAB X IDE is an entirely new IDE with a host of free software components and plug-ins for high-performance application development and debugging. Moving between tools and upgrading from software simulators to hardware debugging and programming tools is simple with the seamless user interface.

With complete project management, visual call graphs, a configurable watch window and a feature-rich editor that includes code completion and context menus, MPLAB X IDE is flexible and friendly enough for new users. With the ability to support multiple tools on multiple projects with simultaneous debugging, MPLAB X IDE is also suitable for the needs of experienced users.

Feature-Rich Editor:

- · Color syntax highlighting

- Smart code completion makes suggestions and provides hints as you type

- Automatic code formatting based on user-defined rules

- · Live parsing

User-Friendly, Customizable Interface:

- Fully customizable interface: toolbars, toolbar buttons, windows, window placement, etc.

- Call graph window

- Project-Based Workspaces:

- Multiple projects

- Multiple tools

- Multiple configurations

- · Simultaneous debugging sessions

File History and Bug Tracking:

- · Local file history feature

- Built-in support for Bugzilla issue tracker

# PIC32MX5XX/6XX/7XX

| DC CHARACT       | ERISTICS                     |            | $\begin{array}{l} \mbox{Standard Operating Conditions: 2.3V to 3.6V} \\ \mbox{(unless otherwise stated)} \\ \mbox{Operating temperature} & -40^{\circ}C \leq TA \leq +85^{\circ}C \mbox{ for Industrial} \\ & -40^{\circ}C \leq TA \leq +105^{\circ}C \mbox{ for V-Temp} \end{array}$ |                     |      |               |  |  |  |  |

|------------------|------------------------------|------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------|------|---------------|--|--|--|--|

| Parameter<br>No. | Typical <sup>(2)</sup>       | Max.       | Units                                                                                                                                                                                                                                                                                 | Units Conditions    |      |               |  |  |  |  |

| Idle Current (I  | IDLE) <sup>(1,3)</sup> for P | PIC32MX575 | /675/695/775                                                                                                                                                                                                                                                                          | 795 Family Devices  |      |               |  |  |  |  |

| DC30             | 4.5                          | 6.5        | mA                                                                                                                                                                                                                                                                                    | -40°C, +25°C, +85°C |      | 4 MHz         |  |  |  |  |

| DC30b            | 5                            | 7          | +105°C                                                                                                                                                                                                                                                                                |                     | —    | 4 MHZ         |  |  |  |  |

| DC31             | 13                           | 15         | mA                                                                                                                                                                                                                                                                                    | -40°C, +25°C, +85°C | —    | 25 MHz        |  |  |  |  |

| DC32             | 28                           | 30         | mA                                                                                                                                                                                                                                                                                    | -40°C, +25°C, +85°C | —    | 60 MHz        |  |  |  |  |

| DC33             | 36                           | 42         | mA                                                                                                                                                                                                                                                                                    | -40°C, +25°C, +85°C |      | 80 MHz        |  |  |  |  |

| DC33b            | 39                           | 45         | mA                                                                                                                                                                                                                                                                                    | +105°C              | —    |               |  |  |  |  |

| DC34             |                              | 40         |                                                                                                                                                                                                                                                                                       | -40°C               |      |               |  |  |  |  |

| DC34a            |                              | 75         |                                                                                                                                                                                                                                                                                       | +25°C               | 2.3V |               |  |  |  |  |

| DC34b            |                              | 800        | μA                                                                                                                                                                                                                                                                                    | +85°C               | 2.3V |               |  |  |  |  |

| DC34c            |                              | 1000       |                                                                                                                                                                                                                                                                                       | +105°C              |      |               |  |  |  |  |

| DC35             | 35                           |            |                                                                                                                                                                                                                                                                                       | -40°C               |      |               |  |  |  |  |

| DC35a            | 65                           |            |                                                                                                                                                                                                                                                                                       | +25°C               | 3.3V | LPRC (31 kHz) |  |  |  |  |

| DC35b            | 600                          | _          | μΑ                                                                                                                                                                                                                                                                                    | +85°C               | 3.3V |               |  |  |  |  |

| DC35c            | 800                          |            |                                                                                                                                                                                                                                                                                       | +105°C              |      |               |  |  |  |  |

| DC36             |                              | 43         |                                                                                                                                                                                                                                                                                       | -40°C               |      |               |  |  |  |  |

| DC36a            |                              | 106        |                                                                                                                                                                                                                                                                                       | +25°C               | 3.6V |               |  |  |  |  |

| DC36b            |                              | 800        | μA                                                                                                                                                                                                                                                                                    | +85°C               | 3.0V |               |  |  |  |  |

| DC36c            |                              | 1000       |                                                                                                                                                                                                                                                                                       | +105°C              |      |               |  |  |  |  |

#### TABLE 32-6: DC CHARACTERISTICS: IDLE CURRENT (IIDLE)

Note 1: The test conditions for IIDLE current measurements are as follows:

- Oscillator mode is EC (for 8 MHz and below) and EC+PLL (for above 8 MHz) with OSC1 driven by external square wave from rail-to-rail, (OSC1 input clock input over/undershoot < 100 mV required)</li>

- OSC2/CLKO is configured as an I/O input pin

- USB PLL oscillator is disabled if the USB module is implemented, PBCLK divisor = 1:8

- CPU is in Idle mode, program Flash memory Wait states = 111, Program Cache and Prefetch are disabled and SRAM data memory Wait states = 1

- No peripheral modules are operating, (ON bit = 0)

- WDT, Clock Switching, Fail-Safe Clock Monitor, and Secondary Oscillator are disabled

- All I/O pins are configured as inputs and pulled to Vss

- MCLR = VDD

- RTCC and JTAG are disabled

- 2: Data in "Typical" column is at 3.3V, 25°C unless otherwise stated. Parameters are for design guidance only and are not tested.

- 3: This parameter is characterized, but not tested in manufacturing.

- **4:** All parameters are characterized, but only those parameters listed for 4 MHz and 80 MHz are tested at 3.3V in manufacturing.

#### TABLE 32-31: SPIX MODULE SLAVE MODE (CKE = 1) TIMING REQUIREMENTS (CONTINUED)

| AC CHARACTERISTICS |                      |                                                       | (unless      | $\begin{array}{l} \mbox{Standard Operating Conditions: 2.3V to 3.6V} \\ \mbox{(unless otherwise stated)} \\ \mbox{Operating temperature} & -40^{\circ}C \leq TA \leq +85^{\circ}C \mbox{ for Industrial} \\ & -40^{\circ}C \leq TA \leq +105^{\circ}C \mbox{ for V-Temp} \end{array}$ |       |            |   |  |  |  |

|--------------------|----------------------|-------------------------------------------------------|--------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------|------------|---|--|--|--|

| Param.<br>No.      | Symbol               | Characteristics <sup>(1)</sup>                        | Min.         | Typical <sup>(2)</sup>                                                                                                                                                                                                                                                                | Units | Conditions |   |  |  |  |

| SP51               | TssH2doZ             | SSx ↑ to SDOx Output<br>High-Impedance <sup>(4)</sup> | 5            | _                                                                                                                                                                                                                                                                                     | 25    | ns         | _ |  |  |  |

| SP52               | TscH2ssH<br>TscL2ssH | SSx ↑ after SCKx Edge                                 | Тscк +<br>20 | —                                                                                                                                                                                                                                                                                     | _     | ns         | _ |  |  |  |

| SP60               | TssL2doV             | SDOx Data Output Valid after<br>SSx Edge              | —            | —                                                                                                                                                                                                                                                                                     | 25    | ns         | — |  |  |  |

**Note 1:** These parameters are characterized, but not tested in manufacturing.

2: Data in "Typical" column is at 3.3V, 25°C unless otherwise stated. Parameters are for design guidance only and are not tested.

3: The minimum clock period for SCKx is 40 ns.

4: Assumes 50 pF load on all SPIx pins.

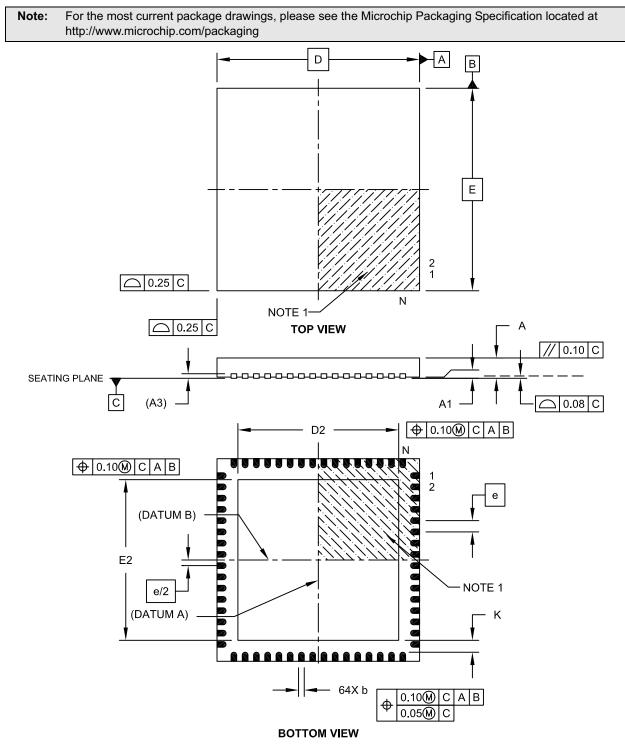

## 64-Lead Plastic Quad Flat, No Lead Package (MR) – 9x9x0.9 mm Body [QFN] With 7.15 x 7.15 Exposed Pad [QFN]

Microchip Technology Drawing C04-149C Sheet 1 of 2