Welcome to **E-XFL.COM**

What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded - Microcontrollers</u>"

| Details                    |                                                                                   |

|----------------------------|-----------------------------------------------------------------------------------|

| Product Status             | Active                                                                            |

| Core Processor             | MIPS32® M4K™                                                                      |

| Core Size                  | 32-Bit Single-Core                                                                |

| Speed                      | 80MHz                                                                             |

| Connectivity               | Ethernet, I <sup>2</sup> C, SPI, UART/USART, USB OTG                              |

| Peripherals                | Brown-out Detect/Reset, DMA, POR, PWM, WDT                                        |

| Number of I/O              | 85                                                                                |

| Program Memory Size        | 512KB (512K x 8)                                                                  |

| Program Memory Type        | FLASH                                                                             |

| EEPROM Size                | -                                                                                 |

| RAM Size                   | 64K x 8                                                                           |

| Voltage - Supply (Vcc/Vdd) | 2.3V ~ 3.6V                                                                       |

| Data Converters            | A/D 16x10b                                                                        |

| Oscillator Type            | Internal                                                                          |

| Operating Temperature      | -40°C ~ 105°C (TA)                                                                |

| Mounting Type              | Surface Mount                                                                     |

| Package / Case             | 100-TQFP                                                                          |

| Supplier Device Package    | 100-TQFP (14x14)                                                                  |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic32mx675f512lt-80v-pf |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

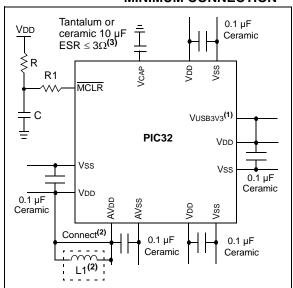

# FIGURE 2-1: RECOMMENDED MINIMUM CONNECTION

Note 1: If the USB module is not used, this pin must be connected to VDD.

2: As an option, instead of a hard-wired connection, an inductor (L1) can be substituted between VDD and AVDD to improve ADC noise rejection. The inductor impedance should be less than 3Ω and the inductor capacity greater than 10 mA.

Where:

$$f=rac{FCNV}{2}$$

(i.e., ADC conversion rate/2)

$$f=rac{1}{(2\pi\sqrt{LC})}$$

$L=\left(rac{1}{(2\pi f\sqrt{C})}

ight)^2$

Aluminum or electrolytic capacitors should not be used. ESR ≤ 3Ω from -40°C to 125°C @ SYSCLK frequency (i.e., MIPS).

#### 2.2.1 BULK CAPACITORS

The use of a bulk capacitor is recommended to improve power supply stability. Typical values range from 4.7  $\mu$ F to 47  $\mu$ F. This capacitor should be located as close to the device as possible.

# 2.3 Capacitor on Internal Voltage Regulator (VCAP)

#### 2.3.1 INTERNAL REGULATOR MODE

A low-ESR (1 ohm) capacitor is required on the VCAP pin, which is used to stabilize the internal voltage regulator output. The VCAP pin must not be connected to VDD, and must have a CEFC capacitor, with at least a 6V rating, connected to ground. The type can be ceramic or tantalum. Refer to **Section 32.0 "Electrical Characteristics"** for additional information on CEFC specifications.

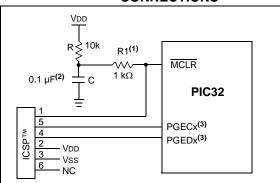

## 2.4 Master Clear (MCLR) Pin

The  $\overline{\text{MCLR}}$  pin provides two specific device functions:

- Device Reset

- Device Programming and Debugging

Pulling The MCLR pin low generates a device Reset. Figure 2-2 illustrates a typical MCLR circuit. During device programming and debugging, the resistance and capacitance that can be added to the pin must be considered. Device programmers and debuggers drive the MCLR pin. Consequently, specific voltage levels (VIH and VIL) and fast signal transitions must not be adversely affected. Therefore, specific values of R and C will need to be adjusted based on the application and PCB requirements.

For example, as illustrated in Figure 2-2, it is recommended that the capacitor C, be isolated from the MCLR pin during programming and debugging operations.

Place the components illustrated in Figure 2-2 within one-quarter inch (6 mm) from the MCLR pin.

# FIGURE 2-2: EXAMPLE OF MCLR PIN CONNECTIONS

- Note 1:  $\frac{470\Omega \leq R1 \leq 1 k\Omega \text{ will limit any current flowing into}}{\overline{MCLR}} \text{ from the external capacitor C, in the event of } \overline{MCLR} \text{ pin breakdown, due to Electrostatic Discharge}$  (ESD) or Electrical Overstress (EOS). Ensure that the \$\overline{MCLR}\$ pin VIH and VIL specifications are met without interfering with the Debug/Programmer tools.

- 2: The capacitor can be sized to prevent unintentional Resets from brief glitches or to extend the device Reset period during POR.

- : No pull-ups or bypass capacitors are allowed on active debug/program PGECx/PGEDx pins.

**NOTES:**

REGISTER 6-1: RCON: RESET CONTROL REGISTER

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1   | Bit<br>24/16/8/0   |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|--------------------|--------------------|

| 31:24        | U-0                | U-0                |

| 31.24        | _                 | _                 | -                 | _                 |                   | _                 | _                  | _                  |

| 22:46        | U-0                | U-0                |

| 23:16        | _                 | _                 | -                 | _                 |                   | _                 | _                  | _                  |

| 45.0         | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | R/W-0, HS          | R/W-0              |

| 15:8         | _                 | _                 | _                 | _                 | _                 | _                 | CMR                | VREGS              |

| 7.0          | R/W-0, HS         | R/W-0, HS         | U-0               | R/W-0, HS         | R/W-0, HS         | R/W-0, HS         | R/W-1, HS          | R/W-1, HS          |

| 7:0          | EXTR              | SWR               | 1                 | WDTO              | SLEEP             | IDLE              | BOR <sup>(1)</sup> | POR <sup>(1)</sup> |

Legend:HS = Set by hardwareR = Readable bitW = Writable bitU = Unimplemented bit, read as '0'-n = Value at POR'1' = Bit is set'0' = Bit is clearedx = Bit is unknown

bit 31-10 Unimplemented: Read as '0'

bit 9 CMR: Configuration Mismatch Reset Flag bit

1 = Configuration mismatch Reset has occurred

0 = Configuration mismatch Reset has not occurred

bit 8 VREGS: Voltage Regulator Standby Enable bit

1 = Regulator is enabled and is on during Sleep mode

0 = Regulator is set to Stand-by Tracking mode

bit 7 EXTR: External Reset (MCLR) Pin Flag bit

1 = Master Clear (pin) Reset has occurred

0 = Master Clear (pin) Reset has not occurred

bit 6 **SWR:** Software Reset Flag bit

1 = Software Reset was executed

0 = Software Reset was not executed

bit 5 **Unimplemented:** Read as '0'

bit 4 WDTO: Watchdog Timer Time-out Flag bit

1 = WDT Time-out has occurred

0 = WDT Time-out has not occurred

bit 3 SLEEP: Wake From Sleep Flag bit

1 = Device was in Sleep mode

0 = Device was not in Sleep mode

bit 2 IDLE: Wake From Idle Flag bit

1 = Device was in Idle mode

0 = Device was not in Idle mode

bit 1 BOR: Brown-out Reset Flag bit<sup>(1)</sup>

1 = Brown-out Reset has occurred

0 = Brown-out Reset has not occurred

bit 0 **POR:** Power-on Reset Flag bit<sup>(1)</sup>

1 = Power-on Reset has occurred

0 = Power-on Reset has not occurred

Note 1: User software must clear this bit to view the next detection.

### REGISTER 9-2: CHEACC: CACHE ACCESS REGISTER

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|

| 31:24        | R/W-0             | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 31.24        | CHEWEN            | _                 | _                 | _                 | _                 | _                 | _                | _                |

| 22,46        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 23:16        | _                 | _                 | _                 | _                 | _                 | -                 | -                | _                |

| 15:8         | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 15.6         | _                 | _                 | _                 | _                 | _                 | _                 | _                | _                |

| 7.0          | U-0               | U-0               | U-0               | U-0               | R/W-0             | R/W-0             | R/W-0            | R/W-0            |

| 7:0          | _                 | _                 | _                 | _                 |                   | CHEID             | X<3:0>           |                  |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

bit 31 CHEWEN: Cache Access Enable bits

These bits apply to registers CHETAG, CHEMSK, CHEW0, CHEW1, CHEW2, and CHEW3.

1 = The cache line selected by CHEIDX<3:0> is writeable

0 = The cache line selected by CHEIDX<3:0> is not writeable

bit 30-4 **Unimplemented:** Write '0'; ignore read

bit 3-0 CHEIDX<3:0>: Cache Line Index bits

The value selects the cache line for reading or writing.

#### REGISTER 10-8: DCHxECON: DMA CHANNEL 'x' EVENT CONTROL REGISTER

| Bit<br>Range | Bit<br>31/23/15/7          | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3    | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |  |  |  |  |

|--------------|----------------------------|-------------------|-------------------|-------------------|----------------------|-------------------|------------------|------------------|--|--|--|--|--|

| 31:24        | U-0                        | U-0               | U-0               | U-0               | U-0                  | U-0               | U-0              | U-0              |  |  |  |  |  |

| 31.24        |                            | _                 | _                 | _                 | _                    |                   | _                | _                |  |  |  |  |  |

| 22,46        | R/W-1                      | R/W-1             | R/W-1             | R/W-1             | R/W-1                | R/W-1             | R/W-1            | R/W-1            |  |  |  |  |  |

| 23:16        | CHAIRQ<7:0> <sup>(1)</sup> |                   |                   |                   |                      |                   |                  |                  |  |  |  |  |  |

| 45.0         | R/W-1                      | R/W-1             | R/W-1             | R/W-1             | R/W-1                | R/W-1             | R/W-1            | R/W-1            |  |  |  |  |  |

| 15:8         |                            |                   |                   | CHSIRQ<           | <7:0> <sup>(1)</sup> |                   |                  |                  |  |  |  |  |  |

| 7.0          | S-0                        | S-0               | R/W-0             | R/W-0             | R/W-0                | U-0               | U-0              | U-0              |  |  |  |  |  |

| 7:0          | CFORCE                     | CABORT            | PATEN             | SIRQEN            | AIRQEN               | _                 | _                | _                |  |  |  |  |  |

Legend:S = Settable bitR = Readable bitW = Writable bitU = Unimplemented bit, read as '0'-n = Value at POR'1' = Bit is set'0' = Bit is clearedx = Bit is unknown

bit 31-24 Unimplemented: Read as '0'

bit 23-16 CHAIRQ<7:0>: Channel Transfer Abort IRQ bits<sup>(1)</sup>

11111111 = Interrupt 255 will abort any transfers in progress and set CHAIF flag

•

•

•

00000001 = Interrupt 1 will abort any transfers in progress and set CHAIF flag 00000000 = Interrupt 0 will abort any transfers in progress and set CHAIF flag

bit 15-8 CHSIRQ<7:0>: Channel Transfer Start IRQ bits(1)

11111111 = Interrupt 255 will initiate a DMA transfer

•

•

00000001 = Interrupt 1 will initiate a DMA transfer 00000000 = Interrupt 0 will initiate a DMA transfer

1 = A DMA transfer is forced to begin when this bit is written to a '1'

0 = This bit always reads '0'

bit 6 CABORT: DMA Abort Transfer bit

1 = A DMA transfer is aborted when this bit is written to a '1'

0 = This bit always reads '0'

bit 5 PATEN: Channel Pattern Match Abort Enable bit

1 = Abort transfer and clear CHEN on pattern match

0 = Pattern match is disabled

bit 4 SIRQEN: Channel Start IRQ Enable bit

1 = Start channel cell transfer if an interrupt matching CHSIRQ occurs

0 = Interrupt number CHSIRQ is ignored and does not start a transfer

bit 3 AIRQEN: Channel Abort IRQ Enable bit

1 = Channel transfer is aborted if an interrupt matching CHAIRQ occurs

0 = Interrupt number CHAIRQ is ignored and does not terminate a transfer

bit 2-0 Unimplemented: Read as '0'

Note 1: See Table 7-1: "Interrupt IRQ, Vector and Bit Location" for the list of available interrupt IRQ sources.

#### REGISTER 10-14: DCHxSPTR: DMA CHANNEL 'x' SOURCE POINTER REGISTER

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|

| 24.24        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 31:24        | _                 | _                 | _                 | _                 | _                 | _                 | -                | _                |

| 22,46        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 23:16        | _                 | _                 | _                 | _                 | _                 | _                 | _                | _                |

| 45.0         | R-0               | R-0               | R-0               | R-0               | R-0               | R-0               | R-0              | R-0              |

| 15:8         |                   |                   |                   | CHSPTR            | <15:8>            |                   |                  |                  |

| 7.0          | R-0               | R-0               | R-0               | R-0               | R-0               | R-0               | R-0              | R-0              |

| 7:0          |                   | _                 |                   | CHSPTF            | R<7:0>            | _                 |                  |                  |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

bit 31-16 Unimplemented: Read as '0'

bit 15-0 CHSPTR<15:0>: Channel Source Pointer bits

111111111111111 = Points to byte 65,535 of the source

•

0000000000000000 = Points to byte 1 of the source 000000000000000 = Points to byte 0 of the source

**Note:** When in Pattern Detect mode, this register is reset on a pattern detect.

#### REGISTER 10-15: DCHxDPTR: DMA CHANNEL 'x' DESTINATION POINTER REGISTER

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|

| 24.24        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 31:24        |                   | _                 | _                 | _                 | _                 |                   | _                | _                |

| 22,46        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 23:16        |                   | _                 | _                 | _                 | _                 |                   | _                | _                |

| 15:8         | R-0               | R-0               | R-0               | R-0               | R-0               | R-0               | R-0              | R-0              |

| 15.6         |                   |                   |                   | CHDPTR            | <15:8>            |                   |                  |                  |

| 7.0          | R-0               | R-0               | R-0               | R-0               | R-0               | R-0               | R-0              | R-0              |

| 7:0          |                   |                   |                   | CHDPTF            | R<7:0>            |                   |                  |                  |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

bit 31-16 Unimplemented: Read as '0'

bit 15-0 CHDPTR<15:0>: Channel Destination Pointer bits

1111111111111111 = Points to byte 65,535 of the destination

•

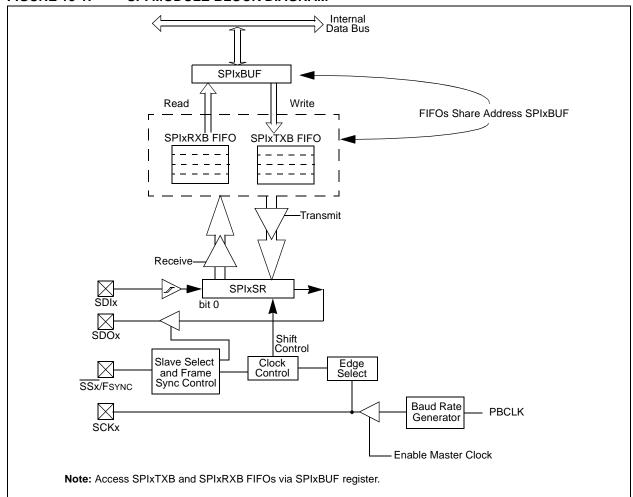

# 18.0 SERIAL PERIPHERAL INTERFACE (SPI)

Note:

This data sheet summarizes the features of the PIC32MX5XX/6XX/7XX family of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to **Section 23. "Serial Peripheral Interface (SPI)"** (DS60001106) in the "PIC32 Family Reference Manual", which is available from the Microchip web site (www.microchip.com/PIC32).

The SPI module is a synchronous serial interface that is useful for communicating with external peripherals and other microcontroller devices. These peripheral devices may be Serial EEPROMs, Shift registers, display drivers, Analog-to-Digital Converters, etc. The PIC32 SPI module is compatible with Motorola® SPI and SIOP interfaces.

The following are some of the key features of the SPI module:

- Master mode and Slave mode support

- · Four different clock formats

- · Enhanced Framed SPI protocol support

- User-configurable 8-bit, 16-bit and 32-bit data width

- · Separate SPI FIFO buffers for receive and transmit

- FIFO buffers act as 4/8/16-level deep FIFOs based on 32/16/8-bit data width

- Programmable interrupt event on every 8-bit, 16-bit and 32-bit data transfer

- · Operation during Sleep and Idle modes

- Fast bit manipulation using CLR, SET and INV registers

FIGURE 18-1: SPI MODULE BLOCK DIAGRAM

### REGISTER 18-1: SPIXCON: SPI CONTROL REGISTER (CONTINUED)

- bit 15 **ON:** SPI Peripheral On bit<sup>(1)</sup>

- 1 = SPI Peripheral is enabled

- 0 = SPI Peripheral is disabled

- bit 14 Unimplemented: Read as '0'

- bit 13 SIDL: Stop in Idle Mode bit

- 1 = Discontinue operation when CPU enters in Idle mode

- 0 = Continue operation in Idle mode

- bit 12 DISSDO: Disable SDOx pin bit

- 1 = SDOx pin is not used by the module (pin is controlled by associated PORT register)

- 0 = SDOx pin is controlled by the module

#### bit 11-10 MODE<32,16>: 32/16-Bit Communication Select bits

| MODE32 | MODE16 | Communication |

|--------|--------|---------------|

| 1      | x      | 32-bit        |

| 0      | 1      | 16-bit        |

| 0      | 0      | 8-bit         |

#### bit 9 SMP: SPI Data Input Sample Phase bit

#### Master mode (MSTEN = 1):

- 1 = Input data sampled at end of data output time

- 0 = Input data sampled at middle of data output time

#### Slave mode (MSTEN = 0):

SMP value is ignored when SPI is used in Slave mode. The module always uses SMP = 0.

- bit 8 **CKE:** SPI Clock Edge Select bit<sup>(3)</sup>

- 1 = Serial output data changes on transition from active clock state to Idle clock state (see CKP bit)

- 0 = Serial output data changes on transition from Idle clock state to active clock state (see CKP bit)

- bit 7 SSEN: Slave Select Enable (Slave mode) bit

- $1 = \overline{SSx}$  pin used for Slave mode

- 0 = SSx pin not used for Slave mode (pin is controlled by port function)

- bit 6 **CKP:** Clock Polarity Select bit

- 1 = Idle state for clock is a high level; active state is a low level

- 0 = Idle state for clock is a low level; active state is a high level

- bit 5 MSTEN: Master Mode Enable bit

- 1 = Master mode

- 0 = Slave mode

- bit 4 Unimplemented: Read as '0'

- bit 3-2 STXISEL<1:0>: SPI Transmit Buffer Empty Interrupt Mode bits

- 11 = Interrupt is generated when the buffer is not full (has one or more empty elements)

- 10 = Interrupt is generated when the buffer is empty by one-half or more

- 01 = Interrupt is generated when the buffer is completely empty

- 00 = Interrupt is generated when the last transfer is shifted out of SPISR and transmit operations are complete

- bit 1-0 SRXISEL<1:0>: SPI Receive Buffer Full Interrupt Mode bits

- 11 = Interrupt is generated when the buffer is full

- 10 = Interrupt is generated when the buffer is full by one-half or more

- 01 = Interrupt is generated when the buffer is not empty

- 00 = Interrupt is generated when the last word in the receive buffer is read (i.e., buffer is empty)

- **Note 1:** When using the 1:1 PBCLK divisor, the user's software should not read or write the peripheral's SFRs in the SYSCLK cycle immediately following the instruction that clears the module's ON bit.

- 2: This bit can only be written when the ON bit = 0.

- 3: This bit is not used in the Framed SPI mode. The user should program this bit to '0' for the Framed SPI mode (FRMEN = 1).

#### REGISTER 22-1: RTCCON: RTC CONTROL REGISTER (CONTINUED)

- bit 3 RTCWREN: RTC Value Registers Write Enable bit (4)

- 1 = RTC Value registers can be written to by the user

- 0 = RTC Value registers are locked out from being written to by the user

- bit 2 RTCSYNC: RTCC Value Registers Read Synchronization bit

- 1 = RTC Value registers can change while reading, due to a rollover ripple that results in an invalid data read. If the register is read twice and results in the same data, the data can be assumed to be valid.

- 0 = RTC Value registers can be read without concern about a rollover ripple

- bit 1 HALFSEC: Half-Second Status bit<sup>(5)</sup>

- 1 = Second half period of a second

- 0 = First half period of a second

- bit 0 RTCOE: RTCC Output Enable bit

- 1 = RTCC clock output is enabled (clock presented onto an I/O)

- 0 = RTCC clock output is disabled

- **Note 1:** The ON bit is only writable when RTCWREN = 1.

- 2: When using the 1:1 PBCLK divisor, the user's software should not read/write the peripheral's SFRs in the SYSCLK cycle immediately following the instruction that clears the module's ON bit.

- 3: Requires RTCOE = 1 (RTCCON<0>) for the output to be active.

- **4:** The RTCWREN bit can only be set when the write sequence is enabled.

- 5: This bit is read-only. It is cleared to '0' on a write to the seconds bit fields (RTCTIME<14:8>).

Note: This register is only reset on a Power-on Reset (POR).

#### **Control Registers** 24.1

TABLE 24-1: CAN1 REGISTER SUMMARY FOR PIC32MX534F064H, PIC32MX564F064H, PIC32MX564F128H, PIC32MX575F256H, PIC32MX575F512H, PIC32MX764F128H, PIC32MX775F256H, PIC32MX775F512H, PIC32MX795F512H, PIC32MX534F064L, PIC32MX564F064L, PIC32MX564F128L, PIC32MX575F256L, PIC32MX575F512L, PIC32MX764F128L, PIC32MX775F256L, PIC32MX775F512L AND PIC32MX795F512L DEVICES

PIC32MX5XX/6XX/7XX

|                             |                                 | ,         | JOZ 111/1/1     | 701012   | L AND    | 1 100211  | 1777 301 6 | TIEL DE     | TIOLO      |           |          |           |          |          |           |            |           |          |            |

|-----------------------------|---------------------------------|-----------|-----------------|----------|----------|-----------|------------|-------------|------------|-----------|----------|-----------|----------|----------|-----------|------------|-----------|----------|------------|

| SSE                         |                                 | _         |                 |          |          |           |            |             |            | Bit       | s        |           |          |          |           |            |           |          |            |

| Virtual Address<br>(BF88_#) | Register<br>Name <sup>(1)</sup> | Bit Range | 31/15           | 30/14    | 29/13    | 28/12     | 27/11      | 26/10       | 25/9       | 24/8      | 23/7     | 22/6      | 21/5     | 20/4     | 19/3      | 18/2       | 17/1      | 16/0     | All Resets |

| B000                        | C1CON                           | 31:16     | _               | _        | _        | _         | ABAT       | -           | REQOP<2:0  | >         | (        | DPMOD<2:0 | >        | CANCAP   | _         | _          | _         | _        | 0480       |

| БООО                        | CICON                           | 15:0      | ON              | _        | SIDLE    | 1         | CANBUSY    | ı           | _          | _         | _        | _         | _        |          | D         | NCNT<4:0>  | >         |          | 0000       |

| B010                        | C1CFG                           | 31:16     | 1               | _        | _        | _         | _          | _           | _          | _         | _        | WAKFIL    | _        | _        | _         | S          | EG2PH<2:0 | >        | 0000       |

| БОТО                        | CICFG                           | 15:0      | SEG2PHTS        | SAM      | S        | EG1PH<2:0 | )>         |             | PRSEG<2:0: | >         | SJW-     | <1:0>     |          |          | BRP<      | 5:0>       |           |          | 0000       |

| B020                        | C1INT                           | 31:16     | IVRIE           | WAKIE    | CERRIE   | SERRIE    | RBOVIE     | ı           | _          | _         | _        | _         | _        | _        | MODIE     | CTMRIE     | RBIE      | TBIE     | 0000       |

| B020                        | CIIIVI                          | 15:0      | IVRIF           | WAKIF    | CERRIF   | SERRIF    | RBOVIF     | _           | _          | _         | _        | _         | _        | _        | MODIF     | CTMRIF     | RBIF      | TBIF     | 0000       |

| B030                        | C1VEC                           | 31:16     | _               | _        | _        | _         | _          | -           | _          | _         | _        | _         | _        | _        | _         | _          | _         | _        | 0000       |

| B030                        | CIVEC                           | 15:0      | _               | _        | _        |           |            | FILHIT<4:0: | >          |           | _        |           |          | 10       | CODE<6:0> |            |           |          | 0040       |

| B040                        | C1TREC                          | 31:16     | _               | _        | _        | _         | _          | _           | _          |           | _        | _         | TXBO     | TXBP     | RXBP      | TXWARN     | RXWARN    | EWARN    | 0000       |

| D070                        | OTTILLO                         | 15:0      |                 |          |          | TERRO     | NT<7:0>    |             |            |           |          |           |          | RERRCN   | T<7:0>    |            |           |          | 0000       |

| B050                        | C1FSTAT                         | 31:16     | FIFOIP31        | FIFOIP30 | FIFOIP29 | FIFOIP28  | FIFOIP27   | FIFOIP26    | FIFOIP25   | FIFOIP24  | FIFOIP23 | FIFOIP22  | FIFOIP21 | FIFOIP20 | FIFOIP19  | FIFOIP18   | FIFOIP17  | FIFOIP16 | 0000       |

| D000                        | 01101741                        | 15:0      |                 | FIFOIP14 |          | FIFOIP12  |            | FIFOIP10    | FIFOIP9    | FIFOIP8   | FIFOIP7  | FIFOIP6   | FIFOIP5  | FIFOIP4  | FIFOIP3   | FIFOIP2    | FIFOIP1   | FIFOIP0  |            |

| B060                        | C1RXOVF                         |           |                 |          | RXOVF29  |           |            | RXOVF26     |            | RXOVF24   | RXOVF23  | RXOVF22   |          |          |           | RXOVF18    | -         | _        | _          |

|                             |                                 |           | RXOVF15         | RXOVF14  | RXOVF13  | RXOVF12   | RXOVF11    | RXOVF10     | RXOVF9     | RXOVF8    | RXOVF7   | RXOVF6    | RXOVF5   | RXOVF4   | RXOVF3    | RXOVF2     | RXOVF1    | RXOVF0   | 0000       |

| B070                        | C1TMR                           | 31:16     |                 |          |          |           |            |             |            | CANTS<    |          |           |          |          |           |            |           | 1        | 0000       |

|                             |                                 | 15:0      |                 |          |          |           |            |             | CAI        | NTSPRE<15 | :0>      |           |          |          |           |            |           |          | 0000       |

| B080                        | C1RXM0                          | 31:16     |                 |          |          |           |            | SID<10:0>   |            |           |          |           |          | -        | MIDE      | _          | EID<1     | 7:16>    | xxxx       |

|                             |                                 | 15:0      |                 |          |          |           |            |             |            | EID<1     | 5:0>     |           |          | 1        |           |            |           |          | xxxx       |

| B090                        | C1RXM1                          | 31:16     |                 |          |          |           |            | SID<10:0>   |            |           |          |           |          |          | MIDE      | _          | EID<1     | 7:16>    | xxxx       |

|                             |                                 | 15:0      |                 |          |          |           |            |             |            | EID<1     | 5:0>     |           |          |          | 1         |            |           |          | xxxx       |

| B0A0                        | C1RXM2                          | 31:16     |                 |          |          |           |            | SID<10:0>   |            |           |          |           |          |          | MIDE      | _          | EID<1     | 7:16>    | xxxx       |

| 20,10                       | 01104112                        | 15:0      |                 |          |          |           |            |             |            | EID<1     | 5:0>     |           |          |          | 1         |            |           |          | xxxx       |

| B0B0                        | C1RXM3                          | 31:16     | 11:16 SID<10:0> |          |          |           |            |             |            |           | xxxx     |           |          |          |           |            |           |          |            |

| Вово                        | OTTOWNO                         | 15:0      |                 |          |          |           |            |             |            | EID<1     | 5:0>     |           |          |          |           |            |           |          | xxxx       |

| B0C0                        | C1FLTCON0                       | 31:16     | FLTEN3          | MSEL:    | 3<1:0>   |           |            | FSEL3<4:0:  | >          |           | FLTEN2   | MSEL      | 2<1:0>   |          | F         | SEL2<4:0>  |           |          | 0000       |

| 2000                        | C.I LI CONO                     | 15:0      | FLTEN1          | MSEL     |          |           |            | FSEL1<4:0:  |            |           | FLTEN0   |           | 0<1:0>   |          |           | SEL0<4:0>  |           |          | 0000       |

| BODO                        | C1FLTCON1                       | 31:16     | FLTEN7          | MSEL     | _        |           |            | FSEL7<4:0:  |            |           | FLTEN6   | _         | 6<1:0>   |          |           | SEL6<4:0>  |           |          | 0000       |

| 3020                        | 2 2. 00111                      | 15:0      | FLTEN5          | MSEL     |          |           |            | FSEL5<4:0:  |            |           | FLTEN4   |           | 4<1:0>   |          |           | SEL4<4:0>  |           |          | 0000       |

| B0E0                        | C1FLTCON2                       | 31:16     | FLTEN11         | MSEL1    |          |           |            | FSEL11<4:0  |            |           | FLTEN10  |           | 10<1:0>  |          |           | SEL10<4:0> |           |          | 0000       |

|                             | E0 C1FLTCON2                    |           | FLTEN9          | MSEL     | 9<1:0>   |           |            | FSEL9<4:0:  | >          |           | FLTEN8   | MSEL      | 8<1:0>   |          | F         | SEL8<4:0>  |           |          | 0000       |

x = unknown value on Reset; — = unimplemented, read as '0'. Reset values are shown in hexadecimal. All registers in this table have corresponding CLR, SET and INV registers at their virtual addresses, plus offsets of 0x4, 0x8 and 0xC, respectively. See Section 12.1.1 "CLR, SET and INV Registers" for more information.

### REGISTER 24-11: CIFLTCON1: CAN FILTER CONTROL REGISTER 1 (CONTINUED)

```

bit 15

FLTEN5: Filter 17 Enable bit

1 = Filter is enabled

0 = Filter is disabled

bit 14-13 MSEL5<1:0>: Filter 5 Mask Select bits

11 = Acceptance Mask 3 selected

10 = Acceptance Mask 2 selected

01 = Acceptance Mask 1 selected

00 = Acceptance Mask 0 selected

bit 12-8 FSEL5<4:0>: FIFO Selection bits

11111 = Message matching filter is stored in FIFO buffer 31

11110 = Message matching filter is stored in FIFO buffer 30

00001 = Message matching filter is stored in FIFO buffer 1

00000 = Message matching filter is stored in FIFO buffer 0

bit 7

FLTEN4: Filter 4 Enable bit

1 = Filter is enabled

0 = Filter is disabled

bit 6-5

MSEL4<1:0>: Filter 4 Mask Select bits

11 = Acceptance Mask 3 selected

10 = Acceptance Mask 2 selected

01 = Acceptance Mask 1 selected

00 = Acceptance Mask 0 selected

FSEL4<4:0>: FIFO Selection bits

bit 4-0

11111 = Message matching filter is stored in FIFO buffer 31

11110 = Message matching filter is stored in FIFO buffer 30

00001 = Message matching filter is stored in FIFO buffer 1

00000 = Message matching filter is stored in FIFO buffer 0

```

Note: The bits in this register can only be modified if the corresponding filter enable (FLTENn) bit is '0'.

#### REGISTER 25-1: ETHCON1: ETHERNET CONTROLLER CONTROL REGISTER 1

| Bit Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0    |  |  |  |  |  |  |

|-----------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|---------------------|--|--|--|--|--|--|

| 24.24     | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0               |  |  |  |  |  |  |

| 31:24     |                   |                   |                   | PTV<              | 15:8>             |                   |                  |                     |  |  |  |  |  |  |

| 22,46     | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0               |  |  |  |  |  |  |

| 23:16     | PTV<7:0>          |                   |                   |                   |                   |                   |                  |                     |  |  |  |  |  |  |

| 45.0      | R/W-0             | U-0               | R/W-0             | U-0               | U-0               | U-0               | R/W-0            | R/W-0               |  |  |  |  |  |  |

| 15:8      | ON                | _                 | SIDL              | _                 | _                 | _                 | TXRTS            | RXEN <sup>(1)</sup> |  |  |  |  |  |  |

| 7.0       | R/W-0             | U-0               | U-0               | R/W-0             | U-0               | U-0               | U-0              | R/W-0               |  |  |  |  |  |  |

| 7:0       | AUTOFC            | _                 | _                 | MANFC             | _                 | _                 | _                | BUFCDEC             |  |  |  |  |  |  |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

bit 31-16 PTV<15:0>: PAUSE Timer Value bits

PAUSE Timer Value used for Flow Control.

This register should only be written when RXEN (ETHCON1<8>) is not set.

These bits are only used for Flow Control operations.

bit 15 ON: Ethernet ON bit

1 = Ethernet module is enabled

0 = Ethernet module is disabled

bit 14 Unimplemented: Read as '0'

bit 13 SIDL: Ethernet Stop in Idle Mode bit

1 = Ethernet module transfers are paused during Idle mode

0 = Ethernet module transfers continue during Idle mode

bit 12-10 Unimplemented: Read as '0'

bit 9 **TXRTS:** Transmit Request to Send bit

1 = Activate the TX logic and send the packet(s) defined in the TX EDT

0 = Stop transmit (when cleared by software) or transmit done (when cleared by hardware)

After the bit is written with a '1', it will clear to a '0' whenever the transmit logic has finished transmitting the requested packets in the Ethernet Descriptor Table (EDT). If a '0' is written by the CPU, the transmit logic finishes the current packet's transmission and then stops any further.

This bit only affects TX operations.

bit 8 **RXEN:** Receive Enable bit<sup>(1)</sup>

- 1 = Enable RX logic, packets are received and stored in the RX buffer as controlled by the filter configuration

- 0 = Disable RX logic, no packets are received in the RX buffer

This bit only affects RX operations.

**Note 1:** It is not recommended to clear the RXEN bit and then make changes to any RX related field/register. The Ethernet Controller must be reinitialized (ON cleared to '0'), and then the RX changes applied.

# REGISTER 25-11: ETHRXFC: ETHERNET CONTROLLER RECEIVE FILTER CONFIGURATION REGISTER (CONTINUED)

- bit 7 CRCERREN: CRC Error Collection Enable bit

- 1 = The received packet CRC must be invalid for the packet to be accepted

- 0 = Disable CRC Error Collection filtering

This bit allows the user to collect all packets that have an invalid CRC.

- bit 6 CRCOKEN: CRC OK Enable bit

- 1 = The received packet CRC must be valid for the packet to be accepted

- 0 = Disable CRC filtering

This bit allows the user to reject all packets that have an invalid CRC.

- bit 5 RUNTERREN: Runt Error Collection Enable bit

- 1 = The received packet must be a runt packet for the packet to be accepted

- 0 = Disable Runt Error Collection filtering

This bit allows the user to collect all packets that are runt packets. For this filter, a runt packet is defined as any packet with a size of less than 64 bytes (when CRCOKEN = 0) or any packet with a size of less than 64 bytes that has a valid CRC (when CRCOKEN = 1).

- bit 4 RUNTEN: Runt Enable bit

- 1 = The received packet must not be a runt packet for the packet to be accepted

- 0 = Disable Runt filtering

This bit allows the user to reject all runt packets. For this filter, a runt packet is defined as any packet with a size of less than 64 bytes.

- bit 3 UCEN: Unicast Enable bit

- 1 = Enable Unicast Filtering

- 0 = Disable Unicast Filtering

This bit allows the user to accept all unicast packets whose Destination Address matches the Station Address.

- bit 2 NOTMEEN: Not Me Unicast Enable bit

- 1 = Enable Not Me Unicast Filtering

- 0 = Disable Not Me Unicast Filtering

This bit allows the user to accept all unicast packets whose Destination Address does not match the Station Address.

- bit 1 MCEN: Multicast Enable bit

- 1 = Enable Multicast Filtering

- 0 = Disable Multicast Filtering

This bit allows the user to accept all Multicast Address packets.

- bit 0 BCEN: Broadcast Enable bit

- 1 = Enable Broadcast Filtering

- 0 = Disable Broadcast Filtering

This bit allows the user to accept all Broadcast Address packets.

- **Note 1:** XOR = True when either one or the other conditions are true, but not both.

- 2: This Hash Table Filter match is active regardless of the value of the HTEN bit.

- 3: This Magic Packet Filter match is active regardless of the value of the MPEN bit.

- Note 1: This register is only used for RX operations.

- 2: The bits in this register may only be changed while the RXEN bit (ETHCON1<8>) = 0.

## 27.1 Control Register

### TABLE 27-1: COMPARATOR VOLTAGE REFERENCE REGISTER MAP

| ddress_#)                |                                 | σ.        |       |       |       |       |       |                        |       | Bits                 |      |       |      |       |      |      |      |      | s s        |

|--------------------------|---------------------------------|-----------|-------|-------|-------|-------|-------|------------------------|-------|----------------------|------|-------|------|-------|------|------|------|------|------------|

| Virtual Addr<br>(BF80_#) | Register<br>Name <sup>(1)</sup> | Bit Range | 31/15 | 30/14 | 29/13 | 28/12 | 27/11 | 26/10                  | 25/9  | 24/8                 | 23/7 | 22/6  | 21/5 | 20/4  | 19/3 | 18/2 | 17/1 | 16/0 | All Resets |

| 0000                     | OV/DOOM                         | 31:16     | _     | _     | _     | _     | _     | _                      | _     | _                    | _    | _     | _    | _     | _    | _    | _    | _    | 0000       |

| 9800                     | CVRCON                          | 15:0      | ON    | _     | _     | _     | _     | VREFSEL <sup>(2)</sup> | BGSEL | <1:0> <sup>(2)</sup> | _    | CVROE | CVRR | CVRSS |      | CVR< | 3:0> |      | 0100       |

**Legend:** x = unknown value on Reset; — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

Note 1: All registers in this table have corresponding CLR, SET and INV registers at their virtual addresses, plus offsets of 0x4, 0x8 and 0xC, respectively. See Section 12.1.1 "CLR, SET and INV Registers" for more information.

PIC32MX5XX/6XX/7XX

2: These bits are not available on PIC32MX575/675/695/775/795 devices. On these devices, reset value for CVRCON is '0000'.

## TABLE 29-1: DEVCFG: DEVICE CONFIGURATION WORD SUMMARY

| ess                         |                  | е         |           |          |       |        |                                                                                                                           |       |             | Bit    | s      |      |            |      |      |      |             |      | <sub>o</sub> |

|-----------------------------|------------------|-----------|-----------|----------|-------|--------|---------------------------------------------------------------------------------------------------------------------------|-------|-------------|--------|--------|------|------------|------|------|------|-------------|------|--------------|

| Virtual Address<br>(BFC0_#) | Register<br>Name | Bit Range | 31/15     | 30/14    | 29/13 | 28/12  | 27/11                                                                                                                     | 26/10 | 25/9        | 24/8   | 23/7   | 22/6 | 21/5       | 20/4 | 19/3 | 18/2 | 17/1        | 16/0 | All Resets   |

| ٥٦٥٥                        | DEVOCA           | 31:16     | FVBUSONIO | FUSBIDIO | _     |        | −         FCANIO         FETHIO         FMIIEN         −         −         −         −         FSRSSEL<2:0>         xxxxx |       |             |        |        |      |            |      |      | xxxx |             |      |              |

| 2770                        | DEVCFG3          | 15:0      |           |          |       |        |                                                                                                                           |       |             | USERID | <15:0> |      |            |      |      |      |             |      | xxxx         |

| 2554                        | DEVCFG2          | 31:16     | _         | _        | _     | I      | _                                                                                                                         | _     | I           | 1      | _      |      | _          |      | _    | FF   | PLLODIV<2:0 | )>   | xxxx         |

| 2                           | DEVCFG2          | 15:0      | UPLLEN    | _        | _     | I      | -                                                                                                                         | UI    | PLLIDIV<2:0 | >      | _      | F    | PLLMUL<2:0 | )>   | _    | F    | PLLIDIV<2:0 | >    | xxxx         |

| 2550                        | DEVCFG1          | 31:16     | _         | _        | _     | -      | FWDTEN WDTPS<4:0> xx:                                                                                                     |       |             |        |        |      |            | xxxx |      |      |             |      |              |

| 2770                        | DEVCEGI          | 15:0      | FCKSM     | <1:0>    | FPBDI | V<1:0> | —         OSCIOFNC         POSCMOD         1:50         —         FSOSCEN         —         —         FNOSC<2:0>          |       |             |        |        | xxxx |            |      |      |      |             |      |              |

| 2FFC                        | DEVCFG0          | 31:16     | _         | _        |       | CP     | _                                                                                                                         | _     | _           | BWP    | _      | _    | _          | _    |      | PWP. | <7:4>       |      | xxxx         |

| 2550                        | DEVCEGO          | 15:0      |           | PWP<     | 3:0>  |        | DEBUG<1:0> _ xx                                                                                                           |       |             |        |        |      |            |      | xxxx |      |             |      |              |

PIC32MX5XX/6XX/7XX

x = unknown value on Reset; — = unimplemented, read as '0'. Reset values are shown in hexadecimal. Legend:

## TABLE 29-2: DEVICE ID, REVISION, AND CONFIGURATION SUMMARY

| ess                         |                  | 0         |                  |              |       |       |       |       |      | Ві   | ts   |       |         |      |        |       |      |       | (1)        |

|-----------------------------|------------------|-----------|------------------|--------------|-------|-------|-------|-------|------|------|------|-------|---------|------|--------|-------|------|-------|------------|

| Virtual Address<br>(BF80_#) | Register<br>Name | Bit Range | 31/15            | 30/14        | 29/13 | 28/12 | 27/11 | 26/10 | 25/9 | 24/8 | 23/7 | 22/6  | 21/5    | 20/4 | 19/3   | 18/2  | 17/1 | 16/0  | All Resets |

| F200                        | DDDCON           | 31:16     | _                | _            | _     | _     |       |       |      |      |      |       |         |      |        | 0000  |      |       |            |

| F200                        | DDPCON           | 15:0      | 1                | _            | _     | _     | _     | _     | _    | _    | _    | _     | _       | _    | JTAGEN | TROEN | _    | TDOEN | 0008       |

| F000                        | DEVID            | 31:16     |                  | VER-         | <3:0> |       |       |       |      |      |      | DEVID | <27:16> |      |        |       |      |       | xxxx       |

| F220                        | DEVID            | 15:0      | DEVID<15:0> xxxx |              |       |       |       |       |      |      |      |       |         |      | xxxx   |       |      |       |            |

| F000                        | CVCKEV           | 31:16     | SYSKEY-31:05     |              |       |       |       |       |      |      |      |       |         | 0000 |        |       |      |       |            |

| F230                        | SYSKEY           | 15:0      |                  | SYSKEY<31:0> |       |       |       |       |      |      |      |       |         |      |        | 0000  |      |       |            |

Legend: x = unknown value on Reset; — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

Reset values are dependent on the device variant. Refer to "PIC32MX5XX/6XX/TXX Family Silicon Errata and Data Sheet Clarification" (DS80000480) for more information.

#### REGISTER 29-4: DEVCFG3: DEVICE CONFIGURATION WORD 3

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2     | Bit<br>25/17/9/1      | Bit<br>24/16/8/0      |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-----------------------|-----------------------|-----------------------|

| 31:24        | R/P               | R/P               | r-1               | r-1               | r-1               | R/P                   | R/P                   | R/P                   |

|              | FVBUSONIO         | FUSBIDIO          | _                 | _                 | _                 | FCANIO <sup>(1)</sup> | FETHIO <sup>(2)</sup> | FMIIEN <sup>(2)</sup> |

| 23:16        | r-1               | r-1               | r-1               | r-1               | r-1               | R/P                   | R/P                   | R/P                   |

|              | _                 | _                 | _                 | _                 | _                 | FSRSSEL<2:0>          |                       |                       |

| 15:8         | R/P               | R/P               | R/P               | R/P               | R/P               | R/P                   | R/P                   | R/P                   |

|              | USERID<15:8>      |                   |                   |                   |                   |                       |                       |                       |

| 7:0          | R/P               | R/P               | R/P               | R/P               | R/P               | R/P                   | R/P                   | R/P                   |

|              | USERID<7:0>       |                   |                   |                   |                   |                       |                       |                       |

Legend:r = Reserved bitP = Programmable bitR = Readable bitW = Writable bitU = Unimplemented bit, read as '0'<math>-n = Value at POR'1' = Bit is set'0' = Bit is clearedx = Bit is unknown

bit 31 FVBUSONIO: USB VBUSON Selection bit

1 = VBUSON pin is controlled by the USB module 0 = VBUSON pin is controlled by the port function

bit 30 FUSBIDIO: USB USBID Selection bit

1 = USBID pin is controlled by the USB module0 = USBID pin is controlled by the port function

bit 29-27 Reserved: Write '1'

bit 26 FCANIO: CAN I/O Pin Selection bit<sup>(1)</sup>

1 = Default CAN I/O Pins 0 = Alternate CAN I/O Pins

bit 25 **FETHIO:** Ethernet I/O Pin Selection bit<sup>(2)</sup>

1 = Default Ethernet I/O Pins 0 = Alternate Ethernet I/O Pins

bit 24 **FMIIEN**: Ethernet MII Enable bit<sup>(2)</sup>

1 = MII is enabled 0 = RMII is enabled bit 23-19 **Reserved:** Write '1'

bit 18-16 FSRSSEL<2:0>: SRS Select bits

111 = Assign Interrupt Priority 7 to a shadow register set

110 = Assign Interrupt Priority 6 to a shadow register set

•

001 = Assign Interrupt Priority 1 to a shadow register set

000 = All interrupt priorities are assigned to a shadow register set

bit 15-0 USERID<15:0>: User ID bits

This is a 16-bit value that is user-defined and is readable via ICSP™ and JTAG.

Note 1: This bit is Reserved and reads '1' on PIC32MX664/675/695 devices.

2: This bit is Reserved and reads '1' on PIC32MX534/564/575 devices.

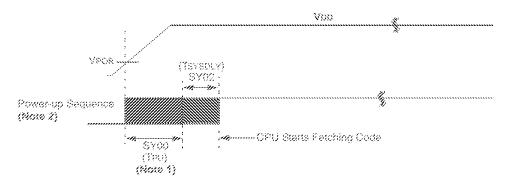

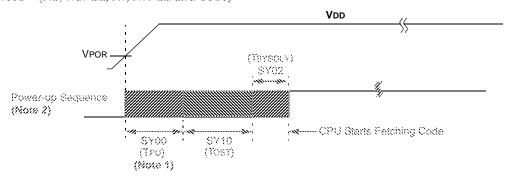

## FIGURE 32-4: POWER-ON RESET TIMING CHARACTERISTICS

Internal Voltage Regulator Enabled

Clock Sources = (FRC, FRCDIV, FRCDIV16, FRCPLL, EC, ECPLL and LPRC)

Internal Voltage Regulator Enabled Clock Sources = (NS, MSPLL, XT, XTPLL and Sosc)

Note 1: The power-up period will be extended if the power-up sequence completes before the device exits from BOR (VDD < VDDMIN).

2: Includes interval voltage regulator stabilization delay.

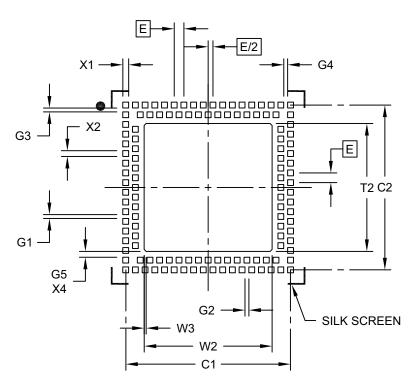

## 124-Very Thin Leadless Array Package (TL) – 9x9x0.9 mm Body [VTLA]

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

RECOMMENDED LAND PATTERN

| Units                                |    | MILLIMETERS |          |      |

|--------------------------------------|----|-------------|----------|------|

| Dimension Limits                     |    | MIN         | NOM      | MAX  |

| Contact Pitch                        |    |             | 0.50 BSC |      |

| Pad Clearance                        | G1 | 0.20        |          |      |

| Pad Clearance                        | G2 | 0.20        |          |      |

| Pad Clearance                        | G3 | 0.20        |          |      |

| Pad Clearance                        | G4 | 0.20        |          |      |

| Contact to Center Pad Clearance (X4) | G5 | 0.30        |          |      |

| Optional Center Pad Width            | T2 |             |          | 6.60 |

| Optional Center Pad Length           | W2 |             |          | 6.60 |

| Optional Center Pad Chamfer (X4)     | W3 |             | 0.10     |      |

| Contact Pad Spacing                  | C1 |             | 8.50     |      |

| Contact Pad Spacing                  | C2 |             | 8.50     |      |

| Contact Pad Width (X124)             | X1 |             |          | 0.30 |

| Contact Pad Length (X124)            |    |             |          | 0.30 |

#### Notes:

1. Dimensioning and tolerancing per ASME Y14.5M

BSC: Basic Dimension. Theoretically exact value shown without tolerances.

Microchip Technology Drawing No. C04-2193A

TABLE B-1: MAJOR SECTION UPDATES (CONTINUED)

| Section Name                                    | Update Description                                                                                                                               |

|-------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------|

| 4.0 "Memory Organization"                       | Updated all register tables to include the Virtual Address and All Resets                                                                        |

|                                                 | columns.                                                                                                                                         |

|                                                 | Updated the title of Figure 4-4 to include the PIC32MX575F256L device.                                                                           |

|                                                 | Updated the title of Figure 4-6 to include the PIC32MX695F512L and PIC32MX695F512H devices. Also changed PIC32MX795F512L to PIC32MX795F512H.     |

|                                                 | Updated the title of Table 4-3 to include the PIC32MX695F512H device.                                                                            |

|                                                 | Updated the title of Table 4-5 to include the PIC32MX575F5256L device.                                                                           |

|                                                 | Updated the title of Table 4-6 to include the PIC32MX695F512L device.                                                                            |

|                                                 | Reversed the order of Table 4-11 and Table 4-12.                                                                                                 |

|                                                 | Reversed the order of Table 4-14 and Table 4-15.                                                                                                 |

|                                                 | Updated the title of Table 4-15 to include the PIC32MX575F256L and PIC32MX695F512L devices.                                                      |

|                                                 | Updated the title of Table 4-45 to include the PIC32MX575F256L device.                                                                           |

|                                                 | Updated the title of Table 4-47 to include the PIC32MX695F512H and PIC32MX695F512L devices.                                                      |

| 1.0 "I/O Ports"                                 | Updated the second paragraph of <b>1.1.2 "Digital Inputs"</b> and removed Table 12-1.                                                            |

| 22.0 "10-bit Analog-to-Digital Converter (ADC)" | Updated the ADC Conversion Clock Period Block Diagram (see Figure 22-2).                                                                         |

| 1.0 "Special Features"                          | Removed references to the ENVREG pin in 1.3 "On-Chip Voltage Regulator".                                                                         |

|                                                 | Updated the first sentence of 1.3.1 "On-Chip Regulator and POR" and 1.3.2 "On-Chip Regulator and BOR".                                           |

|                                                 | Updated the Connections for the On-Chip Regulator (see Figure 1-2).                                                                              |

| 1.0 "Electrical Characteristics"                | Updated the Absolute Maximum Ratings and added Note 3.                                                                                           |

|                                                 | Added Thermal Packaging Characteristics for the 121-pin XBGA package (see Table 1-3).                                                            |

|                                                 | Updated the Operating Current (IDD) DC Characteristics (see Table 1-5).                                                                          |

|                                                 | Updated the Idle Current (IIDLE) DC Characteristics (see Table 1-6).                                                                             |

|                                                 | Updated the Power-Down Current (IPD) DC Characteristics (see Table 1-7).                                                                         |

|                                                 | Removed Note 1 from the Program Flash Memory Wait State Characteristics (see Table 1-12).                                                        |

|                                                 | Updated the SPIx Module Slave Mode (CKE = 1) Timing Characteristics, changing SP52 to SP35 between the MSb and Bit 14 on SDOx (see Figure 1-13). |

| 1.0 "Packaging Information"                     | Added the 121-pin XBGA package marking information and package details.                                                                          |

| "Product Identification System"                 | Added the definition for BG (121-lead 10x10x1.1 mm, XBGA).                                                                                       |

|                                                 | Added the definition for Speed.                                                                                                                  |

### PRODUCT IDENTIFICATION SYSTEM

To order or obtain information, e.g., on pricing or delivery, refer to the factory or the listed sales office.

| PIC32 MX 5XX F 512 H T - 80 I      | <u>PT</u> - <u>XXX</u> |

|------------------------------------|------------------------|

| Microchip Brand                    |                        |

| Architecture                       |                        |

| Product Groups                     |                        |

| Flash Memory Family                |                        |

| Program Memory Size (KB)           |                        |

| Pin Count                          |                        |

| Tape and Reel Flag (if applicable) |                        |

| Speed (see Note 1)                 |                        |

| Temperature Range                  |                        |

| Package                            | _                      |

| Pattern                            |                        |

#### Example:

PIC32MX575F256H-80I/PT: General purpose PIC32, 32-bit RISC MCU, 256 KB program memory, 64-pin, Industrial temperature, TQFP package.

#### Flash Memory Family

Architecture MX = 32-bit RISC MCU core

Product Groups 5XX = General purpose microcontroller family

6XX = General purpose microcontroller family

7XX = General purpose microcontroller family

Flash Memory Family F = Flash program memory

Program Memory Size 64 = 64K

128 = 128K 256 = 256K512 = 512K

Pin Count H = 64-pin

= 100-pin, 121-pin, 124-pin

Speed (see Note 1) Blank or 80 = 80 MHz

= -40°C to +85°C (Industrial) Temperature Range

= -40°C to +105°C (V-Temp)

PT = 64-Lead (10x10x1 mm) TQFP (Thin Quad Flatpack) Package

PT = 100-Lead (12x12x1 mm) TQFP (Thin Quad Flatpack)

PF = 100-Lead (14x14x1 mm) TQFP (Thin Quad Flatpack) MR = 64-Lead (9x9x0.9 mm) QFN (Plastic Quad Flat)

BG = 121-Lead (10x10x1.1 mm) TFBGA (Plastic Thin Profile Ball Grid Array)

TL = 124-Lead (9x9x0.9 mm) VTLA (Very Thin Leadless Array)

Pattern Three-digit QTP, SQTP, Code or Special Requirements (blank otherwise)

ES = Engineering Sample

This option is not available for PIC32MX534/564/664/764 devices. Note