Welcome to E-XFL.COM

### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

# Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

## Details

-·XE

| Product Status             | Active                                                                           |

|----------------------------|----------------------------------------------------------------------------------|

| Core Processor             | MIPS32® M4K™                                                                     |

| Core Size                  | 32-Bit Single-Core                                                               |

| Speed                      | 80MHz                                                                            |

| Connectivity               | Ethernet, I <sup>2</sup> C, SPI, UART/USART, USB OTG                             |

| Peripherals                | Brown-out Detect/Reset, DMA, POR, PWM, WDT                                       |

| Number of I/O              | 53                                                                               |

| Program Memory Size        | 512KB (512K x 8)                                                                 |

| Program Memory Type        | FLASH                                                                            |

| EEPROM Size                | -                                                                                |

| RAM Size                   | 128K x 8                                                                         |

| Voltage - Supply (Vcc/Vdd) | 2.3V ~ 3.6V                                                                      |

| Data Converters            | A/D 16x10b                                                                       |

| Oscillator Type            | Internal                                                                         |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                                |

| Mounting Type              | Surface Mount                                                                    |

| Package / Case             | 64-VFQFN Exposed Pad                                                             |

| Supplier Device Package    | 64-VQFN (9x9)                                                                    |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic32mx695f512h-80i-mr |

|                            |                                                                                  |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

#### **TABLE 13:** PIN NAMES FOR 124-PIN USB, ETHERNET, AND CAN DEVICES (CONTINUED)

| 124               | 4-PIN VTLA (BOTTOM VIEW) <sup>(2,3)</sup>             |     |                   | A34                       |                           |

|-------------------|-------------------------------------------------------|-----|-------------------|---------------------------|---------------------------|

|                   |                                                       | B13 | B29               |                           | Conductive<br>Thermal Pad |

|                   | PIC32MX675F512L<br>PIC32MX695F512L<br>PIC32MX795F512L | B1  | B56               | B41                       | A51                       |

|                   | A1                                                    |     |                   |                           |                           |

|                   | Polarity Indicator                                    |     | A68               |                           |                           |

| Package<br>Bump # | Full Pin Name                                         |     | Package<br>Bump # | F                         | ull Pin Name              |

| B8                | Vss                                                   |     | B33               | TDO/RA5                   |                           |

| B9                | TMS/RA0                                               |     | B34               | OSC1/CLKI/RC              | 212                       |

| B10               | AERXD1/INT2/RE9                                       |     | B35               | No Connect (N             | C)                        |

| B11               | AN4/C1IN-/CN6/RB4                                     |     | B36               | AETXCLK/SCL               | .1/INT3/RA14              |

| B12               | Vss                                                   |     | B37               | RTCC/EMDIO/               | AEMDIO/IC1/RD8            |

| B13               | AN2/C2IN-/CN4/RB2                                     |     | B38               | SCK1/IC3/PMC              | CS2/PMA15/RD10            |

| B14               | PGED1/AN0/CN2/RB0                                     |     | B39               | SDO1/OC1/INT              | [0/RD0                    |

| B15               | No Connect (NC)                                       |     | B40               | SOSCO/T1CK/               | CN0/RC14                  |

| B16               | PGED2/AN7/RB7                                         |     | B41               | Vss                       |                           |

| B17               | VREF+/CVREF+/AERXD3/PMA6/RA10                         |     | B42               | OC3/RD2                   |                           |

| B18               | AVss                                                  |     | B43               | ETXD2/IC5/PN              | ID12/RD12                 |

| B19               | AN9/C2OUT/RB9                                         |     | B44               | OC5/PMWR/CI               | N13/RD4                   |

| B20               | AN11/ERXERR/AETXERR/PMA12/RB11                        |     | B45               | ETXEN/PMD14               | 4/CN15/RD6                |

| B21               | Vdd                                                   |     | B46               | Vss                       |                           |

| B22               | AC1TX/SCK4/U5TX/U2RTS/RF13                            |     | B47               | No Connect (N             | C)                        |

| B23               | AN12/ERXD0/AECRS/PMA11/RB12                           |     | B48               | VCAP                      |                           |

| B24               | AN14/ERXD2/AETXD3/PMALH/PMA1/RB14                     |     | B49               | C1RX <sup>(1)</sup> /ETXD | 1/PMD11/RF0               |

| B25               | Vss                                                   |     | B50               | C2TX <sup>(1)</sup> /ETXE | RR/PMD9/RG1               |

| B26               | AETXD0/SS3/U4RX/U1CTS/CN20/RD14                       |     | B51               | TRCLK/RA6                 |                           |

| B27               | SDA5/SDI4/U2RX/PMA9/CN17/RF4                          |     | B52               | PMD0/RE0                  |                           |

| B28               | No Connect (NC)                                       |     | B53               | Vdd                       |                           |

| B29               | SCL3/SDO3/U1TX/RF8                                    |     | B54               | TRD2/RG14                 |                           |

| B30               | VUSB3V3                                               |     | B55               | TRD0/RG13                 |                           |

| B31               | D+/RG2                                                |     | B56               | PMD3/RE3                  |                           |

This pin is only available on PIC32MX795F512L devices. Note 1:

2:

Shaded package bumps are 5V tolerant. It is recommended that the user connect the printed circuit board (PCB) ground to the conductive thermal pad on the bottom of the package. And to not run non-Vss PCB traces under the conductive thermal pad on the same side of the PCB layout. 3:

# TABLE 1-1: PINOUT I/O DESCRIPTIONS (CONTINUED)

|          |                                               | Pin Nun         | nber <sup>(1)</sup> |                 | D:          | Duffer               |                                                   |  |

|----------|-----------------------------------------------|-----------------|---------------------|-----------------|-------------|----------------------|---------------------------------------------------|--|

| Pin Name | 64-Pin<br>QFN/TQFP                            | 100-Pin<br>TQFP | 121-Pin<br>TFBGA    | 124-pin<br>VTLA | Pin<br>Type | Buffer<br>Type       | Description                                       |  |

| RG0      | —                                             | 90              | A5                  | A61             | I/O         | ST                   | PORTG is a bidirectional I/O port                 |  |

| RG1      | —                                             | 89              | E6                  | B50             | I/O         | ST                   |                                                   |  |

| RG6      | 4                                             | 10              | E3                  | A7              | I/O         | ST                   |                                                   |  |

| RG7      | 5                                             | 11              | F4                  | B6              | I/O         | ST                   |                                                   |  |

| RG8      | 6                                             | 12              | F2                  | A8              | I/O         | ST                   |                                                   |  |

| RG9      | 8                                             | 14              | F3                  | A9              | I/O         | ST                   |                                                   |  |

| RG12     | —                                             | 96              | C3                  | A65             | I/O         | ST                   |                                                   |  |

| RG13     | —                                             | 97              | A3                  | B55             | I/O         | ST                   | -                                                 |  |

| RG14     | —                                             | 95              | C4                  | B54             | I/O         | ST                   |                                                   |  |

| RG15     | —                                             | 1               | B2                  | A2              | I/O         | ST                   |                                                   |  |

| RG2      | 37                                            | 57              | H10                 | B31             | Ι           | ST                   | PORTG input pins                                  |  |

| RG3      | 36                                            | 56              | J11                 | A38             | I           | ST                   |                                                   |  |

| T1CK     | 48                                            | 74              | B11                 | B40             |             | ST                   | Timer1 external clock input                       |  |

| T2CK     | —                                             | 6               | D1                  | A5              | I           | ST                   | Timer2 external clock input                       |  |

| T3CK     | —                                             | 7               | E4                  | B4              |             | ST                   | Timer3 external clock input                       |  |

| T4CK     | —                                             | 8               | E2                  | A6              |             | ST                   | Timer4 external clock input                       |  |

| T5CK     | —                                             | 9               | E1                  | B5              |             | ST                   | Timer5 external clock input                       |  |

| U1CTS    | 43                                            | 47              | L9                  | B26             |             | ST                   | UART1 clear to send                               |  |

| U1RTS    | 49                                            | 48              | K9                  | A31             | 0           |                      | UART1 ready to send                               |  |

| U1RX     | 50                                            | 52              | K11                 | A36             | I           | ST                   | UART1 receive                                     |  |

| U1TX     | 51                                            | 53              | J10                 | B29             | 0           | _                    | UART1 transmit                                    |  |

| U3CTS    | 8                                             | 14              | F3                  | A9              | I           | ST                   | UART3 clear to send                               |  |

| U3RTS    | 4                                             | 10              | E3                  | A7              | 0           | _                    | UART3 ready to send                               |  |

| U3RX     | 5                                             | 11              | F4                  | B6              | I           | ST                   | UART3 receive                                     |  |

| U3TX     | 6                                             | 12              | F2                  | A8              | 0           | _                    | UART3 transmit                                    |  |

| U2CTS    | 21                                            | 40              | K6                  | A27             | I           | ST                   | UART2 clear to send                               |  |

| U2RTS    | 29                                            | 39              | L6                  | B22             | 0           |                      | UART2 ready to send                               |  |

| U2RX     | 31                                            | 49              | L10                 | B27             | I           | ST                   | UART2 receive                                     |  |

| U2TX     | 32                                            | 50              | L11                 | A32             | 0           |                      | UART2 transmit                                    |  |

| U4RX     | 43                                            | 47              | L9                  | B26             | 1           | ST                   | UART4 receive                                     |  |

| U4TX     | 49                                            | 48              | K9                  | A31             | 0           | _                    | UART4 transmit                                    |  |

| U6RX     | 8                                             | 14              | F3                  | A9              | I           | ST                   | UART6 receive                                     |  |

| U6TX     | 4                                             | 10              | E3                  | A7              | 0           | _                    | UART6 transmit                                    |  |

| U5RX     | 21                                            | 40              | K6                  | A27             | I           | ST                   | UART5 receive                                     |  |

| U5TX     | 29                                            | 39              | L6                  | B22             | 0           |                      | UART5 transmit                                    |  |

| SCK1     | _                                             | 70              | D11                 | B38             | I/O         | ST                   | Synchronous serial clock input/output<br>for SPI1 |  |

| 5        | CMOS = CMO<br>ST = Schmitt T<br>TL = TTL inpu | rigger input    |                     |                 |             | nalog = A<br>= Outpu | Analog input P = Power                            |  |

Note 1: Pin numbers are only provided for reference. See the "Device Pin Tables" section for device pin availability.

2: See 25.0 "Ethernet Controller" for more information.

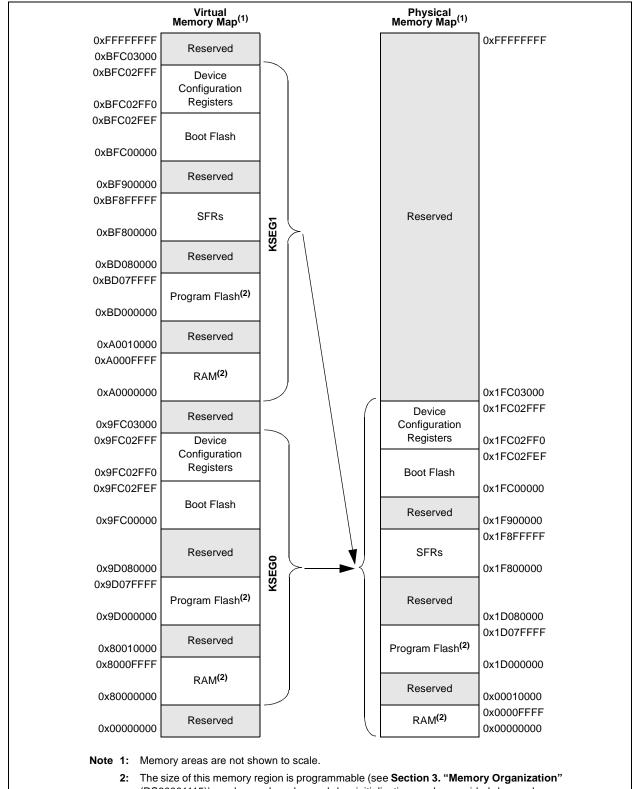

## FIGURE 4-5: MEMORY MAP ON RESET FOR PIC32MX575F512H, PIC32MX575F512L, PIC32MX675F512H, PIC32MX675F512L, PIC32MX775F512H AND PIC32MX775F512L DEVICES

(DS60001115)) and can be changed by initialization code provided by end user development tools (refer to the specific development tool documentation for information).

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |  |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|--|--|

| 04.04        | W-0               | W-0               | W-0               | W-0               | W-0               | W-0               | W-0              | W-0              |  |  |

| 31:24        |                   |                   |                   | NVMKE             | Y<31:24>          |                   |                  |                  |  |  |

| 00.40        | W-0               | W-0               | W-0               | W-0               | W-0               | W-0               | W-0              | W-0              |  |  |

| 23:16        | NVMKEY<23:16>     |                   |                   |                   |                   |                   |                  |                  |  |  |

| 45.0         | W-0               | W-0               | W-0               | W-0               | W-0               | W-0               | W-0              | W-0              |  |  |

| 15:8         |                   |                   |                   | NVMK              | EY<15:8>          |                   |                  |                  |  |  |

| 7.0          | W-0               | W-0               | W-0               | W-0               | W-0               | W-0               | W-0              | W-0              |  |  |

| 7:0          |                   |                   |                   | NVMK              | EY<7:0>           |                   |                  |                  |  |  |

# REGISTER 5-2: NVMKEY: PROGRAMMING UNLOCK REGISTER

# Legend:R = Readable bitW = Writable bitU = Unimplemented bit, read as '0'-n = Value at POR'1' = Bit is set'0' = Bit is clearedx = Bit is unknown

# bit 31-0 NVMKEY<31:0>: Unlock Register bits

These bits are write-only, and read as '0' on any read.

Note: This register is used as part of the unlock sequence to prevent inadvertent writes to the PFM.

# REGISTER 5-3: NVMADDR: FLASH ADDRESS REGISTER

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |  |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|--|--|

| 24.24        | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |

| 31:24        |                   |                   |                   | NVMADI            | DR<31:24>         |                   |                  |                  |  |  |

| 00.40        | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |

| 23:16        | NVMADDR<23:16>    |                   |                   |                   |                   |                   |                  |                  |  |  |

| 45.0         | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |

| 15:8         |                   |                   |                   | NVMAD             | DR<15:8>          |                   |                  |                  |  |  |

| 7.0          | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |

| 7:0          |                   |                   |                   | NVMAE             | DDR<7:0>          |                   |                  |                  |  |  |

| Legend:           |                  |                           |                    |

|-------------------|------------------|---------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, re | ad as '0'          |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared      | x = Bit is unknown |

bit 31-0 NVMADDR<31:0>: Flash Address bits Bulk/Chip/PFM Erase: Address is ignored. Page Erase: Address identifies the page to erase. Row Program: Address identifies the row to program. Word Program: Address identifies the word to program.

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |  |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|--|--|

| 04.04        | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |

| 31:24        |                   |                   |                   | NVMDA             | TA<31:24>         |                   |                  |                  |  |  |

| 00.40        | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |

| 23:16        | NVMDATA<23:16>    |                   |                   |                   |                   |                   |                  |                  |  |  |

| 45.0         | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |

| 15:8         |                   |                   |                   | NVMDA             | TA<15:8>          |                   |                  |                  |  |  |

| 7.0          | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |

| 7:0          |                   |                   |                   | NVMD/             | ATA<7:0>          |                   |                  |                  |  |  |

## REGISTER 5-4: NVMDATA: FLASH PROGRAM DATA REGISTER

| Legend:           |                  |                           |                    |

|-------------------|------------------|---------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, re | ad as '0'          |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared      | x = Bit is unknown |

bit 31-0 NVMDATA<31:0>: Flash Programming Data bits

**Note:** The bits in this register are only reset by a Power-on Reset (POR).

# REGISTER 5-5: NVMSRCADDR: SOURCE DATA ADDRESS REGISTER

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |  |  |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|--|--|--|

| 04.04        | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |  |

| 31:24        |                   |                   |                   | NVMSRCA           | DDR<31:24>        | >                 |                  |                  |  |  |  |

| 00.40        | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |  |

| 23:16        |                   | NVMSRCADDR<23:16> |                   |                   |                   |                   |                  |                  |  |  |  |

| 45.0         | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |  |

| 15:8         |                   |                   |                   | NVMSRC/           | ADDR<15:8>        |                   |                  |                  |  |  |  |

| 7.0          | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |  |

| 7:0          |                   |                   |                   | NVMSRC            | ADDR<7:0>         |                   |                  |                  |  |  |  |

| Legend:           |                  |                           |                    |

|-------------------|------------------|---------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, re | ad as '0'          |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared      | x = Bit is unknown |

# bit 31-0 NVMSRCADDR<31:0>: Source Data Address bits

The system physical address of the data to be programmed into the Flash when the NVMOP<3:0> bits (NVMCON<3:0>) are set to perform row programming.

| Bit<br>Range | Bit<br>31/23/15/7          | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3    | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |  |

|--------------|----------------------------|-------------------|-------------------|-------------------|----------------------|-------------------|------------------|------------------|--|--|

| 31:24        | U-0                        | U-0               | U-0               | U-0               | U-0                  | U-0               | U-0              | U-0              |  |  |

| 31.24        | —                          |                   | _                 |                   | _                    | _                 | _                | —                |  |  |

| 22.16        | R/W-1                      | R/W-1             | R/W-1             | R/W-1             | R/W-1                | R/W-1             | R/W-1            | R/W-1            |  |  |

| 23:16        | CHAIRQ<7:0> <sup>(1)</sup> |                   |                   |                   |                      |                   |                  |                  |  |  |

| 15.0         | R/W-1                      | R/W-1             | R/W-1             | R/W-1             | R/W-1                | R/W-1             | R/W-1            | R/W-1            |  |  |

| 15:8         |                            |                   |                   | CHSIRQ<           | <7:0> <sup>(1)</sup> |                   |                  |                  |  |  |

| 7:0          | S-0                        | S-0               | R/W-0             | R/W-0             | R/W-0                | U-0               | U-0              | U-0              |  |  |

| 7.0          | CFORCE                     | CABORT            | PATEN             | SIRQEN            | AIRQEN               | _                 | _                | —                |  |  |

# REGISTER 10-8: DCHxECON: DMA CHANNEL 'x' EVENT CONTROL REGISTER

| Legend:           | S = Settable bit |                      |                    |

|-------------------|------------------|----------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented b  | it, read as '0'    |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared | x = Bit is unknown |

# bit 31-24 Unimplemented: Read as '0'

| bit 23-16 | CHAIRQ<7:0>: Channel Transfer Abort IRQ bits <sup>(1)</sup>                                                                                                                  |

|-----------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|           | 11111111 = Interrupt 255 will abort any transfers in progress and set CHAIF flag                                                                                             |

|           | •                                                                                                                                                                            |

|           | •                                                                                                                                                                            |

|           | •                                                                                                                                                                            |

|           | 00000001 = Interrupt 1 will abort any transfers in progress and set CHAIF flag<br>00000000 = Interrupt 0 will abort any transfers in progress and set CHAIF flag             |

| bit 15-8  | CHSIRQ<7:0>: Channel Transfer Start IRQ bits <sup>(1)</sup>                                                                                                                  |

|           | 11111111 = Interrupt 255 will initiate a DMA transfer                                                                                                                        |

|           | •                                                                                                                                                                            |

|           | •                                                                                                                                                                            |

|           | •                                                                                                                                                                            |

|           | 00000001 = Interrupt 1 will initiate a DMA transfer<br>00000000 = Interrupt 0 will initiate a DMA transfer                                                                   |

| bit 7     | CFORCE: DMA Forced Transfer bit                                                                                                                                              |

|           | <ul> <li>1 = A DMA transfer is forced to begin when this bit is written to a '1'</li> <li>0 = This bit always reads '0'</li> </ul>                                           |

| bit 6     | CABORT: DMA Abort Transfer bit                                                                                                                                               |

|           | <ul> <li>1 = A DMA transfer is aborted when this bit is written to a '1'</li> <li>0 = This bit always reads '0'</li> </ul>                                                   |

| bit 5     | PATEN: Channel Pattern Match Abort Enable bit                                                                                                                                |

|           | <ul><li>1 = Abort transfer and clear CHEN on pattern match</li><li>0 = Pattern match is disabled</li></ul>                                                                   |

| bit 4     | SIRQEN: Channel Start IRQ Enable bit                                                                                                                                         |

|           | <ul> <li>1 = Start channel cell transfer if an interrupt matching CHSIRQ occurs</li> <li>0 = Interrupt number CHSIRQ is ignored and does not start a transfer</li> </ul>     |

| bit 3     | AIRQEN: Channel Abort IRQ Enable bit                                                                                                                                         |

|           | <ul> <li>1 = Channel transfer is aborted if an interrupt matching CHAIRQ occurs</li> <li>0 = Interrupt number CHAIRQ is ignored and does not terminate a transfer</li> </ul> |

| bit 2-0   | Unimplemented: Read as '0'                                                                                                                                                   |

|           |                                                                                                                                                                              |

Note 1: See Table 7-1: "Interrupt IRQ, Vector and Bit Location" for the list of available interrupt IRQ sources.

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |  |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|--|--|

| 31:24        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |  |  |

|              |                   |                   | _                 |                   | _                 |                   |                  | —                |  |  |

| 22.16        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |  |  |

| 23:16        |                   | _                 | _                 | _                 | _                 |                   | _                | —                |  |  |

| 45.0         | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |

| 15:8         | CHSSIZ<15:8>      |                   |                   |                   |                   |                   |                  |                  |  |  |

| 7.0          | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |

| 7:0          |                   |                   |                   | CHSSIZ            | <7:0>             |                   |                  |                  |  |  |

# REGISTER 10-12: DCHxSSIZ: DMA CHANNEL 'x' SOURCE SIZE REGISTER

# Legend:

| 3                 |                  |                          |                    |

|-------------------|------------------|--------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, r | ead as '0'         |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared     | x = Bit is unknown |

bit 31-16 Unimplemented: Read as '0'

bit 15-0 CHSSIZ<15:0>: Channel Source Size bits

1111111111111111 = 65,535 byte source size

# REGISTER 10-13: DCHxDSIZ: DMA CHANNEL 'x' DESTINATION SIZE REGISTER

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |  |  |  |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|--|--|--|--|

| 31:24        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |  |  |  |  |

| 31.24        | —                 | _                 | _                 | _                 | —                 | —                 | —                | —                |  |  |  |  |

| 22.46        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |  |  |  |  |

| 23:16        | —                 | _                 | _                 |                   | —                 |                   |                  | —                |  |  |  |  |

| 45.0         | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |  |  |

| 15:8         | CHDSIZ<15:8>      |                   |                   |                   |                   |                   |                  |                  |  |  |  |  |

| 7.0          | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |  |  |

| 7:0          |                   | CHDSIZ<7:0>       |                   |                   |                   |                   |                  |                  |  |  |  |  |

| Legend:           |                  |                          |                    |

|-------------------|------------------|--------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, r | ead as '0'         |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared     | x = Bit is unknown |

| bit 31-16 | Unimplemented: Read as '0' |

|-----------|----------------------------|

|-----------|----------------------------|

# TABLE 11-1: USB REGISTER MAP (CONTINUED)

| ess                         |                                 |           |       |       | · · · |       |       |       |      |      | Bits  |          |       |          |        |        |           |          |            |

|-----------------------------|---------------------------------|-----------|-------|-------|-------|-------|-------|-------|------|------|-------|----------|-------|----------|--------|--------|-----------|----------|------------|

| Virtual Address<br>(BF88_#) | Register<br>Name <sup>(1)</sup> | Bit Range | 31/15 | 30/14 | 29/13 | 28/12 | 27/11 | 26/10 | 25/9 | 24/8 | 23/7  | 22/6     | 21/5  | 20/4     | 19/3   | 18/2   | 17/1      | 16/0     | All Resets |

| 5280                        | U1FRML <sup>(3)</sup>           | 31:16     |       | —     | —     | —     | —     | —     | —    | —    | _     | —        | _     | —        | —      | —      | _         | —        | 0000       |

| 5200                        | OTTRIME                         | 15:0      | —     |       | —     | —     | —     | —     | —    | —    |       |          |       | FRML<    | 7:0>   |        |           |          | 0000       |

| 5290                        | U1FRMH <sup>(3)</sup>           | 31:16     | —     | —     | —     | —     | —     | —     | —    | —    | —     | —        | —     | —        | —      | —      | —         | —        | 0000       |

| 0200                        | 01110                           | 15:0      | —     | —     | —     | —     | —     | —     | —    | —    | _     | —        | _     | -        | —      |        | FRMH<2:0> | •        | 0000       |

| 52A0                        | U1TOK                           | 31:16     | —     | —     | —     | —     | —     | —     | —    | —    | —     | —        | —     | —        | —      | —      | —         | —        | 0000       |

| 02/10                       | orron                           | 15:0      | —     | —     | —     | —     | —     | —     | —    | —    |       | PID      | <3:0> |          |        | EP     | <3:0>     |          | 0000       |

| 52B0                        | U1SOF                           | 31:16     | —     | —     | —     | —     | —     | —     | —    | —    | _     | —        | _     | —        | —      | —      | _         | —        | 0000       |

| 5260                        | 0130F                           | 15:0      | —     | _     | _     | —     | _     | _     | _    |      |       |          |       | CNT<7    | 7:0>   |        |           |          | 0000       |

| 52C0                        | U1BDTP2                         | 31:16     | —     | -     | —     | —     | _     | _     | -    |      | —     | —        |       | —        | —      | _      |           | _        | 0000       |

| 5200                        | OIBDIF2                         | 15:0      | —     | —     | —     | —     | —     | —     | —    | —    |       |          |       | BDTPTRH  | H<7:0> |        |           |          | 0000       |

| 52D0                        | U1BDTP3                         | 31:16     | —     | _     | _     | —     | _     | _     | _    |      | —     | _        |       | —        | _      | _      |           | _        | 0000       |

| 5200                        | UIBDIF3                         | 15:0      | —     | _     | _     | _     | _     | _     | -    |      |       |          |       | BDTPTRU  | J<7:0> |        |           |          | 0000       |

| 5250                        | U1CNFG1                         | 31:16     | —     | _     | _     | —     | _     | _     | _    |      | —     | _        |       | —        | _      | _      |           | _        | 0000       |

| 52E0                        | UTCNFGT                         | 15:0      | —     | _     | _     | —     | _     | _     | _    |      | UTEYE | UOEMON   |       | USBSIDL  | —      | _      |           | UASUSPND | 0001       |

| 5300                        | U1EP0                           | 31:16     | —     | _     | _     | _     | _     | _     | -    |      | —     | _        |       | —        | _      | _      |           | _        | 0000       |

| 5300                        | UIEPU                           | 15:0      | —     | _     | _     | —     | _     | _     | _    |      | LSPD  | RETRYDIS |       | EPCONDIS | EPRXEN | EPTXEN | EPSTALL   | EPHSHK   | 0000       |

| 5310                        | U1EP1                           | 31:16     | —     | _     | _     | —     | _     | _     | _    |      | —     | _        |       | —        | _      | _      |           | _        | 0000       |

| 5310                        | UIEPI                           | 15:0      | —     | _     | _     | _     | _     | _     | _    | _    | —     | _        | -     | EPCONDIS | EPRXEN | EPTXEN | EPSTALL   | EPHSHK   | 0000       |

| 5320                        | U1EP2                           | 31:16     | —     | _     | _     | —     | _     | _     | _    |      | —     | _        |       | —        | _      | _      |           | _        | 0000       |

| 5520                        | UIEFZ                           | 15:0      | _     | _     | _     | _     | _     | _     | _    |      | —     | _        | -     | EPCONDIS | EPRXEN | EPTXEN | EPSTALL   | EPHSHK   | 0000       |

| 5330                        | U1EP3                           | 31:16     | —     | _     | _     | _     | _     | _     | _    | _    | —     | _        | -     | —        | _      | -      |           | _        | 0000       |

| 5330                        | UIEP3                           | 15:0      | —     | _     | _     | —     | _     | _     | _    |      | —     | _        |       | EPCONDIS | EPRXEN | EPTXEN | EPSTALL   | EPHSHK   | 0000       |

| 5340                        | U1EP4                           | 31:16     | _     | _     | -     | -     | -     | -     | -    | _    | _     | _        | _     | —        | -      | _      | _         | _        | 0000       |

| 5540                        | UTEP4                           | 15:0      | —     | _     | _     | _     | _     | _     | _    | _    | —     | _        | -     | EPCONDIS | EPRXEN | EPTXEN | EPSTALL   | EPHSHK   | 0000       |

| 5350                        | U1EP5                           | 31:16     | _     | _     | -     | -     | -     | -     | -    | _    | _     | _        | _     | —        | -      | _      | _         | _        | 0000       |

| 5350                        | UIEP5                           | 15:0      | _     | _     | -     | -     | -     | -     | -    | _    | _     | _        | _     | EPCONDIS | EPRXEN | EPTXEN | EPSTALL   | EPHSHK   | 0000       |

| 5260                        | U1EP6                           | 31:16     |       |       | _     | —     | _     |       | _    | _    | —     |          |       | —        | _      | —      |           |          | 0000       |

| 5360                        | UIEP6                           | 15:0      | _     | _     | -     | -     | -     | -     | -    | _    | _     | _        | _     | EPCONDIS | EPRXEN | EPTXEN | EPSTALL   | EPHSHK   | 0000       |

| 5270                        | U1EP7                           | 31:16     | _     | _     | _     | _     | _     | _     | _    | _    | _     | _        | _     | —        | _      | _      | -         | _        | 0000       |

| 5370                        | UTEPT                           | 15:0      |       |       | _     | _     | _     |       | _    | _    | —     |          |       | EPCONDIS | EPRXEN | EPTXEN | EPSTALL   | EPHSHK   | 0000       |

| 5200                        |                                 | 31:16     | _     | _     | _     | _     | _     | _     | _    | —    | -     | —        | _     | —        | _      | —      | _         | _        | 0000       |

| 5380                        | U1EP8                           | 15:0      | —     | _     | —     | —     | _     | _     | —    | _    | _     | _        | -     | EPCONDIS | EPRXEN | EPTXEN | EPSTALL   | EPHSHK   | 0000       |

| 5000                        |                                 | 31:16     | _     | —     | _     | _     | _     | _     | _    | —    | _     | _        | _     | —        | —      | —      | —         | —        | 0000       |

| 5390                        | U1EP9                           | 15:0      | _     | —     | _     | _     | _     | _     | _    | _    | _     | _        | _     | EPCONDIS | EPRXEN | EPTXEN | EPSTALL   | EPHSHK   | 0000       |

5390

U1EP9

Legend:

x =

Note

1:

All n

end: x = unknown value on Reset; — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

1: All registers in this table (except as noted) have corresponding CLR, SET and INV registers at its virtual address, plus an offset of 0x4, 0x8 and 0xC respectively. See Section 12.1.1 "CLR, SET and INV Registers" for more information.

2: This register does not have associated SET and INV registers.

3: This register does not have associated CLR, SET and INV registers.

4: Reset value for this bit is undefined.

NOTES:

# REGISTER 13-1: T1CON: TYPE A TIMER CONTROL REGISTER (CONTINUED)

- bit 3 Unimplemented: Read as '0'

bit 2 TSYNC: Timer External Clock Input Synchronization Selection bit When TCS = 1: 1 = External clock input is synchronized 0 = External clock input is not synchronized When TCS = 0: This bit is ignored.

bit 1 TCS: Timer Clock Source Select bit 1 = External clock from TxCKI pin 0 = Internal peripheral clock

- bit 0 Unimplemented: Read as '0'

- **Note 1:** When using the 1:1 PBCLK divisor, the user's software should not read/write the peripheral SFRs in the SYSCLK cycle immediately following the instruction that clears the module's ON bit.

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|

| 24.24        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 31:24        | _                 | —                 | —                 | _                 | —                 | —                 | —                | —                |

| 00.40        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 23:16        |                   | —                 | —                 | _                 | —                 | —                 | —                | —                |

| 45.0         | R/W-0             | U-0               | R/W-0             | R/W-1, HC         | R/W-0             | R/W-0             | R/W-0            | R/W-0            |

| 15:8         | ON <sup>(1)</sup> | —                 | SIDL              | SCLREL            | STRICT            | A10M              | DISSLW           | SMEN             |

| 7.0          | R/W-0             | R/W-0             | R/W-0             | R/W-0, HC         | R/W-0, HC         | R/W-0, HC         | R/W-0, HC        | R/W-0, HC        |

| 7:0          | GCEN              | STREN             | ACKDT             | ACKEN             | RCEN              | PEN               | RSEN             | SEN              |

# REGISTER 19-1: I2CxCON: I<sup>2</sup>C CONTROL REGISTER

| Legend:           | HC = Cleared by hardwar | e                        |                    |

|-------------------|-------------------------|--------------------------|--------------------|

| R = Readable bit  | W = Writable bit        | U = Unimplemented bit, r | ead as '0'         |

| -n = Value at POR | '1' = Bit is set        | '0' = Bit is cleared     | x = Bit is unknown |

# bit 31-16 Unimplemented: Read as '0'

- bit 15 **ON:** I<sup>2</sup>C Enable bit<sup>(1)</sup>

- 1 = Enables the I<sup>2</sup>C module and configures the SDA and SCL pins as serial port pins

- 0 = Disables the I<sup>2</sup>C module; all I<sup>2</sup>C pins are controlled by PORT functions

- bit 14 Unimplemented: Read as '0'

- bit 13 **SIDL:** Stop in Idle Mode bit

- 1 = Discontinue module operation when device enters Idle mode

- 0 = Continue module operation when device enters Idle mode

- bit 12 **SCLREL:** SCLx Release Control bit (when operating as I<sup>2</sup>C slave)

- 1 = Release SCLx clock

0 = Hold SCLx clock low (clock stretch)

If STREN = 1:

Bit is R/W (software can write '0' to initiate stretch and write '1' to release clock). Cleared by hardware at the beginning of a slave transmission and at the end of slave reception.

If STREN = 0:

Bit is R/S (software can only write '1' to release clock). Cleared by hardware at the beginning of slave transmission.

- bit 11 STRICT: Strict I<sup>2</sup>C Reserved Address Rule Enable bit

- 1 = Strict reserved addressing is enforced. Device does not respond to reserved address space or generate addresses in reserved address space.

- 0 = Strict I<sup>2</sup>C reserved address rule is not enabled

- bit 10 A10M: 10-bit Slave Address bit

- 1 = I2CxADD is a 10-bit slave address

- 0 = I2CxADD is a 7-bit slave address

- bit 9 DISSLW: Disable Slew Rate Control bit

- 1 = Slew rate control is disabled

- 0 = Slew rate control is enabled

- bit 8 SMEN: SMBus Input Levels bit

- 1 = Enable I/O pin thresholds compliant with SMBus specification

- 0 = Disable SMBus input thresholds

- **Note 1:** When using the 1:1 PBCLK divisor, the user's software should not read/write the peripheral's SFRs in the SYSCLK cycle immediately following the instruction that clears the module's ON bit.

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|

| 31:24        | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |

| 31.24        | FLTEN7            | MSEL              | 7<1:0>            |                   | F                 | SEL7<4:0>         |                  |                  |

| 22:16        | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |

| 23:16        | FLTEN6            | MSEL              | 6<1:0>            | FSEL6<4:0>        |                   |                   |                  |                  |

| 15:8         | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |

| 10.0         | FLTEN5            | MSEL              | 5<1:0>            | FSEL5<4:0>        |                   |                   |                  |                  |

| 7.0          | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |

| 7:0          | FLTEN4            | MSEL4<1:0>        |                   | FSEL4<4:0>        |                   |                   |                  |                  |

# **REGISTER 24-11: CIFLTCON1: CAN FILTER CONTROL REGISTER 1**

## Legend:

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, r | ead as '0'         |

|-------------------|------------------|--------------------------|--------------------|

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared     | x = Bit is unknown |

| bit 31    | FLTEN7: Filter 7 Enable bit                                 |

|-----------|-------------------------------------------------------------|

|           | 1 = Filter is enabled                                       |

|           | 0 = Filter is disabled                                      |

| bit 30-29 | MSEL7<1:0>: Filter 7 Mask Select bits                       |

|           | 11 = Acceptance Mask 3 selected                             |

|           | 10 = Acceptance Mask 2 selected                             |

|           | 01 = Acceptance Mask 1 selected                             |

|           | 00 = Acceptance Mask 0 selected                             |

| bit 28-24 | FSEL7<4:0>: FIFO Selection bits                             |

|           | 11111 = Message matching filter is stored in FIFO buffer 31 |

|           | 11110 = Message matching filter is stored in FIFO buffer 30 |

|           | •                                                           |

|           | •                                                           |

|           | 00001 = Message matching filter is stored in FIFO buffer 1  |

|           | 00000 = Message matching filter is stored in FIFO buffer 0  |

| bit 23    | FLTEN6: Filter 6 Enable bit                                 |

|           | 1 = Filter is enabled                                       |

|           | 0 = Filter is disabled                                      |

| bit 22-21 | MSEL6<1:0>: Filter 6 Mask Select bits                       |

|           | 11 = Acceptance Mask 3 selected                             |

|           | 10 = Acceptance Mask 2 selected                             |

|           | 01 = Acceptance Mask 1 selected                             |

|           | 00 = Acceptance Mask 0 selected                             |

| bit 20-16 | FSEL6<4:0>: FIFO Selection bits                             |

|           | 11111 = Message matching filter is stored in FIFO buffer 31 |

|           | 11110 - Massage matching filter is stored in EIEO buffer 30 |

uffer 31 11110 = Message matching filter is stored in FIFO buffer 30

•

•

00001 = Message matching filter is stored in FIFO buffer 1 00000 = Message matching filter is stored in FIFO buffer 0

Note: The bits in this register can only be modified if the corresponding filter enable (FLTENn) bit is '0'.

# REGISTER 24-20: CiFIFOCONn: CAN FIFO CONTROL REGISTER 'n' (n = 0 THROUGH 31)

- bit 6 TXABAT: Message Aborted bit<sup>(2)</sup> 1 = Message was aborted 0 = Message completed successfully bit 5 TXLARB: Message Lost Arbitration bit<sup>(3)</sup> 1 = Message lost arbitration while being sent 0 = Message did not lose arbitration while being sent TXERR: Error Detected During Transmission bit<sup>(3)</sup> bit 4 1 = A bus error occured while the message was being sent 0 = A bus error did not occur while the message was being sent bit 3 **TXREQ:** Message Send Request TXEN = 1: (FIFO configured as a Transmit FIFO) Setting this bit to '1' requests sending a message. The bit will automatically clear when all the messages queued in the FIFO are successfully sent. Clearing the bit to '0' while set ('1') will request a message abort. TXEN = 0: (FIFO configured as a receive FIFO) This bit has no effect. bit 2 RTREN: Auto RTR Enable bit 1 = When a remote transmit is received, TXREQ will be set 0 = When a remote transmit is received, TXREQ will be unaffected bit 1-0 TXPR<1:0>: Message Transmit Priority bits 11 = Highest message priority 10 = High intermediate message priority 01 = Low intermediate message priority 00 = Lowest message priority Note 1: These bits can only be modified when the CAN module is in Configuration mode (OPMOD<2:0> bits (CiCON<23:21>) = 100).

- 2: This bit is updated when a message completes (or aborts) or when the FIFO is reset.

- 3: This bit is reset on any read of this register or when the FIFO is reset.

# 25.1 Control Registers

# TABLE 25-5: ETHERNET CONTROLLER REGISTER SUMMARY FOR PIC32MX664F064H, PIC32MX664F128H, PIC32MX664F064L, PIC32MX664F128L, PIC32MX675F256H, PIC32MX675F512H, PIC32MX695F512H, PIC32MX775F256H, PIC32MX775F512H, PIC32MX795F512H, PIC32MX695F512L, PIC32MX675F256L, PIC32MX675F512L, PIC32MX764F128H, PIC32MX764F128L, PIC32MX775F256L, PIC32MX775F512L AND PIC32MX795F512L DEVICES

| se (                        |                                 | Bits          |       |                |              |       |       |       |              |              |              |               |               |        |              |               |               |               |            |

|-----------------------------|---------------------------------|---------------|-------|----------------|--------------|-------|-------|-------|--------------|--------------|--------------|---------------|---------------|--------|--------------|---------------|---------------|---------------|------------|

| Virtual Address<br>(BF88_#) | Register<br>Name <sup>(1)</sup> | Bit Range     | 31/15 | 30/14          | 29/13        | 28/12 | 27/11 | 26/10 | 25/9         | 24/8         | 23/7         | 22/6          | 21/5          | 20/4   | 19/3         | 18/2          | 17/1          | 16/0          | All Resets |

|                             | FTUOONIA                        | 31:16         |       | PTV<15:0> 0000 |              |       |       |       |              |              |              |               |               |        |              |               |               |               |            |

| 9000                        | ETHCON1                         | 15:0          | ON    | _              | SIDL         | _     | _     | _     | TXRTS        | RXEN         | AUTOFC       | _             | _             | MANFC  | _            | _             | _             | BUFCDEC       | 0000       |

| 9010                        | ETHCON2                         | 31:16         | —     | _              | _            | _     | _     | _     | -            | _            | _            | —             | _             | _      | _            | —             | —             | _             | 0000       |

| 3010                        | LINCONZ                         | 15:0          | —     | —              | —            | —     | —     |       |              |              | XBUFSZ<6:0   | >             |               |        | —            | —             | —             | —             | 0000       |

| 9020                        | ETHTXST                         | 31:16         |       |                |              |       |       |       |              | TXSTADE      | R<31:16>     |               |               |        |              |               |               | -             | 0000       |

| 0020                        |                                 | 15:0          |       |                |              |       |       |       | TXSTAD       |              |              |               |               |        |              |               |               | —             | 0000       |

| 9030                        | ETHRXST                         | 31:16         |       |                |              |       |       |       |              |              | )R<31:16>    |               |               |        |              |               |               |               | 0000       |

|                             |                                 | 15:0          |       |                |              |       |       |       | RXSTADI      | DR<15:2>     |              |               |               |        |              |               |               | —             | 0000       |

| 9040                        | ETHHT0                          | 31:16         |       |                |              |       |       |       |              | HT<          | 31:0>        |               |               |        |              |               |               |               | 0000       |

|                             |                                 | 15:0          |       |                |              |       |       |       |              |              |              |               |               |        |              |               |               |               | 0000       |

| 9050                        | ETHHT1                          | 31:16         |       |                |              |       |       |       |              | HT<6         | 3:32>        |               |               |        |              |               |               |               | 0000       |

|                             |                                 | 15:0          |       |                |              |       |       |       |              |              |              |               |               |        |              |               |               |               | 0000       |

| 9060                        | ETHPMM0                         | 31:16<br>15:0 |       |                |              |       |       |       |              | PMM-         | <31:0>       |               |               |        |              |               |               |               | 0000       |

|                             |                                 | 31:16         |       |                |              |       |       |       |              |              |              |               |               |        |              |               |               |               | 0000       |

| 9070                        | ETHPMM1                         | 15:0          |       |                |              |       |       |       |              | PMM<         | 63:32>       |               |               |        |              |               |               |               | 0000       |

|                             |                                 | 31:16         | _     | _              | _            |       | _     | _     | _            | _            | _            |               | _             | _      | _            | _             |               | _             | 0000       |

| 9080                        | ETHPMCS                         | 15:0          |       |                |              |       |       |       |              | PMCS         | <15:0>       |               |               |        |              |               |               |               | 0000       |

|                             |                                 | 31:16         | _     | _              | _            | _     | _     | _     | _            | _            | _            | _             | _             | _      | _            | _             | _             | _             | 0000       |

| 9090                        | ETHPMO                          | 15:0          |       |                |              |       |       |       |              | PMO.         | <15:0>       |               |               |        |              |               |               |               | 0000       |

|                             |                                 | 31:16         | —     | _              | —            | _     | _     | _     | _            | _            | _            | _             | _             | _      | _            | —             | —             | _             | 0000       |

| 90A0                        | ETHRXFC                         | 15:0          | HTEN  | MPEN           | _            | NOTPM |       | PMMO  | DE<3:0>      |              | CRC<br>ERREN | CRC<br>OKEN   | RUNT<br>ERREN | RUNTEN | UCEN         | NOT<br>MEEN   | MCEN          | BCEN          | 0000       |

| 0000                        | ETHRXWM                         | 31:16         | —     | _              | _            | —     | _     | _     | _            | _            |              |               |               | RXFW   | M<7:0>       |               |               | •             | 0000       |

| 90B0                        | ETHRXWW                         | 15:0          | _     | _              | _            | _     | _     |       | _            |              |              |               |               | RXEW   | M<7:0>       |               |               |               | 0000       |

|                             |                                 | 31:16         | —     | _              | —            | _     | _     |       | —            |              | -            | _             | _             | —      | _            | _             | _             | —             | 0000       |

| 90C0                        | ETHIEN                          | 15:0          | —     | TX<br>BUSEIE   | RX<br>BUSEIE | —     | —     | _     | EW<br>MARKIE | FW<br>MARKIE | RX<br>DONEIE | PK<br>TPENDIE | RX<br>ACTIE   | _      | TX<br>DONEIE | TX<br>ABORTIE | RX<br>BUFNAIE | RX<br>OVFLWIE | 0000       |

| 90D0                        | ETHIRQ                          | 31:16         | —     | —              | —            | _     | _     |       | -            | -            | _            | _             | —             | _      |              | _             | —             | _             | 0000       |

| 3000                        |                                 | 15:0          | —     | TXBUSE         | RXBUSE       | _     | _     | _     | EWMARK       | FWMARK       | RXDONE       | PKTPEND       | RXACT         | -      | TXDONE       | TXABORT       | RXBUFNA       | RXOVFLW       | 0000       |

Note 1: All registers in this table (with the exception of ETHSTAT) have corresponding CLR, SET and INV registers at their virtual addresses, plus offsets of 0x4, 0x8 and 0xC, respectively. See Section 12.1.1 "CLR, SET and INV Registers" for more information.

2: Reset values default to the factory programmed value.

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3        | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0         |

|--------------|-------------------|-------------------|-------------------|-------------------|--------------------------|-------------------|------------------|--------------------------|

| 31:24        | U-0               | U-0               | U-0               | U-0               | U-0                      | U-0               | U-0              | U-0                      |

| 31.24        |                   | —                 | -                 | -                 | —                        | —                 | —                | —                        |

| 23:16        | U-0               | U-0               | U-0               | U-0               | U-0                      | U-0               | U-0              | U-0                      |

| 23.10        |                   | —                 | -                 | -                 | —                        | —                 | —                | —                        |

| 15:8         | U-0               | U-0               | U-0               | U-0               | R/W-0                    | U-0               | U-0              | R/W-0                    |

| 10.0         | _                 | —                 | _                 | _                 | RESETRMII <sup>(1)</sup> | —                 | —                | SPEEDRMII <sup>(1)</sup> |

| 7:0          | U-0               | U-0               | U-0               | U-0               | U-0                      | U-0               | U-0              | U-0                      |

| 7.0          |                   | _                 |                   |                   | _                        | _                 |                  | —                        |

# REGISTER 25-29: EMAC1SUPP: ETHERNET CONTROLLER MAC PHY SUPPORT REGISTER

# Legend:

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, rea | ad as '0'          |

|-------------------|------------------|----------------------------|--------------------|

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared       | x = Bit is unknown |

- bit 31-12 Unimplemented: Read as '0'

- bit 11 **RESETRMII:** Reset RMII Logic bit<sup>(1)</sup>

- 1 = Reset the MAC RMII module

- 0 = Normal operation.

- bit 10-9 Unimplemented: Read as '0'

- bit 8 SPEEDRMII: RMII Speed bit<sup>(1)</sup>

- This bit configures the Reduced MII logic for the current operating speed.

- 1 = RMII is running at 100 Mbps

- 0 = RMII is running at 10 Mbps

- bit 7-0 Unimplemented: Read as '0'

- Note 1: This bit is only used for the RMII module.

**Note:** Both 16-bit and 32-bit accesses are allowed to these registers (including the SET, CLR and INV registers). 8-bit accesses are not allowed and are ignored by the hardware.

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |  |  |  |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|--|--|--|--|

| 31:24        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |  |  |  |  |

| 51.24        |                   | _                 |                   | —                 | —                 | _                 | _                | —                |  |  |  |  |

| 23:16        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |  |  |  |  |

| 23.10        | —                 | —                 | —                 | —                 | —                 | —                 | -                | —                |  |  |  |  |

| 15.0         | R/W-P             | R/W-P             | R/W-P             | R/W-P             | R/W-P             | R/W-P             | R/W-P            | R/W-P            |  |  |  |  |

| 15:8         | STNADDR6<7:0>     |                   |                   |                   |                   |                   |                  |                  |  |  |  |  |

| 7:0          | R/W-P             | R/W-P             | R/W-P             | R/W-P             | R/W-P             | R/W-P             | R/W-P            | R/W-P            |  |  |  |  |

| 7.0          |                   |                   |                   | STNADDR5<         | :7:0>             |                   |                  |                  |  |  |  |  |

# REGISTER 25-37: EMAC1SA0: ETHERNET CONTROLLER MAC STATION ADDRESS 0 REGISTER

| Legend:           |                  | P = Programmable bi  | P = Programmable bit |  |  |  |  |

|-------------------|------------------|----------------------|----------------------|--|--|--|--|

| R = Readable bit  | W = Writable bit | U = Unimplemented b  | oit, read as '0'     |  |  |  |  |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared | x = Bit is unknown   |  |  |  |  |

bit 31-16 Unimplemented: Read as '0'

- bit 15-8 **STNADDR6<7:0>:** Station Address Octet 6 bits These bits hold the sixth transmitted octet of the station address.

- bit 7-0 **STNADDR5<7:0>:** Station Address Octet 5 bits These bits hold the fifth transmitted octet of the station address.

Note 1: Both 16-bit and 32-bit accesses are allowed to these registers (including the SET, CLR and INV registers). 8-bit accesses are not allowed and are ignored by the hardware.

2: This register is loaded at reset from the factory preprogrammed station address.

| DC CHA        | RACTERIS               | TICS                      | Standard Operating Conditions: 2.3V to 3.6V(unless otherwise stated)Operating temperature $-40^{\circ}C \le TA \le +85^{\circ}C$ for Industrial $-40^{\circ}C \le TA \le +105^{\circ}C$ for V-Temp |                                         |                                                                                                                                                                                   |                                                    |  |  |  |  |  |

|---------------|------------------------|---------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------|--|--|--|--|--|

| Param.<br>No. | Typical <sup>(2)</sup> | Max.                      | Units                                                                                                                                                                                              | Conditions                              |                                                                                                                                                                                   |                                                    |  |  |  |  |  |

| Power-D       | Oown Curre             | nt (IPD) <sup>(1)</sup> f | or PIC32                                                                                                                                                                                           | AX534/564/                              | /664/764                                                                                                                                                                          | Family Devices                                     |  |  |  |  |  |