Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFI

| Details                    |                                                                                  |

|----------------------------|----------------------------------------------------------------------------------|

| Product Status             | Active                                                                           |

| Core Processor             | MIPS32® M4K™                                                                     |

| Core Size                  | 32-Bit Single-Core                                                               |

| Speed                      | 80MHz                                                                            |

| Connectivity               | Ethernet, I <sup>2</sup> C, SPI, UART/USART, USB OTG                             |

| Peripherals                | Brown-out Detect/Reset, DMA, POR, PWM, WDT                                       |

| Number of I/O              | 53                                                                               |

| Program Memory Size        | 512KB (512K x 8)                                                                 |

| Program Memory Type        | FLASH                                                                            |

| EEPROM Size                | -                                                                                |

| RAM Size                   | 128K x 8                                                                         |

| Voltage - Supply (Vcc/Vdd) | 2.3V ~ 3.6V                                                                      |

| Data Converters            | A/D 16x10b                                                                       |

| Oscillator Type            | Internal                                                                         |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                                |

| Mounting Type              | Surface Mount                                                                    |

| Package / Case             | 64-TQFP                                                                          |

| Supplier Device Package    | 64-TQFP (10x10)                                                                  |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic32mx695f512h-80i-pt |

|                            |                                                                                  |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

#### TABLE 6:PIN NAMES FOR 64-PIN USB, ETHERNET, AND CAN DEVICES

## 64-PIN QFN<sup>(3)</sup> AND TQFP (TOP VIEW)

### PIC32MX764F128H PIC32MX775F256H PIC32MX775F512H PIC32MX795F512H

|       | 64                                                        | 1                  |                                               |

|-------|-----------------------------------------------------------|--------------------|-----------------------------------------------|

|       |                                                           | QFN <sup>(3)</sup> | 64<br>TQFP                                    |

| Pin # | Full Pin Name                                             | Pin #              | Full Pin Name                                 |

| 1     | ETXEN/PMD5/RE5                                            | 33                 | USBID/RF3                                     |

| 2     | ETXD0/PMD6/RE6                                            | 34                 | VBUS                                          |

| 3     | ETXD1/PMD7/RE7                                            | 35                 | VUSB3V3                                       |

| 4     | SCK2/U6TX/U3RTS/PMA5/CN8/RG6                              | 36                 | D-/RG3                                        |

| 5     | SDA4/SDI2/U3RX/PMA4/CN9/RG7                               | 37                 | D+/RG2                                        |

| 6     | SCL4/SDO2/U3TX/PMA3/CN10/RG8                              | 38                 | Vdd                                           |

| 7     | MCLR                                                      | 39                 | OSC1/CLKI/RC12                                |

| 8     | SS2/U6RX/U3CTS/PMA2/CN11/RG9                              | 40                 | OSC2/CLKO/RC15                                |

| 9     | Vss                                                       | 41                 | Vss                                           |

| 10    | Vdd                                                       | 42                 | RTCC/AERXD1/ETXD3/IC1/INT1/RD8                |

| 11    | AN5/C1IN+/VBUSON/CN7/RB5                                  | 43                 | AERXD0/ETXD2/SS3/U4RX/U1CTS/SDA1/IC2/INT2/RD9 |

| 12    | AN4/C1IN-/CN6/RB4                                         | 44                 | ECOL/AECRSDV/SCL1/IC3/PMCS2/PMA15/INT3/RD10   |

| 13    | AN3/C2IN+/CN5/RB3                                         | 45                 | ECRS/AEREFCLK/IC4/PMCS1/PMA14/INT4/RD11       |

| 14    | AN2/C2IN-/CN4/RB2                                         | 46                 | OC1/INT0/RD0                                  |

| 15    | PGEC1/AN1/VREF-/CVREF-/CN3/RB1                            | 47                 | SOSCI/CN1/RC13                                |

| 16    | PGED1/AN0/VREF+/CVREF+/PMA6/CN2/RB0                       | 48                 | SOSCO/T1CK/CN0/RC14                           |

| 17    | PGEC2/AN6/OCFA/RB6                                        | 49                 | EMDIO/AEMDIO/SCK3/U4TX/U1RTS/OC2/RD1          |

| 18    | PGED2/AN7/RB7                                             | 50                 | SDA3/SDI3/U1RX/OC3/RD2                        |

| 19    | AVdd                                                      | 51                 | SCL3/SDO3/U1TX/OC4/RD3                        |

| 20    | AVss                                                      | 52                 | OC5/IC5/PMWR/CN13/RD4                         |

| 21    | AN8/C2TX <sup>(2)</sup> /SS4/U5RX/U2CTS/C1OUT/RB8         | 53                 | PMRD/CN14/RD5                                 |

| 22    | AN9/C2OUT/PMA7/RB9                                        | 54                 | AETXEN/ETXERR/CN15/RD6                        |

| 23    | TMS/AN10/CVREFOUT/PMA13/RB10                              | 55                 | ETXCLK/AERXERR/CN16/RD7                       |

| 24    | TDO/AN11/PMA12/RB11                                       | 56                 | VCAP                                          |

| 25    | Vss                                                       | 57                 | VDD                                           |

| 26    | Vdd                                                       | 58                 | C1RX/AETXD1/ERXD3/RF0                         |

| 27    | TCK/AN12/PMA11/RB12                                       | 59                 | C1TX/AETXD0/ERXD2/RF1                         |

| 28    | TDI/AN13/PMA10/RB13                                       | 60                 | ERXD1/PMD0/RE0                                |

| 29    | AN14/C2RX <sup>(2)</sup> /SCK4/U5TX/U2RTS/PMALH/PMA1/RB14 | 61                 | ERXD0/PMD1/RE1                                |

| 30    | AN15/EMDC/AEMDC/OCFB/PMALL/PMA0/CN12/RB15                 | 62                 | ERXDV/ECRSDV/PMD2/RE2                         |

| 31    | AC1TX/SDA5/SDI4/U2RX/PMA9/CN17/RF4                        | 63                 | ERXCLK/EREFCLKPMD3/RE3                        |

| 32    | AC1RX/SCL5/SDO4/U2TX/PMA8/CN18/RF5                        | 64                 | ERXERR/PMD4/RE4                               |

| Note  | 1: Shaded pins are 5V tolerant.                           |                    |                                               |

Note 1: Shaded pins are 5V tolerant.

2: This pin is not available on PIC32MX765F128H devices.

3: The metal plane at the bottom of the QFN device is not connected to any pins and is recommended to be connected to Vss externally.

#### **TABLE 13:** PIN NAMES FOR 124-PIN USB, ETHERNET, AND CAN DEVICES (CONTINUED)

| 124               | 4-PIN VTLA (BOTTOM VIEW) <sup>(2,3)</sup>             |     |                   | A3                        | 4                         |

|-------------------|-------------------------------------------------------|-----|-------------------|---------------------------|---------------------------|

|                   |                                                       | B13 | B29               |                           | Conductive<br>Thermal Pad |

|                   | PIC32MX675F512L<br>PIC32MX695F512L<br>PIC32MX795F512L | B1  | B56               | B41                       | A51                       |

|                   | A1                                                    |     |                   |                           |                           |

|                   | Polarity Indicator                                    |     | A68               |                           |                           |

| Package<br>Bump # | Full Pin Name                                         |     | Package<br>Bump # | F                         | ull Pin Name              |

| B8                | Vss                                                   |     | B33               | TDO/RA5                   |                           |

| B9                | TMS/RA0                                               |     | B34               | OSC1/CLKI/RC              | 212                       |

| B10               | AERXD1/INT2/RE9                                       |     | B35               | No Connect (N             | C)                        |

| B11               | AN4/C1IN-/CN6/RB4                                     |     | B36               | AETXCLK/SCL               | .1/INT3/RA14              |

| B12               | Vss                                                   |     | B37               | RTCC/EMDIO/               | AEMDIO/IC1/RD8            |

| B13               | AN2/C2IN-/CN4/RB2                                     |     | B38               | SCK1/IC3/PMC              | CS2/PMA15/RD10            |

| B14               | PGED1/AN0/CN2/RB0                                     |     | B39               | SDO1/OC1/INT              | [0/RD0                    |

| B15               | No Connect (NC)                                       |     | B40               | SOSCO/T1CK/               | CN0/RC14                  |

| B16               | PGED2/AN7/RB7                                         |     | B41               | Vss                       |                           |

| B17               | VREF+/CVREF+/AERXD3/PMA6/RA10                         |     | B42               | OC3/RD2                   |                           |

| B18               | AVss                                                  |     | B43               | ETXD2/IC5/PN              | ID12/RD12                 |

| B19               | AN9/C2OUT/RB9                                         |     | B44               | OC5/PMWR/CI               | N13/RD4                   |

| B20               | AN11/ERXERR/AETXERR/PMA12/RB11                        |     | B45               | ETXEN/PMD14               | 4/CN15/RD6                |

| B21               | Vdd                                                   |     | B46               | Vss                       |                           |

| B22               | AC1TX/SCK4/U5TX/U2RTS/RF13                            |     | B47               | No Connect (N             | C)                        |

| B23               | AN12/ERXD0/AECRS/PMA11/RB12                           |     | B48               | VCAP                      |                           |

| B24               | AN14/ERXD2/AETXD3/PMALH/PMA1/RB14                     |     | B49               | C1RX <sup>(1)</sup> /ETXD | 1/PMD11/RF0               |

| B25               | Vss                                                   |     | B50               | C2TX <sup>(1)</sup> /ETXE | RR/PMD9/RG1               |

| B26               | AETXD0/SS3/U4RX/U1CTS/CN20/RD14                       |     | B51               | TRCLK/RA6                 |                           |

| B27               | SDA5/SDI4/U2RX/PMA9/CN17/RF4                          |     | B52               | PMD0/RE0                  |                           |

| B28               | No Connect (NC)                                       |     | B53               | Vdd                       |                           |

| B29               | SCL3/SDO3/U1TX/RF8                                    |     | B54               | TRD2/RG14                 |                           |

| B30               | VUSB3V3                                               |     | B55               | TRD0/RG13                 |                           |

| B31               | D+/RG2                                                |     | B56               | PMD3/RE3                  |                           |

This pin is only available on PIC32MX795F512L devices. Note 1:

2:

Shaded package bumps are 5V tolerant. It is recommended that the user connect the printed circuit board (PCB) ground to the conductive thermal pad on the bottom of the package. And to not run non-Vss PCB traces under the conductive thermal pad on the same side of the PCB layout. 3:

|                | Pin Number <sup>(1)</sup>                  |                            |                  |                 |             | <b>D</b> "     |                                       |

|----------------|--------------------------------------------|----------------------------|------------------|-----------------|-------------|----------------|---------------------------------------|

| Pin Name       | 64-Pin<br>QFN/TQFP                         | 100-Pin<br>TQFP            | 121-Pin<br>TFBGA | 124-pin<br>VTLA | Pin<br>Type | Buffer<br>Type | Description                           |

| CN0            | 48                                         | 74                         | B11              | B40             | I           | ST             | Change notification inputs. Can be    |

| CN1            | 47                                         | 73                         | C10              | A47             | I           | ST             | software programmed for internal weak |

| CN2            | 16                                         | 25                         | K2               | B14             | I           | ST             | pull-ups on all inputs.               |

| CN3            | 15                                         | 24                         | K1               | A15             | I           | ST             |                                       |

| CN4            | 14                                         | 23                         | J2               | B13             | I           | ST             |                                       |

| CN5            | 13                                         | 22                         | J1               | A13             | I           | ST             |                                       |

| CN6            | 12                                         | 21                         | H2               | B11             | I           | ST             |                                       |

| CN7            | 11                                         | 20                         | H1               | A12             | I           | ST             |                                       |

| CN8            | 4                                          | 10                         | E3               | A7              | I           | ST             |                                       |

| CN9            | 5                                          | 11                         | F4               | B6              | I           | ST             |                                       |

| CN10           | 6                                          | 12                         | F2               | A8              | I           | ST             |                                       |

| CN11           | 8                                          | 14                         | F3               | A9              | I           | ST             |                                       |

| CN12           | 30                                         | 44                         | L8               | A29             | I           | ST             |                                       |

| CN13           | 52                                         | 81                         | C8               | B44             | I           | ST             |                                       |

| CN14           | 53                                         | 82                         | B8               | A55             | I           | ST             |                                       |

| CN15           | 54                                         | 83                         | D7               | B45             | I           | ST             |                                       |

| CN16           | 55                                         | 84                         | C7               | A56             | I           | ST             |                                       |

| CN17           | 31                                         | 49                         | L10              | B27             | I           | ST             |                                       |

| CN18           | 32                                         | 50                         | L11              | A32             | I           | ST             |                                       |

| CN19           | —                                          | 80                         | D8               | A54             | I           | ST             |                                       |

| CN20           | —                                          | 47                         | L9               | B26             | I           | ST             |                                       |

| CN21           | —                                          | 48                         | K9               | A31             | I           | ST             |                                       |

| IC1            | 42                                         | 68                         | E9               | B37             | I           | ST             | Capture Inputs 1-5                    |

| IC2            | 43                                         | 69                         | E10              | A45             | I           | ST             |                                       |

| IC3            | 44                                         | 70                         | D11              | B38             | I           | ST             | -                                     |

| IC4            | 45                                         | 71                         | C11              | A46             | I           | ST             | -                                     |

| IC5            | 52                                         | 79                         | A9               | A60             | I           | ST             | -                                     |

| OCFA           | 17                                         | 26                         | L1               | A20             | I           | ST             | Output Compare Fault A Input          |

| OC1            | 46                                         | 72                         | D9               | B39             | 0           | _              | Output Compare Output 1               |

| OC2            | 49                                         | 76                         | A11              | A52             | 0           |                | Output Compare Output 2               |

| OC3            | 50                                         | 77                         | A10              | B42             | 0           |                | Output Compare Output 3               |

| OC4            | 51                                         | 78                         | B9               | A53             | 0           | _              | Output Compare Output 4               |

| OC5            | 52                                         | 81                         | C8               | B44             | 0           |                | Output Compare Output 5               |

| OCFB           | 30                                         | 44                         | L8               | A29             | I           | ST             | Output Compare Fault B Input          |

| INT0           | 46                                         | 72                         | D9               | B39             | I           | ST             | External Interrupt 0                  |

| INT1           | 42                                         | 18                         | G1               | A11             | I           | ST             | External Interrupt 1                  |

| INT2           | 43                                         | 19                         | G2               | B10             | I           | ST             | External Interrupt 2                  |

| INT3           | 44                                         | 66                         | E11              | B36             | 1           | ST             | External Interrupt 3                  |

| INT4           | 45                                         | 67                         | E8               | A44             | 1           | ST             | External Interrupt 4                  |

| Legend: C<br>S | MOS = CMO<br>T = Schmitt T<br>TL = TTL inp | S compatib<br>rigger input | le input or c    | output          | A           |                | Analog input P = Power                |

TABLE 1-1: PINOUT I/O DESCRIPTIONS (CONTINUED)

Note 1: Pin numbers are only provided for reference. See the "Device Pin Tables" section for device pin availability.

2: See 25.0 "Ethernet Controller" for more information.

## 2.0 GUIDELINES FOR GETTING STARTED WITH 32-BIT MCUS

**Note:** This data sheet summarizes the features of the PIC32MX5XX/6XX/7XX family of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to the related section of the *"PIC32 Family Reference Manual"*, which is available from the Microchip web site (www.microchip.com/PIC32).

## 2.1 Basic Connection Requirements

Getting started with the PIC32MX5XX/6XX/7XX family of 32-bit Microcontrollers (MCUs) requires attention to a minimal set of device pin connections before proceeding with development. The following is a list of pin names, which must always be connected:

- All VDD and Vss pins (see 2.2 "Decoupling Capacitors")

- All AVDD and AVss pins even if the ADC module is not used (see 2.2 "Decoupling Capacitors")

- VCAP pin (see 2.3 "Capacitor on Internal Voltage Regulator (VCAP)")

- MCLR pin (see 2.4 "Master Clear (MCLR) Pin")

- PGECx/PGEDx pins used for In-Circuit Serial Programming<sup>™</sup> (ICSP<sup>™</sup>) and debugging purposes (see **2.5** "ICSP Pins")

- OSC1 and OSC2 pins when external oscillator source is used (see 2.8 "External Oscillator Pins")

The following pin may be required, as well: VREF+/ VREF- pins used when external voltage reference for ADC module is implemented.

**Note:** The AVDD and AVSS pins must be connected, regardless of the ADC use and the ADC voltage reference source.

## 2.2 Decoupling Capacitors

The use of decoupling capacitors on power supply pins, such as VDD, VSS, AVDD and AVSS is required. See Figure 2-1.

Consider the following criteria when using decoupling capacitors:

- Value and type of capacitor: A value of 0.1  $\mu$ F (100 nF), 10-20V is recommended. The capacitor should be a low Equivalent Series Resistance (low-ESR) capacitor and have resonance frequency in the range of 20 MHz and higher. It is further recommended to use ceramic capacitors.

- Placement on the printed circuit board: The decoupling capacitors should be placed as close to the pins as possible. It is recommended that the capacitors be placed on the same side of the board as the device. If space is constricted, the capacitor can be placed on another layer on the PCB using a via; however, ensure that the trace length from the pin to the capacitor is within one-quarter inch (6 mm) in length.

- Handling high frequency noise: If the board is experiencing high frequency noise, upward of tens of MHz, add a second ceramic-type capacitor in parallel to the above described decoupling capacitor. The value of the second capacitor can be in the range of 0.01  $\mu$ F to 0.001  $\mu$ F. Place this second capacitor next to the primary decoupling capacitor. In high-speed circuit designs, consider implementing a decade pair of capacitances as close to the power and ground pins as possible. For example, 0.1  $\mu$ F in parallel with 0.001  $\mu$ F.

- Maximizing performance: On the board layout from the power supply circuit, run the power and return traces to the decoupling capacitors first, and then to the device pins. This ensures that the decoupling capacitors are first in the power chain. Equally important is to keep the trace length between the capacitor and the power pins to a minimum, thereby reducing PCB track inductance.

The MIPS architecture defines that the result of a multiply or divide operation be placed in the HI and LO registers. Using the Move-From-HI (MFHI) and Move-From-LO (MFLO) instructions, these values can be transferred to the General Purpose Register file.

In addition to the HI/LO targeted operations, the MIPS32 architecture also defines a multiply instruction, MUL, which places the least significant results in the primary register file instead of the HI/LO register pair. By avoiding the explicit MFLO instruction required when using the LO register, and by supporting multiple destination registers, the throughput of multiply-intensive operations is increased.

Two other instructions, Multiply-Add (MADD) and Multiply-Subtract (MSUB), are used to perform the multiply-accumulate and multiply-subtract operations. The MADD instruction multiplies two numbers and then adds the product to the current contents of the HI and LO registers. Similarly, the MSUB instruction multiplies two operands and then subtracts the product from the HI and LO registers. The MADD and MSUB operations are commonly used in DSP algorithms.

## 3.2.3 SYSTEM CONTROL COPROCESSOR (CP0)

In the MIPS architecture, CP0 is responsible for the virtual-to-physical address translation, the exception control system, the processor's diagnostics capability, the operating modes (Kernel, User and Debug) and whether interrupts are enabled or disabled. Configuration information, such as presence of options like MIPS16e, is also available by accessing the CP0 registers, listed in Table 3-2.

| Register<br>Number | Register<br>Name        | Function                                                                 |

|--------------------|-------------------------|--------------------------------------------------------------------------|

| 0-6                | Reserved                | Reserved.                                                                |

| 7                  | HWREna                  | Enables access via the RDHWR instruction to selected hardware registers. |

| 8                  | BadVAddr <sup>(1)</sup> | Reports the address for the most recent address-related exception.       |

| 9                  | Count <sup>(1)</sup>    | Processor cycle count.                                                   |

| 10                 | Reserved                | Reserved.                                                                |

| 11                 | Compare <sup>(1)</sup>  | Timer interrupt control.                                                 |

| 12                 | Status <sup>(1)</sup>   | Processor status and control.                                            |

| 12                 | IntCtl <sup>(1)</sup>   | Interrupt system status and control.                                     |

| 12                 | SRSCtl <sup>(1)</sup>   | Shadow register set status and control.                                  |

| 12                 | SRSMap <sup>(1)</sup>   | Provides mapping from vectored interrupt to a shadow set.                |

| 13                 | Cause <sup>(1)</sup>    | Cause of last general exception.                                         |

| 14                 | EPC <sup>(1)</sup>      | Program counter at last exception.                                       |

| 15                 | PRId                    | Processor identification and revision.                                   |

| 15                 | Ebase                   | Exception vector base register.                                          |

| 16                 | Config                  | Configuration register.                                                  |

| 16                 | Config1                 | Configuration Register 1.                                                |

| 16                 | Config2                 | Configuration Register 2.                                                |

| 16                 | Config3                 | Configuration Register 3.                                                |

| 17-22              | Reserved                | Reserved.                                                                |

| 23                 | Debug <sup>(2)</sup>    | Debug control and exception status.                                      |

| 24                 | DEPC <sup>(2)</sup>     | Program counter at last debug exception.                                 |

| 25-29              | Reserved                | Reserved.                                                                |

| 30                 | ErrorEPC <sup>(1)</sup> | Program counter at last error.                                           |

| 31                 | DESAVE <sup>(2)</sup>   | Debug handler scratchpad register.                                       |

|                    | <b>I</b>                |                                                                          |

TABLE 3-2: COPROCESSOR 0 REGISTERS

Note 1: Registers used in exception processing.

2: Registers used during debug.

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |  |  |  |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|--|--|--|--|

| 04.04        | R                 | R                 | R                 | R                 | R                 | R                 | R                | R                |  |  |  |  |

| 31:24        | BMXPFMSZ<31:24>   |                   |                   |                   |                   |                   |                  |                  |  |  |  |  |

| 22:46        | R                 | R                 | R                 | R                 | R                 | R                 | R                | R                |  |  |  |  |

| 23:16        | BMXPFMSZ<23:16>   |                   |                   |                   |                   |                   |                  |                  |  |  |  |  |

| 45.0         | R                 | R                 | R                 | R                 | R                 | R                 | R                | R                |  |  |  |  |

| 15:8         |                   |                   |                   | BMXPF             | /ISZ<15:8>        |                   |                  |                  |  |  |  |  |

| 7.0          | R                 | R                 | R                 | R                 | R                 | R                 | R                | R                |  |  |  |  |

| 7:0          |                   |                   |                   | BMXPF             | MSZ<7:0>          |                   |                  |                  |  |  |  |  |

#### REGISTER 4-7: BMXPFMSZ: PROGRAM FLASH (PFM) SIZE REGISTER

## Legend:

| Legena.           |                  |                           |                    |

|-------------------|------------------|---------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, re | ad as '0'          |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared      | x = Bit is unknown |

bit 31-0 BMXPFMSZ<31:0>: Program Flash Memory (PFM) Size bits

Static value that indicates the size of the PFM in bytes: 0x00010000 = device has 64 KB Flash 0x00020000 = device has 128 KB Flash 0x00040000 = device has 256 KB Flash 0x00080000 = device has 512 KB Flash

#### REGISTER 4-8: BMXBOOTSZ: BOOT FLASH (IFM) SIZE REGISTER

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |  |  |  |  |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|--|--|--|--|--|

| 04.04        | R                 | R                 | R                 | R                 | R                 | R                 | R                | R                |  |  |  |  |  |

| 31:24        |                   | BMXBOOTSZ<31:24>  |                   |                   |                   |                   |                  |                  |  |  |  |  |  |

| 00.40        | R                 | R                 | R                 | R                 | R                 | R                 | R                | R                |  |  |  |  |  |

| 23:16        | BMXBOOTSZ<23:16>  |                   |                   |                   |                   |                   |                  |                  |  |  |  |  |  |

| 15.0         | R                 | R                 | R                 | R                 | R                 | R                 | R                | R                |  |  |  |  |  |

| 15:8         |                   | BMXBOOTSZ<15:8>   |                   |                   |                   |                   |                  |                  |  |  |  |  |  |

| 7.0          | R                 | R                 | R                 | R                 | R                 | R                 | R                | R                |  |  |  |  |  |

| 7:0          |                   |                   |                   | BMXBO             | OTSZ<7:0>         |                   |                  |                  |  |  |  |  |  |

| Legend:           |                  |                           |                    |

|-------------------|------------------|---------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, re | ead as '0'         |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared      | x = Bit is unknown |

bit 31-0 **BMXBOOTSZ<31:0>:** Boot Flash Memory (BFM) Size bits Static value that indicates the size of the Boot PFM in bytes: 0x00003000 = device has 12 KB boot Flash

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |  |  |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|--|--|--|

| 31:24        | R/W-0             | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |  |  |  |

|              | LTAGBOOT          | _                 | _                 | -                 | —                 | _                 | _                | —                |  |  |  |

| 23:16        | R/W-x             | R/W-x             | R/W-x             | R/W-x             | R/W-x             | R/W-x             | R/W-x            | R/W-x            |  |  |  |

| 23.10        | LTAG<19:12>       |                   |                   |                   |                   |                   |                  |                  |  |  |  |

| 15:8         | R/W-x             | R/W-x             | R/W-x             | R/W-x             | R/W-x             | R/W-x             | R/W-x            | R/W-x            |  |  |  |

| 10.0         |                   | LTAG<11:4>        |                   |                   |                   |                   |                  |                  |  |  |  |

| 7:0          | R/W-x             | R/W-x             | R/W-x             | R/W-x             | R/W-0             | R/W-0             | R/W-1            | U-0              |  |  |  |

| 7:0          |                   | LTAG<3:0>         |                   |                   |                   | LLOCK             | LTYPE            | —                |  |  |  |

#### REGISTER 9-3: CHETAG: CACHE TAG REGISTER

## Legend:

| 3                 |                  |                                    |                    |  |

|-------------------|------------------|------------------------------------|--------------------|--|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read as '0' |                    |  |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared               | x = Bit is unknown |  |

#### bit 31 LTAGBOOT: Line Tag Address Boot bit

- 1 = The line is in the 0x1D000000 (physical) area of memory

- 0 = The line is in the 0x1FC00000 (physical) area of memory

#### bit 30-24 Unimplemented: Write '0'; ignore read

#### bit 23-4 LTAG<19:0>: Line Tag Address bits

LTAG<19:0> bits are compared against physical address to determine a hit. Because its address range and position of PFM in kernel space and user space, the LTAG PFM address is identical for virtual addresses, (system) physical addresses, and PFM physical addresses.

#### bit 3 LVALID: Line Valid bit

- 1 = The line is valid and is compared to the physical address for hit detection

- 0 = The line is not valid and is not compared to the physical address for hit detection

#### bit 2 LLOCK: Line Lock bit

- 1 = The line is locked and will not be replaced

- 0 = The line is not locked and can be replaced

#### bit 1 LTYPE: Line Type bit

- 1 = The line caches instruction words

- 0 = The line caches data words

- bit 0 Unimplemented: Write '0'; ignore read

# PIC32MX5XX/6XX/7XX

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |  |  |  |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|--|--|--|--|

| 31:24        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |  |  |  |  |

| 31.24        |                   | _                 |                   |                   |                   |                   |                  | —                |  |  |  |  |

| 22.10        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |  |  |  |  |

| 23:16        |                   |                   |                   |                   |                   |                   |                  | —                |  |  |  |  |

| 15.0         | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |  |  |  |  |

| 15:8         | —                 | —                 | -                 | -                 | —                 | _                 | —                | —                |  |  |  |  |

| 7.0          | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |  |  |

| 7:0          |                   |                   |                   | CNT               | <7:0>             |                   |                  |                  |  |  |  |  |

#### REGISTER 11-16: U1SOF: USB SOF THRESHOLD REGISTER

#### Legend:

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read as '0' |                    |

|-------------------|------------------|------------------------------------|--------------------|

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared               | x = Bit is unknown |

#### bit 31-8 Unimplemented: Read as '0'

- bit 7-0 CNT<7:0>: SOF Threshold Value bits

- Typical values of the threshold are: 01001010 = 64-byte packet 00101010 = 32-byte packet 00011010 = 16-byte packet

00010010 = 8-byte packet

#### REGISTER 11-17: U1BDTP1: USB BUFFER DESCRIPTOR TABLE PAGE 1 REGISTER

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|

| 31:24        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 31.24        | —                 |                   |                   |                   |                   |                   |                  | —                |

| 23:16        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 23.10        | —                 |                   |                   |                   |                   |                   |                  | —                |

| 45.0         | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 15:8         | —                 | -                 | —                 | -                 | -                 | -                 | —                | —                |

| 7.0          | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | U-0              |

| 7:0          |                   |                   | В                 | DTPTRL<15:9       | )>                |                   |                  | —                |

## Legend:

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, r | ead as '0'         |

|-------------------|------------------|--------------------------|--------------------|

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared     | x = Bit is unknown |

#### bit 31-8 Unimplemented: Read as '0'

#### bit 7-1 BDTPTRL<15:9>: BDT Base Address bits

This 7-bit value provides address bits 15 through 9 of the BDT base address, which defines the starting location of the BDT in system memory.

The 32-bit BDT base address is 512-byte aligned.

bit 0 Unimplemented: Read as '0'

## REGISTER 22-1: RTCCON: RTC CONTROL REGISTER (CONTINUED)

- bit 3 RTCWREN: RTC Value Registers Write Enable bit<sup>(4)</sup>

- 1 = RTC Value registers can be written to by the user

- 0 = RTC Value registers are locked out from being written to by the user

- bit 2 RTCSYNC: RTCC Value Registers Read Synchronization bit

- 1 = RTC Value registers can change while reading, due to a rollover ripple that results in an invalid data read. If the register is read twice and results in the same data, the data can be assumed to be valid.

- 0 = RTC Value registers can be read without concern about a rollover ripple

- bit 1 HALFSEC: Half-Second Status bit<sup>(5)</sup>

- 1 = Second half period of a second

- 0 = First half period of a second

- bit 0 RTCOE: RTCC Output Enable bit

- 1 = RTCC clock output is enabled (clock presented onto an I/O)

- 0 = RTCC clock output is disabled

- **Note 1:** The ON bit is only writable when RTCWREN = 1.

- 2: When using the 1:1 PBCLK divisor, the user's software should not read/write the peripheral's SFRs in the SYSCLK cycle immediately following the instruction that clears the module's ON bit.

- **3:** Requires RTCOE = 1 (RTCCON<0>) for the output to be active.

- 4: The RTCWREN bit can only be set when the write sequence is enabled.

- 5: This bit is read-only. It is cleared to '0' on a write to the seconds bit fields (RTCTIME<14:8>).

Note: This register is only reset on a Power-on Reset (POR).

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|

| 04.04        | R/W-x             | R/W-x             | R/W-x             | R/W-x             | R/W-x             | R/W-x             | R/W-x            | R/W-x            |

| 31:24        |                   | HR10-             | <3:0>             |                   |                   | HR01              | <3:0>            |                  |

| 23:16        | R/W-x             | R/W-x             | R/W-x             | R/W-x             | R/W-x             | R/W-x             | R/W-x            | R/W-x            |

| 23:16        | MIN10<3:0>        |                   |                   |                   | MIN01<3:0>        |                   |                  |                  |

| 45.0         | R/W-x             | R/W-x             | R/W-x             | R/W-x             | R/W-x             | R/W-x             | R/W-x            | R/W-x            |

| 15:8         | SEC10<3:0>        |                   |                   |                   | SEC01<3:0>        |                   |                  |                  |

| 7.0          | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 7:0          | —                 | —                 | —                 | —                 | —                 | —                 | —                | —                |

|              |                   |                   |                   |                   |                   |                   |                  |                  |

| Legend:      |                   |                   |                   |                   |                   |                   |                  |                  |

| R = Read     | able bit          |                   | W = Writable      | e bit             | U = Unimple       | emented bit, re   | ead as '0'       |                  |

|              |                   |                   |                   |                   |                   |                   |                  |                  |

#### REGISTER 22-3: RTCTIME: RTC TIME VALUE REGISTER

| IX – IXeauable bit            |                            |                                | it, read as 0      |

|-------------------------------|----------------------------|--------------------------------|--------------------|

| -n = Value at POR             | '1' = Bit is set           | '0' = Bit is cleared           | x = Bit is unknown |

|                               |                            |                                |                    |

| bit 31-28 HR10<3:0>: Binary-0 | Coded Decimal Value of Hou | rs bits, 10 digits; contains a | value from 0 to 2  |

bit 31-28 HR10<3:0>: Binary-Coded Decimal Value of Hours bits, 10 digits, contains a value from 0 to 2

bit 27-24 HR01<3:0>: Binary-Coded Decimal Value of Hours bits, 1 digit; contains a value from 0 to 9

bit 23-20 MIN10<3:0>: Binary-Coded Decimal Value of Minutes bits, 10 digits; contains a value from 0 to 5

bit 19-16 MIN01<3:0>: Binary-Coded Decimal Value of Minutes bits, 1 digit; contains a value from 0 to 9

bit 15-12 SEC10<3:0>: Binary-Coded Decimal Value of Seconds bits, 10 digits; contains a value from 0 to 5

bit 11-8 SEC01<3:0>: Binary-Coded Decimal Value of Seconds bits, 1 digit; contains a value from 0 to 9

bit 17-0 Unimplemented: Read as '0'

**Note:** This register is only writable when RTCWREN = 1 (RTCCON<3>).

# PIC32MX5XX/6XX/7XX

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1    | Bit<br>24/16/8/0    |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|---------------------|---------------------|

| 04.04        | U-0                 | U-0                 |

| 31:24        | —                 | —                 | —                 |                   | _                 | —                 | —                   | _                   |

| 00.40        | U-0                 | U-0                 |

| 23:16        | —                 | —                 | —                 | _                 | —                 | —                 | —                   | _                   |

| 45.0         | R/W-0             | U-0               | R/W-0             | U-0               | U-0               | R/W-0             | R/W-0               | R/W-0               |

| 15:8         | ON <sup>(1)</sup> | —                 | SIDL — —          |                   | F                 | FORM<2:0>         |                     |                     |

| 7.0          | R/W-0             | R/W-0             | R/W-0             | R/W-0             | U-0               | R/W-0             | R/W-0, HSC          | R/C-0, HSC          |

| 7:0          |                   | SSRC<2:0>         |                   | CLRASAM           | —                 | ASAM              | SAMP <sup>(2)</sup> | DONE <sup>(3)</sup> |

#### REGISTER 23-1: AD1CON1: ADC CONTROL REGISTER 1

#### Legend:

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, re | ad as '0'          |

|-------------------|------------------|---------------------------|--------------------|

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared      | x = Bit is unknown |

#### bit 31-16 Unimplemented: Read as '0'

- bit 15 **ON:** ADC Operating Mode bit<sup>(1)</sup>

- 1 = ADC module is operating

- 0 = ADC module is not operating

- bit 14 Unimplemented: Read as '0'

- bit 13 **SIDL:** Stop in Idle Mode bit

- 1 = Discontinue module operation when device enters Idle mode

- 0 = Continue module operation in Idle mode

- bit 12-11 Unimplemented: Read as '0'

#### bit 10-8 **FORM<2:0>:** Data Output Format bits

- 111 = Signed Fractional 32-bit (DOUT = sddd dddd dd00 0000 0000 0000 0000)

- 110 = Fractional 32-bit (DOUT = dddd dddd dd00 0000 0000 0000 0000)

- 101 = Signed Integer 32-bit (DOUT = ssss ssss ssss ssss ssss dddd dddd)

- 100 = Integer 32-bit (DOUT = 0000 0000 0000 0000 0000 00dd dddd dddd)

- 011 = Signed Fractional 16-bit (DOUT = 0000 0000 0000 0000 sddd dddd dd00 0000)

- 010 = Fractional 16-bit (DOUT = 0000 0000 0000 0000 dddd dddd dd00 0000)

- 000 = Integer 16-bit (DOUT = 0000 0000 0000 0000 0000 00dd dddd dddd)

#### bit 7-5 SSRC<2:0>: Conversion Trigger Source Select bits

- 111 = Internal counter ends sampling and starts conversion (auto convert)

- 110 = Reserved

- 101 = Reserved

- 100 = Reserved

- 011 = CTMU ends sampling and starts conversion

- 010 = Timer 3 period match ends sampling and starts conversion

- 001 = Active transition on INT0 pin ends sampling and starts conversion

- 000 = Clearing the SAMP bit ends sampling and starts conversion

- **Note 1:** When using the 1:1 PBCLK divisor, the user's software should not read/write the peripheral's SFRs in the SYSCLK cycle immediately following the instruction that clears the module's ON bit.

- 2: If ASAM = 0, software can write a '1' to start sampling. This bit is automatically set by hardware if ASAM = 1. If SSRC<2:0> = 000, software can write a '0' to end sampling and start conversion. If SSRC<2:0> ≠ '000', this bit is automatically cleared by hardware to end sampling and start conversion.

- **3:** This bit is automatically set by hardware when analog-to-digital conversion is complete. Software can write a '0' to clear this bit (a write of '1' is not allowed). Clearing this bit does not affect any operation already in progress. This bit is automatically cleared by hardware at the start of a new conversion.

# PIC32MX5XX/6XX/7XX

#### REGISTER 25-9: ETHPMCS: ETHERNET CONTROLLER PATTERN MATCH CHECKSUM REGISTER

| Bit Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

|-----------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|

| 31:24     | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 31.24     | —                 | —                 | —                 | —                 | _                 | —                 | —                | —                |

| 23:16     | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 23.10     | —                 | —                 | —                 | —                 | —                 | —                 | —                | —                |

| 15:8      | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |

| 15.6      |                   |                   |                   | PMCS              | <15:8>            |                   |                  |                  |

| 7:0       | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |

| 7.0       |                   |                   |                   | PMCS              | S<7:0>            |                   |                  |                  |

| Legend:           |                  |                        |                    |

|-------------------|------------------|------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, | read as '0'        |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared   | x = Bit is unknown |

bit 31-16 Unimplemented: Read as '0'

bit 15-8 PMCS<15:8>: Pattern Match Checksum 1 bits

bit 7-0 PMCS<7:0>: Pattern Match Checksum 0 bits

**Note 1:** This register is only used for RX operations.

2: The bits in this register may only be changed while the RXEN bit (ETHCON1<8>) = 0 or the PMMODE bit (ETHRXFC<11:8>) = 0.

## REGISTER 25-10: ETHPMO: ETHERNET CONTROLLER PATTERN MATCH OFFSET REGISTER

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|--|

| 31:24        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |  |

| 51.24        | —                 | _                 | _                 | _                 | _                 | _                 | _                | _                |  |

| 23:16        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |  |

| 23.10        | —                 | —                 | —                 | —                 | —                 | —                 | —                | —                |  |

| 15:8         | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |

| 15.0         | PMO<15:8>         |                   |                   |                   |                   |                   |                  |                  |  |

| 7:0          | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |

| 7.0          |                   |                   |                   | PMO               | <7:0>             |                   |                  |                  |  |

| Legend:           |                  |                          |                    |

|-------------------|------------------|--------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, r | read as '0'        |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared     | x = Bit is unknown |

bit 31-16 Unimplemented: Read as '0'

bit 15-0 **PMO<15:0>:** Pattern Match Offset 1 bits

Note 1: This register is only used for RX operations.

2: The bits in this register may only be changed while the RXEN bit (ETHCON1<8>) = 0 or the PMMODE bit (ETHRXFC<11:8>) = 0.

| Bit Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

|-----------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|

| 31:24     | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 31.24     | _                 | _                 |                   |                   |                   |                   |                  | _                |

| 23:16     | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 23.10     | _                 | _                 | _                 | _                 | —                 | -                 | _                | _                |

| 15:8      | U-0               | R/W-0             | R/W-0             | U-0               | U-0               | U-0               | R/W-0            | R/W-0            |

| 15.6      | _                 | TXBUSE            | RXBUSE            | _                 | _                 | _                 | EWMARK           | FWMARK           |

| 7:0       | R/W-0             | R/W-0             | R/W-0             | U-0               | R/W-0             | R/W-0             | R/W-0            | R/W-0            |

| 7.0       | RXDONE            | PKTPEND           | RXACT             | _                 | TXDONE            | TXABORT           | RXBUFNA          | RXOVFLW          |

## **REGISTER 25-14: ETHIRQ: ETHERNET CONTROLLER INTERRUPT REQUEST REGISTER**

#### Legend:

| R = Readable bit  | Readable bit W = Writable bit |                      | U = Unimplemented bit, read as '0' |  |  |

|-------------------|-------------------------------|----------------------|------------------------------------|--|--|

| -n = Value at POR | '1' = Bit is set              | '0' = Bit is cleared | x = Bit is unknown                 |  |  |

| bit 31-15 | Unimplemented: Read as '0'                                                                                                                                                                                                                                      |

|-----------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| bit 14    | TXBUSE: Transmit BVCI Bus Error Interrupt bit                                                                                                                                                                                                                   |

|           | 1 = BVCI Bus Error has occurred<br>0 = BVCI Bus Error has not occurred                                                                                                                                                                                          |

|           | This bit is set when the TX DMA encounters a BVCI Bus error during a memory access. It is cleared by either a Reset or CPU write of a '1' to the CLR register.                                                                                                  |

| bit 13    | RXBUSE: Receive BVCI Bus Error Interrupt bit                                                                                                                                                                                                                    |

|           | 1 = BVCI Bus Error has occurred<br>0 = BVCI Bus Error has not occurred                                                                                                                                                                                          |

|           | This bit is set when the RX DMA encounters a BVCI Bus error during a memory access. It is cleared by either a Reset or CPU write of a '1' to the CLR register.                                                                                                  |

| bit 12-10 | Unimplemented: Read as '0'                                                                                                                                                                                                                                      |

| bit 9     | EWMARK: Empty Watermark Interrupt bit                                                                                                                                                                                                                           |

|           | <ul><li>1 = Empty Watermark pointer reached</li><li>0 = No interrupt pending</li></ul>                                                                                                                                                                          |

|           | This bit is set when the RX Descriptor Buffer Count is less than or equal to the value in the RXEWM bit (ETHRXWM<0:7>) value. It is cleared by BUFCNT bit (ETHSTAT<16:23>) being incremented by hardware. Writing a '0' or a '1' has no effect.                 |

| bit 8     | FWMARK: Full Watermark Interrupt bit                                                                                                                                                                                                                            |

|           | <ul><li>1 = Full Watermark pointer reached</li><li>0 = No interrupt pending</li></ul>                                                                                                                                                                           |

|           | This bit is set when the RX Descriptor Buffer Count is greater than or equal to the value in the RXFWM bit (ETHRXWM<16:23>) field. It is cleared by writing the BUFCDEC (ETHCON1<0>) bit to decrement the BUFCNT counter. Writing a '0' or a '1' has no effect. |

| bit 7     | RXDONE: Receive Done Interrupt bit                                                                                                                                                                                                                              |

|           | <ul><li>1 = RX packet was successfully received</li><li>0 = No interrupt pending</li></ul>                                                                                                                                                                      |

|           | This bit is set whenever an RX packet is successfully received. It is cleared by either a Reset or CPU write of a '1' to the CLR register.                                                                                                                      |

|           |                                                                                                                                                                                                                                                                 |

| Note:     | It is recommended to use the SET, CLR, or INV registers to set or clear any bit in this register. Setting or clearing any bits in this register should only be done for debug/test purposes.                                                                    |

#### REGISTER 25-26: EMAC1IPGR: ETHERNET CONTROLLER MAC NON-BACK-TO-BACK INTERPACKET GAP REGISTER

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|

| 31:24        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

|              |                   | —                 |                   |                   |                   |                   | —                | —                |

| 23:16        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

|              |                   | —                 |                   |                   |                   |                   | —                | _                |

| 15:8         | U-0               | R/W-0             | R/W-0             | R/W-0             | R/W-1             | R/W-1             | R/W-0            | R/W-0            |

|              | —                 | NB2BIPKTGP1<6:0>  |                   |                   |                   |                   |                  |                  |

| 7:0          | U-0               | R/W-0             | R/W-0             | R/W-1             | R/W-0             | R/W-0             | R/W-1            | R/W-0            |

|              |                   | NB2BIPKTGP2<6:0>  |                   |                   |                   |                   |                  |                  |

| Legend:           |                  |                                    |                    |

|-------------------|------------------|------------------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read as '0' |                    |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared               | x = Bit is unknown |

#### bit 31-15 Unimplemented: Read as '0'

#### bit 14-8 NB2BIPKTGP1<6:0>: Non-Back-to-Back Interpacket Gap Part 1 bits

This is a programmable field representing the optional carrierSense window referenced in section 4.2.3.2.1 "Deference" of the IEEE 80.23 Specification. If the carrier is detected during the timing of IPGR1, the MAC defers to the carrier. If, however, the carrier comes after IPGR1, the MAC continues timing IPGR2 and transmits, knowingly causing a collision, thus ensuring fair access to the medium. Its range of values is 0x0 to IPGR2. Its recommend value is 0xC (12d).

#### bit 7 Unimplemented: Read as '0'

## bit 6-0 NB2BIPKTGP2<6:0>: Non-Back-to-Back Interpacket Gap Part 2 bits

This is a programmable field representing the non-back-to-back Inter-Packet-Gap. Its recommended value is 0x12 (18d), which represents the minimum IPG of 0.96  $\mu$ s (in 100 Mbps) or 9.6  $\mu$ s (in 10 Mbps).

**Note:** Both 16-bit and 32-bit accesses are allowed to these registers (including the SET, CLR and INV registers). 8-bit accesses are not allowed and are ignored by the hardware.

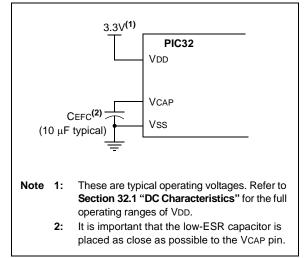

## 29.2 On-Chip Voltage Regulator

All PIC32MX5XX/6XX/7XX devices' core and digital logic are designed to operate at a nominal 1.8V. To simplify system designs, most devices in the PIC32MX-5XX/6XX/7XX family incorporate an on-chip regulator providing the required core logic voltage from VDD.

A low-ESR capacitor (such as tantalum) must be connected to the VCAP pin (see Figure 29-1). This helps to maintain the stability of the regulator. The recommended value for the filter capacitor is provided in **Section 32.1 "DC Characteristics"**.

Note: It is important that the low-ESR capacitor is placed as close as possible to the VCAP pin.

## 29.2.1 ON-CHIP REGULATOR AND POR

It takes a fixed delay for the on-chip regulator to generate an output. During this time, designated as TPU, code execution is disabled. TPU is applied every time the device resumes operation after any power-down, including Sleep mode.

## 29.2.2 ON-CHIP REGULATOR AND BOR

PIC32MX5XX/6XX/7XX devices also have a simple brown-out capability. If the voltage supplied to the regulator is inadequate to maintain a regulated level, the regulator Reset circuitry will generate a Brown-out Reset (BOR). This event is captured by the BOR flag bit (RCON<1>). The brown-out voltage levels are specified in **Section 32.1 "DC Characteristics"**.

## FIGURE 29-1: CONNECTIONS FOR THE ON-CHIP REGULATOR

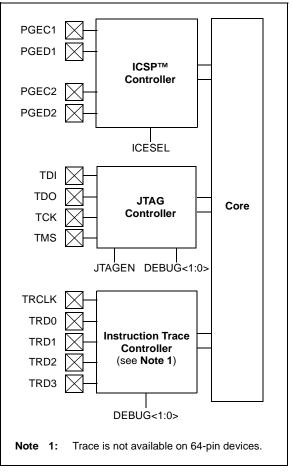

## 29.3 **Programming and Diagnostics**

PIC32MX5XX/6XX/7XX devices provide a complete range of programming and diagnostic features that can increase the flexibility of any application using them. These features allow system designers to include:

- Simplified field programmability using two-wire In-Circuit Serial Programming<sup>™</sup> (ICSP<sup>™</sup>) interfaces

- Debugging using ICSP

- Programming and debugging capabilities using the EJTAG extension of JTAG

- JTAG boundary scan testing for device and board diagnostics

PIC32 devices incorporate two programming and diagnostic modules, and a trace controller, that provide a range of functions to the application developer.

FIGURE 29-2:

PROGRAMMING, DEBUGGING, AND TRACE PORTS BLOCK DIAGRAM

## 31.6 MPLAB X SIM Software Simulator

The MPLAB X SIM Software Simulator allows code development in a PC-hosted environment by simulating the PIC MCUs and dsPIC DSCs on an instruction level. On any given instruction, the data areas can be examined or modified and stimuli can be applied from a comprehensive stimulus controller. Registers can be logged to files for further run-time analysis. The trace buffer and logic analyzer display extend the power of the simulator to record and track program execution, actions on I/O, most peripherals and internal registers.

The MPLAB X SIM Software Simulator fully supports symbolic debugging using the MPLAB XC Compilers, and the MPASM and MPLAB Assemblers. The software simulator offers the flexibility to develop and debug code outside of the hardware laboratory environment, making it an excellent, economical software development tool.

## 31.7 MPLAB REAL ICE In-Circuit Emulator System

The MPLAB REAL ICE In-Circuit Emulator System is Microchip's next generation high-speed emulator for Microchip Flash DSC and MCU devices. It debugs and programs all 8, 16 and 32-bit MCU, and DSC devices with the easy-to-use, powerful graphical user interface of the MPLAB X IDE.

The emulator is connected to the design engineer's PC using a high-speed USB 2.0 interface and is connected to the target with either a connector compatible with in-circuit debugger systems (RJ-11) or with the new high-speed, noise tolerant, Low-Voltage Differential Signal (LVDS) interconnection (CAT5).

The emulator is field upgradable through future firmware downloads in MPLAB X IDE. MPLAB REAL ICE offers significant advantages over competitive emulators including full-speed emulation, run-time variable watches, trace analysis, complex breakpoints, logic probes, a ruggedized probe interface and long (up to three meters) interconnection cables.

## 31.8 MPLAB ICD 3 In-Circuit Debugger System

The MPLAB ICD 3 In-Circuit Debugger System is Microchip's most cost-effective, high-speed hardware debugger/programmer for Microchip Flash DSC and MCU devices. It debugs and programs PIC Flash microcontrollers and dsPIC DSCs with the powerful, yet easy-to-use graphical user interface of the MPLAB IDE.

The MPLAB ICD 3 In-Circuit Debugger probe is connected to the design engineer's PC using a highspeed USB 2.0 interface and is connected to the target with a connector compatible with the MPLAB ICD 2 or MPLAB REAL ICE systems (RJ-11). MPLAB ICD 3 supports all MPLAB ICD 2 headers.

## 31.9 PICkit 3 In-Circuit Debugger/ Programmer

The MPLAB PICkit 3 allows debugging and programming of PIC and dsPIC Flash microcontrollers at a most affordable price point using the powerful graphical user interface of the MPLAB IDE. The MPLAB PICkit 3 is connected to the design engineer's PC using a fullspeed USB interface and can be connected to the target via a Microchip debug (RJ-11) connector (compatible with MPLAB ICD 3 and MPLAB REAL ICE). The connector uses two device I/O pins and the Reset line to implement in-circuit debugging and In-Circuit Serial Programming<sup>™</sup> (ICSP<sup>™</sup>).

## 31.10 MPLAB PM3 Device Programmer

The MPLAB PM3 Device Programmer is a universal, CE compliant device programmer with programmable voltage verification at VDDMIN and VDDMAX for maximum reliability. It features a large LCD display (128 x 64) for menus and error messages, and a modular, detachable socket assembly to support various package types. The ICSP cable assembly is included as a standard item. In Stand-Alone mode, the MPLAB PM3 Device Programmer can read, verify and program PIC devices without a PC connection. It can also set code protection in this mode. The MPLAB PM3 connects to the host PC via an RS-232 or USB cable. The MPLAB PM3 has high-speed communications and optimized algorithms for quick programming of large memory devices, and incorporates an MMC card for file storage and data applications.

## 31.11 Demonstration/Development Boards, Evaluation Kits, and Starter Kits

A wide variety of demonstration, development and evaluation boards for various PIC MCUs and dsPIC DSCs allows quick application development on fully functional systems. Most boards include prototyping areas for adding custom circuitry and provide application firmware and source code for examination and modification.

The boards support a variety of features, including LEDs, temperature sensors, switches, speakers, RS-232 interfaces, LCD displays, potentiometers and additional EEPROM memory.

The demonstration and development boards can be used in teaching environments, for prototyping custom circuits and for learning about various microcontroller applications.