Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFl

| Product Status             | Active                                                                           |

|----------------------------|----------------------------------------------------------------------------------|

| Core Processor             | MIPS32 ® M4K™                                                                    |

| Core Size                  | 32-Bit Single-Core                                                               |

| Speed                      | 80MHz                                                                            |

| Connectivity               | Ethernet, I <sup>2</sup> C, SPI, UART/USART, USB OTG                             |

| Peripherals                | Brown-out Detect/Reset, DMA, POR, PWM, WDT                                       |

| Number of I/O              | 53                                                                               |

| Program Memory Size        | 512KB (512K x 8)                                                                 |

| Program Memory Type        | FLASH                                                                            |

| EEPROM Size                | -                                                                                |

| RAM Size                   | 128K x 8                                                                         |

| Voltage - Supply (Vcc/Vdd) | 2.3V ~ 3.6V                                                                      |

| Data Converters            | A/D 16x10b                                                                       |

| Oscillator Type            | Internal                                                                         |

| Operating Temperature      | -40°C ~ 105°C (TA)                                                               |

| Mounting Type              | Surface Mount                                                                    |

| Package / Case             | 64-VFQFN Exposed Pad                                                             |

| Supplier Device Package    | 64-VQFN (9x9)                                                                    |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic32mx695f512h-80v-mr |

|                            |                                                                                  |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

#### TABLE 11: PIN NAMES FOR USB AND ETHERNET DEVICES

| 1          | 21-PIN TFBGA (BOTTOM VIEW)                                                                  |          | L11                                                          |

|------------|---------------------------------------------------------------------------------------------|----------|--------------------------------------------------------------|

|            | PIC32MX664F064L<br>PIC32MX664F128L<br>PIC32MX675F256L<br>PIC32MX675F512L<br>PIC32MX695F512L |          | L1 A11                                                       |

|            | te: The TFBGA package skips from row "H                                                     |          |                                                              |

| Pin #      | Full Pin Name                                                                               | Pin #    | Full Pin Name                                                |

| A1         | PMD4/RE4                                                                                    | E2       | T4CK/RC3                                                     |

| A2         | PMD3/RE3                                                                                    | E3       | ECOL/SCK2/U6TX/U3RTS/PMA5/CN8/RG6                            |

| A3         | TRD0/RG13                                                                                   | E4       | T3CK/RC2                                                     |

| A4         | PMD0/RE0                                                                                    | E5       | VDD                                                          |

| A5         | PMD8/RG0                                                                                    | E6       | ETXERR/PMD9/RG1                                              |

| A6         | ETXD0/PMD10/RF1                                                                             | E7       | Vss                                                          |

| A7         | Vdd                                                                                         | E8       | AETXEN/SDA1/INT4/RA15                                        |

| A8         | Vss                                                                                         | E9       | RTCC/EMDIO/AEMDIO/IC1/RD8                                    |

| A9         | ETXD2/IC5/PMD12/RD12                                                                        | E10      | SS1/IC2/RD9                                                  |

| A10        | OC3/RD2                                                                                     | E11      | AETXCLK/SCL1/INT3/RA14                                       |

| A11        | OC2/RD1                                                                                     | F1       | MCLR                                                         |

| B1         | No Connect (NC)                                                                             | F2       | ERXDV/AERXDV/ECRSDV/AECRSDV//SCL4/SDO2/U3TX/PMA3/CN10/RG8    |

| B2         | AERXERR/RG15                                                                                | F3       | ERXCLK/AERXCLK/EREFCLK/AEREFCLK/SS2/U6RX/U3CTS/PMA2/CN11/RG9 |

| B3         | PMD2/RE2                                                                                    | F4       | ECRS/SDA4/SDI2/U3RX/PMA4/CN9/RG7                             |

| B4         | PMD1/RE1                                                                                    | F5       | Vss                                                          |

| B5         | TRD3/RA7                                                                                    | F6       | No Connect (NC)                                              |

| B6         | ETXD1/PMD11/RF0                                                                             | F7       | No Connect (NC)                                              |

| B7         | VCAP                                                                                        | F8       | VDD                                                          |

| B8         | PMRD/CN14/RD5                                                                               | F9       | OSC1/CLKI/RC12                                               |

| B9         | OC4/RD3                                                                                     | F10      | Vss                                                          |

| B10        | Vss                                                                                         | F11      | OSC2/CLKO/RC15                                               |

| B11        | SOSCO/T1CK/CN0/RC14                                                                         | G1       | AERXD0/INT1/RE8                                              |

| C1         | PMD6/RE6                                                                                    | G2       | AERXD1/INT2/RE9                                              |

| C2         | VDD                                                                                         | G3       | TMS/RA0                                                      |

| C3<br>C4   | TRD1/RG12<br>TRD2/RG14                                                                      | G4<br>G5 | No Connect (NC)<br>VDD                                       |

| C4         | TRCLK/RA6                                                                                   | G5<br>G6 | Vss                                                          |

|            | No Connect (NC)                                                                             | G0<br>G7 | Vss                                                          |

| C0<br>C7   | ETXCLK/PMD15/CN16/RD7                                                                       | G7<br>G8 | No Connect (NC)                                              |

| C8         | OC5/PMWR/CN13/RD4                                                                           | G9       | TDO/RA5                                                      |

| C9         | VDD                                                                                         | G10      | SDA2/RA3                                                     |

| C10        | SOSCI/CN1/RC13                                                                              | G11      | TDI/RA4                                                      |

| C11        | EMDC/AEMDC/IC4/PMCS1/PMA14/RD11                                                             | H1       | AN5/C1IN+/VBUSON/CN7/RB5                                     |

| D1         | T2CK/RC1                                                                                    | H2       | AN4/C1IN-/CN6/RB4                                            |

| D2         | PMD7/RE7                                                                                    | H3       | Vss                                                          |

| D3         | PMD5/RE5                                                                                    | H4       | VDD                                                          |

| D4         | Vss                                                                                         | H5       | No Connect (NC)                                              |

| D5         | Vss                                                                                         | H6       | VDD                                                          |

| D6         | No Connect (NC)                                                                             | H7       | No Connect (NC)                                              |

| D7         | ETXEN/PMD14/CN15/RD6                                                                        | H8       | VBUS                                                         |

| D8         | ETXD3/PMD13/CN19/RD13                                                                       | H9       | VUSB3V3                                                      |

| D9         | SDO1/OC1/INT0/RD0                                                                           | H10      | D+/RG2                                                       |

| D10        | No Connect (NC)                                                                             | H11      | SCL2/RA2                                                     |

| D11        | SCK1/IC3/PMCS2/PMA15/RD10                                                                   | J1       | AN3/C2IN+/CN5/RB3                                            |

| E1<br>Note | T5CK/SDI1/RC4<br>1: Shaded pins are 5V tolerant.                                            | J2       | AN2/C2IN-/CN4/RB2                                            |

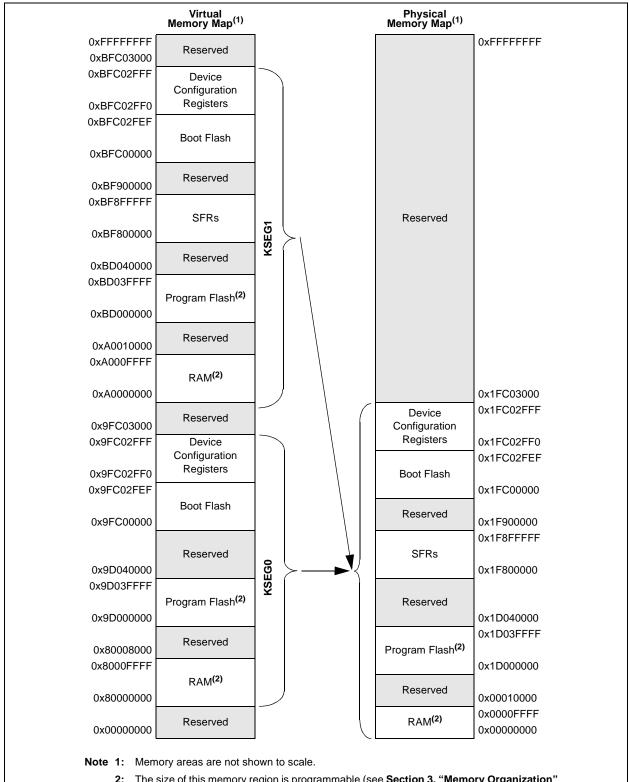

## 4.0 MEMORY ORGANIZATION

Note: This data sheet summarizes the features of the PIC32MX5XX/6XX/7XX family of devices. It is not intended to be a comprehensive reference source. For detailed information, refer to **Section 3.** "Memory Organization" (DS60001115) in the "*PIC32 Family Reference Manual*", which is available from the Microchip web site (www.microchip.com/PIC32).

PIC32MX5XX/6XX/7XX microcontrollers provide 4 GB of unified virtual memory address space. All memory regions, including program, data memory, SFRs and Configuration registers, reside in this address space at their respective unique addresses. The program and data memories can be optionally partitioned into user and kernel memories. In addition, the data memory can be made executable, allowing PIC32MX5XX/6XX/7XX devices to execute from data memory.

Key features include:

- 32-bit native data width

- Separate User (KUSEG) and Kernel (KSEG0/ KSEG1) mode address space

- Flexible program Flash memory partitioning

- Flexible data RAM partitioning for data and program space

- Separate boot Flash memory for protected code

- Robust bus exception handling to intercept runaway code

- Simple memory mapping with Fixed Mapping Translation (FMT) unit

- Cacheable (KSEG0) and non-cacheable (KSEG1) address regions

#### 4.1 Memory Layout

PIC32MX5XX/6XX/7XX microcontrollers implement two address schemes: virtual and physical. All hardware resources, such as program memory, data memory and peripherals, are located at their respective physical addresses. Virtual addresses are exclusively used by the CPU to fetch and execute instructions as well as access peripherals. Physical addresses are used by bus master peripherals, such as DMA and the Flash controller, that access memory independently of the CPU.

The memory maps for the PIC32MX5XX/6XX/7XX devices are illustrated in Figure 4-1 through Figure 4-6. Table 4-1 provides memory map information for the Special Function Registers (SFRs).

#### FIGURE 4-4: MEMORY MAP ON RESET FOR PIC32MX575F256H, PIC32MX575F256L, PIC32MX675F256H, PIC32MX675F256L, PIC32MX775F256H AND PIC32MX775F256L DEVICES

2: The size of this memory region is programmable (see Section 3. "Memory Organization" (DS60001115)) and can be changed by initialization code provided by end user development tools (refer to the specific development tool documentation for information).

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|

| 04.04        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 31:24        | —                 | —                 | —                 | —                 | _                 | —                 | —                | —                |

|              | U-0               | U-0               | U-0               | R/W-1             | R/W-1             | R/W-1             | R/W-1            | R/W-1            |

| 23:16        | _                 | _                 | —                 | BMX<br>ERRIXI     | BMX<br>ERRICD     | BMX<br>ERRDMA     | BMX<br>ERRDS     | BMX<br>ERRIS     |

| 45.0         | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 15:8         | —                 | —                 | —                 | —                 | _                 | —                 | —                | —                |

|              | U-0               | R/W-1             | U-0               | U-0               | U-0               | R/W-0             | R/W-0            | R/W-1            |

| 7:0          | _                 | BMX<br>WSDRM      | —                 | —                 | _                 | E                 | 3MXARB<2:0       | >                |

#### REGISTER 4-1: BMXCON: BUS MATRIX CONFIGURATION REGISTER

## Legend:

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read as '0' |

|-------------------|------------------|------------------------------------|

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared               |

## bit 31-21 **Unimplemented:** Read as '0'

| bit 20   | BMXERRIXI: Enable Bus Error from IXI bit                                                                                                                                                                                              |

|----------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|          | <ul> <li>1 = Enable bus error exceptions for unmapped address accesses initiated from IXI shared bus</li> <li>0 = Disable bus error exceptions for unmapped address accesses initiated from IXI shared bus</li> </ul>                 |

| bit 19   | BMXERRICD: Enable Bus Error from ICD Debug Unit bit                                                                                                                                                                                   |

|          | <ul> <li>1 = Enable bus error exceptions for unmapped address accesses initiated from ICD</li> <li>0 = Disable bus error exceptions for unmapped address accesses initiated from ICD</li> </ul>                                       |

| bit 18   | BMXERRDMA: Bus Error from DMA bit                                                                                                                                                                                                     |

|          | <ul> <li>1 = Enable bus error exceptions for unmapped address accesses initiated from DMA</li> <li>0 = Disable bus error exceptions for unmapped address accesses initiated from DMA</li> </ul>                                       |

| bit 17   | BMXERRDS: Bus Error from CPU Data Access bit (disabled in Debug mode)                                                                                                                                                                 |

|          | <ul> <li>1 = Enable bus error exceptions for unmapped address accesses initiated from CPU data access</li> <li>0 = Disable bus error exceptions for unmapped address accesses initiated from CPU data access</li> </ul>               |

| bit 16   | BMXERRIS: Bus Error from CPU Instruction Access bit (disabled in Debug mode)                                                                                                                                                          |

|          | <ul> <li>1 = Enable bus error exceptions for unmapped address accesses initiated from CPU instruction access</li> <li>0 = Disable bus error exceptions for unmapped address accesses initiated from CPU instruction access</li> </ul> |

| bit 15-7 | Unimplemented: Read as '0'                                                                                                                                                                                                            |

| bit 6    | BMXWSDRM: CPU Instruction or Data Access from Data RAM Wait State bit                                                                                                                                                                 |

|          | <ul> <li>1 = Data RAM accesses from CPU have one wait state for address setup</li> <li>0 = Data RAM accesses from CPU have zero wait states for address setup</li> </ul>                                                              |

| bit 5-3  | Unimplemented: Read as '0'                                                                                                                                                                                                            |

| bit 2-0  | BMXARB<2:0>: Bus Matrix Arbitration Mode bits                                                                                                                                                                                         |

|          | 111 = Reserved (using these Configuration modes will produce undefined behavior)                                                                                                                                                      |

|          |                                                                                                                                                                                                                                       |

|          | •                                                                                                                                                                                                                                     |

|          | 011 = Reserved (using these Configuration modes will produce undefined behavior)                                                                                                                                                      |

|          | 010 = Arbitration Mode 2<br>001 = Arbitration Mode 1 (default)                                                                                                                                                                        |

|          | 000 = Arbitration Mode 0                                                                                                                                                                                                              |

# TABLE 7-5: INTERRUPT REGISTER MAP FOR PIC32MX534F064L, PIC32MX564F064L, PIC32MX564F128L PIC32MX575F512L AND PIC32MX575F256L DEVICES (CONTINUED)

| ess                         |                                 | â         |       |       |       |             |                            |             |               | В                    | its         |        |      |             |             |             |             |                       |            |        |      |

|-----------------------------|---------------------------------|-----------|-------|-------|-------|-------------|----------------------------|-------------|---------------|----------------------|-------------|--------|------|-------------|-------------|-------------|-------------|-----------------------|------------|--------|------|

| Virtual Address<br>(BF88_#) | Register<br>Name <sup>(1)</sup> | Bit Range | 31/15 | 30/14 | 29/13 | 28/12       | 27/11                      | 26/10       | 25/9          | 24/8                 | 23/7        | 22/6   | 21/5 | 20/4        | 19/3        | 18/2        | 17/1        | 16/0                  | All Resets |        |      |

| 10D0                        | IPC4                            | 31:16     | —     | _     | —     | INT4IP<2:0> |                            | INT4IP<2:0> |               | INT4IP<2:0>          |             | S<1:0> |      | —           | —           |             | OC4IP<2:0>  |                       | OC4I       | S<1:0> | 0000 |

| 1000                        | IFC4                            | 15:0      | -     |       | _     |             | IC4IP<2:0>                 |             | IC4IS         | <1:0>                |             | _      | _    |             | T4IP<2:0>   |             | T4IS        | <1:0>                 | 0000       |        |      |

| 4050                        | IDOF                            | 31:16     | Ι     | _     | -     |             | SPI1IP<2:0>                | <b>&gt;</b> | SPI1IS        | S<1:0>               | _           | _      | -    |             | OC5IP<2:0>  |             | OC5I        | S<1:0>                | 0000       |        |      |

| 10E0                        | IPC5                            | 15:0      | _     | _     | _     |             | IC5IP<2:0>                 |             |               | <1:0>                |             | _      | _    |             | T5IP<2:0>   |             | T5IS        | <1:0>                 | 0000       |        |      |

|                             |                                 | 31:16     | _     | _     | _     |             | AD1IP<2:0>                 |             |               | <1:0>                |             | _      | _    |             | CNIP<2:0>   |             | CNIS        | <1:0>                 | 0000       |        |      |

| 10F0                        | IPC6                            |           |       |       |       |             | 710 111 12:07              |             |               |                      |             |        |      |             | U1IP<2:0>   |             | U1IS        | <1:0>                 |            |        |      |

| 10F0                        | IPC6                            | 15:0      | _     | _     | _     |             | I2C1IP<2:0>                |             | I2C1IS<1:0> — |                      | _           | —      |      | SPI3IP<2:0> |             | SPI3I       | SPI3IS<1:0> |                       |            |        |      |

|                             |                                 |           |       |       |       |             |                            |             |               |                      |             |        |      | I2C3IP<2:0> |             | I2C3IS<1:0> |             |                       |            |        |      |

|                             |                                 |           |       |       |       |             | U3IP<2:0>                  |             | U3IS-         | <1:0>                |             |        |      |             |             |             |             |                       |            |        |      |

| 1100                        | IPC7                            | 31:16     | _     | —     | —     |             | SPI2IP<2:0>                | <b>`</b>    | SPI2IS        | S<1:0>               | —           | —      | —    |             | CMP2IP<2:0  | >           | CMP2IS<1:0> |                       | 0000       |        |      |

| 1100                        | 11 07                           |           |       |       |       |             | I2C4IP<2:0>                | •           | I2C4IS<1:0>   |                      |             |        |      |             |             |             |             |                       |            |        |      |

|                             |                                 | 15:0      | —     | —     | —     | (           | CMP1IP<2:0                 | >           | CMP1          | S<1:0>               | _           | _      | —    | PMPIP<2:0>  |             | PMPIS<1:0   |             | 0000                  |            |        |      |

|                             |                                 | 31:16     | —     | —     | —     | F           | RTCCIP<2:0                 | >           | RTCCIS<1:0>   |                      | RTCCIS<1:0> |        | _    | _           | —           |             | FSCMIP<2:0  | >                     | FSCM       | S<1:0> | 0000 |

| 1110                        | IPC8                            |           |       |       |       |             |                            |             |               |                      |             |        |      |             | U2IP<2:0>   |             | U2IS        | <1:0>                 |            |        |      |

| 1110                        | 11 00                           | 15:0      | -     | —     | -     |             | I2C2IP<2:0>                |             | 12C215        | S<1:0>               | —           | —      | —    |             | SPI4IP<2:0> |             | SPI4I       | S<1:0>                | 0000       |        |      |

|                             |                                 |           |       |       |       |             |                            |             |               |                      |             |        |      |             | I2C5IP<2:0> |             | 12C51       | S<1:0>                |            |        |      |

| 1120                        | IPC9                            | 31:16     | -     |       | —     | [           | DMA3IP<2:0                 | >           | DMA3I         | S<1:0>               |             | —      | —    |             | DMA2IP<2:0  | >           | DMA2        | S<1:0>                | 0000       |        |      |

| 1120                        | 11 00                           | 15:0      | —     | _     | —     |             | DMA1IP<2:0                 |             | DMA1          |                      |             |        | —    |             | DMA0IP<2:0  |             |             | S<1:0>                | 0000       |        |      |

| 1130                        | IPC10                           | 31:16     | —     | —     | —     |             | DMA7IP<2:0> <sup>(2)</sup> |             | DMA7IS        | <1:0> <sup>(2)</sup> | _           | _      | —    | D           | MA6IP<2:0>  | (2)         | DMA6IS      | 6<1:0> <sup>(2)</sup> | 0000       |        |      |

| 1130                        | 1 010                           | 15:0      | _     | —     | —     | D           | DMA5IP<2:0> <sup>(2)</sup> |             | DMA5IS        | <1:0> <sup>(2)</sup> | _           | —      | —    | D           | MA4IP<2:0>  | (2)         | DMA4IS      | S<1:0> <sup>(2)</sup> | 0000       |        |      |

| 1140                        | IPC11                           | 31:16     | Ι     |       | _     | _           |                            |             |               |                      | _           | _      | —    | —           | _           |             | CAN1IP<2:0: | >                     | CAN1       | S<1:0> | 0000 |

| 1140                        | 1011                            | 15:0      | _     | _     | —     |             | USBIP<2:0>                 |             | USBIS         | 5<1:0>               | —           | —      | —    |             | FCEIP<2:0>  |             | FCEIS       | S<1:0>                | 0000       |        |      |

| 1150                        | IPC12                           | 31:16     | -     |       | _     |             | U5IP<2:0>                  |             | U5IS-         | <1:0>                | —           | —      | _    | U6IP<2:0>   |             | U6IP<2:0>   |             | U6IS                  | <1:0>      | 0000   |      |

| 1150                        | 11 012                          | 15:0      | -     |       | _     |             | U4IP<2:0>                  |             | U4IS-         | <1:0>                | _           | _      | _    | _           | —           |             | —           | _                     | 0000       |        |      |

PIC32MX5XX/6XX/7XX

Legend: x = unknown value on Reset; - = unimplemented, read as '0'. Reset values are shown in hexadecimal.

Note 1: Except where noted, all registers in this table have corresponding CLR, SET and INV registers at their virtual addresses, plus offsets of 0x4, 0x8 and 0xC, respectively. See Section 12.1.1 "CLR, SET and INV Registers" for more information.

2: These bits are not available on PIC32MX534/564 devices.

3: This register does not have associated CLR, SET, and INV registers.

|                             |                                 | P             | IC32M)  | <b>(795F5</b> 1 | 12L DEV | /ICES                         |                               |                               |                               |                             |                               |                               |                             |                       |                         |        |               |        |            |

|-----------------------------|---------------------------------|---------------|---------|-----------------|---------|-------------------------------|-------------------------------|-------------------------------|-------------------------------|-----------------------------|-------------------------------|-------------------------------|-----------------------------|-----------------------|-------------------------|--------|---------------|--------|------------|

| SS                          |                                 |               |         |                 |         |                               |                               |                               |                               | В                           | its                           |                               |                             |                       |                         |        |               |        |            |

| Virtual Address<br>(BF88_#) | Register<br>Name <sup>(1)</sup> | Bit Range     | 31/15   | 30/14           | 29/13   | 28/12                         | 27/11                         | 26/10                         | 25/9                          | 24/8                        | 23/7                          | 22/6                          | 21/5                        | 20/4                  | 19/3                    | 18/2   | 17/1          | 16/0   | All Resets |

| 1000                        | INTCON                          | 31:16         | _       | _               | —       | _                             | _                             | -                             | —                             | _                           | _                             | —                             | —                           | _                     |                         | —      | —             | SS0    | 0000       |

| 1000                        | INTCON                          | 15:0          | _       | -               | —       | MVEC                          | _                             |                               | TPC<2:0>                      |                             | _                             | —                             | _                           | INT4EP                | INT3EP                  | INT2EP | INT1EP        | INT0EP | 0000       |

| 1010                        | INTSTAT <sup>(3)</sup>          | 31:16         |         | —               | _       | —                             | _                             | _                             | —                             | —                           | _                             | _                             | —                           |                       | —                       | —      | —             |        | 0000       |

|                             |                                 | 15:0          | _       | _               | —       | —                             | —                             |                               | SRIPL<2:0>                    |                             | —                             | —                             |                             |                       | VEC                     | <5:0>  |               |        | 0000       |

| 1020                        | IPTMR                           | 31:16<br>15:0 |         |                 |         |                               |                               |                               |                               | IPTMR                       | <31:0>                        |                               |                             |                       |                         |        |               |        | 0000       |

| 1030                        | IFS0                            | 31:16         | I2C1MIF | I2C1SIF         | I2C1BIF | U1TXIF<br>SPI3TXIF<br>I2C3MIF | U1RXIF<br>SPI3RXIF<br>I2C3SIF | U1EIF<br>SPI3EIF<br>I2C3BIF   | SPI1TXIF                      | SPI1RXIF                    | SPI1EIF                       | OC5IF                         | IC5IF                       | T5IF                  | INT4IF                  | OC4IF  | IC4IF         | T4IF   | 0000       |

|                             |                                 | 15:0          | INT3IF  | OC3IF           | IC3IF   | T3IF                          | INT2IF                        | OC2IF                         | IC2IF                         | T2IF                        | INT1IF                        | OC1IF                         | IC1IF                       | T1IF                  | INT0IF                  | CS1IF  | CS0IF         | CTIF   | 0000       |

|                             |                                 | 31:16         | IC3EIF  | IC2EIF          | IC1EIF  | ETHIF                         | CAN2IF <sup>(2)</sup>         | CAN1IF                        | USBIF                         | FCEIF                       | DMA7IF <sup>(2)</sup>         | DMA6IF <sup>(2)</sup>         | DMA5IF <sup>(2)</sup>       | DMA4IF <sup>(2)</sup> | DMA3IF                  | DMA2IF | DMA1IF        | DMA0IF | 0000       |

| 1040                        | IFS1                            | 15:0          | RTCCIF  | FSCMIF          | I2C2MIF | I2C2SIF                       | I2C2BIF                       | U2TXIF<br>SPI4TXIF<br>I2C5MIF | U2RXIF<br>SPI4RXIF<br>I2C5SIF | U2EIF<br>SPI4EIF<br>I2C5BIF | U3TXIF<br>SPI2TXIF<br>I2C4MIF | U3RXIF<br>SPI2RXIF<br>I2C4SIF | U3EIF<br>SPI2EIF<br>I2C4BIF | CMP2IF                | CMP1IF                  | PMPIF  | AD1IF         | CNIF   | 0000       |

|                             |                                 | 31:16         | _       | _               | _       | _                             | _                             | _                             | _                             | _                           | _                             | _                             | _                           | _                     | _                       | _      | _             | _      | 0000       |

| 1050                        | IFS2                            | 15:0          |         | _               | _       | _                             | U5TXIF                        | U5RXIF                        | U5EIF                         | U6TXIF                      | U6RXIF                        | U6EIF                         | U4TXIF                      | U4RXIF                | U4EIF                   | PMPEIF | IC5EIF        | IC4EIF | 0000       |

| 1060                        | IEC0                            | 31:16         | I2C1MIE | I2C1SIE         | I2C1BIE | U1TXIE<br>SPI3TXIE<br>I2C3MIE | U1RXIE<br>SPI3RXIE<br>I2C3SIE | U1EIE<br>SPI3EIE<br>I2C3BIE   | SPI1TXIE                      | SPI1RXIE                    | SPI1EIE                       | OC5IE                         | IC5IE                       | T5IE                  | INT4IE                  | OC4IE  | IC4IE         | T4IE   | 0000       |

|                             |                                 | 15:0          | INT3IE  | OC3IE           | IC3IE   | T3IE                          | INT2IE                        | OC2IE                         | IC2IE                         | T2IE                        | INT1IE                        | OC1IE                         | IC1IE                       | T1IE                  | INT0IE                  | CS1IE  | CS0IE         | CTIE   | 0000       |

|                             |                                 | 31:16         | IC3EIE  | IC2EIE          | IC1EIE  | ETHIE                         | CAN2IE <sup>(2)</sup>         | CAN1IE                        | USBIE                         | FCEIE                       | DMA7IE <sup>(2)</sup>         | DMA6IE <sup>(2)</sup>         | DMA5IE <sup>(2)</sup>       | DMA4IE <sup>(2)</sup> | DMA3IE                  | DMA2IE | DMA1IE        | DMA0IE | 0000       |

| 1070                        | IEC1                            | 15:0          | RTCCIE  | FSCMIE          | I2C2MIE | I2C2SIE                       | I2C2BIE                       | U2TXIE<br>SPI4TXIE<br>I2C5MIE | U2RXIE<br>SPI4RXIE<br>I2C5SIE | U2EIE<br>SPI4EIE<br>I2C5BIE | U3TXIE<br>SPI2TXIE<br>I2C4MIE | U3RXIE<br>SPI2RXIE<br>I2C4SIE | U3EIE<br>SPI2EIE<br>I2C4BIE | CMP2IE                | CMP1IE                  | PMPIE  | AD1IE         | CNIE   | 0000       |

|                             | 1500                            | 31:16         | _       | _               | _       | _                             | _                             | _                             | _                             | _                           | _                             | _                             | _                           | _                     | _                       | _      | _             | _      | 0000       |

| 1080                        | IEC2                            | 15:0          | _       | —               | _       | _                             | U5TXIE                        | U5RXIE                        | U5EIE                         | U6TXIE                      | U6RXIE                        | U6EIE                         | U4TXIE                      | U4RXIE                | U4EIE                   | PMPEIE | IC5EIE        | IC4EIE | 0000       |

| 1090                        | IPC0                            | 31:16         |         | _               | —       |                               | INT0IP<2:0>                   |                               | INTOIS                        | S<1:0>                      | _                             | —                             | —                           |                       | CS1IP<2:0>              | >      | CS1IS         | S<1:0> | 0000       |

| 1090                        | IFCU                            | 15:0          | —       | —               | —       |                               | CS0IP<2:0>                    |                               | CSOIS                         | 5<1:0>                      | —                             | —                             | —                           |                       | CTIP<2:0>               |        | CTIS          | <1:0>  | 0000       |

| 10A0                        | IPC1                            | 31:16         |         | —               |         |                               | INT1IP<2:0>                   |                               | INT1IS                        |                             | —                             |                               | —                           |                       | OC1IP<2:0>              | >      | OC1IS         |        | 0000       |

|                             |                                 | 15:0          |         | —               | —       |                               | IC1IP<2:0>                    |                               | IC1IS                         |                             | _                             | —                             | —                           |                       | T1IP<2:0>               |        | T1IS          |        | 0000       |

| 10B0                        | IPC2                            | 31:16         |         | —               |         |                               | INT2IP<2:0>                   |                               | INT2IS                        |                             | _                             |                               | —                           |                       | OC2IP<2:0>              | >      | OC2IS         |        | 0000       |

|                             |                                 | 15:0          | _       | _               | _       |                               | IC2IP<2:0>                    |                               | IC2IS                         |                             | _                             | _                             | _                           |                       | T2IP<2:0>               |        | T2IS          |        | 0000       |

| 10C0                        | IPC3                            | 31:16<br>15:0 |         |                 | _       |                               | INT3IP<2:0><br>IC3IP<2:0>     |                               | INT3IS<br>IC3IS               |                             |                               |                               |                             |                       | OC3IP<2:0><br>T3IP<2:0> | >      | OC3IS<br>T3IS |        | 0000       |

| í                           |                                 | 15.0          |         |                 |         |                               | 10315 <2.0>                   |                               | 10313                         | <1.U2                       |                               |                               | _                           |                       | 1015 <2.0>              |        | 1313          | <1.02  | 0000       |

# TABLE 7-7:INTERRUPT REGISTER MAP FOR PIC32MX764F128L, PIC32MX775F256L, PIC32MX775F512L AND<br/>PIC32MX795F512L DEVICES

**d:** x = unknown value on Reset; — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

Note 1: Except where noted, all registers in this table have corresponding CLR, SET and INV registers at their virtual addresses, plus offsets of 0x4, 0x8 and 0xC, respectively. See Section 12.1.1 "CLR, SET and INV Registers" for more information.

PIC32MX5XX/6XX/7XX

2: This bit is unimplemented on PIC32MX764F128L device.

3: This register does not have associated CLR, SET, and INV registers.

#### TABLE 10-3: DMA CHANNELS 0-7 REGISTER MAP (CONTINUED)

| ess                         |                                 |           |       |                   |       |       |       |       |      | Bi     | its     |      |      |       |         |      |      |      |            |

|-----------------------------|---------------------------------|-----------|-------|-------------------|-------|-------|-------|-------|------|--------|---------|------|------|-------|---------|------|------|------|------------|

| Virtual Address<br>(BF88_#) | Register<br>Name <sup>(1)</sup> | Bit Range | 31/15 | 30/14             | 29/13 | 28/12 | 27/11 | 26/10 | 25/9 | 24/8   | 23/7    | 22/6 | 21/5 | 20/4  | 19/3    | 18/2 | 17/1 | 16/0 | All Resets |

| 35E0                        | DCH7SSIZ                        | 31:16     | _     |                   | —     |       | -     | —     | —    |        |         |      |      | —     | —       |      | —    | -    | 0000       |

| 001 0                       | DOINCOL                         | 15:0      |       | CHSSIZ<15:0> 0000 |       |       |       |       |      |        |         |      |      |       |         |      |      |      |            |

| 2600                        | DCH7DSIZ                        | 31:16     | —     |                   | —     | _     | _     | —     | —    | _      | _       | _    | _    | —     | —       | _    | —    | _    | 0000       |

| 3600                        | DCHIDSIZ                        | 15:0      |       |                   |       |       |       |       |      | CHDSIZ | Z<15:0> |      |      |       |         |      |      |      | 0000       |

| 2610                        | DCH7SPTR                        | 31:16     | Ι     | _                 | _     | _     | _     | _     | _    | _      | _       | _    | _    | _     | -       | _    | _    | _    | 0000       |

| 3010                        | DCH/SPIK                        | 15:0      |       |                   |       |       |       |       |      | CHSPT  | R<15:0> |      |      |       |         |      |      |      | 0000       |

| 2620                        | DCH7DPTR                        | 31:16     |       |                   | _     |       |       | _     | _    |        |         |      |      | _     | _       |      | _    |      | 0000       |

| 3020                        | DCHIDFIK                        | 15:0      |       |                   |       |       |       |       |      | CHDPT  | R<15:0> |      |      |       |         |      |      |      | 0000       |

| 2620                        | DCH7CSIZ                        | 31:16     | _     |                   | _     | -     |       | _     |      |        |         |      | -    |       | _       | _    | _    |      | 0000       |

| 3030                        | DCH/CSIZ                        | 15:0      |       |                   |       |       |       |       |      | CHCSIZ | Z<15:0> |      |      |       |         |      |      |      | 0000       |

| 2640                        | DCH7CPTR                        | 31:16     | Ι     | _                 | _     | _     | _     | _     | _    | _      | _       | _    | _    | _     | -       | _    | _    | _    | 0000       |

| 3040                        | DCH/CPIK                        | 15:0      |       |                   |       |       |       |       |      | CHCPT  | R<15:0> |      |      |       |         |      |      |      | 0000       |

| 2650                        | DCH7DAT                         | 31:16     | Ι     | _                 | _     | _     | _     | _     | _    | _      | _       | _    | _    | _     | -       | _    | _    | _    | 0000       |

| 3050                        |                                 | 15:0      | _     | _                 | —     | —     | _     | —     | —    | _      |         |      |      | CHPDA | AT<7:0> |      |      |      | 0000       |

PIC32MX5XX/6XX/7XX

Legend: x = unknown value on Reset; — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

Note 1: All registers in this table have corresponding CLR, SET and INV registers at their virtual addresses, plus offsets of 0x4, 0x8 and 0xC, respectively. See Section 12.1.1 "CLR, SET and INV Registers" for more information.

2: DMA channels 4-7 are not available on PIC32MX534/564/664/764 devices.

# PIC32MX5XX/6XX/7XX

#### REGISTER 11-7: U1IE: USB INTERRUPT ENABLE REGISTER

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1      | Bit<br>24/16/8/0        |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|-----------------------|-------------------------|

| 31:24        | U-0                   | U-0                     |

| 31.24        | —                 | —                 | —                 | —                 | _                 | —                 | _                     |                         |

| 23:16        | U-0                   | U-0                     |

| 23.10        | —                 | —                 | —                 | —                 | _                 | —                 | _                     |                         |

| 15:8         | U-0                   | U-0                     |

| 15.6         | —                 | —                 | —                 | —                 | _                 | —                 | _                     |                         |

|              | R/W-0                 | R/W-0                   |

| 7:0          | STALLIE           | ATTACHIE          | RESUMEIE          | IDLEIE            | TRNIE             | SOFIE             | UERRIE <sup>(1)</sup> | URSTIE <sup>(2)</sup>   |

|              | STALLIE           | ATTACHIE          | RESUMEIE          | IDLEIE            |                   | SOFIE             | UERRIE'               | DETACHIE <sup>(3)</sup> |

#### Legend:

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, | read as '0'        |

|-------------------|------------------|------------------------|--------------------|

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared   | x = Bit is unknown |

#### bit 31-8 Unimplemented: Read as '0'

|       | •·····                                                          |

|-------|-----------------------------------------------------------------|

| bit 7 | STALLIE: STALL Handshake Interrupt Enable bit                   |

|       | 1 = STALL interrupt is enabled                                  |

|       | 0 = STALL interrupt is disabled                                 |

| bit 6 | ATTACHIE: ATTACH Interrupt Enable bit                           |

|       | 1 = ATTACH interrupt is enabled                                 |

|       | 0 = ATTACH interrupt is disabled                                |

| bit 5 | RESUMEIE: RESUME Interrupt Enable bit                           |

|       | 1 = RESUME interrupt is enabled                                 |

|       | 0 = RESUME interrupt is disabled                                |

| bit 4 | IDLEIE: Idle Detect Interrupt Enable bit                        |

|       | 1 = Idle interrupt is enabled                                   |

|       | 0 = Idle interrupt is disabled                                  |

| bit 3 | TRNIE: Token Processing Complete Interrupt Enable bit           |

|       | 1 = TRNIF interrupt is enabled                                  |

|       | 0 = TRNIF interrupt is disabled                                 |

| bit 2 | SOFIE: SOF Token Interrupt Enable bit                           |

|       | 1 = SOFIF interrupt is enabled                                  |

|       | 0 = SOFIF interrupt is disabled                                 |

| bit 1 | UERRIE: USB Error Interrupt Enable bit <sup>(1)</sup>           |

|       | 1 = USB Error interrupt is enabled                              |

|       | 0 = USB Error interrupt is disabled                             |

| bit 0 | URSTIE: USB Reset Interrupt Enable bit <sup>(2)</sup>           |

|       | 1 = URSTIF interrupt is enabled                                 |

|       | 0 = URSTIF interrupt is disabled                                |

|       | <b>DETACHIE:</b> USB Detach Interrupt Enable bit <sup>(3)</sup> |

|       | 1 = DATTCHIF interrupt is enabled                               |

|       | 0 = DATTCHIF interrupt is disabled                              |

|       |                                                                 |

**Note 1:** For an interrupt to propagate USBIF, the UERRIE bit (U1IE<1>) must be set.

- 2: Device mode.

- 3: Host mode.

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|

| 21.24        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 31:24        |                   | —                 | -                 | -                 | _                 | _                 | —                | —                |

| 23:16        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 23.10        | —                 | —                 | _                 | _                 | —                 | _                 | -                | —                |

| 15.0         | R/W-0             | U-0               | R/W-0             | R/W-0             | R-0               | U-0               | U-0              | U-0              |

| 15:8         | ON <sup>(1)</sup> | —                 | SIDL              | TWDIS             | TWIP              | -                 |                  | —                |

| 7.0          | R/W-0             | U-0               | R/W-0             | R/W-0             | U-0               | R/W-0             | R/W-0            | U-0              |

| 7:0          | TGATE             | —                 | TCKPS             | S<1:0>            | _                 | TSYNC             | TCS              | —                |

#### REGISTER 13-1: T1CON: TYPE A TIMER CONTROL REGISTER

#### Legend:

| R = Readable bit  | = Readable bit W = Writable bit |                      | ead as '0'         |

|-------------------|---------------------------------|----------------------|--------------------|

| -n = Value at POR | '1' = Bit is set                | '0' = Bit is cleared | x = Bit is unknown |

#### bit 31-16 Unimplemented: Read as '0'

- bit 15 **ON:** Timer On bit<sup>(1)</sup>

- 1 = Timer is enabled 0 = Timer is disabled

#### bit 14 Unimplemented: Read as '0'

#### bit 13 **SIDL:** Stop in Idle Mode bit

- 1 = Discontinue operation when device enters Idle mode

- 0 = Continue operation when device is in Idle mode

## bit 12 **TWDIS:** Asynchronous Timer Write Disable bit

- 1 = Writes to TMR1 are ignored until pending write operation completes

- 0 = Back-to-back writes are enabled (Legacy Asynchronous Timer functionality)

#### bit 11 TWIP: Asynchronous Timer Write in Progress bit

In Asynchronous Timer mode:

1 = Asynchronous write to TMR1 register in progress

0 = Asynchronous write to TMR1 register complete

In Synchronous Timer mode:

This bit is read as '0'.

- bit 10-8 **Unimplemented:** Read as '0'

- bit 7 TGATE: Timer Gated Time Accumulation Enable bit

<u>When TCS = 1:</u> This bit is ignored.

When TCS = 0:

- 1 = Gated time accumulation is enabled

- 0 =Gated time accumulation is disabled

- bit 6 Unimplemented: Read as '0'

- bit 5-4 TCKPS<1:0>: Timer Input Clock Prescale Select bits

- 11 = 1:256 prescale value

- 10 = 1:64 prescale value

- 01 = 1:8 prescale value

- 00 = 1:1 prescale value

- **Note 1:** When using the 1:1 PBCLK divisor, the user's software should not read/write the peripheral SFRs in the SYSCLK cycle immediately following the instruction that clears the module's ON bit.

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3                  | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

|--------------|-------------------|-------------------|-------------------|-------------------|------------------------------------|-------------------|------------------|------------------|

| 04-04        | R/W-x             | R/W-x             | R/W-x             | R/W-x             | R/W-x                              | R/W-x             | R/W-x            | R/W-x            |

| 31:24        |                   | YEAR1             | 0<3:0>            |                   |                                    | YEAR0             | 1<3:0>           |                  |

| 00.40        | R/W-x             | R/W-x             | R/W-x             | R/W-x             | R/W-x                              | R/W-x             | R/W-x            | R/W-x            |

| 23:16        | MONTH10<3:0>      |                   |                   |                   | MONTH01<3:0>                       |                   |                  |                  |

| 45.0         | R/W-x             | R/W-x             | R/W-x             | R/W-x             | R/W-x                              | R/W-x             | R/W-x            | R/W-x            |

| 15:8         | DAY10<3:0>        |                   |                   |                   | DAY01<3:0>                         |                   |                  |                  |

| 7.0          | U-0               | U-0               | U-0               | U-0               | R/W-x                              | R/W-x             | R/W-x            | R/W-x            |

| 7:0          | —                 | —                 | _                 | _                 | WDAY01<3:0>                        |                   |                  |                  |

|              |                   | •                 |                   |                   | •                                  |                   |                  |                  |

| Legend:      |                   |                   |                   |                   |                                    |                   |                  |                  |

| R = Read     | able bit          |                   | W = Writable      | e bit             | U = Unimplemented bit, read as '0' |                   |                  |                  |

0' = Bit is cleared

#### REGISTER 22-4: RTCDATE: RTC DATE VALUE REGISTER

bit 31-28 YEAR10<3:0>: Binary-Coded Decimal Value of Years bits, 10 digits

'1' = Bit is set

bit 27-24 YEAR01<3:0>: Binary-Coded Decimal Value of Years bits, 1 digit

bit 23-20 MONTH10<3:0>: Binary-Coded Decimal Value of Months bits, 10 digits; contains a value from 0 to 1

bit 19-16 MONTH01<3:0>: Binary-Coded Decimal Value of Months bits, 1 digit; contains a value from 0 to 9

bit 15-12 DAY10<3:0>: Binary-Coded Decimal Value of Days bits, 10 digits; contains a value from 0 to 3

bit 11-8 DAY01<3:0>: Binary-Coded Decimal Value of Days bits, 1 digit; contains a value from 0 to 9

bit 7-4 Unimplemented: Read as '0'

-n = Value at POR

bit 3-0 WDAY01<3:0>: Binary-Coded Decimal Value of Weekdays bits,1 digit; contains a value from 0 to 6

**Note:** This register is only writable when RTCWREN = 1 (RTCCON<3>).

x = Bit is unknown

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|

| 24.24        | U-0               | U-0               | U-0               | U-0               | S/HC-0            | R/W-1             | R/W-0            | R/W-0            |

| 31:24        | —                 | _                 | _                 | —                 | ABAT              | REQOP<2:0>        |                  |                  |

| 23:16        | R-1               | R-0               | R-0               | R/W-0             | U-0               | U-0               | U-0              | U-0              |

| 23.10        | OPMOD<2:0>        |                   |                   | CANCAP            | —                 | —                 | —                | —                |

| 15.0         | R/W-0             | U-0               | R/W-0             | U-0               | R-0               | U-0               | U-0              | U-0              |

| 15:8         | ON <sup>(1)</sup> | _                 | SIDLE             | —                 | CANBUSY           | —                 | —                | —                |

| 7.0          | U-0               | U-0               | U-0               | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |

| 7:0          | —                 | _                 |                   |                   | [                 | DNCNT<4:0>        |                  |                  |

#### REGISTER 24-1: CICON: CAN MODULE CONTROL REGISTER

| Legend: HC = Hardware Clear |                  | S = Settable bit                   |                    |  |

|-----------------------------|------------------|------------------------------------|--------------------|--|

| R = Readable bit            | W = Writable bit | U = Unimplemented bit, read as '0' |                    |  |

| -n = Value at POR           | '1' = Bit is set | '0' = Bit is cleared               | x = Bit is unknown |  |

#### bit 31-28 Unimplemented: Read as '0'

- bit 27 **ABAT:** Abort All Pending Transmissions bit

- 1 = Signal all transmit buffers to abort transmission

- 0 = Module will clear this bit when all transmissions aborted

#### bit 26-24 REQOP<2:0>: Request Operation Mode bits

- 111 = Set Listen All Messages mode

- 110 = Reserved

- 101 = Reserved

- 100 = Set Configuration mode

- 011 = Set Listen Only mode

- 010 = Set Loopback mode

- 001 = Set Disable mode

- 000 = Set Normal Operation mode

#### bit 23-21 OPMOD<2:0>: Operation Mode Status bits

- 111 = Module is in Listen All Messages mode

- 110 = Reserved

- 101 = Reserved

- 100 = Module is in Configuration mode

- 011 = Module is in Listen Only mode

- 010 = Module is in Loopback mode

- 001 = Module is in Disable mode

- 000 = Module is in Normal Operation mode

#### bit 20 CANCAP: CAN Message Receive Time Stamp Timer Capture Enable bit

- 1 = CANTMR value is stored on valid message reception and is stored with the message

- 0 = Disable CAN message receive time stamp timer capture and stop CANTMR to conserve power

- bit 19-16 Unimplemented: Read as '0'

- bit 15 ON: CAN On bit<sup>(1)</sup>

- 1 = CAN module is enabled

- 0 = CAN module is disabled

- bit 14 Unimplemented: Read as '0'

- **Note 1:** If the user application clears this bit, it may take a number of cycles before the CAN module completes the current transaction and responds to this request. The user application should poll the CANBUSY bit to verify that the request has been honored.

#### REGISTER 24-11: CIFLTCON1: CAN FILTER CONTROL REGISTER 1 (CONTINUED)

| bit 15    | FLTEN5: Filter 17 Enable bit                                                                           |

|-----------|--------------------------------------------------------------------------------------------------------|

|           | 0 = Filter is disabled                                                                                 |

| bit 14-13 | MSEL5<1:0>: Filter 5 Mask Select bits                                                                  |

|           | 11 = Acceptance Mask 3 selected                                                                        |

|           | 10 = Acceptance Mask 2 selected                                                                        |

|           | 01 = Acceptance Mask 1 selected<br>00 = Acceptance Mask 0 selected                                     |

| bit 12-8  | FSEL5<4:0>: FIFO Selection bits                                                                        |

|           | 11111 = Message matching filter is stored in FIFO buffer 31                                            |

|           | 11110 = Message matching filter is stored in FIFO buffer 30                                            |

|           | •                                                                                                      |

|           | •                                                                                                      |

|           | 00001 = Message matching filter is stored in FIFO buffer 1                                             |

|           | 00000 = Message matching filter is stored in FIFO buffer 0                                             |

| bit 7     | FLTEN4: Filter 4 Enable bit                                                                            |

|           | <ul><li>1 = Filter is enabled</li><li>0 = Filter is disabled</li></ul>                                 |

| bit 6-5   | MSEL4<1:0>: Filter 4 Mask Select bits                                                                  |

|           | 11 = Acceptance Mask 3 selected                                                                        |

|           | 10 = Acceptance Mask 2 selected                                                                        |

|           | 01 = Acceptance Mask 1 selected<br>00 = Acceptance Mask 0 selected                                     |

| bit 4-0   | FSEL4<4:0>: FIFO Selection bits                                                                        |

|           | 11111 = Message matching filter is stored in FIFO buffer 31                                            |

|           | 11110 = Message matching filter is stored in FIFO buffer 30                                            |

|           | •                                                                                                      |

|           | •                                                                                                      |

|           | 00001 = Message matching filter is stored in FIFO buffer 1                                             |

|           | 00000 = Message matching filter is stored in FIFO buffer 0                                             |

| Note:     | The bits in this register can only be modified if the corresponding filter enable (FLTENn) bit is '0'. |

# PIC32MX5XX/6XX/7XX

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|--|

| 21.24        | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |

| 31:24        | FLTEN19           | MSEL19<1:0>       |                   |                   | FSEL19<4:0>       |                   |                  |                  |  |

| 00.40        | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |

| 23:16        | FLTEN18           | MSEL18<1:0>       |                   | FSEL18<4:0>       |                   |                   |                  |                  |  |

| 45.0         | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |

| 15:8         | FLTEN17           | MSEL17<1:0>       |                   | FSEL17<4:0>       |                   |                   |                  |                  |  |

| 7.0          | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |

| 7:0          | FLTEN16           | MSEL1             | 6<1:0>            | FSEL16<4:0>       |                   |                   |                  |                  |  |

#### REGISTER 24-14: CIFLTCON4: CAN FILTER CONTROL REGISTER 4

#### Legend:

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read as '0' |                    |  |

|-------------------|------------------|------------------------------------|--------------------|--|

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared               | x = Bit is unknown |  |

| bit 31    | <b>FLTEN19:</b> Filter 19 Enable bit<br>1 = Filter is enabled<br>0 = Filter is disabled                                                                                             |

|-----------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| bit 30-29 | MSEL19<1:0>: Filter 19 Mask Select bits<br>11 = Acceptance Mask 3 selected<br>10 = Acceptance Mask 2 selected<br>01 = Acceptance Mask 1 selected<br>00 = Acceptance Mask 0 selected |

| bit 28-24 | <pre>11111 = Message matching filter is stored in FIFO buffer 31 11110 = Message matching filter is stored in FIFO buffer 30</pre>                                                  |

|           | 00001 = Message matching filter is stored in FIFO buffer 1<br>00000 = Message matching filter is stored in FIFO buffer 0                                                            |

| bit 23    | FLTEN18: Filter 18 Enable bit                                                                                                                                                       |

|           | <ul><li>1 = Filter is enabled</li><li>0 = Filter is disabled</li></ul>                                                                                                              |

| bit 22-21 | MSEL18<1:0>: Filter 18 Mask Select bits                                                                                                                                             |

|           | <ul> <li>11 = Acceptance Mask 3 selected</li> <li>10 = Acceptance Mask 2 selected</li> <li>01 = Acceptance Mask 1 selected</li> <li>00 = Acceptance Mask 0 selected</li> </ul>      |

| bit 20-16 | FSEL18<4:0>: FIFO Selection bits                                                                                                                                                    |

|           | 11111 = Message matching filter is stored in FIFO buffer 31                                                                                                                         |

|           | 11110 = Message matching filter is stored in FIFO buffer 30                                                                                                                         |

|           |                                                                                                                                                                                     |

|           | •                                                                                                                                                                                   |

|           | 00001 = Message matching filter is stored in FIFO buffer 1<br>00000 = Message matching filter is stored in FIFO buffer 0                                                            |

|           |                                                                                                                                                                                     |

Note: The bits in this register can only be modified if the corresponding filter enable (FLTENn) bit is '0'.

#### REGISTER 25-1: ETHCON1: ETHERNET CONTROLLER CONTROL REGISTER 1 (CONTINUED)

- bit 7 **AUTOFC:** Automatic Flow Control bit

- 1 = Automatic Flow Control is enabled

- 0 = Automatic Flow Control is disabled

Setting this bit will enable automatic Flow Control. If set, the full and empty watermarks are used to automatically enable and disable the Flow Control, respectively. When the number of received buffers BUFCNT (ETHSTAT<16:23>) rises to the full watermark, Flow Control is automatically enabled. When the BUFCNT falls to the empty watermark, Flow Control is automatically disabled.

This bit is only used for Flow Control operations and affects both TX and RX operations.

#### bit 6-5 Unimplemented: Read as '0'

#### bit 4 MANFC: Manual Flow Control bit

- 1 = Manual Flow Control is enabled

- 0 = Manual Flow Control is disabled

Setting this bit will enable manual Flow Control. If set, the Flow Control logic will send a PAUSE frame using the PAUSE timer value in the PTV register. It will then resend a PAUSE frame every 128 \* PTV<15:0>/2 TX clock cycles until the bit is cleared.

**Note:** For 10 Mbps operation, TX clock runs at 2.5 MHz. For 100 Mbps operation, TX clock runs at 25 MHz.

When this bit is cleared, the Flow Control logic will automatically send a PAUSE frame with a 0x0000 PAUSE timer value to disable Flow Control.

This bit is only used for Flow Control operations and affects both TX and RX operations.

#### bit 3-1 Unimplemented: Read as '0'

bit 0 BUFCDEC: Descriptor Buffer Count Decrement bit

The BUFCDEC bit is a write-1 bit that reads as '0'. When written with a '1', the Descriptor Buffer Counter, BUFCNT, will decrement by one. If BUFCNT is incremented by the RX logic at the same time that this bit is written, the BUFCNT value will remain unchanged. Writing a '0' will have no effect.

This bit is only used for RX operations.

**Note 1:** It is not recommended to clear the RXEN bit and then make changes to any RX related field/register. The Ethernet Controller must be reinitialized (ON cleared to '0'), and then the RX changes applied.

| Bit Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |

|-----------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|--|

| 31:24     | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |

| 31.24     |                   |                   |                   | PMM<              | 31:24>            |                   |                  |                  |  |