Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFI

| Details                    |                                                                                  |

|----------------------------|----------------------------------------------------------------------------------|

| Product Status             | Active                                                                           |

| Core Processor             | MIPS32® M4K™                                                                     |

| Core Size                  | 32-Bit Single-Core                                                               |

| Speed                      | 80MHz                                                                            |

| Connectivity               | Ethernet, I <sup>2</sup> C, SPI, UART/USART, USB OTG                             |

| Peripherals                | Brown-out Detect/Reset, DMA, POR, PWM, WDT                                       |

| Number of I/O              | 51                                                                               |

| Program Memory Size        | 512KB (512K x 8)                                                                 |

| Program Memory Type        | FLASH                                                                            |

| EEPROM Size                |                                                                                  |

| RAM Size                   | 128K x 8                                                                         |

| Voltage - Supply (Vcc/Vdd) | 2.3V ~ 3.6V                                                                      |

| Data Converters            | A/D 16x10b                                                                       |

| Oscillator Type            | Internal                                                                         |

| Operating Temperature      | -40°C ~ 105°C (TA)                                                               |

| Mounting Type              | Surface Mount                                                                    |

| Package / Case             | 64-TQFP                                                                          |

| Supplier Device Package    | 64-TQFP (10x10)                                                                  |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic32mx695f512h-80v-pt |

|                            |                                                                                  |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

### TABLE 11: PIN NAMES FOR USB AND ETHERNET DEVICES (CONTINUED)

| 1     | 21-PIN TFBGA (BOTTOM VIEW                                                                   | /)         | L11                                         |    |  |  |  |

|-------|---------------------------------------------------------------------------------------------|------------|---------------------------------------------|----|--|--|--|

|       | PIC32MX664F064L<br>PIC32MX664F128L<br>PIC32MX675F256L<br>PIC32MX675F512L<br>PIC32MX695F512L |            |                                             | 11 |  |  |  |

| No    | te: The TFBGA package skips from row                                                        | / "H" to r | ow "J" and has no "I" row. A1               |    |  |  |  |

| Pin # | Full Pin Name                                                                               | Pin #      | Full Pin Name                               |    |  |  |  |

| J3    | PGED2/AN7/RB7                                                                               | K8         | VDD                                         |    |  |  |  |

| J4    | AVDD                                                                                        | K9         | AETXD1/SCK3/U4TX/U1RTS/CN21/RD15            |    |  |  |  |

| J5    | AN11/ERXERR/AETXERR/PMA12/RB11                                                              | K10        | USBID/RF3                                   |    |  |  |  |

| J6    | TCK/RA1                                                                                     | K11        | SDA3/SDI3/U1RX/RF2                          |    |  |  |  |

| J7    | AN12/ERXD0/AECRS/PMA11/RB12                                                                 | L1         | PGEC2/AN6/OCFA/RB6                          |    |  |  |  |

| J8    | No Connect (NC)                                                                             | L2         | VREF-/CVREF-/AERXD2/PMA7/RA9                |    |  |  |  |

| J9    | No Connect (NC)                                                                             | L3         | AVss                                        |    |  |  |  |

| J10   | SCL3/SDO3/U1TX/RF8                                                                          | L4         | AN9/C2OUT/RB9                               |    |  |  |  |

| J11   | D-/RG3                                                                                      | L5         | AN10/CVREFOUT/PMA13/RB10                    |    |  |  |  |

| K1    | PGEC1/AN1/CN3/RB1                                                                           | L6         | SCK4/U5TX/U2RTS/RF13                        |    |  |  |  |

| K2    | K2 PGED1/AN0/CN2/RB0 L7 AN13/ERXD1/AECOL/PMA10/RB13                                         |            |                                             |    |  |  |  |

| K3    | VREF+/CVREF+/AERXD3/PMA6/RA10                                                               | L8         | AN15/ERXD3/AETXD2/OCFB/PMALL/PMA0/CN12/RB15 |    |  |  |  |

| K4    | AN8/C1OUT/RB8                                                                               | L9         | AETXD0/SS3/U4RX/U1CTS/CN20/RD14             |    |  |  |  |

| K5    | No Connect (NC)                                                                             | L10        | SDA5/SDI4/U2RX/PMA9/CN17/RF4                |    |  |  |  |

| K6    | SS4/U5RX/U2CTS/RF12                                                                         | L11        | SCL5/SDO4/U2TX/PMA8/CN18/RF5                |    |  |  |  |

| K7    | AN14/ERXD2/AETXD3/PMALH/PMA1/RB14                                                           |            |                                             |    |  |  |  |

Note 1: Shaded pins are 5V tolerant.

|                       |                 | nber <sup>(1)</sup>             |                                                                                                             | <b>.</b> .                                                                                   | Dutt                                                                                                   |                                                                                                                                                                                                                         |  |

|-----------------------|-----------------|---------------------------------|-------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| 64-Pin<br>N/TQFP      | 100-Pin<br>TQFP | 121-Pin<br>TFBGA                | 124-pin<br>VTLA                                                                                             | Pin<br>Type                                                                                  | Buffer<br>Type                                                                                         | Description                                                                                                                                                                                                             |  |

| 46                    | 72              | D9                              | B39                                                                                                         | I/O                                                                                          | ST                                                                                                     | PORTD is a bidirectional I/O port                                                                                                                                                                                       |  |

| 49                    | 76              | A11                             | A52                                                                                                         | I/O                                                                                          | ST                                                                                                     |                                                                                                                                                                                                                         |  |

| 50                    | 77              | A10                             | B42                                                                                                         | I/O                                                                                          | ST                                                                                                     |                                                                                                                                                                                                                         |  |

| 51                    | 78              | B9                              | A53                                                                                                         | I/O                                                                                          | ST                                                                                                     |                                                                                                                                                                                                                         |  |

| 52                    | 81              | C8                              | B44                                                                                                         | I/O                                                                                          | ST                                                                                                     |                                                                                                                                                                                                                         |  |

| 53                    | 82              | B8                              | A55                                                                                                         | I/O                                                                                          | ST                                                                                                     |                                                                                                                                                                                                                         |  |

| 54                    | 83              | D7                              | B45                                                                                                         | I/O                                                                                          | ST                                                                                                     |                                                                                                                                                                                                                         |  |

| 55                    | 84              | C7                              | A56                                                                                                         | I/O                                                                                          | ST                                                                                                     |                                                                                                                                                                                                                         |  |

| 42                    | 68              | E9                              | B37                                                                                                         | I/O                                                                                          | ST                                                                                                     |                                                                                                                                                                                                                         |  |

| 43                    | 69              | E10                             | A45                                                                                                         | I/O                                                                                          | ST                                                                                                     |                                                                                                                                                                                                                         |  |

| 44                    | 70              | D11                             | B38                                                                                                         | I/O                                                                                          | ST                                                                                                     |                                                                                                                                                                                                                         |  |

| 45                    | 71              | C11                             | A46                                                                                                         | I/O                                                                                          | ST                                                                                                     |                                                                                                                                                                                                                         |  |

| _                     | 79              | A9                              | B43                                                                                                         | I/O                                                                                          | ST                                                                                                     |                                                                                                                                                                                                                         |  |

| _                     | 80              | D8                              | A54                                                                                                         | I/O                                                                                          | ST                                                                                                     |                                                                                                                                                                                                                         |  |

| _                     | 47              | L9                              | B26                                                                                                         | I/O                                                                                          | ST                                                                                                     |                                                                                                                                                                                                                         |  |

| _                     | 48              | K9                              | A31                                                                                                         | I/O                                                                                          | ST                                                                                                     |                                                                                                                                                                                                                         |  |

| 60                    | 93              | A4                              | B52                                                                                                         | I/O                                                                                          | ST                                                                                                     | PORTE is a bidirectional I/O port                                                                                                                                                                                       |  |

| 61                    | 94              | B4                              | A64                                                                                                         | I/O                                                                                          | ST                                                                                                     |                                                                                                                                                                                                                         |  |

| 62                    | 98              | B3                              | A66                                                                                                         | I/O                                                                                          | ST                                                                                                     |                                                                                                                                                                                                                         |  |

| 63                    | 99              | A2                              | B56                                                                                                         | I/O                                                                                          | ST                                                                                                     |                                                                                                                                                                                                                         |  |

| 64                    | 100             | A1                              | A67                                                                                                         | I/O                                                                                          | ST                                                                                                     |                                                                                                                                                                                                                         |  |

| 1                     | 3               | D3                              | B2                                                                                                          | I/O                                                                                          | ST                                                                                                     |                                                                                                                                                                                                                         |  |

| 2                     | 4               | C1                              | A4                                                                                                          | I/O                                                                                          | ST                                                                                                     |                                                                                                                                                                                                                         |  |

| 3                     | 5               | D2                              | B3                                                                                                          | I/O                                                                                          | ST                                                                                                     |                                                                                                                                                                                                                         |  |

| _                     | 18              | G1                              | A11                                                                                                         | I/O                                                                                          | ST                                                                                                     |                                                                                                                                                                                                                         |  |

| _                     | 19              | G2                              | B10                                                                                                         | I/O                                                                                          | ST                                                                                                     |                                                                                                                                                                                                                         |  |

| 58                    | 87              | B6                              | B49                                                                                                         | I/O                                                                                          | ST                                                                                                     | PORTF is a bidirectional I/O port                                                                                                                                                                                       |  |

| 59                    | 88              | A6                              | A60                                                                                                         | I/O                                                                                          | ST                                                                                                     |                                                                                                                                                                                                                         |  |

| _                     | 52              | K11                             | A36                                                                                                         | I/O                                                                                          | ST                                                                                                     |                                                                                                                                                                                                                         |  |

| 33                    | 51              | K10                             | A35                                                                                                         | I/O                                                                                          | ST                                                                                                     |                                                                                                                                                                                                                         |  |

| 31                    | 49              | L10                             | B27                                                                                                         | I/O                                                                                          | ST                                                                                                     |                                                                                                                                                                                                                         |  |

| 32                    | 50              | L11                             | A32                                                                                                         | I/O                                                                                          | ST                                                                                                     |                                                                                                                                                                                                                         |  |

| _                     | 53              | J10                             | B29                                                                                                         | I/O                                                                                          | ST                                                                                                     |                                                                                                                                                                                                                         |  |

| _                     | 40              | K6                              | A27                                                                                                         | I/O                                                                                          | ST                                                                                                     |                                                                                                                                                                                                                         |  |

| _                     | 39              | L6                              | B22                                                                                                         | I/O                                                                                          | ST                                                                                                     |                                                                                                                                                                                                                         |  |

| <br><br>S = C<br>Schn | nitt 1          | 53<br>40<br>39<br>CMOS compatib | 53     J10       40     K6       39     L6       CMOS compatible input or contribut Trigger input with CMOS | 53J10B2940K6A2739L6B22CMOS compatible input or output<br>nitt Trigger input with CMOS levels | 53J10B29I/O40K6A27I/O39L6B22I/OCMOS compatible input or output<br>nitt Trigger input with CMOS levelsA | 53     J10     B29     I/O     ST       40     K6     A27     I/O     ST       39     L6     B22     I/O     ST       CMOS compatible input or output nitt Trigger input with CMOS levels     Analog = A     O = Output |  |

TABLE 1-1: PINOUT I/O DESCRIPTIONS (CONTINUED)

Note 1: Pin numbers are only provided for reference. See the "Device Pin Tables" section for device pin availability.

2: See 25.0 "Ethernet Controller" for more information.

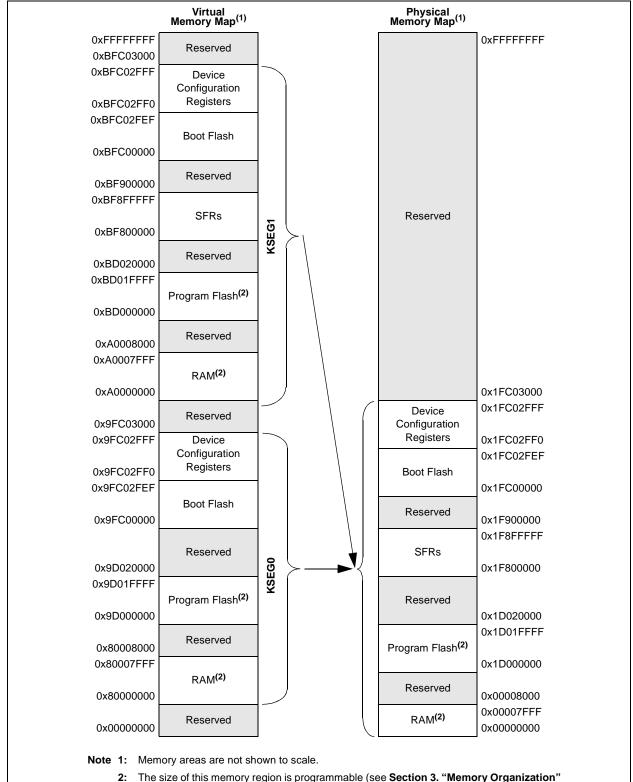

## FIGURE 4-3: MEMORY MAP ON RESET FOR PIC32MX564F128H, PIC32MX564F128L, PIC32MX664F128H, PIC32MX664F128L, PIC32MX764F128H AND PIC32MX764F128L DEVICES

(DS60001115)) and can be changed by initialization code provided by end user development tools (refer to the specific development tool documentation for information).

NOTES:

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1   | Bit<br>24/16/8/0   |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|--------------------|--------------------|

| 31:24        | U-0                | U-0                |

| 31.24        |                   | _                 | -                 | —                 | _                 | —                 |                    | —                  |

| 23:16        | U-0                | U-0                |

| 23.10        | _                 | _                 | _                 | —                 | _                 | —                 |                    | —                  |

| 45.0         | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | R/W-0, HS          | R/W-0              |

| 15:8         | —                 | _                 | —                 | —                 | _                 | —                 | CMR                | VREGS              |

|              | R/W-0, HS         | R/W-0, HS         | U-0               | R/W-0, HS         | R/W-0, HS         | R/W-0, HS         | R/W-1, HS          | R/W-1, HS          |

| 7:0          | EXTR              | SWR               | _                 | WDTO              | SLEEP             | IDLE              | BOR <sup>(1)</sup> | POR <sup>(1)</sup> |

### REGISTER 6-1: RCON: RESET CONTROL REGISTER

| Legend:           | HS = Set by hardware |                                    |                    |  |

|-------------------|----------------------|------------------------------------|--------------------|--|

| R = Readable bit  | W = Writable bit     | U = Unimplemented bit, read as '0' |                    |  |

| -n = Value at POR | '1' = Bit is set     | '0' = Bit is cleared               | x = Bit is unknown |  |

| bit 31-10 | Unimplemented: Read as '0 | n' |

|-----------|---------------------------|----|

|           | eninplemented. Read as    | 0  |

| bit 9 | CMR: Configuration Mismatch Reset Flag bit                                   |

|-------|------------------------------------------------------------------------------|

|       | 1 = Configuration mismatch Reset has occurred                                |

|       | 0 = Configuration mismatch Reset has not occurred                            |

| bit 8 | VREGS: Voltage Regulator Standby Enable bit                                  |

|       | $\ensuremath{\mathtt{l}}$ = Regulator is enabled and is on during Sleep mode |

|       | 0 = Regulator is set to Stand-by Tracking mode                               |

| bit 7 | EXTR: External Reset (MCLR) Pin Flag bit                                     |

|       | 1 = Master Clear (pin) Reset has occurred                                    |

|       | 0 = Master Clear (pin) Reset has not occurred                                |

| bit 6 | SWR: Software Reset Flag bit                                                 |

|       | 1 = Software Reset was executed                                              |

|       | 0 = Software Reset was not executed                                          |

| bit 5 | Unimplemented: Read as '0'                                                   |

| bit 4 | WDTO: Watchdog Timer Time-out Flag bit                                       |

|       | 1 = WDT Time-out has occurred                                                |

|       | 0 = WDT Time-out has not occurred                                            |

| bit 3 | SLEEP: Wake From Sleep Flag bit                                              |

|       | 1 = Device was in Sleep mode                                                 |

|       | 0 = Device was not in Sleep mode                                             |

| bit 2 | IDLE: Wake From Idle Flag bit                                                |

|       | 1 = Device was in Idle mode                                                  |

|       | 0 = Device was not in Idle mode                                              |

| bit 1 | BOR: Brown-out Reset Flag bit <sup>(1)</sup>                                 |

|       | 1 = Brown-out Reset has occurred                                             |

|       | 0 = Brown-out Reset has not occurred                                         |

| bit 0 | <b>POR:</b> Power-on Reset Flag bit <sup>(1)</sup>                           |

|       | 1 = Power-on Reset has occurred                                              |

|       | 0 = Power-on Reset has not occurred                                          |

|       |                                                                              |

Note 1: User software must clear this bit to view the next detection.

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|

| 04.04        | U-0               | U-0               | R/W-y             | R/W-y             | R/W-y             | R/W-0             | R/W-0            | R/W-1            |

| 31:24        | —                 | —                 | Р                 | LLODIV<2:0:       | >                 | FRCDIV<2:0>       |                  |                  |

| 00.40        | U-0               | R-0               | R-1               | R/W-y             | R/W-y             | R/W-y             | R/W-y            | R/W-y            |

| 23:16        | —                 | SOSCRDY           | PBDIVRDY          | PBDIV             | /<1:0>            | PLLMULT<2:0>      |                  |                  |

| 45.0         | U-0               | R-0               | R-0               | R-0               | U-0               | R/W-y             | R/W-y            | R/W-y            |

| 15:8         | —                 | COSC<2:0>         |                   |                   | —                 | NOSC<2:0>         |                  |                  |

| 7.0          | R/W-0             | R-0               | R-0               | R/W-0             | R/W-0             | R/W-0             | R/W-y            | R/W-0            |

| 7:0          | CLKLOCK           | ULOCK             | SLOCK             | SLPEN             | CF                | UFRCEN            | SOSCEN           | OSWEN            |

### REGISTER 8-1: OSCCON: OSCILLATOR CONTROL REGISTER

Legend:

y = Value set from Configuration bits on POR

- R = Readable bit -n = Value at POR

- W = Writable bit U = Unimplemented bit, read as '0'

- '1' = Bit is set

- 0' = Bit is cleared x = Bit is unknown

bit 31-30 Unimplemented: Read as '0'

bit 29-27 PLLODIV<2:0>: Output Divider for PLL

- 111 = PLL output divided by 256

- 110 = PLL output divided by 64

- 101 = PLL output divided by 32

- 100 = PLL output divided by 16

- 011 = PLL output divided by 8

- 010 = PLL output divided by 4

- 001 = PLL output divided by 2

- 000 = PLL output divided by 1

### bit 26-24 FRCDIV<2:0>: Internal Fast RC (FRC) Oscillator Clock Divider bits

- 111 = FRC divided by 256

- 110 = FRC divided by 64

- 101 = FRC divided by 32

- 100 = FRC divided by 16

- 011 = FRC divided by 8

- 010 = FRC divided by 4

- 001 = FRC divided by 2 (default setting)

- 000 = FRC divided by 1

- bit 23 Unimplemented: Read as '0'

- bit 22 SOSCRDY: Secondary Oscillator (Sosc) Ready Indicator bit

- 1 = Indicates that the Secondary Oscillator is running and is stable

- 0 = Secondary Oscillator is still warming up or is turned off

- bit 21 PBDIVRDY: Peripheral Bus Clock (PBCLK) Divisor Ready bit

- 1 = PBDIV<1:0> bits can be written

- 0 = PBDIV<1:0> bits cannot be written

- bit 20-19 **PBDIV<1:0>:** Peripheral Bus Clock (PBCLK) Divisor bits

- 11 = PBCLK is SYSCLK divided by 8 (default)

- 10 = PBCLK is SYSCLK divided by 4

- 01 = PBCLK is SYSCLK divided by 2

- 00 = PBCLK is SYSCLK divided by 1

**Note:** Writes to this register require an unlock sequence. Refer to **Section 6. "Oscillator"** (DS60001112) in the *"PIC32 Family Reference Manual"* for details.

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |  |  |  |  |  |  |  |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|--|--|--|--|--|--|--|--|

| 24.24        | R/W-x             | R/W-x             | R/W-x             | R/W-x             | R/W-x             | R/W-x             | R/W-x            | R/W-x            |  |  |  |  |  |  |  |  |

| 31:24        |                   | CHEW1<31:24>      |                   |                   |                   |                   |                  |                  |  |  |  |  |  |  |  |  |

| 00.40        | R/W-x             | R/W-x             | R/W-x             | R/W-x             | R/W-x             | R/W-x             | R/W-x            | R/W-x            |  |  |  |  |  |  |  |  |

| 23:16        | CHEW1<23:16>      |                   |                   |                   |                   |                   |                  |                  |  |  |  |  |  |  |  |  |

| 45.0         | R/W-x             | R/W-x             | R/W-x             | R/W-x             | R/W-x             | R/W-x             | R/W-x            | R/W-x            |  |  |  |  |  |  |  |  |

| 15:8         | CHEW1<15:8>       |                   |                   |                   |                   |                   |                  |                  |  |  |  |  |  |  |  |  |

| 7:0          | R/W-x             | R/W-x             | R/W-x             | R/W-x             | R/W-x             | R/W-x             | R/W-x            | R/W-x            |  |  |  |  |  |  |  |  |

|              |                   | •                 | •                 | CHEW1             | <7:0>             |                   |                  | CHEW1<7:0>       |  |  |  |  |  |  |  |  |

### REGISTER 9-6: CHEW1: CACHE WORD 1

| Legend:           |                                                                      |                      |                    |  |  |

|-------------------|----------------------------------------------------------------------|----------------------|--------------------|--|--|

| R = Readable bit  | R = Readable bit W = Writable bit U = Unimplemented bit, read as '0' |                      |                    |  |  |

| -n = Value at POR | '1' = Bit is set                                                     | '0' = Bit is cleared | x = Bit is unknown |  |  |

bit 31-0 **CHEW1<31:0>:** Word 1 of the cache line selected by CHEIDX<3:0> bits (CHEACC<3:0>) Readable only if the device is not code-protected.

### REGISTER 9-7: CHEW2: CACHE WORD 2

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |  |  |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|--|--|--|

| 04.04        | R/W-x             | R/W-x             | R/W-x             | R/W-x             | R/W-x             | R/W-x             | R/W-x            | R/W-x            |  |  |  |

| 31:24        |                   | CHEW2<31:24>      |                   |                   |                   |                   |                  |                  |  |  |  |

| 00.40        | R/W-x             | R/W-x             | R/W-x             | R/W-x             | R/W-x             | R/W-x             | R/W-x            | R/W-x            |  |  |  |

| 23:16        | CHEW2<23:16>      |                   |                   |                   |                   |                   |                  |                  |  |  |  |

| 45.0         | R/W-x             | R/W-x             | R/W-x             | R/W-x             | R/W-x             | R/W-x             | R/W-x            | R/W-x            |  |  |  |

| 15:8         | CHEW2<15:8>       |                   |                   |                   |                   |                   |                  |                  |  |  |  |

|              | R/W-x             | R/W-x             | R/W-x             | R/W-x             | R/W-x             | R/W-x             | R/W-x            | R/W-x            |  |  |  |

| 7:0          |                   |                   |                   | CHEW2             | <7:0>             |                   |                  |                  |  |  |  |

| Legend:           |                  |                                    |                    |  |

|-------------------|------------------|------------------------------------|--------------------|--|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read as '0' |                    |  |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared               | x = Bit is unknown |  |

bit 31-0 **CHEW2<31:0>:** Word 2 of the cache line selected by CHEIDX<3:0> bits (CHEACC<3:0>) Readable only if the device is not code-protected.

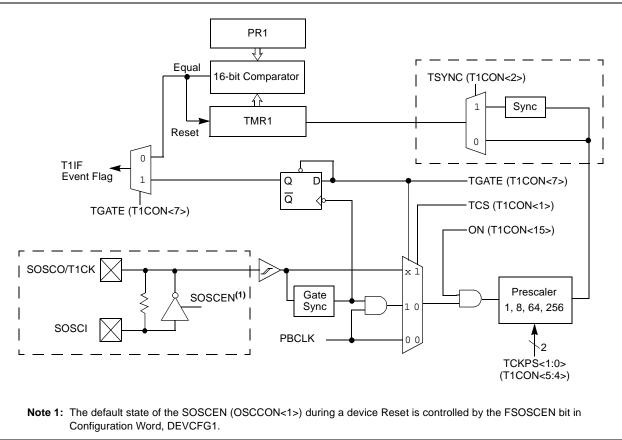

### 13.0 TIMER1

Note: This data sheet summarizes the features of the PIC32MX5XX/6XX/7XX family of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to **Section 14. "Timers"** (DS60001105) in the *"PIC32 Family Reference Manual"*, which is available from the Microchip web site (www.microchip.com/PIC32).

This family of PIC32 devices features one synchronous/ asynchronous 16-bit timer that can operate as a free-running interval timer for various timing applications and counting external events. This timer can also be used with the low-power Secondary Oscillator (Sosc) for Real-Time Clock (RTC) applications. The following modes are supported:

- Synchronous Internal Timer

- Synchronous Internal Gated Timer

- Synchronous External Timer

- Asynchronous External Timer

### FIGURE 13-1: TIMER1 BLOCK DIAGRAM

### 13.1 Additional Supported Features

- Selectable clock prescaler

- Timer operation during Idle and Sleep mode

- Fast bit manipulation using CLR, SET and INV registers

- Asynchronous mode can be used with the Sosc to function as a Real-Time Clock (RTC)

A simplified block diagram of the Timer1 module is illustrated in Figure 13-1.

### REGISTER 13-1: T1CON: TYPE A TIMER CONTROL REGISTER (CONTINUED)

- bit 3 Unimplemented: Read as '0'

bit 2 TSYNC: Timer External Clock Input Synchronization Selection bit When TCS = 1: 1 = External clock input is synchronized 0 = External clock input is not synchronized When TCS = 0: This bit is ignored.

bit 1 TCS: Timer Clock Source Select bit 1 = External clock from TxCKI pin 0 = Internal peripheral clock

- bit 0 Unimplemented: Read as '0'

- **Note 1:** When using the 1:1 PBCLK divisor, the user's software should not read/write the peripheral SFRs in the SYSCLK cycle immediately following the instruction that clears the module's ON bit.

NOTES:

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4     | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

|--------------|-------------------|-------------------|-------------------|-----------------------|-------------------|-------------------|------------------|------------------|

| 31:24        | R/W-0             | R/W-0             | R/W-0             | R/W-0                 | R/W-0             | U-0               | U-0              | U-0              |

| 31.24        | IVRIE             | WAKIE             | CERRIE            | SERRIE                | RBOVIE            | —                 | —                | —                |

| 23:16        | U-0               | U-0               | U-0               | U-0                   | R/W-0             | R/W-0             | R/W-0            | R/W-0            |

| 23.10        | _                 | —                 | _                 | _                     | MODIE             | CTMRIE            | RBIE             | TBIE             |

| 15.0         | R/W-0             | R/W-0             | R/W-0             | R/W-0                 | R/W-0             | U-0               | U-0              | U-0              |

| 15:8         | IVRIF             | WAKIF             | CERRIF            | SERRIF <sup>(1)</sup> | RBOVIF            | —                 | —                | —                |

| 7.0          | U-0               | U-0               | U-0               | U-0                   | R/W-0             | R/W-0             | R/W-0            | R/W-0            |

| 7:0          |                   |                   |                   |                       | MODIF             | CTMRIF            | RBIF             | TBIF             |

### REGISTER 24-3: CIINT: CAN INTERRUPT REGISTER

### Legend:

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, r | ead as '0'         |

|-------------------|------------------|--------------------------|--------------------|

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared     | x = Bit is unknown |

| bit 31    | IVRIE: Invalid Message Received Interrupt Enable bit<br>1 = Interrupt request is enabled<br>0 = Interrupt request is not enabled                                 |

|-----------|------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| bit 30    | WAKIE: CAN Bus Activity Wake-up Interrupt Enable bit<br>1 = Interrupt request is enabled<br>0 = Interrupt request is not enabled                                 |

| bit 29    | <b>CERRIE:</b> CAN Bus Error Interrupt Enable bit<br>1 = Interrupt request is enabled<br>0 = Interrupt request is not enabled                                    |

| bit 28    | SERRIE: System Error Interrupt Enable bit<br>1 = Interrupt request is enabled<br>0 = Interrupt request is not enabled                                            |

| bit 27    | <b>RBOVIE:</b> Receive Buffer Overflow Interrupt Enable bit<br>1 = Interrupt request is enabled<br>0 = Interrupt request is not enabled                          |

| bit 26-20 | Unimplemented: Read as '0'                                                                                                                                       |

| bit 19    | <b>MODIE:</b> Mode Change Interrupt Enable bit<br>1 = Interrupt request is enabled<br>0 = Interrupt request is not enabled                                       |

| bit 18    | <b>CTMRIE:</b> CAN Timestamp Timer Interrupt Enable bit<br>1 = Interrupt request is enabled<br>0 = Interrupt request is not enabled                              |

| bit 17    | <b>RBIE:</b> Receive Buffer Interrupt Enable bit<br>1 = Interrupt request is enabled<br>0 = Interrupt request is not enabled                                     |

| bit 16    | <b>TBIE:</b> Transmit Buffer Interrupt Enable bit<br>1 = Interrupt request is enabled<br>0 = Interrupt request is not enabled                                    |

| bit 15    | <b>IVRIF:</b> Invalid Message Received Interrupt Flag bit<br>1 = An invalid messages interrupt has occurred<br>0 = An invalid message interrupt has not occurred |

| Note 1:   | This bit can only be cleared by turning the CAN module Off and On by                                                                                             |

**Note 1:** This bit can only be cleared by turning the CAN module Off and On by clearing or setting the ON bit (CiCON<15>).

Table 25-1, Table 25-2, Table 25-3 and Table 25-4 show four interfaces and the associated pins that can be used with the Ethernet Controller.

# TABLE 25-1:MII MODE DEFAULT<br/>INTERFACE SIGNALS<br/>(FMIIEN = 1, FETHIO = 1)

| Pin Name | Description          |  |  |

|----------|----------------------|--|--|

| EMDC     | Management Clock     |  |  |

| EMDIO    | Management I/O       |  |  |

| ETXCLK   | Transmit Clock       |  |  |

| ETXEN    | Transmit Enable      |  |  |

| ETXD0    | Transmit Data        |  |  |

| ETXD1    | Transmit Data        |  |  |

| ETXD2    | Transmit Data        |  |  |

| ETXD3    | Transmit Data        |  |  |

| ETXERR   | Transmit Error       |  |  |

| ERXCLK   | Receive Clock        |  |  |

| ERXDV    | Receive Data Valid   |  |  |

| ERXD0    | Receive Data         |  |  |

| ERXD1    | Receive Data         |  |  |

| ERXD2    | Receive Data         |  |  |

| ERXD3    | Receive Data         |  |  |

| ERXERR   | Receive Error        |  |  |

| ECRS     | Carrier Sense        |  |  |

| ECOL     | Collision Indication |  |  |

# TABLE 25-2:RMII MODE DEFAULT<br/>INTERFACE SIGNALS<br/>(FMIIEN = 0, FETHIO = 1)

| Pin Name | Description                        |  |  |

|----------|------------------------------------|--|--|

| EMDC     | Management Clock                   |  |  |

| EMDIO    | Management I/O                     |  |  |

| ETXEN    | Transmit Enable                    |  |  |

| ETXD0    | Transmit Data                      |  |  |

| ETXD1    | Transmit Data                      |  |  |

| EREFCLK  | Reference Clock                    |  |  |

| ECRSDV   | Carrier Sense – Receive Data Valid |  |  |

| ERXD0    | Receive Data                       |  |  |

| ERXD1    | Receive Data                       |  |  |

| ERXERR   | Receive Error                      |  |  |

**Note:** Ethernet controller pins that are not used by selected interface can be used by other peripherals.

# TABLE 25-3:MII MODE ALTERNATE<br/>INTERFACE SIGNALS<br/>(FMIIEN = 1, FETHIO = 0)

| Pin Name                                      | Description                     |  |  |  |

|-----------------------------------------------|---------------------------------|--|--|--|

| AEMDC                                         | Management Clock                |  |  |  |

| AEMDIO                                        | Management I/O                  |  |  |  |

| AETXCLK                                       | Transmit Clock                  |  |  |  |

| AETXEN                                        | Transmit Enable                 |  |  |  |

| AETXD0                                        | Transmit Data                   |  |  |  |

| AETXD1                                        | Transmit Data                   |  |  |  |

| AETXD2                                        | Transmit Data                   |  |  |  |

| AETXD3                                        | Transmit Data                   |  |  |  |

| AETXERR                                       | Transmit Error<br>Receive Clock |  |  |  |

| AERXCLK                                       |                                 |  |  |  |

| AERXDV                                        | Receive Data Valid              |  |  |  |

| AERXD0                                        | Receive Data                    |  |  |  |

| AERXD1                                        | Receive Data                    |  |  |  |

| AERXD2                                        | Receive Data                    |  |  |  |

| AERXD3                                        | Receive Data                    |  |  |  |

| AERXERR                                       | Receive Error                   |  |  |  |

| AECRS                                         | Carrier Sense                   |  |  |  |

| AECOL Collision Indication                    |                                 |  |  |  |

| Note: The MII mode Alternate Interface is not |                                 |  |  |  |

**Note:** The MII mode Alternate Interface is not available on 64-pin devices.

# TABLE 25-4:RMII MODE ALTERNATE<br/>INTERFACE SIGNALS<br/>(FMIIEN = 0, FETHIO = 0)

| Pin Name | Description                        |

|----------|------------------------------------|

| AEMDC    | Management Clock                   |

| AEMDIO   | Management I/O                     |

| AETXEN   | Transmit Enable                    |

| AETXD0   | Transmit Data                      |

| AETXD1   | Transmit Data                      |

| AEREFCLK | Reference Clock                    |

| AECRSDV  | Carrier Sense – Receive Data Valid |

| AERXD0   | Receive Data                       |

| AERXD1   | Receive Data                       |

| AERXERR  | Receive Error                      |

### REGISTER 25-36: EMAC1MIND: ETHERNET CONTROLLER MAC MII MANAGEMENT INDICATORS REGISTER

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|

| 31:24        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 31.24        | _                 |                   | —                 | _                 | —                 | —                 | -                | —                |

| 22.16        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 23:16        | —                 | —                 | —                 | _                 | _                 | —                 | —                | —                |

| 45.0         | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 15:8         | —                 | —                 | —                 | _                 | _                 | —                 | —                | —                |

| 7.0          | U-0               | U-0               | U-0               | U-0               | R/W-0             | R/W-0             | R/W-0            | R/W-0            |

| 7:0          | _                 | _                 | —                 |                   | LINKFAIL          | NOTVALID          | SCAN             | MIIMBUSY         |

### Legend:

| 5                 |                  |                          |                    |   |

|-------------------|------------------|--------------------------|--------------------|---|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, r | read as '0'        |   |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared     | x = Bit is unknown | 1 |

### bit 31-4 Unimplemented: Read as '0'

bit 3 LINKFAIL: Link Fail bit

When '1' is returned - indicates link fail has occurred. This bit reflects the value last read from the PHY status register.

bit 2 NOTVALID: MII Management Read Data Not Valid bit When '1' is returned - indicates an MII management read cycle has not completed and the Read Data is not yet valid.

### bit 1 SCAN: MII Management Scanning bit When '1' is returned - indicates a scan operation (continuous MII Management Read cycles) is in progress.

### bit 0 MIIMBUSY: MII Management Busy bit

When '1' is returned - indicates MII Management module is currently performing an MII Management Read or Write cycle.

**Note:** Both 16-bit and 32-bit accesses are allowed to these registers (including the SET, CLR and INV registers). 8-bit accesses are not allowed and are ignored by the hardware.

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5   | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

|--------------|-------------------|-------------------|---------------------|-------------------|-------------------|-------------------|------------------|------------------|

| 31:24        | U-0               | U-0               | U-0                 | U-0               | U-0               | U-0               | U-0              | U-0              |

| 31.24        |                   | —                 |                     | _                 | _                 | _                 | _                | _                |

| 23:16        | U-0               | U-0               | U-0                 | U-0               | U-0               | U-0               | U-0              | U-0              |

| 23.10        | —                 | —                 | —                   | -                 | —                 | —                 | —                | —                |

| 15.0         | R/W-0             | R/W-0             | R/W-0               | U-0               | U-0               | U-0               | U-0              | R-0              |

| 15:8         | 0N <sup>(1)</sup> | COE               | CPOL <sup>(2)</sup> | -                 | —                 | —                 | —                | COUT             |

| 7:0          | R/W-1             | R/W-1             | U-0                 | R/W-0             | U-0               | U-0               | R/W-1            | R/W-1            |

| 7.0          | EVPOL             | _<1:0>            |                     | CREF              | _                 |                   | CCH              | <1:0>            |

### REGISTER 26-1: CMxCON: COMPARATOR 'x' CONTROL REGISTER

### Legend:

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, re | ead as '0'         |

|-------------------|------------------|---------------------------|--------------------|

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared      | x = Bit is unknown |

### bit 31-16 Unimplemented: Read as '0'

bit 15 ON: Comparator ON bit<sup>(1)</sup>

Clearing this bit does not affect the other bits in this register.

- 1 = Module is enabled. Setting this bit does not affect the other bits in this register

- 0 = Module is disabled and does not consume current.

- bit 14 COE: Comparator Output Enable bit

- 1 = Comparator output is driven on the output CxOUT pin

- 0 = Comparator output is not driven on the output CxOUT pin

- bit 13 **CPOL:** Comparator Output Inversion bit<sup>(2)</sup>

- 1 = Output is inverted

- 0 = Output is not inverted

### bit 12-9 Unimplemented: Read as '0'

- bit 8 COUT: Comparator Output bit

- 1 =Output of the Comparator is a '1'

- 0 = Output of the Comparator is a '0'

- bit 7-6 EVPOL<1:0>: Interrupt Event Polarity Select bits

- 11 = Comparator interrupt is generated on a low-to-high or high-to-low transition of the comparator output

- 10 = Comparator interrupt is generated on a high-to-low transition of the comparator output

- 01 = Comparator interrupt is generated on a low-to-high transition of the comparator output

- 00 = Comparator interrupt generation is disabled

### bit 5 Unimplemented: Read as '0'

- bit 4 **CREF:** Comparator Positive Input Configure bit

- 1 = Comparator non-inverting input is connected to the internal CVREF

- 0 = Comparator non-inverting input is connected to the CxIN+ pin

- bit 3-2 Unimplemented: Read as '0'

- bit 1-0 **CCH<1:0>:** Comparator Negative Input Select bits for Comparator

- 11 = Comparator inverting input is connected to the IVREF

- 10 = Comparator inverting input is connected to the C2IN+ pin for C1 and C1IN+ pin for C2

- 01 = Comparator inverting input is connected to the C1IN+ pin for C1 and C2IN+ pin for C2

- 00 = Comparator inverting input is connected to the C1IN- pin for C1 and C2IN- pin for C2

- **Note 1:** When using the 1:1 PBCLK divisor, the user's software should not read/write the peripheral's SFRs in the SYSCLK cycle immediately following the instruction that clears the module's ON bit.

- 2: Setting this bit will invert the signal to the comparator interrupt generator as well. This will result in an interrupt being generated on the opposite edge from the one selected by EVPOL<1:0>.

### REGISTER 29-2: DEVCFG1: DEVICE CONFIGURATION WORD 1 (CONTINUED)

- bit 13-12 **FPBDIV<1:0>:** Peripheral Bus Clock Divisor Default Value bits

- 11 = PBCLK is SYSCLK divided by 8

- 10 = PBCLK is SYSCLK divided by 4

- 01 = PBCLK is SYSCLK divided by 2

- 00 = PBCLK is SYSCLK divided by 1

- bit 11 Reserved: Write '1'

- bit 10 OSCIOFNC: CLKO Enable Configuration bit

- 1 = CLKO output is disabled

- 0 = CLKO output signal is active on the OSCO pin; the Primary Oscillator must be disabled or configured for External Clock mode (EC) for the CLKO to be active (POSCMOD<1:0> = 11 or 00)

- bit 9-8 **POSCMOD<1:0>:** Primary Oscillator Configuration bits

- 11 = Primary Oscillator is disabled

- 10 = HS Oscillator mode is selected

- 01 = XT Oscillator mode is selected

- 00 = External Clock mode is selected

- bit 7 IESO: Internal External Switchover bit

- 1 = Internal External Switchover mode is enabled (Two-Speed Start-up is enabled)

- 0 = Internal External Switchover mode is disabled (Two-Speed Start-up is disabled)

- bit 6 Reserved: Write '1'

- bit 5 FSOSCEN: Secondary Oscillator Enable bit

- 1 = Enable the Secondary Oscillator

- 0 = Disable the Secondary Oscillator

- bit 4-3 Reserved: Write '1'

- bit 2-0 **FNOSC<2:0>:** Oscillator Selection bits

- 111 = Fast RC Oscillator with divide-by-N (FRCDIV)

- 110 = FRCDIV16 Fast RC Oscillator with fixed divide-by-16 postscaler

- 101 = Low-Power RC Oscillator (LPRC)

- 100 = Secondary Oscillator (Sosc)

- 011 = Primary Oscillator (Posc) with PLL module (XT+PLL, HS+PLL, EC+PLL)

- 010 = Primary Oscillator (XT, HS, EC)<sup>(1)</sup>

- 001 = Fast RC Oscillator with divide-by-N with PLL module (FRCDIV+PLL)

- 000 = Fast RC Oscillator (FRC)

- **Note 1:** Do not disable the POSC (POSCMOD = 11) when using this oscillator source.

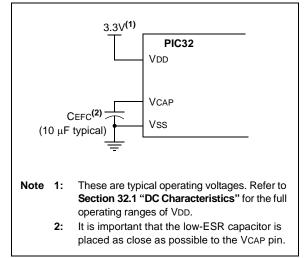

### 29.2 On-Chip Voltage Regulator

All PIC32MX5XX/6XX/7XX devices' core and digital logic are designed to operate at a nominal 1.8V. To simplify system designs, most devices in the PIC32MX-5XX/6XX/7XX family incorporate an on-chip regulator providing the required core logic voltage from VDD.

A low-ESR capacitor (such as tantalum) must be connected to the VCAP pin (see Figure 29-1). This helps to maintain the stability of the regulator. The recommended value for the filter capacitor is provided in **Section 32.1 "DC Characteristics"**.

Note: It is important that the low-ESR capacitor is placed as close as possible to the VCAP pin.

### 29.2.1 ON-CHIP REGULATOR AND POR

It takes a fixed delay for the on-chip regulator to generate an output. During this time, designated as TPU, code execution is disabled. TPU is applied every time the device resumes operation after any power-down, including Sleep mode.

### 29.2.2 ON-CHIP REGULATOR AND BOR

PIC32MX5XX/6XX/7XX devices also have a simple brown-out capability. If the voltage supplied to the regulator is inadequate to maintain a regulated level, the regulator Reset circuitry will generate a Brown-out Reset (BOR). This event is captured by the BOR flag bit (RCON<1>). The brown-out voltage levels are specified in **Section 32.1 "DC Characteristics"**.

### FIGURE 29-1: CONNECTIONS FOR THE ON-CHIP REGULATOR

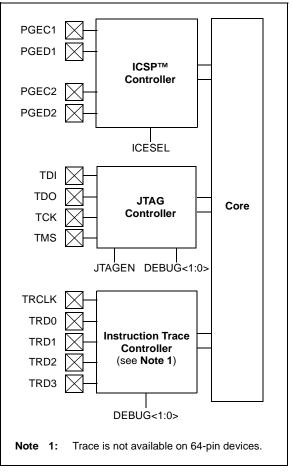

### 29.3 **Programming and Diagnostics**

PIC32MX5XX/6XX/7XX devices provide a complete range of programming and diagnostic features that can increase the flexibility of any application using them. These features allow system designers to include:

- Simplified field programmability using two-wire In-Circuit Serial Programming<sup>™</sup> (ICSP<sup>™</sup>) interfaces

- Debugging using ICSP

- Programming and debugging capabilities using the EJTAG extension of JTAG

- JTAG boundary scan testing for device and board diagnostics

PIC32 devices incorporate two programming and diagnostic modules, and a trace controller, that provide a range of functions to the application developer.

FIGURE 29-2:

PROGRAMMING, DEBUGGING, AND TRACE PORTS BLOCK DIAGRAM

### TABLE 32-35: ETHERNET MODULE SPECIFICATIONS

| АС СНА        | RACTERISTICS                        | $\begin{tabular}{ l l l l l l l l l l l l l l l l l l l$ |         |      |       |                  |

|---------------|-------------------------------------|----------------------------------------------------------|---------|------|-------|------------------|

| Param.<br>No. | Characteristic                      | Min.                                                     | Typical | Max. | Units | Conditions       |

| MIIM Tin      | ning Requirements                   |                                                          |         |      |       |                  |

| ET1           | MDC Duty Cycle                      | 40                                                       |         | 60   | %     | —                |

| ET2           | MDC Period                          | 400                                                      | —       | —    | ns    | —                |

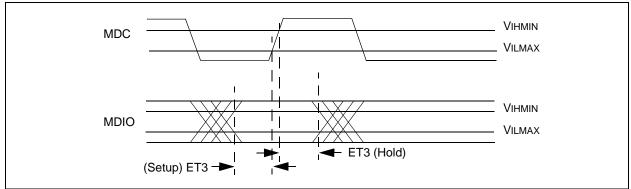

| ET3           | MDIO Output Setup and Hold          | 10                                                       | —       | 10   | ns    | See Figure 32-19 |

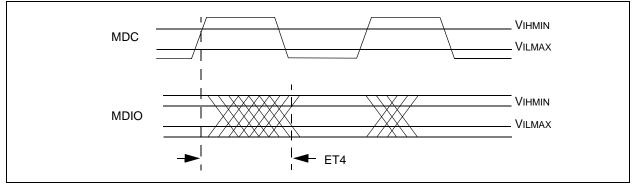

| ET4           | MDIO Input Setup and Hold           | 0                                                        | —       | 300  | ns    | See Figure 32-20 |

| MII Timi      | ng Requirements                     |                                                          |         |      |       |                  |

| ET5           | TX Clock Frequency                  | —                                                        | 25      | _    | MHz   | —                |

| ET6           | TX Clock Duty Cycle                 | 35                                                       | —       | 65   | %     | —                |

| ET7           | ETXDx, ETEN, ETXERR Output Delay    | 0                                                        | —       | 25   | ns    | See Figure 32-21 |

| ET8           | RX Clock Frequency                  | —                                                        | 25      | _    | MHz   | —                |

| ET9           | RX Clock Duty Cycle                 | 35                                                       | —       | 65   | %     | —                |

| ET10          | ERXDx, ERXDV, ERXERR Setup and Hold | 10                                                       | —       | 30   | ns    | See Figure 32-22 |

| RMII Tin      | ning Requirements                   |                                                          |         |      |       |                  |

| ET11          | Reference Clock Frequency           |                                                          | 50      | —    | MHz   | —                |

| ET12          | Reference Clock Duty Cycle          | 35                                                       |         | 65   | %     | —                |

| ET13          | ETXDx, ETEN, Setup and Hold         | 2                                                        | —       | 4    | ns    | —                |

| ET14          | ERXDx, ERXDV, ERXERR Setup and Hold | 2                                                        | —       | 4    | ns    | —                |

**Note 1:** The Ethernet module is functional at VBORMIN < VDD < 2.9V, but with degraded performance. Unless otherwise stated, module functionality is tested, but not characterized.

### FIGURE 32-19: MDIO SOURCED BY THE PIC32 DEVICE

### FIGURE 32-20: MDIO SOURCED BY THE PHY

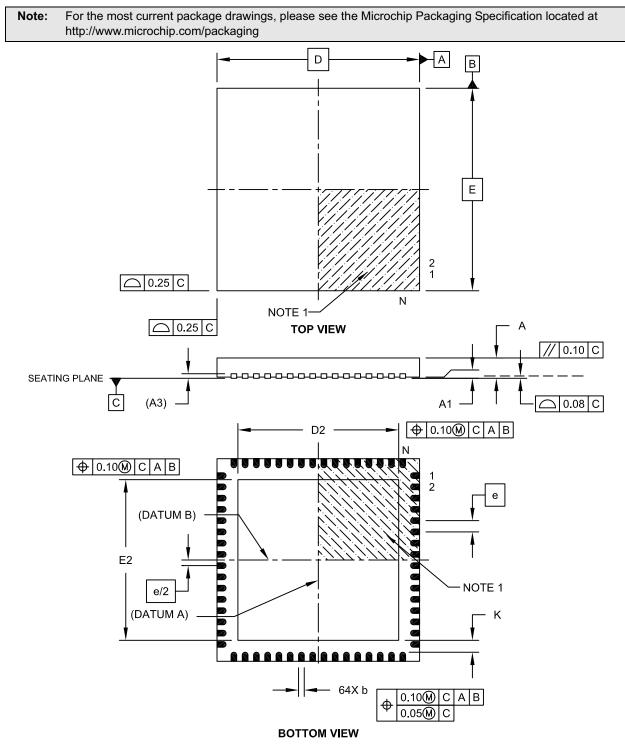

### 64-Lead Plastic Quad Flat, No Lead Package (MR) – 9x9x0.9 mm Body [QFN] With 7.15 x 7.15 Exposed Pad [QFN]

Microchip Technology Drawing C04-149C Sheet 1 of 2

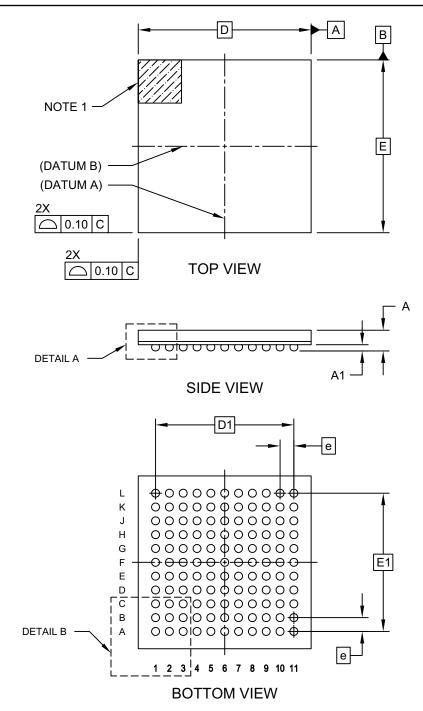

## 121-Ball Plastic Thin Profile Fine Pitch Ball Grid Array (BG) - 10x10x1.10 mm Body [TFBGA]

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

Microchip Technology Drawing C04-148 Rev F Sheet 1 of 2

| TABLE B-3: | MAJOR SECTION UPDATES | (CONTINUED) |  |

|------------|-----------------------|-------------|--|

|            |                       |             |  |

| Section Name                     | Update Description                                                                                    |  |

|----------------------------------|-------------------------------------------------------------------------------------------------------|--|

| 1.0 "Electrical Characteristics" | Updated the Typical and Maximum DC Characteristics: Operating Current (IDD) in Table 1-5.             |  |

|                                  | Updated the Typical and Maximum DC Characteristics: Idle Current (IIDLE) in Table 1-6.                |  |

|                                  | Updated the Typical and Maximum DC Characteristics: Power-Down Current (IPD) in Table 1-7.            |  |

|                                  | Added DC Characteristics: Program Memory parameters D130a and D132a in Table 1-11.                    |  |

|                                  | Added the Internal Voltage Reference parameter (D305) to the Comparator Specifications in Table 1-13. |  |