Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

ĿXFl

| Product Status             | Active                                                                            |

|----------------------------|-----------------------------------------------------------------------------------|

| Core Processor             | MIPS32® M4K™                                                                      |

| Core Size                  | 32-Bit Single-Core                                                                |

| Speed                      | 80MHz                                                                             |

| Connectivity               | Ethernet, I <sup>2</sup> C, SPI, UART/USART, USB OTG                              |

| Peripherals                | Brown-out Detect/Reset, DMA, POR, PWM, WDT                                        |

| Number of I/O              | 53                                                                                |

| Program Memory Size        | 512KB (512K x 8)                                                                  |

| Program Memory Type        | FLASH                                                                             |

| EEPROM Size                | -                                                                                 |

| RAM Size                   | 128K x 8                                                                          |

| Voltage - Supply (Vcc/Vdd) | 2.3V ~ 3.6V                                                                       |

| Data Converters            | A/D 16x10b                                                                        |

| Oscillator Type            | Internal                                                                          |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                                 |

| Mounting Type              | Surface Mount                                                                     |

| Package / Case             | 64-VFQFN Exposed Pad                                                              |

| Supplier Device Package    | 64-VQFN (9x9)                                                                     |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic32mx695f512ht-80i-mr |

|                            |                                                                                   |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

|                  | USB, Ethernet, and CAN |                         |                  |     |          |        |                        |                                          |                       |                    |                                 |                              |             |         |      |       |                         |

|------------------|------------------------|-------------------------|------------------|-----|----------|--------|------------------------|------------------------------------------|-----------------------|--------------------|---------------------------------|------------------------------|-------------|---------|------|-------|-------------------------|

| Device           | Pins                   | Program Memory (KB)     | Data Memory (KB) | USB | Ethernet | CAN    | Timers/Capture/Compare | DMA Channels<br>(Programmable/Dedicated) | UART <sup>(2,3)</sup> | SPI <sup>(3)</sup> | I <sup>2</sup> C <sup>(3)</sup> | 10-bit 1 Msps ADC (Channels) | Comparators | dSd/dMd | JTAG | Trace | Packages <sup>(4)</sup> |

| PIC32MX764F128H  | 64                     | 128 + 12 <sup>(1)</sup> | 32               | 1   | 1        | 1      | 5/5/5                  | 4/8                                      | 6                     | 3                  | 4                               | 16                           | 2           | Yes     | Yes  | No    | PT,<br>MR               |

| PIC32MX775F256H  | 64                     | 256 + 12 <sup>(1)</sup> | 64               | 1   | 1        | 2      | 5/5/5                  | 8/8                                      | 6                     | 3                  | 4                               | 16                           | 2           | Yes     | Yes  | No    | PT,<br>MR               |

| PIC32MX775F512H  | 64                     | 512 + 12 <sup>(1)</sup> | 64               | 1   | 1        | 2      | 5/5/5                  | 8/8                                      | 6                     | 3                  | 4                               | 16                           | 2           | Yes     | Yes  | No    | PT,<br>MR               |

| PIC32MX795F512H  | 64                     | 512 + 12 <sup>(1)</sup> | 128              | 1   | 1        | 2      | 5/5/5                  | 8/8                                      | 6                     | 3                  | 4                               | 16                           | 2           | Yes     | Yes  | No    | PT,<br>MR               |

| PIC32MX764F128L  | 100                    | 128 + 12 <sup>(1)</sup> | 32               | 1   | 1        | 1      | 5/5/5                  | 4/6                                      | 6                     | 4                  | 5                               | 16                           | 2           | Yes     | Yes  | Yes   | PT, PF,<br>BG           |

| PIC32MX775F256L  | 100                    | 256 + 12 <sup>(1)</sup> | 64               | 1   | 1        | 2      | 5/5/5                  | 8/8                                      | 6                     | 4                  | 5                               | 16                           | 2           | Yes     | Yes  | Yes   | PT, PF,<br>BG           |

| PIC32MX775F512L  | 100                    | 512 + 12 <sup>(1)</sup> | 64               | 1   | 1        | 2      | 5/5/5                  | 8/8                                      | 6                     | 4                  | 5                               | 16                           | 2           | Yes     | Yes  | Yes   | PT, PF,<br>BG           |

| PIC32MX795F512L  | 100                    | 512 + 12 <sup>(1)</sup> | 128              | 1   | 1        | 2      | 5/5/5                  | 8/8                                      | 6                     | 4                  | 5                               | 16                           | 2           | Yes     | Yes  | Yes   | PT, PF,<br>BG, TL       |

| Legend: PF, PT = | TQFF                   | P MR = C                | QFN              |     | BG       | G = TF | BGA                    |                                          | TL = \                | /TLA               | 5)                              |                              |             |         |      |       |                         |

#### TABLE 3: PIC32MX7XX USB, ETHERNET, AND CAN FEATURES

Note 1: This device features 12 KB boot Flash memory.

2: CTS and RTS pins may not be available for all UART modules. Refer to the "Device Pin Tables" section for more information.

3: Some pins between the UART, SPI and I<sup>2</sup>C modules may be shared. Refer to the "Device Pin Tables" section for more information.

4: Refer to Section 34.0 "Packaging Information" for more information.

5: 100-pin devices other than those listed here are available in the VTLA package upon request. Please contact your local Microchip Sales Office for details.

|          |                    | Pin Nur         | nber <sup>(1)</sup> |                 | <b>D</b> '  | D ((           |                                                                                                                                                                                                |

|----------|--------------------|-----------------|---------------------|-----------------|-------------|----------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Pin Name | 64-Pin<br>QFN/TQFP | 100-Pin<br>TQFP | 121-Pin<br>TFBGA    | 124-pin<br>VTLA | Pin<br>Type | Buffer<br>Type | Description                                                                                                                                                                                    |

| AN0      | 16                 | 25              | K2                  | B14             | I           | Analog         | Analog input channels                                                                                                                                                                          |

| AN1      | 15                 | 24              | K1                  | A15             | I           | Analog         |                                                                                                                                                                                                |

| AN2      | 14                 | 23              | J2                  | B13             | I           | Analog         |                                                                                                                                                                                                |

| AN3      | 13                 | 22              | J1                  | A13             | I           | Analog         |                                                                                                                                                                                                |

| AN4      | 12                 | 21              | H2                  | B11             | I           | Analog         |                                                                                                                                                                                                |

| AN5      | 11                 | 20              | H1                  | A12             | I           | Analog         |                                                                                                                                                                                                |

| AN6      | 17                 | 26              | L1                  | A20             | I           | Analog         |                                                                                                                                                                                                |

| AN7      | 18                 | 27              | J3                  | B16             | I           | Analog         |                                                                                                                                                                                                |

| AN8      | 21                 | 32              | K4                  | A23             | I           | Analog         |                                                                                                                                                                                                |

| AN9      | 22                 | 33              | L4                  | B19             | I           | Analog         |                                                                                                                                                                                                |

| AN10     | 23                 | 34              | L5                  | A24             | I           | Analog         |                                                                                                                                                                                                |

| AN11     | 24                 | 35              | J5                  | B20             | I           | Analog         |                                                                                                                                                                                                |

| AN12     | 27                 | 41              | J7                  | B23             | I           | Analog         |                                                                                                                                                                                                |

| AN13     | 28                 | 42              | L7                  | A28             | I           | Analog         |                                                                                                                                                                                                |

| AN14     | 29                 | 43              | K7                  | B24             | I           | Analog         |                                                                                                                                                                                                |

| AN15     | 30                 | 44              | L8                  | A29             | I           | Analog         |                                                                                                                                                                                                |

| CLKI     | 39                 | 63              | F9                  | B34             | I           | ST/<br>CMOS    | External clock source input. Always associated with OSC1 pin function.                                                                                                                         |

| CLKO     | 40                 | 64              | F11                 | A42             | 0           | _              | Oscillator crystal output. Connects to<br>crystal or resonator in Crystal Oscillator<br>mode. Optionally functions as CLKO in<br>RC and EC modes. Always associated<br>with OSC2 pin function. |

| OSC1     | 39                 | 63              | F9                  | B34             | I           | ST/<br>CMOS    | Oscillator crystal input. ST buffer when configured in RC mode; CMOS otherwise.                                                                                                                |

| OSC2     | 40                 | 64              | F11                 | A42             | I/O         |                | Oscillator crystal output. Connects to<br>crystal or resonator in Crystal Oscillator<br>mode. Optionally functions as CLKO in<br>RC and EC modes.                                              |

| SOSCI    | 47                 | 73              | C10                 | A47             | I           | ST/<br>CMOS    | 32.768 kHz low-power oscillator crystal<br>input; CMOS otherwise                                                                                                                               |

| SOSCO    | 48                 | 74              | B11                 | B40             | 0           | _              | 32.768 kHz low-power oscillator crystal<br>output                                                                                                                                              |

# TABLE 1-1: PINOUT I/O DESCRIPTIONS

ST = Schmitt Trigger input with CMOS levels O = Output I = Input I = Input I = Input I = TTL = TTL input buffer

Note 1: Pin numbers are only provided for reference. See the "Device Pin Tables" section for device pin availability.

2: See 25.0 "Ethernet Controller" for more information.

# 2.9 Configuration of Analog and Digital Pins During ICSP Operations

If MPLAB ICD 3 or REAL ICE is selected as a debugger, it automatically initializes all of the Analog-to-Digital input pins (ANx) as "digital" pins by setting all bits in the AD1PCFG register.

The bits in this register that correspond to the Analogto-Digital pins that are initialized by MPLAB ICD 3 or REAL ICE, must not be cleared by the user application firmware; otherwise, communication errors will result between the debugger and the device.

If your application needs to use certain ADC pins as analog input pins during the debug session, the user application must clear the corresponding bits in the AD1PCFG register during initialization of the ADC module.

When MPLAB ICD 3 or REAL ICE is used as a programmer, the user application firmware must correctly configure the AD1PCFG register. Automatic initialization of this register is only done during debugger operation. Failure to correctly configure the register(s) will result in all ADC pins being recognized as analog input pins, resulting in the port value being read as a logic '0', which may affect user application functionality.

# 2.10 Unused I/Os

Unused I/O pins should not be allowed to float as inputs. They can be configured as outputs and driven to a logic-low state.

Alternatively, inputs can be reserved by connecting the pin to Vss through a 1k to 10k resistor and configuring the pin as an input.

## 2.11 EMI/EMC/EFT (IEC 61000-4-4 and IEC 61000-4-2) Suppression Considerations

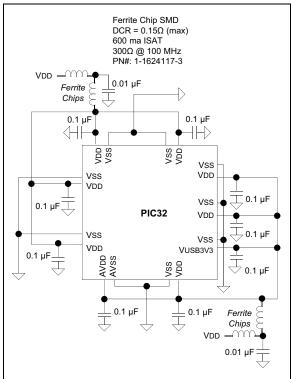

The use of LDO regulators is preferred to reduce overall system noise and provide a cleaner power source. However, when utilizing switching Buck/ Boost regulators as the local power source for PIC32 devices, as well as in electrically noisy environments or test conditions required for IEC 61000-4-4 and IEC 61000-4-2, users should evaluate the use of T-Filters (i.e., L-C-L) on the power pins, as shown in Figure 2-4. In addition to a more stable power source, use of this type of T-Filter can greatly reduce susceptibility to EMI sources and events.

#### FIGURE 2-4: EMI/EMC/EFT SUPPRESSION CIRCUIT

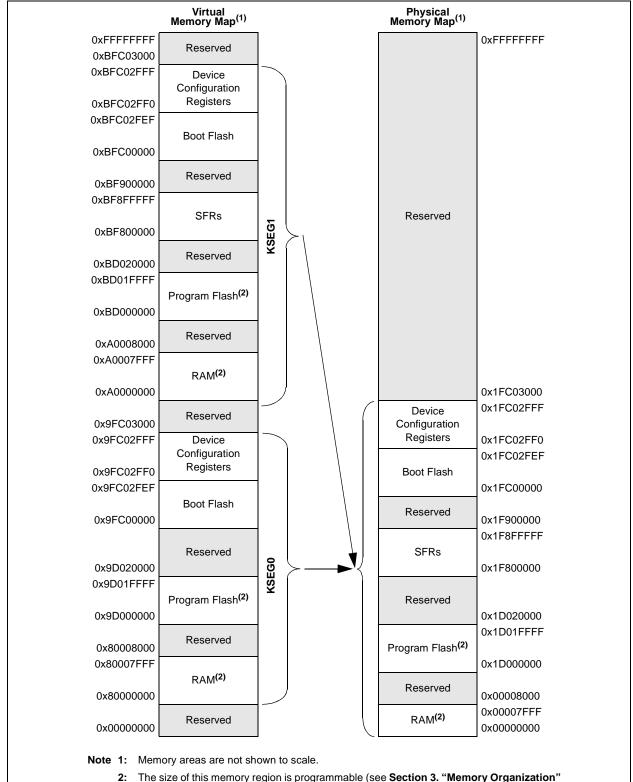

# FIGURE 4-3: MEMORY MAP ON RESET FOR PIC32MX564F128H, PIC32MX564F128L, PIC32MX664F128H, PIC32MX664F128L, PIC32MX764F128H AND PIC32MX764F128L DEVICES

(DS60001115)) and can be changed by initialization code provided by end user development tools (refer to the specific development tool documentation for information).

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0     |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|----------------------|

| 24.24        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0                  |

| 31:24        | —                 | _                 | _                 | —                 | _                 | _                 | -                | —                    |

| 22.16        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0                  |

| 23:16        | -                 | _                 | _                 | —                 | _                 | _                 | _                | —                    |

| 45.0         | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0                  |

| 15:8         | _                 | _                 | _                 | —                 | _                 | _                 | _                | —                    |

| 7.0          | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | W-0, HC              |

| 7:0          |                   | _                 | _                 | —                 | —                 |                   |                  | SWRST <sup>(1)</sup> |

#### REGISTER 6-2: RSWRST: SOFTWARE RESET REGISTER

| Le   | gend:          | HC = Cleared by hardwar | e                         |                    |

|------|----------------|-------------------------|---------------------------|--------------------|

| R =  | = Readable bit | W = Writable bit        | U = Unimplemented bit, re | ead as '0'         |

| -n : | = Value at POR | '1' = Bit is set        | '0' = Bit is cleared      | x = Bit is unknown |

bit 31-1 Unimplemented: Read as '0'

- bit 0 SWRST: Software Reset Trigger bit<sup>(1)</sup> 1 = Enable software Reset event 0 = No effect

- Note 1: The system unlock sequence must be performed before the SWRST bit can be written. Refer to Section 6. "Oscillator" (DS60001112) in the "PIC32 Family Reference Manual" for details.

#### TABLE 7-1: INTERRUPT IRQ, VECTOR AND BIT LOCATION

| Interment Course(1)              | IRQ    | Vector      |               | Interru  | pt Bit Location |              |

|----------------------------------|--------|-------------|---------------|----------|-----------------|--------------|

| Interrupt Source <sup>(1)</sup>  | Number | Number      | Flag          | Enable   | Priority        | Sub-Priority |

|                                  | Highe  | est Natural | Order Priorit | y        |                 |              |

| CT – Core Timer Interrupt        | 0      | 0           | IFS0<0>       | IEC0<0>  | IPC0<4:2>       | IPC0<1:0>    |

| CS0 – Core Software Interrupt 0  | 1      | 1           | IFS0<1>       | IEC0<1>  | IPC0<12:10>     | IPC0<9:8>    |

| CS1 – Core Software Interrupt 1  | 2      | 2           | IFS0<2>       | IEC0<2>  | IPC0<20:18>     | IPC0<17:16>  |

| INT0 – External Interrupt 0      | 3      | 3           | IFS0<3>       | IEC0<3>  | IPC0<28:26>     | IPC0<25:24>  |

| T1 – Timer1                      | 4      | 4           | IFS0<4>       | IEC0<4>  | IPC1<4:2>       | IPC1<1:0>    |

| IC1 – Input Capture 1            | 5      | 5           | IFS0<5>       | IEC0<5>  | IPC1<12:10>     | IPC1<9:8>    |

| OC1 – Output Compare 1           | 6      | 6           | IFS0<6>       | IEC0<6>  | IPC1<20:18>     | IPC1<17:16>  |

| INT1 – External Interrupt 1      | 7      | 7           | IFS0<7>       | IEC0<7>  | IPC1<28:26>     | IPC1<25:24>  |

| T2 – Timer2                      | 8      | 8           | IFS0<8>       | IEC0<8>  | IPC2<4:2>       | IPC2<1:0>    |

| IC2 – Input Capture 2            | 9      | 9           | IFS0<9>       | IEC0<9>  | IPC2<12:10>     | IPC2<9:8>    |

| OC2 – Output Compare 2           | 10     | 10          | IFS0<10>      | IEC0<10> | IPC2<20:18>     | IPC2<17:16>  |

| INT2 – External Interrupt 2      | 11     | 11          | IFS0<11>      | IEC0<11> | IPC2<28:26>     | IPC2<25:24>  |

| T3 – Timer3                      | 12     | 12          | IFS0<12>      | IEC0<12> | IPC3<4:2>       | IPC3<1:0>    |

| IC3 – Input Capture 3            | 13     | 13          | IFS0<13>      | IEC0<13> | IPC3<12:10>     | IPC3<9:8>    |

| OC3 – Output Compare 3           | 14     | 14          | IFS0<14>      | IEC0<14> | IPC3<20:18>     | IPC3<17:16>  |

| INT3 – External Interrupt 3      | 15     | 15          | IFS0<15>      | IEC0<15> | IPC3<28:26>     | IPC3<25:24>  |

| T4 – Timer4                      | 16     | 16          | IFS0<16>      | IEC0<16> | IPC4<4:2>       | IPC4<1:0>    |

| IC4 – Input Capture 4            | 17     | 17          | IFS0<17>      | IEC0<17> | IPC4<12:10>     | IPC4<9:8>    |

| OC4 – Output Compare 4           | 18     | 18          | IFS0<18>      | IEC0<18> | IPC4<20:18>     | IPC4<17:16>  |

| INT4 – External Interrupt 4      | 19     | 19          | IFS0<19>      | IEC0<19> | IPC4<28:26>     | IPC4<25:24>  |

| T5 – Timer5                      | 20     | 20          | IFS0<20>      | IEC0<20> | IPC5<4:2>       | IPC5<1:0>    |

| IC5 – Input Capture 5            | 21     | 21          | IFS0<21>      | IEC0<21> | IPC5<12:10>     | IPC5<9:8>    |

| OC5 – Output Compare 5           | 22     | 22          | IFS0<22>      | IEC0<22> | IPC5<20:18>     | IPC5<17:16>  |

| SPI1E – SPI1 Fault               | 23     | 23          | IFS0<23>      | IEC0<23> | IPC5<28:26>     | IPC5<25:24>  |

| SPI1RX – SPI1 Receive Done       | 24     | 23          | IFS0<24>      | IEC0<24> | IPC5<28:26>     | IPC5<25:24>  |

| SPI1TX – SPI1 Transfer Done      | 25     | 23          | IFS0<25>      | IEC0<25> | IPC5<28:26>     | IPC5<25:24>  |

| U1E – UART1 Error                |        |             |               |          |                 |              |

| SPI3E – SPI3 Fault               | 26     | 24          | IFS0<26>      | IEC0<26> | IPC6<4:2>       | IPC6<1:0>    |

| I2C3B – I2C3 Bus Collision Event |        |             |               |          |                 |              |

| U1RX – UART1 Receiver            |        |             |               |          |                 |              |

| SPI3RX – SPI3 Receive Done       | 27     | 24          | IFS0<27>      | IEC0<27> | IPC6<4:2>       | IPC6<1:0>    |

| I2C3S - I2C3 Slave Event         |        |             |               |          |                 |              |

| U1TX – UART1 Transmitter         |        |             |               |          |                 |              |

| SPI3TX – SPI3 Transfer Done      | 28     | 24          | IFS0<28>      | IEC0<28> | IPC6<4:2>       | IPC6<1:0>    |

| I2C3M – I2C3 Master Event        | 1      |             |               |          |                 |              |

| I2C1B – I2C1 Bus Collision Event | 29     | 25          | IFS0<29>      | IEC0<29> | IPC6<12:10>     | IPC6<9:8>    |

| I2C1S – I2C1 Slave Event         | 30     | 25          | IFS0<30>      | IEC0<30> | IPC6<12:10>     | IPC6<9:8>    |

| I2C1M – I2C1 Master Event        | 31     | 25          | IFS0<31>      | IEC0<31> | IPC6<12:10>     | IPC6<9:8>    |

| CN – Input Change Interrupt      | 32     | 26          | IFS1<0>       | IEC1<0>  | IPC6<20:18>     | IPC6<17:16>  |

Note 1: Not all interrupt sources are available on all devices. See TABLE 1: "PIC32MX5XX USB and CAN Features", TABLE 2: "PIC32MX6XX USB and Ethernet Features" and TABLE 3: "PIC32MX7XX USB, Ethernet, and CAN Features" for the list of available peripherals.

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |  |  |  |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|--|--|--|--|

| 24.24        | R/W-x             | R/W-x             | R/W-x             | R/W-x             | R/W-x             | R/W-x             | R/W-x            | R/W-x            |  |  |  |  |

| 31:24        |                   |                   |                   | CHEW3<            | :31:24>           |                   |                  |                  |  |  |  |  |

| 00.40        | R/W-x             | R/W-x             | R/W-x             | R/W-x             | R/W-x             | R/W-x             | R/W-x            | R/W-x            |  |  |  |  |

| 23:16        | CHEW3<23:16>      |                   |                   |                   |                   |                   |                  |                  |  |  |  |  |

| 45.0         | R/W-x             | R/W-x             | R/W-x             | R/W-x             | R/W-x             | R/W-x             | R/W-x            | R/W-x            |  |  |  |  |

| 15:8         |                   |                   |                   | CHEW3             | <15:8>            |                   |                  |                  |  |  |  |  |

| 7.0          | R/W-x             | R/W-x             | R/W-x             | R/W-x             | R/W-x             | R/W-x             | R/W-x            | R/W-x            |  |  |  |  |

| 7:0          | CHEW3<7:0>        |                   |                   |                   |                   |                   |                  |                  |  |  |  |  |

#### REGISTER 9-8: CHEW3: CACHE WORD 3

| Legend:           |                  |                      |                    |

|-------------------|------------------|----------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bi | t, read as '0'     |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared | x = Bit is unknown |

bit 31-0 **CHEW3<31:0>:** Word 3 of the cache line selected by CHEIDX<3:0> bits (CHEACC<3:0>) Readable only if the device is not code-protected.

Note: This register is a window into the cache data array and is only readable if the device is not code-protected.

#### REGISTER 9-9: CHELRU: CACHE LRU REGISTER

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |  |  |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|--|--|--|

| 31:24        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | R-0              |  |  |  |

| 31.24        | —                 | —                 | _                 | —                 | —                 | _                 | —                | CHELRU<24>       |  |  |  |

| 22:16        | R-0               | R-0               | R-0               | R-0               | R-0               | R-0               | R-0              | R-0              |  |  |  |

| 23:16        |                   | CHELRU<23:16>     |                   |                   |                   |                   |                  |                  |  |  |  |

| 45.0         | R-0               | R-0               | R-0               | R-0               | R-0               | R-0               | R-0              | R-0              |  |  |  |

| 15:8         |                   |                   |                   | CHELR             | U<15:8>           |                   |                  |                  |  |  |  |

| 7:0          | R-0               | R-0               | R-0               | R-0               | R-0               | R-0               | R-0              | R-0              |  |  |  |

| 7.0          | CHELRU<7:0>       |                   |                   |                   |                   |                   |                  |                  |  |  |  |

| Legend:           |                  |                        |                    |

|-------------------|------------------|------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, | read as '0'        |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared   | x = Bit is unknown |

bit 31-25 Unimplemented: Write '0'; ignore read

bit 24-0 **CHELRU<24:0>:** Cache Least Recently Used State Encoding bits Indicates the pseudo-LRU state of the cache.

### TABLE 10-3: DMA CHANNELS 0-7 REGISTER MAP (CONTINUED)

| ess                         |                                 | a             |                    |       |       |       |        |       |      | Bi     | ts      |        |        |        |         |        |        |        | 6          |

|-----------------------------|---------------------------------|---------------|--------------------|-------|-------|-------|--------|-------|------|--------|---------|--------|--------|--------|---------|--------|--------|--------|------------|

| Virtual Address<br>(BF88_#) | Register<br>Name <sup>(1)</sup> | Bit Range     | 31/15              | 30/14 | 29/13 | 28/12 | 27/11  | 26/10 | 25/9 | 24/8   | 23/7    | 22/6   | 21/5   | 20/4   | 19/3    | 18/2   | 17/1   | 16/0   | All Resets |

|                             | DCH4SSIZ                        | 31:16         | —                  |       | —     | —     | _      | _     | -    | —      | _       | _      | _      | _      | —       | —      | —      | _      | 000        |

| 0000                        | DONIOOIZ                        | 15:0          |                    |       |       |       |        |       |      | CHSSI  | Z15:0>  |        |        |        |         |        |        |        | 000        |

| 300                         | DCH4DSIZ                        | 31:16         | —                  | _     | —     | _     | _      | —     | —    | —      | _       | —      | —      | —      | —       | _      | _      | —      | 00         |

|                             | DOITIDOIL                       | 15:0          |                    |       |       |       |        |       |      | CHDSIZ | 2<15:0> |        |        |        |         |        |        |        | 00         |

| 3D0                         | DCH4SPTR                        | 31:16         | —                  | _     | —     | _     | _      | —     | _    | —      | _       | —      | —      | —      | —       | —      | —      | —      | 00         |

| 000                         |                                 | 15:0          |                    |       |       |       |        |       |      | CHSPTI | R<15:0> |        |        |        |         |        |        |        | 00         |

| 3E0                         | DCH4DPTR                        | 31:16         | —                  | —     |       | —     | _      | —     | —    | —      | _       | —      | —      | —      | —       |        |        | —      | 00         |

| 020                         |                                 | 15:0          |                    |       |       |       |        |       |      | CHDPTI |         |        |        |        |         |        |        |        | 00         |

| 3F0                         | DCH4CSIZ                        | 31:16         | —                  | _     | —     | —     | —      | —     | _    | —      | —       | —      | —      | —      |         |        | —      | —      | 00         |

| 01 0                        |                                 | 15:0          |                    |       |       |       |        |       |      | CHCSIZ | 2<15:0> |        |        |        |         |        |        |        | 00         |

| 400                         | DCH4CPTR                        | 31:16         | _                  | —     | —     | —     | —      | -     | —    | —      | —       | —      | -      | —      | —       | _      | _      | —      | 00         |

| -00                         | 5011101 111                     | 15:0          |                    |       |       |       |        |       |      | CHCPT  | R<15:0> |        |        |        |         | 1      | 1      |        | 00         |

| 8410                        | DCH4DAT                         | 31:16         | —                  | —     | —     | _     | -      | —     | _    | —      | -       | —      | —      | —      | —       | _      | —      | —      | 00         |

| -10                         | 501115/11                       | 15:0          | —                  |       | —     | —     | —      | —     | _    | —      |         |        |        | CHPDA  | AT<7:0> |        |        |        | 00         |

| 120                         | DCH5CON                         | 31:16         | —                  | _     | —     | _     | _      | _     | _    | —      | _       | _      | _      | _      | —       | _      | _      | —      | 00         |

| 420                         | Donocon                         | 15:0          | CHBUSY             |       | —     | —     | —      | —     | _    | CHCHNS | CHEN    | CHAED  | CHCHN  | CHAEN  | —       | CHEDET | CHPR   | l<1:0> | 00         |

| 120                         | DCH5ECON                        | 31:16         | —                  | _     | _     | —     | _      | —     | _    | —      |         |        |        | CHAIR  | Q<7:0>  |        |        |        | 00         |

| 430                         | DONOLOON                        | 15:0          |                    |       |       | CHSIR | Q<7:0> |       |      |        | CFORCE  | CABORT | PATEN  | SIRQEN | AIRQEN  | —      | —      | —      | FF         |

| 3440                        | DCH5INT                         | 31:16         | —                  | _     |       | —     | _      | —     | _    | —      | CHSDIE  | CHSHIE | CHDDIE | CHDHIE | CHBCIE  | CHCCIE | CHTAIE | CHERIE | 00         |

| 440                         | Donointi                        | 15:0          | —                  | _     | _     | —     | _      | —     | _    | —      | CHSDIF  | CHSHIF | CHDDIF | CHDHIF | CHBCIF  | CHCCIF | CHTAIF | CHERIF | 00         |

| 450                         | DCH5SSA                         | 31:16<br>15:0 |                    |       |       |       |        |       |      | CHSSA  | <31:0>  |        |        |        |         |        |        |        | 00         |

| 3460                        | DCH5DSA                         | 31:16         |                    |       |       |       |        |       |      | CHDSA  | <31:0>  |        |        |        |         |        |        |        | 00         |

| 100                         |                                 | 15:0          |                    |       | 1     | 1     |        |       |      |        |         |        |        |        |         | 1      | 1      |        | 00         |

| 470                         | DCH5SSIZ                        | 31:16         | —                  | —     |       | —     | _      | —     | —    | —      | _       | —      | —      | —      | —       |        |        | —      | 00         |

|                             |                                 | 15:0          |                    |       |       |       |        |       |      | CHSSIZ | <15:0>  |        |        |        |         |        | 1      |        | 00         |

| 8480                        | DCH5DSIZ                        | 31:16         | —                  | —     | _     | _     | —      | —     | —    | —      | —       | —      | —      | —      | —       | -      |        | —      | 00         |

| 400                         | 501105012                       | 15:0          |                    |       |       |       |        |       |      | CHDSIZ | .<15:0> |        |        |        |         |        |        | -      | 00         |

| 100                         | DCH5SPTR                        | 31:16         | —                  |       | —     | —     | —      | —     | —    | —      | —       | —      | —      | —      | —       | —      | —      | —      | 00         |

| , 100                       | - 51.00. 110                    | 15:0          |                    |       |       |       |        |       |      | CHSPTI | R<15:0> |        |        |        |         |        |        |        | 00         |

| 110                         | DCH5DPTR                        | 31:16         | —                  | _     | _     | —     | _      | —     | _    | —      | _       | —      | _      | _      | —       | _      |        | —      | 00         |

| <del>4</del> AU             |                                 | 15:0          |                    |       |       |       |        |       |      | CHDPTI | R<15:0> |        |        |        |         |        |        |        | 00         |

| 400                         | DCH5CSIZ                        | 31:16         | _                  | _     | _     | _     | _      | —     | _    | _      | _       | _      | —      | 1      | -       | _      | _      | —      | 00         |

| 4BU                         | DCH3C3IZ                        | 15:0          | 0 CHCSIZ<15:0> 000 |       |       |       |        |       |      |        |         |        |        |        |         |        |        |        |            |

| 400                         | DCH5CPTR                        | 31:16         | _                  | _     | _     | _     | _      | _     | _    | _      | _       | _      | -      |        | —       | _      | _      | —      | 00         |

|                             | IDCHOCKIK                       | 15:0          |                    |       |       |       |        |       |      | CHCPTI |         |        |        |        |         |        |        |        | 00         |

All registers in this table have corresponding CLR, SET and INV registers at their virtual addresses, plus offsets of 0x4, 0x8 and 0xC, respectively. See Section 12.1.1 "CLR, SET and INV Registers" for more Note 1: information.

DMA channels 4-7 are not available on PIC32MX534/564/664/764 devices. 2:

#### REGISTER 11-11: U1CON: USB CONTROL REGISTER

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5        | Bit<br>28/20/12/4 | Bit<br>27/19/11/3     | Bit<br>26/18/10/2     | Bit<br>25/17/9/1 | Bit<br>24/16/8/0     |

|--------------|-------------------|-------------------|--------------------------|-------------------|-----------------------|-----------------------|------------------|----------------------|

| 21.24        | U-0               | U-0               | U-0                      | U-0               | U-0                   | U-0                   | U-0              | U-0                  |

| 31:24        |                   |                   | —                        | —                 |                       |                       | —                | —                    |

| 00.40        | U-0               | U-0               | U-0                      | U-0               | U-0                   | U-0                   | U-0              | U-0                  |

| 23:16        | -                 | _                 | —                        | —                 | _                     | -                     | —                | —                    |

| 15:8         | U-0               | U-0               | U-0                      | U-0               | U-0                   | U-0                   | U-0              | U-0                  |

| 15.6         |                   |                   | —                        | —                 |                       |                       | —                | —                    |

|              | R-x               | R-x               | R/W-0                    | R/W-0             | R/W-0                 | R/W-0                 | R/W-0            | R/W-0                |

| 7:0          | JSTATE            | SE0               | PKTDIS <sup>(4)</sup>    | USBRST            | HOSTEN <sup>(2)</sup> | RESUME <sup>(3)</sup> | PPBRST           | USBEN <sup>(4)</sup> |

|              | JUNE              | 320               | TOKBUSY <sup>(1,5)</sup> | 030631            | TIOSTEIN'             | KESUME"               | FFDKOI           | SOFEN <sup>(5)</sup> |

| Legend:           |                  |                          |                    |

|-------------------|------------------|--------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, r | ead as '0'         |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared     | x = Bit is unknown |

#### bit 31-8 Unimplemented: Read as '0'

- bit 7 **JSTATE:** Live Differential Receiver JSTATE flag bit 1 = JSTATE was detected on the USB

- 0 = JSTATE was not detected

- bit 6 SE0: Live Single-Ended Zero flag bit

1 = Single-ended zero was detected on the USB

0 = Single-ended zero was not detected

- bit 5 **PKTDIS:** Packet Transfer Disable bit<sup>(4)</sup>

- 1 = Token and packet processing disabled (set upon SETUP token received)

- 0 = Token and packet processing enabled

TOKBUSY: Token Busy Indicator bit<sup>(1,5)</sup>

- 1 = Token being executed by the USB module

- 0 = No token being executed

- bit 4 USBRST: Module Reset bit<sup>(5)</sup>

- 1 = USB reset is generated

- 0 = USB reset is terminated

#### bit 3 HOSTEN: Host Mode Enable bit<sup>(2)</sup>

- 1 = USB host capability is enabled

- 0 = USB host capability is disabled

- bit 2 **RESUME:** RESUME Signaling Enable bit<sup>(3)</sup>

- 1 = RESUME signaling is activated

- 0 = RESUME signaling is disabled

- **Note 1:** Software is required to check this bit before issuing another token command to the U1TOK register (see Register 11-15).

- 2: All host control logic is reset any time that the value of this bit is toggled.

- 3: Software must set RESUME for 10 ms in Device mode, or for 25 ms in Host mode, and then clear it to enable remote wake-up. In Host mode, the USB module will append a low-speed EOP to the RESUME signaling when this bit is cleared.

- 4: Device mode.

- 5: Host mode.

# **19.1 Control Registers**

#### TABLE 19-1: I2C1THROUGH I2C5 REGISTER MAP

| ss                          |                                 |               |              |             |       |        |        |       |             | Bi         | ts    |             |              |              |               |          |          |          |            |

|-----------------------------|---------------------------------|---------------|--------------|-------------|-------|--------|--------|-------|-------------|------------|-------|-------------|--------------|--------------|---------------|----------|----------|----------|------------|

| Virtual Address<br>(BF80_#) | Register<br>Name <sup>(1)</sup> | Bit Range     | 31/15        | 30/14       | 29/13 | 28/12  | 27/11  | 26/10 | 25/9        | 24/8       | 23/7  | 22/6        | 21/5         | 20/4         | 19/3          | 18/2     | 17/1     | 16/0     | All Resets |

| 5000                        | I2C3CON                         | 31:16         | _            | _           | —     | _      |        |       | _           | _          |       |             | —            | _            | —             |          |          |          | 0000       |

|                             |                                 | 15:0          | ON           | —           | SIDL  | SCLREL | STRICT | A10M  | DISSLW      | SMEN       | GCEN  | STREN       | ACKDT        | ACKEN        | RCEN          | PEN      | RSEN     | SEN      | 1000       |

| 5010                        | I2C3STAT                        | 31:16<br>15:0 | —<br>ACKSTAT | —<br>TRSTAT |       |        | _      | BCL   | —<br>GCSTAT | —<br>ADD10 |       | –<br>I2COV  | —<br>D/A     | —<br>P       |               | —<br>R/W | —<br>RBF | —<br>TBF | 0000       |

|                             | 1000100                         | 31:16         | —            | -           | _     | _      | _      | -     |             | -          | —     | -           |              | -            | _             | -        | —        | —        | 0000       |

| 5020                        | I2C3ADD                         | 15:0          | _            | _           | _     | _      | _      | _     |             |            |       |             | ADD          | <9:0>        |               |          |          |          | 0000       |

| 5000                        | IOCOMOK                         | 31:16         | _            | _           | —     | —      | —      | _     | —           | _          | —     | _           | —            | —            | —             | _        | _        | _        | 0000       |

| 5030                        | I2C3MSK                         | 15:0          | _            | _           | —     | _      | —      |       |             |            |       |             | MSK          | <9:0>        |               |          |          |          | 0000       |

| 5040                        | I2C3BRG                         | 31:16         | _            | _           | —     | _      | _      | -     | _           | _          | -     | _           | _            | _            | _             | _        | _        | _        | 0000       |

| 5040                        | IZCODKG                         | 15:0          | _            | _           | —     | —      |        |       |             |            | Ba    | ud Rate Ger | nerator Regi | ster         |               |          |          |          | 0000       |

| 5050                        | I2C3TRN                         | 31:16         | —            | —           |       |        | —      |       |             | _          |       | —           | -            | _            | -             | —        | —        | -        | 0000       |

| 5050                        | 120311(1)                       | 15:0          | —            | —           |       |        | —      |       |             | _          |       |             | -            | Transmit     | Register      |          |          |          | 0000       |

| 5060                        | I2C3RCV                         | 31:16         | —            | —           | —     | —      | —      | _     | —           | —          | _     | —           | —            | —            | —             | —        | —        | —        | 0000       |

| 0000                        | 12001101                        | 15:0          | _            | _           | —     | _      | —      | _     | _           | —          |       |             |              | Receive      | Register      | -        | -        |          | 0000       |

| 5100                        | I2C4CON                         | 31:16         | _            | _           | —     | _      | _      | _     | _           | _          | _     | —           | _            | _            | _             | —        | —        | —        | 0000       |

|                             |                                 | 15:0          | ON           | _           | SIDL  | SCLREL | STRICT | A10M  | DISSLW      | SMEN       | GCEN  | STREN       | ACKDT        | ACKEN        | RCEN          | PEN      | RSEN     | SEN      | 1000       |

| 5110                        | I2C4STAT                        | 31:16         | —            | —           | —     |        | _      | —     | —           | _          | —     | —           |              | —            |               | —        | —        | —        | 0000       |

| L                           |                                 | 15:0          | ACKSTAT      | TRSTAT      | —     | —      | —      | BCL   | GCSTAT      | ADD10      | IWCOL | I2COV       | D/A          | Р            | S             | R/W      | RBF      | TBF      | 0000       |

| 5120                        | I2C4ADD                         | 31:16         | _            | _           | —     | _      | _      | _     | —           |            | —     | —           | —            | —            | —             | _        | _        | —        | 0000       |

| <b></b>                     |                                 | 15:0          | _            | _           | _     | _      | _      |       |             |            |       |             | ADD          | <9:0>        |               |          |          |          | 0000       |

| 5130                        | I2C4MSK                         | 31:16         | _            | _           |       |        |        |       |             | _          | _     | _           |              |              |               |          | _        | _        | 0000       |

| ┢────┼                      |                                 | 15:0          |              | _           |       |        | _      |       |             |            |       |             | MSK          | <9:0>        |               |          |          |          | 0000       |

| 5140                        | I2C4BRG                         | 31:16         |              | _           | _     |        |        | —     | —           |            | -     | —           | —            | —            | —             | _        | _        | —        | 0000       |

|                             |                                 | 15:0<br>31:16 | _            | _           | _     |        |        |       |             |            |       | ud Rate Ger | erator Regi  | ster         |               |          |          |          | 0000       |

| 5150                        | I2C4TRN                         | 15:0          |              |             |       |        |        |       |             |            | _     | _           | _            | <br>Transmit | —<br>Register | —        | —        | —        | 0000       |

| ł                           |                                 | 31:16         |              |             |       |        |        |       |             |            |       |             |              |              |               | _        | _        | _        | 0000       |

| 5160                        | I2C4RCV                         | 15:0          | _            | _           |       |        |        |       |             | _          | _     |             |              | Receive      | Register      |          |          |          | 0000       |

|                             |                                 | 31:16         | _            | _           | _     | _      | _      | _     | _           | _          | _     | _           | _            | _            | _             | _        | _        | _        | 0000       |

| 5200                        | I2C5CON                         | 15:0          | ON           | _           | SIDL  | SCLREL | STRICT | A10M  | DISSLW      | SMEN       | GCEN  | STREN       | ACKDT        | ACKEN        | RCEN          | PEN      | RSEN     | SEN      | 1000       |

| 5040                        | 10050747                        | 31:16         | _            | _           | —     | —      | _      | _     | —           |            | _     | _           | —            | —            | —             | _        | _        | _        | 0000       |

| 5210                        | I2C5STAT                        | 15:0          | ACKSTAT      | TRSTAT      | —     | —      | —      | BCL   | GCSTAT      | ADD10      | IWCOL | I2COV       | D/A          | Р            | S             | R/W      | RBF      | TBF      | 0000       |

| 5000                        | 1005405                         | 31:16         | _            | _           | —     | —      | _      | —     | —           | _          | —     | _           | —            | —            | —             | _        | _        | _        | 0000       |

| 5220                        | I2C5ADD                         | 15:0          | _            | _           | _     | _      | _      | _     |             |            |       |             | ADD          | <9:0>        |               |          |          |          | 0000       |

Legend: x = unknown value on Reset; - = unimplemented, read as '0'. Reset values are shown in hexadecimal.

Note 1: All registers in this table except I2CxRCV have corresponding CLR, SET and INV registers at their virtual addresses, plus offsets of 0x4, 0x8 and 0xC, respectively. See Section 12.1.1 "CLR, SET and INV Registers" for more information.

PIC32MX5XX/6XX/7XX

2: This register is not available on 64-pin devices.

| Bit   | Bit        | Bit        | Bit        | Bit        | Bit        | Bit        | Bit       | Bit       |

|-------|------------|------------|------------|------------|------------|------------|-----------|-----------|

| Range | 31/23/15/7 | 30/22/14/6 | 29/21/13/5 | 28/20/12/4 | 27/19/11/3 | 26/18/10/2 | 25/17/9/1 | 24/16/8/0 |

| 24.24 | U-0        | U-0        | U-0        | U-0        | U-0        | U-0        | U-0       | U-0       |

| 31:24 | —          | _          | -          | —          | —          | —          | _         | _         |

| 00.40 | U-0        | U-0        | U-0        | U-0        | U-0        | U-0        | U-0       | U-0       |

| 23:16 | —          | _          | _          | _          | _          | —          | _         | _         |

| 45.0  | R-0, HSC   | R-0, HSC   | U-0        | U-0        | U-0        | R/C-0, HS  | R-0, HSC  | R-0, HSC  |

| 15:8  | ACKSTAT    | TRSTAT     | _          | —          | —          | BCL        | GCSTAT    | ADD10     |

| 7.0   | R/C-0, HS  | R/C-0, HS  | R-0, HSC   | R/C-0, HSC | R/C-0, HSC | R-0, HSC   | R-0, HSC  | R-0, HSC  |

| 7:0   | IWCOL      | I2COV      | D_A        | Р          | S          | R_W        | RBF       | TBF       |

# REGISTER 19-2: I2CxSTAT: I<sup>2</sup>C STATUS REGISTER

| Legend: HS = Set by hardware |                  | HSC = Hardware set/cleared         |                   |  |

|------------------------------|------------------|------------------------------------|-------------------|--|

| R = Readable bit             | W = Writable bit | U = Unimplemented bit, read as '0' |                   |  |

| -n = Value at POR            | '1' = Bit is set | '0' = Bit is cleared               | C = Clearable bit |  |

#### bit 31-16 Unimplemented: Read as '0'

- bit 15 **ACKSTAT:** Acknowledge Status bit (when operating as I<sup>2</sup>C master, applicable to master transmit operation) This bit is set or cleared by hardware at the end of a slave Acknowledge.

- 1 = NACK received from slave

- 0 = ACK received from slave

- bit 14 **TRSTAT:** Transmit Status bit (when operating as I<sup>2</sup>C master, applicable to master transmit operation) This bit is set by hardware at the beginning of a master transmission, and is cleared by hardware at the end of a slave Acknowledge.

- 1 = Master transmit is in progress (8 bits + ACK)

- 0 = Master transmit is not in progress

- bit 13-11 Unimplemented: Read as '0'

- bit 10 BCL: Master Bus Collision Detect bit

This bit is set by hardware at the detection of a bus collision.

- 1 = A bus collision has been detected during a master operation

- 0 = No collision

- bit 9 GCSTAT: General Call Status bit

This bit is set by hardware when the address matches the general call address, and is cleared by hardware clear at a Stop detection.

- 1 = General call address was received

- 0 = General call address was not received

#### bit 8 ADD10: 10-bit Address Status bit

This bit is set by hardware upon a match of the 2nd byte of the matched 10-bit address, and is cleared by hardware at a Stop detection.

- 1 = 10-bit address was matched

- 0 = 10-bit address was not matched

#### bit 7 IWCOL: Write Collision Detect bit

- This bit is set by hardware at the occurrence of a write to I2CxTRN while busy (cleared by software).

- 1 = An attempt to write the I2CxTRN register failed because the  $I^2C$  module is busy

- 0 = No collision

# bit 6 I2COV: Receive Overflow Flag bit

- This bit is set by hardware at an attempt to transfer I2CxRSR to I2CxRCV (cleared by software).

- 1 = A byte was received while the I2CxRCV register is still holding the previous byte

- 0 = No overflow

### REGISTER 22-1: RTCCON: RTC CONTROL REGISTER (CONTINUED)

- bit 3 RTCWREN: RTC Value Registers Write Enable bit<sup>(4)</sup>

- 1 = RTC Value registers can be written to by the user

- 0 = RTC Value registers are locked out from being written to by the user

- bit 2 RTCSYNC: RTCC Value Registers Read Synchronization bit

- 1 = RTC Value registers can change while reading, due to a rollover ripple that results in an invalid data read. If the register is read twice and results in the same data, the data can be assumed to be valid.

- 0 = RTC Value registers can be read without concern about a rollover ripple

- bit 1 HALFSEC: Half-Second Status bit<sup>(5)</sup>

- 1 = Second half period of a second

- 0 = First half period of a second

- bit 0 RTCOE: RTCC Output Enable bit

- 1 = RTCC clock output is enabled (clock presented onto an I/O)

- 0 = RTCC clock output is disabled

- **Note 1:** The ON bit is only writable when RTCWREN = 1.

- 2: When using the 1:1 PBCLK divisor, the user's software should not read/write the peripheral's SFRs in the SYSCLK cycle immediately following the instruction that clears the module's ON bit.

- **3:** Requires RTCOE = 1 (RTCCON<0>) for the output to be active.

- 4: The RTCWREN bit can only be set when the write sequence is enabled.

- 5: This bit is read-only. It is cleared to '0' on a write to the seconds bit fields (RTCTIME<14:8>).

Note: This register is only reset on a Power-on Reset (POR).

### REGISTER 24-17: CIFLTCON7: CAN FILTER CONTROL REGISTER 7 (CONTINUED)

| bit 15    | FLTEN29: Filter 29 Enable bit<br>1 = Filter is enabled<br>0 = Filter is disabled                                                                                               |

|-----------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| bit 14-13 | MSEL29<1:0>: Filter 29 Mask Select bits                                                                                                                                        |

|           | <ul> <li>11 = Acceptance Mask 3 selected</li> <li>10 = Acceptance Mask 2 selected</li> <li>01 = Acceptance Mask 1 selected</li> <li>00 = Acceptance Mask 0 selected</li> </ul> |

| bit 12-8  | FSEL29<4:0>: FIFO Selection bits                                                                                                                                               |

|           | 11111 = Message matching filter is stored in FIFO buffer 31                                                                                                                    |

|           | 11110 = Message matching filter is stored in FIFO buffer 30                                                                                                                    |

|           | •                                                                                                                                                                              |

|           |                                                                                                                                                                                |

|           | 00001 = Message matching filter is stored in FIFO buffer 1<br>00000 = Message matching filter is stored in FIFO buffer 0                                                       |

| bit 7     | FLTEN28: Filter 28 Enable bit                                                                                                                                                  |

|           | <ul><li>1 = Filter is enabled</li><li>0 = Filter is disabled</li></ul>                                                                                                         |

| bit 6-5   | MSEL28<1:0>: Filter 28 Mask Select bits                                                                                                                                        |

|           | 11 = Acceptance Mask 3 selected                                                                                                                                                |

|           | 10 = Acceptance Mask 2 selected                                                                                                                                                |

|           | 01 = Acceptance Mask 1 selected<br>00 = Acceptance Mask 0 selected                                                                                                             |

| bit 4-0   | FSEL28<4:0>: FIFO Selection bits                                                                                                                                               |

|           | 11111 = Message matching filter is stored in FIFO buffer 31                                                                                                                    |

|           | 11110 = Message matching filter is stored in FIFO buffer 30                                                                                                                    |

|           | •                                                                                                                                                                              |

|           |                                                                                                                                                                                |

|           | 00001 = Message matching filter is stored in FIFO buffer 1                                                                                                                     |

|           | 00000 = Message matching filter is stored in FIFO buffer 0                                                                                                                     |

| Note:     | The bits in this register can only be modified if the corresponding filter enable (FLTENn) bit is '0'.                                                                         |

| Bit Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0    |  |  |  |

|-----------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|---------------------|--|--|--|

| 24.24     | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0               |  |  |  |

| 31:24     | PTV<15:8>         |                   |                   |                   |                   |                   |                  |                     |  |  |  |

| 00.40     | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0               |  |  |  |

| 23:16     | PTV<7:0>          |                   |                   |                   |                   |                   |                  |                     |  |  |  |

| 45.0      | R/W-0             | U-0               | R/W-0             | U-0               | U-0               | U-0               | R/W-0            | R/W-0               |  |  |  |

| 15:8      | ON                | —                 | SIDL              | _                 | _                 | _                 | TXRTS            | RXEN <sup>(1)</sup> |  |  |  |

| 7:0       | R/W-0             | U-0               | U-0               | R/W-0             | U-0               | U-0               | U-0              | R/W-0               |  |  |  |

| 7:0       | AUTOFC            |                   | _                 | MANFC             | _                 |                   |                  | BUFCDEC             |  |  |  |

### REGISTER 25-1: ETHCON1: ETHERNET CONTROLLER CONTROL REGISTER 1

#### Legend:

| Legenu.           |                  |                          |                    |

|-------------------|------------------|--------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, I | read as '0'        |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared     | x = Bit is unknown |

bit 31-16 PTV<15:0>: PAUSE Timer Value bits PAUSE Timer Value used for Flow Control. This register should only be written when RXEN (ETHCON1<8>) is not set. These bits are only used for Flow Control operations. bit 15 **ON:** Ethernet ON bit 1 = Ethernet module is enabled 0 = Ethernet module is disabled bit 14 Unimplemented: Read as '0' bit 13 SIDL: Ethernet Stop in Idle Mode bit 1 = Ethernet module transfers are paused during Idle mode 0 = Ethernet module transfers continue during Idle mode bit 12-10 Unimplemented: Read as '0' bit 9 TXRTS: Transmit Request to Send bit 1 = Activate the TX logic and send the packet(s) defined in the TX EDT 0 = Stop transmit (when cleared by software) or transmit done (when cleared by hardware)

After the bit is written with a '1', it will clear to a '0' whenever the transmit logic has finished transmitting the requested packets in the Ethernet Descriptor Table (EDT). If a '0' is written by the CPU, the transmit logic finishes the current packet's transmission and then stops any further.

This bit only affects TX operations.

#### bit 8 **RXEN:** Receive Enable bit<sup>(1)</sup>

- 1 = Enable RX logic, packets are received and stored in the RX buffer as controlled by the filter configuration

- 0 = Disable RX logic, no packets are received in the RX buffer

This bit only affects RX operations.

**Note 1:** It is not recommended to clear the RXEN bit and then make changes to any RX related field/register. The Ethernet Controller must be reinitialized (ON cleared to '0'), and then the RX changes applied.

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |  |  |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|--|--|--|

| 31:24        | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |  |

| 31.24        | HT<31:24          |                   |                   |                   |                   |                   |                  |                  |  |  |  |

| 22.10        | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |  |

| 23:16        | HT<23:16>         |                   |                   |                   |                   |                   |                  |                  |  |  |  |

| 45.0         | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |  |

| 15:8         | HT<15:8>          |                   |                   |                   |                   |                   |                  |                  |  |  |  |

| 7.0          | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |  |

| 7:0          | HT<7:0>           |                   |                   |                   |                   |                   |                  |                  |  |  |  |

#### REGISTER 25-5: ETHHT0: ETHERNET CONTROLLER HASH TABLE 0 REGISTER

| Legend:           |                  |                           |                    |

|-------------------|------------------|---------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, re | ead as '0'         |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared      | x = Bit is unknown |

bit 31-0 HT<31:0>: Hash Table Bytes 0-3 bits

Note 1: This register is only used for RX operations.

2: The bits in this register may only be changed while the RXEN bit (ETHCON1<8>) = 0 or the HTEN bit (ETHRXFC<15>) = 0.

#### REGISTER 25-6: ETHHT1: ETHERNET CONTROLLER HASH TABLE 1 REGISTER

| Bit Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |  |  |  |

|-----------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|--|--|--|--|

| 21.24     | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |  |  |

| 31:24     |                   | HT<63:56>         |                   |                   |                   |                   |                  |                  |  |  |  |  |

| 00.40     | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |  |  |

| 23:16     | HT<55:48>         |                   |                   |                   |                   |                   |                  |                  |  |  |  |  |

| 45.0      | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |  |  |

| 15:8      | HT<47:40>         |                   |                   |                   |                   |                   |                  |                  |  |  |  |  |

| 7.0       | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |  |  |

| 7:0       |                   |                   |                   | HT<3              | 9:32>             |                   |                  |                  |  |  |  |  |

| Legend:           |                  |                          |                    |

|-------------------|------------------|--------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, I | ead as '0'         |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared     | x = Bit is unknown |

#### bit 31-0 HT<63:32>: Hash Table Bytes 4-7 bits

Note 1: This register is only used for RX operations.

2: The bits in this register may only be changed while the RXEN bit (ETHCON1<8>) = 0 or the HTEN bit (ETHRXFC<15>) = 0.

NOTES:

#### TABLE 32-35: ETHERNET MODULE SPECIFICATIONS

| АС СНА        | RACTERISTICS                        | $\begin{array}{ll} \mbox{Standard Operating Conditions (see Note 1): 2.9V to 3.6V} \\ \mbox{(unless otherwise stated)} \\ \mbox{Operating temperature} & -40^{\circ}C \leq TA \leq +85^{\circ}C \mbox{ for Industrial} \\ & -40^{\circ}C \leq TA \leq +105^{\circ}C \mbox{ for V-Temp} \end{array}$ |         |      |       |                  |  |  |  |

|---------------|-------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------|------|-------|------------------|--|--|--|

| Param.<br>No. | Characteristic                      | Min.                                                                                                                                                                                                                                                                                                | Typical | Max. | Units | Conditions       |  |  |  |

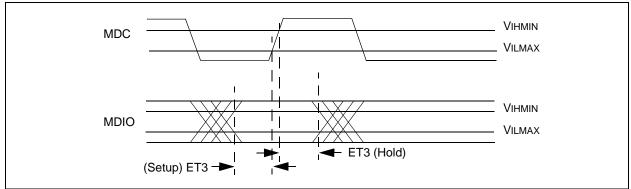

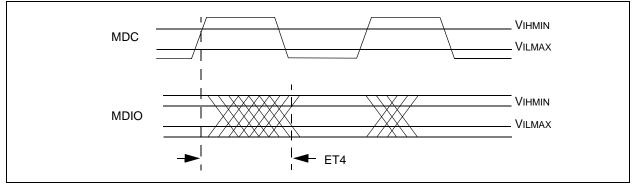

| MIIM Tin      | ning Requirements                   |                                                                                                                                                                                                                                                                                                     |         |      |       |                  |  |  |  |

| ET1           | MDC Duty Cycle                      | 40                                                                                                                                                                                                                                                                                                  |         | 60   | %     | —                |  |  |  |

| ET2           | MDC Period                          | 400                                                                                                                                                                                                                                                                                                 | —       | _    | ns    | —                |  |  |  |