Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Details                    |                                                                                   |

|----------------------------|-----------------------------------------------------------------------------------|

| Product Status             | Active                                                                            |

| Core Processor             | MIPS32 ® M4K™                                                                     |

| Core Size                  | 32-Bit Single-Core                                                                |

| Speed                      | 80MHz                                                                             |

| Connectivity               | Ethernet, I <sup>2</sup> C, SPI, UART/USART, USB OTG                              |

| Peripherals                | Brown-out Detect/Reset, DMA, POR, PWM, WDT                                        |

| Number of I/O              | 53                                                                                |

| Program Memory Size        | 512KB (512K x 8)                                                                  |

| Program Memory Type        | FLASH                                                                             |

| EEPROM Size                | -                                                                                 |

| RAM Size                   | 128K x 8                                                                          |

| Voltage - Supply (Vcc/Vdd) | 2.3V ~ 3.6V                                                                       |

| Data Converters            | A/D 16x10b                                                                        |

| Oscillator Type            | Internal                                                                          |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                                 |

| Mounting Type              | Surface Mount                                                                     |

| Package / Case             | 64-TQFP                                                                           |

| Supplier Device Package    | 64-TQFP (10x10)                                                                   |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic32mx695f512ht-80i-pt |

|                            |                                                                                   |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

## TO OUR VALUED CUSTOMERS

It is our intention to provide our valued customers with the best documentation possible to ensure successful use of your Microchip products. To this end, we will continue to improve our publications to better suit your needs. Our publications will be refined and enhanced as new volumes and updates are introduced.

If you have any questions or comments regarding this publication, please contact the Marketing Communications Department via E-mail at **docerrors@microchip.com** or fax the **Reader Response Form** in the back of this data sheet to (480) 792-4150. We welcome your feedback.

### Most Current Data Sheet

To obtain the most up-to-date version of this data sheet, please register at our Worldwide Web site at:

#### http://www.microchip.com

You can determine the version of a data sheet by examining its literature number found on the bottom outside corner of any page. The last character of the literature number is the version number, (e.g., DS30000000A is version A of document DS30000000).

#### Errata

An errata sheet, describing minor operational differences from the data sheet and recommended workarounds, may exist for current devices. As device/documentation issues become known to us, we will publish an errata sheet. The errata will specify the revision of silicon and revision of document to which it applies.

To determine if an errata sheet exists for a particular device, please check with one of the following:

- Microchip's Worldwide Web site; http://www.microchip.com

- Your local Microchip sales office (see last page)

When contacting a sales office, please specify which device, revision of silicon and data sheet (include literature number) you are using.

#### **Customer Notification System**

Register on our web site at www.microchip.com to receive the most current information on all of our products.

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |  |  |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|--|--|--|

| 04.04        | R                 | R                 | R                 | R                 | R                 | R                 | R                | R                |  |  |  |

| 31:24        | BMXDRMSZ<31:24>   |                   |                   |                   |                   |                   |                  |                  |  |  |  |

| 00.40        | R                 | R                 | R                 | R                 | R                 | R                 | R                | R                |  |  |  |

| 23:16        |                   |                   |                   | BMXDRM            | ISZ<23:16>        |                   |                  |                  |  |  |  |

| 45.0         | R                 | R                 | R                 | R                 | R                 | R                 | R                | R                |  |  |  |

| 15:8         |                   |                   |                   | BMXDR             | MSZ<15:8>         |                   |                  |                  |  |  |  |

| 7.0          | R                 | R                 | R                 | R                 | R                 | R                 | R                | R                |  |  |  |

| 7:0          | BMXDRMSZ<7:0>     |                   |                   |                   |                   |                   |                  |                  |  |  |  |

#### REGISTER 4-5: BMXDRMSZ: DATA RAM SIZE REGISTER

| Legend:           |                  |                           |                    |

|-------------------|------------------|---------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, re | ad as '0'          |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared      | x = Bit is unknown |

bit 31-0 **BMXDRMSZ<31:0>:** Data RAM Memory (DRM) Size bits Static value that indicates the size of the Data RAM in bytes: 0x00004000 = device has 16 KB RAM 0x00008000 = device has 32 KB RAM 0x00010000 = device has 64 KB RAM

## REGISTER 4-6: BMXPUPBA: PROGRAM FLASH (PFM) USER PROGRAM BASE ADDRESS REGISTER<sup>(1,2)</sup>

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |  |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|--|--|

| 24.24        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |  |  |

| 31:24        | _                 | _                 | _                 | —                 | _                 | —                 |                  | _                |  |  |

| 00.40        | U-0               | U-0               | U-0               | U-0               | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |

| 23:16        | _                 | —                 | _                 | —                 | BMXPUPBA<19:16>   |                   |                  |                  |  |  |

| 45.0         | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R-0               | R-0              | R-0              |  |  |

| 15:8         |                   |                   |                   | BMXPU             | PBA<15:8>         |                   |                  |                  |  |  |

| 7.0          | R-0               | R-0               | R-0               | R-0               | R-0               | R-0               | R-0              | R-0              |  |  |

| 7:0          | BMXPUPBA<7:0>     |                   |                   |                   |                   |                   |                  |                  |  |  |

| Legend:           |                  |                           |                    |

|-------------------|------------------|---------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, re | ad as '0'          |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared      | x = Bit is unknown |

bit 31-20 Unimplemented: Read as '0'

bit 19-11 BMXPUPBA<19:11>: Program Flash (PFM) User Program Base Address bits

bit 10-0 **BMXPUPBA<10:0>:** Program Flash (PFM) User Program Base Address Read-Only bits Value is always '0', which forces 2 KB increments

- **Note 1:** At Reset, the value in this register is forced to zero, which causes all of the RAM to be allocated to Kernal mode data usage.

- **2:** The value in this register must be less than or equal to BMXPFMSZ.

NOTES:

#### **TABLE 7-3**: INTERRUPT REGISTER MAP FOR PIC32MX664F064H, PIC32MX664F128H, PIC32MX675F256H, PIC32MX675F512H AND PIC32MX695F512H DEVICES (CONTINUED)

| ess                         |                                 |           |       |       |       |       |             |       |        | В                | its  |      |      |             |             |      |             |                      |            |

|-----------------------------|---------------------------------|-----------|-------|-------|-------|-------|-------------|-------|--------|------------------|------|------|------|-------------|-------------|------|-------------|----------------------|------------|

| Virtual Address<br>(BF88_#) | Register<br>Name <sup>(1)</sup> | Bit Range | 31/15 | 30/14 | 29/13 | 28/12 | 27/11       | 26/10 | 25/9   | 24/8             | 23/7 | 22/6 | 21/5 | 20/4        | 19/3        | 18/2 | 17/1        | 16/0                 | All Resets |

| 4000                        | IPC4                            | 31:16     | —     | _     | —     |       | INT4IP<2:0> |       | INT4IS | S<1:0>           | —    | -    | —    |             | OC4IP<2:0>  | •    | OC4IS       | 5<1:0>               | 0000       |

| 10D0                        | IPC4                            | 15:0      | _     | -     | _     |       | IC4IP<2:0>  |       | IC4IS  | <1:0>            | _    | _    | _    |             | T4IP<2:0>   |      | T4IS        | <1:0>                | 0000       |

| 10E0                        | IPC5                            | 31:16     | _     | -     | _     | _     | _           | _     | _      | _                | _    | _    | _    |             | OC5IP<2:0>  | •    | OC5IS       | 5<1:0>               | 0000       |

| IUEU                        | IPC5                            | 15:0      | —     | _     |       |       | IC5IP<2:0>  |       | IC5IS  | <1:0>            | —    |      |      |             | T5IP<2:0>   |      | T5IS<       | <1:0>                | 0000       |

|                             |                                 | 31:16     | _     | -     | _     |       | AD1IP<2:0>  |       | AD1IS  | 5<1:0>           | _    | _    | _    |             | CNIP<2:0>   |      | CNIS        | <1:0>                | 0000       |

| 10F0                        | IPC6                            |           |       |       |       |       |             |       |        |                  |      |      |      |             | U1IP<2:0>   |      | U1IS-       | <1:0>                |            |

| IOFU                        | IFCO                            | 15:0      | —     | —     | —     |       | I2C1IP<2:0> |       | 12C115 | S<1:0>           | —    | —    | —    | SPI3IP<2:0> |             | >    | SPI3IS      | S<1:0>               | 0000       |

|                             |                                 |           |       |       |       |       |             |       |        |                  |      |      |      | I2C3IP<2:0> |             | >    | I2C3IS<1:0> |                      |            |

|                             |                                 |           |       |       |       |       | U3IP<2:0>   |       | U3IS-  | <1:0>            |      |      |      |             |             |      |             |                      |            |

| 1100                        | IPC7                            | 31:16     | —     | -     | —     |       | SPI2IP<2:0> |       | SPI2IS | S<1:0>           | —    | —    | —    |             | CMP2IP<2:0  | >    | CMP2IS<1:0> |                      | 0000       |

| 1100                        | 11 07                           |           |       |       |       |       | I2C4IP<2:0> |       | 12C415 | S<1:0>           |      |      |      |             |             |      |             |                      |            |

|                             |                                 | 15:0      | _     | —     |       | (     | CMP1IP<2:0: | >     | CMP1   | S<1:0>           | —    |      |      |             | PMPIP<2:0>  | >    | PMPIS<1:0>  |                      | 0000       |

|                             |                                 | 31:16     | —     | —     | —     | F     | RTCCIP<2:0: | >     | RTCCI  | S<1:0>           | —    | _    |      | I           | FSCMIP<2:0  | >    | FSCM        | S<1:0>               | 0000       |

| 1110                        | IPC8                            |           |       |       |       |       |             |       |        |                  |      |      |      |             | U2IP<2:0>   |      | U2IS-       | <1:0>                |            |

|                             | 11 00                           | 15:0      | —     | -     | —     | —     | —           | —     | —      | —                | —    | —    | —    |             | SPI4IP<2:0> | >    | SPI4IS      | S<1:0>               | 0000       |

|                             |                                 |           |       |       |       |       |             |       |        |                  |      |      |      |             | I2C5IP<2:0> | >    | 12C515      | S<1:0>               |            |

| 1120                        | IPC9                            | 31:16     | —     | —     | —     |       | DMA3IP<2:0: |       | DMA3   |                  | —    | _    |      |             | DMA2IP<2:0  |      | DMA2        |                      | 0000       |

| 1120                        | 11 00                           | 15:0      | _     | —     |       |       | DMA1IP<2:0: |       | DMA1   |                  | —    | _    |      |             | DMA0IP<2:0  |      | DMA0I       |                      | 0000       |

| 1130                        | IPC10                           | 31:16     | —     | —     | —     |       | MA7IP<2:0>  |       |        | <1:0> <b>(2)</b> | —    | _    |      |             | MA6IP<2:0>  |      | DMA6IS      |                      | 0000       |

| 1130                        | 11 010                          | 15:0      | _     | —     |       | D     | MA5IP<2:0>  | (2)   | DMA5IS | <1:0> <b>(2)</b> | —    | _    |      | D           | MA4IP<2:0>  | (2)  | DMA4IS      | <1:0> <sup>(2)</sup> | 0000       |

| 1140                        | IPC11                           | 31:16     | —     | —     | _     | _     | —           | —     | —      | —                | —    | _    | _    | —           | _           | —    | —           | —                    | 0000       |

|                             |                                 | 15:0      | —     | —     | —     |       | USBIP<2:0>  |       | USBIS  |                  | —    | —    | —    |             | FCEIP<2:0>  |      | FCEIS       |                      | 0000       |

| 1150                        | IPC12                           | 31:16     | —     | —     | —     |       | U5IP<2:0>   |       | U5IS-  | <1:0>            | —    | _    | _    |             | U6IP<2:0>   |      | U6IS-       | <1:0>                | 0000       |

| 1100                        | 11 012                          | 15:0      | _     | —     | —     |       | U4IP<2:0>   |       | U4IS-  | <1:0>            | —    | _    | —    |             | ETHIP<2:0>  |      | ETHIS       | i<1:0>               | 0000       |

Legend: x = unknown value on Reset; ---- = unimplemented, read as '0'. Reset values are shown in hexadecimal.

Except where noted, all registers in this table have corresponding CLR, SET and INV registers at their virtual addresses, plus offsets of 0x4, 0x8 and 0xC respectively. See Section 12.1.1 "CLR, SET and INV Note 1: Registers" for more information. These bits are not available on PIC32MX664 devices. This register does not have associated CLR, SET, and INV registers.

2:

3:

NOTES:

## TABLE 23-1: ADC REGISTER MAP (CONTINUED)

| ess                         |                  |               |       |                                                   |       |       |       |       |        | Bi          | ts        |          |      |      |      |      |      |      |            |

|-----------------------------|------------------|---------------|-------|---------------------------------------------------|-------|-------|-------|-------|--------|-------------|-----------|----------|------|------|------|------|------|------|------------|

| Virtual Address<br>(BF80_#) | Register<br>Name | Bit Range     | 31/15 | 30/14                                             | 29/13 | 28/12 | 27/11 | 26/10 | 25/9   | 24/8        | 23/7      | 22/6     | 21/5 | 20/4 | 19/3 | 18/2 | 17/1 | 16/0 | All Resets |

| 9120                        | ADC1BUFB         | 31:16<br>15:0 |       | ADC Result Word B (ADC1BUFB<31:0>)                |       |       |       |       |        |             |           |          |      |      |      |      |      |      |            |

| 9130                        | ADC1BUFC         | 31:16<br>15:0 |       | ADC Result Word C (ADC1BUFC<31:0>) 0000 0000      |       |       |       |       |        |             |           |          |      |      |      |      |      |      |            |

| 9140                        | ADC1BUFD         | 31:16<br>15:0 |       |                                                   |       |       |       |       | ADC Re | sult Word D | (ADC1BUFE | 0<31:0>) |      |      |      |      |      |      | 0000       |

| 9150                        | ADC1BUFE         | 31:16<br>15:0 |       | ADC Result Word E (ADC1BUFE<31:0>) 0000 0000 0000 |       |       |       |       |        |             |           |          |      |      |      |      |      |      |            |

| 9160                        | ADC1BUFF         | 31:16<br>15:0 |       |                                                   |       |       |       |       | ADC Re | sult Word F | (ADC1BUFF | -<31:0>) |      |      |      |      |      |      | 0000       |

= unimplemented, read as '0'. Reset values are shown in hexadecimal. Legend: x = unknown value on Reset

This register has corresponding CLR, SET and INV registers at their virtual addresses, plus offsets of 0x4, 0x8 and 0xC, respectively. See Section 12.1.1 "CLR, SET and INV Registers" for more information. Note 1:

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |  |  |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|--|--|--|

| 04.04        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |  |  |  |

| 31:24        | —                 | —                 | —                 | _                 | —                 | —                 | —                | —                |  |  |  |

| 00.40        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |  |  |  |

| 23:16        | —                 | —                 | —                 | _                 | —                 | —                 | —                | —                |  |  |  |

| 45.0         | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |  |

| 15:8         | CSSL15            | CSSL14            | CSSL13            | CSSL12            | CSSL11            | CSSL10            | CSSL9            | CSSL8            |  |  |  |

| 7.0          | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |  |

| 7:0          | CSSL7             | CSSL6             | CSSL5             | CSSL4             | CSSL3             | CSSL2             | CSSL1            | CSSL0            |  |  |  |

## REGISTER 23-5: AD1CSSL: ADC INPUT SCAN SELECT REGISTER

## Legend:

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, re | ead as '0'         |

|-------------------|------------------|---------------------------|--------------------|

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared      | x = Bit is unknown |

bit 31-16 Unimplemented: Read as '0'

1 = Select ANx for input scan

0 =Skip ANx for input scan

Note 1: CSSL = ANx, where 'x' = 0-15.

bit 15-0 CSSL<15:0>: ADC Input Pin Scan Selection bits<sup>(1)</sup>

#### REGISTER 25-28: EMAC1MAXF: ETHERNET CONTROLLER MAC MAXIMUM FRAME LENGTH REGISTER

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3     | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

|--------------|-------------------|-------------------|-------------------|-------------------|-----------------------|-------------------|------------------|------------------|

| 31:24        | U-0               | U-0               | U-0               | U-0               | U-0                   | U-0               | U-0              | U-0              |

| 31.24        | —                 | —                 | —                 | —                 | —                     | —                 | _                | —                |

| 00.40        | U-0               | U-0               | U-0               | U-0               | U-0                   | U-0               | U-0              | U-0              |

| 23:16        | —                 | —                 | —                 | —                 | —                     | —                 | _                | —                |

| 15.0         | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0                 | R/W-1             | R/W-0            | R/W-1            |

| 15:8         |                   |                   |                   | MACMAXF<          | :15:8> <sup>(1)</sup> |                   |                  |                  |

| 7.0          | R/W-1             | R/W-1             | R/W-1             | R/W-0             | R/W-1                 | R/W-1             | R/W-1            | R/W-0            |

| 7:0          |                   |                   |                   | MACMAXF           | <7:0> <sup>(1)</sup>  |                   |                  |                  |

| Legend:           |                  |                          |                    |

|-------------------|------------------|--------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, r | ead as '0'         |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared     | x = Bit is unknown |

#### bit 31-16 Unimplemented: Read as '0'

bit 15-0 MACMAXF<15:0>: Maximum Frame Length bits<sup>(1)</sup>

These bits reset to 0x05EE, which represents a maximum receive frame of 1518 octets. An untagged maximum size Ethernet frame is 1518 octets. A tagged frame adds four octets for a total of 1522 octets. If a shorter/longer maximum length restriction is desired, program this 16-bit field.

**Note 1:** If a proprietary header is allowed, this bit should be adjusted accordingly. For example, if 4-byte headers are prepended to frames, MACMAXF could be set to 1527 octets. This would allow the maximum VLAN tagged frame plus the 4-byte header.

**Note:** Both 16-bit and 32-bit accesses are allowed to these registers (including the SET, CLR and INV registers). 8-bit accesses are not allowed and are ignored by the hardware.

| Bit<br>Range | Bit<br>31/23/15/7                                   | Bit<br>30/22/14/6         | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3    | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |  |

|--------------|-----------------------------------------------------|---------------------------|-------------------|-------------------|----------------------|-------------------|------------------|------------------|--|--|

| 04-04        | R                                                   | R                         | R                 | R                 | R                    | R                 | R                | R                |  |  |

| 31:24        | VER<3:0> <sup>(1)</sup> DEVID<27:24> <sup>(1)</sup> |                           |                   |                   |                      |                   |                  |                  |  |  |

| 00.40        | R                                                   | R                         | R                 | R                 | R                    | R                 | R                | R                |  |  |

| 23:16        |                                                     |                           |                   | DEVID<2           | 3:16> <sup>(1)</sup> |                   |                  |                  |  |  |

| 45.0         | R                                                   | R                         | R                 | R                 | R                    | R                 | R                | R                |  |  |

| 15:8         |                                                     |                           |                   | DEVID<1           | 5:8> <sup>(1)</sup>  |                   |                  |                  |  |  |

| 7.0          | R                                                   | R                         | R                 | R                 | R                    | R                 | R                | R                |  |  |

| 7:0          |                                                     | DEVID<7:0> <sup>(1)</sup> |                   |                   |                      |                   |                  |                  |  |  |

#### REGISTER 29-5: DEVID: DEVICE AND REVISION ID REGISTER

## Legend:

| Legena.           |                  |                          |                    |

|-------------------|------------------|--------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, r | read as '0'        |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared     | x = Bit is unknown |

bit 31-28 VER<3:0>: Revision Identifier bits<sup>(1)</sup>

bit 27-0 DEVID<27:0>: Device ID bits<sup>(1)</sup>

Note 1: See the "PIC32 Flash Programming Specification" (DS60001145) for a list of Revision and Device ID values.

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|

| 21.24        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 31:24        |                   | _                 | _                 |                   |                   |                   |                  | —                |

| 00.40        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 23:16        | _                 | _                 | _                 | _                 | _                 | _                 | _                | —                |

| 45.0         | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 15:8         | _                 | _                 | _                 | _                 | _                 | _                 | _                | —                |

| 7.0          | U-0               | U-0               | U-0               | U-0               | R/W-1             | R/W-0             | U-0              | R/W-0            |

| 7:0          | _                 | _                 | _                 | _                 | JTAGEN            | TROEN             | _                | TDOEN            |

### REGISTER 29-6: DDPCON: DEBUG DATA PORT CONTROL REGISTER

| Legend:           |                  |                      |                    |

|-------------------|------------------|----------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bi | t, read as '0'     |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared | x = Bit is unknown |

#### bit 31-4 Unimplemented: Read as '0'

- bit 3 JTAGEN: JTAG Port Enable bit

- 1 = Enable the JTAG port

- 0 = Disable the JTAG port

- bit 2 **TROEN:** Trace Output Enable bit

- 1 = Enable the trace port

- 0 = Disable the trace port

- bit 1 Unimplemented: Read as '0'

- bit 0 TDOEN: TDO Enable for 2-Wire JTAG

- 1 = 2-wire JTAG protocol uses TDO

- 0 = 2-wire JTAG protocol does not use TDO

## **30.0 INSTRUCTION SET**

The PIC32MX5XX/6XX/7XX family instruction set complies with the MIPS32 Release 2 instruction set architecture. The PIC32 device family does not support the following features:

- Core Extend instructions

- Coprocessor 1 instructions

- Coprocessor 2 instructions

Note: Refer to "MIPS32<sup>®</sup> Architecture for Programmers Volume II: The MIPS32<sup>®</sup> Instruction Set" at www.imgtec.com for more information.

NOTES:

## 31.11 Demonstration/Development Boards, Evaluation Kits, and Starter Kits

A wide variety of demonstration, development and evaluation boards for various PIC MCUs and dsPIC DSCs allows quick application development on fully functional systems. Most boards include prototyping areas for adding custom circuitry and provide application firmware and source code for examination and modification.

The boards support a variety of features, including LEDs, temperature sensors, switches, speakers, RS-232 interfaces, LCD displays, potentiometers and additional EEPROM memory.

The demonstration and development boards can be used in teaching environments, for prototyping custom circuits and for learning about various microcontroller applications.

In addition to the PICDEM<sup>™</sup> and dsPICDEM<sup>™</sup> demonstration/development board series of circuits, Microchip has a line of evaluation kits and demonstration software for analog filter design, KEELOQ<sup>®</sup> security ICs, CAN, IrDA<sup>®</sup>, PowerSmart battery management, SEEVAL<sup>®</sup> evaluation system, Sigma-Delta ADC, flow rate sensing, plus many more.

Also available are starter kits that contain everything needed to experience the specified device. This usually includes a single application and debug capability, all on one board.

Check the Microchip web page (www.microchip.com) for the complete list of demonstration, development and evaluation kits.

## 31.12 Third-Party Development Tools

Microchip also offers a great collection of tools from third-party vendors. These tools are carefully selected to offer good value and unique functionality.

- Device Programmers and Gang Programmers from companies, such as SoftLog and CCS

- Software Tools from companies, such as Gimpel and Trace Systems

- Protocol Analyzers from companies, such as Saleae and Total Phase

- Demonstration Boards from companies, such as MikroElektronika, Digilent<sup>®</sup> and Olimex

- Embedded Ethernet Solutions from companies, such as EZ Web Lynx, WIZnet and IPLogika<sup>®</sup>

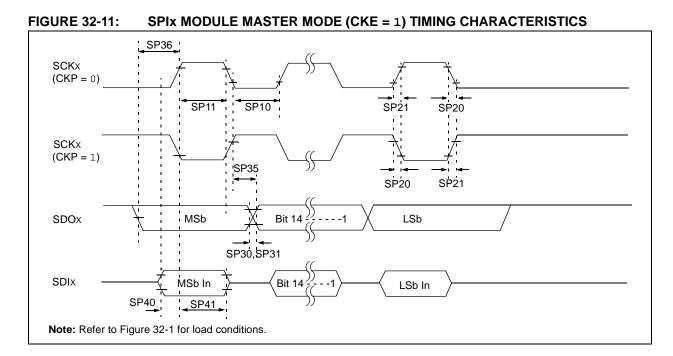

#### TABLE 32-29: SPIX MODULE MASTER MODE (CKE = 1) TIMING REQUIREMENTS

| AC CHARACTERISTICS |                      | $\begin{array}{l} \mbox{Standard Operating Conditions: 2.3V to 3.6V} \\ \mbox{(unless otherwise stated)} \\ \mbox{Operating temperature} & -40^{\circ}C \leq TA \leq +85^{\circ}C \mbox{ for Industrial} \\ & -40^{\circ}C \leq TA \leq +105^{\circ}C \mbox{ for V-Temp} \end{array}$ |        |                     |      |       |                    |

|--------------------|----------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------|---------------------|------|-------|--------------------|

| Param.<br>No.      | Symbol               | Characteristics <sup>(1)</sup>                                                                                                                                                                                                                                                        | Min.   | Тур. <sup>(2)</sup> | Max. | Units | Conditions         |

| SP10               | TscL                 | SCKx Output Low Time <sup>(3)</sup>                                                                                                                                                                                                                                                   | Tsck/2 | —                   | _    | ns    | —                  |

| SP11               | TscH                 | SCKx Output High Time <sup>(3)</sup>                                                                                                                                                                                                                                                  | Tsck/2 | —                   | _    | ns    | —                  |

| SP20               | TscF                 | SCKx Output Fall Time <sup>(4)</sup>                                                                                                                                                                                                                                                  | _      | —                   | —    | ns    | See parameter DO32 |

| SP21               | TscR                 | SCKx Output Rise Time <sup>(4)</sup>                                                                                                                                                                                                                                                  | _      | —                   | _    | ns    | See parameter DO31 |

| SP30               | TDOF                 | SDOx Data Output Fall Time <sup>(4)</sup>                                                                                                                                                                                                                                             | _      | —                   |      | ns    | See parameter DO32 |

| SP31               | TDOR                 | SDOx Data Output Rise Time <sup>(4)</sup>                                                                                                                                                                                                                                             | _      | —                   | —    | ns    | See parameter DO31 |

| SP35               | TscH2doV,            | SDOx Data Output Valid after                                                                                                                                                                                                                                                          | _      | —                   | 15   | ns    | VDD > 2.7V         |

|                    | TscL2doV             | SCKx Edge                                                                                                                                                                                                                                                                             | —      | —                   | 20   | ns    | Vdd < 2.7V         |

| SP36               | TDOV2SC,<br>TDOV2SCL | SDOx Data Output Setup to<br>First SCKx Edge                                                                                                                                                                                                                                          | 15     | —                   | _    | ns    | —                  |

| SP40               | TDIV2scH,            | Setup Time of SDIx Data Input to                                                                                                                                                                                                                                                      | 15     | —                   |      | ns    | VDD > 2.7V         |

|                    | TDIV2SCL SCKx Edge   |                                                                                                                                                                                                                                                                                       | 20     | —                   | —    | ns    | Vdd < 2.7V         |

| SP41               | SP41 TscH2DIL,       | Hold Time of SDIx Data Input                                                                                                                                                                                                                                                          | 15     | —                   |      | ns    | VDD > 2.7V         |

|                    | TscL2DIL             | to SCKx Edge                                                                                                                                                                                                                                                                          | 20     | —                   | _    | ns    | VDD < 2.7V         |

**Note 1:** These parameters are characterized, but not tested in manufacturing.

2: Data in "Typical" column is at 3.3V, 25°C unless otherwise stated. Parameters are for design guidance only and are not tested.

- **3:** The minimum clock period for SCKx is 40 ns. Therefore, the clock generated in Master mode must not violate this specification.

- 4: Assumes 50 pF load on all SPIx pins.

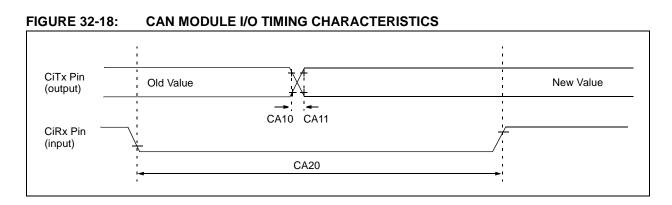

#### TABLE 32-34: CAN MODULE I/O TIMING REQUIREMENTS

| AC CHARACTERISTICS |        |                                              | (unless                                     | rd Operat<br>otherwis<br>g tempera | se stated | <b>)</b><br>40°C ≤ Ta | 2.3V to 3.6V<br>≤ +85°C for Industrial<br>≤ +105°C for V-Temp |

|--------------------|--------|----------------------------------------------|---------------------------------------------|------------------------------------|-----------|-----------------------|---------------------------------------------------------------|

| Param<br>No.       | Symbol | Characteristic <sup>(1)</sup>                | Min Typ <sup>(2)</sup> Max Units Conditions |                                    |           |                       | Conditions                                                    |

| CA10               | TioF   | Port Output Fall Time                        | _                                           | —                                  | _         | ns                    | See parameter DO32                                            |

| CA11               | TioR   | Port Output Rise Time                        | _                                           | —                                  | _         | ns                    | See parameter DO31                                            |

| CA20               | Tcwf   | Pulse Width to Trigger<br>CAN Wake-up Filter | 700                                         |                                    |           | ns                    | _                                                             |

Note 1: These parameters are characterized but not tested in manufacturing.

2: Data in "Typ" column is at 3.3V, 25°C unless otherwise stated. Parameters are for design guidance only and are not tested.

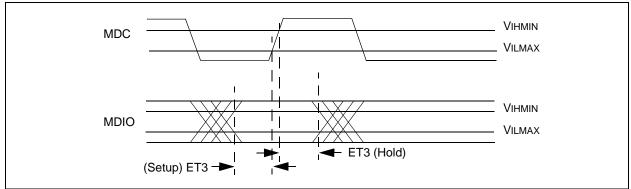

### TABLE 32-35: ETHERNET MODULE SPECIFICATIONS

| AC CHARACTERISTICS |                                     | $\begin{tabular}{lllllllllllllllllllllllllllllllllll$ |         |      |       |                  |  |

|--------------------|-------------------------------------|-------------------------------------------------------|---------|------|-------|------------------|--|

| Param.<br>No.      | Characteristic                      | Min.                                                  | Typical | Max. | Units | Conditions       |  |

| MIIM Tin           | ning Requirements                   |                                                       |         |      |       |                  |  |

| ET1                | MDC Duty Cycle                      | 40                                                    |         | 60   | %     | —                |  |

| ET2                | MDC Period                          | 400                                                   | —       | —    | ns    | —                |  |

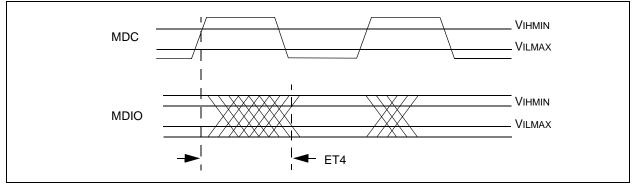

| ET3                | MDIO Output Setup and Hold          | 10                                                    | —       | 10   | ns    | See Figure 32-19 |  |

| ET4                | MDIO Input Setup and Hold           | 0                                                     | —       | 300  | ns    | See Figure 32-20 |  |

| MII Timi           | ng Requirements                     |                                                       |         |      |       |                  |  |

| ET5                | TX Clock Frequency                  | —                                                     | 25      | _    | MHz   | —                |  |

| ET6                | TX Clock Duty Cycle                 | 35                                                    | —       | 65   | %     | —                |  |

| ET7                | ETXDx, ETEN, ETXERR Output Delay    | 0                                                     | —       | 25   | ns    | See Figure 32-21 |  |

| ET8                | RX Clock Frequency                  | _                                                     | 25      |      | MHz   | —                |  |

| ET9                | RX Clock Duty Cycle                 | 35                                                    | —       | 65   | %     | —                |  |

| ET10               | ERXDx, ERXDV, ERXERR Setup and Hold | 10                                                    | —       | 30   | ns    | See Figure 32-22 |  |

| RMII Tin           | ning Requirements                   |                                                       |         |      |       |                  |  |

| ET11               | Reference Clock Frequency           | —                                                     | 50      | _    | MHz   | —                |  |

| ET12               | Reference Clock Duty Cycle          | 35                                                    |         | 65   | %     | —                |  |

| ET13               | ETXDx, ETEN, Setup and Hold         | 2                                                     | —       | 4    | ns    | —                |  |

| ET14               | ERXDx, ERXDV, ERXERR Setup and Hold | 2                                                     | —       | 4    | ns    | —                |  |

**Note 1:** The Ethernet module is functional at VBORMIN < VDD < 2.9V, but with degraded performance. Unless otherwise stated, module functionality is tested, but not characterized.

#### FIGURE 32-19: MDIO SOURCED BY THE PIC32 DEVICE

### FIGURE 32-20: MDIO SOURCED BY THE PHY

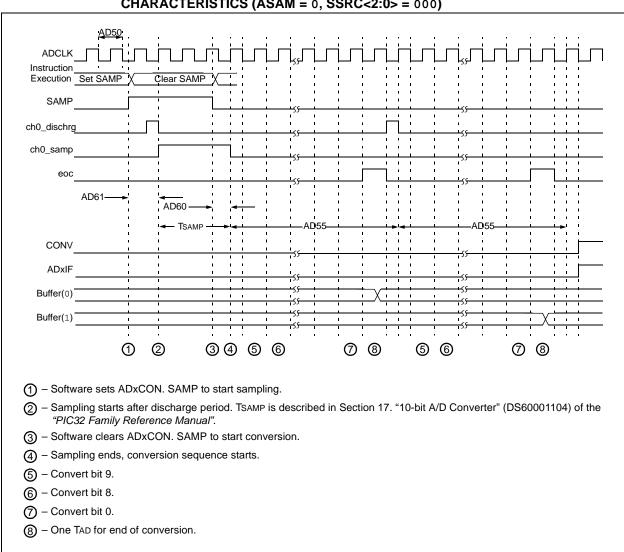

## FIGURE 32-23: ANALOG-TO-DIGITAL CONVERSION (10-BIT MODE) TIMING CHARACTERISTICS (ASAM = 0, SSRC<2:0> = 000)

## 34.1 Package Marking Information (Continued)

## 121-Lead TFBGA (10x10x1.1 mm)

## 124-Lead VTLA (9x9x0.9 mm)

### Example

| Lanand | VV V                                          | Customer eneritie information                                                                       |  |  |

|--------|-----------------------------------------------|-----------------------------------------------------------------------------------------------------|--|--|

| Legena | XXX                                           | Customer-specific information                                                                       |  |  |

|        | Y                                             | Year code (last digit of calendar year)                                                             |  |  |

|        | YY                                            | Year code (last 2 digits of calendar year)                                                          |  |  |

|        | WW Week code (week of January 1 is week '01') |                                                                                                     |  |  |

|        | NNN                                           | Alphanumeric traceability code                                                                      |  |  |

|        |                                               | Pb-free JEDEC designator for Matte Tin (Sn)                                                         |  |  |

|        | *                                             | This package is Pb-free. The Pb-free JEDEC designator (e3)                                          |  |  |

|        |                                               | can be found on the outer packaging for this package.                                               |  |  |

| Note:  | In the eve                                    | nt the full Microchip part number cannot be marked on one line, it will                             |  |  |

|        |                                               | d over to the next line, thus limiting the number of available s for customer-specific information. |  |  |

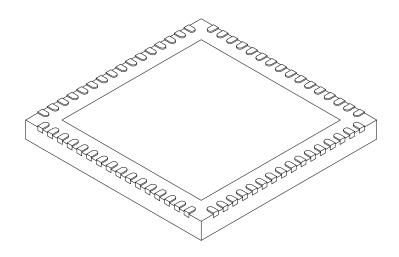

## 64-Lead Plastic Quad Flat, No Lead Package (MR) – 9x9x0.9 mm Body [QFN] With 7.15 x 7.15 Exposed Pad [QFN]

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

|                        | Units    |          | MILLIMETERS |      |  |  |

|------------------------|----------|----------|-------------|------|--|--|

| Dimensio               | n Limits | MIN      | NOM         | MAX  |  |  |

| Number of Pins         | N        |          | 64          |      |  |  |

| Pitch                  | е        |          | 0.50 BSC    |      |  |  |

| Overall Height         | A        | 0.80     | 0.90        | 1.00 |  |  |

| Standoff               | A1       | 0.00     | 0.02        | 0.05 |  |  |

| Contact Thickness      | A3       | 0.20 REF |             |      |  |  |

| Overall Width          | E        | 9.00 BSC |             |      |  |  |

| Exposed Pad Width      | E2       | 7.05     | 7.15        | 7.50 |  |  |

| Overall Length         | D        | 9.00 BSC |             |      |  |  |

| Exposed Pad Length     | D2       | 7.05     | 7.15        | 7.50 |  |  |

| Contact Width          | b        | 0.18     | 0.25        | 0.30 |  |  |

| Contact Length         | L        | 0.30     | 0.40        | 0.50 |  |  |

| Contact-to-Exposed Pad | K        | 0.20     | -           | -    |  |  |

#### Notes:

- 1. Pin 1 visual index feature may vary, but must be located within the hatched area.

- 2. Package is saw singulated.

- 3. Dimensioning and tolerancing per ASME Y14.5M.

- BSC: Basic Dimension. Theoretically exact value shown without tolerances.

REF: Reference Dimension, usually without tolerance, for information purposes only.

Microchip Technology Drawing C04-149C Sheet 2 of 2

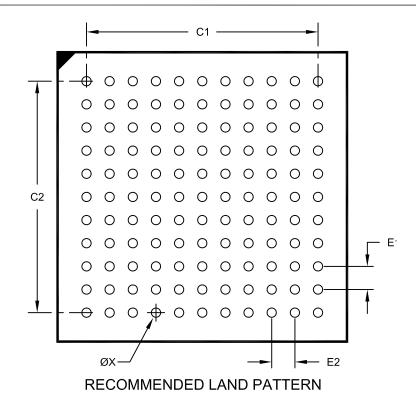

## 121-Lead Plastic Thin Profile Ball Grid Array (BG) - 10x10x1.10 mm Body [TFBGA--Formerly XBGA]

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

|                             | Units            |  | <b>ILLIMETER</b> | S    |

|-----------------------------|------------------|--|------------------|------|

| Dimensior                   | Dimension Limits |  | NOM              | MAX  |

| Contact Pitch               | E1               |  | 0.80 BSC         |      |

| Contact Pitch               | E2               |  | 0.80 BSC         |      |

| Contact Pad Spacing         | C1               |  | 8.00             |      |

| Contact Pad Spacing         | C2               |  | 8.00             |      |

| Contact Pad Diameter (X121) | X                |  |                  | 0.32 |

Notes:

1. Dimensioning and tolerancing per ASME Y14.5M

BSC: Basic Dimension. Theoretically exact value shown without tolerances.

Microchip Technology Drawing No. C04-2148 Rev D

## **PRODUCT IDENTIFICATION SYSTEM**

To order or obtain information, e.g., on pricing or delivery, refer to the factory or the listed sales office.

| Program Memory Size<br>Pin Count<br>Tape and Reel Flag (if<br>Speed (see Note 1)<br>Temperature Range<br>Package | 32-bit RISC MCU,<br>256 KB program memory.                                                                                                                                                                                                                                                                                                                          |

|------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Flash Memory Fan                                                                                                 | nily                                                                                                                                                                                                                                                                                                                                                                |

| Architecture                                                                                                     | MX = 32-bit RISC MCU core                                                                                                                                                                                                                                                                                                                                           |

| Product Groups                                                                                                   | 5XX = General purpose microcontroller family<br>6XX = General purpose microcontroller family<br>7XX = General purpose microcontroller family                                                                                                                                                                                                                        |

| Flash Memory Family                                                                                              | F = Flash program memory                                                                                                                                                                                                                                                                                                                                            |

| Program Memory Size                                                                                              | <b>64 = 64K</b><br><b>128 = 128K</b><br>256 = 256K<br>512 = 512K                                                                                                                                                                                                                                                                                                    |

| Pin Count                                                                                                        | H = 64-pin<br>L = 100-pin, 121-pin, 124-pin                                                                                                                                                                                                                                                                                                                         |

| Speed (see Note 1)                                                                                               | Blank or 80 = 80 MHz                                                                                                                                                                                                                                                                                                                                                |

| Temperature Range                                                                                                | I = -40°C to +85°C (Industrial)<br>V = -40°C to +105°C (V-Temp)                                                                                                                                                                                                                                                                                                     |

| Package                                                                                                          | PT = 64-Lead (10x10x1 mm) TQFP (Thin Quad Flatpack)<br>PT = 100-Lead (12x12x1 mm) TQFP (Thin Quad Flatpack)<br>PF = 100-Lead (14x14x1 mm) TQFP (Thin Quad Flatpack)<br>MR = 64-Lead (9x9x0.9 mm) QFN (Plastic Quad Flat)<br>BG = 121-Lead (10x10x1.1 mm) TFBGA (Plastic Thin Profile Ball Grid Array)<br>TL = 124-Lead (9x9x0.9 mm) VTLA (Very Thin Leadless Array) |

| Pattern                                                                                                          | Three-digit QTP, SQTP, Code or Special Requirements (blank otherwise)<br>ES = Engineering Sample                                                                                                                                                                                                                                                                    |

| Note 1: This opt                                                                                                 | ion is not available for PIC32MX534/564/664/764 devices.                                                                                                                                                                                                                                                                                                            |