Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

## Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Detuns                     |                                                                                   |

|----------------------------|-----------------------------------------------------------------------------------|

| Product Status             | Active                                                                            |

| Core Processor             | MIPS32® M4K™                                                                      |

| Core Size                  | 32-Bit Single-Core                                                                |

| Speed                      | 80MHz                                                                             |

| Connectivity               | Ethernet, I <sup>2</sup> C, SPI, UART/USART, USB OTG                              |

| Peripherals                | Brown-out Detect/Reset, DMA, POR, PWM, WDT                                        |

| Number of I/O              | 53                                                                                |

| Program Memory Size        | 512KB (512K x 8)                                                                  |

| Program Memory Type        | FLASH                                                                             |

| EEPROM Size                |                                                                                   |

| RAM Size                   | 128K x 8                                                                          |

| Voltage - Supply (Vcc/Vdd) | 2.3V ~ 3.6V                                                                       |

| Data Converters            | A/D 16x10b                                                                        |

| Oscillator Type            | Internal                                                                          |

| Operating Temperature      | -40°C ~ 105°C (TA)                                                                |

| Mounting Type              | Surface Mount                                                                     |

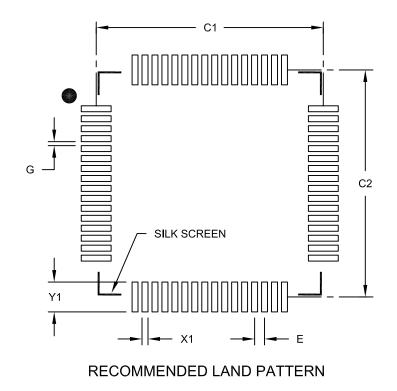

| Package / Case             | 64-TQFP                                                                           |

| Supplier Device Package    | 64-TQFP (10x10)                                                                   |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic32mx695f512ht-80v-pt |

|                            |                                                                                   |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

NOTES:

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|

| 04.04        | R                 | R                 | R                 | R                 | R                 | R                 | R                | R                |

| 31:24        |                   |                   | BMXDRMSZ<31:24>   |                   |                   |                   |                  |                  |

| 00.40        | R                 | R                 | R                 | R                 | R                 | R                 | R                | R                |

| 23:16        |                   |                   |                   | BMXDRM            | XDRMSZ<23:16>     |                   |                  |                  |

| 45.0         | R                 | R                 | R                 | R                 | R                 | R                 | R                | R                |

| 15:8         |                   |                   |                   | BMXDR             | MSZ<15:8>         |                   | R F              |                  |

| 7.0          | R                 | R                 | R                 | R                 | R                 | R                 | R                | R                |

| 7:0          |                   |                   |                   | BMXDR             | MSZ<7:0>          |                   |                  |                  |

## REGISTER 4-5: BMXDRMSZ: DATA RAM SIZE REGISTER

| Legend:           |                  |                           |                    |

|-------------------|------------------|---------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, re | ad as '0'          |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared      | x = Bit is unknown |

bit 31-0 **BMXDRMSZ<31:0>:** Data RAM Memory (DRM) Size bits Static value that indicates the size of the Data RAM in bytes: 0x00004000 = device has 16 KB RAM 0x00008000 = device has 32 KB RAM 0x00010000 = device has 64 KB RAM

# REGISTER 4-6: BMXPUPBA: PROGRAM FLASH (PFM) USER PROGRAM BASE ADDRESS REGISTER<sup>(1,2)</sup>

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |  |  |  |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|--|--|--|--|

| 24.24        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |  |  |  |  |

| 31:24        | -                 | _                 | _                 | —                 | _                 | —                 |                  | _                |  |  |  |  |

| 00.40        | U-0               | U-0               | U-0               | U-0               | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |  |  |

| 23:16        | _                 | —                 | _                 | —                 | BMXPUPBA<19:16>   |                   |                  |                  |  |  |  |  |

| 45.0         | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R-0               | R-0              | R-0              |  |  |  |  |

| 15:8         |                   | BMXPUPBA<15:8>    |                   |                   |                   |                   |                  |                  |  |  |  |  |

| 7.0          | R-0               | R-0               | R-0               | R-0               | R-0               | R-0               | R-0              | R-0              |  |  |  |  |

| 7:0          |                   |                   |                   | BMXPU             | PBA<7:0>          |                   |                  |                  |  |  |  |  |

| Legend:           |                  |                                    |                    |  |  |  |

|-------------------|------------------|------------------------------------|--------------------|--|--|--|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read as '0' |                    |  |  |  |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared               | x = Bit is unknown |  |  |  |

bit 31-20 Unimplemented: Read as '0'

bit 19-11 BMXPUPBA<19:11>: Program Flash (PFM) User Program Base Address bits

bit 10-0 **BMXPUPBA<10:0>:** Program Flash (PFM) User Program Base Address Read-Only bits Value is always '0', which forces 2 KB increments

- **Note 1:** At Reset, the value in this register is forced to zero, which causes all of the RAM to be allocated to Kernal mode data usage.

- **2:** The value in this register must be less than or equal to BMXPFMSZ.

| TABLE 7-1: INTERRUPT IRQ                                                            | VECTOR | AND BIT | IT LOCATION (CONTINUED) |          |                 |              |  |  |  |

|-------------------------------------------------------------------------------------|--------|---------|-------------------------|----------|-----------------|--------------|--|--|--|

| Interrupt Source <sup>(1)</sup>                                                     | IRQ    | Vector  |                         | Interru  | pt Bit Location |              |  |  |  |

| interrupt Source ?                                                                  | Number | Number  | Flag                    | Enable   | Priority        | Sub-Priority |  |  |  |

| AD1 – ADC1 Convert Done                                                             | 33     | 27      | IFS1<1>                 | IEC1<1>  | IPC6<28:26>     | IPC6<25:24>  |  |  |  |

| PMP – Parallel Master Port                                                          | 34     | 28      | IFS1<2>                 | IEC1<2>  | IPC7<4:2>       | IPC7<1:0>    |  |  |  |

| CMP1 – Comparator Interrupt                                                         | 35     | 29      | IFS1<3>                 | IEC1<3>  | IPC7<12:10>     | IPC7<9:8>    |  |  |  |

| CMP2 – Comparator Interrupt                                                         | 36     | 30      | IFS1<4>                 | IEC1<4>  | IPC7<20:18>     | IPC7<17:16>  |  |  |  |

| U2E – UART2 Error<br>SPI2E – SPI2 Fault<br>I2C4B – I2C4 Bus Collision Event         | 37     | 31      | IFS1<5>                 | IEC1<5>  | IPC7<28:26>     | IPC7<25:24>  |  |  |  |

| U2RX – UART2 Receiver<br>SPI2RX – SPI2 Receive Done<br>I2C4S – I2C4 Slave Event     | 38     | 31      | IFS1<6>                 | IEC1<6>  | IPC7<28:26>     | IPC7<25:24>  |  |  |  |

| U2TX – UART2 Transmitter<br>SPI2TX – SPI2 Transfer Done<br>IC4M – I2C4 Master Event | 39     | 31      | IFS1<7>                 | IEC1<7>  | IPC7<28:26>     | IPC7<25:24>  |  |  |  |

| U3E – UART3 Error<br>SPI4E – SPI4 Fault<br>I2C5B – I2C5 Bus Collision Event         | 40     | 32      | IFS1<8>                 | IEC1<8>  | IPC8<4:2>       | IPC8<1:0>    |  |  |  |

| U3RX – UART3 Receiver<br>SPI4RX – SPI4 Receive Done<br>I2C5S – I2C5 Slave Event     | 41     | 32      | IFS1<9>                 | IEC1<9>  | IPC8<4:2>       | IPC8<1:0>    |  |  |  |

| U3TX – UART3 Transmitter<br>SPI4TX – SPI4 Transfer Done<br>IC5M – I2C5 Master Event | 42     | 32      | IFS1<10>                | IEC1<10> | IPC8<4:2>       | IPC8<1:0>    |  |  |  |

| I2C2B – I2C2 Bus Collision Event                                                    | 43     | 33      | IFS1<11>                | IEC1<11> | IPC8<12:10>     | IPC8<9:8>    |  |  |  |

| I2C2S – I2C2 Slave Event                                                            | 44     | 33      | IFS1<12>                | IEC1<12> | IPC8<12:10>     | IPC8<9:8>    |  |  |  |

| I2C2M – I2C2 Master Event                                                           | 45     | 33      | IFS1<13>                | IEC1<13> | IPC8<12:10>     | IPC8<9:8>    |  |  |  |

| FSCM – Fail-Safe Clock Monitor                                                      | 46     | 34      | IFS1<14>                | IEC1<14> | IPC8<20:18>     | IPC8<17:16>  |  |  |  |

| RTCC – Real-Time Clock and<br>Calendar                                              | 47     | 35      | IFS1<15>                | IEC1<15> | IPC8<28:26>     | IPC8<25:24>  |  |  |  |

| DMA0 – DMA Channel 0                                                                | 48     | 36      | IFS1<16>                | IEC1<16> | IPC9<4:2>       | IPC9<1:0>    |  |  |  |

| DMA1 – DMA Channel 1                                                                | 49     | 37      | IFS1<17>                | IEC1<17> | IPC9<12:10>     | IPC9<9:8>    |  |  |  |

| DMA2 – DMA Channel 2                                                                | 50     | 38      | IFS1<18>                | IEC1<18> | IPC9<20:18>     | IPC9<17:16>  |  |  |  |

| DMA3 – DMA Channel 3                                                                | 51     | 39      | IFS1<19>                | IEC1<19> | IPC9<28:26>     | IPC9<25:24>  |  |  |  |

| DMA4 – DMA Channel 4                                                                | 52     | 40      | IFS1<20>                | IEC1<20> | IPC10<4:2>      | IPC10<1:0>   |  |  |  |

| DMA5 – DMA Channel 5                                                                | 53     | 41      | IFS1<21>                | IEC1<21> | IPC10<12:10>    | IPC10<9:8>   |  |  |  |

| DMA6 – DMA Channel 6                                                                | 54     | 42      | IFS1<22>                | IEC1<22> | IPC10<20:18>    | IPC10<17:16> |  |  |  |

| DMA7 – DMA Channel 7                                                                | 55     | 43      | IFS1<23>                | IEC1<23> | IPC10<28:26>    | IPC10<25:24> |  |  |  |

| FCE – Flash Control Event                                                           | 56     | 44      | IFS1<24>                | IEC1<24> | IPC11<4:2>      | IPC11<1:0>   |  |  |  |

| USB – USB Interrupt                                                                 | 57     | 45      | IFS1<25>                | IEC1<25> | IPC11<12:10>    | IPC11<9:8>   |  |  |  |

| CAN1 – Control Area Network 1                                                       | 58     | 46      | IFS1<26>                | IEC1<26> | IPC11<20:18>    | IPC11<17:16> |  |  |  |

| CAN2 – Control Area Network 2                                                       | 59     | 47      | IFS1<27>                | IEC1<27> | IPC11<28:26>    | IPC11<25:24> |  |  |  |

| ETH – Ethernet Interrupt                                                            | 60     | 48      | IFS1<28>                | IEC1<28> | IPC12<4:2>      | IPC12<1:0>   |  |  |  |

| IC1E – Input Capture 1 Error                                                        | 61     | 5       | IFS1<29>                | IEC1<29> | IPC1<12:10>     | IPC1<9:8>    |  |  |  |

| IC2E – Input Capture 2 Error                                                        | 62     | 9       | IFS1<30>                | IEC1<30> | IPC2<12:10>     | IPC2<9:8>    |  |  |  |

# TABLE 7-1: INTERRUPT IRQ, VECTOR AND BIT LOCATION (CONTINUED)

Note 1: Not all interrupt sources are available on all devices. See TABLE 1: "PIC32MX5XX USB and CAN Features", TABLE 2: "PIC32MX6XX USB and Ethernet Features" and TABLE 3: "PIC32MX7XX USB, Ethernet, and CAN Features" for the list of available peripherals.

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|

| 31:24        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 31.24        | _                 | _                 |                   | _                 |                   |                   | —                | —                |

| 23:16        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 23.10        | _                 | -                 | _                 | _                 |                   | _                 | —                | _                |

| 15:8         | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 15.0         | _                 | -                 | _                 | _                 |                   | _                 | —                | _                |

| 7:0          | R-0               | U-0               | U-0               | R/W-0             | R/W-0             | U-0               | R/W-0            | R/W-0            |

| 7.0          | UACTPND           | _                 |                   | USLPGRD           | USBBUSY           |                   | USUSPEND         | USBPWR           |

# REGISTER 11-5: U1PWRC: USB POWER CONTROL REGISTER

# Legend:

| Logona.           |                  |                                    |                    |  |  |  |

|-------------------|------------------|------------------------------------|--------------------|--|--|--|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read as '0' |                    |  |  |  |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared               | x = Bit is unknown |  |  |  |

#### bit 31-8 Unimplemented: Read as '0'

- bit 7 UACTPND: USB Activity Pending bit

- 1 = USB bus activity has been detected; but an interrupt is pending, it has not been generated yet

- 0 = An interrupt is not pending

#### bit 6-5 Unimplemented: Read as '0'

- bit 4 USLPGRD: USB Sleep Entry Guard bit

- 1 = Sleep entry is blocked if USB bus activity is detected or if a notification is pending

- 0 = USB module does not block Sleep entry

#### bit 3 USBBUSY: USB Module Busy bit

- 1 = USB module is active or disabled, but not ready to be enabled

- 0 = USB module is not active and is ready to be enabled

- **Note:** When USBPWR = 0 and USBBUSY = 1, status from all other registers is invalid and writes to all USB module registers produce undefined results.

#### bit 2 Unimplemented: Read as '0'

## bit 1 USUSPEND: USB Suspend Mode bit

- 1 = USB module is placed in Suspend mode

- (The 48 MHz USB clock will be gated off. The transceiver is placed in a low-power state.)

- 0 = USB module operates normally

- bit 0 USBPWR: USB Operation Enable bit

- 1 = USB module is turned on

- 0 = USB module is disabled

(Outputs held inactive, device pins not used by USB, analog features are shut down to reduce power consumption.)

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit         Bit         Bit         Bit           29/21/13/5         28/20/12/4         27/19/11/3         26/18/10/2 |                      | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |                        |            |  |  |

|--------------|-------------------|-------------------|-----------------------------------------------------------------------------------------------------------------------|----------------------|------------------|------------------|------------------------|------------|--|--|

| 31:24        | U-0               | U-0               | U-0                                                                                                                   | U-0                  | U-0              | U-0              | U-0                    | U-0        |  |  |

| 31.24        |                   |                   | —                                                                                                                     |                      | —                | —                | —                      | —          |  |  |

| 23:16        | U-0               | U-0               | U-0                                                                                                                   | U-0                  | U-0              | U-0              | U-0                    | U-0        |  |  |

| 23.10        |                   |                   | —                                                                                                                     |                      | —                | —                | —                      | —          |  |  |

| 15:8         | U-0               | U-0               | U-0                                                                                                                   | U-0                  | U-0              | U-0              | U-0                    | U-0        |  |  |

| 15.0         | _                 | _                 | —                                                                                                                     | _                    | _                |                  | —                      | _          |  |  |

|              | R/WC-0, HS        | R/WC-0, HS        | R/WC-0, HS                                                                                                            | R/WC-0, HS           | R/WC-0, HS       | R/WC-0, HS       | R/WC-0, HS             | R/WC-0, HS |  |  |

| 7:0          | BTSEF             | BMXEF             | DMAEF <sup>(1)</sup>                                                                                                  | BTOEF <sup>(2)</sup> | DFN8EF           | CRC16EF          | CRC5EF <sup>(4)</sup>  | PIDEF      |  |  |

|              | DIGLI             | DIVIALI           |                                                                                                                       | DIOLIN               |                  | ONCIULI          | EOFEF <sup>(3,5)</sup> | FIDEF      |  |  |

# REGISTER 11-8: U1EIR: USB ERROR INTERRUPT STATUS REGISTER

| Legend:           | WC = Write '1' to clear | HS = Hardware Settable b           | pit                |  |  |

|-------------------|-------------------------|------------------------------------|--------------------|--|--|

| R = Readable bit  | W = Writable bit        | U = Unimplemented bit, read as '0' |                    |  |  |

| -n = Value at POR | '1' = Bit is set        | '0' = Bit is cleared               | x = Bit is unknown |  |  |

- bit 31-8 Unimplemented: Read as '0'

bit 7 BTSEF: Bit Stuff Error Flag bit 1 = Packet is rejected due to bit stuff error 0 = Packet is accepted

bit 6 BMXEF: Bus Matrix Error Flag bit 1 = Invalid base address of the BDT, or the address of an individual buffer pointed to by a BDT entry 0 = No address error

bit 5 DMAEF: DMA Error Flag bit<sup>(1)</sup> 1 = USB DMA error condition detected 0 = No DMA error

- bit 4 **BTOEF:** Bus Turnaround Time-Out Error Flag bit<sup>(2)</sup> 1 = Bus turnaround time-out has occurred

- 0 = No bus turnaround time-out

- bit 3 DFN8EF: Data Field Size Error Flag bit

1 = Data field received is not an integral number of bytes

0 = Data field received is an integral number of bytes

- bit 2 CRC16EF: CRC16 Failure Flag bit

- 1 = Data packet is rejected due to CRC16 error

0 = Data packet is accepted

- bit 1 CRC5EF: CRC5 Host Error Flag bit<sup>(4)</sup> 1 = Token packet is rejected due to CRC5 error 0 = Token packet is accepted EOFEF: EOF Error Flag bit<sup>(3,5)</sup> 1 = EOF error condition is detected

- 0 = No EOF error condition

- bit 0 PIDEF: PID Check Failure Flag bit

- 1 = PID check is failed

- 0 = PID check is passed

- **Note 1:** This type of error occurs when the module's request for the DMA bus is not granted in time to service the module's demand for memory, resulting in an overflow or underflow condition, and/or the allocated buffer size is not sufficient to store the received data packet causing it to be truncated.

- 2: This type of error occurs when more than 16-bit-times of Idle from the previous End-of-Packet (EOP) has elapsed.

- **3:** This type of error occurs when the module is transmitting or receiving data and the SOF counter has reached zero.

- 4: Device mode.

- 5: Host mode.

# REGISTER 18-2: SPIxSTAT: SPI STATUS REGISTER

- bit 1 SPITBF: SPI Transmit Buffer Full Status bit

- 1 = Transmit not yet started, SPITXB is full

- 0 = Transmit buffer is not full

#### Standard Buffer Mode:

Automatically set in hardware when the core writes to the SPIBUF location, loading SPITXB. Automatically cleared in hardware when the SPI module transfers data from SPITXB to SPISR.

## Enhanced Buffer Mode:

Set when CWPTR + 1 = SRPTR; cleared otherwise

SPIRBF: SPI Receive Buffer Full Status bit

1 = Receive buffer, SPIxRXB is full

0 = Receive buffer, SPIxRXB is not full

Standard Buffer Mode:

bit 0

Automatically set in hardware when the SPI module transfers data from SPIxSR to SPIxRXB. Automatically cleared in hardware when SPIxBUF is read from, reading SPIxRXB.

Enhanced Buffer Mode:

Set when SWPTR + 1 = CRPTR; cleared otherwise

# **19.1 Control Registers**

# TABLE 19-1: I2C1THROUGH I2C5 REGISTER MAP

| ss                          |                                 |               |              |             |       |        |                  |       |             | Bi         | ts    |             |              |              |               |          |          |          |            |

|-----------------------------|---------------------------------|---------------|--------------|-------------|-------|--------|------------------|-------|-------------|------------|-------|-------------|--------------|--------------|---------------|----------|----------|----------|------------|

| Virtual Address<br>(BF80_#) | Register<br>Name <sup>(1)</sup> | Bit Range     | 31/15        | 30/14       | 29/13 | 28/12  | 27/11            | 26/10 | 25/9        | 24/8       | 23/7  | 22/6        | 21/5         | 20/4         | 19/3          | 18/2     | 17/1     | 16/0     | All Resets |

| 5000                        | I2C3CON                         | 31:16         | _            | _           | —     | _      |                  |       | _           | _          |       |             | _            | _            | _             |          |          |          | 0000       |

|                             |                                 | 15:0          | ON           | —           | SIDL  | SCLREL | STRICT           | A10M  | DISSLW      | SMEN       | GCEN  | STREN       | ACKDT        | ACKEN        | RCEN          | PEN      | RSEN     | SEN      | 1000       |

| 5010                        | I2C3STAT                        | 31:16<br>15:0 | —<br>ACKSTAT | —<br>TRSTAT |       |        | _                | BCL   | —<br>GCSTAT | —<br>ADD10 |       | –<br>I2COV  | —<br>D/A     | —<br>P       |               | —<br>R/W | —<br>RBF | —<br>TBF | 0000       |

|                             | 1000100                         | 31:16         | —            | -           | _     | _      | _                | -     |             | -          | —     | -           |              | -            | _             | -        | —        | —        | 0000       |

| 5020                        | I2C3ADD                         | 15:0          | _            | _           | _     | _      | _                | _     |             |            |       |             | ADD          | <9:0>        |               |          |          |          | 0000       |

| 5000                        | IOCOMOK                         | 31:16         | _            | _           | —     | —      | —                | _     | —           | _          | —     | _           | —            | —            | —             | _        | —        | _        | 0000       |

| 5030                        | I2C3MSK                         | 15:0          | _            | _           | —     | _      | —                |       |             |            |       |             | MSK          | <9:0>        |               |          |          |          | 0000       |

| 5040                        | I2C3BRG                         | 31:16         | _            | _           | —     | _      | _                | _     | _           | _          | -     | _           | _            | _            | _             | _        | _        | _        | 0000       |

| 5040                        | IZCODKG                         | 15:0          | _            | _           | —     | —      |                  |       |             |            | Ba    | ud Rate Ger | nerator Regi | ster         |               |          |          |          | 0000       |

| 5050                        | I2C3TRN                         | 31:16         | —            | —           |       |        | —                |       |             | _          |       | -           | -            | _            | -             | —        | —        | —        | 0000       |

| 5050                        | 120311(1)                       | 15:0          | —            | —           |       |        | —                |       |             | _          |       |             | -            | Transmit     | Register      |          |          |          | 0000       |

| 5060                        | I2C3RCV                         | 31:16         | —            | —           | —     | —      | —                | _     | —           | —          | _     | —           | —            | —            | —             | —        | —        | —        | 0000       |

| 0000                        | 12001101                        | 15:0          | _            | _           | —     | _      | Receive Register |       |             |            |       | -           |              | 0000         |               |          |          |          |            |

| 5100                        | I2C4CON                         | 31:16         | _            | _           | —     | _      | _                | _     | _           | —          | _     | —           | _            | _            | _             | —        | —        | —        | 0000       |

|                             |                                 | 15:0          | ON           | _           | SIDL  | SCLREL | STRICT           | A10M  | DISSLW      | SMEN       | GCEN  | STREN       | ACKDT        | ACKEN        | RCEN          | PEN      | RSEN     | SEN      | 1000       |

| 5110                        | I2C4STAT                        | 31:16         | —            | —           | —     |        | _                | —     | —           | _          | —     | —           |              | —            |               | —        | —        | —        | 0000       |

| L                           |                                 | 15:0          | ACKSTAT      | TRSTAT      | —     | —      | —                | BCL   | GCSTAT      | ADD10      | IWCOL | I2COV       | D/A          | Р            | S             | R/W      | RBF      | TBF      | 0000       |

| 5120                        | I2C4ADD                         | 31:16         | _            | _           | —     | _      | _                | _     | —           |            | —     | —           | —            | —            | —             | _        | _        | —        | 0000       |

| <b></b>                     |                                 | 15:0          | _            | _           | _     | _      | _                |       |             |            |       |             | ADD          | <9:0>        |               |          |          |          | 0000       |

| 5130                        | I2C4MSK                         | 31:16         | _            | _           |       |        |                  |       |             | _          | _     | _           |              |              |               |          | _        | _        | 0000       |

| ┢────┼                      |                                 | 15:0          |              | _           |       |        | _                |       |             |            |       |             | MSK          | <9:0>        |               |          |          |          | 0000       |

| 5140                        | I2C4BRG                         | 31:16         |              | _           | _     |        |                  | —     | —           |            | -     | —           | —            | —            | —             | _        | _        | —        | 0000       |

|                             |                                 | 15:0<br>31:16 | _            | _           | _     |        |                  |       |             |            |       | ud Rate Ger | erator Regi  | ster         |               |          |          |          | 0000       |

| 5150                        | I2C4TRN                         | 15:0          |              |             |       |        |                  |       |             |            | _     | _           | _            | <br>Transmit | —<br>Register | —        | —        | —        | 0000       |

| ł                           |                                 | 31:16         |              |             |       |        |                  |       |             |            |       |             |              |              |               | _        | _        | _        | 0000       |

| 5160                        | I2C4RCV                         | 15:0          | _            | _           |       |        |                  |       |             | _          | _     |             |              | Receive      | Register      |          |          |          | 0000       |

|                             |                                 | 31:16         | _            | _           | _     | _      | _                | _     | _           | _          | _     | _           | _            | _            | _             | _        | _        | _        | 0000       |

| 5200                        | I2C5CON                         | 15:0          | ON           | _           | SIDL  | SCLREL | STRICT           | A10M  | DISSLW      | SMEN       | GCEN  | STREN       | ACKDT        | ACKEN        | RCEN          | PEN      | RSEN     | SEN      | 1000       |

| 5040                        | 10050747                        | 31:16         | _            | _           | —     | —      | _                | _     | —           |            | _     | _           | —            | —            | —             | _        | _        | _        | 0000       |

| 5210                        | I2C5STAT                        | 15:0          | ACKSTAT      | TRSTAT      | —     | —      | —                | BCL   | GCSTAT      | ADD10      | IWCOL | I2COV       | D/A          | Р            | S             | R/W      | RBF      | TBF      | 0000       |

| 5000                        | 1005405                         | 31:16         | _            | _           | —     | —      | _                | —     | —           | _          | —     | _           | —            | —            | —             | _        | _        | _        | 0000       |

| 5220                        | I2C5ADD                         | 15:0          | _            | _           | _     | _      | _                | _     |             |            |       |             | ADD          | <9:0>        |               |          |          |          | 0000       |

Legend: x = unknown value on Reset; - = unimplemented, read as '0'. Reset values are shown in hexadecimal.

Note 1: All registers in this table except I2CxRCV have corresponding CLR, SET and INV registers at their virtual addresses, plus offsets of 0x4, 0x8 and 0xC, respectively. See Section 12.1.1 "CLR, SET and INV Registers" for more information.

PIC32MX5XX/6XX/7XX

2: This register is not available on 64-pin devices.

# REGISTER 21-2: PMMODE: PARALLEL PORT MODE REGISTER (CONTINUED)

- WAITM<3:0>: Data Read/Write Strobe Wait States bits<sup>(1)</sup> bit 5-2 1111 = Wait of 16 TPB 0001 = Wait of 2 ТРВ 0000 = Wait of 1 TPB (default) WAITE<1:0>: Data Hold After Read/Write Strobe Wait States bits<sup>(1)</sup> bit 1-0 11 = Wait of 4 Трв 10 = Wait of 3 TPB 01 = Wait of 2 TPB 00 = Wait of 1 TPB (default) For Read operations: 11 = Wait of 3 TPB 10 = Wait of 2 TPB 01 = Wait of 1 TPB 00 = Wait of 0 TPB (default)

- **Note 1:** Whenever WAITM<3:0> = 0000, WAITB and WAITE bits are ignored and forced to 1 TPBCLK cycle for a write operation; WAITB = 1 TPBCLK cycle, WAITE = 0 TPBCLK cycles for a read operation.

- 2: Address bit A14 is not subject to auto-increment/decrement if configured as Chip Select CS1.

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |  |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|--|--|

| 31:24        | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |

| 31.24        | FLTEN15           | MSEL1             | 5<1:0>            |                   | FSEL15<4:0>       |                   |                  |                  |  |  |

| 22:46        | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |

| 23:16        | FLTEN14           | MSEL1             | 4<1:0>            | FSEL14<4:0>       |                   |                   |                  |                  |  |  |

| 15:8         | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |

| 10.0         | FLTEN13           | MSEL1             | 3<1:0>            |                   | FSEL13<4:0>       |                   |                  |                  |  |  |

| 7.0          | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |

| 7:0          | FLTEN12           | MSEL1             | 2<1:0>            | FSEL12<4:0>       |                   |                   |                  |                  |  |  |

# REGISTER 24-13: CIFLTCON3: CAN FILTER CONTROL REGISTER 3

## Legend:

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read as '0' |                    |

|-------------------|------------------|------------------------------------|--------------------|

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared               | x = Bit is unknown |

| bit 31    | FLTEN15: Filter 15 Enable bit<br>1 = Filter is enabled<br>0 = Filter is disabled                                                                                                                                                                                                           |

|-----------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| bit 30-29 | MSEL15<1:0>: Filter 15 Mask Select bits<br>11 = Acceptance Mask 3 selected<br>10 = Acceptance Mask 2 selected<br>01 = Acceptance Mask 1 selected<br>00 = Acceptance Mask 0 selected                                                                                                        |

| bit 28-24 | FSEL15<4:0>: FIFO Selection bits<br>11111 = Message matching filter is stored in FIFO buffer 31<br>11110 = Message matching filter is stored in FIFO buffer 30<br>00001 = Message matching filter is stored in FIFO buffer 1<br>00000 = Message matching filter is stored in FIFO buffer 0 |

| bit 23    | FLTEN14: Filter 14 Enable bit<br>1 = Filter is enabled<br>0 = Filter is disabled                                                                                                                                                                                                           |

| bit 22-21 | MSEL14<1:0>: Filter 14 Mask Select bits<br>11 = Acceptance Mask 3 selected<br>10 = Acceptance Mask 2 selected<br>01 = Acceptance Mask 1 selected<br>00 = Acceptance Mask 0 selected                                                                                                        |

| bit 20-16 | FSEL14<4:0>: FIFO Selection bits<br>11111 = Message matching filter is stored in FIFO buffer 31<br>11110 = Message matching filter is stored in FIFO buffer 30<br>00001 = Message matching filter is stored in FIFO buffer 1<br>00000 = Message matching filter is stored in FIFO buffer 0 |

| Note:     | The hits in this register can only be modified if the correspondir                                                                                                                                                                                                                         |

**Note:** The bits in this register can only be modified if the corresponding filter enable (FLTENn) bit is '0'.

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|

| 31:24        | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |

| 31.24        | FLTEN23           | MSEL2             | 3<1:0>            |                   | FSEL23<4:0>       |                   |                  |                  |

| 22:16        | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |

| 23:16        | FLTEN22           | MSEL22<1:0>       |                   | FSEL22<4:0>       |                   |                   |                  |                  |

| 15:8         | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |

| 10.0         | FLTEN21           | MSEL21<1:0>       |                   | FSEL21<4:0>       |                   |                   |                  |                  |

| 7.0          | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |

| 7:0          | FLTEN20           | MSEL2             | 20<1:0>           | FSEL20<4:0>       |                   |                   |                  |                  |

# REGISTER 24-15: CIFLTCON5: CAN FILTER CONTROL REGISTER 5

## Legend:

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read as '0' |                    |  |

|-------------------|------------------|------------------------------------|--------------------|--|

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared               | x = Bit is unknown |  |

| bit 31    | FLTEN23: Filter 23 Enable bit                                                                                            |

|-----------|--------------------------------------------------------------------------------------------------------------------------|

|           | 1 = Filter is enabled<br>0 = Filter is disabled                                                                          |

| bit 30-29 | MSEL23<1:0>: Filter 23 Mask Select bits                                                                                  |

| 511 00 25 | 11 = Acceptance Mask 3 selected                                                                                          |

|           | 10 = Acceptance Mask 2 selected                                                                                          |

|           | 01 = Acceptance Mask 1 selected                                                                                          |

| bit 28-24 | 00 = Acceptance Mask 0 selected<br><b>FSEL23&lt;4:0&gt;:</b> FIFO Selection bits                                         |

| DIL 20-24 | 11111 = Message matching filter is stored in FIFO buffer 31                                                              |

|           | 11110 = Message matching filter is stored in FIFO buffer 30                                                              |

|           | •                                                                                                                        |

|           | :                                                                                                                        |

|           | 00001 = Message matching filter is stored in FIFO buffer 1<br>00000 = Message matching filter is stored in FIFO buffer 0 |

| bit 23    | FLTEN22: Filter 22 Enable bit                                                                                            |

|           | 1 = Filter is enabled                                                                                                    |

|           | 0 = Filter is disabled                                                                                                   |

| bit 22-21 | MSEL22<1:0>: Filter 22 Mask Select bits                                                                                  |

|           | <ul><li>11 = Acceptance Mask 3 selected</li><li>10 = Acceptance Mask 2 selected</li></ul>                                |

|           | 01 = Acceptance Mask 1 selected                                                                                          |

|           | 00 = Acceptance Mask 0 selected                                                                                          |

| bit 20-16 | FSEL22<4:0>: FIFO Selection bits                                                                                         |

|           | 11111 = Message matching filter is stored in FIFO buffer 31                                                              |

|           | 11110 = Message matching filter is stored in FIFO buffer 30                                                              |

|           |                                                                                                                          |

|           | •<br>00001 = Message matching filter is stored in FIFO buffer 1                                                          |

|           | 00000 = Message matching filter is stored in FIFO buffer 0                                                               |

|           |                                                                                                                          |

| Nata      | The bits in this register can only be medified if the server and                                                         |

Note: The bits in this register can only be modified if the corresponding filter enable (FLTENn) bit is '0'.

| Bit Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

|-----------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|

| 31:24     | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 31.24     |                   | —                 | —                 | —                 |                   | —                 |                  | _                |

| 23:16     | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 23.10     | _                 | —                 | —                 | —                 | _                 | —                 | _                | —                |

| 15:8      | U-0               | U-0               | U-0               | U-0               | U-0               | R/W-0             | R/W-0            | R/W-0            |

| 10.0      | _                 | —                 | —                 | —                 | _                 | RXBUFSZ<6:4>      |                  |                  |

| 7:0       | R/W-0             | R/W-0             | R/W-0             | R/W-0             | U-0               | U-0               | U-0              | U-0              |

|           |                   | RXBUFSZ<3:0>      |                   |                   |                   | _                 |                  | _                |

# REGISTER 25-2: ETHCON2: ETHERNET CONTROLLER CONTROL REGISTER 2

# Legend:

| Logona.                           |                  |                                    |                    |  |

|-----------------------------------|------------------|------------------------------------|--------------------|--|

| R = Readable bit W = Writable bit |                  | U = Unimplemented bit, read as '0' |                    |  |

| -n = Value at POR                 | '1' = Bit is set | '0' = Bit is cleared               | x = Bit is unknown |  |

# bit 31-11 Unimplemented: Read as '0'

bit 10-4 RXBUFSZ<6:0>: RX Data Buffer Size for All RX Descriptors (in 16-byte increments) bits

1111111 = RX data Buffer size for descriptors is 2032 bytes

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.</li

Note 1: This register is only used for RX operations.

2: The bits in this register may only be changed while the RXEN bit (ETHCON1<8>) = 0.

| Bit Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

|-----------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|

| 31:24     | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |

| 31.24     |                   |                   |                   | PMM<              | 31:24>            |                   |                  |                  |

| 23:16     | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |

| 23.10     | PMM<23:16>        |                   |                   |                   |                   |                   |                  |                  |

| 15:8      | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |

| 15.0      | PMM<15:8>         |                   |                   |                   |                   |                   |                  |                  |

| 7:0       | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |

|           |                   |                   |                   | PMM               | <7:0>             |                   |                  |                  |

## REGISTER 25-7: ETHPMM0: ETHERNET CONTROLLER PATTERN MATCH MASK 0 REGISTER

# Legend:

| 9                                 |                  |                                    |                    |  |  |

|-----------------------------------|------------------|------------------------------------|--------------------|--|--|

| R = Readable bit W = Writable bit |                  | U = Unimplemented bit, read as '0' |                    |  |  |

| -n = Value at POR                 | '1' = Bit is set | '0' = Bit is cleared               | x = Bit is unknown |  |  |

| bit 31-24 | PMM<31:24>: Pattern Match Mask 3 bits |

|-----------|---------------------------------------|

| hit 23-16 | PMM-23-16- Pattern Match Mask 2 hits  |

- bit 23-16 PMM<23:16>: Pattern Match Mask 2 bits

- bit 15-8 **PMM<15:8>:** Pattern Match Mask 1 bits

- bit 7-0 PMM<7:0>: Pattern Match Mask 0 bits

- Note 1: This register is only used for RX operations.

2: The bits in this register may only be changed while the RXEN bit (ETHCON1<8>) = 0 or the PMMODE bit (ETHRXFC<11:8>) = 0.

# REGISTER 25-8: ETHPMM1: ETHERNET CONTROLLER PATTERN MATCH MASK 1 REGISTER

| Bit Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |

|-----------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|--|

| 31:24     | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |

| 31.24     | PMM<63:56>        |                   |                   |                   |                   |                   |                  |                  |  |

| 23:16     | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |

| 23.10     | PMM<55:48>        |                   |                   |                   |                   |                   |                  |                  |  |

| 15:8      | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |

| 15.6      | PMM<47:40>        |                   |                   |                   |                   |                   |                  |                  |  |

| 7:0       | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |

| 7.0       |                   |                   |                   | PMM<              | 39:32>            |                   |                  |                  |  |

| Legend:           |                  |                      |                    |

|-------------------|------------------|----------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented b  | vit, read as '0'   |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared | x = Bit is unknown |

|                   |                  |                      |                    |

| bit 31-24 | PMM<63:56>: Pattern Match Mask 7 bits |

|-----------|---------------------------------------|

| bit 23-16 | PMM<55:48>: Pattern Match Mask 6 bits |

| bit 15-8  | PMM<47:40>: Pattern Match Mask 5 bits |

| bit 7-0   | PMM<39:32>: Pattern Match Mask 4 bits |

# Note 1: This register is only used for RX operations. 2: The bits in this register may only be changed while the RXEN bit (ETHCON1<8>) = 0 or the PMMODE bit (ETHRXFC<11:8>) = 0.

# REGISTER 25-24: EMAC1CFG2: ETHERNET CONTROLLER MAC CONFIGURATION 2 REGISTER (CONTINUED)

- VLANPAD: VLAN Pad Enable bit<sup>(1,2)</sup> bit 6 1 = The MAC will pad all short frames to 64 bytes and append a valid CRC 0 = The MAC does not perform padding of short frames PADENABLE: Pad/CRC Enable bit<sup>(1,3)</sup> bit 5 1 = The MAC will pad all short frames 0 = The frames presented to the MAC have a valid length bit 4 CRCENABLE: CRC Enable1 bit 1 = The MAC will append a CRC to every frame whether padding was required or not. Must be set if the PADENABLE bit is set. 0 = The frames presented to the MAC have a valid CRC bit 3 DELAYCRC: Delayed CRC bit This bit determines the number of bytes, if any, of proprietary header information that exist on the front of the IEEE 802.3 frames. 1 = Four bytes of header (ignored by the CRC function) 0 = No proprietary header bit 2 HUGEFRM: Huge Frame enable bit 1 = Frames of any length are transmitted and received 0 = Huge frames are not allowed for receive or transmit LENGTHCK: Frame Length checking bit bit 1 1 = Both transmit and receive frame lengths are compared to the Length/Type field. If the Length/Type field represents a length then the check is performed. Mismatches are reported on the transmit/receive statistics vector. 0 = Length/Type field check is not performed bit 0 FULLDPLX: Full-Duplex Operation bit 1 = The MAC operates in Full-Duplex mode 0 = The MAC operates in Half-Duplex mode

- Note 1: Table 25-6 provides a description of the pad function based on the configuration of this register.

- 2: This bit is ignored if the PADENABLE bit is cleared.

- **3:** This bit is used in conjunction with the AUTOPAD and VLANPAD bits.

**Note:** Both 16-bit and 32-bit accesses are allowed to these registers (including the SET, CLR and INV registers). 8-bit accesses are not allowed and are ignored by the hardware

## TABLE 25-6:PAD OPERATION

| Туре | AUTOPAD | VLANPAD | PADENABLE | Action                                                                                  |

|------|---------|---------|-----------|-----------------------------------------------------------------------------------------|

| Any  | x       | x       | 0         | No pad, check CRC                                                                       |

| Any  | 0       | 0       | 1         | Pad to 60 Bytes, append CRC                                                             |

| Any  | x       | 1       | 1         | Pad to 64 Bytes, append CRC                                                             |

| Any  | 1       | 0       | 1         | If untagged: Pad to 60 Bytes, append CRC<br>If VLAN tagged: Pad to 64 Bytes, append CRC |

# 32.2 AC Characteristics and Timing Parameters

The information contained in this section defines PIC32MX5XX/6XX/7XX AC characteristics and timing parameters.

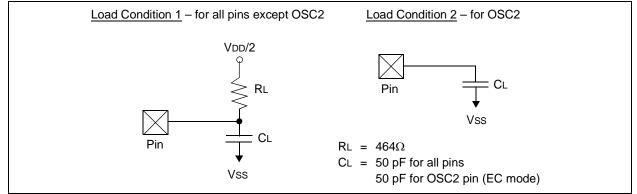

# FIGURE 32-1: LOAD CONDITIONS FOR DEVICE TIMING SPECIFICATIONS

# TABLE 32-16: CAPACITIVE LOADING REQUIREMENTS ON OUTPUT PINS

| AC CHARACTERISTICS |        | $\begin{tabular}{lllllllllllllllllllllllllllllllllll$ |                                                   |   |     |    |                                                                         |

|--------------------|--------|-------------------------------------------------------|---------------------------------------------------|---|-----|----|-------------------------------------------------------------------------|

| Param.<br>No.      | Symbol | Characteristics                                       | Min. Typical <sup>(1)</sup> Max. Units Conditions |   |     |    | Conditions                                                              |

| DO50               | Cosco  | OSC2 pin                                              |                                                   | _ | 15  | pF | In XT and HS modes when an<br>external crystal is used to drive<br>OSC1 |

| DO56               | Сю     | All I/O pins and OSC2                                 |                                                   | — | 50  | pF | In EC mode                                                              |

| DO58               | Св     | SCLx, SDAx                                            |                                                   | — | 400 | pF | In I <sup>2</sup> C mode                                                |

Note 1: Data in "Typical" column is at 3.3V, 25°C unless otherwise stated. Parameters are for design guidance only and are not tested.

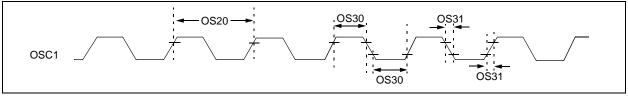

# FIGURE 32-2: EXTERNAL CLOCK TIMING

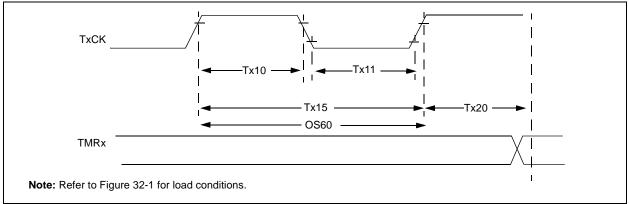

# FIGURE 32-6: TIMER1, 2, 3, 4, 5 EXTERNAL CLOCK TIMING CHARACTERISTICS

# TABLE 32-23: TIMER1 EXTERNAL CLOCK TIMING REQUIREMENTS<sup>(1)</sup>

|               |                                                     |                                                                                                         |                          |                                            | Standard Operating Conditions: 2.3V to 3.6V(unless otherwise stated)Operating temperature $-40^{\circ}C \le TA \le +85^{\circ}C$ for Industrial $-40^{\circ}C \le TA \le +105^{\circ}C$ for V-Temp |         |      |            |                                  |  |

|---------------|-----------------------------------------------------|---------------------------------------------------------------------------------------------------------|--------------------------|--------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------|------|------------|----------------------------------|--|

| Param.<br>No. | Symbol                                              | Characteristics <sup>(2)</sup>                                                                          |                          |                                            | Min.                                                                                                                                                                                               | Typical | Max. | Units      | Conditions                       |  |

| TA10          | T⊤xH                                                | TxCK<br>High Time                                                                                       | Synchrono<br>with presca |                                            | [(12.5 ns or 1 ТРВ)/N]<br>+ 25 ns                                                                                                                                                                  | —       | —    | ns         | Must also meet parameter TA15    |  |

|               |                                                     |                                                                                                         | Asynchron<br>with presca |                                            | 10                                                                                                                                                                                                 |         | —    | ns         | —                                |  |

| TA11          | T⊤xL                                                | TxCK<br>Low Time                                                                                        | ,                        |                                            | [(12.5 ns or 1 Трв)/N]<br>+ 25 ns                                                                                                                                                                  | _       | _    | ns         | Must also meet<br>parameter TA15 |  |

|               | Asynchronou<br>with prescale                        |                                                                                                         |                          | 10                                         | _                                                                                                                                                                                                  | —       | ns   | _          |                                  |  |

| TA15          | A15 TTXP TxCK Synchrono<br>Input Period with presca |                                                                                                         |                          | [(Greater of 25 ns or<br>2 TPB)/N] + 30 ns |                                                                                                                                                                                                    | _       | ns   | VDD > 2.7V |                                  |  |

|               |                                                     |                                                                                                         |                          |                                            | [(Greater of 25 ns or<br>2 TPB)/N] + 50 ns                                                                                                                                                         | —       | _    | ns         | Vdd < 2.7V                       |  |

|               |                                                     |                                                                                                         | Asynchron<br>with presca |                                            | 20                                                                                                                                                                                                 | —       | _    | ns         | VDD > 2.7V<br>(Note 3)           |  |

|               |                                                     |                                                                                                         |                          |                                            | 50                                                                                                                                                                                                 | —       | _    | ns         | VDD < 2.7V<br>(Note 3)           |  |

| OS60          | FT1                                                 | SOSC1/T1CK Oscillator<br>Input Frequency Range<br>(oscillator enabled by setting<br>TCS bit (T1CON<1>)) |                          |                                            | 32                                                                                                                                                                                                 | —       | 100  | kHz        | _                                |  |

| TA20          | TCKEXTMRL                                           | Delay from External TxCK<br>Clock Edge to Timer<br>Increment                                            |                          | ĸ                                          | —                                                                                                                                                                                                  | —       | 1    | Трв        | —                                |  |

Note 1: Timer1 is a Type A.

2: This parameter is characterized, but not tested in manufacturing.

**3:** N = Prescale Value (1, 8, 64, 256).

# TABLE 32-32: I2Cx BUS DATA TIMING REQUIREMENTS (MASTER MODE)

| AC CHARACTERISTICS |                               |                              | $\begin{tabular}{lllllllllllllllllllllllllllllllllll$ |                     |          |                   |                         |

|--------------------|-------------------------------|------------------------------|-------------------------------------------------------|---------------------|----------|-------------------|-------------------------|

| Param.<br>No.      | Symbol                        | bol Characteristics          |                                                       | Min. <sup>(1)</sup> | Max.     | Units             | Conditions              |

| IM10               | TLO:SCL                       | Clock Low Time               | 100 kHz mode                                          | Трв * (BRG + 2)     | —        | μS                | _                       |

|                    |                               |                              | 400 kHz mode                                          | Трв * (BRG + 2)     | _        | μS                | _                       |

|                    |                               |                              | 1 MHz mode <sup>(2)</sup>                             | Tpb * (BRG + 2)     | —        | μS                | _                       |

| IM11               | THI:SCL                       | Clock High Time              | 100 kHz mode                                          | Трв * (BRG + 2)     | —        | μS                | _                       |

|                    |                               |                              | 400 kHz mode                                          | Tpb * (BRG + 2)     | —        | μS                | _                       |

|                    |                               |                              | 1 MHz mode <sup>(2)</sup>                             | Трв * (BRG + 2)     | _        | μS                | _                       |

| IM20               | TF:SCL                        | SDAx and SCLx                | 100 kHz mode                                          | —                   | 300      | ns                | CB is specified to be   |

|                    |                               | Fall Time                    | 400 kHz mode                                          | 20 + 0.1 Св         | 300      | ns                | from 10 to 400 pF       |

|                    |                               |                              | 1 MHz mode <sup>(2)</sup>                             | —                   | 100      | ns                |                         |

| IM21               | TR:SCL                        | SDAx and SCLx                | 100 kHz mode                                          | _                   | 1000     | ns                | CB is specified to be   |

|                    |                               | Rise Time                    | 400 kHz mode                                          | 20 + 0.1 Св         | 300      | ns                | from 10 to 400 pF       |

|                    |                               |                              | 1 MHz mode <sup>(2)</sup>                             | —                   | 300      | ns                |                         |

| IM25               | TSU:DAT                       | Data Input                   | 100 kHz mode                                          | 250                 | _        | ns                | _                       |

|                    |                               | Setup Time                   | 400 kHz mode                                          | 100                 | _        | ns                |                         |

|                    |                               |                              | 1 MHz mode <sup>(2)</sup>                             | 100                 | _        | ns                |                         |

| IM26 Thd:dat       | THD:DAT                       | Data Input                   | 100 kHz mode                                          | 0                   | —        | μS                | _                       |

|                    | Hold Time                     | 400 kHz mode                 | 0                                                     | 0.9                 | μS       |                   |                         |

|                    |                               | 1 MHz mode <sup>(2)</sup>    | 0                                                     | 0.3                 | μS       |                   |                         |

| IM30 Tsu:sta       | Start Condition<br>Setup Time | 100 kHz mode                 | Трв * (BRG + 2)                                       | —                   | ns       | Only relevant for |                         |

|                    |                               | 400 kHz mode                 | Трв * (BRG + 2)                                       | _                   | ns       | Repeated Start    |                         |

|                    |                               | 1 MHz mode <sup>(2)</sup>    | Трв * (BRG + 2)                                       | _                   | ns       | condition         |                         |

| IM31               | THD:STA                       | Start Condition<br>Hold Time | 100 kHz mode                                          | Трв * (BRG + 2)     | —        | ns                | After this period, the  |

|                    |                               |                              | 400 kHz mode                                          | Трв * (BRG + 2)     | _        | ns                | first clock pulse is    |

|                    |                               |                              | 1 MHz mode <sup>(2)</sup>                             | Трв * (BRG + 2)     | _        | ns                | generated               |

| IM33               | Tsu:sto                       | Stop Condition               | 100 kHz mode                                          | Трв * (BRG + 2)     | _        | ns                | _                       |

|                    |                               | Setup Time                   | 400 kHz mode                                          | Трв * (BRG + 2)     | _        | ns                |                         |

|                    |                               |                              | 1 MHz mode <sup>(2)</sup>                             | Трв * (BRG + 2)     | _        | ns                |                         |

| IM34               | THD:STO                       | Stop Condition               | 100 kHz mode                                          | Трв * (BRG + 2)     | _        | ns                | _                       |

|                    |                               | Hold Time                    | 400 kHz mode                                          | Трв * (BRG + 2)     | _        | ns                |                         |

|                    |                               |                              | 1 MHz mode <sup>(2)</sup>                             | Трв * (BRG + 2)     | _        | ns                |                         |

| IM40               | TAA:SCL                       | Output Valid from            | 100 kHz mode                                          | _                   | 3500     | ns                | _                       |

|                    |                               | Clock                        | 400 kHz mode                                          | _                   | 1000     | ns                | _                       |

|                    |                               |                              | 1 MHz mode <sup>(2)</sup>                             | _                   | 350      | ns                | _                       |

| IM45               | TBF:SDA                       | Bus Free Time                | 100 kHz mode                                          | 4.7                 | _        | μS                | The amount of time the  |

|                    |                               |                              | 400 kHz mode                                          | 1.3                 | <u> </u> | μS                | bus must be free before |

|                    |                               |                              | 1 MHz mode <sup>(2)</sup>                             | 0.5                 | <u> </u> | μS                | a new                   |

| IMEO               | CD                            | Rue Consolitive La           | ading                                                 |                     | 400      |                   | transmission can start  |