Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFl

| Details                    |                                                                                  |

|----------------------------|----------------------------------------------------------------------------------|

| Product Status             | Active                                                                           |

| Core Processor             | MIPS32® M4K™                                                                     |

| Core Size                  | 32-Bit Single-Core                                                               |

| Speed                      | 80MHz                                                                            |

| Connectivity               | Ethernet, I <sup>2</sup> C, SPI, UART/USART, USB OTG                             |

| Peripherals                | Brown-out Detect/Reset, DMA, POR, PWM, WDT                                       |

| Number of I/O              | 83                                                                               |

| Program Memory Size        | 512KB (512K x 8)                                                                 |

| Program Memory Type        | FLASH                                                                            |

| EEPROM Size                | •                                                                                |

| RAM Size                   | 128K × 8                                                                         |

| Voltage - Supply (Vcc/Vdd) | 2.3V ~ 3.6V                                                                      |

| Data Converters            | A/D 16x10b                                                                       |

| Oscillator Type            | Internal                                                                         |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                                |

| Mounting Type              | Surface Mount                                                                    |

| Package / Case             | 121-TFBGA                                                                        |

| Supplier Device Package    | 121-TFBGA (10x10)                                                                |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic32mx695f512l-80i-bg |

|                            |                                                                                  |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

NOTES:

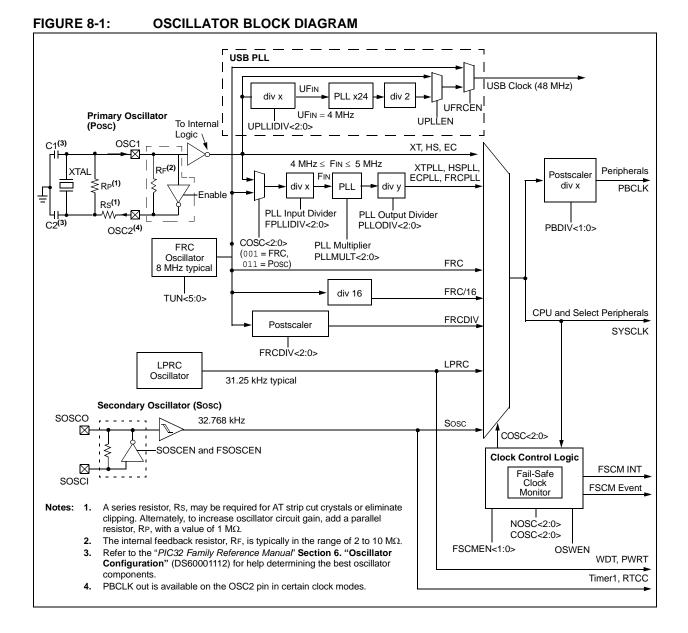

### 8.0 OSCILLATOR CONFIGURATION

Note: This data sheet summarizes the features of the PIC32MX5XX/6XX/7XX family of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to Section 6. "Oscillator" (DS60001112) in the "PIC32 Family Reference Manual", which is available from the Microchip web site (www.microchip.com/PIC32). The Oscillator module has the following features:

- A total of four external and internal oscillator options as clock sources

- On-chip PLL with user-selectable input divider, multiplier and output divider to boost operating frequency on select internal and external oscillator sources

- On-chip user-selectable divisor postscaler on select oscillator sources

- Software-controllable switching between various clock sources

- A Fail-Safe Clock Monitor (FSCM) that detects clock failure and permits safe application recovery or shutdown

- Dedicated On-Chip PLL for USB peripheral

Figure 8-1shows the Oscillator module block diagram.

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|

| 24.24        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 31:24        | _                 | _                 | _                 | _                 | _                 | _                 | —                | —                |

| 00.40        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 23:16        | _                 | _                 | —                 | _                 | _                 | _                 | —                | _                |

| 45.0         | R/W-0             | U-0               | U-0               | R/W-0             | R/W-0             | U-0               | U-0              | U-0              |

| 15:8         | 0N <sup>(1)</sup> | —                 | —                 | SUSPEND           | DMABUSY           | —                 | —                | —                |

| 7.0          | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 7:0          |                   | _                 | _                 | _                 | _                 | _                 | _                | _                |

#### REGISTER 10-1: DMACON: DMA CONTROLLER CONTROL REGISTER

#### Legend:

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, rea | d as '0'           |

|-------------------|------------------|----------------------------|--------------------|

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared       | x = Bit is unknown |

#### bit 31-16 Unimplemented: Read as '0'

- ON: DMA On bit<sup>(1)</sup> bit 15

- 1 = DMA module is enabled

- 0 = DMA module is disabled

- bit 14-13 Unimplemented: Read as '0'

- bit 12 SUSPEND: DMA Suspend bit

- 1 = DMA transfers are suspended to allow CPU uninterrupted access to data bus

- 0 = DMA operates normally

- bit 11 DMABUSY: DMA Module Busy bit

- 1 = DMA module is active

- 0 = DMA module is disabled and not actively transferring data

- bit 10-0 Unimplemented: Read as '0'

- Note 1: When using the 1:1 PBCLK divisor, the user's software should not read/write the peripheral's SFRs in the SYSCLK cycle immediately following the instruction that clears the module's ON bit.

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|

| 21.24        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 31:24        |                   | —                 | -                 | -                 | _                 | _                 | —                | —                |

| 23:16        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 23.10        | —                 | —                 | _                 | _                 | —                 | _                 | -                | —                |

| 15.0         | R/W-0             | U-0               | R/W-0             | R/W-0             | R-0               | U-0               | U-0              | U-0              |

| 15:8         | ON <sup>(1)</sup> | —                 | SIDL              | TWDIS             | TWIP              | -                 |                  | —                |

| 7.0          | R/W-0             | U-0               | R/W-0             | R/W-0             | U-0               | R/W-0             | R/W-0            | U-0              |

| 7:0          | TGATE             | —                 | TCKPS             | S<1:0>            | _                 | TSYNC             | TCS              | —                |

#### REGISTER 13-1: T1CON: TYPE A TIMER CONTROL REGISTER

#### Legend:

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, r | ead as '0'         |

|-------------------|------------------|--------------------------|--------------------|

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared     | x = Bit is unknown |

#### bit 31-16 Unimplemented: Read as '0'

- bit 15 **ON:** Timer On bit<sup>(1)</sup>

- 1 = Timer is enabled 0 = Timer is disabled

#### bit 14 Unimplemented: Read as '0'

#### bit 13 **SIDL:** Stop in Idle Mode bit

- 1 = Discontinue operation when device enters Idle mode

- 0 = Continue operation when device is in Idle mode

### bit 12 **TWDIS:** Asynchronous Timer Write Disable bit

- 1 = Writes to TMR1 are ignored until pending write operation completes

- 0 = Back-to-back writes are enabled (Legacy Asynchronous Timer functionality)

#### bit 11 TWIP: Asynchronous Timer Write in Progress bit

In Asynchronous Timer mode:

1 = Asynchronous write to TMR1 register in progress

0 = Asynchronous write to TMR1 register complete

In Synchronous Timer mode:

This bit is read as '0'.

- bit 10-8 **Unimplemented:** Read as '0'

- bit 7 TGATE: Timer Gated Time Accumulation Enable bit

<u>When TCS = 1:</u> This bit is ignored.

When TCS = 0:

- 1 = Gated time accumulation is enabled

- 0 =Gated time accumulation is disabled

- bit 6 Unimplemented: Read as '0'

- bit 5-4 TCKPS<1:0>: Timer Input Clock Prescale Select bits

- 11 = 1:256 prescale value

- 10 = 1:64 prescale value

- 01 = 1:8 prescale value

- 00 = 1:1 prescale value

- **Note 1:** When using the 1:1 PBCLK divisor, the user's software should not read/write the peripheral SFRs in the SYSCLK cycle immediately following the instruction that clears the module's ON bit.

### 14.2 Control Registers

| TABLE 14-1: | TIMER2 THROUGH TIMER5 REGISTER MAP |

|-------------|------------------------------------|

|             |                                    |

|                             |                                 | ••            |       |       |       |       |       |       |      |          |            |      |                |          |      |      |                         |      |            |

|-----------------------------|---------------------------------|---------------|-------|-------|-------|-------|-------|-------|------|----------|------------|------|----------------|----------|------|------|-------------------------|------|------------|

| ess                         |                                 |               |       |       |       |       |       |       |      | В        | ts         |      |                |          |      |      |                         |      |            |

| Virtual Address<br>(BF80_#) | Register<br>Name <sup>(1)</sup> | Bit Range     | 31/15 | 30/14 | 29/13 | 28/12 | 27/11 | 26/10 | 25/9 | 24/8     | 23/7       | 22/6 | 21/5           | 20/4     | 19/3 | 18/2 | 17/1                    | 16/0 | All Resets |

| 0800                        | T2CON                           | 31:16         | —     | _     | —     | —     |       | —     |      |          | —          | —    | —              |          | —    | -    | —                       |      | 0000       |

| 0800                        | 12001                           | 15:0          | ON    | _     | SIDL  | _     | -     | —     | 1    |          | TGATE      |      | TCKPS<2:0>     |          | T32  |      | TCS <sup>(2)</sup>      |      | 0000       |

| 0810                        | TMR2                            | 31:16         | _     | —     | —     | —     | _     | —     | _    | —        | —          | _    | —              | _        | —    | —    | —                       | _    | 0000       |

| 0010                        | T IVIT VZ                       | 15:0          |       |       | -     |       |       |       |      | TMR2     | <15:0>     |      |                |          | -    |      |                         |      | 0000       |

| 0820                        | PR2                             | 31:16         | —     | —     | —     | —     | —     | —     | —    | —        | —          | —    | —              | —        | —    | —    | —                       | —    | 0000       |

| 0020                        | 1112                            | 15:0          |       |       |       |       |       |       |      | PR2<     | 15:0>      |      | •              |          |      |      |                         |      | FFFF       |

| 0A00                        | T3CON                           | 31:16         | —     | —     | —     | —     | —     | —     | —    | _        | —          | —    | —              | —        | —    | —    | —                       | —    | 0000       |

| 0,100                       | 100011                          | 15:0          | ON    | —     | SIDL  | _     | _     | —     | _    | _        | TGATE      |      | TCKPS<2:0>     | <b>`</b> | —    | —    | TCS <sup>(2)</sup>      | _    | 0000       |

| 0A10                        | TMR3                            | 31:16         | —     | —     | —     | _     | —     | —     | —    | —        | —          | —    | —              | —        | —    | —    | —                       | —    | 0000       |

|                             |                                 | 15:0          |       |       | 1     |       |       |       |      | TMR3     | <15:0>     |      |                |          |      |      |                         |      | 0000       |

| 0A20                        | PR3                             | 31:16         | —     | —     | —     | —     | —     | —     | —    | —        | —          | —    | —              | —        | —    | —    | —                       | —    | 0000       |

|                             | -                               | 15:0          |       |       |       |       |       |       |      | PR3<     | 15:0>      |      | -              |          |      |      |                         |      | FFFF       |

| 0C00                        | T4CON                           | 31:16         | _     | —     | —     | —     | —     | —     | —    | —        | —          | —    | —              | —        |      | —    |                         | —    | 0000       |

|                             |                                 | 15:0          | ON    | _     | SIDL  | —     | _     | _     |      | _        | TGATE      |      | TCKPS<2:0>     | >        | T32  | _    | TCS <sup>(2)</sup>      | _    | 0000       |

| 0C10                        | TMR4                            | 31:16         | —     | —     |       | —     | —     | —     | _    |          |            | —    | —              | —        |      | _    | —                       | _    | 0000       |

|                             |                                 | 15:0          |       |       |       |       |       |       |      | TMR4     |            |      |                |          |      |      |                         |      | 0000       |

| 0C20                        | PR4                             | 31:16         | -     | —     | —     | —     | _     | _     | _    | -        | -          | _    | —              | _        | —    | _    | —                       | —    | 0000       |

|                             |                                 | 15:0          | _     |       |       | _     |       |       |      | PR4<     |            |      |                | _        |      | _    | _                       | _    | FFFF       |

| 0E00                        | T5CON                           | 31:16<br>15:0 | ON    |       |       |       |       |       |      |          | —<br>TGATE |      | <br>TCKPS<2:0> |          |      |      | —<br>TCS <sup>(2)</sup> |      | 0000       |

| <u> </u>                    |                                 | 31:16         | - UN  |       | SIDL  |       |       |       |      | _        | IGATE      | _    |                | ,<br>    | _    |      | -                       | _    | 0000       |

| 0E10                        | TMR5                            | 15:0          |       |       |       |       |       |       |      |          | 0000       |      |                |          |      |      |                         |      |            |

|                             |                                 | 31:16         | _     | _     |       | _     | _     | _     | _    | —        |            | _    | _              | _        | _    | _    | _                       | _    | 0000       |

| 0E20                        | PR5                             | 15:0          |       |       |       |       |       |       |      | <br>PR5< |            |      | _              |          |      |      |                         |      | FFFF       |

|                             |                                 | 13.0          |       |       |       |       |       |       |      | 11/04    | 10.02      |      |                |          |      |      |                         |      | LLLL       |

Legend: x = unknown value on Reset; — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

Note 1: All registers in this table have corresponding CLR, SET and INV registers at their virtual addresses, plus offsets of 0x4, 0x8 and 0xC, respectively. See Section 12.1.1 "CLR, SET and INV Registers" for more information.

2: These bits are not available on 64-pin devices.

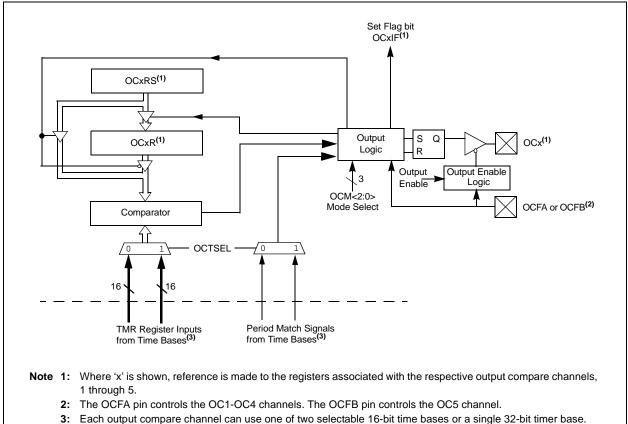

### 17.0 OUTPUT COMPARE

Note: This data sheet summarizes the features of the PIC32MX5XX/6XX/7XX family of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to **Section 16. "Output Compare"** (DS60001111) in the *"PIC32 Family Reference Manual"*, which is available from the Microchip web site (www.microchip.com/PIC32).

The Output Compare module is used to generate a single pulse or a series of pulses in response to selected time base events. For all modes of operation, the Output Compare module compares the values stored in the OCxR and/or the OCxRS registers to the value in the selected timer. When a match occurs, the Output Compare module generates an event based on the selected mode of operation.

The following are key features of the Output Compare module:

- Multiple Output Compare modules in a device

- Programmable interrupt generation on compare event

- Single and Dual Compare modes

- Single and continuous output pulse generation

- Pulse-Width Modulation (PWM) mode

- Hardware-based PWM Fault detection and automatic output disable

- Programmable selection of 16-bit or 32-bit time bases

- Can operate from either of two available 16-bit time bases or a single 32-bit time base

#### TABLE 19-1: I2C1THROUGH I2C5 REGISTER MAP (CONTINUED)

| ess                         |                                 |               |          |        |                              |        | •      |                   | -             | Bi      | ts    |             |             |           |          |        |      |          |            |

|-----------------------------|---------------------------------|---------------|----------|--------|------------------------------|--------|--------|-------------------|---------------|---------|-------|-------------|-------------|-----------|----------|--------|------|----------|------------|

| Virtual Address<br>(BF80_#) | Register<br>Name <sup>(1)</sup> | Bit Range     | 31/15    | 30/14  | 29/13                        | 28/12  | 27/11  | 26/10             | 25/9          | 24/8    | 23/7  | 22/6        | 21/5        | 20/4      | 19/3     | 18/2   | 17/1 | 16/0     | All Resets |

| 5230                        | I2C5MSK                         | 31:16         | -        | —      | —                            | _      |        | _                 | —             | -       | _     | _           |             | _         | —        | —      | _    |          | 0000       |

| 5230                        | IZCONISK                        | 15:0          | -        | —      | —                            | -      |        | _                 |               |         |       |             | MSK         | <9:0>     |          |        |      | -        | 0000       |

| 5240                        | I2C5BRG                         | 31:16         | _        | _      | _                            | —      | _      | —                 | —             | —       | _     | —           | _           | —         | —        |        | -    |          | 0000       |

| 5240                        |                                 | 15:0          | —        | —      | Baud Rate Generator Register |        |        |                   |               |         | •     |             | 0000        |           |          |        |      |          |            |

| 5250                        | I2C5TRN                         | 31:16         | —        | —      | —                            | —      | _      | —                 | _             | —       | _     | —           | —           | —         | —        |        | —    | —        | 0000       |

| 0200                        |                                 | 15:0          | —        | _      | _                            | —      | _      | —                 | _             | _       |       | -           |             | Transmit  | Register |        | •    |          | 0000       |

| 5260                        | I2C5RCV                         | 31:16         | -        |        |                              | _      | _      | -                 |               | _       | _     | —           | _           | —         |          | _      | —    | _        | 0000       |

|                             |                                 | 15:0          | -        |        | —                            | —      |        | —                 |               | _       |       |             |             | Receive   | Register |        |      |          | 0000       |

| 5300                        | I2C1CON                         | 31:16         | _        | —      | —                            | —      | —      | —                 | —             | —       | —     | —           | —           | —         | —        | —      | —    | —        | 0000       |

|                             |                                 | 15:0          | ON       | _      | SIDL                         | SCLREL | STRICT | A10M              | DISSLW        | SMEN    | GCEN  | STREN       | ACKDT       | ACKEN     | RCEN     | PEN    | RSEN | SEN      | 1000       |

| 5310                        | I2C1STAT                        | 31:16         | —        | _      | _                            | _      | _      | _                 | —             | —       | _     | —           | —           | _         | _        |        | —    | —        | 0000       |

|                             |                                 |               | ACKSTAT  | TRSTAT | —                            | —      | —      | BCL               | GCSTAT        | ADD10   | IWCOL | I2COV       | D/A         | Р         | S        | R/W    | RBF  | TBF      | 0000       |

| 5320                        | I2C1ADD                         | 31:16         | _        |        |                              |        |        |                   |               |         | —     | —           | 0000        |           |          |        |      |          |            |

|                             |                                 |               | ADD<9:0> |        |                              |        |        | 0000              |               |         |       |             |             |           |          |        |      |          |            |

| 5330                        | I2C1MSK                         | 31:16         | _        | _      | _                            | _      | _      | -                 | _             | -       | _     | _           | —           | -         | _        | -      | —    | —        | 0000       |

|                             |                                 | 15:0          | _        |        | _                            | _      |        | _                 |               |         |       |             | MSK         | <9:0>     |          |        |      |          | 0000       |

| 5340                        | I2C1BRG                         | 31:16         | _        |        |                              | —      | _      | —                 |               | _       | -     | -           |             | _         | —        |        | -    | _        | 0000       |

| -                           |                                 | 15:0          | _        |        |                              | —      |        |                   |               |         | Ва    | ud Rate Ger | Ū.          | ster      |          |        | 1    |          | 0000       |

| 5350                        | I2C1TRN                         | 31:16         | _        | —      | —                            | _      | _      | _                 | _             | _       | _     | _           | —           |           | —        | —      | —    | —        | 0000       |

|                             |                                 | 15:0          | _        | _      | _                            | _      | _      | _                 |               | _       |       |             |             | Transmit  | Register |        |      |          | 0000       |

| 5360                        | I2C1RCV                         | 31:16<br>15:0 | _        | _      |                              |        |        | —                 |               |         | —     | —           | —           | - Deseive | Register | —      | —    | —        | 0000       |

|                             |                                 |               |          |        |                              |        |        | _                 |               |         |       |             |             | Receive   |          |        |      |          |            |

| 5400                        | 12C2CON(2)                      | 31:16<br>15:0 | ON       |        | -                            | -      |        | -                 | —<br>DI001144 | -       | -     | —<br>STREN  | —<br>ACKDT  |           |          | -      |      | -        | 0000       |

|                             |                                 |               |          | _      | SIDL                         | SCLREL | STRICT | A10M              | DISSLW        | SMEN    | GCEN  |             |             |           |          | PEN    | RSEN | SEN      | 1000       |

| 5410                        | 12C2STAT <sup>(2)</sup>         | 31:16         |          |        | _                            | _      | _      | —<br>DCI          | —<br>         | -       | -     | -           | —<br>D/A    | —<br>P    | -        | —<br>• | -    | —<br>TDF | 0000       |

|                             |                                 | 15:0<br>31:16 | ACKSTAT  | TRSTAT |                              | _      | _      | BCL               | GCSTAT        | ADD10   | IWCOL | I2COV       | D/A         | Р         | S        | R/W    | RBF  | TBF      | 0000       |

| 5420                        | 12C2ADD(2)                      | 15:0          |          |        |                              | _      | _      |                   | _             | -       | —     | —           |             | <br><9:0> | —        |        | _    | —        | 0000       |

|                             |                                 | 31:16         | _        |        |                              | _      |        | _                 | _             |         | _     |             | ADD         | <9.0>     |          |        | _    | _        | 0000       |

| 5430                        | 12C2MSK <sup>(2)</sup>          | 15:0          |          |        |                              |        |        |                   | _             | _       | _     | _           | <br>MSK     | <0.0>     | _        |        | _    | _        | 0000       |

|                             |                                 | 31:16         |          |        |                              |        |        |                   |               |         | _     |             |             | < 3.02    |          |        |      | _        | 0000       |

| 5440                        | I2C2BRG <sup>(2)</sup>          | 15:0          | _        |        |                              | _      | _      | _                 | _             |         | Ra    | ud Rate Ger | erator Regi | ster      | _        |        |      |          | 0000       |

|                             |                                 | 31:16         | _        | _      | _                            | _      | _      | _                 | _             | _       | Da    |             |             |           | _        |        | _    | _        | 0000       |

| 5450                        | I2C2TRN <sup>(2)</sup>          | 15:0          | _        | _      | _                            |        | _      |                   | _             |         |       |             |             | Transmit  | Register |        |      |          | 0000       |

|                             |                                 | 31:16         | _        | _      | _                            | _      |        | _                 | _             | _       | _     | _           | _           |           |          |        | _    | _        | 0000       |

| 5460                        | 12C2RCV <sup>(2)</sup>          | 15:0          | _        | _      | _                            | _      | _      | _                 | _             | _       |       |             |             | Receive   | Register |        |      |          | 0000       |

| Legen                       |                                 |               |          |        |                              |        |        | L<br>ues are show | l<br>         | aire al |       |             |             | 110001100 |          |        |      |          | 0000       |

Legend: x = unknown value on Reset; --- = unimplemented, read as '0'. Reset values are shown in hexadecimal.

Note 1: All registers in this table except I2CxRCV have corresponding CLR, SET and INV registers at their virtual addresses, plus offsets of 0x4, 0x8 and 0xC, respectively. See Section 12.1.1 "CLR, SET and INV Registers" for more information.

2: This register is not available on 64-pin devices.

#### REGISTER 24-11: CIFLTCON1: CAN FILTER CONTROL REGISTER 1 (CONTINUED)

| bit 15    | FLTEN5: Filter 17 Enable bit                                                                           |

|-----------|--------------------------------------------------------------------------------------------------------|

|           | 0 = Filter is disabled                                                                                 |

| bit 14-13 | MSEL5<1:0>: Filter 5 Mask Select bits                                                                  |

|           | 11 = Acceptance Mask 3 selected                                                                        |

|           | 10 = Acceptance Mask 2 selected                                                                        |

|           | 01 = Acceptance Mask 1 selected<br>00 = Acceptance Mask 0 selected                                     |

| bit 12-8  | FSEL5<4:0>: FIFO Selection bits                                                                        |

|           | 11111 = Message matching filter is stored in FIFO buffer 31                                            |

|           | 11110 = Message matching filter is stored in FIFO buffer 30                                            |

|           | •                                                                                                      |

|           | •                                                                                                      |

|           | 00001 = Message matching filter is stored in FIFO buffer 1                                             |

|           | 00000 = Message matching filter is stored in FIFO buffer 0                                             |

| bit 7     | FLTEN4: Filter 4 Enable bit                                                                            |

|           | <ul><li>1 = Filter is enabled</li><li>0 = Filter is disabled</li></ul>                                 |

| bit 6-5   | MSEL4<1:0>: Filter 4 Mask Select bits                                                                  |

|           | 11 = Acceptance Mask 3 selected                                                                        |

|           | 10 = Acceptance Mask 2 selected                                                                        |

|           | 01 = Acceptance Mask 1 selected<br>00 = Acceptance Mask 0 selected                                     |

| bit 4-0   | FSEL4<4:0>: FIFO Selection bits                                                                        |

|           | 11111 = Message matching filter is stored in FIFO buffer 31                                            |

|           | 11110 = Message matching filter is stored in FIFO buffer 30                                            |

|           | •                                                                                                      |

|           | •                                                                                                      |

|           | 00001 = Message matching filter is stored in FIFO buffer 1                                             |

|           | 00000 = Message matching filter is stored in FIFO buffer 0                                             |

| Note:     | The bits in this register can only be modified if the corresponding filter enable (FLTENn) bit is '0'. |

#### **REGISTER 25-13: ETHIEN: ETHERNET CONTROLLER INTERRUPT ENABLE REGISTER**

| Bit<br>Range | Bit<br>31/23/15/7       | Bit<br>30/22/14/6        | Bit<br>29/21/13/5       | Bit<br>28/20/12/4 | Bit<br>27/19/11/3       | Bit<br>26/18/10/2        | Bit<br>25/17/9/1         | Bit<br>24/16/8/0         |

|--------------|-------------------------|--------------------------|-------------------------|-------------------|-------------------------|--------------------------|--------------------------|--------------------------|

| 31:24        | U-0                     | U-0                      | U-0                     | U-0               | U-0                     | U-0                      | U-0                      | U-0                      |

| 31.24        |                         | —                        |                         | —                 |                         |                          |                          | —                        |

| 23:16        | U-0                     | U-0                      | U-0                     | U-0               | U-0                     | U-0                      | U-0                      | U-0                      |

| 23.10        | _                       | —                        | _                       | —                 |                         | _                        | —                        | —                        |

| 15:8         | U-0                     | R/W-0                    | R/W-0                   | U-0               | U-0                     | U-0                      | R/W-0                    | R/W-0                    |

| 10.0         | —                       | TXBUSEIE <sup>(1)</sup>  | RXBUSEIE <sup>(2)</sup> | _                 | _                       | —                        | EWMARKIE <sup>(2)</sup>  | FWMARKIE <sup>(2)</sup>  |

| 7:0          | R/W-0                   | R/W-0                    | R/W-0                   | U-0               | R/W-0                   | R/W-0                    | R/W-0                    | R/W-0                    |

| 7.0          | RXDONEIE <sup>(2)</sup> | PKTPENDIE <sup>(2)</sup> | RXACTIE <sup>(2)</sup>  |                   | TXDONEIE <sup>(1)</sup> | TXABORTIE <sup>(1)</sup> | RXBUFNAIE <sup>(2)</sup> | RXOVFLWIE <sup>(2)</sup> |

#### Legend:

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, r | ead as '0'         |

|-------------------|------------------|--------------------------|--------------------|

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared     | x = Bit is unknown |

bit 31-15 Unimplemented: Read as '0'

- bit 14 **TXBUSEIE:** Transmit BVCI Bus Error Interrupt Enable bit<sup>(1)</sup>

- 1 = Enable TXBUS Error Interrupt

- 0 = Disable TXBUS Error Interrupt

- bit 13 **RXBUSEIE:** Receive BVCI Bus Error Interrupt Enable bit<sup>(2)</sup>

- 1 = Enable RXBUS Error Interrupt 0 = Disable RXBUS Error Interrupt

- 0 = Disable RABOS Efformetry

- bit 12-10 Unimplemented: Read as '0'

| bit 9 | <b>EWMARKIE:</b> Empty Watermark Interrupt Enable bit <sup>(2)</sup><br>1 = Enable EWMARK Interrupt<br>0 = Disable EWMARK Interrupt                 |

|-------|-----------------------------------------------------------------------------------------------------------------------------------------------------|

| bit 8 | <b>FWMARKIE:</b> Full Watermark Interrupt Enable bit <sup>(2)</sup><br>1 = Enable FWMARK Interrupt<br>0 = Disable FWMARK Interrupt                  |

| bit 7 | <b>RXDONEIE:</b> Receiver Done Interrupt Enable bit <sup>(2)</sup><br>1 = Enable RXDONE Interrupt<br>0 = Disable RXDONE Interrupt                   |

| bit 6 | PKTPENDIE: Packet Pending Interrupt Enable bit <sup>(2)</sup><br>1 = Enable PKTPEND Interrupt<br>0 = Disable PKTPEND Interrupt                      |

| bit 5 | <b>RXACTIE:</b> RX Activity Interrupt Enable bit<br>1 = Enable RXACT Interrupt<br>0 = Disable RXACT Interrupt                                       |

| bit 4 | Unimplemented: Read as '0'                                                                                                                          |

| bit 3 | <b>TXDONEIE:</b> Transmitter Done Interrupt Enable bit <sup>(1)</sup><br>1 = Enable TXDONE Interrupt<br>0 = Disable TXDONE Interrupt                |

| bit 2 | <b>TXABORTIE:</b> Transmitter Abort Interrupt Enable bit <sup>(1)</sup><br>1 = Enable TXABORT Interrupt<br>0 = Disable TXABORT Interrupt            |

| bit 1 | <b>RXBUFNAIE:</b> Receive Buffer Not Available Interrupt Enable bit <sup>(2)</sup><br>1 = Enable RXBUFNA Interrupt<br>0 = Disable RXBUFNA Interrupt |

| bit 0 | <b>RXOVFLWIE:</b> Receive FIFO Overflow Interrupt Enable bit <sup>(2)</sup><br>1 = Enable RXOVFLW Interrupt<br>0 = Disable RXOVFLW Interrupt        |

- **Note 1:** This bit is only used for TX operations.

- **2:** This bit is only used for RX operations.

#### REGISTER 25-18: ETHSCOLFRM: ETHERNET CONTROLLER SINGLE COLLISION FRAMES STATISTICS REGISTER

| Bit Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |  |

|-----------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|--|--|

| 31:24     | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |  |  |

| 31.24     | -                 | —                 | _                 | —                 | -                 | —                 | _                | —                |  |  |

| 22.46     | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |  |  |

| 23:16     | _                 | —                 | _                 | _                 | _                 | —                 | _                | —                |  |  |

| 15.0      | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |

| 15:8      | SCOLFRMCNT<15:8>  |                   |                   |                   |                   |                   |                  |                  |  |  |

| 7.0       | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |

| 7:0       | SCOLFRMCNT<7:0>   |                   |                   |                   |                   |                   |                  |                  |  |  |

### Legend:

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, | read as '0'        |  |

|-------------------|------------------|------------------------|--------------------|--|

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared   | x = Bit is unknown |  |

#### bit 31-16 Unimplemented: Read as '0'

bit 15-0 **SCOLFRMCNT<15:0>:** Single Collision Frame Count bits Increment count for frames that were successfully transmitted on the second try.

Note 1: This register is only used for TX operations.

2: This register is automatically cleared by hardware after a read operation, unless the byte enables for bytes 0/1 are '0'.

**3:** It is recommended to use the SET, CLR, or INV registers to set or clear any bit in this register. Setting or clearing any bits in this register should only be done for debug/test purposes.

#### REGISTER 25-33: EMAC1MADR: ETHERNET CONTROLLER MAC MII MANAGEMENT ADDRESS REGISTER

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|--|

| 31:24        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |  |

| 31.24        |                   | _                 |                   | —                 | _                 | —                 | -                | —                |  |

| 23:16        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |  |

| 23.10        | —                 | _                 | —                 | —                 | _                 | —                 | _                | —                |  |

| 15:8         | U-0               | U-0               | U-0               | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-1            |  |

| 10.0         | —                 | _                 | —                 | PHYADDR<4:0>      |                   |                   |                  |                  |  |

| 7.0          | U-0               | U-0               | U-0               | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |

| 7:0          |                   | _                 |                   | REGADDR<4:0>      |                   |                   |                  |                  |  |

#### Legend:

| 0                 |                  |                                    |                    |  |  |

|-------------------|------------------|------------------------------------|--------------------|--|--|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read as '0' |                    |  |  |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared               | x = Bit is unknown |  |  |

#### bit 31-13 Unimplemented: Read as '0'

- bit 12-8 **PHYADDR<4:0>:** MII Management PHY Address bits This field represents the 5-bit PHY Address field of Management cycles. Up to 31 PHYs can be addressed (0 is reserved).

- bit 7-5 Unimplemented: Read as '0'

- bit 4-0 **REGADDR<4:0>:** MII Management Register Address bits This field represents the 5-bit Register Address field of Management cycles. Up to 32 registers can be accessed.

**Note:** Both 16-bit and 32-bit accesses are allowed to these registers (including the SET, CLR and INV registers). 8-bit accesses are not allowed and are ignored by the hardware.

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|

| 31:24        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 31.24        | —                 | —                 |                   | —                 | —                 | —                 |                  | —                |

| 22:46        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 23:16        |                   | -                 |                   | —                 | —                 |                   |                  | —                |

| 15:8         | U-0               | U-0               | R/W-0             | U-0               | U-0               | U-0               | U-0              | U-0              |

| 15.6         | —                 | —                 | SIDL              | —                 | —                 | —                 |                  | —                |

| 7:0          | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | R-0              | R-0              |

| 7:0          | —                 | —                 | —                 | —                 |                   | —                 | C2OUT            | C1OUT            |

#### REGISTER 26-2: CMSTAT: COMPARATOR STATUS REGISTER

| -   | -    |  |

|-----|------|--|

|     | ond  |  |

| Leu | ena: |  |

|     |      |  |

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read as '0' |                    |  |  |  |

|-------------------|------------------|------------------------------------|--------------------|--|--|--|

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared               | x = Bit is unknown |  |  |  |

#### bit 31-14 Unimplemented: Read as '0'

- bit 13 SIDL: Stop in Idle Control bit

- 1 = All Comparator modules are disabled while in Idle mode

- 0 = All Comparator modules continue to operate while in Idle mode

#### bit 12-2 Unimplemented: Read as '0'

- bit 1 **C2OUT:** Comparator Output bit

- 1 = Output of Comparator 2 is a '1'

- 0 = Output of Comparator 2 is a '0'

- bit 0 C1OUT: Comparator Output bit

- 1 = Output of Comparator 1 is a '1'

- 0 = Output of Comparator 1 is a '0'

#### TABLE 32-5: DC CHARACTERISTICS: OPERATING CURRENT (IDD) (CONTINUED)

| DC CHA        | RACTERIST                                                                          | ICS  | $\begin{array}{l} \mbox{Standard Operating Conditions: 2.3V to 3.6V} \\ \mbox{(unless otherwise stated)} \\ \mbox{Operating temperature} & -40^{\circ}C \leq TA \leq +85^{\circ}C \mbox{ for Industrial} \\ & -40^{\circ}C \leq TA \leq +105^{\circ}C \mbox{ for V-Temp} \end{array}$ |                           |                           |      |                           |  |  |  |

|---------------|------------------------------------------------------------------------------------|------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------|---------------------------|------|---------------------------|--|--|--|

| Param.<br>No. | Typical <sup>(3)</sup>                                                             | Max. | Units                                                                                                                                                                                                                                                                                 | nits Conditions           |                           |      |                           |  |  |  |

| Operatir      | Operating Current (IDD) <sup>(1,2)</sup> for PIC32MX534/564/664/764 Family Devices |      |                                                                                                                                                                                                                                                                                       |                           |                           |      |                           |  |  |  |

| DC20c         | 6                                                                                  | 9    | mA                                                                                                                                                                                                                                                                                    | Code executing from Flash | -40ºC,<br>+25ºC,<br>+85ºC |      | 4 MHz                     |  |  |  |

| DC20d         | 7                                                                                  | 10   |                                                                                                                                                                                                                                                                                       |                           | +105⁰C                    |      |                           |  |  |  |

| DC20e         | 2                                                                                  |      |                                                                                                                                                                                                                                                                                       | Code executing from SRAM  |                           |      |                           |  |  |  |

| DC21b         | 19                                                                                 | 32   | ~^^                                                                                                                                                                                                                                                                                   | Code executing from Flash |                           |      | 25 MHz                    |  |  |  |

| DC21c         | 14                                                                                 | _    | mA                                                                                                                                                                                                                                                                                    | Code executing from SRAM  |                           | _    | (Note 4)                  |  |  |  |

| DC22b         | 31                                                                                 | 50   | ~^^                                                                                                                                                                                                                                                                                   | Code executing from Flash |                           |      | 60 MHz                    |  |  |  |

| DC22c         | 29                                                                                 | _    | mA                                                                                                                                                                                                                                                                                    | Code executing from SRAM  |                           |      | (Note 4)                  |  |  |  |

| DC23c         | 39                                                                                 | 65   | mA                                                                                                                                                                                                                                                                                    | Code executing from Flash | -40⁰C,<br>+25⁰C,<br>+85⁰C |      | 80 MHz                    |  |  |  |

| DC23d         | 49                                                                                 | 70   |                                                                                                                                                                                                                                                                                       |                           | +105⁰C                    |      |                           |  |  |  |

| DC23e         | 39                                                                                 | _    | 1                                                                                                                                                                                                                                                                                     | Code executing from SRAM  | _                         |      |                           |  |  |  |

| DC25b         | 100                                                                                | 150  | μA                                                                                                                                                                                                                                                                                    | _                         | +25°C                     | 3.3V | LPRC (31 kHz)<br>(Note 4) |  |  |  |

**Note 1:** A device's IDD supply current is mainly a function of the operating voltage and frequency. Other factors, such as PBCLK (Peripheral Bus Clock) frequency, number of peripheral modules enabled, internal code execution pattern, execution from Program Flash memory vs. SRAM, I/O pin loading and switching rate, oscillator type, as well as temperature, can have an impact on the current consumption.

- **2:** The test conditions for IDD measurements are as follows:

- Oscillator mode is EC (for 8 MHz and below) and EC+PLL (for above 8 MHz) with OSC1 driven by external square wave from rail-to-rail, (OSC1 input clock input over/undershoot < 100 mV required)</li>

- OSC2/CLKO is configured as an I/O input pin

- USB PLL oscillator is disabled if the USB module is implemented, PBCLK divisor = 1:8

- CPU, program Flash, and SRAM data memory are operational, program Flash memory Wait states = 111, Program Cache and Prefetch are disabled and SRAM data memory Wait states = 1

- No peripheral modules are operating, (ON bit = 0)

- WDT, Clock Switching, Fail-Safe Clock Monitor, and Secondary Oscillator are disabled

- All I/O pins are configured as inputs and pulled to Vss

- MCLR = VDD

- CPU executing while(1) statement from Flash

- RTCC and JTAG are disabled

- **3:** Data in "Typical" column is at 3.3V, 25°C at specified operating frequency unless otherwise stated. Parameters are for design guidance only and are not tested.

- **4:** All parameters are characterized, but only those parameters listed for 4 MHz and 80 MHz are tested at 3.3V in manufacturing.

#### TABLE 32-24: TIMER2, 3, 4, 5 EXTERNAL CLOCK TIMING REQUIREMENTS

| AC CHARACTERISTICS (unles |           |                          |                             |                  | Standard Operating Conditions: 2.3V to 3.6V<br>unless otherwise stated)<br>Operating temperature $-40^{\circ}C \le TA \le +85^{\circ}C$ for Industrial<br>$-40^{\circ}C \le TA \le +105^{\circ}C$ for V-Temp |      |       |                                     |                       |

|---------------------------|-----------|--------------------------|-----------------------------|------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|-------|-------------------------------------|-----------------------|

| Param.<br>No.             | Symbol    | Chai                     | racteristic                 | s <sup>(1)</sup> | Min.                                                                                                                                                                                                         | Max. | Units | Condit                              | ions                  |

| TB10                      | ТтхН      | TxCK<br>High Time        | Synchronous, with prescaler |                  | [(12.5 ns or 1 TPB)/N]<br>+ 25 ns                                                                                                                                                                            | —    | ns    | Must also meet<br>parameter<br>TB15 | value<br>(1, 2, 4, 8, |

| TB11                      | ΤτxL      | TxCK<br>Low Time         | Synchrono<br>prescaler      | ous, with        | [(12.5 ns or 1 ТРВ)/N]<br>+ 25 ns                                                                                                                                                                            |      | ns    | Must also meet<br>parameter<br>TB15 | 16, 32, 64,<br>256)   |

| TB15                      | ΤτχΡ      | TxCK<br>Input            | Synchronous, with prescaler |                  | [(Greater of [(25 ns or<br>2 Трв)/N] + 30 ns                                                                                                                                                                 | _    | ns    | VDD > 2.7V                          |                       |

| P                         |           | Period                   | Period                      |                  | [(Greater of [(25 ns or<br>2 Трв)/N] + 50 ns                                                                                                                                                                 | —    | ns    | VDD < 2.7V                          |                       |

| TB20                      | TCKEXTMRL | Delay from<br>Clock Edge |                             |                  | _                                                                                                                                                                                                            | 1    | Трв   |                                     |                       |

Note 1: These parameters are characterized, but not tested in manufacturing.

#### TABLE 32-35: ETHERNET MODULE SPECIFICATIONS

| АС СНА                   | RACTERISTICS                        | $\begin{tabular}{lllllllllllllllllllllllllllllllllll$ |         |      |       |                  |  |  |  |

|--------------------------|-------------------------------------|-------------------------------------------------------|---------|------|-------|------------------|--|--|--|

| Param.<br>No.            | Characteristic                      | Min.                                                  | Typical | Max. | Units | Conditions       |  |  |  |

| MIIM Timing Requirements |                                     |                                                       |         |      |       |                  |  |  |  |

| ET1                      | MDC Duty Cycle                      | 40                                                    |         | 60   | %     | —                |  |  |  |

| ET2                      | MDC Period                          | 400                                                   | —       | _    | ns    | —                |  |  |  |

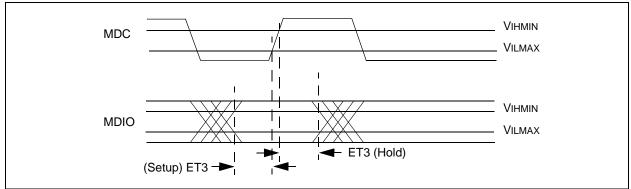

| ET3                      | MDIO Output Setup and Hold          | 10                                                    | —       | 10   | ns    | See Figure 32-19 |  |  |  |

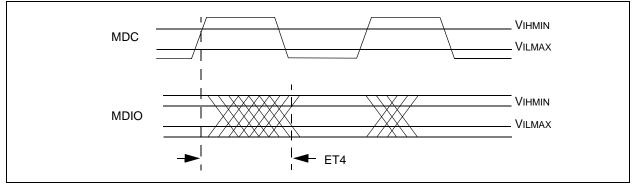

| ET4                      | MDIO Input Setup and Hold           | 0                                                     | —       | 300  | ns    | See Figure 32-20 |  |  |  |

| MII Timi                 | ng Requirements                     |                                                       |         |      |       |                  |  |  |  |

| ET5                      | TX Clock Frequency                  | —                                                     | 25      | _    | MHz   | —                |  |  |  |

| ET6                      | TX Clock Duty Cycle                 | 35                                                    | —       | 65   | %     | —                |  |  |  |

| ET7                      | ETXDx, ETEN, ETXERR Output Delay    | 0                                                     | —       | 25   | ns    | See Figure 32-21 |  |  |  |

| ET8                      | RX Clock Frequency                  | —                                                     | 25      | _    | MHz   | —                |  |  |  |

| ET9                      | RX Clock Duty Cycle                 | 35                                                    | —       | 65   | %     | —                |  |  |  |

| ET10                     | ERXDx, ERXDV, ERXERR Setup and Hold | 10                                                    | —       | 30   | ns    | See Figure 32-22 |  |  |  |

| RMII Tin                 | ning Requirements                   |                                                       |         |      |       |                  |  |  |  |

| ET11                     | Reference Clock Frequency           |                                                       | 50      | _    | MHz   | —                |  |  |  |

| ET12                     | Reference Clock Duty Cycle          | 35                                                    |         | 65   | %     | —                |  |  |  |

| ET13                     | ETXDx, ETEN, Setup and Hold         | 2                                                     | —       | 4    | ns    | —                |  |  |  |

| ET14                     | ERXDx, ERXDV, ERXERR Setup and Hold | 2                                                     | —       | 4    | ns    | —                |  |  |  |

**Note 1:** The Ethernet module is functional at VBORMIN < VDD < 2.9V, but with degraded performance. Unless otherwise stated, module functionality is tested, but not characterized.

#### FIGURE 32-19: MDIO SOURCED BY THE PIC32 DEVICE

#### FIGURE 32-20: MDIO SOURCED BY THE PHY

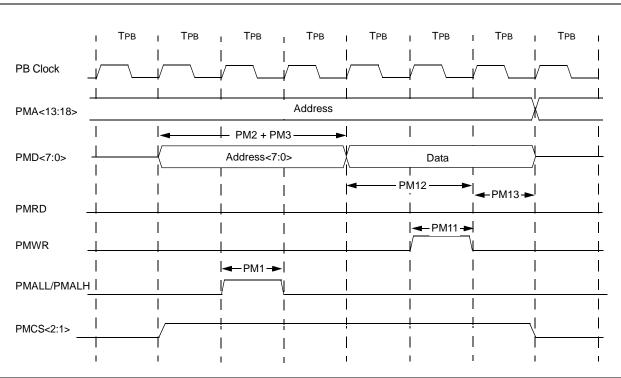

#### FIGURE 32-27: PARALLEL MASTER PORT WRITE TIMING DIAGRAM

### TABLE 32-41: PARALLEL MASTER PORT WRITE TIMING REQUIREMENTS

| АС СНА        | RACTERI | STICS                                                                     | $\begin{array}{l} \mbox{Standard Operating Conditions: 2.3V to 3.6V} \\ \mbox{(unless otherwise stated)} \\ \mbox{Operating temperature} & -40^{\circ}C \leq TA \leq +85^{\circ}C \mbox{ for Industrial} \\ & -40^{\circ}C \leq TA \leq +105^{\circ}C \mbox{ for V-Temp} \end{array}$ |         |      |       |            |

|---------------|---------|---------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------|------|-------|------------|

| Param.<br>No. | Symbol  | Characteristics <sup>(1)</sup>                                            | Min.                                                                                                                                                                                                                                                                                  | Typical | Max. | Units | Conditions |

| PM11          | Twr     | PMWR Pulse Width                                                          | _                                                                                                                                                                                                                                                                                     | 1 Трв   |      | —     | _          |

| PM12          | TDVSU   | Data Out Valid before PMWR or<br>PMENB goes Inactive (data setup<br>time) | —                                                                                                                                                                                                                                                                                     | 2 Трв   | _    | —     | _          |

| PM13          | TDVHOLD | PMWR or PMEMB Invalid to Data<br>Out Invalid (data hold time)             | —                                                                                                                                                                                                                                                                                     | 1 Трв   |      | —     | —          |

**Note 1:** These parameters are characterized, but not tested in manufacturing.

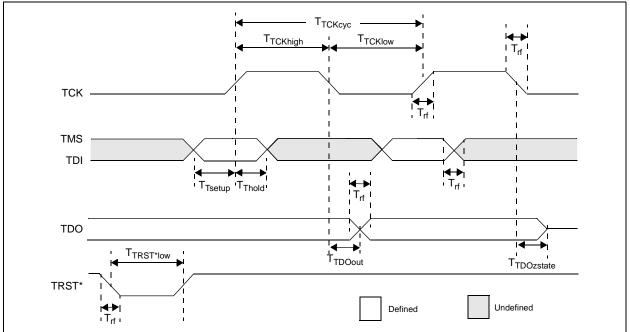

#### FIGURE 32-28: EJTAG TIMING CHARACTERISTICS

#### TABLE 32-43: EJTAG TIMING REQUIREMENTS

| AC CHA        | AC CHARACTERISTICS |                                                  |      | $\label{eq:constraint} \begin{array}{ll} \mbox{Standard Operating Conditions: 2.3V to 3.6V} \\ \mbox{(unless otherwise stated)} \\ \mbox{Operating temperature} & -40^\circ C \leq TA \leq +85^\circ C \mbox{ for Industrial} \\ & -40^\circ C \leq TA \leq +105^\circ C \mbox{ for V-Temp} \end{array}$ |       |            |  |  |  |

|---------------|--------------------|--------------------------------------------------|------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------|------------|--|--|--|

| Param.<br>No. | Symbol             | Description <sup>(1)</sup>                       | Min. | Max.                                                                                                                                                                                                                                                                                                     | Units | Conditions |  |  |  |

| EJ1           | Ттсксүс            | TCK Cycle Time                                   | 25   | _                                                                                                                                                                                                                                                                                                        | ns    |            |  |  |  |

| EJ2           | Ттскнідн           | TCK High Time                                    | 10   |                                                                                                                                                                                                                                                                                                          | ns    | —          |  |  |  |

| EJ3           | TTCKLOW            | TCK Low Time                                     | 10   |                                                                                                                                                                                                                                                                                                          | ns    | —          |  |  |  |

| EJ4           | TTSETUP            | TAP Signals Setup Time Before<br>Rising TCK      | 5    | —                                                                                                                                                                                                                                                                                                        | ns    | _          |  |  |  |

| EJ5           | TTHOLD             | TAP Signals Hold Time After<br>Rising TCK        | 3    | —                                                                                                                                                                                                                                                                                                        | ns    | _          |  |  |  |

| EJ6           | Ττροουτ            | TDO Output Delay Time from<br>Falling TCK        | —    | 5                                                                                                                                                                                                                                                                                                        | ns    | _          |  |  |  |

| EJ7           | TTDOZSTATE         | TDO 3-State Delay Time from<br>Falling TCK       | -    | 5                                                                                                                                                                                                                                                                                                        | ns    | —          |  |  |  |

| EJ8           | TTRSTLOW           | TRST Low Time                                    | 25   | _                                                                                                                                                                                                                                                                                                        | ns    | —          |  |  |  |

| EJ9           | Trf                | TAP Signals Rise/Fall Time, All Input and Output | —    | —                                                                                                                                                                                                                                                                                                        | ns    | _          |  |  |  |

Note 1: These parameters are characterized, but not tested in manufacturing.

### TABLE B-4: SECTION UPDATES (CONTINUED)

| Section Name                                                 | Update Description                                                                                                                                                                            |

|--------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7.0 "Interrupt Controller"                                   | Updated the following Interrupt Sources in Table 7-1:                                                                                                                                         |

|                                                              | - Changed IC2AM – I2C4 Master Event to: IC4M – I2C4 Master Event                                                                                                                              |

|                                                              | - Changed IC3AM – I2C5 Master Event to: IC5M – I2C4 Master Event                                                                                                                              |

|                                                              | <ul> <li>Changed U1E – UART1A Error to: U1E – UART1 Error</li> </ul>                                                                                                                          |

|                                                              | - Changed U4E – UART1B Error to: U4E – UART4 Error                                                                                                                                            |

|                                                              | - Changed U1RX – UART1A Receiver to: U1RX – UART1 Receiver                                                                                                                                    |

|                                                              | <ul> <li>Changed U4RX – UART1B Receiver to: U4RX – UART4 Receiver</li> <li>Changed U1TX – UART1A Transmitter to: U1TX – UART1 Transmitter</li> </ul>                                          |

|                                                              | <ul> <li>Changed UTTX – UART1A Transmitter to: UTTX – UART4 Transmitter</li> <li>Changed U4TX – UART1B Transmitter to: U4TX – UART4 Transmitter</li> </ul>                                    |

|                                                              | <ul> <li>Changed U6E – UART2B Error to: U6E – UART6 Error</li> </ul>                                                                                                                          |

|                                                              | - Changed U6RX – UART2B Receiver to: U6RX – UART6 Receiver                                                                                                                                    |

|                                                              | - Changed U6TX – UART2B Transmitter to: U6TX – UART6 Transmitter                                                                                                                              |

|                                                              | <ul> <li>Changed U5E – UART3B Error to: U5E – UART5 Error</li> </ul>                                                                                                                          |

|                                                              | <ul> <li>Changed U5RX – UART3B Receiver to: U5RX – UART5 Receiver</li> </ul>                                                                                                                  |

|                                                              | - Changed U5TX – UART3B Transmitter to: U5TX – UART5 Transmitter                                                                                                                              |

| 1.0 "Oscillator Configuration"                               | Updated Figure 1-1                                                                                                                                                                            |

| 1.0 "Output Compare"                                         | Updated Figure 1-1                                                                                                                                                                            |

| 1.0 "Ethernet Controller"                                    | Added a note on using the Ethernet controller pins (see note above Table 1-3)                                                                                                                 |