Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XE

| Detuns                     |                                                                                  |

|----------------------------|----------------------------------------------------------------------------------|

| Product Status             | Active                                                                           |

| Core Processor             | MIPS32® M4K™                                                                     |

| Core Size                  | 32-Bit Single-Core                                                               |

| Speed                      | 80MHz                                                                            |

| Connectivity               | Ethernet, I <sup>2</sup> C, SPI, UART/USART, USB OTG                             |

| Peripherals                | Brown-out Detect/Reset, DMA, POR, PWM, WDT                                       |

| Number of I/O              | 83                                                                               |

| Program Memory Size        | 512KB (512K x 8)                                                                 |

| Program Memory Type        | FLASH                                                                            |

| EEPROM Size                | -                                                                                |

| RAM Size                   | 128K x 8                                                                         |

| Voltage - Supply (Vcc/Vdd) | 2.3V ~ 3.6V                                                                      |

| Data Converters            | A/D 16x10b                                                                       |

| Oscillator Type            | Internal                                                                         |

| Operating Temperature      | -40°C ~ 105°C (TA)                                                               |

| Mounting Type              | Surface Mount                                                                    |

| Package / Case             | 121-TFBGA                                                                        |

| Supplier Device Package    | 121-TFBGA (10x10)                                                                |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic32mx695f512l-80v-bg |

|                            |                                                                                  |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# PIC32MX5XX/6XX/7XX

|         |                      | Pin Number <sup>(1)</sup> |     |     |             |                |                                   |  |

|---------|----------------------|---------------------------|-----|-----|-------------|----------------|-----------------------------------|--|

| Pin Nam | e 64-Pin<br>QFN/TQFP | 100-Pin<br>TQFP           |     |     | Pin<br>Type | Buffer<br>Type | Description                       |  |

| RA0     | _                    | 17                        | G3  | B9  | I/O         | ST             | PORTA is a bidirectional I/O port |  |

| RA1     | —                    | 38                        | J6  | A26 | I/O         | ST             |                                   |  |

| RA2     | —                    | 58                        | H11 | A39 | I/O         | ST             |                                   |  |

| RA3     | —                    | 59                        | G10 | B32 | I/O         | ST             |                                   |  |

| RA4     | —                    | 60                        | G11 | A40 | I/O         | ST             |                                   |  |

| RA5     | —                    | 61                        | G9  | B33 | I/O         | ST             |                                   |  |

| RA6     | —                    | 91                        | C5  | B51 | I/O         | ST             |                                   |  |

| RA7     | —                    | 92                        | B5  | A62 | I/O         | ST             |                                   |  |

| RA9     | —                    | 28                        | L2  | A21 | I/O         | ST             |                                   |  |

| RA10    |                      | 29                        | K3  | B17 | I/O         | ST             | ]                                 |  |

| RA14    |                      | 66                        | E11 | B36 | I/O         | ST             | ]                                 |  |

| RA15    | —                    | 67                        | E8  | A44 | I/O         | ST             |                                   |  |

| RB0     | 16                   | 25                        | K2  | B14 | I/O         | ST             | PORTB is a bidirectional I/O port |  |

| RB1     | 15                   | 24                        | K1  | A15 | I/O         | ST             |                                   |  |

| RB2     | 14                   | 23                        | J2  | B13 | I/O         | ST             |                                   |  |

| RB3     | 13                   | 22                        | J1  | A13 | I/O         | ST             |                                   |  |

| RB4     | 12                   | 21                        | H2  | B11 | I/O         | ST             |                                   |  |

| RB5     | 11                   | 20                        | H1  | A12 | I/O         | ST             |                                   |  |

| RB6     | 17                   | 26                        | L1  | A20 | I/O         | ST             |                                   |  |

| RB7     | 18                   | 27                        | J3  | B16 | I/O         | ST             |                                   |  |

| RB8     | 21                   | 32                        | K4  | A23 | I/O         | ST             |                                   |  |

| RB9     | 22                   | 33                        | L4  | B19 | I/O         | ST             |                                   |  |

| RB10    | 23                   | 34                        | L5  | A24 | I/O         | ST             | 1                                 |  |

| RB11    | 24                   | 35                        | J5  | B20 | I/O         | ST             | ]                                 |  |

| RB12    | 27                   | 41                        | J7  | B23 | I/O         | ST             | ]                                 |  |

| RB13    | 28                   | 42                        | L7  | A28 | I/O         | ST             | ]                                 |  |

| RB14    | 29                   | 43                        | K7  | B24 | I/O         | ST             |                                   |  |

| RB15    | 30                   | 44                        | L8  | A29 | I/O         | ST             |                                   |  |

| RC1     | —                    | 6                         | D1  | A5  | I/O         | ST             | PORTC is a bidirectional I/O port |  |

| RC2     | —                    | 7                         | E4  | B4  | I/O         | ST             |                                   |  |

| RC3     | —                    | 8                         | E2  | A6  | I/O         | ST             |                                   |  |

| RC4     |                      | 9                         | E1  | B5  | I/O         | ST             | ]                                 |  |

| RC12    | 39                   | 63                        | F9  | B34 | I/O         | ST             | ]                                 |  |

| RC13    | 47                   | 73                        | C10 | A47 | I/O         | ST             | ]                                 |  |

| RC14    | 48                   | 74                        | B11 | B40 | I/O         | ST             | ]                                 |  |

|         | -                    | 64                        | F11 | A42 | I/O         | ST             | 1                                 |  |

TTL = TTL input buffer

Note 1: Pin numbers are only provided for reference. See the "Device Pin Tables" section for device pin availability.

2: See 25.0 "Ethernet Controller" for more information.

The MIPS architecture defines that the result of a multiply or divide operation be placed in the HI and LO registers. Using the Move-From-HI (MFHI) and Move-From-LO (MFLO) instructions, these values can be transferred to the General Purpose Register file.

In addition to the HI/LO targeted operations, the MIPS32 architecture also defines a multiply instruction, MUL, which places the least significant results in the primary register file instead of the HI/LO register pair. By avoiding the explicit MFLO instruction required when using the LO register, and by supporting multiple destination registers, the throughput of multiply-intensive operations is increased.

Two other instructions, Multiply-Add (MADD) and Multiply-Subtract (MSUB), are used to perform the multiply-accumulate and multiply-subtract operations. The MADD instruction multiplies two numbers and then adds the product to the current contents of the HI and LO registers. Similarly, the MSUB instruction multiplies two operands and then subtracts the product from the HI and LO registers. The MADD and MSUB operations are commonly used in DSP algorithms.

#### 3.2.3 SYSTEM CONTROL COPROCESSOR (CP0)

In the MIPS architecture, CP0 is responsible for the virtual-to-physical address translation, the exception control system, the processor's diagnostics capability, the operating modes (Kernel, User and Debug) and whether interrupts are enabled or disabled. Configuration information, such as presence of options like MIPS16e, is also available by accessing the CP0 registers, listed in Table 3-2.

| Register<br>Number | Register<br>Name        | Function                                                                 |

|--------------------|-------------------------|--------------------------------------------------------------------------|

| 0-6                | Reserved                | Reserved.                                                                |

| 7                  | HWREna                  | Enables access via the RDHWR instruction to selected hardware registers. |

| 8                  | BadVAddr <sup>(1)</sup> | Reports the address for the most recent address-related exception.       |

| 9                  | Count <sup>(1)</sup>    | Processor cycle count.                                                   |

| 10                 | Reserved                | Reserved.                                                                |

| 11                 | Compare <sup>(1)</sup>  | Timer interrupt control.                                                 |

| 12                 | Status <sup>(1)</sup>   | Processor status and control.                                            |

| 12                 | IntCtl <sup>(1)</sup>   | Interrupt system status and control.                                     |

| 12                 | SRSCtl <sup>(1)</sup>   | Shadow register set status and control.                                  |

| 12                 | SRSMap <sup>(1)</sup>   | Provides mapping from vectored interrupt to a shadow set.                |

| 13                 | Cause <sup>(1)</sup>    | Cause of last general exception.                                         |

| 14                 | EPC <sup>(1)</sup>      | Program counter at last exception.                                       |

| 15                 | PRId                    | Processor identification and revision.                                   |

| 15                 | Ebase                   | Exception vector base register.                                          |

| 16                 | Config                  | Configuration register.                                                  |

| 16                 | Config1                 | Configuration Register 1.                                                |

| 16                 | Config2                 | Configuration Register 2.                                                |

| 16                 | Config3                 | Configuration Register 3.                                                |

| 17-22              | Reserved                | Reserved.                                                                |

| 23                 | Debug <sup>(2)</sup>    | Debug control and exception status.                                      |

| 24                 | DEPC <sup>(2)</sup>     | Program counter at last debug exception.                                 |

| 25-29              | Reserved                | Reserved.                                                                |

| 30                 | ErrorEPC <sup>(1)</sup> | Program counter at last error.                                           |

| 31                 | DESAVE <sup>(2)</sup>   | Debug handler scratchpad register.                                       |

|                    | <b>I</b>                |                                                                          |

TABLE 3-2: COPROCESSOR 0 REGISTERS

Note 1: Registers used in exception processing.

2: Registers used during debug.

# 4.0 MEMORY ORGANIZATION

Note: This data sheet summarizes the features of the PIC32MX5XX/6XX/7XX family of devices. It is not intended to be a comprehensive reference source. For detailed information, refer to **Section 3.** "Memory Organization" (DS60001115) in the "*PIC32 Family Reference Manual*", which is available from the Microchip web site (www.microchip.com/PIC32).

PIC32MX5XX/6XX/7XX microcontrollers provide 4 GB of unified virtual memory address space. All memory regions, including program, data memory, SFRs and Configuration registers, reside in this address space at their respective unique addresses. The program and data memories can be optionally partitioned into user and kernel memories. In addition, the data memory can be made executable, allowing PIC32MX5XX/6XX/7XX devices to execute from data memory.

Key features include:

- 32-bit native data width

- Separate User (KUSEG) and Kernel (KSEG0/ KSEG1) mode address space

- Flexible program Flash memory partitioning

- Flexible data RAM partitioning for data and program space

- Separate boot Flash memory for protected code

- Robust bus exception handling to intercept runaway code

- Simple memory mapping with Fixed Mapping Translation (FMT) unit

- Cacheable (KSEG0) and non-cacheable (KSEG1) address regions

# 4.1 Memory Layout

PIC32MX5XX/6XX/7XX microcontrollers implement two address schemes: virtual and physical. All hardware resources, such as program memory, data memory and peripherals, are located at their respective physical addresses. Virtual addresses are exclusively used by the CPU to fetch and execute instructions as well as access peripherals. Physical addresses are used by bus master peripherals, such as DMA and the Flash controller, that access memory independently of the CPU.

The memory maps for the PIC32MX5XX/6XX/7XX devices are illustrated in Figure 4-1 through Figure 4-6. Table 4-1 provides memory map information for the Special Function Registers (SFRs).

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|--|

| 04.04        | R                 | R                 | R                 | R                 | R                 | R                 | R                | R                |  |

| 31:24        | BMXPFMSZ<31:24>   |                   |                   |                   |                   |                   |                  |                  |  |

| 22:46        | R                 | R                 | R                 | R                 | R                 | R                 | R                | R                |  |

| 23:16        | BMXPFMSZ<23:16>   |                   |                   |                   |                   |                   |                  |                  |  |

| 45.0         | R                 | R                 | R                 | R                 | R                 | R                 | R                | R                |  |

| 15:8         | BMXPFMSZ<15:8>    |                   |                   |                   |                   |                   |                  |                  |  |

| 7.0          | R                 | R                 | R                 | R                 | R                 | R                 | R                | R                |  |

| 7:0          |                   |                   |                   | BMXPF             | MSZ<7:0>          |                   |                  |                  |  |

#### REGISTER 4-7: BMXPFMSZ: PROGRAM FLASH (PFM) SIZE REGISTER

# Legend:

| Legena.                           |                  |                                    |                    |  |

|-----------------------------------|------------------|------------------------------------|--------------------|--|

| R = Readable bit W = Writable bit |                  | U = Unimplemented bit, read as '0' |                    |  |

| -n = Value at POR                 | '1' = Bit is set | '0' = Bit is cleared               | x = Bit is unknown |  |

bit 31-0 BMXPFMSZ<31:0>: Program Flash Memory (PFM) Size bits

Static value that indicates the size of the PFM in bytes: 0x00010000 = device has 64 KB Flash 0x00020000 = device has 128 KB Flash 0x00040000 = device has 256 KB Flash 0x00080000 = device has 512 KB Flash

#### REGISTER 4-8: BMXBOOTSZ: BOOT FLASH (IFM) SIZE REGISTER

| Bit<br>Range           | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |

|------------------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|--|

| 04.04                  | R                 | R                 | R                 | R                 | R                 | R                 | R                | R                |  |

| 31:24 BMXBOOTSZ<31:24> |                   |                   |                   |                   |                   |                   |                  |                  |  |

| 00.40                  | R                 | R                 | R                 | R                 | R                 | R                 | R                | R                |  |

| 23:16                  | BMXBOOTSZ<23:16>  |                   |                   |                   |                   |                   |                  |                  |  |

| 15.0                   | R                 | R                 | R                 | R                 | R                 | R                 | R                | R                |  |

| 15:8                   | BMXBOOTSZ<15:8>   |                   |                   |                   |                   |                   |                  |                  |  |

| 7.0                    | R                 | R                 | R                 | R                 | R                 | R                 | R                | R                |  |

| 7:0                    |                   |                   |                   | BMXBO             | OTSZ<7:0>         |                   |                  |                  |  |

| Legend:           |                  |                           |                    |

|-------------------|------------------|---------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, re | ead as '0'         |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared      | x = Bit is unknown |

bit 31-0 **BMXBOOTSZ<31:0>:** Boot Flash Memory (BFM) Size bits Static value that indicates the size of the Boot PFM in bytes: 0x00003000 = device has 12 KB boot Flash

# 12.1 Parallel I/O (PIO) Ports

All port pins have three registers (TRIS, LAT and PORT) that are directly associated with their operation.

TRIS is a Data Direction or Tri-State Control register that determines whether a digital pin is an input or an output. Setting a TRISx register bit = 1, configures the corresponding I/O pin as an input; setting a TRISx register bit = 0, configures the corresponding I/O pin as an output. All port I/O pins are defined as inputs after a device Reset. Certain I/O pins are shared with analog peripherals and default to analog inputs after a device Reset.

PORT is a register used to read the current state of the signal applied to the port I/O pins. Writing to a PORTx register performs a write to the port's latch, LATx register, latching the data to the port's I/O pins.

LAT is a register used to write data to the port I/O pins. The LATx Latch register holds the data written to either the LATx or PORTx registers. Reading the LATx Latch register reads the last value written to the corresponding PORT or Latch register.

Not all port I/O pins are implemented on some devices, therefore, the corresponding PORTx, LATx and TRISx register bits will read as zeros.

#### 12.1.1 CLR, SET AND INV REGISTERS

Every I/O module register has a corresponding Clear (CLR), Set (SET) and Invert (INV) register designed to provide fast atomic bit manipulations. As the name of the register implies, a value written to a SET, CLR or INV register effectively performs the implied operation, but only on the corresponding base register and only bits specified as '1' are modified. Bits specified as '0' are not modified.

Reading SET, CLR and INV registers returns undefined values. To see the affects of a write operation to a SET, CLR or INV register, the base register must be read.

| Note: | Using a PORTxINV register to toggle a bit |

|-------|-------------------------------------------|

|       | is recommended because the operation is   |

|       | performed in hardware atomically, using   |

|       | fewer instructions, as compared to the    |

|       | traditional read-modify-write method, as  |

|       | follows:                                  |

|       | PORTC $^{ = 0x0001:}$                     |

#### 12.1.2 DIGITAL INPUTS

Pins are configured as digital inputs by setting the corresponding TRIS register bits = 1. When configured as inputs, they are either TTL buffers or Schmitt Triggers. Several digital pins share functionality with analog inputs and default to the analog inputs at POR. Setting the corresponding bit in the AD1PCFG register = 1 enables the pin as a digital pin.

The maximum input voltage allowed on the input pins is the same as the maximum VIH specification. Refer to **Section 32.0 "Electrical Characteristics"** for VIH specification details.

| Note: | Analog levels on any pin that is defined as<br>a digital input (including the ANx pins)<br>may cause the input buffer to consume |  |  |  |  |  |  |

|-------|----------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|

|       | current that exceeds the device specifications.                                                                                  |  |  |  |  |  |  |

#### 12.1.3 ANALOG INPUTS

Certain pins can be configured as analog inputs used by the ADC and comparator modules. Setting the corresponding bits in the AD1PCFG register = 0 enables the pin as an analog input pin and must have the corresponding TRIS bit set = 1 (input). If the TRIS bit is cleared = 0 (output), the digital output level (VOH or VOL) will be converted. Any time a port I/O pin is configured as analog, its digital input is disabled and the corresponding PORTx register bit will read '0'. The AD1PCFG register has a default value of 0x0000; therefore, all pins that share ANx functions are analog (not digital) by default.

#### 12.1.4 DIGITAL OUTPUTS

Pins are configured as digital outputs by setting the corresponding TRIS register bits = 0. When configured as digital outputs, these pins are CMOS drivers or can be configured as open-drain outputs by setting the corresponding bits in the Open-Drain Configuration (ODCx) register.

The open-drain feature allows generation of outputs higher than VDD (e.g., 5V) on any desired 5V tolerant pins by using external pull-up resistors. The maximum open-drain voltage allowed is the same as the maximum VIH specification.

See the **"Device Pin Tables"** section for the available pins and their functionality.

#### 12.1.5 ANALOG OUTPUTS

Certain pins can be configured as analog outputs, such as the CVREF output voltage used by the comparator module. Configuring the comparator reference module to provide this output will present the analog output voltage on the pin, independent of the TRIS register setting for the corresponding pin.

#### 12.1.6 INPUT CHANGE NOTIFICATION

The input change notification function of the I/O ports (CNx) allows devices to generate interrupt requests in response to change-of-state on selected pin.

Each CNx pin also has a weak pull-up, which acts as a current source connected to the pin. The pull-ups are enabled by setting the corresponding bit in the CNPUE register.

# PIC32MX5XX/6XX/7XX

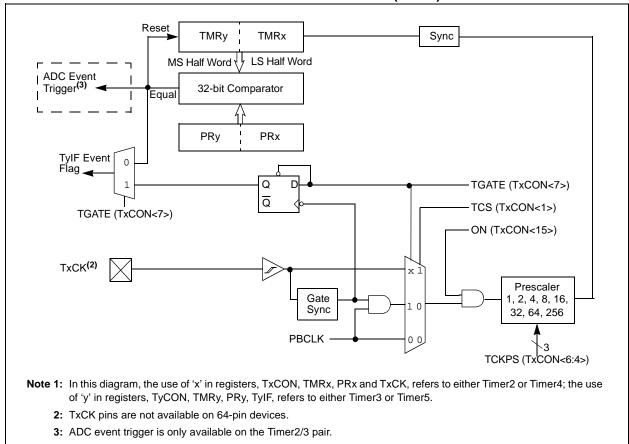

#### FIGURE 14-2: TIMER2/3 AND TIMER4/5 BLOCK DIAGRAM (32-BIT)

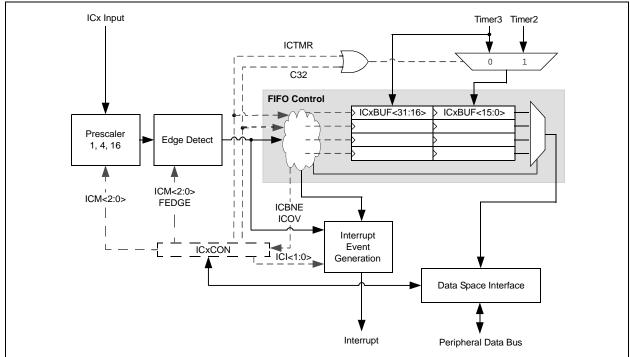

# 16.0 INPUT CAPTURE

Note: This data sheet summarizes the features of the PIC32MX5XX/6XX/7XX family of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to Section 15. "Input Capture" (DS60001122) of the "*PIC32 Family Reference Manual*", which is available from the Microchip web site (www.microchip.com/PIC32).

The Input Capture module is useful in applications requiring frequency (period) and pulse measurement.

The Input Capture module captures the 16-bit or 32-bit value of the selected Time Base registers when an event occurs at the ICx pin. The following events cause capture events:

- Simple capture event modes:

- Capture timer value on every falling edge of input at ICx pin

- Capture timer value on every rising edge of input at ICx pin

- Capture timer value on every edge (rising and falling)

- Capture timer value on every edge (rising and falling), specified edge first.

- Prescaler capture event modes:

- Capture timer value on every 4th rising edge of input at ICx pin

- Capture timer value on every 16th rising edge of input at ICx pin

Each input capture channel can select between one of two 16-bit timers (Timer2 or Timer3) for the time base, or two 16-bit timers (Timer2 and Timer3) together to form a 32-bit timer. The selected timer can use either an internal or external clock.

Other operational features include:

- Device wake-up from capture pin during Sleep and Idle modes

- Interrupt on input capture event

- 4-word FIFO buffer for capture values Interrupt optionally generated after 1, 2, 3 or 4 buffer locations are filled

- Input Capture module can also be used to provide additional sources of external interrupts

### FIGURE 16-1: INPUT CAPTURE BLOCK DIAGRAM

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|

| 24.24        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 31:24        |                   | —                 | _                 | _                 | —                 | _                 | _                | —                |

| 00.40        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 23:16        |                   | —                 | _                 | —                 | —                 | -                 | _                | —                |

| 45.0         | R/W-0             | U-0               | R/W-0             | R/W-0             | R/W-0             | U-0               | R/W-0            | R/W-0            |

| 15:8         | ON <sup>(1)</sup> | —                 | SIDL              | IREN              | RTSMD             | -                 | UEN              | <1:0>            |

| 7.0          | R/W-0             | R/W-0             | R/W-0, HC         | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |

| 7:0          | WAKE              | LPBACK            | ABAUD             | RXINV             | BRGH              | PDSEL             | <1:0>            | STSEL            |

#### **REGISTER 20-1: UXMODE: UARTX MODE REGISTER**

| Legend:           |                  | HC = Cleared by hard | ware               |

|-------------------|------------------|----------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented b  | it, read as '0'    |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared | x = Bit is unknown |

#### bit 31-16 Unimplemented: Read as '0'

- bit 15 **ON:** UARTx Enable bit<sup>(1)</sup>

- 1 = UARTx is enabled. UARTx pins are controlled by UARTx as defined by UEN<1:0> and UTXEN control bits.

- 0 = UARTx is disabled. All UARTx pins are controlled by corresponding bits in the PORTx, TRISx and LATx registers; UARTx power consumption is minimal.

- bit 14 Unimplemented: Read as '0'

- bit 13 **SIDL:** Stop in Idle Mode bit

- 1 = Discontinue operation when device enters Idle mode

- 0 = Continue operation when device enters Idle mode

- bit 12 IREN: IrDA Encoder and Decoder Enable bit

- 1 = IrDA is enabled

- 0 = IrDA is disabled

- bit 11 **RTSMD:** Mode Selection for UxRTS Pin bit

- $1 = \overline{\text{UxRTS}}$  pin is in Simplex mode

- $0 = \overline{\text{UxRTS}}$  pin is in Flow Control mode

- bit 10 Unimplemented: Read as '0'

- bit 9-8 UEN<1:0>: UARTx Enable bits

- 11 = UxTX, UxRX and UxBCLK pins are enabled and used; UxCTS pin is controlled by corresponding bits in the PORTx register

- 10 = UxTX, UxRX,  $\overline{\text{UxCTS}}$  and  $\overline{\text{UxRTS}}$  pins are enabled and used

- 01 = UxTX, UxRX and UxRTS pins are enabled and used; UxCTS pin is controlled by corresponding bits in the PORTx register

- 00 = UxTX and UxRX pins are enabled and used; UxCTS and UxRTS/UxBCLK pins are controlled by corresponding bits in the PORTx register

- bit 7 WAKE: Enable Wake-up on Start bit Detect During Sleep Mode bit

- 1 = Wake-up is enabled

- 0 = Wake-up is disabled

- bit 6 LPBACK: UARTx Loopback Mode Select bit

- 1 = Loopback mode is enabled

- 0 = Loopback mode is disabled

- **Note 1:** When using the 1:1 PBCLK divisor, the user software should not read/write the peripheral SFRs in the SYSCLK cycle immediately following the instruction that clears the module's ON bit.

# 21.1 Control Registers

# TABLE 21-1: PARALLEL MASTER PORT REGISTER MAP

| 15 <del>6</del> 15                      |                                 |           |                                                                                            | Bits      |       |       |         |        |        |        |         |        |      |      |      |      |      |      |            |

|-----------------------------------------|---------------------------------|-----------|--------------------------------------------------------------------------------------------|-----------|-------|-------|---------|--------|--------|--------|---------|--------|------|------|------|------|------|------|------------|

| Virtual Address<br>(BF80_#)<br>Register | Register<br>Name <sup>(1)</sup> | Bit Range | 31/15                                                                                      | 30/14     | 29/13 | 28/12 | 27/11   | 26/10  | 25/9   | 24/8   | 23/7    | 22/6   | 21/5 | 20/4 | 19/3 | 18/2 | 17/1 | 16/0 | All Resets |

| 7000 PM0                                | ACON                            | 31:16     | _                                                                                          | _         | _     | _     | _       | _      | —      | _      |         | _      | —    | _    | —    | _    | —    | _    | 0000       |

| 7000 1 100                              |                                 | 15:0      | ON                                                                                         | —         | SIDL  | ADRMU | IX<1:0> | PMPTTL | PTWREN | PTRDEN | CSF     | <1:0>  | ALP  | CS2P | CS1P | —    | WRSP | RDSP | 0000       |

| 7010 PMM                                | MODE                            | 31:16     | —                                                                                          | —         | —     | —     | —       | —      | —      | —      | —       | —      | —    | —    | —    | —    | —    | —    | 0000       |

| 7010 Pivily                             | INODE                           | 15:0      | BUSY IRQM<1:0> INCM<1:0> MODE16 MODE<1:0> WAITB<1:0> WAITB<1:0> WAITM<3:0> WAITE<1:0> 0000 |           |       |       |         |        |        |        | 0000    |        |      |      |      |      |      |      |            |

| 7020 PMA                                |                                 | 31:16     |                                                                                            | _         | _     | _     | _       | _      | _      |        | _       | -      | _    | _    | _    | _    | _    | _    | 0000       |

| 7020 PINA                               | IADDK                           | 15:0      | CS2EN/A15                                                                                  | CS1EN/A14 |       |       |         |        |        |        | ADDR    | <13:0> |      |      |      |      |      |      | 0000       |

| 7000 040                                |                                 | 31:16     |                                                                                            |           |       |       |         |        |        | DATAOU | T 04.0  |        |      |      |      |      |      |      | 0000       |

| 7030 PMD                                |                                 | 15:0      |                                                                                            |           |       |       |         |        |        | DATAOU | 1<31:0> |        |      |      |      |      |      |      | 0000       |

| 7040 DM                                 | MDIN -                          | 31:16     |                                                                                            |           |       |       |         |        |        |        | .01.0   |        |      |      |      |      |      |      | 0000       |

| 7040 PM                                 |                                 | 15:0      |                                                                                            |           |       |       |         |        |        | DATAIN | <31:0>  |        |      |      |      |      |      |      | 0000       |

| 7050 DM                                 | MAEN                            | 31:16     | _                                                                                          | _         | _     | _     | _       | _      | _      | _      | _       | _      | _    | _    | _    | _    | _    | _    | 0000       |

| 7050 PM/                                | VIAEN                           | 15:0      |                                                                                            |           |       |       |         |        |        | PTEN<  | :15:0>  |        |      |      |      |      |      |      | 0000       |

| 7000 0140                               | 40TAT                           | 31:16     | _                                                                                          | _         | _     | _     | _       | _      | _      | _      | _       | _      | _    | —    | _    | —    | _    | _    | 0000       |

| 7060 PMS                                | ISTAL                           | 15:0      | IBF                                                                                        | IBOV      | _     | -     | IB3F    | IB2F   | IB1F   | IB0F   | OBE     | OBUF   | _    |      | OB3E | OB2E | OB1E | OB0E | 008F       |

Legend: x = unknown value on Reset; — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

Note 1: All registers in this table have corresponding CLR, SET and INV registers at their virtual addresses, plus offsets of 0x4, 0x8 and 0xC, respectively. See Section 12.1.1 "CLR, SET and INV Registers" for more information.

#### REGISTER 21-2: PMMODE: PARALLEL PORT MODE REGISTER (CONTINUED)

- WAITM<3:0>: Data Read/Write Strobe Wait States bits<sup>(1)</sup> bit 5-2 1111 = Wait of 16 TPB 0001 = Wait of 2 ТРВ 0000 = Wait of 1 TPB (default) WAITE<1:0>: Data Hold After Read/Write Strobe Wait States bits<sup>(1)</sup> bit 1-0 11 = Wait of 4 Трв 10 = Wait of 3 TPB 01 = Wait of 2 TPB 00 = Wait of 1 TPB (default) For Read operations: 11 = Wait of 3 TPB 10 = Wait of 2 TPB 01 = Wait of 1 TPB 00 = Wait of 0 TPB (default)

- **Note 1:** Whenever WAITM<3:0> = 0000, WAITB and WAITE bits are ignored and forced to 1 TPBCLK cycle for a write operation; WAITB = 1 TPBCLK cycle, WAITE = 0 TPBCLK cycles for a read operation.

- 2: Address bit A14 is not subject to auto-increment/decrement if configured as Chip Select CS1.

#### REGISTER 24-12: CIFLTCON2: CAN FILTER CONTROL REGISTER 2 (CONTINUED)

| bit 15    | FLTEN9: Filter 9 Enable bit<br>1 = Filter is enabled<br>0 = Filter is disabled                                                                                                                                                                                                            |

|-----------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| bit 14-13 | MSEL9<1:0>: Filter 9 Mask Select bits<br>11 = Acceptance Mask 3 selected<br>10 = Acceptance Mask 2 selected<br>01 = Acceptance Mask 1 selected<br>00 = Acceptance Mask 0 selected                                                                                                         |

| bit 12-8  | FSEL9<4:0>: FIFO Selection bits<br>11111 = Message matching filter is stored in FIFO buffer 31<br>11110 = Message matching filter is stored in FIFO buffer 30<br>•                                                                                                                        |

|           | 00001 = Message matching filter is stored in FIFO buffer 1<br>00000 = Message matching filter is stored in FIFO buffer 0                                                                                                                                                                  |

| bit 7     | FLTEN8: Filter 8 Enable bit<br>1 = Filter is enabled<br>0 = Filter is disabled                                                                                                                                                                                                            |

| bit 6-5   | MSEL8<1:0>: Filter 8 Mask Select bits<br>11 = Acceptance Mask 3 selected<br>10 = Acceptance Mask 2 selected<br>01 = Acceptance Mask 1 selected<br>00 = Acceptance Mask 0 selected                                                                                                         |

| bit 4-0   | FSEL8<4:0>: FIFO Selection bits<br>11111 = Message matching filter is stored in FIFO buffer 31<br>11110 = Message matching filter is stored in FIFO buffer 30<br>00001 = Message matching filter is stored in FIFO buffer 1<br>00000 = Message matching filter is stored in FIFO buffer 0 |

| r         |                                                                                                                                                                                                                                                                                           |

Note: The bits in this register can only be modified if the corresponding filter enable (FLTENn) bit is '0'.

### REGISTER 24-17: CIFLTCON7: CAN FILTER CONTROL REGISTER 7 (CONTINUED)

| bit 15    | FLTEN29: Filter 29 Enable bit<br>1 = Filter is enabled<br>0 = Filter is disabled                                                                                               |

|-----------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| bit 14-13 | MSEL29<1:0>: Filter 29 Mask Select bits                                                                                                                                        |

|           | <ul> <li>11 = Acceptance Mask 3 selected</li> <li>10 = Acceptance Mask 2 selected</li> <li>01 = Acceptance Mask 1 selected</li> <li>00 = Acceptance Mask 0 selected</li> </ul> |

| bit 12-8  | FSEL29<4:0>: FIFO Selection bits                                                                                                                                               |

|           | 11111 = Message matching filter is stored in FIFO buffer 31                                                                                                                    |

|           | 11110 = Message matching filter is stored in FIFO buffer 30                                                                                                                    |

|           | •                                                                                                                                                                              |

|           | •                                                                                                                                                                              |

|           | 00001 = Message matching filter is stored in FIFO buffer 1<br>00000 = Message matching filter is stored in FIFO buffer 0                                                       |

| bit 7     | FLTEN28: Filter 28 Enable bit                                                                                                                                                  |

|           | <ul><li>1 = Filter is enabled</li><li>0 = Filter is disabled</li></ul>                                                                                                         |

| bit 6-5   | MSEL28<1:0>: Filter 28 Mask Select bits                                                                                                                                        |

|           | 11 = Acceptance Mask 3 selected                                                                                                                                                |

|           | 10 = Acceptance Mask 2 selected                                                                                                                                                |

|           | 01 = Acceptance Mask 1 selected<br>00 = Acceptance Mask 0 selected                                                                                                             |

| bit 4-0   | FSEL28<4:0>: FIFO Selection bits                                                                                                                                               |

|           | 11111 = Message matching filter is stored in FIFO buffer 31                                                                                                                    |

|           | 11110 = Message matching filter is stored in FIFO buffer 30                                                                                                                    |

|           | •                                                                                                                                                                              |

|           | •                                                                                                                                                                              |

|           | 00001 = Message matching filter is stored in FIFO buffer 1                                                                                                                     |

|           | 00000 = Message matching filter is stored in FIFO buffer 0                                                                                                                     |

| Note:     | The bits in this register can only be modified if the corresponding filter enable (FLTENn) bit is '0'.                                                                         |

# PIC32MX5XX/6XX/7XX

|              |                   |                   |                   |                   |                   |                   |                  | ,                |  |  |  |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|--|--|--|

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |  |  |

| 01.04        | R/W-x             | R/W-x             | R/W-x             | R/W-x             | R/W-x             | R/W-x             | R/W-x            | R/W-x            |  |  |  |

| 31:24        | SID<10:3>         |                   |                   |                   |                   |                   |                  |                  |  |  |  |

| 22:46        | R/W-x             | R/W-x             | R/W-x             | U-0               | R/W-0             | U-0               | R/W-x            | R/W-x            |  |  |  |

| 23:16        |                   | SID<2:0>          |                   | —                 | EXID              | — EID<17:16       |                  | 7:16>            |  |  |  |

| 15.0         | R/W-x             | R/W-x             | R/W-x             | R/W-x             | R/W-x             | R/W-x             | R/W-x            | R/W-x            |  |  |  |

| 15:8         | EID<15:8>         |                   |                   |                   |                   |                   |                  |                  |  |  |  |

| 7.0          | R/W-x             | R/W-x             | R/W-x             | R/W-x             | R/W-x             | R/W-x             | R/W-x            | R/W-x            |  |  |  |

| 7:0          |                   |                   |                   | EID<              | :7:0>             |                   |                  |                  |  |  |  |

#### REGISTER 24-18: CIRXFn: CAN ACCEPTANCE FILTER 'n' REGISTER 7 (n = 0 THROUGH 31)

#### Legend:

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, r | ead as '0'         |

|-------------------|------------------|--------------------------|--------------------|

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared     | x = Bit is unknown |

bit 31-21 SID<10:0>: Standard Identifier bits

- 1 = Message address bit SIDx must be '1' to match filter

- 0 = Message address bit SIDx must be '0' to match filter

- bit 20 Unimplemented: Read as '0'

- bit 19 **EXID:** Extended Identifier Enable bits

- 1 = Match only messages with extended identifier addresses

- 0 = Match only messages with standard identifier addresses

- bit 18 Unimplemented: Read as '0'

- bit 17-0 EID<17:0>: Extended Identifier bits

- 1 = Message address bit EIDx must be '1' to match filter

- 0 = Message address bit EIDx must be '0' to match filter

**Note:** This register can only be modified when the filter is disabled (FLTENn = 0).

#### TABLE 25-5: ETHERNET CONTROLLER REGISTER SUMMARY FOR PIC32MX664F064H, PIC32MX664F128H, PIC32MX664F064L, PIC32MX664F128L, PIC32MX675F256H, PIC32MX675F512H, PIC32MX695F512H, PIC32MX775F256H, PIC32MX775F512H, PIC32MX795F512H, PIC32MX695F512L, PIC32MX675F256L, PIC32MX675F512L, PIC32MX764F128H, PIC32MX764F128L, PIC32MX775F256L, PIC32MX775F512L AND PIC32MX795F512L DEVICES (CONTINUED)

| ess                         |                                 | 0                       |                       |               |               |         |               |               |               | В             | its       |         |               |               |            |         |          |          | 6          |

|-----------------------------|---------------------------------|-------------------------|-----------------------|---------------|---------------|---------|---------------|---------------|---------------|---------------|-----------|---------|---------------|---------------|------------|---------|----------|----------|------------|

| Virtual Address<br>(BF88_#) | Register<br>Name <sup>(1)</sup> | Bit Range               | 31/15                 | 30/14         | 29/13         | 28/12   | 27/11         | 26/10         | 25/9          | 24/8          | 23/7      | 22/6    | 21/5          | 20/4          | 19/3       | 18/2    | 17/1     | 16/0     | All Resets |

| 90E0                        | ETHSTAT                         | 31:16<br>15:0           | _                     |               |               |         |               |               |               |               |           |         | 0000          |               |            |         |          |          |            |

|                             | ETH                             | 31:16                   | _                     |               |               | _       |               |               | _             |               | _         |         | _             |               | _          | _       | _        |          | 0000       |

| 9100                        | RXOVFLOW                        | 15:0                    |                       |               |               |         |               |               |               | RXOVFLW       | CNT<15:0> |         |               |               |            |         |          |          | 0000       |

|                             | ETH                             | 31:16                   | _                     | _             |               | _       |               | _             | _             |               | _         | _       |               | _             |            |         |          | _        | 0000       |

| 9110                        | FRMTXOK                         | 15:0                    |                       |               |               |         |               |               |               | FRMTXOK       | CNT<15:0> |         |               |               |            |         |          |          | 0000       |

| 9120                        | ETH                             | 31:16                   | _                     | -             | _             | _       | _             | -             | —             | -             | _         | _       | _             | -             |            | _       | _        | —        | 0000       |

| 9120                        | SCOLFRM                         | 15:0                    |                       |               |               |         |               |               |               | SCOLFRM       | CNT<15:0> |         |               |               |            |         |          |          | 0000       |

| 9130                        | ETH                             | 31:16                   | —                     | _             | —             | —       | _             | _             | —             | —             | —         | —       | _             | _             | —          | —       | —        | —        | 0000       |

|                             | MCOLFRM                         | 15:0                    | MCOLFRMCNT<15:0> 0000 |               |               |         |               |               |               |               |           |         |               |               |            |         |          |          |            |

| 9140                        | ETH<br>FRMRXOK                  | 31:16                   | —                     | _             | —             | —       | _             | _             | —             | -             | -         | —       | _             | —             | —          |         | —        | —        | 0000       |

|                             |                                 | 15:0                    |                       |               |               |         |               |               |               |               |           |         | 0000          |               |            |         |          |          |            |

| 9150                        | ETH<br>FCSERR                   | 31:16<br>15:0           | _                     | —             | _             | —       | _             | —             | —             | FCSERRO       |           | _       |               | —             | —          | _       | —        | —        | 0000       |

|                             | ETH                             | 31:16                   | _                     | _             | _             | _       | _             | _             | _             |               | _         | _       | _             | _             | _          | _       | _        | _        | 0000       |

| 9160                        | ALGNERR                         | 15:0                    |                       |               |               |         |               |               |               | ALGNERR       | CNT<15:0> |         |               |               |            |         |          |          | 0000       |

|                             | 51404                           | 31:16                   | _                     | _             | _             | _       | _             | _             | _             | _             | _         | —       | _             | _             | _          | _       | _        | _        | 0000       |

| 9200                        | EMAC1<br>CFG1                   | 15:0                    | SOFT<br>RESET         | SIM<br>RESET  | _             | _       | RESET<br>RMCS | RESET<br>RFUN | RESET<br>TMCS | RESET<br>TFUN | _         | _       | _             | LOOPBACK      | TXPAUSE    | RXPAUSE | PASSALL  | RXENABLE | 800D       |

|                             | EMAC1                           | 31:16                   | _                     |               | _             | —       |               | _             | _             |               | _         | _       |               | _             | _          | —       | _        | —        | 0000       |

| 9210                        | CFG2                            | 15:0                    | _                     | EXCESS<br>DFR | BP<br>NOBKOFF | NOBKOFF | —             |               | LONGPRE       | PUREPRE       | AUTOPAD   | VLANPAD | PAD<br>ENABLE | CRC<br>ENABLE | DELAYCRC   | HUGEFRM | LENGTHCK | FULLDPLX | 4082       |

| 9220                        | EMAC1                           | 31:16                   | _                     |               | _             | _       | _             | _             | _             | _             | _         | _       | _             | _             | —          |         | _        | _        | 0000       |

| 3220                        | IPGT                            | 15:0                    | —                     | _             | —             | —       | —             | _             | _             | _             | _         |         |               | B             | 2BIPKTGP<6 | :0>     |          | -        | 0012       |

| 9230                        | EMAC1                           | 31:16                   | _                     | —             | —             | —       | _             | _             | -             | _             | _         | _       | —             | _             | —          | —       | _        | -        | 0000       |

|                             | IPGR                            | 15:0                    | _                     |               |               |         |               |               |               |               | 0C12      |         |               |               |            |         |          |          |            |

| 9240                        | EMAC1<br>CLRT                   | 31:16                   | _                     |               | —             | -       | -             | -             | -             | _             | _         |         |               |               | —          |         | <u> </u> | -        | 0000       |

|                             |                                 | 15:0                    | _                     | _             |               |         | CWINDO        | )vv<5:0>      | r             |               |           |         | _             | _             |            | RET)    | <<3:0>   | -        | 370F       |

| 9250                        | EMAC1<br>MAXF                   | 31:16                   | —                     | _             | —             | —       | -             | —             | —             |               | -         | —       | _             | _             |            | —       | _        | _        | 0000       |

|                             |                                 | 15:0 MACMAXF<15:0> 05EE |                       |               |               |         |               |               |               |               |           |         |               |               |            |         |          |          |            |

PIC32MX5XX/6XX/7XX

x = unknown value on Reset; - = unimplemented, read as '0'. Reset values are shown in hexadecimal. Legend:

Note 1: All registers in this table (with the exception of ETHSTAT) have corresponding CLR, SET and INV registers at their virtual addresses, plus offsets of 0x4, 0x8 and 0xC, respectively. See Section 12.1.1 "CLR, SET and INV Registers" for more information.

Reset values default to the factory programmed value. 2:

DS60001156J-page 282

## 31.6 MPLAB X SIM Software Simulator

The MPLAB X SIM Software Simulator allows code development in a PC-hosted environment by simulating the PIC MCUs and dsPIC DSCs on an instruction level. On any given instruction, the data areas can be examined or modified and stimuli can be applied from a comprehensive stimulus controller. Registers can be logged to files for further run-time analysis. The trace buffer and logic analyzer display extend the power of the simulator to record and track program execution, actions on I/O, most peripherals and internal registers.

The MPLAB X SIM Software Simulator fully supports symbolic debugging using the MPLAB XC Compilers, and the MPASM and MPLAB Assemblers. The software simulator offers the flexibility to develop and debug code outside of the hardware laboratory environment, making it an excellent, economical software development tool.

### 31.7 MPLAB REAL ICE In-Circuit Emulator System

The MPLAB REAL ICE In-Circuit Emulator System is Microchip's next generation high-speed emulator for Microchip Flash DSC and MCU devices. It debugs and programs all 8, 16 and 32-bit MCU, and DSC devices with the easy-to-use, powerful graphical user interface of the MPLAB X IDE.

The emulator is connected to the design engineer's PC using a high-speed USB 2.0 interface and is connected to the target with either a connector compatible with in-circuit debugger systems (RJ-11) or with the new high-speed, noise tolerant, Low-Voltage Differential Signal (LVDS) interconnection (CAT5).

The emulator is field upgradable through future firmware downloads in MPLAB X IDE. MPLAB REAL ICE offers significant advantages over competitive emulators including full-speed emulation, run-time variable watches, trace analysis, complex breakpoints, logic probes, a ruggedized probe interface and long (up to three meters) interconnection cables.

#### 31.8 MPLAB ICD 3 In-Circuit Debugger System

The MPLAB ICD 3 In-Circuit Debugger System is Microchip's most cost-effective, high-speed hardware debugger/programmer for Microchip Flash DSC and MCU devices. It debugs and programs PIC Flash microcontrollers and dsPIC DSCs with the powerful, yet easy-to-use graphical user interface of the MPLAB IDE.

The MPLAB ICD 3 In-Circuit Debugger probe is connected to the design engineer's PC using a highspeed USB 2.0 interface and is connected to the target with a connector compatible with the MPLAB ICD 2 or MPLAB REAL ICE systems (RJ-11). MPLAB ICD 3 supports all MPLAB ICD 2 headers.

# 31.9 PICkit 3 In-Circuit Debugger/ Programmer

The MPLAB PICkit 3 allows debugging and programming of PIC and dsPIC Flash microcontrollers at a most affordable price point using the powerful graphical user interface of the MPLAB IDE. The MPLAB PICkit 3 is connected to the design engineer's PC using a fullspeed USB interface and can be connected to the target via a Microchip debug (RJ-11) connector (compatible with MPLAB ICD 3 and MPLAB REAL ICE). The connector uses two device I/O pins and the Reset line to implement in-circuit debugging and In-Circuit Serial Programming<sup>™</sup> (ICSP<sup>™</sup>).

# 31.10 MPLAB PM3 Device Programmer

The MPLAB PM3 Device Programmer is a universal, CE compliant device programmer with programmable voltage verification at VDDMIN and VDDMAX for maximum reliability. It features a large LCD display (128 x 64) for menus and error messages, and a modular, detachable socket assembly to support various package types. The ICSP cable assembly is included as a standard item. In Stand-Alone mode, the MPLAB PM3 Device Programmer can read, verify and program PIC devices without a PC connection. It can also set code protection in this mode. The MPLAB PM3 connects to the host PC via an RS-232 or USB cable. The MPLAB PM3 has high-speed communications and optimized algorithms for quick programming of large memory devices, and incorporates an MMC card for file storage and data applications.

#### TABLE 32-14: VOLTAGE REFERENCE SPECIFICATIONS

| DC CHA        | RACTERI | STICS                                                        | $\begin{array}{l} \mbox{Standard Operating Conditions: 2.3V to 3.6V} \\ \mbox{(unless otherwise stated)} \\ \mbox{Operating temperature} & -40^\circ C \leq TA \leq +85^\circ C \mbox{ for Industrial} \\ & -40^\circ C \leq TA \leq +105^\circ C \mbox{ for V-Temp} \end{array}$ |         |                    |          |                                                                 |  |  |  |

|---------------|---------|--------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------|--------------------|----------|-----------------------------------------------------------------|--|--|--|

| Param.<br>No. | Symbol  | Characteristics                                              | Min.                                                                                                                                                                                                                                                                              | Typical | Max.               | Comments |                                                                 |  |  |  |

| D312          | TSET    | Internal 4-bit DAC<br>Comparator Reference<br>Settling time. | _                                                                                                                                                                                                                                                                                 | —       | 10                 | μs       | See Note 1                                                      |  |  |  |

| D313          | DACREFH | CVREF Input Voltage                                          | AVss                                                                                                                                                                                                                                                                              | _       | AVdd               | V        | CVRSRC with CVRSS = 0                                           |  |  |  |

|               |         | Reference Range                                              | VREF-                                                                                                                                                                                                                                                                             | _       | VREF+              | V        | CVRSRC with CVRSS = 1                                           |  |  |  |

| D314          | DVref   | CVREF Programmable<br>Output Range                           | 0                                                                                                                                                                                                                                                                                 | —       | 0.625 x<br>DACREFH | V        | 0 to 0.625 DACREFH with<br>DACREFH/24 step size                 |  |  |  |

|               |         |                                                              | 0.25 x<br>DACREFH                                                                                                                                                                                                                                                                 | —       | 0.719 x<br>DACREFH | V        | 0.25 x DACREFH to 0.719<br>DACREFH with DACREFH/32<br>step size |  |  |  |

| D315          | DACRES  | Resolution                                                   | —                                                                                                                                                                                                                                                                                 | —       | DACREFH/<br>24     |          | CVRCON <cvrr> = 1</cvrr>                                        |  |  |  |

|               |         |                                                              | —                                                                                                                                                                                                                                                                                 | _       | DACREFH/<br>32     |          | CVRCON <cvrr> = 0</cvrr>                                        |  |  |  |

| D316          | DACACC  | Absolute Accuracy <sup>(2)</sup>                             | —                                                                                                                                                                                                                                                                                 |         | 1/4                | LSB      | DACREFH/24,<br>CVRCON <cvrr> = 1</cvrr>                         |  |  |  |

|               |         |                                                              | —                                                                                                                                                                                                                                                                                 |         | 1/2                | LSB      | DACREFH/32,<br>CVRCON <cvrr> = 0</cvrr>                         |  |  |  |

**Note 1:** Settling time measured while CVRR = 1 and CVR<3:0> transitions from '0000' to '1111'. This parameter is characterized, but not tested in manufacturing.

2: These parameters are characterized but not tested.

#### TABLE 32-15: INTERNAL VOLTAGE REGULATOR SPECIFICATIONS

| DC CHARACTERISTICS |        |                                 |      | $\begin{array}{l} \mbox{Standard Operating Conditions: 2.3V to 3.6V} \\ \mbox{(unless otherwise stated)} \\ \mbox{Operating temperature} & -40^\circ C \leq TA \leq +85^\circ C \mbox{ for Industrial} \\ & -40^\circ C \leq TA \leq +105^\circ C \mbox{ for V-Temp} \end{array}$ |      |       |                                                 |  |  |  |

|--------------------|--------|---------------------------------|------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|-------|-------------------------------------------------|--|--|--|

| Param.<br>No.      | Symbol | Characteristics                 | Min. | Typical                                                                                                                                                                                                                                                                           | Max. | Units | Comments                                        |  |  |  |

| D321               | Cefc   | External Filter Capacitor Value | 8    | 10                                                                                                                                                                                                                                                                                | —    | μF    | Capacitor must be low series resistance (1 ohm) |  |  |  |

| D322               | TPWRT  | Power-up Timer Period           | _    | 64                                                                                                                                                                                                                                                                                | _    | ms    | —                                               |  |  |  |

| AC CHA        | RACTERI | STICS                             | $\begin{tabular}{lllllllllllllllllllllllllllllllllll$ |         |      |       |                                                                                   |  |  |

|---------------|---------|-----------------------------------|-------------------------------------------------------|---------|------|-------|-----------------------------------------------------------------------------------|--|--|

| Param.<br>No. | Symbol  | Characteristics <sup>(1)</sup>    | Min.                                                  | Typical | Max. | Units | Conditions                                                                        |  |  |

| USB313        | VUSB3V3 | USB Voltage                       | 3.0                                                   | —       | 3.6  | V     | Voltage on VUSB3V3<br>must be in this range for<br>proper USB operation           |  |  |

| USB315        | VILUSB  | Input Low Voltage for USB Buffer  | _                                                     | —       | 0.8  | V     | —                                                                                 |  |  |

| USB316        | VIHUSB  | Input High Voltage for USB Buffer | 2.0                                                   | —       | _    | V     | —                                                                                 |  |  |

| USB318        | VDIFS   | Differential Input Sensitivity    | —                                                     | —       | 0.2  | V     | The difference between<br>D+ and D- must exceed<br>this value while VCM is<br>met |  |  |

| USB319        | VCM     | Differential Common Mode Range    | 0.8                                                   | —       | 2.5  | V     | —                                                                                 |  |  |

| USB320        | Ζουτ    | Driver Output Impedance           | 28.0                                                  | —       | 44.0 | Ω     | —                                                                                 |  |  |

| USB321        | Vol     | Voltage Output Low                | 0.0                                                   | —       | 0.3  | V     | 1.425 kΩ load<br>connected to VUSB3V3                                             |  |  |

| USB322        | Vон     | Voltage Output High               | 2.8                                                   | _       | 3.6  | V     | 14.25 k $\Omega$ load connected to ground                                         |  |  |

#### TABLE 32-42: USB OTG ELECTRICAL SPECIFICATIONS

**Note 1:** These parameters are characterized, but not tested in manufacturing.

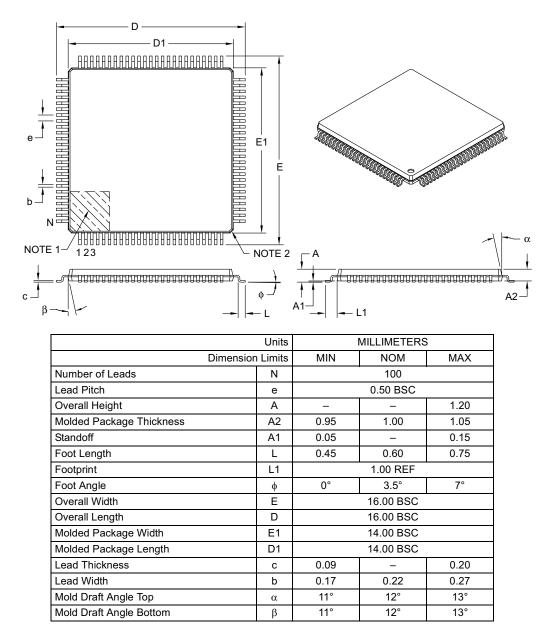

## 100-Lead Plastic Thin Quad Flatpack (PF) – 14x14x1 mm Body, 2.00 mm [TQFP]

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

#### Notes:

- 1. Pin 1 visual index feature may vary, but must be located within the hatched area.

- 2. Chamfers at corners are optional; size may vary.

- 3. Dimensions D1 and E1 do not include mold flash or protrusions. Mold flash or protrusions shall not exceed 0.25 mm per side.

- 4. Dimensioning and tolerancing per ASME Y14.5M.

- BSC: Basic Dimension. Theoretically exact value shown without tolerances.

REF: Reference Dimension, usually without tolerance, for information purposes only.

Microchip Technology Drawing C04-110B

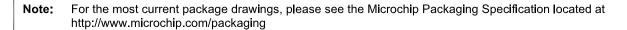

# 124-Terminal Very Thin Leadless Array Package (TL) – 9x9x0.9 mm Body [VTLA]

|                                      | Units | MILLIMETERS |          |      |  |

|--------------------------------------|-------|-------------|----------|------|--|

| Dimension                            | MIN   | NOM         | MAX      |      |  |

| Number of Pins                       | N     |             | 124      |      |  |

| Pitch                                | еT    |             | 0.50 BSC |      |  |

| Pitch (Inner to outer terminal ring) |       | 0.50 BSC    |          |      |  |

| Overall Height                       | A     | 0.80        | 0.85     | 0.90 |  |

| Standoff                             | A1    | 0.00        | -        | 0.05 |  |

| Overall Width                        | E     | 9.00 BSC    |          |      |  |

| Exposed Pad Width                    | E2    | 6.40        | 6.55     | 6.70 |  |

| Overall Length                       | D     | 9.00 BSC    |          |      |  |

| Exposed Pad Length                   | D2    | 6.40        | 6.55     | 6.70 |  |

| Contact Width                        | b     | 0.20        | 0.25     | 0.30 |  |

| Contact Length                       | L     | 0.20        | 0.25     | 0.30 |  |

| Contact-to-Exposed Pad               | K     | 0.20        | -        | -    |  |

Notes:

1. Pin 1 visual index feature may vary, but must be located within the hatched area.

2. Package is saw singulated.

3. Dimensioning and tolerancing per ASME Y14.5M.

BSC: Basic Dimension. Theoretically exact value shown without tolerances.