Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFI

| Product Status             | Active                                                                           |

|----------------------------|----------------------------------------------------------------------------------|

| Core Processor             | MIPS32® M4K™                                                                     |

| Core Size                  | 32-Bit Single-Core                                                               |

| Speed                      | 80MHz                                                                            |

| Connectivity               | Ethernet, I <sup>2</sup> C, SPI, UART/USART, USB OTG                             |

| Peripherals                | Brown-out Detect/Reset, DMA, POR, PWM, WDT                                       |

| Number of I/O              | 85                                                                               |

| Program Memory Size        | 512KB (512K x 8)                                                                 |

| Program Memory Type        | FLASH                                                                            |

| EEPROM Size                | -                                                                                |

| RAM Size                   | 128K x 8                                                                         |

| Voltage - Supply (Vcc/Vdd) | 2.3V ~ 3.6V                                                                      |

| Data Converters            | A/D 16x10b                                                                       |

| Oscillator Type            | Internal                                                                         |

| Operating Temperature      | -40°C ~ 105°C (TA)                                                               |

| Mounting Type              | Surface Mount                                                                    |

| Package / Case             | 100-TQFP                                                                         |

| Supplier Device Package    | 100-TQFP (12x12)                                                                 |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic32mx695f512l-80v-pt |

|                            |                                                                                  |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

### TABLE 11: PIN NAMES FOR USB AND ETHERNET DEVICES

| 1          | 21-PIN TFBGA (BOTTOM VIEW)                                                                  |          | L11                                                          |

|------------|---------------------------------------------------------------------------------------------|----------|--------------------------------------------------------------|

|            | PIC32MX664F064L<br>PIC32MX664F128L<br>PIC32MX675F256L<br>PIC32MX675F512L<br>PIC32MX695F512L |          | L1 A11                                                       |

|            | te: The TFBGA package skips from row "H                                                     |          |                                                              |

| Pin #      | Full Pin Name                                                                               | Pin #    | Full Pin Name                                                |

| A1         | PMD4/RE4                                                                                    | E2       | T4CK/RC3                                                     |

| A2         | PMD3/RE3                                                                                    | E3       | ECOL/SCK2/U6TX/U3RTS/PMA5/CN8/RG6                            |

| A3         | TRD0/RG13                                                                                   | E4       | T3CK/RC2                                                     |

| A4         | PMD0/RE0                                                                                    | E5       | VDD                                                          |

| A5         | PMD8/RG0                                                                                    | E6       | ETXERR/PMD9/RG1                                              |

| A6         | ETXD0/PMD10/RF1                                                                             | E7       | Vss                                                          |

| A7         | Vdd                                                                                         | E8       | AETXEN/SDA1/INT4/RA15                                        |

| A8         | Vss                                                                                         | E9       | RTCC/EMDIO/AEMDIO/IC1/RD8                                    |

| A9         | ETXD2/IC5/PMD12/RD12                                                                        | E10      | SS1/IC2/RD9                                                  |

| A10        | OC3/RD2                                                                                     | E11      | AETXCLK/SCL1/INT3/RA14                                       |

| A11        | OC2/RD1                                                                                     | F1       | MCLR                                                         |

| B1         | No Connect (NC)                                                                             | F2       | ERXDV/AERXDV/ECRSDV/AECRSDV//SCL4/SDO2/U3TX/PMA3/CN10/RG8    |

| B2         | AERXERR/RG15                                                                                | F3       | ERXCLK/AERXCLK/EREFCLK/AEREFCLK/SS2/U6RX/U3CTS/PMA2/CN11/RG9 |

| B3         | PMD2/RE2                                                                                    | F4       | ECRS/SDA4/SDI2/U3RX/PMA4/CN9/RG7                             |

| B4         | PMD1/RE1                                                                                    | F5       | Vss                                                          |

| B5         | TRD3/RA7                                                                                    | F6       | No Connect (NC)                                              |

| B6         | ETXD1/PMD11/RF0                                                                             | F7       | No Connect (NC)                                              |

| B7         | VCAP                                                                                        | F8       | VDD                                                          |

| B8         | PMRD/CN14/RD5                                                                               | F9       | OSC1/CLKI/RC12                                               |

| B9         | OC4/RD3                                                                                     | F10      | Vss                                                          |

| B10        | Vss                                                                                         | F11      | OSC2/CLKO/RC15                                               |

| B11        | SOSCO/T1CK/CN0/RC14                                                                         | G1       | AERXD0/INT1/RE8                                              |

| C1         | PMD6/RE6                                                                                    | G2       | AERXD1/INT2/RE9                                              |

| C2         | VDD                                                                                         | G3       | TMS/RA0                                                      |

| C3<br>C4   | TRD1/RG12<br>TRD2/RG14                                                                      | G4<br>G5 | No Connect (NC)<br>VDD                                       |

| C4         | TRCLK/RA6                                                                                   | G5<br>G6 | Vss                                                          |

|            | No Connect (NC)                                                                             | G0<br>G7 | Vss                                                          |

| C0<br>C7   | ETXCLK/PMD15/CN16/RD7                                                                       | G7<br>G8 | No Connect (NC)                                              |

| C8         | OC5/PMWR/CN13/RD4                                                                           | G9       | TDO/RA5                                                      |

| C9         | VDD                                                                                         | G10      | SDA2/RA3                                                     |

| C10        | SOSCI/CN1/RC13                                                                              | G11      | TDI/RA4                                                      |

| C11        | EMDC/AEMDC/IC4/PMCS1/PMA14/RD11                                                             | H1       | AN5/C1IN+/VBUSON/CN7/RB5                                     |

| D1         | T2CK/RC1                                                                                    | H2       | AN4/C1IN-/CN6/RB4                                            |

| D2         | PMD7/RE7                                                                                    | H3       | Vss                                                          |

| D3         | PMD5/RE5                                                                                    | H4       | VDD                                                          |

| D4         | Vss                                                                                         | H5       | No Connect (NC)                                              |

| D5         | Vss                                                                                         | H6       | VDD                                                          |

| D6         | No Connect (NC)                                                                             | H7       | No Connect (NC)                                              |

| D7         | ETXEN/PMD14/CN15/RD6                                                                        | H8       | VBUS                                                         |

| D8         | ETXD3/PMD13/CN19/RD13                                                                       | H9       | VUSB3V3                                                      |

| D9         | SDO1/OC1/INT0/RD0                                                                           | H10      | D+/RG2                                                       |

| D10        | No Connect (NC)                                                                             | H11      | SCL2/RA2                                                     |

| D11        | SCK1/IC3/PMCS2/PMA15/RD10                                                                   | J1       | AN3/C2IN+/CN5/RB3                                            |

| E1<br>Note | T5CK/SDI1/RC4<br>1: Shaded pins are 5V tolerant.                                            | J2       | AN2/C2IN-/CN4/RB2                                            |

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |  |  |  |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|--|--|--|--|

| 04.04        | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |  |  |

| 31:24        |                   |                   |                   | NVMDA             | TA<31:24>         |                   |                  |                  |  |  |  |  |

| 00.40        | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |  |  |

| 23:16        | NVMDATA<23:16>    |                   |                   |                   |                   |                   |                  |                  |  |  |  |  |

| 45.0         | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |  |  |

| 15:8         |                   |                   |                   | NVMDA             | TA<15:8>          |                   |                  |                  |  |  |  |  |

| 7.0          | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |  |  |

| 7:0          |                   |                   |                   | NVMD/             | ATA<7:0>          |                   |                  |                  |  |  |  |  |

#### REGISTER 5-4: NVMDATA: FLASH PROGRAM DATA REGISTER

| Legend:           |                  |                           |                    |

|-------------------|------------------|---------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, re | ad as '0'          |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared      | x = Bit is unknown |

bit 31-0 NVMDATA<31:0>: Flash Programming Data bits

**Note:** The bits in this register are only reset by a Power-on Reset (POR).

#### REGISTER 5-5: NVMSRCADDR: SOURCE DATA ADDRESS REGISTER

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |  |  |  |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|--|--|--|--|

| 04.04        | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |  |  |

| 31:24        |                   |                   |                   | NVMSRCA           | DDR<31:24>        | >                 |                  |                  |  |  |  |  |

| 00.40        | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |  |  |

| 23:16        | NVMSRCADDR<23:16> |                   |                   |                   |                   |                   |                  |                  |  |  |  |  |

| 45.0         | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |  |  |

| 15:8         |                   |                   |                   | NVMSRC/           | ADDR<15:8>        |                   |                  |                  |  |  |  |  |

| 7.0          | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |  |  |

| 7:0          |                   |                   |                   | NVMSRC            | ADDR<7:0>         |                   |                  |                  |  |  |  |  |

| Legend:           |                  |                           |                    |

|-------------------|------------------|---------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, re | ad as '0'          |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared      | x = Bit is unknown |

#### bit 31-0 NVMSRCADDR<31:0>: Source Data Address bits

The system physical address of the data to be programmed into the Flash when the NVMOP<3:0> bits (NVMCON<3:0>) are set to perform row programming.

PIC32MX5XX/6XX/7XX

#### TABLE 12-3: PORTC REGISTER MAP FOR PIC32MX534F064H, PIC32MX564F064H, PIC32MX564F128H, PIC32MX575F256H, PIC32MX575F512H, PIC32MX664F064H, PIC32MX664F128H, PIC32MX675F256H, PIC32MX675F512H, PIC32MX695F512H, PIC32MX764F128H, PIC32MX775F256H, PIC32MX775F512H AND PIC32MX795F512H DEVICES

| ess                         |       | n         |         |          |            |             |             |             |            | Bi      | ts   |      |      |      |      |      |      |      | ő          |

|-----------------------------|-------|-----------|---------|----------|------------|-------------|-------------|-------------|------------|---------|------|------|------|------|------|------|------|------|------------|

| Virtual Address<br>(BF88_#) |       | Bit Range | 31/15   | 30/14    | 29/13      | 28/12       | 27/11       | 26/10       | 25/9       | 24/8    | 23/7 | 22/6 | 21/5 | 20/4 | 19/3 | 18/2 | 17/1 | 16/0 | All Resets |

| 6080                        | TRISC | 31:16     | —       | _        | -          | —           | _           | -           | —          | _       | -    | -    | -    | _    | _    | _    | _    | -    | 0000       |

| 6060                        | IRISC | 15:0      | TRISC15 | TRISC14  | TRISC13    | TRISC12     | _           | _           | _          | _       | _    | _    | _    | _    | _    | _    | _    | _    | F000       |

| 6000                        | PORTC | 31:16     | —       | -        |            | —           | —           |             | -          |         |      | _    |      | _    | _    | _    | _    |      | 0000       |

| 6090                        | PURIC | 15:0      | RC15    | RC14     | RC13       | RC12        | _           | -           | —          | -       | -    | -    | -    | -    |      | -    |      | -    | xxxx       |

| 60A0                        | LATC  | 31:16     | _       | _        | _          | _           | _           | _           | _          | _       | _    | _    | _    | _    | _    | _    | _    | _    | 0000       |

| 60A0                        | LAIC  | 15:0      | LATC15  | LATC14   | LATC13     | LATC12      | _           | _           | -          | —       | _    | —    | _    | —    | _    | _    | _    | _    | xxxx       |

| 60B0                        | ODCC  | 31:16     | _       | _        | _          | _           | _           | _           | _          | _       | _    | _    | _    | _    | _    | _    | _    | _    | 0000       |

| 00B0                        | ODCC  | 15:0      | ODCC15  | ODCC14   | ODCC13     | ODCC12      | _           | _           | —          | _       | _    | _    | _    | _    | _    | _    | _    | _    | 0000       |

| Logon                       | 4     | - unkno   |         | Pocot: - | unimplomon | ted read as | '0' Poset v | luce are ch | we in hove | locimol |      |      |      |      |      |      |      |      |            |

Legend: x = unknown value on Reset; — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

Note 1: All registers in this table have corresponding CLR, SET and INV registers at their virtual addresses, plus offsets of 0x4, 0x8 and 0xC, respectively. See Section 12.1.1 "CLR, SET and INV Registers" for more information.

#### TABLE 12-4: PORTC REGISTER MAP FOR PIC32MX534F064L, PIC32MX564F064L, PIC32MX564F128L, PIC32MX575F256L, PIC32MX575F512L, PIC32MX664F064L, PIC32MX664F128L, PIC32MX675F256L, PIC32MX675F512L, PIC32MX695F512L, PIC32MX764F128L. PIC32MX775F256L. PIC32MX775F512L AND PIC32MX795F512L DEVICES

| ess                         |                                 | 0         |         |         |         |         |       |       |      | Bi   | ts   |      |      |        |        |        |        |      | ú          |

|-----------------------------|---------------------------------|-----------|---------|---------|---------|---------|-------|-------|------|------|------|------|------|--------|--------|--------|--------|------|------------|

| Virtual Address<br>(BF88_#) | Register<br>Name <sup>(1)</sup> | Bit Range | 31/15   | 30/14   | 29/13   | 28/12   | 27/11 | 26/10 | 25/9 | 24/8 | 23/7 | 22/6 | 21/5 | 20/4   | 19/3   | 18/2   | 17/1   | 16/0 | All Resets |

| 6080                        | TRISC                           | 31:16     |         | _       | —       | _       | _     | _     | _    | _    | _    | _    | _    | _      | _      | _      | _      | _    | 0000       |

| 6060                        | TRISC                           | 15:0      | TRISC15 | TRISC14 | TRISC13 | TRISC12 | _     | _     | _    | _    | _    | _    | _    | TRISC4 | TRISC3 | TRISC2 | TRISC1 | _    | FOOF       |

| 6000                        | PORTC                           | 31:16     | _       | —       | —       | —       | —     | —     | —    | —    | _    | —    | —    | —      | —      | —      | —      | —    | 0000       |

| 6090                        | PURIC                           | 15:0      | RC15    | RC14    | RC13    | RC12    | _     | _     | —    | —    | _    | —    | —    | RC4    | RC3    | RC2    | RC1    | —    | xxxx       |

| 60A0                        | LATC                            | 31:16     | _       | _       | _       | _       | _     | _     | _    | _    | _    | _    | _    | _      | _      | _      | _      | _    | 0000       |

| 60A0                        | LAIC                            | 15:0      | LATC15  | LATC14  | LATC13  | LATC12  | _     | _     | —    | —    | _    | —    | —    | LATC4  | LATC3  | LATC2  | LATC1  | —    | xxxx       |

| 60B0                        | ODCC                            | 31:16     | —       | _       | _       | —       | _     | _     | _    | _    | _    | _    | _    | _      | _      | _      | _      | _    | 0000       |

| 00B0                        | ODCC                            | 15:0      | ODCC15  | ODCC14  | ODCC13  | ODCC12  | _     | _     | _    | _    | _    | _    | _    | ODCC4  | ODCC3  | ODCC2  | ODCC1  | _    | 0000       |

Legend: x = unknown value on Reset; --- = unimplemented, read as '0'. Reset values are shown in hexadecimal.

Note 1: All registers in this table have corresponding CLR, SET and INV registers at their virtual addresses, plus offsets of 0x4, 0x8 and 0xC, respectively. See Section 12.1.1 "CLR, SET and INV Registers" for more information

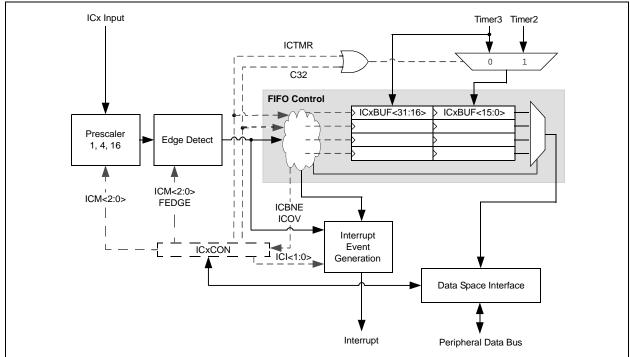

## 16.0 INPUT CAPTURE

Note: This data sheet summarizes the features of the PIC32MX5XX/6XX/7XX family of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to Section 15. "Input Capture" (DS60001122) of the "*PIC32 Family Reference Manual*", which is available from the Microchip web site (www.microchip.com/PIC32).

The Input Capture module is useful in applications requiring frequency (period) and pulse measurement.

The Input Capture module captures the 16-bit or 32-bit value of the selected Time Base registers when an event occurs at the ICx pin. The following events cause capture events:

- Simple capture event modes:

- Capture timer value on every falling edge of input at ICx pin

- Capture timer value on every rising edge of input at ICx pin

- Capture timer value on every edge (rising and falling)

- Capture timer value on every edge (rising and falling), specified edge first.

- Prescaler capture event modes:

- Capture timer value on every 4th rising edge of input at ICx pin

- Capture timer value on every 16th rising edge of input at ICx pin

Each input capture channel can select between one of two 16-bit timers (Timer2 or Timer3) for the time base, or two 16-bit timers (Timer2 and Timer3) together to form a 32-bit timer. The selected timer can use either an internal or external clock.

Other operational features include:

- Device wake-up from capture pin during Sleep and Idle modes

- Interrupt on input capture event

- 4-word FIFO buffer for capture values Interrupt optionally generated after 1, 2, 3 or 4 buffer locations are filled

- Input Capture module can also be used to provide additional sources of external interrupts

### FIGURE 16-1: INPUT CAPTURE BLOCK DIAGRAM

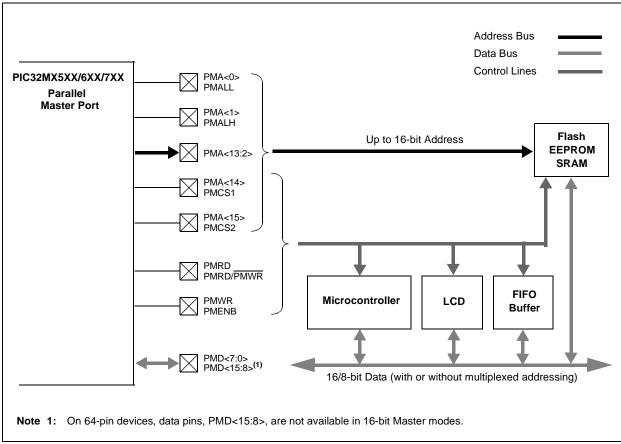

#### 21.0 PARALLEL MASTER PORT (PMP)

Note: This data sheet summarizes the features of the PIC32MX5XX/6XX/7XX family of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to Section 13. "Parallel Master Port (PMP)" (DS60001128) in the "PIC32 Family Reference Manual", which is available from the Microchip web site (www.microchip.com/PIC32).

The PMP is a parallel 8-bit/16-bit input/output module specifically designed to communicate with a wide variety of parallel devices, such as communications peripherals, LCDs, external memory devices and microcontrollers. Because the interface to parallel peripherals varies significantly, the PMP module is highly configurable. Figure 21-1 shows the PMP module pinout and its connections to external devices.

**FIGURE 21-1:**

The following are key features of the PMP module:

- 8-bit and 16-bit interface

- Up to 16 programmable address lines

- Up to two Chip Select lines

- Programmable strobe options

- Individual read and write strobes, or

- Read/Write strobe with enable strobe

- · Address auto-increment/auto-decrement

- · Programmable address/data multiplexing

- Programmable polarity on control signals

- · Parallel Slave Port support

- Legacy addressable

- Address support

- 4-byte deep auto-incrementing buffer

- · Programmable wait states

- · Operates during Sleep and Idle modes

- Fast bit manipulation using CLR, SET and INV registers

Note: On 64-pin devices, the PMD<15:8> data pins are not available.

PMP MODULE PINOUT AND CONNECTIONS TO EXTERNAL DEVICES

| Bit<br>Range | Bit<br>31/23/15/7     | Bit<br>30/22/14/6                           | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |  |  |

|--------------|-----------------------|---------------------------------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|--|--|--|

| 24.24        | U-0                   | U-0                                         | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |  |  |  |

| 31:24        | —                     | _                                           |                   |                   |                   | _                 | _                |                  |  |  |  |

| 00.40        | U-0                   | U-0                                         | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |  |  |  |

| 23:16        | —                     | —                                           | _                 | _                 | _                 | —                 |                  | _                |  |  |  |

|              | R/W-0                 | R/W-0                                       | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |  |

| 15:8         | CS2 <sup>(1)</sup>    | CS1 <sup>(3)</sup>                          |                   |                   |                   | .4.2.0            |                  |                  |  |  |  |

|              | ADDR15 <sup>(2)</sup> | ADDR15 <sup>(2)</sup> ADDR14 <sup>(4)</sup> |                   |                   |                   |                   |                  |                  |  |  |  |

| 7:0          | R/W-0                 | R/W-0                                       | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |  |

|              |                       |                                             |                   | ADDR              | <7:0>             |                   |                  |                  |  |  |  |

#### REGISTER 21-3: PMADDR: PARALLEL PORT ADDRESS REGISTER

#### Legend:

| 5                 |                  |                          |                    |  |

|-------------------|------------------|--------------------------|--------------------|--|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, r | ead as '0'         |  |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared     | x = Bit is unknown |  |

#### bit 31-16 **Unimplemented:** Read as '0'

- bit 15 CS2: Chip Select 2 bit<sup>(1)</sup>

- 1 = Chip Select 2 is active

- 0 = Chip Select 2 is inactive

- bit 15 ADDR<15>: Destination Address bit 15<sup>(2)</sup>

- bit 14 CS1: Chip Select 1 bit<sup>(3)</sup>

- 1 = Chip Select 1 is active 0 = Chip Select 1 is inactive

- bit 14 ADDR<14>: Destination Address bit 14<sup>(4)</sup>

- bit 13-0 ADDR<13:0>: Address bits

- Note 1: When the CSF<1:0> bits (PMCON<7:6>) = 10 or 01.

- **2:** When the CSF<1:0> bits (PMCON<7:6>) = 00.

- **3:** When the CSF<1:0> bits (PMCON<7:6>) = 10.

- **4:** When the CSF<1:0> bits (PMCON<7:6>) = 00 or 01.

#### REGISTER 24-10: CIFLTCONO: CAN FILTER CONTROL REGISTER 0 (CONTINUED)

| bit 15    | FLTEN1: Filter 1 Enable bit<br>1 = Filter is enabled               |

|-----------|--------------------------------------------------------------------|

|           | 0 = Filter is disabled                                             |

| bit 14-13 | MSEL1<1:0>: Filter 1 Mask Select bits                              |

|           | 11 = Acceptance Mask 3 selected                                    |

|           | 10 = Acceptance Mask 2 selected<br>01 = Acceptance Mask 1 selected |

|           | 00 = Acceptance Mask 0 selected                                    |

| bit 12-8  | FSEL1<4:0>: FIFO Selection bits                                    |

|           | 11111 = Message matching filter is stored in FIFO buffer 31        |

|           | 11110 = Message matching filter is stored in FIFO buffer 30        |

|           | •                                                                  |

|           | •                                                                  |

|           | 00001 = Message matching filter is stored in FIFO buffer 1         |

|           | 00000 = Message matching filter is stored in FIFO buffer 0         |

| bit 7     | FLTEN0: Filter 0 Enable bit                                        |

|           | 1 = Filter is enabled<br>0 = Filter is disabled                    |

| bit 6-5   | MSEL0<1:0>: Filter 0 Mask Select bits                              |

|           | 11 = Acceptance Mask 3 selected                                    |

|           | 10 = Acceptance Mask 2 selected                                    |

|           | 01 = Acceptance Mask 1 selected<br>00 = Acceptance Mask 0 selected |

| bit 4-0   | FSEL0<4:0>: FIFO Selection bits                                    |

| DIL 4-0   | 11111 = Message matching filter is stored in FIFO buffer 31        |

|           | 11110 = Message matching filter is stored in FIFO buffer 30        |

|           | •                                                                  |

|           | •                                                                  |

|           | •<br>00001 = Message matching filter is stored in FIFO buffer 1    |

|           | 00000 = Message matching filter is stored in FIFO buffer 0         |

Note: The bits in this register can only be modified if the corresponding filter enable (FLTENn) bit is '0'.

# PIC32MX5XX/6XX/7XX

|              |                   |                       |                       |                      |                   | •                         |                  | ,                |

|--------------|-------------------|-----------------------|-----------------------|----------------------|-------------------|---------------------------|------------------|------------------|

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6     | Bit<br>29/21/13/5     | Bit<br>28/20/12/4    | Bit<br>27/19/11/3 | Bit<br>26/18/10/2         | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

| 21.24        | U-0               | U-0                   | U-0                   | U-0                  | U-0               | U-0                       | U-0              | U-0              |

| 31:24        | —                 | —                     | —                     | _                    | —                 | _                         | _                | —                |

| 22.46        | U-0               | U-0                   | U-0                   | R/W-0                | R/W-0             | R/W-0                     | R/W-0            | R/W-0            |

| 23:16        | —                 | —                     | —                     |                      |                   | FSIZE<4:0> <sup>(1)</sup> | )                |                  |

| 15.0         | U-0               | S/HC-0                | S/HC-0                | R/W-0                | U-0               | U-0                       | U-0              | U-0              |

| 15:8         | —                 | FRESET                | UINC                  | DONLY <sup>(1)</sup> | —                 | _                         | _                | —                |

| 7.0          | R/W-0             | R-0                   | R-0                   | R-0                  | R/W-0             | R/W-0                     | R/W-0            | R/W-0            |

| 7:0          | TXEN              | TXABAT <sup>(2)</sup> | TXLARB <sup>(3)</sup> | TXERR <sup>(3)</sup> | TXREQ             | RTREN                     | TXPR             | <1:0>            |

#### **REGISTER 24-20:** CiFIFOCONn: CAN FIFO CONTROL REGISTER 'n' (n = 0 THROUGH 31)

#### Legend:

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, r | ead as '0'         |

|-------------------|------------------|--------------------------|--------------------|

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared     | x = Bit is unknown |

#### bit 31-21 Unimplemented: Read as '0'

| bit 20-16 FSIZE<4:0>: FIFO Size bits' | bit 20-16 | E<4:0>: FIFO Size bits <sup>(1)</sup> |

|---------------------------------------|-----------|---------------------------------------|

|---------------------------------------|-----------|---------------------------------------|

- 11111 = FIFO is 32 messages deep

- •

- 00010 = FIFO is 3 messages deep 00001 = FIFO is 2 messages deep

00000 = FIFO is 1 message deep

#### bit 15 Unimplemented: Read as '0'

#### bit 14 FRESET: FIFO Reset bits

1 = FIFO will be reset when bit is set, cleared by hardware when FIFO is reset. After setting, the user should poll whether this bit is clear before taking any action.

#### 0 = No effect

#### bit 13 UINC: Increment Head/Tail bit

$\frac{TXEN = 1:}{When this bit is set the FIFO head will increment by a single message$  $<math display="block">\frac{TXEN = 0:}{When this bit is set the FIFO tail will increment by a single message$ When this bit is set the FIFO tail will increment by a single message $<math display="block">\frac{TXEN = 0:}{When this bit is set the FIFO tail will increment by a single message }$

### bit 12 DONLY: Store Message Data Only bit<sup>(1)</sup>

$\frac{\text{TXEN} = 1:}{\text{This bit is not used and has no effect.}}$   $\frac{\text{TXEN} = 0:}{\text{TXEN} = 0:}$ (FIFO configured as a Receive FIFO)

1 =Only data bytes will be stored in the FIFO

0 = Full message is stored, including identifier

#### bit 11-8 Unimplemented: Read as '0'

- bit 7 **TXEN:** TX/RX Buffer Selection bit

- 1 = FIFO is a Transmit FIFO

- 0 = FIFO is a Receive FIFO

- **Note 1:** These bits can only be modified when the CAN module is in Configuration mode (OPMOD<2:0> bits (CiCON<23:21>) = 100).

- 2: This bit is updated when a message completes (or aborts) or when the FIFO is reset.

- 3: This bit is reset on any read of this register or when the FIFO is reset.

### **REGISTER 24-21:** CiFIFOINTn: CAN FIFO INTERRUPT REGISTER 'n' (n = 0 THROUGH 31)

- bit 9 TXHALFIF: FIFO Transmit FIFO Half Empty Interrupt Flag bit<sup>(1)</sup> TXEN = 1: (FIFO configured as a transmit buffer) 1 = FIFO is  $\leq$  half full 0 = FIFO is > half full TXEN = 0: (FIFO configured as a receive buffer) Unused, reads '0' bit 8 **TXEMPTYIF:** Transmit FIFO Empty Interrupt Flag bit<sup>(1)</sup> TXEN = 1: (FIFO configured as a transmit buffer) 1 = FIFO is empty 0 = FIFO is not empty, at least 1 message queued to be transmitted TXEN = 0: (FIFO configured as a receive buffer) Unused, reads '0' bit 7-4 Unimplemented: Read as '0' bit 3 **RXOVFLIF:** Receive FIFO Overflow Interrupt Flag bit TXEN = 1: (FIFO configured as a transmit buffer) Unused, reads '0' TXEN = 0: (FIFO configured as a receive buffer) 1 = Overflow event has occurred 0 = No overflow event occured bit 2 **RXFULLIF:** Receive FIFO Full Interrupt Flag bit<sup>(1)</sup> TXEN = 1: (FIFO configured as a transmit buffer) Unused, reads '0' TXEN = 0: (FIFO configured as a receive buffer) 1 = FIFO is full 0 = FIFO is not full RXHALFIF: Receive FIFO Half Full Interrupt Flag bit<sup>(1)</sup> bit 1 TXEN = 1: (FIFO configured as a transmit buffer) Unused, reads '0' TXEN = 0: (FIFO configured as a receive buffer) 1 = FIFO is  $\geq$  half full 0 = FIFO is < half full bit 0 **RXNEMPTYIF:** Receive Buffer Not Empty Interrupt Flag bit<sup>(1)</sup> TXEN = 1: (FIFO configured as a transmit buffer) Unused, reads '0' TXEN = 0: (FIFO configured as a receive buffer) 1 = FIFO is not empty, has at least 1 message 0 = FIFO is empty

- Note 1: This bit is read-only and reflects the status of the FIFO.

# PIC32MX5XX/6XX/7XX

| Bit<br>Range | Bit<br>31/23/15/7                                         | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |

|--------------|-----------------------------------------------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|--|

| 31:24        | R-x                                                       | R-x               | R-x               | R-x               | R-x               | R-x               | R-x              | R-x              |  |

| 31.24        |                                                           |                   |                   | CiFIFOUA          | n<31:24>          |                   |                  | •                |  |

| 23:16        | R-x                                                       | R-x               | R-x               | R-x               | R-x               | R-x               | R-x              | R-x              |  |

| 23.10        | CiFIFOUAn<23:16>                                          |                   |                   |                   |                   |                   |                  |                  |  |

| 45.0         | R-x                                                       | R-x               | R-x               | R-x               | R-x               | R-x               | R-x              | R-x              |  |

| 15:8         |                                                           |                   |                   | CiFIFOU           | An<15:8>          |                   |                  |                  |  |

| 7.0          | R-x R-x R-x R-x R-x R-0 <sup>(1)</sup> R-0 <sup>(1)</sup> |                   |                   |                   |                   |                   |                  |                  |  |

| 7:0          |                                                           | •                 |                   | CiFIFOU           | IAn<7:0>          |                   |                  |                  |  |

#### REGISTER 24-22: CiFIFOUAn: CAN FIFO USER ADDRESS REGISTER 'n' (n = 0 THROUGH 31)

#### Legend:

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, r | ead as '0'         |

|-------------------|------------------|--------------------------|--------------------|

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared     | x = Bit is unknown |

bit 31-0 CiFIFOUAn<31:0>: CAN FIFO User Address bits

TXEN = 1: (FIFO configured as a transmit buffer)

A read of this register will return the address where the next message is to be written (FIFO head).

TXEN = 0: (FIFO configured as a receive buffer)

A read of this register will return the address where the next message is to be read (FIFO tail).

**Note 1:** This bit will always read '0', which forces byte-alignment of messages.

**Note:** This register is not guaranteed to read correctly in Configuration mode, and should only be accessed when the module is not in Configuration mode.

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|

| 31:24        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 31.24        | —                 | —                 | —                 | —                 | —                 | —                 | —                | —                |

| 23:16        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 23.10        | —                 | —                 | _                 | _                 | _                 | _                 |                  | _                |

| 15:8         | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 15.0         | —                 | —                 | _                 | _                 | _                 | _                 |                  | _                |

| 7:0          | U-0               | U-0               | U-0               | R-0               | R-0               | R-0               | R-0              | R-0              |

| 7.0          | —                 | —                 | -                 |                   | (                 | CiFIFOCI<4:0      | >                |                  |

#### **REGISTER 24-23:** CiFIFOCIN: CAN MODULE MESSAGE INDEX REGISTER 'n' (n = 0 THROUGH 31)

#### Legend:

| J                 |                  |                          |                    |

|-------------------|------------------|--------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, r | ead as '0'         |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared     | x = Bit is unknown |

bit 31-5 Unimplemented: Read as '0'

bit 4-0 CiFIFOCIn<4:0>: CAN Side FIFO Message Index bits

TXEN = 1: (FIFO configured as a transmit buffer)

A read of this register will return an index to the message that the FIFO will next attempt to transmit.

TXEN = 0: (FIFO configured as a receive buffer)

A read of this register will return an index to the message that the FIFO will use to save the next message.

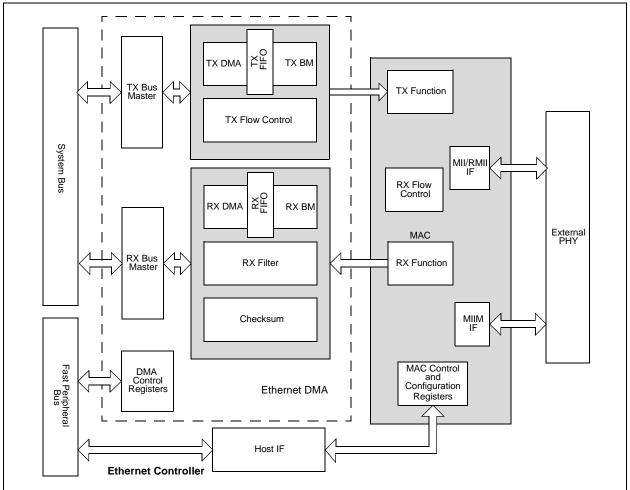

# 25.0 ETHERNET CONTROLLER

Note: This data sheet summarizes the features of the PIC32MX5XX/6XX/7XX family of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to Section 35. "Ethernet Controller" (DS60001155) in the "PIC32 Family Reference Manual", which is available from the Microchip web site (www.microchip.com/PIC32).

The Ethernet controller is a bus master module that interfaces with an off-chip Physical Layer (PHY) to implement a complete Ethernet node in a system.

Key features of the Ethernet Controller include:

- Supports 10/100 Mbps data transfer rates

- Supports full-duplex and half-duplex operation

- Supports RMII and MII PHY interface

- Supports MIIM PHY management interface

- Supports both manual and automatic Flow Control

- RAM descriptor-based DMA operation for both receive and transmit path

- · Fully configurable interrupts

- Configurable receive packet filtering

- CRC check

- 64-byte pattern match

- Broadcast, multicast and unicast packets

- Magic Packet™

- 64-bit hash table

- Runt packet

- Supports packet payload checksum calculation

- · Supports various hardware statistics counters

Figure 25-1 illustrates a block diagram of the Ethernet controller.

#### FIGURE 25-1: ETHERNET CONTROLLER BLOCK DIAGRAM

#### REGISTER 25-20: ETHFRMRXOK: ETHERNET CONTROLLER FRAMES RECEIVED OK STATISTICS REGISTER

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|

| 24.24        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 31:24        | _                 | _                 | _                 | _                 | _                 | _                 | _                | —                |

| 00.40        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 23:16        | _                 | _                 | _                 | _                 | _                 | _                 | _                | —                |

| 45.0         | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |

| 15:8         |                   |                   |                   | FRMRXOK           | CNT<15:8>         |                   |                  |                  |

| 7.0          | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |

| 7:0          |                   |                   |                   | FRMRXOK           | (CNT<7:0>         |                   |                  |                  |

#### Legend:

| 3                 |                  |                        |                    |  |

|-------------------|------------------|------------------------|--------------------|--|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, | read as '0'        |  |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared   | x = Bit is unknown |  |

#### bit 31-16 Unimplemented: Read as '0'

bit 15-0 FRMRXOKCNT<15:0>: Frames Received OK Count bits

Increment count for frames received successfully by the RX Filter. This count will not be incremented if there is a Frame Check Sequence (FCS) or Alignment error.

Note 1: This register is only used for RX operations.

- 2: This register is automatically cleared by hardware after a read operation, unless the byte enables for bytes 0/1 are '0'.

- **3:** It is recommended to use the SET, CLR, or INV registers to set or clear any bit in this register. Setting or clearing any bits in this register should only be done for debug/test purposes.

# REGISTER 25-24: EMAC1CFG2: ETHERNET CONTROLLER MAC CONFIGURATION 2 REGISTER (CONTINUED)

- VLANPAD: VLAN Pad Enable bit<sup>(1,2)</sup> bit 6 1 = The MAC will pad all short frames to 64 bytes and append a valid CRC 0 = The MAC does not perform padding of short frames PADENABLE: Pad/CRC Enable bit<sup>(1,3)</sup> bit 5 1 = The MAC will pad all short frames 0 = The frames presented to the MAC have a valid length bit 4 CRCENABLE: CRC Enable1 bit 1 = The MAC will append a CRC to every frame whether padding was required or not. Must be set if the PADENABLE bit is set. 0 = The frames presented to the MAC have a valid CRC bit 3 DELAYCRC: Delayed CRC bit This bit determines the number of bytes, if any, of proprietary header information that exist on the front of the IEEE 802.3 frames. 1 = Four bytes of header (ignored by the CRC function) 0 = No proprietary header bit 2 HUGEFRM: Huge Frame enable bit 1 = Frames of any length are transmitted and received 0 = Huge frames are not allowed for receive or transmit LENGTHCK: Frame Length checking bit bit 1 1 = Both transmit and receive frame lengths are compared to the Length/Type field. If the Length/Type field represents a length then the check is performed. Mismatches are reported on the transmit/receive statistics vector. 0 = Length/Type field check is not performed bit 0 FULLDPLX: Full-Duplex Operation bit 1 = The MAC operates in Full-Duplex mode 0 = The MAC operates in Half-Duplex mode

- Note 1: Table 25-6 provides a description of the pad function based on the configuration of this register.

- 2: This bit is ignored if the PADENABLE bit is cleared.

- **3:** This bit is used in conjunction with the AUTOPAD and VLANPAD bits.

**Note:** Both 16-bit and 32-bit accesses are allowed to these registers (including the SET, CLR and INV registers). 8-bit accesses are not allowed and are ignored by the hardware

#### TABLE 25-6:PAD OPERATION

| Туре | AUTOPAD | VLANPAD | PADENABLE | Action                                                                                  |

|------|---------|---------|-----------|-----------------------------------------------------------------------------------------|

| Any  | x       | x       | 0         | No pad, check CRC                                                                       |

| Any  | 0       | 0       | 1         | Pad to 60 Bytes, append CRC                                                             |

| Any  | x       | 1       | 1         | Pad to 64 Bytes, append CRC                                                             |

| Any  | 1       | 0       | 1         | If untagged: Pad to 60 Bytes, append CRC<br>If VLAN tagged: Pad to 64 Bytes, append CRC |

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3        | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0         |

|--------------|-------------------|-------------------|-------------------|-------------------|--------------------------|-------------------|------------------|--------------------------|

| 31:24        | U-0               | U-0               | U-0               | U-0               | U-0                      | U-0               | U-0              | U-0                      |

| 31.24        |                   | —                 | -                 | -                 | —                        | —                 | —                | —                        |

| 23:16        | U-0               | U-0               | U-0               | U-0               | U-0                      | U-0               | U-0              | U-0                      |

| 23.10        |                   | —                 | -                 | -                 | —                        | —                 | —                | —                        |

| 15:8         | U-0               | U-0               | U-0               | U-0               | R/W-0                    | U-0               | U-0              | R/W-0                    |

| 10.0         | _                 | —                 | _                 | _                 | RESETRMII <sup>(1)</sup> | —                 | —                | SPEEDRMII <sup>(1)</sup> |

| 7:0          | U-0               | U-0               | U-0               | U-0               | U-0                      | U-0               | U-0              | U-0                      |

| 7.0          |                   | _                 |                   |                   | _                        | _                 |                  | —                        |

#### REGISTER 25-29: EMAC1SUPP: ETHERNET CONTROLLER MAC PHY SUPPORT REGISTER

#### Legend:

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read as '0' |                    |  |  |

|-------------------|------------------|------------------------------------|--------------------|--|--|

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared               | x = Bit is unknown |  |  |

- bit 31-12 Unimplemented: Read as '0'

- bit 11 **RESETRMII:** Reset RMII Logic bit<sup>(1)</sup>

- 1 = Reset the MAC RMII module

- 0 = Normal operation.

- bit 10-9 Unimplemented: Read as '0'

- bit 8 SPEEDRMII: RMII Speed bit<sup>(1)</sup>

- This bit configures the Reduced MII logic for the current operating speed.

- 1 = RMII is running at 100 Mbps

- 0 = RMII is running at 10 Mbps

- bit 7-0 Unimplemented: Read as '0'

- Note 1: This bit is only used for the RMII module.

**Note:** Both 16-bit and 32-bit accesses are allowed to these registers (including the SET, CLR and INV registers). 8-bit accesses are not allowed and are ignored by the hardware.

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5   | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

|--------------|-------------------|-------------------|---------------------|-------------------|-------------------|-------------------|------------------|------------------|

| 31:24        | U-0               | U-0               | U-0                 | U-0               | U-0               | U-0               | U-0              | U-0              |

| 31.24        |                   | —                 |                     | _                 | _                 | _                 | _                | _                |

| 23:16        | U-0               | U-0               | U-0                 | U-0               | U-0               | U-0               | U-0              | U-0              |

| 23.10        | —                 | —                 | —                   | -                 | —                 | —                 | —                | —                |

| 15.0         | R/W-0             | R/W-0             | R/W-0               | U-0               | U-0               | U-0               | U-0              | R-0              |

| 15:8         | 0N <sup>(1)</sup> | COE               | CPOL <sup>(2)</sup> | -                 | —                 | —                 | —                | COUT             |

| 7:0          | R/W-1             | R/W-1             | U-0                 | R/W-0             | U-0               | U-0               | R/W-1            | R/W-1            |

| 7.0          | EVPOL             | _<1:0>            |                     | CREF              | _                 |                   | CCH              | <1:0>            |

#### REGISTER 26-1: CMxCON: COMPARATOR 'x' CONTROL REGISTER

#### Legend:

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, re | ead as '0'         |

|-------------------|------------------|---------------------------|--------------------|

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared      | x = Bit is unknown |

#### bit 31-16 Unimplemented: Read as '0'

bit 15 ON: Comparator ON bit<sup>(1)</sup>

Clearing this bit does not affect the other bits in this register.

- 1 = Module is enabled. Setting this bit does not affect the other bits in this register

- 0 = Module is disabled and does not consume current.

- bit 14 COE: Comparator Output Enable bit

- 1 = Comparator output is driven on the output CxOUT pin

- 0 = Comparator output is not driven on the output CxOUT pin

- bit 13 **CPOL:** Comparator Output Inversion bit<sup>(2)</sup>

- 1 = Output is inverted

- 0 = Output is not inverted

#### bit 12-9 Unimplemented: Read as '0'

- bit 8 COUT: Comparator Output bit

- 1 =Output of the Comparator is a '1'

- 0 = Output of the Comparator is a '0'

- bit 7-6 EVPOL<1:0>: Interrupt Event Polarity Select bits

- 11 = Comparator interrupt is generated on a low-to-high or high-to-low transition of the comparator output

- 10 = Comparator interrupt is generated on a high-to-low transition of the comparator output

- 01 = Comparator interrupt is generated on a low-to-high transition of the comparator output

- 00 = Comparator interrupt generation is disabled

#### bit 5 Unimplemented: Read as '0'

- bit 4 **CREF:** Comparator Positive Input Configure bit

- 1 = Comparator non-inverting input is connected to the internal CVREF

- 0 = Comparator non-inverting input is connected to the CxIN+ pin

- bit 3-2 Unimplemented: Read as '0'

- bit 1-0 **CCH<1:0>:** Comparator Negative Input Select bits for Comparator

- 11 = Comparator inverting input is connected to the IVREF

- 10 = Comparator inverting input is connected to the C2IN+ pin for C1 and C1IN+ pin for C2

- 01 = Comparator inverting input is connected to the C1IN+ pin for C1 and C2IN+ pin for C2

- 00 = Comparator inverting input is connected to the C1IN- pin for C1 and C2IN- pin for C2

- **Note 1:** When using the 1:1 PBCLK divisor, the user's software should not read/write the peripheral's SFRs in the SYSCLK cycle immediately following the instruction that clears the module's ON bit.

- 2: Setting this bit will invert the signal to the comparator interrupt generator as well. This will result in an interrupt being generated on the opposite edge from the one selected by EVPOL<1:0>.

## **30.0 INSTRUCTION SET**

The PIC32MX5XX/6XX/7XX family instruction set complies with the MIPS32 Release 2 instruction set architecture. The PIC32 device family does not support the following features:

- Core Extend instructions

- Coprocessor 1 instructions

- Coprocessor 2 instructions

Note: Refer to "MIPS32<sup>®</sup> Architecture for Programmers Volume II: The MIPS32<sup>®</sup> Instruction Set" at www.imgtec.com for more information.

#### TABLE 32-7: DC CHARACTERISTICS: POWER-DOWN CURRENT (IPD)

| DC CHA                                                                                | RACTERIS               | TICS           | $\begin{tabular}{lllllllllllllllllllllllllllllllllll$ |            |                                                   |                                                    |  |  |  |

|---------------------------------------------------------------------------------------|------------------------|----------------|-------------------------------------------------------|------------|---------------------------------------------------|----------------------------------------------------|--|--|--|

| Param.<br>No.                                                                         | Typical <sup>(2)</sup> | Max.           | Units                                                 | Conditions |                                                   |                                                    |  |  |  |

| Power-Down Current (IPD) <sup>(1)</sup> for PIC32MX575/675/695/775/795 Family Devices |                        |                |                                                       |            |                                                   |                                                    |  |  |  |

| DC40                                                                                  | 10                     | 40             |                                                       | -40°C      |                                                   |                                                    |  |  |  |

| DC40a                                                                                 | 36                     | 100            |                                                       | +25°C      | 2.3V                                              | Base Power-Down Current (Note 6)                   |  |  |  |

| DC40b                                                                                 | 400                    | 720            |                                                       | +85°C      | 2.30                                              | Base Power-Down Current (Note 6)                   |  |  |  |

| DC40h                                                                                 | 900                    | 1800           |                                                       | +105°C     |                                                   |                                                    |  |  |  |

| DC40c                                                                                 | 41                     | 120            |                                                       | +25°C      | 3.3V                                              | Base Power-Down Current                            |  |  |  |

| DC40d                                                                                 | 22                     | 80             | μA                                                    | -40°C      |                                                   |                                                    |  |  |  |

| DC40e                                                                                 | 42                     | 120            |                                                       | +25°C      |                                                   |                                                    |  |  |  |

| DC40g                                                                                 | 315                    | 400 <b>(5)</b> |                                                       | +70°C      | 3.6V                                              | Base Power-Down Current (Note 6)                   |  |  |  |

| DC40f                                                                                 | 410                    | 800            |                                                       | +85°C      |                                                   |                                                    |  |  |  |

| DC40i                                                                                 | 1000                   | 2000           |                                                       | +105°C     |                                                   |                                                    |  |  |  |

| Module                                                                                | Differential           | Current fo     | or PIC32N                                             | IX575/675/ | 695/775/                                          | 795 Family Devices                                 |  |  |  |

| DC41                                                                                  |                        | 10             |                                                       |            | 2.3V                                              | Watchdog Timer Current: AIWDT (Notes 3,6)          |  |  |  |

| DC41a                                                                                 | 5                      |                | μA                                                    | _          | 3.3V                                              | Watchdog Timer Current: ∆IwDT (Note 3)             |  |  |  |

| DC41b                                                                                 | —                      | 20             |                                                       |            | 3.6V                                              | Watchdog Timer Current: ∆IwDT (Note 3,6)           |  |  |  |

| DC42                                                                                  |                        | 40             |                                                       |            | 2.3V                                              | RTCC + Timer1 w/32 kHz Crystal: ΔIRTCC (Notes 3,6) |  |  |  |

| DC42a                                                                                 | 23                     | _              | μA                                                    | —          | 3.3V RTCC + Timer1 w/32 kHz Crystal: ΔIRTCC (Note |                                                    |  |  |  |

| DC42b                                                                                 | —                      | 50             | 1                                                     |            | 3.6V                                              | RTCC + Timer1 w/32 kHz Crystal: ΔIRTCC (Note 3,6)  |  |  |  |

| DC43                                                                                  | —                      | 1300           |                                                       |            | 2.5V                                              | ADC: ΔIADC (Notes 3,4,6)                           |  |  |  |

| DC43a                                                                                 | 1100                   |                | μA                                                    | —          | 3.3V                                              | ADC: Aladc (Notes 3,4)                             |  |  |  |

| DC43b                                                                                 | —                      | 1300           | 1                                                     |            | 3.6V                                              | ADC: ΔIADC (Notes 3,4,6)                           |  |  |  |

Note 1: The test conditions for IPD current measurements are as follows:

- Oscillator mode is EC (for 8 MHz and below) and EC+PLL (for above 8 MHz) with OSC1 driven by external square wave from rail-to-rail, (OSC1 input clock input over/undershoot < 100 mV required)</li>

- OSC2/CLKO is configured as an I/O input pin

- USB PLL oscillator is disabled if the USB module is implemented, PBCLK divisor = 1:8

- CPU is in Sleep mode, program Flash memory Wait states = 111, Program Cache and Prefetch are disabled and SRAM data memory Wait states = 1

- No peripheral modules are operating, (ON bit = 0)

- WDT, Clock Switching, Fail-Safe Clock Monitor, and Secondary Oscillator are disabled

- All I/O pins are configured as inputs and pulled to Vss

- $\overline{\text{MCLR}} = \text{VDD}$

- RTCC and JTAG are disabled

- 2: Data in the "Typical" column is at 3.3V, 25°C unless otherwise stated. Parameters are for design guidance only and are not tested.

- 3: The ∆ current is the additional current consumed when the module is enabled. This current should be added to the base IPD current.

- 4: Test conditions for ADC module differential current are as follows: Internal ADC RC oscillator enabled.

- 5: Data is characterized at +70°C and not tested. Parameter is for design guidance only.

- 6: This parameter is characterized, but not tested in manufacturing.

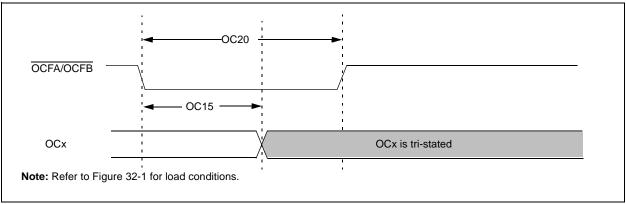

#### FIGURE 32-9: OCx/PWM MODULE TIMING CHARACTERISTICS

#### TABLE 32-27: SIMPLE OCx/PWM MODE TIMING REQUIREMENTS

| AC CHAF      | AC CHARACTERISTICS               |                                | $\begin{array}{l} \mbox{Standard Operating Conditions: 2.3V to 3.6V} \\ \mbox{(unless otherwise stated)} \\ \mbox{Operating temperature} & -40^{\circ}C \leq TA \leq +85^{\circ}C \mbox{ for Industrial} \\ & -40^{\circ}C \leq TA \leq +105^{\circ}C \mbox{ for V-Temp} \end{array}$ |                        |     |       |            |  |

|--------------|----------------------------------|--------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------|-----|-------|------------|--|

| Param<br>No. | Symbol                           | Characteristics <sup>(1)</sup> | Min                                                                                                                                                                                                                                                                                   | Typical <sup>(2)</sup> | Max | Units | Conditions |  |

| OC15         | Tfd                              | Fault Input to PWM I/O Change  | —                                                                                                                                                                                                                                                                                     | —                      | 50  | ns    | _          |  |

| OC20         | C20 TFLT Fault Input Pulse Width |                                | 50                                                                                                                                                                                                                                                                                    | —                      | _   | ns    | —          |  |

Note 1: These parameters are characterized, but not tested in manufacturing.

2: Data in "Typical" column is at 3.3V, 25°C unless otherwise stated. Parameters are for design guidance only and are not tested.

# PIC32MX5XX/6XX/7XX

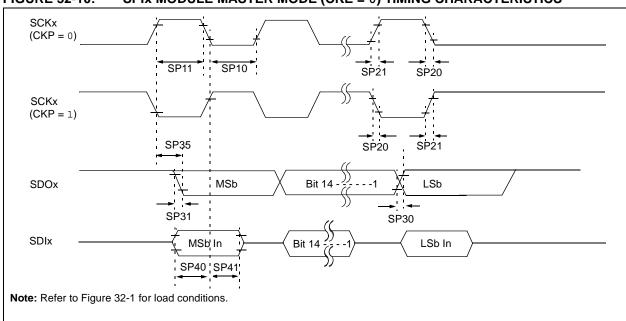

### FIGURE 32-10: SPIX MODULE MASTER MODE (CKE = 0) TIMING CHARACTERISTICS

#### TABLE 32-28: SPIx MASTER MODE (CKE = 0) TIMING REQUIREMENTS

| АС СНА               | ARACTERIST            | TICS                                         | $\begin{array}{l} \mbox{Standard Operating Conditions: 2.3V to 3.6V} \\ \mbox{(unless otherwise stated)} \\ \mbox{Operating temperature} & -40^\circ C \leq TA \leq +85^\circ C \mbox{ for Industrial} \\ -40^\circ C \leq TA \leq +105^\circ C \mbox{ for V-Temp} \end{array}$ |   |    |            |                    |  |

|----------------------|-----------------------|----------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---|----|------------|--------------------|--|

| Param.<br>No. Symbol |                       | Characteristics <sup>(1)</sup>               | Min. Typical <sup>(2)</sup> Max. Units Condit                                                                                                                                                                                                                                   |   |    | Conditions |                    |  |

| SP10                 | TscL                  | SCKx Output Low Time <sup>(3)</sup>          | Tsck/2                                                                                                                                                                                                                                                                          | _ | —  | ns         | _                  |  |

| SP11                 | TscH                  | SCKx Output High Time <sup>(3)</sup>         | Tsck/2                                                                                                                                                                                                                                                                          | _ |    | ns         | —                  |  |

| SP20                 | TscF                  | SCKx Output Fall Time <sup>(4)</sup>         | _                                                                                                                                                                                                                                                                               | _ |    | ns         | See parameter DO32 |  |

| SP21                 | TscR                  | SCKx Output Rise Time <sup>(4)</sup>         | -                                                                                                                                                                                                                                                                               | _ |    | ns         | See parameter DO31 |  |

| SP30                 | TDOF                  | SDOx Data Output Fall Time <sup>(4)</sup>    | _                                                                                                                                                                                                                                                                               | _ | —  | ns         | See parameter DO32 |  |

| SP31                 | TDOR                  | SDOx Data Output Rise<br>Time <sup>(4)</sup> | _                                                                                                                                                                                                                                                                               | — | —  | ns         | See parameter DO31 |  |

| SP35                 | TscH2doV,<br>TscL2doV | SDOx Data Output Valid after<br>SCKx Edge    | _                                                                                                                                                                                                                                                                               | — | 15 | ns         | VDD > 2.7V         |  |

|                      |                       |                                              | _                                                                                                                                                                                                                                                                               | — | 20 | ns         | VDD < 2.7V         |  |

| SP40                 | TDIV2SCH,<br>TDIV2SCL | Setup Time of SDIx Data Input to SCKx Edge   | 10                                                                                                                                                                                                                                                                              | — | —  | ns         | —                  |  |

| SP41                 | TSCH2DIL,<br>TSCL2DIL | Hold Time of SDIx Data Input to SCKx Edge    | 10                                                                                                                                                                                                                                                                              | — | —  | ns         | —                  |  |

Note 1: These parameters are characterized, but not tested in manufacturing.

2: Data in "Typical" column is at 3.3V, 25°C unless otherwise stated. Parameters are for design guidance only and are not tested.

**3:** The minimum clock period for SCKx is 40 ns. Therefore, the clock generated in Master mode must not violate this specification.

4: Assumes 50 pF load on all SPIx pins.

64-Lead Plastic Quad Flat, No Lead Package (MR) – 9x9x0.9 mm Body [QFN] With 0.40 mm Contact Length

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging