Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFI

| Detano                     |                                                                                |

|----------------------------|--------------------------------------------------------------------------------|

| Product Status             | Active                                                                         |

| Core Processor             | MIPS32® M4K™                                                                   |

| Core Size                  | 32-Bit Single-Core                                                             |

| Speed                      | 80MHz                                                                          |

| Connectivity               | CANbus, Ethernet, I <sup>2</sup> C, SPI, UART/USART, USB OTG                   |

| Peripherals                | Brown-out Detect/Reset, DMA, POR, PWM, WDT                                     |

| Number of I/O              | 53                                                                             |

| Program Memory Size        | 128KB (128K x 8)                                                               |

| Program Memory Type        | FLASH                                                                          |

| EEPROM Size                | -                                                                              |

| RAM Size                   | 32K x 8                                                                        |

| Voltage - Supply (Vcc/Vdd) | 2.3V ~ 3.6V                                                                    |

| Data Converters            | A/D 16x10b                                                                     |

| Oscillator Type            | Internal                                                                       |

| Operating Temperature      | -40°C ~ 105°C (TA)                                                             |

| Mounting Type              | Surface Mount                                                                  |

| Package / Case             | 64-TQFP                                                                        |

| Supplier Device Package    | 64-TQFP (10x10)                                                                |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic32mx764f128h-v-pt |

|                            |                                                                                |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

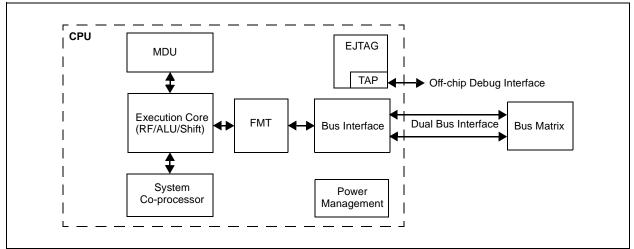

# 3.0 CPU

Note: This data sheet summarizes the features of the PIC32MX5XX/6XX/7XX family of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to Section 2. "CPU" (DS60001113) in the "PIC32 Family Reference Manual", which is available from the Microchip web site (www.microchip.com/PIC32). Resources for the MIPS32<sup>®</sup> M4K<sup>®</sup> Processor Core are available at http://www.imgtec.com.

The MIPS32<sup>®</sup> M4K<sup>®</sup> Processor core is the heart of the PIC32MX5XX/6XX/7XX family processor. The CPU fetches instructions, decodes each instruction, fetches source operands, executes each instruction and writes the results of instruction execution to the proper destinations.

# 3.1 Features

- 5-stage pipeline

- · 32-bit address and data paths

- MIPS32 Enhanced Architecture (Release 2)

- Multiply-accumulate and multiply-subtract instructions

- Targeted multiply instruction

- Zero/One detect instructions

- WAIT instruction

- Conditional move instructions (MOVN, MOVZ)

- Vectored interrupts

- Programmable exception vector base

- Atomic interrupt enable/disable

- GPR shadow registers to minimize latency for interrupt handlers

- Bit field manipulation instructions

- MIPS16e<sup>®</sup> code compression

- 16-bit encoding of 32-bit instructions to improve code density

- Special PC-relative instructions for efficient loading of addresses and constants

- SAVE and RESTORE macro instructions for setting up and tearing down stack frames within subroutines

- Improved support for handling 8-bit and 16-bit data types

- Simple Fixed Mapping Translation (FMT) mechanism

- Simple dual bus interface

- Independent 32-bit address and data busses

- Transactions can be aborted to improve interrupt latency

- · Autonomous multiply/divide unit

- Maximum issue rate of one 32x16 multiply per clock

- Maximum issue rate of one 32x32 multiply every other clock

- Early-in iterative divide. Minimum 11 and maximum 33 clock latency (dividend (*rs*) sign extension-dependent)

- Power control

- Minimum frequency: 0 MHz

- Low-Power mode (triggered by WAIT instruction)

- Extensive use of local gated clocks

- EJTAG debug and instruction trace

- Support for single stepping

- Virtual instruction and data address/value

- Breakpoints

- PC tracing with trace compression

# FIGURE 3-1: MIPS32<sup>®</sup> M4K<sup>®</sup> PROCESSOR CORE BLOCK DIAGRAM

## 3.3 Power Management

The MIPS32 M4K Processor core offers a number of power management features, including low-power design, active power management and power-down modes of operation. The core is a static design that supports slowing or halting the clocks, which reduces system power consumption during idle periods.

#### 3.3.1 INSTRUCTION-CONTROLLED POWER MANAGEMENT

The mechanism for invoking Power-Down mode is through execution of the WAIT instruction. For more information on power management, see Section 28.0 "Power-Saving Features".

#### 3.3.2 LOCAL CLOCK GATING

The majority of the power consumed by the PIC32MX-5XX/6XX/7XX family core is in the clock tree and clocking registers. The PIC32 family uses extensive use of local gated clocks to reduce this dynamic power consumption.

## 3.4 EJTAG Debug Support

The MIPS32 M4K Processor core provides for an Enhanced JTAG (EJTAG) interface for use in the software debug of application and kernel code. In addition to standard User mode and Kernel modes of operation, the MIPS M4K core provides a Debug mode that is entered after a debug exception (derived from a hardware breakpoint, single-step exception, etc.) is taken and continues until a Debug Exception Return (DERET) instruction is executed. During this time, the processor executes the debug exception handler routine.

The EJTAG interface operates through the Test Access Port (TAP), a serial communication port used for transferring test data in and out of the MIPS32 M4K processor core. In addition to the standard JTAG instructions, special instructions defined in the EJTAG specification define which registers are selected and how they are used.

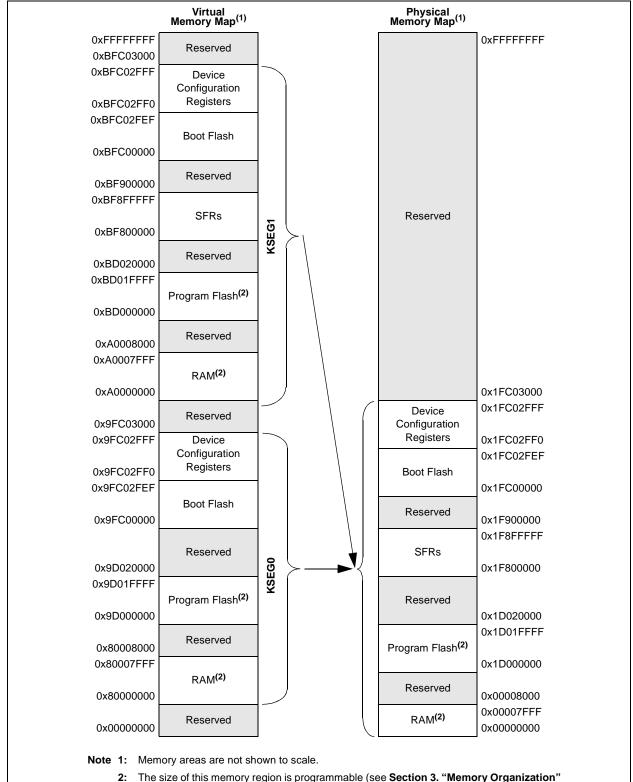

# FIGURE 4-3: MEMORY MAP ON RESET FOR PIC32MX564F128H, PIC32MX564F128L, PIC32MX664F128H, PIC32MX664F128L, PIC32MX764F128H AND PIC32MX764F128L DEVICES

(DS60001115)) and can be changed by initialization code provided by end user development tools (refer to the specific development tool documentation for information).

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1   | Bit<br>24/16/8/0   |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|--------------------|--------------------|

| 31:24        | U-0                | U-0                |

| 31.24        |                   | _                 | -                 | —                 | _                 | —                 |                    | —                  |

| 23:16        | U-0                | U-0                |

| 23.10        | _                 | _                 | _                 | —                 | _                 | —                 |                    | —                  |

| 45.0         | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | R/W-0, HS          | R/W-0              |

| 15:8         | —                 | _                 | —                 | —                 | _                 | —                 | CMR                | VREGS              |

| 7.0          | R/W-0, HS         | R/W-0, HS         | U-0               | R/W-0, HS         | R/W-0, HS         | R/W-0, HS         | R/W-1, HS          | R/W-1, HS          |

| 7:0          | EXTR              | SWR               | _                 | WDTO              | SLEEP             | IDLE              | BOR <sup>(1)</sup> | POR <sup>(1)</sup> |

#### REGISTER 6-1: RCON: RESET CONTROL REGISTER

| Legend:           | HS = Set by hardware |                           |                    |

|-------------------|----------------------|---------------------------|--------------------|

| R = Readable bit  | W = Writable bit     | U = Unimplemented bit, re | ad as '0'          |

| -n = Value at POR | '1' = Bit is set     | '0' = Bit is cleared      | x = Bit is unknown |

| bit 31-10 | Unimplemented: Read as '0 | n' |

|-----------|---------------------------|----|

|           | eninplemented. Read as    |    |

| bit 9 | CMR: Configuration Mismatch Reset Flag bit                                   |

|-------|------------------------------------------------------------------------------|

|       | 1 = Configuration mismatch Reset has occurred                                |

|       | 0 = Configuration mismatch Reset has not occurred                            |

| bit 8 | VREGS: Voltage Regulator Standby Enable bit                                  |

|       | $\ensuremath{\mathtt{l}}$ = Regulator is enabled and is on during Sleep mode |

|       | 0 = Regulator is set to Stand-by Tracking mode                               |

| bit 7 | EXTR: External Reset (MCLR) Pin Flag bit                                     |

|       | 1 = Master Clear (pin) Reset has occurred                                    |

|       | 0 = Master Clear (pin) Reset has not occurred                                |

| bit 6 | SWR: Software Reset Flag bit                                                 |

|       | 1 = Software Reset was executed                                              |

|       | 0 = Software Reset was not executed                                          |

| bit 5 | Unimplemented: Read as '0'                                                   |

| bit 4 | WDTO: Watchdog Timer Time-out Flag bit                                       |

|       | 1 = WDT Time-out has occurred                                                |

|       | 0 = WDT Time-out has not occurred                                            |

| bit 3 | SLEEP: Wake From Sleep Flag bit                                              |

|       | 1 = Device was in Sleep mode                                                 |

|       | 0 = Device was not in Sleep mode                                             |

| bit 2 | IDLE: Wake From Idle Flag bit                                                |

|       | 1 = Device was in Idle mode                                                  |

|       | 0 = Device was not in Idle mode                                              |

| bit 1 | BOR: Brown-out Reset Flag bit <sup>(1)</sup>                                 |

|       | 1 = Brown-out Reset has occurred                                             |

|       | 0 = Brown-out Reset has not occurred                                         |

| bit 0 | <b>POR:</b> Power-on Reset Flag bit <sup>(1)</sup>                           |

|       | 1 = Power-on Reset has occurred                                              |

|       | 0 = Power-on Reset has not occurred                                          |

|       |                                                                              |

Note 1: User software must clear this bit to view the next detection.

#### **TABLE 7-3**: INTERRUPT REGISTER MAP FOR PIC32MX664F064H, PIC32MX664F128H, PIC32MX675F256H, PIC32MX675F512H AND PIC32MX695F512H DEVICES (CONTINUED)

| ess                         |                                 |           |       |       |       |       |                        |       |        | В                | its  |      |      |                            |             |        |                      |        |            |

|-----------------------------|---------------------------------|-----------|-------|-------|-------|-------|------------------------|-------|--------|------------------|------|------|------|----------------------------|-------------|--------|----------------------|--------|------------|

| Virtual Address<br>(BF88_#) | Register<br>Name <sup>(1)</sup> | Bit Range | 31/15 | 30/14 | 29/13 | 28/12 | 27/11                  | 26/10 | 25/9   | 24/8             | 23/7 | 22/6 | 21/5 | 20/4                       | 19/3        | 18/2   | 17/1                 | 16/0   | All Resets |

| 4000                        | IPC4                            | 31:16     | —     | _     | —     |       | INT4IP<2:0>            |       | INT4IS | S<1:0>           | —    | -    | —    |                            | OC4IP<2:0>  | •      | OC4IS                | 5<1:0> | 0000       |

| 10D0                        | IPC4                            | 15:0      | _     | -     | _     |       | IC4IP<2:0>             |       | IC4IS  | <1:0>            | _    | _    | _    |                            | T4IP<2:0>   |        | T4IS                 | <1:0>  | 0000       |

| 10E0                        | IPC5                            | 31:16     | _     | -     | _     | _     | _                      | _     | _      | _                | _    | _    | _    |                            | OC5IP<2:0>  | •      | OC5IS                | 5<1:0> | 0000       |

| IUEU                        | IPC5                            | 15:0      | —     | _     | -     |       | IC5IP<2:0>             |       | IC5IS  | <1:0>            | —    |      |      |                            | T5IP<2:0>   |        | T5IS<                | <1:0>  | 0000       |

|                             |                                 | 31:16     | _     | -     | _     |       | AD1IP<2:0>             |       | AD1IS  | S<1:0>           | _    | _    | _    |                            | CNIP<2:0>   |        | CNIS                 | <1:0>  | 0000       |

| 10F0                        | IPC6                            |           |       |       |       |       |                        |       |        |                  |      |      |      |                            | U1IP<2:0>   |        | U1IS-                | <1:0>  |            |

| IOFU                        | IFCO                            | 15:0      | —     | —     | —     |       | I2C1IP<2:0>            |       | 12C115 | S<1:0>           | —    | —    | —    |                            | SPI3IP<2:0> | >      | SPI3IS               | S<1:0> | 0000       |

|                             |                                 |           |       |       |       |       |                        |       |        |                  |      |      |      | I2C3IP<2:0>                |             | >      | I2C3IS<1:0>          |        |            |

|                             |                                 |           |       |       |       |       | U3IP<2:0>              |       | U3IS-  | <1:0>            |      |      |      |                            |             |        |                      |        |            |

| 1100                        | IPC7                            | 31:16     | —     | -     | —     |       | SPI2IP<2:0>            |       | SPI2IS | S<1:0>           | —    | —    | —    | CMP2IP<2:0>                |             | CMP2I  | S<1:0>               | 0000   |            |

| 1100                        | 11 07                           |           |       |       |       |       | I2C4IP<2:0>            |       | 12C415 | S<1:0>           |      |      |      |                            |             |        |                      |        |            |

|                             |                                 | 15:0      | _     | —     |       | (     | CMP1IP<2:0:            | >     | CMP1   | S<1:0>           | —    |      |      |                            | PMPIP<2:0>  | >      | PMPIS                | S<1:0> | 0000       |

|                             |                                 | 31:16     | —     | —     | —     | F     | RTCCIP<2:0:            | >     | RTCCI  | S<1:0>           | —    | —    |      | I                          | FSCMIP<2:0  | >      | FSCM                 | S<1:0> | 0000       |

| 1110                        | IPC8                            |           |       |       |       |       |                        |       |        |                  |      |      |      |                            | U2IP<2:0>   |        | U2IS-                | <1:0>  |            |

|                             | 11 00                           | 15:0      | —     | -     | —     | —     | —                      | —     | —      | —                | —    | —    | —    |                            | SPI4IP<2:0> | >      | SPI4IS               | S<1:0> | 0000       |

|                             |                                 |           |       |       |       |       |                        |       |        |                  |      |      |      |                            | I2C5IP<2:0> | >      | 12C515               | S<1:0> |            |

| 1120                        | IPC9                            | 31:16     | —     | —     | —     |       | DMA3IP<2:0:            |       | DMA3   |                  | —    | _    |      |                            | DMA2IP<2:0  |        | DMA2                 |        | 0000       |

| 1120                        | 11 00                           | 15:0      | _     | —     |       |       | DMA1IP<2:0:            |       | DMA1   |                  | —    | _    |      |                            | DMA0IP<2:0  |        | DMA0I                |        | 0000       |

| 1130                        | IPC10                           | 31:16     | —     | —     | —     |       | DMA7IP<2:0> <b>(2)</b> |       |        | <1:0> <b>(2)</b> | —    | _    |      | DMA6IP<2:0> <sup>(2)</sup> |             | DMA6IS |                      | 0000   |            |

| 1130                        | 11 010                          | 15:0      | _     | —     |       | D     | MA5IP<2:0>             | (2)   | DMA5IS | <1:0> <b>(2)</b> | —    | _    |      | DMA4IP<2:0> <sup>(2)</sup> |             | DMA4IS | <1:0> <sup>(2)</sup> | 0000   |            |

| 1140                        | IPC11                           | 31:16     | —     | —     | —     | _     | —                      | —     | —      | —                | —    | _    | _    | —                          | _           | —      | —                    | —      | 0000       |

|                             |                                 | 15:0      | —     | —     | —     |       | USBIP<2:0>             |       | USBIS  |                  | —    | —    | —    |                            | FCEIP<2:0>  |        | FCEIS                |        | 0000       |

| 1150                        | IPC12                           | 31:16     | —     | —     | _     |       | U5IP<2:0>              |       | U5IS-  | <1:0>            | —    | _    | _    |                            | U6IP<2:0>   |        | U6IS-                | <1:0>  | 0000       |

| 1100                        | 11 012                          | 15:0      | _     | —     | —     |       | U4IP<2:0>              |       | U4IS-  | <1:0>            | —    | _    | —    |                            | ETHIP<2:0>  |        | ETHIS                | i<1:0> | 0000       |

Legend: x = unknown value on Reset; ---- = unimplemented, read as '0'. Reset values are shown in hexadecimal.

Except where noted, all registers in this table have corresponding CLR, SET and INV registers at their virtual addresses, plus offsets of 0x4, 0x8 and 0xC respectively. See Section 12.1.1 "CLR, SET and INV Note 1: Registers" for more information. These bits are not available on PIC32MX664 devices. This register does not have associated CLR, SET, and INV registers.

2:

3:

### TABLE 10-3: DMA CHANNELS 0-7 REGISTER MAP (CONTINUED)

| ess                         |                                 |               |                 |       |       |               |        |       |      | Bi     | ts       |        |        |        |         |        |        |         |            |

|-----------------------------|---------------------------------|---------------|-----------------|-------|-------|---------------|--------|-------|------|--------|----------|--------|--------|--------|---------|--------|--------|---------|------------|

| Virtual Address<br>(BF88_#) | Register<br>Name <sup>(1)</sup> | Bit Range     | 31/15           | 30/14 | 29/13 | 28/12         | 27/11  | 26/10 | 25/9 | 24/8   | 23/7     | 22/6   | 21/5   | 20/4   | 19/3    | 18/2   | 17/1   | 16/0    | All Resets |

| 3180                        | DCH1DSIZ                        | 31:16         | _               | -     | —     | _             | -      | -     | _    | —      | _        | _      | _      | —      | —       | _      | —      | _       | 0000       |

| 5100                        |                                 | 15:0          |                 |       |       | -             |        |       | -    | CHDSIZ | <15:0>   |        |        | -      | -       |        |        |         | 0000       |

| 3190                        | DCH1SPTR                        | 31:16         | —               | —     | —     | —             | —      | —     | _    | —      | —        | —      | —      | —      | —       | —      | —      | —       | 0000       |

| 5150                        | Donnor IIX                      | 15:0          |                 |       |       |               |        |       |      | CHSPTI | R<15:0>  |        |        |        |         |        |        |         | 0000       |

| 31A0                        | DCH1DPTR                        | 31:16         |                 |       |       |               |        |       |      |        |          |        |        |        | 0000    |        |        |         |            |

| 5170                        |                                 | 15:0          | CHDPTR<15:0> 00 |       |       |               |        |       |      |        |          |        |        |        | 0000    |        |        |         |            |

| 31B0                        | DCH1CSIZ                        | 31:16         | —               | —     | —     | —             | —      | —     | _    | —      | —        | —      | —      | —      | —       | —      | —      | —       | 0000       |

| 0100                        |                                 | 15:0          |                 |       |       |               |        |       |      | CHCSIZ | 2<15:0>  |        |        |        |         |        |        |         | 0000       |

| 31C0                        | DCH1CPTR                        | 31:16         | _               | —     | —     | _             | —      | —     | —    | —      | _        | —      | —      | —      | —       | —      | —      | —       | 0000       |

| 0100                        |                                 | 15:0          |                 |       |       |               |        |       |      | CHCPTI | R<15:0>  |        |        |        |         | -      | -      | -       | 0000       |

| 31D0                        | DCH1DAT                         | 31:16         | _               | _     | —     | _             | _      | _     | _    | —      | —        | —      | —      | —      | _       | —      | —      | —       | 0000       |

| 0120                        | Bonnbra                         | 15:0          | _               | _     | —     | _             | _      | _     | _    | —      |          |        |        | CHPDA  | \T<7:0> | -      | -      | -       | 0000       |

| 31E0                        | DCH2CON                         | 31:16         | —               | —     | —     | —             | —      | —     |      | —      | —        | —      | —      | —      | —       | —      | —      | —       | 0000       |

| 0120                        | DONZOON                         | 15:0          | CHBUSY          | _     | —     | —             | _      | _     |      | CHCHNS | CHEN     | CHAED  | CHCHN  | CHAEN  | _       | CHEDET | CHPR   | :l<1:0> | 0000       |

| 31E0                        | DCH2ECON                        | 31:16         | —               | —     | —     | —             | —      | —     | _    | —      |          | -      |        | CHAIR  |         |        |        |         | OOFF       |

| 511.0                       | DONZEOON                        | 15:0          |                 |       |       | CHSIR         | Q<7:0> |       |      |        | CFORCE   | CABORT | PATEN  | SIRQEN | AIRQEN  | —      | —      | —       | FF00       |

| 3200                        | DCH2INT                         | 31:16         | _               | _     | —     | —             | _      | _     |      | —      | CHSDIE   | CHSHIE | CHDDIE | CHDHIE | CHBCIE  | CHCCIE | CHTAIE | CHERIE  | 0000       |

| 5200                        | DONZINI                         | 15:0          | —               | —     | —     | —             | —      | —     | _    | —      | CHSDIF   | CHSHIF | CHDDIF | CHDHIF | CHBCIF  | CHCCIF | CHTAIF | CHERIF  | 0000       |

| 3210                        | DCH2SSA                         | 31:16<br>15:0 |                 |       |       |               |        |       |      | CHSSA  | <31:0>   |        |        |        |         |        |        |         | 0000       |

| 3220                        | DCH2DSA                         | 31:16<br>15:0 |                 |       |       |               |        |       |      | CHDSA  | <31:0>   |        |        |        |         |        |        |         | 0000       |

|                             |                                 | 31:16         |                 | _     | _     | _             | _      | _     | _    |        | _        | _      | _      | _      |         |        | _      |         | 0000       |

| 3230                        | DCH2SSIZ                        | 15:0          |                 |       |       |               |        |       |      | CHSSIZ |          |        |        |        |         |        |        |         | 0000       |

|                             |                                 | 31:16         | _               | _     | _     | _             | _      | _     | _    | _      | _        | _      | _      | _      |         | _      | _      | _       | 0000       |

| 3240                        | DCH2DSIZ                        | 15:0          |                 |       |       |               |        |       |      | CHDSIZ |          |        |        |        |         |        |        |         | 0000       |

|                             |                                 | 31:16         | _               | _     | _     | _             | _      | _     | _    | _      | _        | _      | _      | _      | _       | _      | _      | _       | 0000       |

| 3250                        | DCH2SPTR                        | 15:0          |                 |       |       |               |        |       |      | CHSPTI |          |        |        |        |         |        |        |         | 0000       |

| <u> </u>                    |                                 | 31:16         | _               | _     | _     | _             | _      | _     | _    | _      |          | _      | _      | _      |         |        | _      |         | 0000       |

| 3260                        | DCH2DPTR                        | 15:0          |                 |       |       |               |        |       |      | CHDPTI | 8<15.0>  |        |        |        |         |        |        |         | 0000       |

|                             |                                 | 31:16         | _               |       |       |               |        |       | _    |        |          | _      |        | _      | _       |        | _      | _       | 0000       |

| 3270                        | DCH2CSIZ                        | 15:0          |                 |       |       |               |        |       |      | CHCSIZ |          |        |        |        |         |        |        |         | 0000       |

|                             |                                 |               |                 |       |       |               |        |       |      | 010312 | .< 10.02 |        |        |        |         |        |        |         |            |

| 3280                        | DCH2CPTR                        | 31:16         | _               | _     | —     | —             | _      | _     | _    | —      | _        | —      | —      | —      | —       | _      | _      | _       | 0000       |

|                             |                                 | 15:0          |                 |       |       | n, tead as ,0 |        |       |      | CHCPTI | ۲<15:0>  |        |        |        |         |        |        |         | 0000       |

Legend: x = unknown value on Reset; - = unimplemented, read as '0'. Reset values are shown in hexadecimal.

Note 1: All registers in this table have corresponding CLR, SET and INV registers at their virtual addresses, plus offsets of 0x4, 0x8 and 0xC, respectively. See Section 12.1.1 "CLR, SET and INV Registers" for more information.

2: DMA channels 4-7 are not available on PIC32MX534/564/664/764 devices.

|           |                   |                   | -                 |                   |                   |                   |                  |                  |  |  |  |

|-----------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|--|--|--|

| Bit Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |  |  |

| 04-04     | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |  |

| 31:24     |                   | CHSSA<31:24>      |                   |                   |                   |                   |                  |                  |  |  |  |

| 00.40     | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |  |

| 23:16     | CHSSA<23:16>      |                   |                   |                   |                   |                   |                  |                  |  |  |  |

| 45.0      | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |  |

| 15:8      |                   |                   |                   | CHSSA<            | <15:8>            |                   |                  |                  |  |  |  |

| 7.0       | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |  |

| 7:0       |                   |                   |                   | CHSSA             | <7:0>             |                   |                  |                  |  |  |  |

## REGISTER 10-10: DCHxSSA: DMA CHANNEL 'x' SOURCE START ADDRESS REGISTER

| Legend:           |                  |                        |                    |

|-------------------|------------------|------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, | read as '0'        |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared   | x = Bit is unknown |

bit 31-0 CHSSA<31:0> Channel Source Start Address bits Channel source start address. Note: This must be the physical address of the source.

## REGISTER 10-11: DCHxDSA: DMA CHANNEL 'x' DESTINATION START ADDRESS REGISTER

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6                                     | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |  |  |

|--------------|-------------------|-------------------------------------------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|--|--|--|

| 04.04        | R/W-0             | R/W-0                                                 | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |  |

| 31:24        |                   | CHDSA<31:24>                                          |                   |                   |                   |                   |                  |                  |  |  |  |

| 00.40        | R/W-0             | R/W-0                                                 | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |  |

| 23:16        | CHDSA<23:16>      |                                                       |                   |                   |                   |                   |                  |                  |  |  |  |

| 45.0         | R/W-0             | R/W-0                                                 | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |  |

| 15:8         |                   |                                                       |                   | CHDSA.            | <15:8>            |                   |                  |                  |  |  |  |

| 7.0          | R/W-0             | R/W-0                                                 | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |  |

| 7:0          |                   | R/W-0 R/W-0 R/W-0 R/W-0 R/W-0 R/W-0 R/W-0 R/W-0 R/W-0 |                   |                   |                   |                   |                  |                  |  |  |  |

| Legend:           |                  |                           |                    |

|-------------------|------------------|---------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, re | ead as '0'         |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared      | x = Bit is unknown |

bit 31-0 CHDSA<31:0>: Channel Destination Start Address bits Channel destination start address.

Note: This must be the physical address of the destination.

NOTES:

### REGISTER 22-2: RTCALRM: RTC ALARM CONTROL REGISTER (CONTINUED)

- bit 7-0 ARPT<7:0>: Alarm Repeat Counter Value bits<sup>(2)</sup>

11111111 = Alarm will trigger 256 times

...

...

...

...

...

...

...

...

...

...

...

...

...

...

...

...

...

...

...

...

...

...

...

...

...

...

...

...

...

...

...

...

...

...

...

...

...

...

...

...

...

...

...

...

...

...

...

...

...

...

...

...

...

...

...

...

...

...

...

...

...

...

...

...

...

...

...

...

...

...

...

...

...

...

...

...

...

...

...

...

...

...

...

...

...

...

...

...

...

...

...

...

...

...

...

...

...

...

...

...

...

...

...

...

...

...

...

...

...

...

...

...

...

...

...

...

...

...

...

...

...

...

...

...

...

...

...

...

...

...

...

...

...

...

...

...

...

...

...

...

...

...

...

...

...

...

...

...

<li

- 3: This assumes a CPU read will execute in less than 32 PBCLKs.

Note: This register is only reset on a Power-on Reset (POR).

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |  |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|--|--|

| 04.04        | R/W-x             | R/W-x             | R/W-x             | R/W-x             | R/W-x             | R/W-x             | R/W-x            | R/W-x            |  |  |

| 31:24        |                   | HR10-             | <3:0>             |                   | HR01              | <3:0>             |                  |                  |  |  |

| 00.40        | R/W-x             | R/W-x             | R/W-x             | R/W-x             | R/W-x             | R/W-x             | R/W-x            | R/W-x            |  |  |

| 23:16        |                   | MIN10             | <3:0>             |                   | MIN01<3:0>        |                   |                  |                  |  |  |

| 45-0         | R/W-x             | R/W-x             | R/W-x             | R/W-x             | R/W-x             | R/W-x             | R/W-x            | R/W-x            |  |  |

| 15:8         |                   | SEC10             | <3:0>             |                   | SEC01<3:0>        |                   |                  |                  |  |  |

| 7.0          | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |  |  |

| 7:0          | —                 | —                 | —                 | —                 | —                 | —                 | —                | —                |  |  |

|              |                   |                   |                   |                   |                   |                   |                  |                  |  |  |

| Legend:      |                   |                   |                   |                   |                   |                   |                  |                  |  |  |

| R = Read     | able bit          |                   | W = Writable      | e bit             | U = Unimple       | emented bit, re   | ead as '0'       |                  |  |  |

|              |                   |                   |                   |                   |                   |                   |                  |                  |  |  |

#### REGISTER 22-3: RTCTIME: RTC TIME VALUE REGISTER

| IX – IXeauable bit            |                            |                                | it, read as 0      |

|-------------------------------|----------------------------|--------------------------------|--------------------|

| -n = Value at POR             | '1' = Bit is set           | '0' = Bit is cleared           | x = Bit is unknown |

|                               |                            |                                |                    |

| bit 31-28 HR10<3:0>: Binary-0 | Coded Decimal Value of Hou | rs bits, 10 digits; contains a | value from 0 to 2  |

bit 31-28 HR10<3:0>: Binary-Coded Decimal Value of Hours bits, 10 digits, contains a value from 0 to 2

bit 27-24 HR01<3:0>: Binary-Coded Decimal Value of Hours bits, 1 digit; contains a value from 0 to 9

bit 23-20 MIN10<3:0>: Binary-Coded Decimal Value of Minutes bits, 10 digits; contains a value from 0 to 5

bit 19-16 MIN01<3:0>: Binary-Coded Decimal Value of Minutes bits, 1 digit; contains a value from 0 to 9

bit 15-12 SEC10<3:0>: Binary-Coded Decimal Value of Seconds bits, 10 digits; contains a value from 0 to 5

bit 11-8 SEC01<3:0>: Binary-Coded Decimal Value of Seconds bits, 1 digit; contains a value from 0 to 9

bit 17-0 Unimplemented: Read as '0'

**Note:** This register is only writable when RTCWREN = 1 (RTCCON<3>).

### REGISTER 24-3: CIINT: CAN INTERRUPT REGISTER (CONTINUED)

- bit 14 WAKIF: CAN Bus Activity Wake-up Interrupt Flag bit 1 = A bus wake-up activity interrupt has occurred 0 = A bus wake-up activity interrupt has not occurred CERRIF: CAN Bus Error Interrupt Flag bit bit 13 1 = A CAN bus error has occurred 0 = A CAN bus error has not occurred bit 12 SERRIF: System Error Interrupt Flag bit 1 = A system error occurred (typically an illegal address was presented to the system bus) 0 = A system error has not occurred bit 11 **RBOVIF:** Receive Buffer Overflow Interrupt Flag bit 1 = A receive buffer overflow has occurred 0 = A receive buffer overflow has not occurred bit 10-4 Unimplemented: Read as '0' MODIF: CAN Mode Change Interrupt Flag bit bit 3 1 = A CAN module mode change has occurred (OPMOD<2:0> has changed to reflect REQOP) 0 = A CAN module mode change has not occurred bit 2 CTMRIF: CAN Timer Overflow Interrupt Flag bit 1 = A CAN timer (CANTMR) overflow has occurred 0 = A CAN timer (CANTMR) overflow has not occurred bit 1 **RBIF:** Receive Buffer Interrupt Flag bit 1 = A receive buffer interrupt is pending 0 = A receive buffer interrupt is not pending bit 0 TBIF: Transmit Buffer Interrupt Flag bit 1 = A transmit buffer interrupt is pending

- 1 = A transmit buffer interrupt is pending

0 = A transmit buffer interrupt is not pending

- **Note 1:** This bit can only be cleared by turning the CAN module Off and On by clearing or setting the ON bit (CiCON<15>).

### REGISTER 24-14: CIFLTCON4: CAN FILTER CONTROL REGISTER 4 (CONTINUED)

|           | (                                                           |

|-----------|-------------------------------------------------------------|

| bit 15    | FLTEN17: Filter 13 Enable bit                               |

|           | 1 = Filter is enabled                                       |

|           | 0 = Filter is disabled                                      |

| bit 14-13 | MSEL17<1:0>: Filter 17 Mask Select bits                     |

|           | 11 = Acceptance Mask 3 selected                             |

|           | 10 = Acceptance Mask 2 selected                             |

|           | 01 = Acceptance Mask 1 selected                             |

|           | 00 = Acceptance Mask 0 selected                             |

| bit 12-8  | FSEL17<4:0>: FIFO Selection bits                            |

|           | 11111 = Message matching filter is stored in FIFO buffer 31 |

|           | 11110 = Message matching filter is stored in FIFO buffer 30 |

|           | •                                                           |

|           |                                                             |

|           | 00001 = Message matching filter is stored in FIFO buffer 1  |

|           | 00000 = Message matching filter is stored in FIFO buffer 0  |

| bit 7     | FLTEN16: Filter 16 Enable bit                               |

|           | 1 = Filter is enabled                                       |

|           | 0 = Filter is disabled                                      |

| bit 6-5   | MSEL16<1:0>: Filter 16 Mask Select bits                     |

|           | 11 = Acceptance Mask 3 selected                             |

|           | 10 = Acceptance Mask 2 selected                             |

|           | 01 = Acceptance Mask 1 selected                             |

|           | 00 = Acceptance Mask 0 selected                             |

| bit 4-0   | FSEL16<4:0>: FIFO Selection bits                            |

|           | 11111 = Message matching filter is stored in FIFO buffer 31 |

|           | 11110 = Message matching filter is stored in FIFO buffer 30 |

|           | •                                                           |

|           | •                                                           |

|           | 00001 = Message matching filter is stored in FIFO buffer 1  |

|           | 00000 = Message matching filter is stored in FIFO buffer 0  |

| r         |                                                             |

Note: The bits in this register can only be modified if the corresponding filter enable (FLTENn) bit is '0'.

### REGISTER 24-15: CIFLTCON5: CAN FILTER CONTROL REGISTER 5 (CONTINUED)

|           | · · · · · · · · · · · · · · · · · · ·                              |  |

|-----------|--------------------------------------------------------------------|--|

| bit 15    | FLTEN21: Filter 21 Enable bit                                      |  |

|           | 1 = Filter is enabled                                              |  |

|           | 0 = Filter is disabled                                             |  |

| bit 14-13 | MSEL21<1:0>: Filter 21 Mask Select bits                            |  |

|           | 11 = Acceptance Mask 3 selected                                    |  |

|           | 10 = Acceptance Mask 2 selected                                    |  |

|           | 01 = Acceptance Mask 1 selected                                    |  |

|           | 00 = Acceptance Mask 0 selected                                    |  |

| bit 12-8  | FSEL21<4:0>: FIFO Selection bits                                   |  |

|           | 11111 = Message matching filter is stored in FIFO buffer 31        |  |

|           | 11110 = Message matching filter is stored in FIFO buffer 30        |  |

|           |                                                                    |  |

|           | •                                                                  |  |

|           | 00001 = Message matching filter is stored in FIFO buffer 1         |  |

|           | 00000 = Message matching filter is stored in FIFO buffer 0         |  |

| bit 7     | FLTEN20: Filter 20 Enable bit                                      |  |

|           | 1 = Filter is enabled                                              |  |

|           | 0 = Filter is disabled                                             |  |

| bit 6-5   | MSEL20<1:0>: Filter 20 Mask Select bits                            |  |

|           | 11 = Acceptance Mask 3 selected                                    |  |

|           | 10 = Acceptance Mask 2 selected                                    |  |

|           | 01 = Acceptance Mask 1 selected<br>00 = Acceptance Mask 0 selected |  |

| h:+ 4 0   | •                                                                  |  |

| bit 4-0   | FSEL20<4:0>: FIFO Selection bits                                   |  |

|           | 11111 = Message matching filter is stored in FIFO buffer 31        |  |

|           | 11110 = Message matching filter is stored in FIFO buffer 30        |  |

|           |                                                                    |  |

|           | •                                                                  |  |

|           | 00001 = Message matching filter is stored in FIFO buffer 1         |  |

|           | 00000 = Message matching filter is stored in FIFO buffer 0         |  |

|           |                                                                    |  |

Note: The bits in this register can only be modified if the corresponding filter enable (FLTENn) bit is '0'.

|              |                   |                   |                   |                   |                   | •                 |                    | ,                  |  |  |  |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|--------------------|--------------------|--|--|--|

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1   | Bit<br>24/16/8/0   |  |  |  |

| 31:24        | R-x                | R-x                |  |  |  |

| 31.24        |                   |                   |                   | CiFIFOUA          | n<31:24>          |                   |                    | •                  |  |  |  |

| 23:16        | R-x                | R-x                |  |  |  |

| 23.10        | CiFIFOUAn<23:16>  |                   |                   |                   |                   |                   |                    |                    |  |  |  |

| 45.0         | R-x                | R-x                |  |  |  |

| 15:8         | CiFIFOUAn<15:8>   |                   |                   |                   |                   |                   |                    |                    |  |  |  |

| 7.0          | R-x               | R-x               | R-x               | R-x               | R-x               | R-x               | R-0 <sup>(1)</sup> | R-0 <sup>(1)</sup> |  |  |  |

| 7:0          |                   | •                 |                   | CiFIFOU           | IAn<7:0>          |                   |                    |                    |  |  |  |

#### REGISTER 24-22: CiFIFOUAn: CAN FIFO USER ADDRESS REGISTER 'n' (n = 0 THROUGH 31)

#### Legend:

| 3                 |                  |                        |                                    |  |  |  |

|-------------------|------------------|------------------------|------------------------------------|--|--|--|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, | U = Unimplemented bit, read as '0' |  |  |  |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared   | x = Bit is unknown                 |  |  |  |

bit 31-0 CiFIFOUAn<31:0>: CAN FIFO User Address bits

TXEN = 1: (FIFO configured as a transmit buffer)

A read of this register will return the address where the next message is to be written (FIFO head).

TXEN = 0: (FIFO configured as a receive buffer)

A read of this register will return the address where the next message is to be read (FIFO tail).

**Note 1:** This bit will always read '0', which forces byte-alignment of messages.

**Note:** This register is not guaranteed to read correctly in Configuration mode, and should only be accessed when the module is not in Configuration mode.

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |  |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|--|--|

| 31:24        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |  |  |

| 31.24        | —                 | —                 | —                 | —                 | —                 | —                 | —                | —                |  |  |

| 23:16        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |  |  |

| 23.10        | _                 | _                 | _                 | _                 | _                 | —                 |                  | —                |  |  |

| 15:8         | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |  |  |

| 15.0         | —                 | —                 | —                 | —                 | —                 | —                 | —                | —                |  |  |

| 7.0          | U-0               | U-0               | U-0               | R-0               | R-0               | R-0               | R-0              | R-0              |  |  |

| 7:0          | _                 | _                 | _                 |                   | (                 | CiFIFOCI<4:0:     | >                |                  |  |  |

#### **REGISTER 24-23:** CiFIFOCIN: CAN MODULE MESSAGE INDEX REGISTER 'n' (n = 0 THROUGH 31)

#### Legend:

| 0                 |                  |                          |                    |

|-------------------|------------------|--------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, r | ead as '0'         |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared     | x = Bit is unknown |

bit 31-5 Unimplemented: Read as '0'

bit 4-0 CiFIFOCIn<4:0>: CAN Side FIFO Message Index bits

TXEN = 1: (FIFO configured as a transmit buffer)

A read of this register will return an index to the message that the FIFO will next attempt to transmit.

TXEN = 0: (FIFO configured as a receive buffer)

A read of this register will return an index to the message that the FIFO will use to save the next message.

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|--|

| 24.24        | r-1               | r-1               | r-1               | r-1               | r-1               | r-1               | r-1              | r-1              |  |

| 31:24        | —                 | _                 | —                 | —                 | —                 | _                 | _                | —                |  |

| 23:16        | R/P               | r-1               | r-1               | R/P               | R/P               | R/P               | R/P              | R/P              |  |

|              | FWDTEN            | —                 | —                 | WDTPS<4:0>        |                   |                   |                  |                  |  |

| 45.0         | R/P               | R/P               | R/P               | R/P               | r-1               | R/P               | R/P              | R/P              |  |

| 15:8         | FCKSM             | 1<1:0>            | FPBDI             | V<1:0>            | —                 | OSCIOFNC          | POSCM            | OD<1:0>          |  |

| 7:0          | R/P               | r-1               | R/P               | r-1               | r-1               | R/P               | R/P              | R/P              |  |

|              | IESO              |                   | FSOSCEN           | _                 | —                 | F                 | NOSC<2:0>        |                  |  |

#### REGISTER 29-2: DEVCFG1: DEVICE CONFIGURATION WORD 1

| Legend: r = Reserved bit |                  | P = Programmable bit               |                    |  |

|--------------------------|------------------|------------------------------------|--------------------|--|

| R = Readable bit         | W = Writable bit | U = Unimplemented bit, read as '0' |                    |  |

| -n = Value at POR        | '1' = Bit is set | '0' = Bit is cleared               | x = Bit is unknown |  |

bit 31-24 Reserved: Write '1'

bit 23 FWDTEN: Watchdog Timer Enable bit

1 = The WDT is enabled and cannot be disabled by software 0 = The WDT is not enabled; it can be enabled in software

- bit 22-21 Reserved: Write '1'

- bit 20-16 WDTPS<4:0>: Watchdog Timer Postscale Select bits

10100 = 1:1048576 10011 = 1:524288 10010 = 1:262144 10001 = 1:131072 10000 = 1:65536 01111 = 1:32768 01110 = 1:16384 01101 = 1:8192 01100 = 1:4096 01011 = 1:204801010 = 1:1024 01001 = 1:51201000 = 1:256 00111 = 1:128 00110 = 1:6400101 = 1:32 00100 = 1:1600011 = 1:800010 = 1:4 00001 = 1:2 00000 = 1:1

All other combinations not shown result in operation = 10100

bit 15-14 FCKSM<1:0>: Clock Switching and Monitor Selection Configuration bits

1x = Clock switching is disabled, Fail-Safe Clock Monitor is disabled

01 = Clock switching is enabled, Fail-Safe Clock Monitor is disabled

00 = Clock switching is enabled, Fail-Safe Clock Monitor is enabled

**Note 1:** Do not disable the Posc (POSCMOD = 11) when using this oscillator source.

| Bit<br>Range | Bit<br>31/23/15/7           | Bit<br>30/22/14/6 | Bit<br>29/21/13/5  | Bit<br>28/20/12/4 | Bit<br>27/19/11/3   | Bit<br>26/18/10/2 | Bit<br>25/17/9/1      | Bit<br>24/16/8/0 |  |  |  |

|--------------|-----------------------------|-------------------|--------------------|-------------------|---------------------|-------------------|-----------------------|------------------|--|--|--|

| 04-04        | R                           | R                 | R                  | R                 | R                   | R                 | R                     | R                |  |  |  |

| 31:24        |                             | VER<3             | :0> <sup>(1)</sup> |                   |                     | DEVID<2           | 27:24> <sup>(1)</sup> |                  |  |  |  |

| 00.40        | R                           | R                 | R                  | R                 | R                   | R                 | R                     | R                |  |  |  |

| 23:16        | DEVID<23:16> <sup>(1)</sup> |                   |                    |                   |                     |                   |                       |                  |  |  |  |

| 45.0         | R                           | R                 | R                  | R                 | R                   | R                 | R                     | R                |  |  |  |

| 15:8         |                             |                   |                    | DEVID<1           | 5:8> <sup>(1)</sup> |                   |                       |                  |  |  |  |

| 7.0          | R                           | R                 | R                  | R                 | R                   | R                 | R                     | R                |  |  |  |

| 7:0          |                             |                   |                    | DEVID<            | 7:0> <sup>(1)</sup> |                   |                       |                  |  |  |  |

#### REGISTER 29-5: DEVID: DEVICE AND REVISION ID REGISTER

# Legend:

| Legena.           |                  |                          |                    |

|-------------------|------------------|--------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, r | ead as '0'         |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared     | x = Bit is unknown |

bit 31-28 VER<3:0>: Revision Identifier bits<sup>(1)</sup>

bit 27-0 DEVID<27:0>: Device ID bits<sup>(1)</sup>

Note 1: See the "PIC32 Flash Programming Specification" (DS60001145) for a list of Revision and Device ID values.

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|

| 21.24        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 31:24        |                   | _                 |                   |                   |                   |                   | _                | —                |

| 00.40        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 23:16        | _                 | _                 | _                 | _                 | _                 | _                 | _                | —                |

| 45.0         | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 15:8         | _                 | _                 | _                 | _                 | _                 | _                 | _                | —                |

| 7.0          | U-0               | U-0               | U-0               | U-0               | R/W-1             | R/W-0             | U-0              | R/W-0            |

| 7:0          | _                 | _                 | _                 | _                 | JTAGEN            | TROEN             |                  | TDOEN            |

### REGISTER 29-6: DDPCON: DEBUG DATA PORT CONTROL REGISTER

| Legend:           |                  |                      |                    |

|-------------------|------------------|----------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bi | it, read as '0'    |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared | x = Bit is unknown |

#### bit 31-4 Unimplemented: Read as '0'

- bit 3 JTAGEN: JTAG Port Enable bit

- 1 = Enable the JTAG port

- 0 = Disable the JTAG port

- bit 2 **TROEN:** Trace Output Enable bit

- 1 = Enable the trace port

- 0 = Disable the trace port

- bit 1 Unimplemented: Read as '0'

- bit 0 TDOEN: TDO Enable for 2-Wire JTAG

- 1 = 2-wire JTAG protocol uses TDO

- 0 = 2-wire JTAG protocol does not use TDO

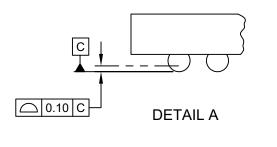

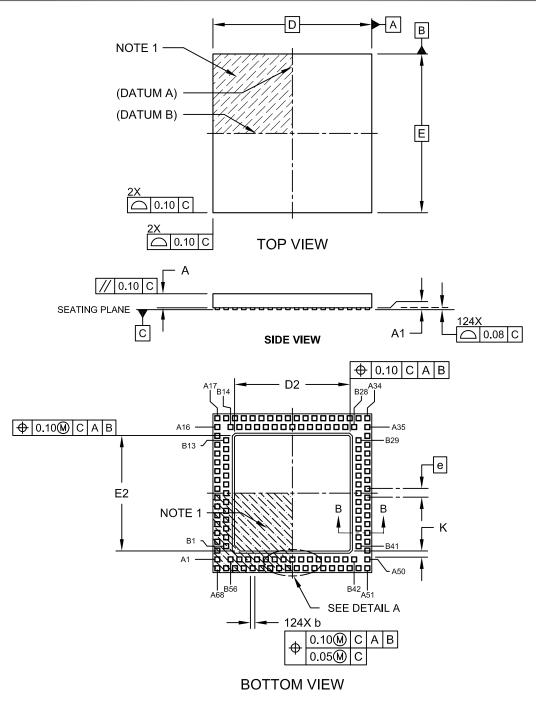

# 121-Ball Plastic Thin Profile Fine Pitch Ball Grid Array (BG) - 10x10x1.10 mm Body [TFBGA]

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

DETAIL B

|                    | Units    | Ν    | ILLIMETER: | S    |

|--------------------|----------|------|------------|------|

| Dimension          | l Limits | MIN  | NOM        | MAX  |

| Number of Contacts | N        |      | 121        |      |

| Contact Pitch      | е        |      | 0.80 BSC   |      |

| Overall Height     | Α        | 1.00 | 1.10       | 1.20 |

| Ball Height        | A1       | 0.25 | 0.30       | 0.35 |

| Overall Width      | E        |      | 10.00 BSC  |      |

| Array Width        | E1       |      | 8.00 BSC   |      |

| Overall Length     | D        |      | 10.00 BSC  |      |

| Array Length       | D1       |      | 8.00 BSC   |      |

| Contact Diameter   | b        | 0.35 | 0.40       | 0.45 |

Notes:

- 1. Ball A1 visual index feature may vary, but must be located within the hatched area.

- 2. Dimensioning and tolerancing per ASME Y14.5M.

- BSC: Basic Dimension. Theoretically exact value shown without tolerances. REF: Reference Dimension, usually without tolerance, for information purposes only.

- 3. The outer rows and colums of balls are located with respect to datums A and B.

- 4. Ball interface to package body: 0.37mm nominal diameter.

Microchip Technology Drawing C04-148 Rev F Sheet 2 of 2

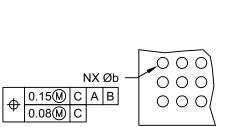

# 124-Terminal Very Thin Leadless Array Package (TL) – 9x9x0.9 mm Body [VTLA]

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

Microchip Technology Drawing C04-193A Sheet 1 of 2

# Revision G (May 2011)

The revision includes the following global updates:

- All references to VDDCORE/VCAP have been changed to: VCORE/VCAP

- Added references to the new V-Temp temperature range: -40°C to +105°C

# TABLE B-5: MAJOR SECTION UPDATES

This revision also includes minor typographical and formatting changes throughout the data sheet text. Major updates are referenced by their respective section in Table B-5.

| Section Name                                                             | Update Description                                                                                                                                                                                           |

|--------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| High-Performance, USB, CAN and<br>Ethernet 32-bit Flash Microcontrollers | Removed the shading for all D- and D+ pins in all pin diagrams.                                                                                                                                              |

| 1.0 "Device Overview"                                                    | Updated the VBUS description in Table 1-1.                                                                                                                                                                   |

| 1.0 "Guidelines for Getting Started with<br>32-bit Microcontrollers"     | Added "Alternatively, inputs can be reserved by connecting the pin<br>to Vss through a 1k to 10k resistor and configuring the pin as an<br>input.".                                                          |

| 4.0 "Memory Organization"                                                | Added Note 3 to the Interrupt Register Map tables (see Table 4-2 through Table 4-7.                                                                                                                          |

| 22.0 "10-bit Analog-to-Digital Converter (ADC)"                          | Updated the ADC Conversion Clock Period Block Diagram (see Figure 22-2).                                                                                                                                     |

| 1.0 "Comparator Voltage Reference (CVREF)"                               | Updated the Comparator Voltage Reference Block Diagram (see Figure 1-1).                                                                                                                                     |

| 1.0 "Special Features"                                                   | Removed the second paragraph from <b>1.3.1</b> " <b>On-Chip Regulator and POR</b> ".                                                                                                                         |

| 1.0 "Electrical Characteristics"                                         | Added the new V-Temp temperature range (-40°C to +105°C) to the heading of all specification tables.                                                                                                         |

|                                                                          | Updated the Ambient temperature under bias, updated the Voltage on<br>any 5V tolerant pin with respect to Vss when VDD < 2.3V, and added<br>Voltage on VBUS with respect to Vss in Absolute Maximum Ratings. |

|                                                                          | Added the characteristic, DC5a to Operating MIPS vs. Voltage (see Table 1-1).                                                                                                                                |

|                                                                          | Updated or added the following parameters to the Operating Current (IDD) DC Characteristics: DC20, DC20b, DC23, and DC23b (see Table 1-5).                                                                   |

|                                                                          | Added the following parameters to the Idle Current (IIDLE) DC<br>Characteristics: DC30b, DC33b, DC34c, DC35c, and DC36c (see<br>Table 1-6).                                                                  |

|                                                                          | Added the following parameters to the Power-down Current (IPD) DC Characteristics: DC40g, DC40h, DC40i, and DC41g, (see Table 1-7).                                                                          |

|                                                                          | Added parameter IM51 and Note 3 to the I2Cx Bus Data Timing Requirements (Master Mode) (see Table 1-32).                                                                                                     |

|                                                                          | Updated the 10-bit ADC Conversion Rate Parameters (see Table 1-37).                                                                                                                                          |

|                                                                          | Updated parameter AD57 (TSAMP) in the Analog-to-Digital Conversion Timing Requirements (see Table 1-38).                                                                                                     |

| 1.0 "Packaging Information"                                              | Updated the 64-Lead Plastic Quad Flat, No Lead Package (MR) –<br>9x9x0.9 mm Body [QFN] packing diagram.                                                                                                      |

| Product Identification System                                            | Added the new V-Temp (V) temperature information.                                                                                                                                                            |

| Oscillator Configuration                | 95  |

|-----------------------------------------|-----|

| Output Compare                          | 185 |

| Ρ                                       |     |

| Packaging                               | 401 |

| Details                                 |     |

| Marking                                 | 401 |

| Parallel Master Port (PMP)              | 211 |

| PIC32 Family USB Interface Diagram      | 134 |

| PICkit 3 In-Circuit Debugger/Programmer |     |

| Pinout I/O Descriptions (table)         | 26  |

| Power-on Reset (POR)                    |     |

| and On-Chip Voltage Regulator           | 343 |

| Power-Saving Features                   | 331 |

| CPU Halted Methods                      | 331 |

| Operation                               | 331 |

| with CPU Running                        | 331 |

| Prefetch Cache                          | 101 |

| Program Flash Memory                    |     |

| Wait State Characteristics              | 363 |

# R

| Real-Time Clock and Calendar (RTCC)                  | . 221 |

|------------------------------------------------------|-------|

| Register Maps                                        | -283  |

| Registers                                            |       |

| AD1CHS (ADC Input Select)                            | . 239 |

| AD1CON1 (ADC Control 1)                              | . 235 |

| AD1CON2 (ADC Control 2)                              |       |

| AD1CON3 (ADC Control 3)                              |       |

| AD1CSSL (ADC Input Scan Select)                      | . 240 |

| ALRMDATE (Alarm Date Value)                          | . 230 |

| ALRMTIME (Alarm Time Value)                          | . 229 |

| BMXBOOTSZ (Boot Flash (IFM) Size)                    | 61    |

| BMXCON (Bus Matrix Configuration)                    | 56    |

| BMXDKPBA (Data RAM Kernel Program                    |       |

| Base Address)                                        | 57    |

| BMXDRMSZ (Data RAM Size)                             | 60    |

| BMXDUDBA (Data RAM User Data Base Address)           | 58    |

| BMXDUPBA (Data RAM User Program                      |       |

| Base Address)                                        | 59    |

| BMXPFMSZ (Program Flash (PFM) Size)                  | 61    |

| BMXPUPBA (Program Flash (PFM) User Program           |       |

| Base Address)                                        | 60    |

| CHEACC (Cache Access)                                | . 104 |

| CHECON (Cache Control)                               | . 103 |

| CHEHIT (Cache Hit Statistics)                        | . 109 |

| CHELRU (Cache LRU)                                   | . 108 |

| CHEMIS (Cache Miss Statistics)                       | . 109 |

| CHEMSK (Cache TAG Mask)                              | . 106 |

| CHETAG (Cache TAG)                                   | . 105 |

| CHEW0 (Cache Word 0)                                 | . 106 |

| CHEW1 (Cache Word 1)                                 | . 107 |

| CHEW2 (Cache Word 2)                                 | . 107 |

| CHEW3 (Cache Word 3)                                 |       |

| CiCFG (CAN Baud Rate Configuration)                  | . 248 |

| CiCON (CAN Module Control)                           | .246  |

| CiFIFOBA (CAN Message Buffer Base Address)           | . 273 |

| CiFIFOCINn (CAN Module Message Index Register<br>278 | ʻ'n') |

| CiFIFOCONn (CAN FIFO Control Register 'n')           | .274  |

| CiFIFOINTn (CAN FIFO Interrupt Register 'n')         |       |

| CiFIFOUAn (CAN FIFO User Address Register 'n').      |       |

| CiFLTCON0 (CAN Filter Control 0)                     |       |

| CiFLTCON1 (CAN Filter Control 1)                     |       |

| CiFLTCON2 (CAN Filter Control 2)                     |       |

| CiFLTCON3 (CAN Filter Control 3)                     |       |

|                                                      |       |

| CiFLTCON4 (CAN Filter Control 4)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |