Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

## Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFI

| Product Status             | Active                                                                          |

|----------------------------|---------------------------------------------------------------------------------|

| Core Processor             | MIPS32® M4K™                                                                    |

| Core Size                  | 32-Bit Single-Core                                                              |

| Speed                      | 80MHz                                                                           |

| Connectivity               | CANbus, Ethernet, I <sup>2</sup> C, SPI, UART/USART, USB OTG                    |

| Peripherals                | Brown-out Detect/Reset, DMA, POR, PWM, WDT                                      |

| Number of I/O              | 53                                                                              |

| Program Memory Size        | 128KB (128K x 8)                                                                |

| Program Memory Type        | FLASH                                                                           |

| EEPROM Size                | -                                                                               |

| RAM Size                   | 32K x 8                                                                         |

| Voltage - Supply (Vcc/Vdd) | 2.3V ~ 3.6V                                                                     |

| Data Converters            | A/D 16x10b                                                                      |

| Oscillator Type            | Internal                                                                        |

| Operating Temperature      | -40°C ~ 105°C (TA)                                                              |

| Mounting Type              | Surface Mount                                                                   |

| Package / Case             | 64-TQFP                                                                         |

| Supplier Device Package    | 64-TQFP (10x10)                                                                 |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic32mx764f128ht-v-pt |

|                            |                                                                                 |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# PIC32MX5XX/6XX/7XX

## TABLE 1:PIC32MX5XX USB AND CAN FEATURES

|                  |      |                         |                  |     | U    | SB and                 | I CAN                                    |                       |                    |                                 |                              |             |         |      |       |                         |

|------------------|------|-------------------------|------------------|-----|------|------------------------|------------------------------------------|-----------------------|--------------------|---------------------------------|------------------------------|-------------|---------|------|-------|-------------------------|

| Device           | Pins | Program Memory (KB)     | Data Memory (KB) | USB | CAN  | Timers/Capture/Compare | DMA Channels<br>(Programmable/Dedicated) | UART <sup>(2,3)</sup> | Spl <sup>(3)</sup> | I <sup>2</sup> C <sup>(3)</sup> | 10-bit 1 Msps ADC (Channels) | Comparators | dSd/dWd | JTAG | Trace | Packages <sup>(4)</sup> |

| PIC32MX534F064H  | 64   | 64 + 12 <sup>(1)</sup>  | 16               | 1   | 1    | 5/5/5                  | 4/4                                      | 6                     | 3                  | 4                               | 16                           | 2           | Yes     | Yes  | No    | PT,<br>MR               |

| PIC32MX564F064H  | 64   | 64 + 12 <sup>(1)</sup>  | 32               | 1   | 1    | 5/5/5                  | 4/4                                      | 6                     | 3                  | 4                               | 16                           | 2           | Yes     | Yes  | No    | PT,<br>MR               |

| PIC32MX564F128H  | 64   | 128 + 12 <sup>(1)</sup> | 32               | 1   | 1    | 5/5/5                  | 4/4                                      | 6                     | 3                  | 4                               | 16                           | 2           | Yes     | Yes  | No    | PT,<br>MR               |

| PIC32MX575F256H  | 64   | 256 + 12 <sup>(1)</sup> | 64               | 1   | 1    | 5/5/5                  | 8/4                                      | 6                     | 3                  | 4                               | 16                           | 2           | Yes     | Yes  | No    | PT,<br>MR               |

| PIC32MX575F512H  | 64   | 512 + 12 <sup>(1)</sup> | 64               | 1   | 1    | 5/5/5                  | 8/4                                      | 6                     | 3                  | 4                               | 16                           | 2           | Yes     | Yes  | No    | PT,<br>MR               |

| PIC32MX534F064L  | 100  | 64 + 12 <sup>(1)</sup>  | 16               | 1   | 1    | 5/5/5                  | 4/4                                      | 6                     | 4                  | 5                               | 16                           | 2           | Yes     | Yes  | Yes   | PT,<br>PF,<br>BG        |

| PIC32MX564F064L  | 100  | 64 + 12 <sup>(1)</sup>  | 32               | 1   | 1    | 5/5/5                  | 4/4                                      | 6                     | 4                  | 5                               | 16                           | 2           | Yes     | Yes  | Yes   | PT,<br>PF,<br>BG        |

| PIC32MX564F128L  | 100  | 128 + 12 <sup>(1)</sup> | 32               | 1   | 1    | 5/5/5                  | 4/4                                      | 6                     | 4                  | 5                               | 16                           | 2           | Yes     | Yes  | Yes   | PT,<br>PF,<br>BG        |

| PIC32MX575F256L  | 100  | 256 + 12 <sup>(1)</sup> | 64               | 1   | 1    | 5/5/5                  | 8/4                                      | 6                     | 4                  | 5                               | 16                           | 2           | Yes     | Yes  | Yes   | PT,<br>PF,<br>BG        |

| PIC32MX575F512L  | 100  | 512 + 12 <b>(1)</b>     | 64               | 1   | 1    | 5/5/5                  | 8/4                                      | 6                     | 4                  | 5                               | 16                           | 2           | Yes     | Yes  | Yes   | PT,<br>PF,<br>BG        |

| Legend: PF, PT = | TQFP | MR = Q                  | FN               |     | BG = | TFBG/                  | 4                                        | TL =                  | VTLA               | (5)                             |                              |             |         |      |       |                         |

Note 1: This device features 12 KB boot Flash memory.

2: CTS and RTS pins may not be available for all UART modules. Refer to the "Device Pin Tables" section for more information.

**3:** Some pins between the UART, SPI and I<sup>2</sup>C modules may be shared. Refer to the "**Device Pin Tables**" section for more information.

4: Refer to 34.0 "Packaging Information" for more information.

5: 100-pin devices in the VTLA package are available upon request. Please contact your local Microchip Sales Office for details.

1

## TABLE 8: PIN NAMES FOR 100-PIN USB AND ETHERNET DEVICES (CONTINUED)

## **100-PIN TQFP (TOP VIEW)**

PIC32MX664F064L PIC32MX664F128L PIC32MX675F256L PIC32MX675F512L PIC32MX695F512L

100

| Pin # | Full Pin Name                   | Pin # | Full Pin Name   |

|-------|---------------------------------|-------|-----------------|

| 71    | EMDC/AEMDC/IC4/PMCS1/PMA14/RD11 | 86    | VDD             |

| 72    | SDO1/OC1/INT0/RD0               | 87    | ETXD1/PMD11/RF0 |

| 73    | SOSCI/CN1/RC13                  | 88    | ETXD0/PMD10/RF1 |

| 74    | SOSCO/T1CK/CN0/RC14             | 89    | ETXERR/PMD9/RG1 |

| 75    | Vss                             | 90    | PMD8/RG0        |

| 76    | OC2/RD1                         | 91    | TRCLK/RA6       |

| 77    | OC3/RD2                         | 92    | TRD3/RA7        |

| 78    | OC4/RD3                         | 93    | PMD0/RE0        |

| 79    | ETXD2/IC5/PMD12/RD12            | 94    | PMD1/RE1        |

| 80    | ETXD3/PMD13/CN19/RD13           | 95    | TRD2/RG14       |

| 81    | OC5/PMWR/CN13/RD4               | 96    | TRD1/RG12       |

| 82    | PMRD/CN14/RD5                   | 97    | TRD0/RG13       |

| 83    | ETXEN/PMD14/CN15/RD6            | 98    | PMD2/RE2        |

| 84    | ETXCLK/PMD15/CN16/RD7           | 99    | PMD3/RE3        |

| 85    | VCAP/VDDCORE                    | 100   | PMD4/RE4        |

Note 1: Shaded pins are 5V tolerant.

## 2.9 Configuration of Analog and Digital Pins During ICSP Operations

If MPLAB ICD 3 or REAL ICE is selected as a debugger, it automatically initializes all of the Analog-to-Digital input pins (ANx) as "digital" pins by setting all bits in the AD1PCFG register.

The bits in this register that correspond to the Analogto-Digital pins that are initialized by MPLAB ICD 3 or REAL ICE, must not be cleared by the user application firmware; otherwise, communication errors will result between the debugger and the device.

If your application needs to use certain ADC pins as analog input pins during the debug session, the user application must clear the corresponding bits in the AD1PCFG register during initialization of the ADC module.

When MPLAB ICD 3 or REAL ICE is used as a programmer, the user application firmware must correctly configure the AD1PCFG register. Automatic initialization of this register is only done during debugger operation. Failure to correctly configure the register(s) will result in all ADC pins being recognized as analog input pins, resulting in the port value being read as a logic '0', which may affect user application functionality.

## 2.10 Unused I/Os

Unused I/O pins should not be allowed to float as inputs. They can be configured as outputs and driven to a logic-low state.

Alternatively, inputs can be reserved by connecting the pin to Vss through a 1k to 10k resistor and configuring the pin as an input.

## 2.11 EMI/EMC/EFT (IEC 61000-4-4 and IEC 61000-4-2) Suppression Considerations

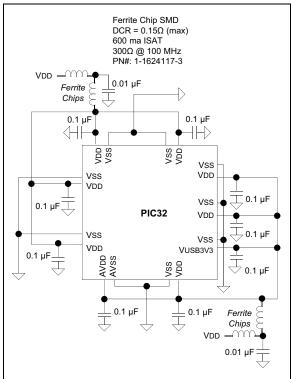

The use of LDO regulators is preferred to reduce overall system noise and provide a cleaner power source. However, when utilizing switching Buck/ Boost regulators as the local power source for PIC32 devices, as well as in electrically noisy environments or test conditions required for IEC 61000-4-4 and IEC 61000-4-2, users should evaluate the use of T-Filters (i.e., L-C-L) on the power pins, as shown in Figure 2-4. In addition to a more stable power source, use of this type of T-Filter can greatly reduce susceptibility to EMI sources and events.

## FIGURE 2-4: EMI/EMC/EFT SUPPRESSION CIRCUIT

#### 5.1 **Control Registers**

## FLASH CONTROLLER REGISTER MAP

| ess                         |                        |           |                       |                                              |       |       |       |       |      | Bi      | ts       |      |      |      |      |      |      |      |            |

|-----------------------------|------------------------|-----------|-----------------------|----------------------------------------------|-------|-------|-------|-------|------|---------|----------|------|------|------|------|------|------|------|------------|

| Virtual Address<br>(BF80_#) | Register<br>Name       | Bit Range | 31/15                 | 30/14                                        | 29/13 | 28/12 | 27/11 | 26/10 | 25/9 | 24/8    | 23/7     | 22/6 | 21/5 | 20/4 | 19/3 | 18/2 | 17/1 | 16/0 | All Resets |

| E400                        | NVMCON <sup>(1)</sup>  | 31:16     | _                     | _                                            |       | _     | _     |       | —    |         |          |      | —    | _    |      | —    | —    | —    | 0000       |

| F400                        | INVIVICOIN**           | 15:0      | WR                    | WR WREN WRERR LVDERR LVDSTAT NVMOP<3:0> 0000 |       |       |       |       |      |         |          |      |      |      |      |      |      |      |            |

| F410                        | NVMKEY                 | 31:16     |                       |                                              |       |       |       |       |      | NVMKE   | V~31·0>  |      |      |      |      |      |      |      | 0000       |

| 1410                        |                        | 15:0      |                       |                                              |       |       |       |       |      |         | 1<31.02  |      |      |      |      |      |      |      | 0000       |

| E420                        | NVMADDR <sup>(1)</sup> | 31:16     |                       |                                              |       |       |       |       |      | NVMADE  | P-31.0>  |      |      |      |      |      |      |      | 0000       |

| 1 420                       |                        | 15:0      |                       |                                              |       |       |       |       |      | NVINADL | //<31.02 |      |      |      |      |      |      |      | 0000       |

| E420                        | NVMDATA                | 31:16     |                       |                                              |       |       |       |       |      |         | A -21.0  |      |      |      |      |      |      |      | 0000       |

| F430                        | INVIVIDATA             | 15:0      |                       | NVMDATA<31:0>                                |       |       |       |       |      |         |          |      |      |      |      |      |      |      |            |

| F440                        |                        | 31:16     |                       | NVMSRCADDR<31:0>                             |       |       |       |       |      |         |          |      |      |      |      |      |      |      |            |

| F440                        | ADDR                   | 15:0      | NVMSRCADDR<51.0> 0000 |                                              |       |       |       |       |      |         |          |      |      |      |      |      |      |      |            |

PIC32MX5XX/6XX/7XX

x = unknown value on Reset; ---- = unimplemented, read as '0'. Reset values are shown in hexadecimal. Legend:

This register has corresponding CLR, SET and INV registers at their virtual addresses, plus offsets of 0x4, 0x8 and 0xC, respectively. See Section 12.1.1 "CLR, SET and INV Registers" for more information. Note 1:

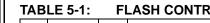

## 6.0 RESETS

Note: This data sheet summarizes the features of the PIC32MX5XX/6XX/7XX family of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to **Section 7.** "**Resets**" (DS60001118) in the "*PIC32 Family Reference Manual*", which is available from the Microchip web site (www.microchip.com/PIC32).

The Reset module combines all Reset sources and controls the device Master Reset signal, SYSRST. The following is a list of device Reset sources:

- Power-on Reset (POR)

- Master Clear Reset pin (MCLR)

- Software Reset (SWR)

- Watchdog Timer Reset (WDTR)

- Brown-out Reset (BOR)

- Configuration Mismatch Reset (CMR)

A simplified block diagram of the Reset module is illustrated in Figure 6-1.

## FIGURE 6-1: SYSTEM RESET BLOCK DIAGRAM

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1   | Bit<br>24/16/8/0   |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|--------------------|--------------------|

| 31:24        | U-0                | U-0                |

| 31.24        |                   | _                 | -                 | —                 | _                 | —                 |                    | —                  |

| 23:16        | U-0                | U-0                |

| 23.10        | _                 | _                 | _                 | —                 | _                 | —                 |                    | —                  |

| 45.0         | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | R/W-0, HS          | R/W-0              |

| 15:8         | —                 | _                 | —                 | —                 | _                 | —                 | CMR                | VREGS              |

| 7.0          | R/W-0, HS         | R/W-0, HS         | U-0               | R/W-0, HS         | R/W-0, HS         | R/W-0, HS         | R/W-1, HS          | R/W-1, HS          |

| 7:0          | EXTR              | SWR               | _                 | WDTO              | SLEEP             | IDLE              | BOR <sup>(1)</sup> | POR <sup>(1)</sup> |

#### REGISTER 6-1: RCON: RESET CONTROL REGISTER

| Legend:           | HS = Set by hardware |                           |                    |

|-------------------|----------------------|---------------------------|--------------------|

| R = Readable bit  | W = Writable bit     | U = Unimplemented bit, re | ad as '0'          |

| -n = Value at POR | '1' = Bit is set     | '0' = Bit is cleared      | x = Bit is unknown |

| bit 31-10 | Unimplemented: Read as '0 | n' |

|-----------|---------------------------|----|

|           | eninplemented. Read as    |    |

| bit 9 | CMR: Configuration Mismatch Reset Flag bit                                   |

|-------|------------------------------------------------------------------------------|

|       | 1 = Configuration mismatch Reset has occurred                                |

|       | 0 = Configuration mismatch Reset has not occurred                            |

| bit 8 | VREGS: Voltage Regulator Standby Enable bit                                  |

|       | $\ensuremath{\mathtt{l}}$ = Regulator is enabled and is on during Sleep mode |

|       | 0 = Regulator is set to Stand-by Tracking mode                               |

| bit 7 | EXTR: External Reset (MCLR) Pin Flag bit                                     |

|       | 1 = Master Clear (pin) Reset has occurred                                    |

|       | 0 = Master Clear (pin) Reset has not occurred                                |

| bit 6 | SWR: Software Reset Flag bit                                                 |

|       | 1 = Software Reset was executed                                              |

|       | 0 = Software Reset was not executed                                          |

| bit 5 | Unimplemented: Read as '0'                                                   |

| bit 4 | WDTO: Watchdog Timer Time-out Flag bit                                       |

|       | 1 = WDT Time-out has occurred                                                |

|       | 0 = WDT Time-out has not occurred                                            |

| bit 3 | SLEEP: Wake From Sleep Flag bit                                              |

|       | 1 = Device was in Sleep mode                                                 |

|       | 0 = Device was not in Sleep mode                                             |

| bit 2 | IDLE: Wake From Idle Flag bit                                                |

|       | 1 = Device was in Idle mode                                                  |

|       | 0 = Device was not in Idle mode                                              |

| bit 1 | BOR: Brown-out Reset Flag bit <sup>(1)</sup>                                 |

|       | 1 = Brown-out Reset has occurred                                             |

|       | 0 = Brown-out Reset has not occurred                                         |

| bit 0 | <b>POR:</b> Power-on Reset Flag bit <sup>(1)</sup>                           |

|       | 1 = Power-on Reset has occurred                                              |

|       | 0 = Power-on Reset has not occurred                                          |

|       |                                                                              |

Note 1: User software must clear this bit to view the next detection.

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0     |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|----------------------|

| 24.24        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0                  |

| 31:24        | —                 | _                 | _                 | —                 | _                 | _                 | -                | —                    |

| 22.16        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0                  |

| 23:16        | -                 | _                 | _                 | —                 | _                 | _                 | _                | —                    |

| 45.0         | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0                  |

| 15:8         | _                 | _                 | _                 | —                 | _                 | _                 | _                | —                    |

| 7.0          | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | W-0, HC              |

| 7:0          |                   | _                 | _                 | —                 | —                 |                   |                  | SWRST <sup>(1)</sup> |

## REGISTER 6-2: RSWRST: SOFTWARE RESET REGISTER

| Le   | gend:          | HC = Cleared by hardwar | e                         |                    |

|------|----------------|-------------------------|---------------------------|--------------------|

| R =  | = Readable bit | W = Writable bit        | U = Unimplemented bit, re | ead as '0'         |

| -n : | = Value at POR | '1' = Bit is set        | '0' = Bit is cleared      | x = Bit is unknown |

bit 31-1 Unimplemented: Read as '0'

- bit 0 SWRST: Software Reset Trigger bit<sup>(1)</sup> 1 = Enable software Reset event 0 = No effect

- Note 1: The system unlock sequence must be performed before the SWRST bit can be written. Refer to Section 6. "Oscillator" (DS60001112) in the "PIC32 Family Reference Manual" for details.

# TABLE 7-5: INTERRUPT REGISTER MAP FOR PIC32MX534F064L, PIC32MX564F064L, PIC32MX564F128L PIC32MX575F512L AND PIC32MX575F256L DEVICES (CONTINUED)

| ess                         |                                 | â         |       |       |       |             |                            |             |             | В                    | its         |             |             |             |             |            |        |                       |            |       |            |       |            |        |      |        |      |

|-----------------------------|---------------------------------|-----------|-------|-------|-------|-------------|----------------------------|-------------|-------------|----------------------|-------------|-------------|-------------|-------------|-------------|------------|--------|-----------------------|------------|-------|------------|-------|------------|--------|------|--------|------|

| Virtual Address<br>(BF88_#) | Register<br>Name <sup>(1)</sup> | Bit Range | 31/15 | 30/14 | 29/13 | 28/12       | 27/11                      | 26/10       | 25/9        | 24/8                 | 23/7        | 22/6        | 21/5        | 20/4        | 19/3        | 18/2       | 17/1   | 16/0                  | All Resets |       |            |       |            |        |      |        |      |

| 10D0                        | IPC4                            | 31:16     | —     | _     | —     | INT4IP<2:0> |                            | INT4IP<2:0> |             | INT4IP<2:0>          |             | INT4IP<2:0> |             | INT4IP<2:0> |             | S<1:0>     |        | —                     | —          |       | OC4IP<2:0> |       | OC4I       | S<1:0> | 0000 |        |      |

| 1000                        | IFC4                            | 15:0      | -     |       | _     |             | IC4IP<2:0>                 |             | IC4IS       | <1:0>                |             | _           | _           |             | T4IP<2:0>   |            | T4IS   | <1:0>                 | 0000       |       |            |       |            |        |      |        |      |

| 4050                        | IDOF                            | 31:16     | Ι     | _     | -     |             | SPI1IP<2:0>                | <b>&gt;</b> | SPI1IS      | S<1:0>               | _           | _           | -           |             | OC5IP<2:0>  |            | OC5I   | S<1:0>                | 0000       |       |            |       |            |        |      |        |      |

| 10E0                        | IPC5                            | 15:0      | _     | _     | _     |             | IC5IP<2:0>                 |             | IC5IS       | <1:0>                |             | _           | _           |             | T5IP<2:0>   |            | T5IS   | <1:0>                 | 0000       |       |            |       |            |        |      |        |      |

|                             |                                 | 31:16     | _     | _     | _     |             | AD1IP<2:0>                 |             | AD1IS       | <1:0>                |             | _           | _           |             | CNIP<2:0>   |            | CNIS   | <1:0>                 | 0000       |       |            |       |            |        |      |        |      |

| 10F0                        | IPC6                            |           |       |       |       |             |                            |             |             |                      |             |             |             |             | U1IP<2:0>   |            | U1IS   | <1:0>                 |            |       |            |       |            |        |      |        |      |

| 10F0                        | IPC6                            | 15:0      | _     | _     | _     | I2C1IP<2:0> |                            | I2C1IP<2:0> |             | S<1:0>               | _           | _           | —           |             | SPI3IP<2:0> |            | SPI3I  | S<1:0>                | 0000       |       |            |       |            |        |      |        |      |

|                             |                                 |           |       |       |       |             |                            |             |             |                      |             |             |             |             | I2C3IP<2:0> |            | 12C31  | S<1:0>                |            |       |            |       |            |        |      |        |      |

|                             |                                 |           |       |       |       |             | U3IP<2:0>                  |             | U3IS-       | <1:0>                |             |             |             |             |             |            |        |                       |            |       |            |       |            |        |      |        |      |

| 1100                        | IPC7                            | 31:16     | _     | —     | —     |             | SPI2IP<2:0>                | <b>`</b>    | SPI2IS<1:0> |                      | —           | —           | —           |             | CMP2IP<2:0  | >          | CMP2   | S<1:0>                | 0000       |       |            |       |            |        |      |        |      |

| 1100                        | 11 07                           |           |       |       |       |             | I2C4IP<2:0>                |             |             |                      | 12C415      | S<1:0>      |             |             |             |            |        |                       |            |       |            |       |            |        |      |        |      |

|                             |                                 | 15:0      | —     | —     | —     | CMP1IP<2:0> |                            | CMP1IP<2:0> |             | S<1:0>               | _           | _           | —           |             | PMPIP<2:0>  |            | PMPI   | S<1:0>                | 0000       |       |            |       |            |        |      |        |      |

|                             |                                 | 31:16     | —     | —     | —     | F           | RTCCIP<2:0>                |             | RTCCIP<2:0> |                      | RTCCIP<2:0> |             | RTCCIP<2:0> |             | RTCCIP<2:0> |            | RTCCI  | S<1:0>                | _          | _     | —          |       | FSCMIP<2:0 | >      | FSCM | S<1:0> | 0000 |

| 1110                        | IPC8                            |           |       |       |       |             |                            |             |             |                      |             |             |             |             |             |            |        |                       | U2IP<2:0>  |       | U2IS       | <1:0> |            |        |      |        |      |

| 1110                        | 11 00                           | 15:0      | -     | —     | -     |             | I2C2IP<2:0>                | •           | 12C215      | S<1:0>               | —           | —           | —           |             | SPI4IP<2:0> |            | SPI4I  | S<1:0>                | 0000       |       |            |       |            |        |      |        |      |

|                             |                                 |           |       |       |       |             |                            |             |             |                      |             |             |             |             | I2C5IP<2:0> |            | 12C51  | S<1:0>                |            |       |            |       |            |        |      |        |      |

| 1120                        | IPC9                            | 31:16     | -     |       | —     | [           | DMA3IP<2:0                 | >           | DMA3I       | S<1:0>               |             | —           | —           | DMA2IP<2:0> |             | DMA2       | S<1:0> | 0000                  |            |       |            |       |            |        |      |        |      |

| 1120                        | 11 00                           | 15:0      | —     | _     | —     |             | DMA1IP<2:0                 |             | DMA1        |                      |             |             | —           |             | DMA0IP<2:0  |            |        | S<1:0>                | 0000       |       |            |       |            |        |      |        |      |

| 1130                        | IPC10                           | 31:16     | —     | —     | —     |             | DMA7IP<2:0> <sup>(2)</sup> |             | DMA7IS      | <1:0> <sup>(2)</sup> | _           | _           | —           | D           | MA6IP<2:0>  | (2)        | DMA6IS | 6<1:0> <sup>(2)</sup> | 0000       |       |            |       |            |        |      |        |      |

| 1130                        | 1 010                           | 15:0      | _     | _     | —     | D           | DMA5IP<2:0> <sup>(2)</sup> |             | DMA5IS      | <1:0> <sup>(2)</sup> | _           | _           | —           | D           | MA4IP<2:0>  | (2)        | DMA4IS | S<1:0> <sup>(2)</sup> | 0000       |       |            |       |            |        |      |        |      |

| 1140                        | IPC11                           | 31:16     | Ι     |       | _     | _           |                            |             | _           | _                    | —           | —           | _           | CAN1IP<2:0> |             | CAN1       | S<1:0> | 0000                  |            |       |            |       |            |        |      |        |      |

| 1140                        | 1011                            | 15:0      | _     | _     | —     |             | USBIP<2:0>                 |             | USBIP<2:0>  |                      | USBIS       | 5<1:0>      | —           | —           | —           | FCEIP<2:0> |        | FCEIP<2:0>            |            | FCEIS | S<1:0>     | 0000  |            |        |      |        |      |

| 1150                        | IPC12                           | 31:16     | -     |       | _     |             | U5IP<2:0>                  |             | U5IS-       | <1:0>                | —           | —           | _           | U6IP<2:0>   |             | U6IP<2:0>  |        | U6IS                  | <1:0>      | 0000  |            |       |            |        |      |        |      |

| 1150                        | 11 012                          | 15:0      | -     |       | _     |             | U4IP<2:0>                  |             | U4IS-       | <1:0>                | _           | _           | _           | _           | —           |            | —      | _                     | 0000       |       |            |       |            |        |      |        |      |

PIC32MX5XX/6XX/7XX

Legend: x = unknown value on Reset; - = unimplemented, read as '0'. Reset values are shown in hexadecimal.

Note 1: Except where noted, all registers in this table have corresponding CLR, SET and INV registers at their virtual addresses, plus offsets of 0x4, 0x8 and 0xC, respectively. See Section 12.1.1 "CLR, SET and INV Registers" for more information.

2: These bits are not available on PIC32MX534/564 devices.

3: This register does not have associated CLR, SET, and INV registers.

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|

| 24.24        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 31:24        |                   |                   | _                 | —                 | -                 | _                 | _                | _                |

| 23:16        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | R/W-0            |

| 23.10        | —                 | —                 | —                 | —                 | _                 | —                 | —                | SS0              |

| 45.0         | U-0               | U-0               | U-0               | R/W-0             | U-0               | R/W-0             | R/W-0            | R/W-0            |

| 15:8         | _                 | —                 | —                 | MVEC              | _                 |                   | TPC<2:0>         |                  |

| 7.0          | U-0               | U-0               | U-0               | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |

| 7:0          |                   |                   | _                 | INT4EP            | INT3EP            | INT2EP            | INT1EP           | INT0EP           |

## REGISTER 7-1: INTCON: INTERRUPT CONTROL REGISTER

#### Legend:

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, re | ad as '0'          |

|-------------------|------------------|---------------------------|--------------------|

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared      | x = Bit is unknown |

#### bit 31-17 Unimplemented: Read as '0'

- bit 16 **SS0:** Single Vector Shadow Register Set bit

- 1 = Single vector is presented with a shadow register set

- 0 = Single vector is not presented with a shadow register set

- bit 15-13 Unimplemented: Read as '0'

- bit 12 MVEC: Multiple Vector Configuration bit

- 1 = Interrupt controller configured for Multi-vector mode

- 0 = Interrupt controller configured for Single-vector mode

- bit 11 Unimplemented: Read as '0'

- bit 10-8 TPC<2:0>: Interrupt Proximity Timer Control bits

- 111 = Interrupts of group priority 7 or lower start the Interrupt Proximity timer 110 = Interrupts of group priority 6 or lower start the Interrupt Proximity timer 101 = Interrupts of group priority 5 or lower start the Interrupt Proximity timer 100 = Interrupts of group priority 4 or lower start the Interrupt Proximity timer 011 = Interrupts of group priority 3 or lower start the Interrupt Proximity timer

- 010 = Interrupts of group priority 2 or lower start the Interrupt Proximity timer

- 001 = Interrupts of group priority 1 start the Interrupt Proximity timer

- 000 = Disables Interrupt Proximity timer

- bit 7-5 Unimplemented: Read as '0'

- bit 4 INT4EP: External Interrupt 4 Edge Polarity Control bit

- 1 = Rising edge

- 0 = Falling edge

- bit 3 INT3EP: External Interrupt 3 Edge Polarity Control bit

- 1 = Rising edge

- 0 = Falling edge

- bit 2 INT2EP: External Interrupt 2 Edge Polarity Control bit

- 1 = Rising edge

- 0 = Falling edge

- bit 1 **INT1EP:** External Interrupt 1 Edge Polarity Control bit

- 1 = Rising edge

- 0 = Falling edge

- bit 0 INTOEP: External Interrupt 0 Edge Polarity Control bit

- 1 = Rising edge

- 0 = Falling edge

## 8.1 Control Registers

## TABLE 8-1: OSCILLATOR REGISTER MAP

| ess                         |                                 | Ð         |       |       |           |            |       |       |           | В    | its     |         |          |       |       |        |            |       | (2)        |

|-----------------------------|---------------------------------|-----------|-------|-------|-----------|------------|-------|-------|-----------|------|---------|---------|----------|-------|-------|--------|------------|-------|------------|

| Virtual Address<br>(BF80_#) | Register<br>Name <sup>(1)</sup> | Bit Range | 31/15 | 30/14 | 29/13     | 28/12      | 27/11 | 26/10 | 25/9      | 24/8 | 23/7    | 22/6    | 21/5     | 20/4  | 19/3  | 18/2   | 17/1       | 16/0  | All Resets |

| E000                        | OSCCON                          | 31:16     | —     | _     | P         | LLODIV<2:0 | >     | F     | RCDIV<2:0 | >    | —       | SOSCRDY | _        | PBDIV | <1:0> | Р      | LLMULT<2:0 | >     | 0000       |

| FUUU                        | USCCON                          | 15:0      | _     |       | COSC<2:0> |            | _     |       | NOSC<2:0> |      | CLKLOCK | ULOCK   | SLOCK    | SLPEN | CF    | UFRCEN | SOSCEN     | OSWEN | 0000       |

| E010                        | OSCTUN                          | 31:16     | —     | _     | _         | —          | _     | _     |           | -    | —       | —       | _        | —     | —     | _      | _          | —     | 0000       |

| FUIU                        | USCIUN                          | 15:0      | _     |       | _         | _          | _     |       |           | _    | —       |         | TUN<5:0> |       |       |        |            | 0000  |            |

Legend: x = unknown value on Reset; — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

Note 1: All registers in this table have corresponding CLR, SET and INV registers at their virtual addresses, plus offsets of 0x4, 0x8 and 0xC, respectively. See Section 12.1.1 "CLR, SET and INV Registers" for more information.

2: Reset values are dependent on the DEVCFGx Configuration bits and the type of Reset.

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |  |  |  |  |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|--|--|--|--|--|

| 24.24        | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |  |  |  |

| 31:24        |                   |                   |                   | DCRCDAT/          | 4<31:24>          |                   |                  |                  |  |  |  |  |  |

| 23:16        | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |  |  |  |

| 23.10        | DCRCDATA<23:16>   |                   |                   |                   |                   |                   |                  |                  |  |  |  |  |  |

| 15.0         | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |  |  |  |

| 15:8         |                   |                   |                   | DCRCDAT           | A<15:8>           |                   |                  |                  |  |  |  |  |  |

| 7.0          | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |  |  |  |

| 7:0          |                   |                   | DCRCDATA<7:0>     |                   |                   |                   |                  |                  |  |  |  |  |  |

## REGISTER 10-5: DCRCDATA: DMA CRC DATA REGISTER

## Legend:

| Legend:           |                  |                           |                    |

|-------------------|------------------|---------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, re | ead as '0'         |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared      | x = Bit is unknown |

## bit 31-0 DCRCDATA<31:0>: CRC Data Register bits

Writing to this register will seed the CRC generator. Reading from this register will return the current value of the CRC. Bits greater than PLEN will return '0' on any read.

<u>When CRCTYP (DCRCCON<15>) = 1</u> (CRC module is in IP Header mode): Only the lower 16 bits contain IP header checksum information. The upper 16 bits are always '0'. Data written to this register is converted and read back in 1's complement form (current IP header checksum value).

<u>When CRCTYP (DCRCCON<15>) = 0</u> (CRC module is in LFSR mode): Bits greater than PLEN will return '0' on any read.

## REGISTER 10-6: DCRCXOR: DMA CRCXOR ENABLE REGISTER

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |  |  |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|--|--|--|

| 31:24        | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |  |

| 31.24        | DCRCXOR<31:24>    |                   |                   |                   |                   |                   |                  |                  |  |  |  |

| 00.40        | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |  |

| 23:16        | DCRCXOR<23:16>    |                   |                   |                   |                   |                   |                  |                  |  |  |  |

| 15.0         | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |  |

| 15:8         |                   |                   |                   | DCRCXO            | R<15:8>           |                   |                  |                  |  |  |  |

| 7.0          | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |  |

| 7:0          | DCRCXOR<7:0>      |                   |                   |                   |                   |                   |                  |                  |  |  |  |

| Legend:           |                  |                          |                    |

|-------------------|------------------|--------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, r | ead as '0'         |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared     | x = Bit is unknown |

## bit 31-0 DCRCXOR<31:0>: CRC XOR Register bits

<u>When CRCTYP (DCRCCON<15>) = 1</u> (CRC module is in IP Header mode): This register is unused.

<u>When CRCTYP (DCRCCON<15>) = 0</u> (CRC module is in LFSR mode):

## 1 = Enable the XOR input to the Shift register

0 = Disable the XOR input to the Shift register; data is shifted in directly from the previous stage in the register

## TABLE 11-1: USB REGISTER MAP (CONTINUED)

| ess                        |                                 | Bits      |       |       |       |       |       |       |      |      |      |      |      |          |        |        |         |        |            |

|----------------------------|---------------------------------|-----------|-------|-------|-------|-------|-------|-------|------|------|------|------|------|----------|--------|--------|---------|--------|------------|

| Virtual Addres<br>(BF88_#) | Register<br>Name <sup>(1)</sup> | Bit Range | 31/15 | 30/14 | 29/13 | 28/12 | 27/11 | 26/10 | 25/9 | 24/8 | 23/7 | 22/6 | 21/5 | 20/4     | 19/3   | 18/2   | 17/1    | 16/0   | All Resets |

| 53A0                       | U1EP10                          | 31:16     | _     | _     | _     | _     | _     | —     | _    | _    |      | _    | —    | —        | -      |        | _       | _      | 0000       |

| 55A0                       | UIEFIU                          | 15:0      | —     | —     | _     | _     | _     | —     | _    | _    | _    | —    | —    | EPCONDIS | EPRXEN | EPTXEN | EPSTALL | EPHSHK | 0000       |

| 53B0                       | U1EP11                          | 31:16     | -     | _     | _     |       |       | _     |      |      |      | _    | _    | —        |        |        | _       |        | 0000       |

| 5560                       | UIEFII                          | 15:0      | -     | _     | _     |       |       | _     |      |      |      | -    | _    | EPCONDIS | EPRXEN | EPTXEN | EPSTALL | EPHSHK | 0000       |

| 53C0                       | U1EP12                          | 31:16     | Ι     | _     |       | -     |       | _     |      |      | _    | —    | —    | _        | -      | -      | _       | -      | 0000       |

| 5300                       | UTEPTZ                          | 15:0      | Ι     | -     | _     | _     | _     | -     | _    | _    | —    | -    | _    | EPCONDIS | EPRXEN | EPTXEN | EPSTALL | EPHSHK | 0000       |

| 5000                       |                                 | 31:16     |       | _     | _     | —     | _     | -     | —    | —    | _    | -    | —    | —        | —      | _      | _       | _      | 0000       |

| 53D0                       | U1EP13                          | 15:0      | Ι     | -     | _     | _     | _     | -     | _    | _    | —    | -    | _    | EPCONDIS | EPRXEN | EPTXEN | EPSTALL | EPHSHK | 0000       |

|                            |                                 | 31:16     |       | _     | _     | _     | _     | _     | _    | _    | _    |      | _    | _        | _      | _      | _       | _      | 0000       |

| 53E0                       | U1EP14                          | 15:0      | _     | _     | _     | _     | _     | —     | _    | _    | _    | _    | —    | EPCONDIS | EPRXEN | EPTXEN | EPSTALL | EPHSHK | 0000       |

| 5050                       |                                 | 31:16     | _     | _     | _     |       | -     | _     | _    | _    | -    | _    | —    | _        |        |        | —       | -      | 0000       |

| 53F0                       | U1EP15                          | 15:0      | _     | —     | —     | -     |       | —     | -    | —    |      | _    | —    | EPCONDIS | EPRXEN | EPTXEN | EPSTALL | EPHSHK | 0000       |

Legend:

x = unknown value on Reset; — = unimplemented, read as '0'. Reset values are shown in hexadecimal. Note 1:

All registers in this table (except as noted) have corresponding CLR, SET and INV registers at its virtual address, plus an offset of 0x4, 0x8 and 0xC respectively. See Section 12.1.1 "CLR, SET and INV Registers" for more information.

This register does not have associated SET and INV registers. 2:

3: This register does not have associated CLR, SET and INV registers.

Reset value for this bit is undefined. 4:

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |  |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|--|--|

| 04.04        | U-0               | U-0               | U-0               | R-0               | R-0 R-0           |                   | R-0              | R-0              |  |  |

| 31:24        |                   | —                 | —                 |                   | R                 | 0>                |                  |                  |  |  |

| 00.40        | U-0               | U-0               | U-0               | R-0 R-0           |                   | R-0               | R-0              | R-0              |  |  |

| 23:16        | —                 | —                 | —                 | TXBUFELM<4:0>     |                   |                   |                  |                  |  |  |

| 45.0         | U-0               | U-0               | U-0               | U-0               | R-0               | U-0               | U-0              | R-0              |  |  |

| 15:8         | —                 | —                 | —                 | _                 | SPIBUSY           | _                 | _                | SPITUR           |  |  |

| 7.0          | R-0               | R/W-0             | R-0               | U-0               | R-1               | U-0               | R-0              | R-0              |  |  |

| 7:0          | SRMT              | SPIROV            | SPIRBE            |                   | SPITBE            |                   | SPITBF           | SPIRBF           |  |  |

## REGISTER 18-2: SPIxSTAT: SPI STATUS REGISTER

| Legend:           | C = Clearable bit | HS = Set in hardware |                    |

|-------------------|-------------------|----------------------|--------------------|

| R = Readable bit  | W = Writable bit  | U = Unimplemented bi | it, read as '0'    |

| -n = Value at POR | '1' = Bit is set  | '0' = Bit is cleared | x = Bit is unknown |

- bit 31-29 Unimplemented: Read as '0'

- bit 28-24 **RXBUFELM<4:0>:** Receive Buffer Element Count bits (only valid when ENHBUF = 1)

- bit 23-21 Unimplemented: Read as '0'

- bit 20-16 **TXBUFELM<4:0>:** Transmit Buffer Element Count bits (only valid when ENHBUF = 1)

- bit 15-12 Unimplemented: Read as '0'

- bit 11 **SPIBUSY:** SPI Activity Status bit 1 = SPI peripheral is currently busy with some transactions

- 0 = SPI peripheral is currently idle

- bit 10-9 **Unimplemented:** Read as '0'

- bit 8 SPITUR: Transmit Under Run bit

- $\ensuremath{\mathtt{l}}$  = Transmit buffer has encountered an underrun condition

- 0 = Transmit buffer has no underrun condition

This bit is only valid in Framed Sync mode; the underrun condition must be cleared by disabling/re-enabling the module.

- bit 7 **SRMT:** Shift Register Empty bit (only valid when ENHBUF = 1)

- 1 = When SPI module shift register is empty

- 0 = When SPI module shift register is not empty

- bit 6 **SPIROV:** Receive Overflow Flag bit

- 1 = A new data is completely received and discarded. The user software has not read the previous data in the SPIxBUF register.

- 0 = No overflow has occurred

- This bit is set in hardware; can only be cleared (= 0) in software.

- bit 5 SPIRBE: RX FIFO Empty bit (only valid when ENHBUF = 1) 1 = RX FIFO is empty (CRPTR = SWPTR) 0 = RX FIFO is not empty (CRPTR ≠ SWPTR)

- bit 4 Unimplemented: Read as '0'

- bit 3 SPITBE: SPI Transmit Buffer Empty Status bit

- 1 = Transmit buffer, SPIxTXB is empty

- 0 = Transmit buffer, SPIxTXB is not empty

- Automatically set in hardware when SPI transfers data from SPIxTXB to SPIxSR.

- Automatically cleared in hardware when SPIxBUF is written to, loading SPIxTXB.

- bit 2 Unimplemented: Read as '0'

| Bit<br>Range | Bit<br>31/23/15/7        | Bit<br>30/22/14/6    | Bit<br>29/21/13/5  | Bit<br>28/20/12/4       | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1     | Bit<br>24/16/8/0 |  |  |  |

|--------------|--------------------------|----------------------|--------------------|-------------------------|-------------------|-------------------|----------------------|------------------|--|--|--|

| 04.04        | U-0                      | U-0                  | U-0                | U-0                     | U-0               | U-0               | U-0                  | U-0              |  |  |  |

| 31:24        | _                        | —                    | —                  | —                       | _                 | —                 | _                    | —                |  |  |  |

| 23:16        | U-0                      | U-0                  | U-0                | U-0                     | U-0               | U-0               | U-0                  | U-0              |  |  |  |

| 23:16        | _                        |                      | —                  | —                       | —                 | _                 | _                    | —                |  |  |  |

| 45.0         | R/W-0                    | R/W-0                | R/W-0              | R-0                     | R/W-0             | R/W-0             | R/W-0                | R/W-0            |  |  |  |

| 15:8         | ALRMEN <sup>(1,2)</sup>  | CHIME <sup>(2)</sup> | PIV <sup>(2)</sup> | ALRMSYNC <sup>(3)</sup> |                   | AMASK             | <3:0> <sup>(2)</sup> |                  |  |  |  |

| 7.0          | R/W-0                    | R/W-0                | R/W-0              | R/W-0                   | R/W-0             | R/W-0             | R/W-0                | R/W-0            |  |  |  |

| 7:0          | ARPT<7:0> <sup>(2)</sup> |                      |                    |                         |                   |                   |                      |                  |  |  |  |

## REGISTER 22-2: RTCALRM: RTC ALARM CONTROL REGISTER

#### Legend:

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, | , read as '0'      |

|-------------------|------------------|------------------------|--------------------|

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared   | x = Bit is unknown |

#### bit 31-16 Unimplemented: Read as '0'

- bit 15 ALRMEN: Alarm Enable bit<sup>(1,2)</sup>

- 1 = Alarm is enabled

- 0 = Alarm is disabled

- bit 14 **CHIME:** Chime Enable bit<sup>(2)</sup>

- 1 = Chime is enabled ARPT<7:0> is allowed to rollover from 0x00 to 0xFF

- 0 = Chime is disabled ARPT<7:0> stops once it reaches 0x00

#### bit 13 **PIV:** Alarm Pulse Initial Value bit<sup>(3)</sup>

When ALRMEN = 0, PIV is writable and determines the initial value of the Alarm Pulse. When ALRMEN = 1, PIV is read-only and returns the state of the Alarm Pulse.

#### bit 12 ALRMSYNC: Alarm Sync bit<sup>(3)</sup>

- 1 = ARPT<7:0> and ALRMEN may change as a result of a half second rollover during a read.

The ARPT must be read repeatedly until the same value is read twice. This must be done since multiple bits may be changing, which are then synchronized to the PB clock domain.

- 0 = ARPT<7:0> and ALRMEN can be read without concerns of rollover because the prescaler is > 32 RTC clocks away from a half-second rollover

#### bit 11-8 AMASK<3:0>: Alarm Mask Configuration bits<sup>(2)</sup>

1111 = Reserved

- 1010 = Reserved

- 1001 = Once a year (except when configured for February 29, once every four years)

- 1000 = Once a month

- 0111 = Once a week

- 0110 = Once a day

- 0101 = Every hour

- 0100 = Every 10 minutes

- 0011 = Every minute

- 0010 = Every 10 seconds

- 0001 = Every second

- 0000 = Every half-second

- Note 1: Hardware clears the ALRMEN bit anytime the alarm event occurs, when ARPT<7:0 > = 0.0 and CHIME = 0.

- **2:** This field should not be written when the RTCC ON bit = '1' (RTCCON<15>) and ALRMSYNC = 1.

- 3: This assumes a CPU read will execute in less than 32 PBCLKs.

**Note:** This register is only reset on a Power-on Reset (POR).

| Bit Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0    |  |  |  |  |

|-----------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|---------------------|--|--|--|--|

| 24.24     | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0               |  |  |  |  |

| 31:24     | PTV<15:8>         |                   |                   |                   |                   |                   |                  |                     |  |  |  |  |

| 00.40     | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0               |  |  |  |  |

| 23:16     | PTV<7:0>          |                   |                   |                   |                   |                   |                  |                     |  |  |  |  |

| 45.0      | R/W-0             | U-0               | R/W-0             | U-0               | U-0               | U-0               | R/W-0            | R/W-0               |  |  |  |  |

| 15:8      | ON                | —                 | SIDL              | _                 | _                 | _                 | TXRTS            | RXEN <sup>(1)</sup> |  |  |  |  |

| 7:0       | R/W-0             | U-0               | U-0               | R/W-0             | U-0               | U-0               | U-0              | R/W-0               |  |  |  |  |

| 7:0       | AUTOFC            |                   | _                 | MANFC             | _                 |                   |                  | BUFCDEC             |  |  |  |  |

## REGISTER 25-1: ETHCON1: ETHERNET CONTROLLER CONTROL REGISTER 1

## Legend:

| Legenu.           |                  |                          |                    |

|-------------------|------------------|--------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, I | read as '0'        |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared     | x = Bit is unknown |

bit 31-16 PTV<15:0>: PAUSE Timer Value bits PAUSE Timer Value used for Flow Control. This register should only be written when RXEN (ETHCON1<8>) is not set. These bits are only used for Flow Control operations. bit 15 **ON:** Ethernet ON bit 1 = Ethernet module is enabled 0 = Ethernet module is disabled bit 14 Unimplemented: Read as '0' bit 13 SIDL: Ethernet Stop in Idle Mode bit 1 = Ethernet module transfers are paused during Idle mode 0 = Ethernet module transfers continue during Idle mode bit 12-10 Unimplemented: Read as '0' bit 9 TXRTS: Transmit Request to Send bit 1 = Activate the TX logic and send the packet(s) defined in the TX EDT 0 = Stop transmit (when cleared by software) or transmit done (when cleared by hardware)

After the bit is written with a '1', it will clear to a '0' whenever the transmit logic has finished transmitting the requested packets in the Ethernet Descriptor Table (EDT). If a '0' is written by the CPU, the transmit logic finishes the current packet's transmission and then stops any further.

This bit only affects TX operations.

## bit 8 **RXEN:** Receive Enable bit<sup>(1)</sup>

- 1 = Enable RX logic, packets are received and stored in the RX buffer as controlled by the filter configuration

- 0 = Disable RX logic, no packets are received in the RX buffer

This bit only affects RX operations.

**Note 1:** It is not recommended to clear the RXEN bit and then make changes to any RX related field/register. The Ethernet Controller must be reinitialized (ON cleared to '0'), and then the RX changes applied.

## REGISTER 25-18: ETHSCOLFRM: ETHERNET CONTROLLER SINGLE COLLISION FRAMES STATISTICS REGISTER

| Bit Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |  |  |  |  |  |  |  |  |

|-----------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|--|--|--|--|--|--|--|--|--|

| 31:24     | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |  |  |  |  |  |  |  |  |  |

| 31.24     | -                 | —                 | _                 | —                 | -                 | —                 | _                | —                |  |  |  |  |  |  |  |  |  |

| 22.46     | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |  |  |  |  |  |  |  |  |  |

| 23:16     | _                 | —                 | _                 | —                 | —                 | —                 | _                | —                |  |  |  |  |  |  |  |  |  |

| 15.0      | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |  |  |  |  |  |  |  |

| 15:8      | SCOLFRMCNT<15:8>  |                   |                   |                   |                   |                   |                  |                  |  |  |  |  |  |  |  |  |  |

| 7.0       | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |  |  |  |  |  |  |  |

| 7:0       |                   |                   |                   | SCOLFRM           | CNT<7:0>          |                   |                  | SCOLFRMCNT<7:0>  |  |  |  |  |  |  |  |  |  |

## Legend:

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read as '0'       |  |

|-------------------|------------------|------------------------------------------|--|

| -n = Value at POR | '1' = Bit is set | 0' = Bit is cleared $x = Bit is unknown$ |  |

## bit 31-16 Unimplemented: Read as '0'

bit 15-0 **SCOLFRMCNT<15:0>:** Single Collision Frame Count bits Increment count for frames that were successfully transmitted on the second try.

Note 1: This register is only used for TX operations.

2: This register is automatically cleared by hardware after a read operation, unless the byte enables for bytes 0/1 are '0'.

**3:** It is recommended to use the SET, CLR, or INV registers to set or clear any bit in this register. Setting or clearing any bits in this register should only be done for debug/test purposes.

| AC CHARACTERISTICS |               | $\begin{tabular}{lllllllllllllllllllllllllllllllllll$                                                            |             |                        |             |            |                                         |

|--------------------|---------------|------------------------------------------------------------------------------------------------------------------|-------------|------------------------|-------------|------------|-----------------------------------------|

| Param.<br>No.      | Symbol        | Characteristics                                                                                                  | Min.        | Typical <sup>(1)</sup> | Max.        | Units      | Conditions                              |

| OS10               | Fosc          | External CLKI Frequency<br>(External clocks only allowed<br>in EC and ECPLL modes)                               | DC<br>4     |                        | 50<br>50    | MHz<br>MHz | EC (Note 4)<br>ECPLL (Note 3)           |

| OS11               |               | Oscillator Crystal Frequency                                                                                     | 3           | —                      | 10          | MHz        | XT <b>(Note 4)</b>                      |

| OS12               |               |                                                                                                                  | 4           | —                      | 10          | MHz        | XTPLL<br>(Notes 3,4)                    |

| OS13               |               |                                                                                                                  | 10          | —                      | 25          | MHz        | HS (Note 4)                             |

| OS14               |               |                                                                                                                  | 10          | —                      | 25          | MHz        | HSPLL<br>(Notes 3,4)                    |

| OS15               |               |                                                                                                                  | 32          | 32.768                 | 100         | kHz        | Sosc (Note 4)                           |

| OS20               | Tosc          | Tosc = 1/Fosc = Tcy <sup>(2)</sup>                                                                               | _           | _                      | _           | —          | See parameter<br>OS10 for Fosc<br>value |

| OS30               | TosL,<br>TosH | External Clock In (OSC1)<br>High or Low Time                                                                     | 0.45 x Tosc | —                      | _           | ns         | EC (Note 4)                             |

| OS31               | TosR,<br>TosF | External Clock In (OSC1)<br>Rise or Fall Time                                                                    | —           | —                      | 0.05 x Tosc | ns         | EC (Note 4)                             |

| OS40               | Tost          | Oscillator Start-up Timer Period<br>(Only applies to HS, HSPLL,<br>XT, XTPLL and Sosc Clock<br>Oscillator modes) | _           | 1024                   | _           | Tosc       | (Note 4)                                |

| OS41               | TFSCM         | Primary Clock Fail Safe<br>Time-out Period                                                                       | _           | 2                      | _           | ms         | (Note 4)                                |

| OS42               | Gм            | External Oscillator<br>Transconductance (Primary<br>Oscillator only)                                             | _           | 12                     | _           | mA/V       | VDD = 3.3V,<br>TA = +25°C<br>(Note 4)   |

## TABLE 32-17: EXTERNAL CLOCK TIMING REQUIREMENTS

Note 1: Data in "Typical" column is at 3.3V, 25°C unless otherwise stated. Parameters are characterized but are not tested.

2: Instruction cycle period (TCY) equals the input oscillator time base period. All specified values are based on characterization data for that particular oscillator type under standard operating conditions with the device executing code. Exceeding these specified limits may result in an unstable oscillator operation and/or higher than expected current consumption. All devices are tested to operate at "min." values with an external clock applied to the OSC1/CLKI pin.

**3:** PLL input requirements: 4 MHz ≤ FPLLIN ≤ 5 MHz (use PLL prescaler to reduce Fosc). This parameter is characterized, but is only tested at 10 MHz at manufacturing.

4: This parameter is characterized, but not tested in manufacturing.

#### TABLE 32-20: INTERNAL RC ACCURACY

| AC CHA                          | RACTERISTICS    | (unless | $\begin{tabular}{lllllllllllllllllllllllllllllllllll$ |      |       |            |  |  |  |

|---------------------------------|-----------------|---------|-------------------------------------------------------|------|-------|------------|--|--|--|

| Param.<br>No.                   | Characteristics | Min.    | Typical                                               | Max. | Units | Conditions |  |  |  |

| LPRC @ 31.25 kHz <sup>(1)</sup> |                 |         |                                                       |      |       |            |  |  |  |

| F21                             | LPRC            | -15     | _                                                     | +15  | %     | —          |  |  |  |

**Note 1:** Change of LPRC frequency as VDD changes.

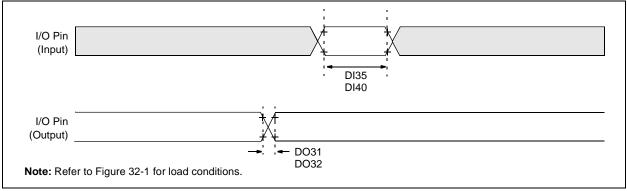

## FIGURE 32-3: I/O TIMING CHARACTERISTICS

## TABLE 32-21: I/O TIMING REQUIREMENTS

| AC CHARACTERISTICS |        | Standard Ope<br>(unless other<br>Operating tem | wise state                   |      | ≤ +85°C fc             | or Industria |         |            |

|--------------------|--------|------------------------------------------------|------------------------------|------|------------------------|--------------|---------|------------|

| Param.<br>No.      | Symbol | ol Characteristics <sup>(2)</sup>              |                              | Min. | Typical <sup>(1)</sup> | Max.         | Units   | Conditions |

| DO31               | TIOR   | Port Output Rise Time                          |                              | _    | 5                      | 15           | ns      | Vdd < 2.5V |

|                    |        |                                                |                              | —    | 5                      | 10           | ns      | Vdd > 2.5V |

| DO32               | TIOF   | Port Output Fall Time                          |                              | _    | 5                      | 15           | ns      | Vdd < 2.5V |

|                    |        |                                                |                              | —    | 5                      | 10           | ns      | VDD > 2.5V |

| DI35               | TINP   | INTx Pin High or Low Time                      |                              | 10   | _                      | _            | ns      | —          |

| DI40               | Trbp   | CNx High or Low Tir                            | CNx High or Low Time (input) |      | _                      | _            | TSYSCLK | _          |

**Note 1:** Data in "Typical" column is at 3.3V, 25°C unless otherwise stated.

2: This parameter is characterized, but not tested in manufacturing.

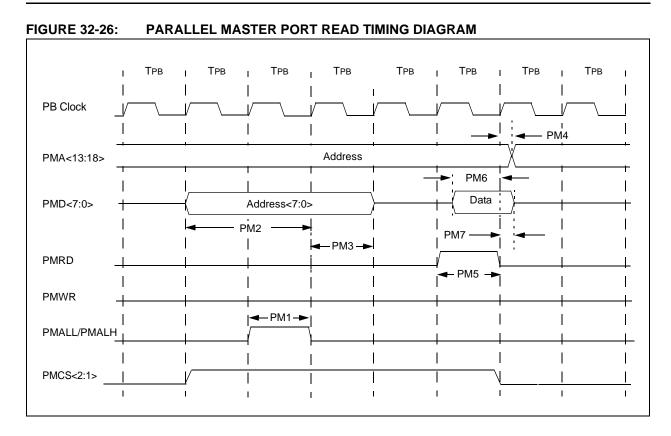

## TABLE 32-40: PARALLEL MASTER PORT READ TIMING REQUIREMENTS

| AC CHARACTERISTICS |         | (unless o                                                         | l Operating<br>otherwise signature<br>temperatur | <b>tated)</b><br><sup>.</sup> e -40°C | ≤ Ta ≤ +8 | t <b>o 3.6V</b><br>35°C for Industrial<br>105°C for V-Temp |            |

|--------------------|---------|-------------------------------------------------------------------|--------------------------------------------------|---------------------------------------|-----------|------------------------------------------------------------|------------|

| Param.<br>No.      | Symbol  | Characteristics <sup>(1)</sup>                                    | Min.                                             | Typical                               | Max.      | Units                                                      | Conditions |

| PM1                | TLAT    | PMALL/PMALH Pulse Width                                           | —                                                | 1 Трв                                 | —         | _                                                          | —          |

| PM2                | Tadsu   | Address Out Valid to PMALL/<br>PMALH Invalid (address setup time) | —                                                | 2 Трв                                 | —         | —                                                          | —          |

| PM3                | TADHOLD | PMALL/PMALH Invalid to Address<br>Out Invalid (address hold time) | —                                                | 1 Трв                                 | —         | —                                                          | —          |

| PM4                | TAHOLD  | PMRD Inactive to Address Out<br>Invalid<br>(address hold time)    | 5                                                | _                                     | _         | ns                                                         | —          |

| PM5                | Trd     | PMRD Pulse Width                                                  | —                                                | 1 Трв                                 | —         |                                                            | —          |

| PM6                | TDSU    | PMRD or PMENB Active to Data In Valid (data setup time)           | 15                                               | _                                     | _         | ns                                                         | _          |

| PM7                | TDHOLD  | PMRD or PMENB Inactive to Data<br>In Invalid (data hold time)     | 1 TPBCLK                                         | —                                     | —         | ns                                                         | PMP PBCLK  |

**Note 1:** These parameters are characterized, but not tested in manufacturing.

| TABLE B-3: | MAJOR SECTION UPDATES | (CONTINUED) |  |

|------------|-----------------------|-------------|--|

|            |                       |             |  |

| Section Name                     | Update Description                                                                                    |

|----------------------------------|-------------------------------------------------------------------------------------------------------|

| 1.0 "Electrical Characteristics" | Updated the Typical and Maximum DC Characteristics: Operating Current (IDD) in Table 1-5.             |

|                                  | Updated the Typical and Maximum DC Characteristics: Idle Current (IIDLE) in Table 1-6.                |