Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFI

| Product Status             | Active                                                                         |

|----------------------------|--------------------------------------------------------------------------------|

| Core Processor             | MIPS32® M4K™                                                                   |

| Core Size                  | 32-Bit Single-Core                                                             |

| Speed                      | 80MHz                                                                          |

| Connectivity               | CANbus, Ethernet, I <sup>2</sup> C, SPI, UART/USART, USB OTG                   |

| Peripherals                | Brown-out Detect/Reset, DMA, POR, PWM, WDT                                     |

| Number of I/O              | 85                                                                             |

| Program Memory Size        | 128KB (128K x 8)                                                               |

| Program Memory Type        | FLASH                                                                          |

| EEPROM Size                | -                                                                              |

| RAM Size                   | 32K x 8                                                                        |

| Voltage - Supply (Vcc/Vdd) | 2.3V ~ 3.6V                                                                    |

| Data Converters            | A/D 16x10b                                                                     |

| Oscillator Type            | Internal                                                                       |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                              |

| Mounting Type              | Surface Mount                                                                  |

| Package / Case             | 100-TQFP                                                                       |

| Supplier Device Package    | 100-TQFP (14x14)                                                               |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic32mx764f128l-i-pf |

|                            |                                                                                |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

#### 2.0 GUIDELINES FOR GETTING STARTED WITH 32-BIT MCUS

**Note:** This data sheet summarizes the features of the PIC32MX5XX/6XX/7XX family of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to the related section of the *"PIC32 Family Reference Manual"*, which is available from the Microchip web site (www.microchip.com/PIC32).

#### 2.1 Basic Connection Requirements

Getting started with the PIC32MX5XX/6XX/7XX family of 32-bit Microcontrollers (MCUs) requires attention to a minimal set of device pin connections before proceeding with development. The following is a list of pin names, which must always be connected:

- All VDD and Vss pins (see 2.2 "Decoupling Capacitors")

- All AVDD and AVss pins even if the ADC module is not used (see 2.2 "Decoupling Capacitors")

- VCAP pin (see 2.3 "Capacitor on Internal Voltage Regulator (VCAP)")

- MCLR pin (see 2.4 "Master Clear (MCLR) Pin")

- PGECx/PGEDx pins used for In-Circuit Serial Programming<sup>™</sup> (ICSP<sup>™</sup>) and debugging purposes (see **2.5** "ICSP Pins")

- OSC1 and OSC2 pins when external oscillator source is used (see 2.8 "External Oscillator Pins")

The following pin may be required, as well: VREF+/ VREF- pins used when external voltage reference for ADC module is implemented.

**Note:** The AVDD and AVSS pins must be connected, regardless of the ADC use and the ADC voltage reference source.

#### 2.2 Decoupling Capacitors

The use of decoupling capacitors on power supply pins, such as VDD, VSS, AVDD and AVSS is required. See Figure 2-1.

Consider the following criteria when using decoupling capacitors:

- Value and type of capacitor: A value of 0.1  $\mu$ F (100 nF), 10-20V is recommended. The capacitor should be a low Equivalent Series Resistance (low-ESR) capacitor and have resonance frequency in the range of 20 MHz and higher. It is further recommended to use ceramic capacitors.

- Placement on the printed circuit board: The decoupling capacitors should be placed as close to the pins as possible. It is recommended that the capacitors be placed on the same side of the board as the device. If space is constricted, the capacitor can be placed on another layer on the PCB using a via; however, ensure that the trace length from the pin to the capacitor is within one-quarter inch (6 mm) in length.

- Handling high frequency noise: If the board is experiencing high frequency noise, upward of tens of MHz, add a second ceramic-type capacitor in parallel to the above described decoupling capacitor. The value of the second capacitor can be in the range of 0.01  $\mu$ F to 0.001  $\mu$ F. Place this second capacitor next to the primary decoupling capacitor. In high-speed circuit designs, consider implementing a decade pair of capacitances as close to the power and ground pins as possible. For example, 0.1  $\mu$ F in parallel with 0.001  $\mu$ F.

- Maximizing performance: On the board layout from the power supply circuit, run the power and return traces to the decoupling capacitors first, and then to the device pins. This ensures that the decoupling capacitors are first in the power chain. Equally important is to keep the trace length between the capacitor and the power pins to a minimum, thereby reducing PCB track inductance.

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |  |  |  |  |  |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|--|--|--|--|--|--|

| 04.04        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |  |  |  |  |  |  |

| 31:24        | -                 | _                 | _                 | —                 | _                 | —                 | -                | —                |  |  |  |  |  |  |

| 22.16        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |  |  |  |  |  |  |

| 23:16        | _                 | —                 | _                 | —                 | _                 | —                 | _                | —                |  |  |  |  |  |  |

| 45.0         | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R-0              | R-0              |  |  |  |  |  |  |

| 15:8         | BMXDKPBA<15:8>    |                   |                   |                   |                   |                   |                  |                  |  |  |  |  |  |  |

| 7.0          | R-0               | R-0               | R-0               | R-0               | R-0               | R-0               | R-0              | R-0              |  |  |  |  |  |  |

| 7:0          | BMXDKPBA<7:0>     |                   |                   |                   |                   |                   |                  |                  |  |  |  |  |  |  |

#### REGISTER 4-2: BMXDKPBA: DATA RAM KERNEL PROGRAM BASE ADDRESS REGISTER

#### Legend:

| Legenu.           |                  |                           |                    |

|-------------------|------------------|---------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, re | ad as '0'          |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared      | x = Bit is unknown |

bit 31-16 Unimplemented: Read as '0'

bit 15-10 **BMXDKPBA<15:10>:** DRM Kernel Program Base Address bits When non-zero, this value selects the relative base address for kernel program space in RAM

bit 9-0 **BMXDKPBA<9:0>:** DRM Kernel Program Base Address Read-Only bits Value is always '0', which forces 1 KB increments

**Note 1:** At Reset, the value in this register is forced to zero, which causes all of the RAM to be allocated to Kernal mode data usage.

2: The value in this register must be less than or equal to BMXDRMSZ.

|                             |                                 | P             | IC32M)        | <b>(695F5</b> 1 | 12L DE      | /ICES                         |                               |                             |                    |                  |                       |                       |                       |                       |                         |        |                |        |            |

|-----------------------------|---------------------------------|---------------|---------------|-----------------|-------------|-------------------------------|-------------------------------|-----------------------------|--------------------|------------------|-----------------------|-----------------------|-----------------------|-----------------------|-------------------------|--------|----------------|--------|------------|

| SS                          |                                 |               |               |                 |             |                               |                               |                             |                    | Bi               | its                   |                       |                       |                       |                         |        |                |        |            |

| Virtual Address<br>(BF88_#) | Register<br>Name <sup>(1)</sup> | Bit Range     | 31/15         | 30/14           | 29/13       | 28/12                         | 27/11                         | 26/10                       | 25/9               | 24/8             | 23/7                  | 22/6                  | 21/5                  | 20/4                  | 19/3                    | 18/2   | 17/1           | 16/0   | All Resets |

| 1000                        | INTCON                          | 31:16         | _             | _               | —           | —                             | _                             |                             | —                  | —                | —                     | —                     | _                     | _                     | _                       | —      | —              | SS0    | 0000       |

| 1000                        | introom                         | 15:0          | —             | —               | —           | MVEC                          | —                             |                             | TPC<2:0>           | -                | —                     | —                     | —                     | INT4EP                | INT3EP                  | INT2EP | INT1EP         | INT0EP | 0000       |

| 1010                        | INTSTAT <sup>(3)</sup>          | 31:16         | _             | _               |             |                               | _                             | —                           | —                  | —                |                       |                       | _                     | _                     | _                       | —      | —              | _      | 0000       |

|                             |                                 | 15:0          |               |                 | —           | —                             | _                             |                             | SRIPL<2:0>         | •                | —                     | —                     |                       |                       | VEC                     | <5:0>  |                |        | 0000       |

| 1020                        | IPTMR                           | 31:16<br>15:0 |               |                 |             |                               |                               |                             |                    | IPTMR            | <31:0>                |                       |                       |                       |                         |        |                |        | 0000       |

| 1030                        | IFS0                            | 31:16         | I2C1MIF       | I2C1SIF         | I2C1BIF     | U1TXIF<br>SPI3TXIF<br>I2C3MIF | U1RXIF<br>SPI3RXIF<br>I2C3SIF | U1EIF<br>SPI3EIF<br>I2C3BIF | SPI1TXIF           | SPI1RXIF         | SPI1EIF               | OC5IF                 | IC5IF                 | T5IF                  | INT4IF                  | OC4IF  | IC4IF          | T4IF   | 0000       |

|                             |                                 | 15:0          | INT3IF        | OC3IF           | IC3IF       | T3IF                          | INT2IF                        | OC2IF                       | IC2IF              | T2IF             | INT1IF                | OC1IF                 | IC1IF                 | T1IF                  | INTOIF                  | CS1IF  | CS0IF          | CTIF   | 0000       |

|                             |                                 | 31:16         | IC3EIF        | IC2EIF          | IC1EIF      | ETHIF                         | —                             | _                           | USBIF              | FCEIF            | DMA7IF <sup>(2)</sup> | DMA6IF <sup>(2)</sup> | DMA5IF <sup>(2)</sup> | DMA4IF <sup>(2)</sup> | DMA3IF                  | DMA2IF | DMA1IF         | DMA0IF | 0000       |

| 1040                        | IFS1                            | 15:0          | RTCCIF        | FSCMIF          | I2C2MIF     | I2C2SIF                       | I2C2BIF                       | U2TXIF<br>SPI4TXIF          | U2RXIF<br>SPI4RXIF | U2EIF<br>SPI4EIF | U3TXIF<br>SPI2TXIF    | U3RXIF<br>SPI2RXIF    | U3EIF<br>SPI2EIF      | CMP2IF                | CMP1IF                  | PMPIF  | AD1IF          | CNIF   | 0000       |

|                             |                                 |               |               |                 |             |                               |                               | I2C5MIF                     | I2C5SIF            | I2C5BIF          | I2C4MIF               | I2C4SIF               | I2C4BIF               |                       |                         |        |                |        |            |

| 1050                        | IFS2                            | 31:16         | _             |                 | _           | _                             |                               | —                           | _                  | —                | —                     | _                     | _                     | —                     | —                       | —      | _              | —      | 0000       |

|                             |                                 | 15:0          | _             | _               | _           | -                             | U5TXIF                        | U5RXIF                      | U5EIF              | U6TXIF           | U6RXIF                | U6EIF                 | U4TXIF                | U4RXIF                | U4EIF                   | PMPEIF | IC5EIF         | IC4EIF | 0000       |

| 1060                        | IEC0                            | 31:16         | I2C1MIE       | I2C1SIE         | I2C1BIE     | U1TXIE<br>SPI3TXIE<br>I2C3MIE | U1RXIE<br>SPI3RXIE<br>I2C3SIE | U1EIE<br>SPI3EIE<br>I2C3BIE | SPI1TXIE           | SPI1RXIE         | SPI1EIE               | OC5IE                 | IC5IE                 | T5IE                  | INT4IE                  | OC4IE  | IC4IE          | T4IE   | 0000       |

|                             |                                 | 15:0          | INT3IE        | OC3IE           | IC3IE       | T3IE                          | INT2IE                        | OC2IE                       | IC2IE              | T2IE             | INT1IE                | OC1IE                 | IC1IE                 | T1IE                  | INT0IE                  | CS1IE  | CS0IE          | CTIE   | 0000       |

|                             |                                 | 31:16         | <b>IC3EIE</b> | IC2EIE          | IC1EIE      | ETHIE                         | _                             | -                           | USBIE              | FCEIE            | DMA7IE <sup>(2)</sup> | DMA6IE <sup>(2)</sup> | DMA5IE <sup>(2)</sup> | DMA4IE <sup>(2)</sup> | DMA3IE                  | DMA2IE | DMA1IE         | DMA0IE | 0000       |

| 1070                        | IEC1                            | 15:0          | RTCCIE        | FSCMIE          | I2C2MIE     | I2C2SIE                       | I2C2BIE                       | U2TXIE<br>SPI4TXIE          | U2RXIE<br>SPI4RXIE | U2EIE<br>SPI4EIE | U3TXIE<br>SPI2TXIE    | U3RXIE<br>SPI2RXIE    | U3EIE<br>SPI2EIE      | CMP2IE                | CMP1IE                  | PMPIE  | AD1IE          | CNIE   | 0000       |

|                             |                                 |               |               |                 |             |                               |                               | I2C5MIE                     | I2C5SIE            | I2C5BIE          | I2C4MIE               | I2C4SIE               | I2C4BIE               |                       |                         |        |                |        |            |

| 1080                        | IEC2                            | 31:16         | —             | _               | —           | —                             | —                             | -                           | —                  | —                | —                     | —                     | —                     | —                     | —                       | —      | —              | —      | 0000       |

| 1000                        | 1202                            | 15:0          | _             |                 | —           | —                             | U5TXIE                        | U5RXIE                      | U5EIE              | U6TXIE           | U6RXIE                | U6EIE                 | U4TXIE                | U4RXIE                | U4EIE                   | PMPEIE | IC5EIE         | IC4EIE | 0000       |

| 1090                        | IPC0                            | 31:16         | -             | _               |             |                               | INT0IP<2:0>                   |                             |                    | S<1:0>           |                       |                       | _                     |                       | CS1IP<2:0>              |        | CS1IS          |        | 0000       |

|                             |                                 | 15:0          | —             | —               | —           |                               | CS0IP<2:0>                    |                             |                    | S<1:0>           | —                     | —                     | —                     |                       | CTIP<2:0>               |        | CTIS           |        | 0000       |

| 10A0                        | IPC1                            | 31:16         | _             |                 | _           |                               | INT1IP<2:0>                   |                             |                    | S<1:0>           | _                     | _                     | _                     |                       | OC1IP<2:0>              | •      | OC1IS          |        | 0000       |

|                             |                                 | 15:0          | _             | _               | _           |                               | IC1IP<2:0>                    |                             |                    | <1:0>            | _                     | _                     | _                     | T1IP<2:0>             |                         |        | T1IS-          |        | 0000       |

| 10B0                        | IPC2                            | 31:16         | _             | _               | —           |                               | INT2IP<2:0>                   |                             |                    | S<1:0>           | —                     | _                     | _                     |                       | OC2IP<2:0>              | •      | OC2IS          |        | 0000       |

|                             |                                 | 15:0          | _             |                 |             |                               | IC2IP<2:0><br>INT3IP<2:0>     |                             |                    | <1:0><br>S<1:0>  |                       |                       |                       |                       | T2IP<2:0><br>OC3IP<2:0> |        | T2IS-<br>OC3IS | -      | 0000       |

| 10C0                        | IPC3                            | 31:16<br>15:0 | _             |                 |             |                               | IC3IP<2:0>                    |                             |                    | <1:0>            | _                     |                       |                       |                       | T3IP<2:0>               | •      | T3IS-          |        | 0000       |

| Legend                      | d: x=                           |               | n value on F  | Reset; — = u    | Inimplement | ed, read as '                 |                               | ues are sho                 |                    |                  | I                     | I                     |                       | 1                     | .011 \2.02              |        | 1010           |        | 0000       |

#### **TABLE 7-6:** INTERRUPT REGISTER MAP FOR PIC32MX664F064L, PIC32MX664F128L, PIC32MX675F256L, PIC32MX675F512L AND

Except where noted, all registers in this table have corresponding CLR, SET and INV registers at their virtual addresses, plus offsets of 0x4, 0x8 and 0xC, respectively. See Section 12.1.1 "CLR, SET and INV Note 1: Registers" for more information.

These bits are not available on PIC32MX664 devices. 2:

This register does note have associated CLR, SET, and INV registers. 3:

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|

| 24.24        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 31:24        |                   |                   | _                 | —                 | -                 | _                 | _                | _                |

| 23:16        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | R/W-0            |

| 23.10        | —                 | —                 | —                 | —                 | _                 | —                 | —                | SS0              |

| 45.0         | U-0               | U-0               | U-0               | R/W-0             | U-0               | R/W-0             | R/W-0            | R/W-0            |

| 15:8         | _                 | —                 | —                 | MVEC              | _                 |                   | TPC<2:0>         |                  |

| 7.0          | U-0               | U-0               | U-0               | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |

| 7:0          |                   |                   | _                 | INT4EP            | INT3EP            | INT2EP            | INT1EP           | INT0EP           |

#### REGISTER 7-1: INTCON: INTERRUPT CONTROL REGISTER

#### Legend:

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, re | ad as '0'          |

|-------------------|------------------|---------------------------|--------------------|

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared      | x = Bit is unknown |

#### bit 31-17 Unimplemented: Read as '0'

- bit 16 **SS0:** Single Vector Shadow Register Set bit

- 1 = Single vector is presented with a shadow register set

- 0 = Single vector is not presented with a shadow register set

- bit 15-13 Unimplemented: Read as '0'

- bit 12 MVEC: Multiple Vector Configuration bit

- 1 = Interrupt controller configured for Multi-vector mode

- 0 = Interrupt controller configured for Single-vector mode

- bit 11 Unimplemented: Read as '0'

- bit 10-8 TPC<2:0>: Interrupt Proximity Timer Control bits

- 111 = Interrupts of group priority 7 or lower start the Interrupt Proximity timer 110 = Interrupts of group priority 6 or lower start the Interrupt Proximity timer 101 = Interrupts of group priority 5 or lower start the Interrupt Proximity timer 100 = Interrupts of group priority 4 or lower start the Interrupt Proximity timer 011 = Interrupts of group priority 3 or lower start the Interrupt Proximity timer

- 010 = Interrupts of group priority 2 or lower start the Interrupt Proximity timer

- 001 = Interrupts of group priority 1 start the Interrupt Proximity timer

- 000 = Disables Interrupt Proximity timer

- bit 7-5 Unimplemented: Read as '0'

- bit 4 INT4EP: External Interrupt 4 Edge Polarity Control bit

- 1 = Rising edge

- 0 = Falling edge

- bit 3 INT3EP: External Interrupt 3 Edge Polarity Control bit

- 1 = Rising edge

- 0 = Falling edge

- bit 2 INT2EP: External Interrupt 2 Edge Polarity Control bit

- 1 = Rising edge

- 0 = Falling edge

- bit 1 **INT1EP:** External Interrupt 1 Edge Polarity Control bit

- 1 = Rising edge

- 0 = Falling edge

- bit 0 INTOEP: External Interrupt 0 Edge Polarity Control bit

- 1 = Rising edge

- 0 = Falling edge

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|

| 31:24        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0 U-0           |                  | U-0              |

| 31.24        |                   |                   |                   |                   | _                 | _                 |                  | -                |

| 22:46        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 23:16        |                   |                   |                   |                   | _                 | _                 |                  | -                |

| 15:8         | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 15.0         |                   |                   |                   |                   | _                 | _                 |                  | -                |

| 7:0          | U-0               | U-0               | U-0               | U-0               | U-0               | R-0               | R-0              | R-0              |

| 7.0          |                   | _                 | _                 | _                 | _                 |                   | FRMH<2:0>        |                  |

#### REGISTER 11-14: U1FRMH: USB FRAME NUMBER HIGH REGISTER

#### Legend:

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, r | ead as '0'         |  |

|-------------------|------------------|--------------------------|--------------------|--|

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared     | x = Bit is unknown |  |

bit 31-3 Unimplemented: Read as '0'

bit 2-0 **FRMH<2:0>:** Upper 3 bits of the Frame Numbers bits These register bits are updated with the current frame number whenever a SOF TOKEN is received.

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |  |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|--|--|

| 31:24        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |  |  |

| 31.24        |                   | _                 |                   | —                 |                   | _                 |                  | —                |  |  |

| 23:16        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |  |  |

| 23.10        | —                 | _                 | —                 | —                 | —                 | _                 | —                | —                |  |  |

| 15:8         | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |  |  |

| 15.6         | —                 | _                 | —                 | —                 | —                 | _                 | —                | —                |  |  |

| 7.0          | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |

| 7:0          |                   | PID<              | :3:0>             |                   | EP<3:0>           |                   |                  |                  |  |  |

#### REGISTER 11-15: U1TOK: USB TOKEN REGISTER

| Legend:           |                  |                                              |                    |  |  |  |

|-------------------|------------------|----------------------------------------------|--------------------|--|--|--|

| R = Readable bit  | W = Writable bit | N = Writable bit $U =$ Unimplemented bit, re |                    |  |  |  |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared                         | x = Bit is unknown |  |  |  |

bit 31-8 Unimplemented: Read as '0'

bit 7-4 PID<3:0>: Token Type Indicator bits<sup>(1)</sup> 1101 = SETUP (TX) token type transaction 1001 = IN (RX) token type transaction 0001 = OUT (TX) token type transaction Note: All other values not listed, are Reserved and must not be used.

#### bit 3-0 **EP<3:0>:** Token Command Endpoint Address bits The four bit value must specify a valid endpoint.

# TABLE 12-5: PORTD REGISTER MAP FOR PIC32MX534F064H, PIC32MX564F064H, PIC32MX564F128H, PIC32MX575F512H, PIC32MX575F512H, PIC32MX664F064H, PIC32MX664F128H, PIC32MX675F256H, PIC32MX675F512H, PIC32MX695F512H, PIC32MX775F512H, PIC32MX775F512H, AND PIC32MX795F512H DEVICES

| ess                         |                                 |           |       |       |       |       |         |         |        | Bi     | ts     |        |        |        |        |        |        |        | ú          |

|-----------------------------|---------------------------------|-----------|-------|-------|-------|-------|---------|---------|--------|--------|--------|--------|--------|--------|--------|--------|--------|--------|------------|

| Virtual Address<br>(BF88_#) | Register<br>Name <sup>(1)</sup> | Bit Range | 31/15 | 30/14 | 29/13 | 28/12 | 27/11   | 26/10   | 25/9   | 24/8   | 23/7   | 22/6   | 21/5   | 20/4   | 19/3   | 18/2   | 17/1   | 16/0   | All Resets |

| 60C0                        | TRISD                           | 31:16     | -     | -     | -     | _     | _       | -       | —      | —      | —      | —      | —      | -      | _      | -      | -      | —      | 0000       |

| 6000                        | TRISD                           | 15:0      | _     | _     | _     | -     | TRISD11 | TRISD10 | TRISD9 | TRISD8 | TRISD7 | TRISD6 | TRISD5 | TRISD4 | TRISD3 | TRISD2 | TRISD1 | TRISD0 | OFFF       |

| 6000                        | PORTD                           | 31:16     | -     |       |       | _     | _       |         | -      |        |        |        |        | _      | _      |        | _      | _      | 0000       |

| 6000                        | PORID                           | 15:0      | -     | -     | _     | _     | RD11    | RD10    | RD9    | RD8    | RD7    | RD6    | RD5    | RD4    | RD3    | RD2    | RD1    | RD0    | xxxx       |

| 60E0                        | LATD                            | 31:16     | _     | _     | _     | -     | _       | -       | _      | _      | _      | _      | _      | _      | -      | _      | _      | _      | 0000       |

| 60E0                        | LAID                            | 15:0      | _     | _     | _     | -     | LATD11  | LATD10  | LATD9  | LATD8  | LATD7  | LATD6  | LATD5  | LATD4  | LATD3  | LATD2  | LATD1  | LATD0  | xxxx       |

| 60F0                        | ODCD                            | 31:16     | _     |       | _     | _     | _       | —       | -      | -      | -      |        |        | —      | _      | _      | _      | -      | 0000       |

| OUFU                        | ODCD                            | 15:0      |       | _     | —     | _     | ODCD11  | ODCD10  | ODCD9  | ODCD8  | ODCD7  | ODCD6  | ODCD5  | ODCD4  | ODCD3  | ODCD2  | ODCD1  | ODCD0  | 0000       |

Legend: x = unknown value on Reset; - = unimplemented, read as '0'. Reset values are shown in hexadecimal.

Note 1: All registers in this table have corresponding CLR, SET and INV registers at their virtual addresses, plus offsets of 0x4, 0x8 and 0xC, respectively. See Section 12.1.1 "CLR, SET and INV Registers" for more information.

## TABLE 12-6: PORTD REGISTER MAP FOR PIC32MX534F064L, PIC32MX564F064L, PIC32MX564F128L, PIC32MX575F512L, PIC32MX664F064L, PIC32MX664F128L, PIC32MX675F256L, PIC32MX675F512L, PIC32MX695F512L, PIC32MX764F128L, PIC32MX775F512L, AND PIC32MX795F512L DEVICES

| ess                         |                                 | Ċ,        |         |         |         |         |         |         |        | Bi     | ts     |        |        |        |        |        |        |        | 6         |

|-----------------------------|---------------------------------|-----------|---------|---------|---------|---------|---------|---------|--------|--------|--------|--------|--------|--------|--------|--------|--------|--------|-----------|

| Virtual Address<br>(BF88_#) | Register<br>Name <sup>(1)</sup> | Bit Range | 31/15   | 30/14   | 29/13   | 28/12   | 27/11   | 26/10   | 25/9   | 24/8   | 23/7   | 22/6   | 21/5   | 20/4   | 19/3   | 18/2   | 17/1   | 16/0   | All Reset |

| 60C0                        | TRISD                           | 31:16     | _       | _       | _       | -       | -       | _       |        | _      | -      | -      | _      |        | -      | -      | —      | —      | 0000      |

| 6000                        | TRISD                           | 15:0      | TRISD15 | TRISD14 | TRISD13 | TRISD12 | TRISD11 | TRISD10 | TRISD9 | TRISD8 | TRISD7 | TRISD6 | TRISD5 | TRISD4 | TRISD3 | TRISD2 | TRISD1 | TRISD0 | FFFF      |

| 60D0                        | PORTD                           | 31:16     | _       | _       |         |         |         | -       |        |        |        |        | -      |        |        |        | _      | _      | 0000      |

| 0000                        | FORID                           | 15:0      | RD15    | RD14    | RD13    | RD12    | RD11    | RD10    | RD9    | RD8    | RD7    | RD6    | RD5    | RD4    | RD3    | RD2    | RD1    | RD0    | xxxx      |

| 60E0                        | LATD                            | 31:16     | —       | _       | _       | _       | _       | _       | _      | _      | -      | _      | _      | _      | _      | _      | —      | —      | 0000      |

| OUEU                        | LAID                            | 15:0      | LAT15   | LAT14   | LAT13   | LAT12   | LATD11  | LATD10  | LATD9  | LATD8  | LATD7  | LATD6  | LATD5  | LATD4  | LATD3  | LATD2  | LATD1  | LATD0  | xxxx      |

| 60F0                        | ODCD                            | 31:16     | _       | _       |         |         |         | _       | -      |        |        |        | _      | -      |        |        | _      | -      | 0000      |

| OUFU                        | ODCD                            | 15:0      | ODCD15  | ODCD14  | ODCD13  | ODCD12  | ODCD11  | ODCD10  | ODCD9  | ODCD8  | ODCD7  | ODCD6  | ODCD5  | ODCD4  | ODCD3  | ODCD2  | ODCD1  | ODCD0  | 0000      |

Ļ

Legend: x = unknown value on Reset; — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

Note 1: All registers in this table have corresponding CLR, SET and INV registers at their virtual addresses, plus offsets of 0x4, 0x8 and 0xC, respectively. See Section 12.1.1 "CLR, SET and INV Registers" for more information.

| Т | ABLE 12 | PORTG REGISTER MAP FOR PIC32MX534F064H, PIC32MX564F064H, PIC32MX564F128H, PIC32MX575F256H, PIC32MX575F512H, PIC32MX664F064H, PIC32MX664F128H, PIC32MX675F256H, PIC32MX675F512H, PIC32MX695F512H | Н. |

|---|---------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

|   |         | PIC32MX764F128H, PIC32MX775F256H, PIC32MX775F512H AND PIC32MX795F512H DEVICES                                                                                                                   | ,  |

|   | ssa     | Bits                                                                                                                                                                                            |    |

| ö                          |                                 | Φ         |       |        |       |       |           |                    |        | -               |        |        |      |      |        |        |      |      | <i>(</i> 0 |

|----------------------------|---------------------------------|-----------|-------|--------|-------|-------|-----------|--------------------|--------|-----------------|--------|--------|------|------|--------|--------|------|------|------------|

| Virtual Addres<br>(BF88_#) | Register<br>Name <sup>(1)</sup> | Bit Range | 31/15 | 30/14  | 29/13 | 28/12 | 27/11     | 26/10              | 25/9   | 24/8            | 23/7   | 22/6   | 21/5 | 20/4 | 19/3   | 18/2   | 17/1 | 16/0 | All Reset  |

| 6180                       | TRISG                           | 31:16     | —     | —      | —     | _     | —         | —                  | _      | —               | —      | —      | _    | _    | -      | _      | _    | _    | 0000       |

| 6160                       | TRIBU                           | 15:0      | _     | _      | _     | _     | _         |                    | TRISG9 | TRISG8          | TRISG7 | TRISG6 | _    |      | TRISG3 | TRISG2 | -    |      | 03CC       |

| 6100                       | PORTG                           | 31:16     | _     | _      | _     | _     | _         |                    | _      | _               | _      | _      | _    |      |        |        | -    |      | 0000       |

| 6190                       | PURIG                           | 15:0      | _     | _      | _     | _     | _         |                    | RG9    | RG8             | RG7    | RG6    | _    |      | RG3    | RG2    | -    |      | xxxx       |

| 61A0                       | LATG                            | 31:16     | _     | _      | _     | _     | _         |                    | _      | _               | _      | _      | _    |      |        |        | -    |      | 0000       |

| OTAU                       | LAIG                            | 15:0      | _     | _      | _     | _     | _         |                    | LATG9  | LATG8           | LATG7  | LATG6  | _    |      | LATG3  | LATG2  | -    |      | xxxx       |

| 61B0                       | ODCG                            | 31:16     | -     | _      | _     | _     | -         | _                  | _      | _               | _      | -      | _    |      |        | -      | _    |      | 0000       |

| 0180                       | ODCG                            | 15:0      | -     | _      | _     | _     | -         | _                  | ODCG9  | ODCG8           | ODCG7  | ODCG6  | _    |      | ODCG3  | ODCG2  | _    |      | 0000       |

| Laware                     |                                 |           |       | Divisi |       |       | fal Deset | alter a successful |        | dia statistical |        |        |      |      |        |        |      |      |            |

Legend: x = unknown value on Reset; — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

All registers in this table have corresponding CLR, SET and INV registers at their virtual addresses, plus offsets of 0x4, 0x8 and 0xC, respectively. See Section 12.1.1 "CLR, SET and INV Registers" for more Note 1: information.

#### TABLE 12-12: PORTG REGISTER MAP FOR PIC32MX534F064L, PIC32MX564F064L, PIC32MX564F128L, PIC32MX575F256L, PIC32MX575F512L, PIC32MX664F064L, PIC32MX664F128L, PIC32MX675F256L, PIC32MX675F512L, PIC32MX695F512L, PIC32MX764F128L. PIC32MX775F256L. PIC32MX775F512L AND PIC32MX795F512L DEVICES

| ess                         | <b></b>                         |           |         |         |         |         |       |       |        | Bi     | ts     |        |      |      |        |        |        |        | <i>(</i> 0 |

|-----------------------------|---------------------------------|-----------|---------|---------|---------|---------|-------|-------|--------|--------|--------|--------|------|------|--------|--------|--------|--------|------------|

| Virtual Address<br>(BF88_#) | Register<br>Name <sup>(1)</sup> | Bit Range | 31/15   | 30/14   | 29/13   | 28/12   | 27/11 | 26/10 | 25/9   | 24/8   | 23/7   | 22/6   | 21/5 | 20/4 | 19/3   | 18/2   | 17/1   | 16/0   | All Resets |

| 6180                        | TRISG                           | 31:16     | _       | —       | _       | -       | _     | —     | -      | —      | —      | -      | —    | -    | -      | -      | -      | -      | 0000       |

| 0100                        | TRISG                           | 15:0      | TRISG15 | TRISG14 | TRISG13 | TRISG12 | _     | _     | TRISG9 | TRISG8 | TRISG7 | TRISG6 | _    | _    | TRISG3 | TRISG2 | TRISG1 | TRISG0 | F3CF       |

| 6100                        | PORTG                           | 31:16     |         | _       |         | _       |       | -     | -      | -      | -      | —      | -    | —    | —      | —      | _      | —      | 0000       |

| 6190                        | PURIG                           | 15:0      | RG15    | RG14    | RG13    | RG12    |       |       | RG9    | RG8    | RG7    | RG6    |      | -    | RG3    | RG2    | RG1    | RG0    | xxxx       |

| 61A0                        | LATG                            | 31:16     | -       | _       |         | _       | -     | -     | -      | -      | -      | —      | -    | —    | —      | —      | —      | —      | 0000       |

| 61A0                        | LAIG                            | 15:0      | LATG15  | LATG14  | LATG13  | LATG12  | _     | _     | LATG9  | LATG8  | LATG7  | LATG6  | _    | -    | LATG3  | LATG2  | LATG1  | LATG0  | xxxx       |

| 61B0                        | ODCG                            | 31:16     |         | —       | _       | _       |       | _     |        | _      | _      | —      | _    | —    | —      | —      | —      | —      | 0000       |

| 0160                        | ODCG                            | 15:0      | ODCG15  | ODCG14  | ODCG13  | ODCG12  | _     | -     | ODCG9  | ODCG8  | ODCG7  | ODCG6  | -    | _    | ODCG3  | ODCG2  | ODCG1  | ODCG0  | 0000       |

Legend: x = unknown value on Reset; --- = unimplemented, read as '0'. Reset values are shown in hexadecimal.

All registers in this table have corresponding CLR, SET and INV registers at their virtual addresses, plus offsets of 0x4, 0x8 and 0xC, respectively. See Section 12.1.1 "CLR, SET and INV Registers" for more Note 1: information.

#### I2CxSTAT: I<sup>2</sup>C STATUS REGISTER (CONTINUED) REGISTER 19-2: **D\_A:** Data/Address bit (when operating as I<sup>2</sup>C slave) bit 5 This bit is cleared by hardware upon a device address match, and is set by hardware by reception of the slave byte. 1 = Indicates that the last byte received was data 0 = Indicates that the last byte received was device address bit 4 P: Stop bit This bit is set or cleared by hardware when a Start, Repeated Start, or Stop condition is detected. 1 = Indicates that a Stop bit has been detected last 0 = Stop bit was not detected last bit 3 S: Start bit This bit is set or cleared by hardware when a Start, Repeated Start, or Stop condition is detected. 1 = Indicates that a Start (or Repeated Start) bit has been detected last 0 = Start bit was not detected last **R\_W:** Read/Write Information bit (when operating as I<sup>2</sup>C slave) bit 2 This bit is set or cleared by hardware after reception of an I<sup>2</sup>C device address byte. 1 = Read – indicates data transfer is output from slave 0 = Write - indicates data transfer is input to slave **RBF:** Receive Buffer Full Status bit bit 1 This bit is set by hardware when the I2CxRCV register is written with a received byte, and is cleared by hardware when software reads I2CxRCV. 1 = Receive complete, I2CxRCV is full 0 = Receive not complete, I2CxRCV is empty bit 0 TBF: Transmit Buffer Full Status bit This bit is set by hardware when software writes to the I2CxTRN register, and is cleared by hardware upon completion of data transmission.

1 = Transmit in progress, I2CxTRN is full

0 = Transmit complete, I2CxTRN is empty

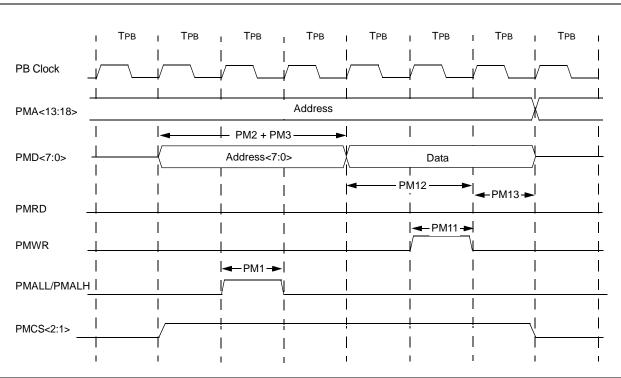

#### 21.1 Control Registers

#### TABLE 21-1: PARALLEL MASTER PORT REGISTER MAP

|                                         |                                 |           |           |           |       |       |         |        |        | Bi     | ts      |        |      |       |        |      |       |       |            |

|-----------------------------------------|---------------------------------|-----------|-----------|-----------|-------|-------|---------|--------|--------|--------|---------|--------|------|-------|--------|------|-------|-------|------------|

| Virtual Address<br>(BF80_#)<br>Register | Register<br>Name <sup>(1)</sup> | Bit Range | 31/15     | 30/14     | 29/13 | 28/12 | 27/11   | 26/10  | 25/9   | 24/8   | 23/7    | 22/6   | 21/5 | 20/4  | 19/3   | 18/2 | 17/1  | 16/0  | All Resets |

| 7000 PM0                                | /CON                            | 31:16     | _         | _         | _     | _     | _       | _      | _      | _      |         | _      | _    | _     | —      | _    | —     | _     | 0000       |

| 7000 1 100                              |                                 | 15:0      | ON        | —         | SIDL  | ADRMU | IX<1:0> | PMPTTL | PTWREN | PTRDEN | CSF     | <1:0>  | ALP  | CS2P  | CS1P   | —    | WRSP  | RDSP  | 0000       |

| 7010 PMM                                | MODE                            | 31:16     | —         | —         | —     | —     | —       | —      | —      | —      | —       | —      | —    | —     | —      | —    | —     | —     | 0000       |

| 7010 Pivily                             | NODE                            | 15:0      | BUSY      | IRQM      | <1:0> | INCM  | <1:0>   | MODE16 | MODE   | <1:0>  | WAITE   | 3<1:0> |      | WAITM | A<3:0> |      | WAITE | <1:0> | 0000       |

| 7020 PMA                                |                                 | 31:16     |           | _         | _     | _     | _       | _      | _      |        | _       | -      | -    | _     | _      | _    | _     | _     | 0000       |

| 7020 PINA                               | IADDR                           | 15:0      | CS2EN/A15 | CS1EN/A14 |       |       |         |        |        |        | ADDR    | <13:0> |      |       |        |      |       |       | 0000       |

| 7000 040                                |                                 | 31:16     |           |           |       |       |         |        |        | DATAOU | T 04.0  |        |      |       |        |      |       |       | 0000       |

| 7030 PMD                                |                                 | 15:0      |           |           |       |       |         |        |        | DATAOU | 1<31:0> |        |      |       |        |      |       |       | 0000       |

| 7040 DM                                 | MDIN                            | 31:16     |           |           |       |       |         |        |        |        | .01.0   |        |      |       |        |      |       |       | 0000       |

| 7040 PM                                 |                                 | 15:0      |           |           |       |       |         |        |        | DATAIN | <31:0>  |        |      |       |        |      |       |       | 0000       |

| 7050 014                                | MAEN                            | 31:16     |           | _         | _     | _     | _       | _      | _      |        | _       | -      | -    | _     | _      | _    | _     | _     | 0000       |

| 7050 PM/                                | VIAEN                           | 15:0      |           |           |       |       |         |        |        | PTEN<  | :15:0>  |        |      |       |        |      |       |       | 0000       |

| 7000 0140                               | 10TAT                           | 31:16     | _         | _         | _     | _     | _       | _      | _      | _      | _       | _      | —    | _     | _      | _    | _     | _     | 0000       |

| 7060 PMS                                | ISTAL                           | 15:0      | IBF       | IBOV      | _     | -     | IB3F    | IB2F   | IB1F   | IB0F   | OBE     | OBUF   | —    | -     | OB3E   | OB2E | OB1E  | OB0E  | 008F       |

Legend: x = unknown value on Reset; — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

Note 1: All registers in this table have corresponding CLR, SET and INV registers at their virtual addresses, plus offsets of 0x4, 0x8 and 0xC, respectively. See Section 12.1.1 "CLR, SET and INV Registers" for more information.

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|

| 24.24        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 31:24        | —                 | _                 | _                 | —                 | _                 | _                 | _                | _                |

| 00.40        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 23:16        | —                 | _                 | _                 | —                 | _                 | _                 | _                | —                |

| 45.0         | U-0               | R/W-0             | U-0               | U-0               | U-0               | R/W-0             | R/W-0            | R/W-0            |

| 15:8         | —                 | PTEN14            | _                 | —                 | _                 |                   | PTEN<10:8>       |                  |

| 7.0          | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |

| 7:0          |                   |                   |                   | PTEN              | <7:0>             |                   |                  |                  |

#### REGISTER 21-4: PMAEN: PARALLEL PORT PIN ENABLE REGISTER

#### Legend:

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, re | ead as '0'         |  |

|-------------------|------------------|---------------------------|--------------------|--|

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared      | x = Bit is unknown |  |

- bit 31-15 **Unimplemented:** Read as '0'

- bit 15-14 **PTEN14:** PMCS1 Strobe Enable bits

- 1 = PMA14 functions as either PMA14 or PMCS1<sup>(1)</sup>

- 0 = PMA14 functions as port I/O

- bit 13-11 Unimplemented: Read as '0'

- bit 10-2 PTEN<10:2>: PMP Address Port Enable bits

- 1 = PMA<10:2> function as PMP address lines

- 0 = PMA<10:2> function as port I/O

- bit 1-0 **PTEN<1:0>:** PMALH/PMALL Strobe Enable bits

- 1 = PMA1 and PMA0 function as either PMA<1:0> or PMALH and PMALL<sup>(2)</sup>

- 0 = PMA1 and PMA0 pads function as port I/O

- **Note 1:** The use of this pin as PMA14 or CS1 is selected by the CSF<1:0> bits in the PMCON register.

- 2: The use of these pins as PMA1/PMA0 or PMALH/PMALL depends on the Address/Data Multiplex mode selected by bits ADRMUX<1:0> in the PMCON register.

#### REGISTER 24-14: CIFLTCON4: CAN FILTER CONTROL REGISTER 4 (CONTINUED)

|           | (                                                           |

|-----------|-------------------------------------------------------------|

| bit 15    | FLTEN17: Filter 13 Enable bit                               |

|           | 1 = Filter is enabled                                       |

|           | 0 = Filter is disabled                                      |

| bit 14-13 | MSEL17<1:0>: Filter 17 Mask Select bits                     |

|           | 11 = Acceptance Mask 3 selected                             |

|           | 10 = Acceptance Mask 2 selected                             |

|           | 01 = Acceptance Mask 1 selected                             |

|           | 00 = Acceptance Mask 0 selected                             |

| bit 12-8  | FSEL17<4:0>: FIFO Selection bits                            |

|           | 11111 = Message matching filter is stored in FIFO buffer 31 |

|           | 11110 = Message matching filter is stored in FIFO buffer 30 |

|           | •                                                           |

|           | •                                                           |

|           | 00001 = Message matching filter is stored in FIFO buffer 1  |

|           | 00000 = Message matching filter is stored in FIFO buffer 0  |

| bit 7     | FLTEN16: Filter 16 Enable bit                               |

|           | 1 = Filter is enabled                                       |

|           | 0 = Filter is disabled                                      |

| bit 6-5   | MSEL16<1:0>: Filter 16 Mask Select bits                     |

|           | 11 = Acceptance Mask 3 selected                             |

|           | 10 = Acceptance Mask 2 selected                             |

|           | 01 = Acceptance Mask 1 selected                             |

|           | 00 = Acceptance Mask 0 selected                             |

| bit 4-0   | FSEL16<4:0>: FIFO Selection bits                            |

|           | 11111 = Message matching filter is stored in FIFO buffer 31 |

|           | 11110 = Message matching filter is stored in FIFO buffer 30 |

|           | •                                                           |

|           | •                                                           |

|           | 00001 = Message matching filter is stored in FIFO buffer 1  |

|           | 00000 = Message matching filter is stored in FIFO buffer 0  |

|           |                                                             |

Note: The bits in this register can only be modified if the corresponding filter enable (FLTENn) bit is '0'.

| REGIST | ER 24-21:  | CiFIFOIN   | Tn: CAN F  |            |            | GISTER 'n' (n | = 0 THROU | GH 31)    |

|--------|------------|------------|------------|------------|------------|---------------|-----------|-----------|

| Bit    | Bit        | Bit        | Bit        | Bit        | Bit        | Bit           | Bit       | Bit       |

| Range  | 31/23/15/7 | 30/22/14/6 | 29/21/13/5 | 28/20/12/4 | 27/19/11/3 | 26/18/10/2    | 25/17/9/1 | 24/16/8/0 |

| Range | 31/23/15/7 | 30/22/14/6 | 29/21/13/5 28/20/12/4 |     | 27/19/11/3 | 26/18/10/2               | 25/17/9/1               | 24/16/8/0                 |

|-------|------------|------------|-----------------------|-----|------------|--------------------------|-------------------------|---------------------------|

| 24.24 | U-0        | U-0        | U-0                   | U-0 | U-0        | R/W-0                    | R/W-0                   | R/W-0                     |

| 31:24 | —          | _          |                       |     |            | TXNFULLIE                | TXHALFIE                | TXEMPTYIE                 |

| 00.40 | U-0        | U-0        | U-0                   | U-0 | R/W-0      | R/W-0                    | R/W-0                   | R/W-0                     |

| 23:16 | —          | —          | —                     | _   | RXOVFLIE   | RXFULLIE                 | RXHALFIE                | RXNEMPTYIE                |

| 15.0  | U-0        | U-0        | U-0                   | U-0 | U-0        | R-0                      | R-0                     | R-0                       |

| 15:8  | —          | —          |                       |     | _          | TXNFULLIF <sup>(1)</sup> | TXHALFIF                | TXEMPTYIF <sup>(1)</sup>  |

| 7.0   | U-0        | U-0        | U-0                   | U-0 | R/W-0      | R-0                      | R-0                     | R-0                       |

| 7:0   | _          | _          | _                     | _   | RXOVFLIF   | RXFULLIF <sup>(1)</sup>  | RXHALFIF <sup>(1)</sup> | RXNEMPTYIF <sup>(1)</sup> |

#### Legend:

| R = Readable bit  | W = Writable bit | U = Unimplemented bit | t, read as '0'     |

|-------------------|------------------|-----------------------|--------------------|

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared  | x = Bit is unknown |

#### bit 31-27 Unimplemented: Read as '0'

| bit 26    | <b>TXNFULLIE:</b> Transmit FIFO Not Full Interrupt Enable bit<br>1 = Interrupt enabled for FIFO not full<br>0 = Interrupt disabled for FIFO not full   |

|-----------|--------------------------------------------------------------------------------------------------------------------------------------------------------|

| bit 25    | <b>TXHALFIE:</b> Transmit FIFO Half Full Interrupt Enable bit<br>1 = Interrupt enabled for FIFO half full<br>0 = Interrupt disabled for FIFO half full |

| bit 24    | <b>TXEMPTYIE:</b> Transmit FIFO Empty Interrupt Enable bit<br>1 = Interrupt enabled for FIFO empty<br>0 = Interrupt disabled for FIFO empty            |

| bit 23-20 | Unimplemented: Read as '0'                                                                                                                             |

| bit 19    | RXOVFLIE: Overflow Interrupt Enable bit                                                                                                                |

|           | <ul><li>1 = Interrupt enabled for overflow event</li><li>0 = Interrupt disabled for overflow event</li></ul>                                           |

| bit 18    | RXFULLIE: Full Interrupt Enable bit                                                                                                                    |

|           | <ol> <li>1 = Interrupt enabled for FIFO full</li> <li>0 = Interrupt disabled for FIFO full</li> </ol>                                                  |

| bit 17    | RXHALFIE: FIFO Half Full Interrupt Enable bit                                                                                                          |

|           | <ul><li>1 = Interrupt enabled for FIFO half full</li><li>0 = Interrupt disabled for FIFO half full</li></ul>                                           |

| bit 16    | <b>RXNEMPTYIE:</b> Empty Interrupt Enable bit                                                                                                          |

|           | <ul><li>1 = Interrupt enabled for FIFO not empty</li><li>0 = Interrupt disabled for FIFO not empty</li></ul>                                           |

| bit 15-11 | Unimplemented: Read as '0'                                                                                                                             |

| bit 10    | TXNFULLIF: Transmit FIFO Not Full Interrupt Flag bit <sup>(1)</sup>                                                                                    |

|           | <u>TXEN = 1:</u> (FIFO configured as a transmit buffer)<br>1 = FIFO is not full<br>0 = FIFO is full                                                    |

|           | <u>TXEN = 0:</u> (FIFO configured as a receive buffer)<br>Unused, reads '0'                                                                            |

**Note 1:** This bit is read-only and reflects the status of the FIFO.

# TABLE 25-5:ETHERNET CONTROLLER REGISTER SUMMARY FOR PIC32MX664F064H, PIC32MX664F128H, PIC32MX664F064L,<br/>PIC32MX664F128L, PIC32MX675F256H, PIC32MX675F512H, PIC32MX695F512H, PIC32MX775F256H, PIC32MX775F512H,<br/>PIC32MX795F512H, PIC32MX695F512L, PIC32MX675F256L, PIC32MX764F128H, PIC32MX764F128H,<br/>PIC32MX775F256L, PIC32MX775F512L AND PIC32MX795F512L DEVICES (CONTINUED)

| sseptimize         and the sector         and the sector <th< th=""><th>:16        5:0        :16        :16    </th><th>30/14<br/></th><th>29/13<br/></th><th>28/12<br/></th><th><b>27/11</b><br/>—<br/>RESET</th><th>26/10</th><th>25/9</th><th>24/8</th><th>its<br/>23/7</th><th>22/6</th><th>21/5</th><th>20/4</th><th>19/3</th><th>18/2</th><th>17/1</th><th>16/0</th><th>All Resets</th></th<> | :16        5:0        :16        :16 | 30/14<br>                        | 29/13<br> | 28/12<br>                      | <b>27/11</b><br>—<br>RESET | 26/10      | 25/9 | 24/8          | its<br>23/7 | 22/6 | 21/5 | 20/4 | 19/3          | 18/2      | 17/1      | 16/0     | All Resets |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------|----------------------------------|-----------|--------------------------------|----------------------------|------------|------|---------------|-------------|------|------|------|---------------|-----------|-----------|----------|------------|

| 9260         EMAC1<br>SUPP         31:10<br>15:0           9270         EMAC1<br>TEST         31:10<br>15:0           9280         EMAC1<br>31:10         31:10                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | :16        5:0        :16        :16 |                                  |           | _                              | —<br>RESET                 |            |      |               | 23/7        | 22/6 | 21/5 | 20/4 | 19/3          | 18/2      | 17/1      | 16/0     | All Resets |

| 9260         EMAC1<br>SUPP         15:0           9270         EMAC1<br>TEST         31:16<br>15:0           9280         EMAC1<br>31:16         31:16                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 5:0 —<br>:16 —<br>5:0 —<br>:16 —     | -                                | _         |                                |                            | —          | _    |               |             |      |      |      |               |           |           |          |            |

| 9260         SUPP         15:0           9270         EMAC1<br>TEST         31:16<br>15:0           9280         EMAC1         31:16                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | :16 —<br>5:0 —<br>:16 —              | _                                |           | -                              |                            |            |      |               | _           | _    | —    |      | _             | _         | —         | _        | 0000       |

| 9270 TEST 15:0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 5:0 <u>—</u><br>:16 —                |                                  | —         |                                | RMII                       | —          | —    | SPEED<br>RMII | -           | -    | —    | -    | —             | -         | -         | _        | 1000       |

| EMAC1 31:16                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | :16 —                                | -                                |           | _                              | —                          | _          | _    | _             | _           | —    | _    | -    | —             | _         | _         |          | 0000       |