Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFI

| Details                    |                                                                                |

|----------------------------|--------------------------------------------------------------------------------|

| Product Status             | Active                                                                         |

| Core Processor             | MIPS32® M4K™                                                                   |

| Core Size                  | 32-Bit Single-Core                                                             |

| Speed                      | 80MHz                                                                          |

| Connectivity               | CANbus, Ethernet, I <sup>2</sup> C, SPI, UART/USART, USB OTG                   |

| Peripherals                | Brown-out Detect/Reset, DMA, POR, PWM, WDT                                     |

| Number of I/O              | -                                                                              |

| Program Memory Size        | 128KB (128K x 8)                                                               |

| Program Memory Type        | FLASH                                                                          |

| EEPROM Size                | -                                                                              |

| RAM Size                   | 32K x 8                                                                        |

| Voltage - Supply (Vcc/Vdd) | 2.3V ~ 3.6V                                                                    |

| Data Converters            | A/D 16x10b                                                                     |

| Oscillator Type            | Internal                                                                       |

| Operating Temperature      | -40°C ~ 105°C (TA)                                                             |

| Mounting Type              | Surface Mount                                                                  |

| Package / Case             | 121-TFBGA                                                                      |

| Supplier Device Package    | 121-TFBGA (10x10)                                                              |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic32mx764f128l-v-bg |

|                            |                                                                                |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

### REGISTER 7-6: IPCx: INTERRUPT PRIORITY CONTROL REGISTER

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|

| 31:24        | U-0               | U-0               | U-0               | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |

| 31.24        |                   | —                 | —                 |                   | IP03<2:0>         |                   | IS03             | <1:0>            |

| 23:16        | U-0               | U-0               | U-0               | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |

| 23.10        |                   | —                 | —                 |                   | IP02<2:0>         |                   | IS02-            | <1:0>            |

| 15:8         | U-0               | U-0               | U-0               | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |

| 15.0         |                   | —                 | —                 |                   | IP01<2:0>         | IS01-             | <1:0>            |                  |

| 7:0          | U-0               | U-0               | U-0               | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |

| 7.0          |                   | _                 |                   |                   | IP00<2:0>         |                   | IS00-            | <1:0>            |

### Legend:

| 3                 |                  |                           |                    |

|-------------------|------------------|---------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, re | ead as '0'         |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared      | x = Bit is unknown |

### bit 31-29 Unimplemented: Read as '0'

| bit 28-26 | IP03<2:0>: Interrupt Priority bits                                   |

|-----------|----------------------------------------------------------------------|

|           | 111 = Interrupt priority is 7                                        |

|           | •                                                                    |

|           | •                                                                    |

|           | •<br>010 = Interrupt priority is 2                                   |

|           | 010 = Interrupt priority is 2<br>001 = Interrupt priority is 1       |

|           | 000 = Interrupt is disabled                                          |

| bit 25-24 | <b>IS03&lt;1:0&gt;:</b> Interrupt Sub-priority bits                  |

|           | 11 = Interrupt sub-priority is 3                                     |

|           | 10 = Interrupt sub-priority is 2                                     |

|           | 01 = Interrupt sub-priority is 1                                     |

|           | 00 = Interrupt sub-priority is 0                                     |

| bit 23-21 | Unimplemented: Read as '0'                                           |

| bit 20-18 | IP02<2:0>: Interrupt Priority bits                                   |

|           | 111 = Interrupt priority is 7                                        |

|           | •                                                                    |

|           | •                                                                    |

|           | •                                                                    |

|           | 010 = Interrupt priority is 2                                        |

|           | 001 = Interrupt priority is 1<br>000 = Interrupt is disabled         |

| hit 17 16 | •                                                                    |

| DIL 17-10 | <b>IS02&lt;1:0&gt;:</b> Interrupt Sub-priority bits                  |

|           | 11 = Interrupt sub-priority is 3                                     |

|           | 10 = Interrupt sub-priority is 2<br>01 = Interrupt sub-priority is 1 |

|           | 00 = Interrupt sub-priority is 0                                     |

| hit 15-13 | Unimplemented: Read as '0'                                           |

| 511 10 10 | Chimpionionicu. Nodu do 0                                            |

| Note:     | This register represents a generic definition                        |

| 1         | · · · ·                                                              |

definitions.

ister represents a generic definition of the IPCx register. Refer to Table 7-1 for the exact bit ns.

### 11.0 USB ON-THE-GO (OTG)

Note: This data sheet summarizes the features of the PIC32MX5XX/6XX/7XX family of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to Section 27. "USB On-The-Go (OTG)" (DS60001126) in the "PIC32 Family Reference Manual", which is available from the Microchip web site (www.microchip.com/PIC32).

The Universal Serial Bus (USB) module contains analog and digital components to provide a USB 2.0 full-speed and low-speed embedded Host, full-speed Device or OTG implementation with a minimum of external components. This module in Host mode is intended for use as an embedded host and therefore does not implement a UHCI or OHCI controller.

The USB module consists of the clock generator, the USB voltage comparators, the transceiver, the Serial Interface Engine (SIE), a dedicated USB DMA controller, pull-up and pull-down resistors, and the register interface. A block diagram of the PIC32 USB OTG module is presented in Figure 11-1.

The clock generator provides the 48 MHz clock required for USB full-speed and low-speed communication. The voltage comparators monitor the voltage on the VBUS pin to determine the state of the bus. The transceiver provides the analog translation between the USB bus and the digital logic. The SIE is a state machine that transfers data to and from the endpoint buffers and generates the hardware protocol for data transfers. The USB DMA controller transfers data between the data buffers in RAM and the SIE. The integrated pull-up and pull-down resistors eliminate the need for external signaling components. The register interface allows the CPU to configure and communicate with the module.

The USB module includes the following features:

- USB Full-speed support for host and device

- Low-speed host support

- USB OTG support

- Integrated signaling resistors

- Integrated analog comparators for VBUS monitoring

- Integrated USB transceiver

- Transaction handshaking performed by hardware

- Endpoint buffering anywhere in system RAM

- Integrated DMA to access system RAM and Flash

- The implementation and use of the USB Note: specifications, as well as other third party may specifications or technologies, require licensing; including, but not limited to, USB Implementers Forum, Inc. (also referred to as USB-IF). The user is fully responsible for investigating and satisfying any applicable licensing obligations.

### TABLE 11-1: USB REGISTER MAP (CONTINUED)

| ess                         |                                 |           |       |       | · · · |       |       |       |      |      | Bits  |          |       |          |        |        |           |          |            |

|-----------------------------|---------------------------------|-----------|-------|-------|-------|-------|-------|-------|------|------|-------|----------|-------|----------|--------|--------|-----------|----------|------------|

| Virtual Address<br>(BF88_#) | Register<br>Name <sup>(1)</sup> | Bit Range | 31/15 | 30/14 | 29/13 | 28/12 | 27/11 | 26/10 | 25/9 | 24/8 | 23/7  | 22/6     | 21/5  | 20/4     | 19/3   | 18/2   | 17/1      | 16/0     | All Resets |

| 5280                        | U1FRML <sup>(3)</sup>           | 31:16     |       | —     | —     | —     | —     | —     | —    | —    | _     | —        | _     | —        | —      | —      | _         | _        | 0000       |

| 5200                        | OTTRIME                         | 15:0      | —     | _     | —     | —     | —     | —     | —    | —    |       |          |       | FRML<    | 7:0>   |        |           |          | 0000       |

| 5290                        | U1FRMH <sup>(3)</sup>           | 31:16     | —     | —     | —     | —     | —     | —     | —    | —    | —     | —        | —     | —        | —      | —      | —         | —        | 0000       |

| 0200                        | 01110                           | 15:0      | —     | —     | —     | —     | —     | —     | —    | —    | _     | —        | _     | -        | —      |        | FRMH<2:0> | •        | 0000       |

| 52A0                        | U1TOK                           | 31:16     | —     | —     | —     | —     | —     | —     | —    | —    | —     | —        | —     | —        | —      | —      | —         | —        | 0000       |

| 02/10                       | orron                           | 15:0      | —     | —     | —     | —     | —     | —     | —    | —    |       | PID      | <3:0> |          |        | EP     | <3:0>     |          | 0000       |

| 52B0                        | U1SOF                           | 31:16     | —     | —     | —     | —     | —     | —     | —    | —    | _     | —        | _     | —        | —      | —      | _         | —        | 0000       |

| 5260                        | 0130F                           | 15:0      | —     | _     | _     | —     | _     | _     | _    |      |       |          |       | CNT<7    | 7:0>   |        |           |          | 0000       |

| 52C0                        | U1BDTP2                         | 31:16     | —     | -     | —     | —     | _     | _     | -    |      | —     | —        |       | —        | —      | _      |           | _        | 0000       |

| 5200                        | OIBDIF2                         | 15:0      | —     | —     | —     | —     | —     | —     | —    | —    |       |          |       | BDTPTRH  | H<7:0> |        |           |          | 0000       |

| 52D0                        | U1BDTP3                         | 31:16     | —     | _     | _     | —     | _     | _     | _    |      | —     | _        |       | —        | _      | _      |           | _        | 0000       |

| 5200                        | UIBDIF3                         | 15:0      | —     | _     | _     | _     | _     | _     | -    |      |       |          |       | BDTPTRU  | J<7:0> |        |           |          | 0000       |

| 52E0                        | U1CNFG1                         | 31:16     | —     | _     | _     | —     | _     | _     | _    |      | —     | _        |       | —        | _      | _      |           | _        | 0000       |

| 52E0                        | UTCINFGT                        | 15:0      | —     | _     | _     | —     | _     | _     | _    |      | UTEYE | UOEMON   |       | USBSIDL  | —      | _      |           | UASUSPND | 0001       |

| 5300                        | U1EP0                           | 31:16     | —     | _     | _     | _     | _     | _     | -    |      | —     | _        |       | —        | _      | _      |           | _        | 0000       |

| 5300                        | UIEPU                           | 15:0      | —     | _     | _     | —     | _     | _     | _    |      | LSPD  | RETRYDIS |       | EPCONDIS | EPRXEN | EPTXEN | EPSTALL   | EPHSHK   | 0000       |

| 5310                        | U1EP1                           | 31:16     | —     | _     | _     | —     | _     | _     | _    |      | —     | _        |       | —        | _      | _      |           | _        | 0000       |

| 5310                        | UIEPI                           | 15:0      | —     | _     | _     | _     | _     | _     | _    | _    | —     | _        | -     | EPCONDIS | EPRXEN | EPTXEN | EPSTALL   | EPHSHK   | 0000       |

| 5320                        | U1EP2                           | 31:16     | —     | _     | _     | —     | _     | _     | _    |      | —     | _        |       | —        | _      | _      |           | _        | 0000       |

| 5520                        | UIEFZ                           | 15:0      | _     | _     | _     | _     | _     | _     | _    |      | —     | _        | -     | EPCONDIS | EPRXEN | EPTXEN | EPSTALL   | EPHSHK   | 0000       |

| 5330                        | U1EP3                           | 31:16     | —     | _     | _     | _     | _     | _     | _    | _    | —     | _        | -     | —        | _      | -      |           | _        | 0000       |

| 5330                        | UIEP3                           | 15:0      | —     | _     | _     | —     | _     | _     | _    |      | —     | _        |       | EPCONDIS | EPRXEN | EPTXEN | EPSTALL   | EPHSHK   | 0000       |

| 5340                        | U1EP4                           | 31:16     | _     | _     | -     | -     | -     | -     | -    | _    | _     | _        | _     | —        | -      | _      | _         | _        | 0000       |

| 5540                        | UTEP4                           | 15:0      | —     | _     | _     | _     | _     | _     | _    | _    | —     | _        | -     | EPCONDIS | EPRXEN | EPTXEN | EPSTALL   | EPHSHK   | 0000       |

| 5350                        | U1EP5                           | 31:16     | _     | _     | -     | -     | -     | -     | -    | _    | _     | _        | _     | —        | -      | _      | _         | _        | 0000       |

| 5350                        | UIEP5                           | 15:0      | _     | _     | -     | -     | -     | -     | -    | _    | _     | _        | _     | EPCONDIS | EPRXEN | EPTXEN | EPSTALL   | EPHSHK   | 0000       |

| 5260                        | U1EP6                           | 31:16     |       |       | _     | —     | _     |       | _    | _    | —     |          |       | —        | _      | —      |           |          | 0000       |

| 5360                        | UIEP6                           | 15:0      | _     | _     | -     | -     | -     | -     | -    | _    | _     | _        | _     | EPCONDIS | EPRXEN | EPTXEN | EPSTALL   | EPHSHK   | 0000       |

| 5270                        | U1EP7                           | 31:16     | _     | _     | _     | _     | _     | _     | _    | —    | _     | _        | _     | —        | _      | _      | -         | _        | 0000       |

| 5370                        | UTEPT                           | 15:0      |       |       | _     | _     | _     |       | _    | _    | —     |          |       | EPCONDIS | EPRXEN | EPTXEN | EPSTALL   | EPHSHK   | 0000       |

| 5200                        |                                 | 31:16     | _     | _     | _     | _     | _     | _     | _    | —    | -     | —        | _     | —        | _      | —      | _         | _        | 0000       |

| 5380                        | U1EP8                           | 15:0      | —     | _     | —     | —     | _     | —     | —    | _    | _     | _        | -     | EPCONDIS | EPRXEN | EPTXEN | EPSTALL   | EPHSHK   | 0000       |

| 5000                        |                                 | 31:16     | _     | —     | _     | _     | _     | _     | _    | —    | _     | —        | _     | —        | —      | —      | —         | —        | 0000       |

| 5390                        | U1EP9                           | 15:0      | _     | —     | _     | _     | _     | _     | _    | _    | _     | _        | _     | EPCONDIS | EPRXEN | EPTXEN | EPSTALL   | EPHSHK   | 0000       |

5390

U1EP9

Legend:

x =

Note

1:

All n

end: x = unknown value on Reset; — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

1: All registers in this table (except as noted) have corresponding CLR, SET and INV registers at its virtual address, plus an offset of 0x4, 0x8 and 0xC respectively. See Section 12.1.1 "CLR, SET and INV Registers" for more information.

2: This register does not have associated SET and INV registers.

3: This register does not have associated CLR, SET and INV registers.

4: Reset value for this bit is undefined.

### REGISTER 11-11: U1CON: USB CONTROL REGISTER (CONTINUED)

- bit 1 **PPBRST:** Ping-Pong Buffers Reset bit

- 1 = Reset all Even/Odd buffer pointers to the Even buffer descriptor banks

- 0 = Even/Odd buffer pointers are not reset

- bit 0 USBEN: USB Module Enable bit<sup>(4)</sup>

- 1 = USB module and supporting circuitry is enabled

- 0 = USB module and supporting circuitry is disabled

SOFEN: SOF Enable bit(5)

- 1 = SOF token is sent every 1 ms

- 0 = SOF token is disabled

- **Note 1:** Software is required to check this bit before issuing another token command to the U1TOK register (see Register 11-15).

- 2: All host control logic is reset any time that the value of this bit is toggled.

- **3:** Software must set RESUME for 10 ms in Device mode, or for 25 ms in Host mode, and then clear it to enable remote wake-up. In Host mode, the USB module will append a low-speed EOP to the RESUME signaling when this bit is cleared.

- 4: Device mode.

- 5: Host mode.

# TABLE 12-9: PORTF REGISTER MAP FOR PIC32MX534F064H, PIC32MX564F064H, PIC32MX564F128H, PIC32MX575F512H, PIC32MX664F064H, PIC32MX664F128H, PIC32MX675F256H, PIC32MX675F512H, PIC32MX695F512H, PIC32MX775F512H, PIC32MX775F512H, PIC32MX775F512H, PIC32MX795F512H, DEVICES

| ess                         |                                 | e         |       |       |       |       |       |       |      | Bi   | its  |      |        |        |        |      |        |        |            |

|-----------------------------|---------------------------------|-----------|-------|-------|-------|-------|-------|-------|------|------|------|------|--------|--------|--------|------|--------|--------|------------|

| Virtual Address<br>(BF88_#) | Register<br>Name <sup>(1)</sup> | Bit Range | 31/15 | 30/14 | 29/13 | 28/12 | 27/11 | 26/10 | 25/9 | 24/8 | 23/7 | 22/6 | 21/5   | 20/4   | 19/3   | 18/2 | 17/1   | 16/0   | All Resets |

| 6140                        | TRISF                           | 31:16     | _     | —     | _     | —     | -     | —     | —    | —    | _    | —    | _      | —      | —      | _    | -      | —      | 0000       |

| 6140                        | IRIOF                           | 15:0      |       | _     | _     | _     | _     | _     | _    | _    | _    | _    | TRISF5 | TRISF4 | TRISF3 | _    | TRISF1 | TRISF0 | 003B       |

| 6150                        | PORTF                           | 31:16     | _     | _     |       | _     |       | _     |      |      |      |      | -      | _      | _      | _    |        | -      | 0000       |

| 6150                        | PURIF                           | 15:0      |       | -     | -     | —     | —     | —     | -    | -    | -    | -    | RF5    | RF4    | RF3    |      | RF1    | RF0    | xxxx       |

| 6160                        | LATF                            | 31:16     |       | _     | _     | _     | _     | _     | _    | _    | _    | _    | -      | _      | _      | _    | _      | _      | 0000       |

| 6160                        | LAIF                            | 15:0      | -     | _     | —     | _     | _     | _     | _    | _    | _    | _    | LATF5  | LATF4  | LATF3  | —    | LATF1  | LATF0  | xxxx       |

| 6170                        | ODCF                            | 31:16     |       | _     | _     | _     | _     | _     | _    | _    | _    | _    | -      | _      | _      | _    | _      | _      | 0000       |

| 0170                        | ODCF                            | 15:0      | _     | _     | _     |       | -     |       |      |      |      |      | ODCF5  | ODCF4  | ODCF3  |      | ODCF1  | ODCF0  | 0000       |

Legend: x = unknown value on Reset; - = unimplemented, read as '0'. Reset values are shown in hexadecimal.

Note 1: All registers in this table have corresponding CLR, SET and INV registers at their virtual addresses, plus offsets of 0x4, 0x8 and 0xC, respectively. See Section 12.1.1 "CLR, SET and INV Registers" for more information.

# TABLE 12-10: PORTF REGISTER MAP PIC32MX534F064L, PIC32MX564F064L, PIC32MX564F128L, PIC32MX575F256L, PIC32MX575F512L, PIC32MX664F064L, PIC32MX664F128L, PIC32MX675F256L, PIC32MX675F512L, PIC32MX775F512L, PIC32MX7

| ess                         |       | Ċ,        |       |       |         |         |       |       |      | Bi     | ts   |      |        |        |        |        |        |        | - y       |

|-----------------------------|-------|-----------|-------|-------|---------|---------|-------|-------|------|--------|------|------|--------|--------|--------|--------|--------|--------|-----------|

| Virtual Address<br>(BF88_#) |       | Bit Range | 31/15 | 30/14 | 29/13   | 28/12   | 27/11 | 26/10 | 25/9 | 24/8   | 23/7 | 22/6 | 21/5   | 20/4   | 19/3   | 18/2   | 17/1   | 16/0   | All Reset |

|                             | TDIOF | 31:16     | _     | _     | _       | _       | _     | _     | _    | _      | _    | _    | _      | _      | _      | _      | _      | _      | 0000      |

| 6140                        | IRISE | 15:0      | -     | _     | TRISF13 | TRISF12 | _     | _     | _    | TRISF8 | _    | _    | TRISF5 | TRISF4 | TRISF3 | TRISF2 | TRISF1 | TRISF0 | 313F      |

| 6150                        | PORTF | 31:16     | -     | _     | _       | _       | _     | -     | _    | _      | -    |      | -      |        | _      |        | _      | _      | 0000      |

| 0150                        | FUNIF | 15:0      | -     | —     | RF13    | RF12    | _     |       | _    | RF8    |      |      | RF5    | RF4    | RF3    | RF2    | RF1    | RF0    | xxxx      |

| 6160                        | LATF  | 31:16     | —     | —     | _       |         | —     | _     | _    |        | -    | _    | _      | _      | _      | _      | —      | —      | 0000      |

| 0100                        | LAIF  | 15:0      |       | —     | LATF13  | LATF12  |       | -     |      | LATF8  |      | -    | LATF5  | LATF4  | LATF3  | LATF2  | LATF1  | LATF0  | xxxx      |

| 6170                        | ODCF  | 31:16     | —     | _     | _       | —       | _     |       | _    |        |      |      | _      |        | —      |        | -      | -      | 0000      |

| 0170                        | ODCF  | 15:0      | _     | _     | ODCF13  | ODCF12  | _     | -     | —    | ODCF8  | _    | -    | ODCF5  | ODCF4  | ODCF3  | ODCF2  | ODCF1  | ODCF0  | 0000      |

Legend: x = unknown value on Reset; — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

Note 1: All registers in this table have corresponding CLR, SET and INV registers at their virtual addresses, plus offsets of 0x4, 0x8 and 0xC, respectively. See Section 12.1.1 "CLR, SET and INV Registers" for more information.

NOTES:

| Bit Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

|-----------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|

| 24.24     | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 31:24     | _                 | —                 |                   |                   | _                 |                   |                  |                  |

| 00.40     | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 23:16     | _                 | —                 | _                 | _                 | _                 | _                 | _                | _                |

| 45.0      | R/W-0             | U-0               | R/W-0             | U-0               | U-0               | U-0               | R/W-0            | R/W-0            |

| 15:8      | ON <sup>(1)</sup> | —                 | SIDL              | _                 | _                 | _                 | FEDGE            | C32              |

| 7.0       | R/W-0             | R/W-0             | R/W-0             | R-0               | R-0               | R/W-0             | R/W-0            | R/W-0            |

| 7:0       | ICTMR             | ICI<              | 1:0>              | ICOV              | ICBNE             |                   | ICM<2:0>         |                  |

### REGISTER 16-1: ICxCON: INPUT CAPTURE 'x' CONTROL REGISTER

### Legend:

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, | read as '0'        |

|-------------------|------------------|------------------------|--------------------|

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared   | x = Bit is unknown |

| bit 31-16 | Unimplemented: Read as '0'                                                                                                                                |

|-----------|-----------------------------------------------------------------------------------------------------------------------------------------------------------|

| bit 15    | ON: Input Capture Module Enable bit <sup>(1)</sup>                                                                                                        |

|           | <ul> <li>1 = Module is enabled</li> <li>0 = Disable and reset module, disable clocks, disable interrupt generation and allow SFR modifications</li> </ul> |

| bit 14    | Unimplemented: Read as '0'                                                                                                                                |

| bit 13    | SIDL: Stop in Idle Control bit                                                                                                                            |

|           | <ul><li>1 = Halt in Idle mode</li><li>0 = Continue to operate in Idle mode</li></ul>                                                                      |

| bit 12-10 | Unimplemented: Read as '0'                                                                                                                                |

| bit 9     | FEDGE: First Capture Edge Select bit (only used in mode 6, ICM<2:0> = 110)                                                                                |

|           | <ul> <li>1 = Capture rising edge first</li> <li>0 = Capture falling edge first</li> </ul>                                                                 |

| bit 8     | C32: 32-bit Capture Select bit                                                                                                                            |

|           | <ul><li>1 = 32-bit timer resource capture</li><li>0 = 16-bit timer resource capture</li></ul>                                                             |

| bit 7     | ICTMR: Timer Select bit (Does not affect timer selection when C32 (ICxCON<8>) is '1')                                                                     |

|           | <ul> <li>1 = Timer2 is the counter source for capture</li> <li>0 = Timer3 is the counter source for capture</li> </ul>                                    |

| bit 6-5   | ICI<1:0>: Interrupt Control bits                                                                                                                          |

|           | 11 = Interrupt on every fourth capture event                                                                                                              |

|           | <ul> <li>10 = Interrupt on every third capture event</li> <li>01 = Interrupt on every second capture event</li> </ul>                                     |

|           | 00 = Interrupt on every capture event                                                                                                                     |

| bit 4     | ICOV: Input Capture Overflow Status Flag bit (read-only)                                                                                                  |

|           | <ul> <li>1 = Input capture overflow is occurred</li> <li>0 = No input capture overflow is occurred</li> </ul>                                             |

| bit 3     | ICBNE: Input Capture Buffer Not Empty Status bit (read-only)                                                                                              |

|           | <ul> <li>1 = Input capture buffer is not empty; at least one more capture value can be read</li> <li>0 = Input capture buffer is empty</li> </ul>         |

|           |                                                                                                                                                           |

**Note 1:** When using the 1:1 PBCLK divisor, the user's software should not read/write the peripheral's SFRs in the SYSCLK cycle immediately following the instruction that clears the module's ON bit.

NOTES:

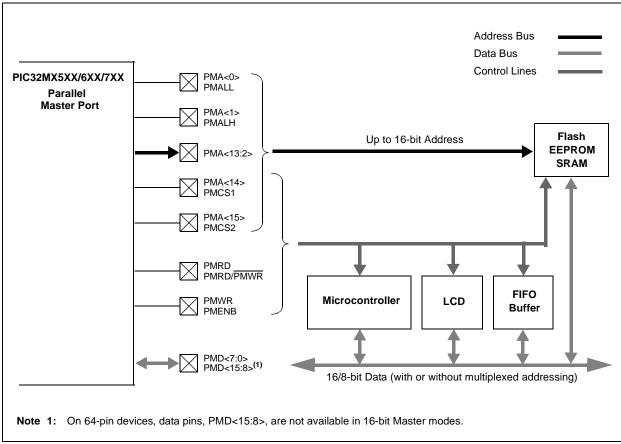

#### 21.0 PARALLEL MASTER PORT (PMP)

Note: This data sheet summarizes the features of the PIC32MX5XX/6XX/7XX family of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to Section 13. "Parallel Master Port (PMP)" (DS60001128) in the "PIC32 Family Reference Manual", which is available from the Microchip web site (www.microchip.com/PIC32).

The PMP is a parallel 8-bit/16-bit input/output module specifically designed to communicate with a wide variety of parallel devices, such as communications peripherals, LCDs, external memory devices and microcontrollers. Because the interface to parallel peripherals varies significantly, the PMP module is highly configurable. Figure 21-1 shows the PMP module pinout and its connections to external devices.

**FIGURE 21-1:**

The following are key features of the PMP module:

- 8-bit and 16-bit interface

- Up to 16 programmable address lines

- Up to two Chip Select lines

- Programmable strobe options

- Individual read and write strobes, or

- Read/Write strobe with enable strobe

- · Address auto-increment/auto-decrement

- · Programmable address/data multiplexing

- Programmable polarity on control signals

- · Parallel Slave Port support

- Legacy addressable

- Address support

- 4-byte deep auto-incrementing buffer

- · Programmable wait states

- · Operates during Sleep and Idle modes

- Fast bit manipulation using CLR, SET and INV registers

Note: On 64-pin devices, the PMD<15:8> data pins are not available.

PMP MODULE PINOUT AND CONNECTIONS TO EXTERNAL DEVICES

### REGISTER 23-1: AD1CON1: ADC CONTROL REGISTER 1 (CONTINUED)

- bit 4 **CLRASAM:** Stop Conversion Sequence bit (when the first ADC interrupt is generated)

- 1 = Stop conversions when the first ADC interrupt is generated. Hardware clears the ASAM bit when the ADC interrupt is generated.

- 0 = Normal operation, buffer contents will be overwritten by the next conversion sequence

- bit 3 Unimplemented: Read as '0'

- bit 2 ASAM: ADC Sample Auto-Start bit

- 1 = Sampling begins immediately after last conversion completes; SAMP bit is automatically set

- 0 = Sampling begins when SAMP bit is set

- bit 1 SAMP: ADC Sample Enable bit<sup>(2)</sup>

- 1 = The ADC S&H circuit is sampling

- 0 = The ADC S&H circuit is holding

- When ASAM = 0, writing '1' to this bit starts sampling.

- When SSRC < 2:0 > = 000, writing '0' to this bit will end sampling and start conversion.

### bit 0 **DONE:** Analog-to-Digital Conversion Status bit<sup>(3)</sup>

- Clearing this bit will not affect any operation in progress.

- 1 = Analog-to-digital conversion is done

- 0 = Analog-to-digital conversion is not done or has not started

- **Note 1:** When using the 1:1 PBCLK divisor, the user's software should not read/write the peripheral's SFRs in the SYSCLK cycle immediately following the instruction that clears the module's ON bit.

- 2: If ASAM = 0, software can write a '1' to start sampling. This bit is automatically set by hardware if ASAM = 1. If SSRC<2:0> = 000, software can write a '0' to end sampling and start conversion. If SSRC<2:0> ≠ '000', this bit is automatically cleared by hardware to end sampling and start conversion.

- **3:** This bit is automatically set by hardware when analog-to-digital conversion is complete. Software can write a '0' to clear this bit (a write of '1' is not allowed). Clearing this bit does not affect any operation already in progress. This bit is automatically cleared by hardware at the start of a new conversion.

### REGISTER 24-12: CIFLTCON2: CAN FILTER CONTROL REGISTER 2 (CONTINUED)

| bit 15    | FLTEN9: Filter 9 Enable bit<br>1 = Filter is enabled<br>0 = Filter is disabled                                                                                                                                                                                                            |

|-----------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| bit 14-13 | MSEL9<1:0>: Filter 9 Mask Select bits<br>11 = Acceptance Mask 3 selected<br>10 = Acceptance Mask 2 selected<br>01 = Acceptance Mask 1 selected<br>00 = Acceptance Mask 0 selected                                                                                                         |

| bit 12-8  | FSEL9<4:0>: FIFO Selection bits<br>11111 = Message matching filter is stored in FIFO buffer 31<br>11110 = Message matching filter is stored in FIFO buffer 30<br>•                                                                                                                        |

|           | 00001 = Message matching filter is stored in FIFO buffer 1<br>00000 = Message matching filter is stored in FIFO buffer 0                                                                                                                                                                  |

| bit 7     | FLTEN8: Filter 8 Enable bit<br>1 = Filter is enabled<br>0 = Filter is disabled                                                                                                                                                                                                            |

| bit 6-5   | MSEL8<1:0>: Filter 8 Mask Select bits<br>11 = Acceptance Mask 3 selected<br>10 = Acceptance Mask 2 selected<br>01 = Acceptance Mask 1 selected<br>00 = Acceptance Mask 0 selected                                                                                                         |

| bit 4-0   | FSEL8<4:0>: FIFO Selection bits<br>11111 = Message matching filter is stored in FIFO buffer 31<br>11110 = Message matching filter is stored in FIFO buffer 30<br>00001 = Message matching filter is stored in FIFO buffer 1<br>00000 = Message matching filter is stored in FIFO buffer 0 |

| r         |                                                                                                                                                                                                                                                                                           |

Note: The bits in this register can only be modified if the corresponding filter enable (FLTENn) bit is '0'.

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |  |  |  |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|--|--|--|--|

| 31:24        | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |  |  |

| 31.24        |                   |                   |                   | HT<3              | 1:24>             |                   |                  |                  |  |  |  |  |

| 22.10        | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |  |  |

| 23:16        | HT<23:16>         |                   |                   |                   |                   |                   |                  |                  |  |  |  |  |

| 45.0         | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |  |  |

| 15:8         |                   |                   |                   | HT<1              | 5:8>              |                   |                  |                  |  |  |  |  |

| 7.0          | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |  |  |

| 7:0          | HT<7:0>           |                   |                   |                   |                   |                   |                  |                  |  |  |  |  |

### REGISTER 25-5: ETHHT0: ETHERNET CONTROLLER HASH TABLE 0 REGISTER

| Legend:           |                  |                           |                    |

|-------------------|------------------|---------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, re | ead as '0'         |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared      | x = Bit is unknown |

bit 31-0 HT<31:0>: Hash Table Bytes 0-3 bits

Note 1: This register is only used for RX operations.

2: The bits in this register may only be changed while the RXEN bit (ETHCON1<8>) = 0 or the HTEN bit (ETHRXFC<15>) = 0.

### REGISTER 25-6: ETHHT1: ETHERNET CONTROLLER HASH TABLE 1 REGISTER

| Bit Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |  |  |

|-----------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|--|--|--|

| 04.04     | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |  |

| 31:24     |                   |                   |                   | HT<6              | 3:56>             |                   |                  |                  |  |  |  |

| 00.40     | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |  |

| 23:16     | HT<55:48>         |                   |                   |                   |                   |                   |                  |                  |  |  |  |

| 45.0      | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |  |

| 15:8      |                   |                   |                   | HT<4              | 7:40>             |                   |                  |                  |  |  |  |

| 7:0       | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |  |

|           |                   | HT<39:32>         |                   |                   |                   |                   |                  |                  |  |  |  |

| Legend:           |                  |                          |                    |

|-------------------|------------------|--------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, I | ead as '0'         |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared     | x = Bit is unknown |

### bit 31-0 HT<63:32>: Hash Table Bytes 4-7 bits

Note 1: This register is only used for RX operations.

2: The bits in this register may only be changed while the RXEN bit (ETHCON1<8>) = 0 or the HTEN bit (ETHRXFC<15>) = 0.

| Bit Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |  |

|-----------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|--|--|

| 31:24     | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |  |  |

| 31.24     | —                 | —                 |                   | —                 |                   | —                 |                  | _                |  |  |

| 23:16     | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |

| 23.10     | RXFWM<7:0>        |                   |                   |                   |                   |                   |                  |                  |  |  |

| 15:8      | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |  |  |

| 15.0      | —                 | —                 |                   | —                 |                   | —                 |                  | _                |  |  |

| 7:0       | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |

| 7.0       |                   |                   |                   | RXEW              | M<7:0>            |                   |                  |                  |  |  |

### REGISTER 25-12: ETHRXWM: ETHERNET CONTROLLER RECEIVE WATERMARKS REGISTER

### Legend:

| Legena.           |                  |                        |                    |

|-------------------|------------------|------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, | read as '0'        |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared   | x = Bit is unknown |

- bit 31-24 Unimplemented: Read as '0'

- bit 23-16 **RXFWM<7:0>:** Receive Full Watermark bits

The software controlled RX Buffer Full Watermark Pointer is compared against the RX BUFCNT to determine the full watermark condition for the FWMARK interrupt and for enabling Flow Control when automatic Flow Control is enabled. The Full Watermark Pointer should always be greater than the Empty Watermark Pointer.

- bit 15-8 Unimplemented: Read as '0'

- bit 7-0 **RXEWM<7:0>:** Receive Empty Watermark bits

The software controlled RX Buffer Empty Watermark Pointer is compared against the RX BUFCNT to determine the empty watermark condition for the EWMARK interrupt and for disabling Flow Control when automatic Flow Control is enabled. The Empty Watermark Pointer should always be less than the Full Watermark Pointer.

Note: This register is only used for RX operations.

### **30.0 INSTRUCTION SET**

The PIC32MX5XX/6XX/7XX family instruction set complies with the MIPS32 Release 2 instruction set architecture. The PIC32 device family does not support the following features:

- Core Extend instructions

- Coprocessor 1 instructions

- Coprocessor 2 instructions

Note: Refer to "MIPS32<sup>®</sup> Architecture for Programmers Volume II: The MIPS32<sup>®</sup> Instruction Set" at www.imgtec.com for more information.

### TABLE 32-4: DC TEMPERATURE AND VOLTAGE SPECIFICATIONS

| DC CHA                               | RACTER    | ISTICS                                                        | $\begin{tabular}{lllllllllllllllllllllllllllllllllll$ |         |       |       |            |

|--------------------------------------|-----------|---------------------------------------------------------------|-------------------------------------------------------|---------|-------|-------|------------|

| Param.<br>No. Symbol Characteristics |           |                                                               | Min.                                                  | Typical | Max.  | Units | Conditions |

| Operati                              | ng Voltag | e                                                             |                                                       |         |       |       |            |

| DC10                                 | Vdd       | Supply Voltage                                                | 2.3                                                   |         | 3.6   | V     |            |

| DC12                                 | Vdr       | RAM Data Retention Voltage <sup>(1)</sup>                     | 1.75                                                  |         |       | V     |            |

| DC16                                 | VPOR      | VDD Start Voltage to Ensure<br>Internal Power-on Reset Signal | 1.75                                                  |         | 2.1   | V     |            |

| DC17                                 | SVDD      | VDD Rise Rate to Ensure<br>Internal Power-on Reset Signal     | 0.00005                                               |         | 0.115 | V/µs  | —          |

**Note 1:** This is the limit to which VDD can be lowered without losing RAM data.

2: Overall functional device operation at VBORMIN < VDD < VDDMIN is tested, but not characterized. All device Analog modules, such as ADC, etc., will function, but with degraded performance below VDDMIN. Refer to parameter BO10 in Table 32-10 for BOR values.

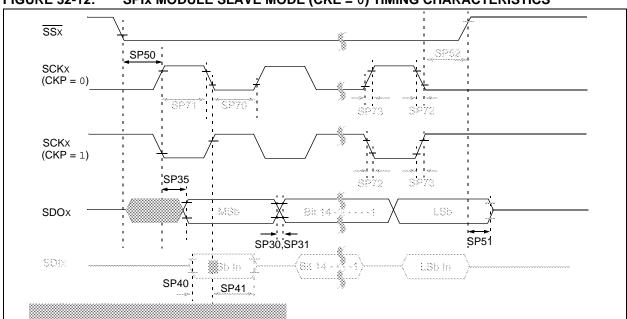

#### FIGURE 32-12: SPIX MODULE SLAVE MODE (CKE = 0) TIMING CHARACTERISTICS

### TABLE 32-30: SPIX MODULE SLAVE MODE (CKE = 0) TIMING REQUIREMENTS

| АС СНА        | ARACTERIS             | Standard<br>(unless o<br>Operating                                 | therwise  | e stated            | <b>)</b><br>40°C ≤ T | <b>2.3V to 3.6V</b><br>$TA \le +85^{\circ}C$ for Industrial $TA \le +105^{\circ}C$ for V-Temp |                    |

|---------------|-----------------------|--------------------------------------------------------------------|-----------|---------------------|----------------------|-----------------------------------------------------------------------------------------------|--------------------|

| Param.<br>No. | Symbol                | Characteristics <sup>(1)</sup>                                     | Min.      | Тур. <sup>(2)</sup> | Max.                 | Units                                                                                         | Conditions         |

| SP70          | TscL                  | SCKx Input Low Time <sup>(3)</sup>                                 | Тѕск/2    | _                   |                      | ns                                                                                            | —                  |

| SP71          | TscH                  | SCKx Input High Time <sup>(3)</sup>                                | Tsck/2    | _                   |                      | ns                                                                                            | —                  |

| SP72          | TscF                  | SCKx Input Fall Time                                               | —         | —                   | _                    | ns                                                                                            | See parameter DO32 |

| SP73          | TscR                  | SCKx Input Rise Time                                               | —         | —                   | _                    | ns                                                                                            | See parameter DO31 |

| SP30          | TDOF                  | SDOx Data Output Fall Time <sup>(4)</sup>                          | —         | _                   | _                    | ns                                                                                            | See parameter DO32 |

| SP31          | TdoR                  | SDOx Data Output Rise Time <sup>(4)</sup>                          | —         | _                   | _                    | ns                                                                                            | See parameter DO31 |

| SP35          | TscH2doV,             | SDOx Data Output Valid after                                       | —         | —                   | 15                   | ns                                                                                            | VDD > 2.7V         |

|               | TscL2doV              | SCKx Edge                                                          | —         | _                   | 20                   | ns                                                                                            | VDD < 2.7V         |

| SP40          | TDIV2SCH,<br>TDIV2SCL | Setup Time of SDIx Data Input to SCKx Edge                         | 10        |                     |                      | ns                                                                                            | —                  |

| SP41          | TscH2diL,<br>TscL2diL | Hold Time of SDIx Data Input to SCKx Edge                          | 10        | —                   | _                    | ns                                                                                            | _                  |

| SP50          | TssL2scH,<br>TssL2scL | $\overline{\text{SSx}}\downarrow$ to SCKx $\uparrow$ or SCKx Input | 175       |                     |                      | ns                                                                                            | —                  |

| SP51          | TssH2doZ              | SSx ↑ to SDOx Output<br>High-Impedance <sup>(3)</sup>              | 5         | —                   | 25                   | ns                                                                                            | —                  |

| SP52          | TscH2ssH<br>TscL2ssH  | SSx after SCKx Edge                                                | Тѕск + 20 | _                   | _                    | ns                                                                                            | —                  |

Note 1: These parameters are characterized, but not tested in manufacturing.

2: Data in "Typical" column is at 3.3V, 25°C unless otherwise stated. Parameters are for design guidance only and are not tested.

**3:** The minimum clock period for SCKx is 40 ns.

4: Assumes 50 pF load on all SPIx pins.

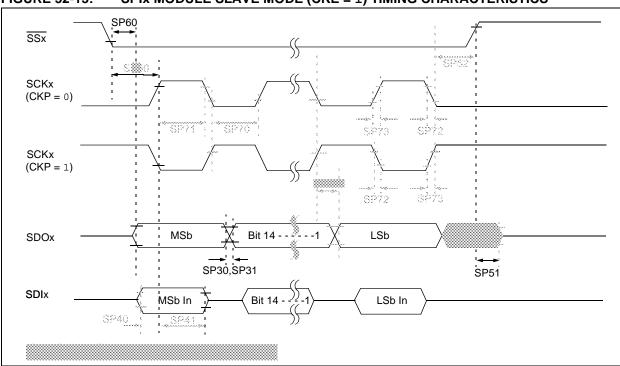

### FIGURE 32-13: SPIX MODULE SLAVE MODE (CKE = 1) TIMING CHARACTERISTICS

### TABLE 32-31: SPIX MODULE SLAVE MODE (CKE = 1) TIMING REQUIREMENTS

| AC CHA        |                       | (unless o                                                                 | d Operating<br>otherwise st<br>g temperatur | t <b>ated)</b><br>e -40° | °C ≤ TA ≤ | <b>3V to 3.6V</b><br>≤ +85°C for Industrial<br>≤ +105°C for V-Temp |                    |

|---------------|-----------------------|---------------------------------------------------------------------------|---------------------------------------------|--------------------------|-----------|--------------------------------------------------------------------|--------------------|

| Param.<br>No. | Symbol                | Characteristics <sup>(1)</sup>                                            | Min.                                        | Typical <sup>(2)</sup>   | Max.      | Units                                                              | Conditions         |

| SP70          | TscL                  | SCKx Input Low Time <sup>(3)</sup>                                        | Tsck/2                                      |                          | —         | ns                                                                 | —                  |

| SP71          | TscH                  | SCKx Input High Time <sup>(3)</sup>                                       | Tsck/2                                      | —                        | _         | ns                                                                 | —                  |

| SP72          | TscF                  | SCKx Input Fall Time                                                      | _                                           | 5                        | 10        | ns                                                                 | —                  |

| SP73          | TscR                  | SCKx Input Rise Time                                                      |                                             | 5                        | 10        | ns                                                                 | —                  |

| SP30          | TDOF                  | SDOx Data Output Fall Time <sup>(4)</sup>                                 | —                                           | —                        | _         | ns                                                                 | See parameter DO32 |

| SP31          | TDOR                  | SDOx Data Output Rise Time <sup>(4)</sup>                                 |                                             | —                        | _         | ns                                                                 | See parameter DO31 |

| SP35          | TscH2doV,             | SDOx Data Output Valid after                                              |                                             | _                        | 20        | ns                                                                 | VDD > 2.7V         |

|               | TscL2doV              | SCKx Edge                                                                 |                                             | _                        | 30        | ns                                                                 | VDD < 2.7V         |

| SP40          | TDIV2SCH,<br>TDIV2SCL | Setup Time of SDIx Data Input to SCKx Edge                                | 10                                          | —                        | —         | ns                                                                 | —                  |

| SP41          | TscH2diL,<br>TscL2diL | Hold Time of SDIx Data Input to SCKx Edge                                 | 10                                          | —                        | —         | ns                                                                 | —                  |

| SP50          | TssL2scH,<br>TssL2scL | $\overline{SSx} \downarrow$ to SCKx $\downarrow$ or SCKx $\uparrow$ Input | 175                                         | —                        | —         | ns                                                                 | —                  |

Note 1: These parameters are characterized, but not tested in manufacturing.

2: Data in "Typical" column is at 3.3V, 25°C unless otherwise stated. Parameters are for design guidance only and are not tested.

- 3: The minimum clock period for SCKx is 40 ns.

- 4: Assumes 50 pF load on all SPIx pins.

### TABLE 32-31: SPIX MODULE SLAVE MODE (CKE = 1) TIMING REQUIREMENTS (CONTINUED)

| AC CHA        | RACTERIS             | ΓΙCS                                                  | $\begin{array}{l} \mbox{Standard Operating Conditions: 2.3V to 3.6V} \\ \mbox{(unless otherwise stated)} \\ \mbox{Operating temperature} & -40^{\circ}C \leq TA \leq +85^{\circ}C \mbox{ for Industri} \\ & -40^{\circ}C \leq TA \leq +105^{\circ}C \mbox{ for V-Temperature} \\ \end{array}$ |                        |      | ≤ +85°C for Industrial |            |

|---------------|----------------------|-------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------|------|------------------------|------------|

| Param.<br>No. | Symbol               | Characteristics <sup>(1)</sup>                        | Min.                                                                                                                                                                                                                                                                                          | Typical <sup>(2)</sup> | Max. | Units                  | Conditions |

| SP51          | TssH2doZ             | SSx ↑ to SDOx Output<br>High-Impedance <sup>(4)</sup> | 5                                                                                                                                                                                                                                                                                             | _                      | 25   | ns                     | _          |

| SP52          | TscH2ssH<br>TscL2ssH | SSx ↑ after SCKx Edge                                 | Тscк +<br>20                                                                                                                                                                                                                                                                                  | —                      | _    | ns                     | _          |

| SP60          | TssL2doV             | SDOx Data Output Valid after<br>SSx Edge              | —                                                                                                                                                                                                                                                                                             | —                      | 25   | ns                     | —          |

**Note 1:** These parameters are characterized, but not tested in manufacturing.

2: Data in "Typical" column is at 3.3V, 25°C unless otherwise stated. Parameters are for design guidance only and are not tested.

3: The minimum clock period for SCKx is 40 ns.

4: Assumes 50 pF load on all SPIx pins.

### TABLE 32-32: I2Cx BUS DATA TIMING REQUIREMENTS (MASTER MODE)

| АС СНА        | RACTERI | STICS              |                           | $\begin{tabular}{lllllllllllllllllllllllllllllllllll$ |          |       |                         |  |

|---------------|---------|--------------------|---------------------------|-------------------------------------------------------|----------|-------|-------------------------|--|

| Param.<br>No. | Symbol  | Charact            | eristics                  | Min. <sup>(1)</sup>                                   | Max.     | Units | Conditions              |  |

| IM10          | TLO:SCL | Clock Low Time     | 100 kHz mode              | Трв * (BRG + 2)                                       | —        | μS    | _                       |  |

|               |         |                    | 400 kHz mode              | Трв * (BRG + 2)                                       | _        | μS    | _                       |  |

|               |         |                    | 1 MHz mode <sup>(2)</sup> | Tpb * (BRG + 2)                                       | —        | μS    | _                       |  |

| IM11          | THI:SCL | Clock High Time    | 100 kHz mode              | Трв * (BRG + 2)                                       | —        | μS    | _                       |  |

|               |         |                    | 400 kHz mode              | Tpb * (BRG + 2)                                       | —        | μS    | _                       |  |

|               |         |                    | 1 MHz mode <sup>(2)</sup> | Трв * (BRG + 2)                                       | _        | μS    | _                       |  |

| IM20          | TF:SCL  | SDAx and SCLx      | 100 kHz mode              | —                                                     | 300      | ns    | CB is specified to be   |  |

|               |         | Fall Time          | 400 kHz mode              | 20 + 0.1 Св                                           | 300      | ns    | from 10 to 400 pF       |  |

|               |         |                    | 1 MHz mode <sup>(2)</sup> | —                                                     | 100      | ns    |                         |  |

| IM21          | TR:SCL  | SDAx and SCLx      | 100 kHz mode              | _                                                     | 1000     | ns    | CB is specified to be   |  |

|               |         | Rise Time          | 400 kHz mode              | 20 + 0.1 Св                                           | 300      | ns    | from 10 to 400 pF       |  |

|               |         |                    | 1 MHz mode <sup>(2)</sup> | —                                                     | 300      | ns    |                         |  |

| IM25          | TSU:DAT | Data Input         | 100 kHz mode              | 250                                                   | _        | ns    | _                       |  |

|               |         | Setup Time         | 400 kHz mode              | 100                                                   | _        | ns    |                         |  |

|               |         |                    | 1 MHz mode <sup>(2)</sup> | 100                                                   | _        | ns    |                         |  |

| IM26          | THD:DAT | Data Input         | 100 kHz mode              | 0                                                     | —        | μS    | _                       |  |

|               |         | Hold Time          | 400 kHz mode              | 0                                                     | 0.9      | μS    |                         |  |

|               |         |                    | 1 MHz mode <sup>(2)</sup> | 0                                                     | 0.3      | μS    |                         |  |

| IM30          | TSU:STA | Start Condition    | 100 kHz mode              | Трв * (BRG + 2)                                       | —        | ns    | Only relevant for       |  |

|               |         | Setup Time         | 400 kHz mode              | Трв * (BRG + 2)                                       | _        | ns    | Repeated Start          |  |

|               |         |                    | 1 MHz mode <sup>(2)</sup> | Трв * (BRG + 2)                                       | _        | ns    | condition               |  |

| IM31          | THD:STA | Start Condition    | 100 kHz mode              | Трв * (BRG + 2)                                       | —        | ns    | After this period, the  |  |

|               |         | Hold Time          | 400 kHz mode              | Трв * (BRG + 2)                                       | _        | ns    | first clock pulse is    |  |

|               |         |                    | 1 MHz mode <sup>(2)</sup> | Трв * (BRG + 2)                                       | _        | ns    | generated               |  |

| IM33          | Tsu:sto | Stop Condition     | 100 kHz mode              | Трв * (BRG + 2)                                       | _        | ns    | _                       |  |

|               |         | Setup Time         | 400 kHz mode              | Трв * (BRG + 2)                                       | _        | ns    |                         |  |

|               |         |                    | 1 MHz mode <sup>(2)</sup> | Трв * (BRG + 2)                                       | _        | ns    |                         |  |

| IM34          | THD:STO | Stop Condition     | 100 kHz mode              | Трв * (BRG + 2)                                       | _        | ns    | _                       |  |

|               |         | Hold Time          | 400 kHz mode              | Трв * (BRG + 2)                                       | _        | ns    |                         |  |

|               |         |                    | 1 MHz mode <sup>(2)</sup> | Трв * (BRG + 2)                                       | _        | ns    |                         |  |

| IM40          | TAA:SCL | Output Valid from  | 100 kHz mode              | _                                                     | 3500     | ns    | _                       |  |

|               |         | Clock              | 400 kHz mode              | _                                                     | 1000     | ns    | _                       |  |

|               |         |                    | 1 MHz mode <sup>(2)</sup> | _                                                     | 350      | ns    | _                       |  |

| IM45          | TBF:SDA | Bus Free Time      | 100 kHz mode              | 4.7                                                   | _        | μS    | The amount of time the  |  |

|               |         |                    | 400 kHz mode              | 1.3                                                   | <u> </u> | μS    | bus must be free before |  |

|               |         |                    | 1 MHz mode <sup>(2)</sup> | 0.5                                                   | <u> </u> | μS    | a new                   |  |

| IMEO          | CD      | Rue Consolitive La | ading                     |                                                       | 400      |       | transmission can start  |  |

| IM50          | Св      | Bus Capacitive Lo  | -                         | -                                                     | 400      | pF    | —                       |  |

| IM51          | Tpgd    | Pulse Gobbler Del  | -                         | 52                                                    | 312      | ns    | _                       |  |

**Note 1:** BRG is the value of the I<sup>2</sup>C Baud Rate Generator.

2: Maximum pin capacitance = 10 pF for all I2Cx pins (only for 1 MHz mode).

3: The typical value for this parameter is 104 ns.

Example

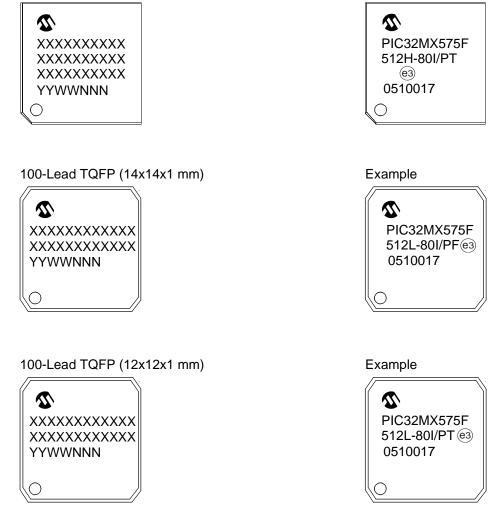

### 34.0 PACKAGING INFORMATION

### 34.1 Package Marking Information

64-Lead TQFP (10x10x1 mm)

| Legend: | XXX        | Customer-specific information                                                                       |

|---------|------------|-----------------------------------------------------------------------------------------------------|

|         | Y          | Year code (last digit of calendar year)                                                             |

|         | ΥY         | Year code (last 2 digits of calendar year)                                                          |

|         | WW         | Week code (week of January 1 is week '01')                                                          |

|         | NNN        | Alphanumeric traceability code                                                                      |

|         |            | Pb-free JEDEC designator for Matte Tin (Sn)                                                         |

|         | *          | This package is Pb-free. The Pb-free JEDEC designator (e3)                                          |

|         |            | can be found on the outer packaging for this package.                                               |

| Note:   | In the eve | nt the full Microchip part number cannot be marked on one line, it will                             |

|         | be carrie  | d over to the next line, thus limiting the number of available s for customer-specific information. |