Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

-·XE

| Product Status             | Active                                                                           |

|----------------------------|----------------------------------------------------------------------------------|

| Core Processor             | MIPS32® M4K™                                                                     |

| Core Size                  | 32-Bit Single-Core                                                               |

| Speed                      | 80MHz                                                                            |

| Connectivity               | CANbus, Ethernet, I <sup>2</sup> C, SPI, UART/USART, USB OTG                     |

| Peripherals                | Brown-out Detect/Reset, DMA, POR, PWM, WDT                                       |

| Number of I/O              | 53                                                                               |

| Program Memory Size        | 256KB (256K x 8)                                                                 |

| Program Memory Type        | FLASH                                                                            |

| EEPROM Size                | -                                                                                |

| RAM Size                   | 64K x 8                                                                          |

| Voltage - Supply (Vcc/Vdd) | 2.3V ~ 3.6V                                                                      |

| Data Converters            | A/D 16x10b                                                                       |

| Oscillator Type            | Internal                                                                         |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                                |

| Mounting Type              | Surface Mount                                                                    |

| Package / Case             | 64-VFQFN Exposed Pad                                                             |

| Supplier Device Package    | 64-VQFN (9x9)                                                                    |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic32mx775f256h-80i-mr |

|                            |                                                                                  |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

## TABLE 1:PIC32MX5XX USB AND CAN FEATURES

|                  |      |                         |                  |     | U    | SB and                 | I CAN                                    |                       |                    |                                 |                              |             |         |      |       |                         |

|------------------|------|-------------------------|------------------|-----|------|------------------------|------------------------------------------|-----------------------|--------------------|---------------------------------|------------------------------|-------------|---------|------|-------|-------------------------|

| Device           | Pins | Program Memory (KB)     | Data Memory (KB) | USB | CAN  | Timers/Capture/Compare | DMA Channels<br>(Programmable/Dedicated) | UART <sup>(2,3)</sup> | Spl <sup>(3)</sup> | I <sup>2</sup> C <sup>(3)</sup> | 10-bit 1 Msps ADC (Channels) | Comparators | dSd/dWd | JTAG | Trace | Packages <sup>(4)</sup> |

| PIC32MX534F064H  | 64   | 64 + 12 <sup>(1)</sup>  | 16               | 1   | 1    | 5/5/5                  | 4/4                                      | 6                     | 3                  | 4                               | 16                           | 2           | Yes     | Yes  | No    | PT,<br>MR               |

| PIC32MX564F064H  | 64   | 64 + 12 <sup>(1)</sup>  | 32               | 1   | 1    | 5/5/5                  | 4/4                                      | 6                     | 3                  | 4                               | 16                           | 2           | Yes     | Yes  | No    | PT,<br>MR               |

| PIC32MX564F128H  | 64   | 128 + 12 <sup>(1)</sup> | 32               | 1   | 1    | 5/5/5                  | 4/4                                      | 6                     | 3                  | 4                               | 16                           | 2           | Yes     | Yes  | No    | PT,<br>MR               |

| PIC32MX575F256H  | 64   | 256 + 12 <sup>(1)</sup> | 64               | 1   | 1    | 5/5/5                  | 8/4                                      | 6                     | 3                  | 4                               | 16                           | 2           | Yes     | Yes  | No    | PT,<br>MR               |

| PIC32MX575F512H  | 64   | 512 + 12 <sup>(1)</sup> | 64               | 1   | 1    | 5/5/5                  | 8/4                                      | 6                     | 3                  | 4                               | 16                           | 2           | Yes     | Yes  | No    | PT,<br>MR               |

| PIC32MX534F064L  | 100  | 64 + 12 <sup>(1)</sup>  | 16               | 1   | 1    | 5/5/5                  | 4/4                                      | 6                     | 4                  | 5                               | 16                           | 2           | Yes     | Yes  | Yes   | PT,<br>PF,<br>BG        |

| PIC32MX564F064L  | 100  | 64 + 12 <sup>(1)</sup>  | 32               | 1   | 1    | 5/5/5                  | 4/4                                      | 6                     | 4                  | 5                               | 16                           | 2           | Yes     | Yes  | Yes   | PT,<br>PF,<br>BG        |

| PIC32MX564F128L  | 100  | 128 + 12 <sup>(1)</sup> | 32               | 1   | 1    | 5/5/5                  | 4/4                                      | 6                     | 4                  | 5                               | 16                           | 2           | Yes     | Yes  | Yes   | PT,<br>PF,<br>BG        |

| PIC32MX575F256L  | 100  | 256 + 12 <sup>(1)</sup> | 64               | 1   | 1    | 5/5/5                  | 8/4                                      | 6                     | 4                  | 5                               | 16                           | 2           | Yes     | Yes  | Yes   | PT,<br>PF,<br>BG        |

| PIC32MX575F512L  | 100  | 512 + 12 <b>(1)</b>     | 64               | 1   | 1    | 5/5/5                  | 8/4                                      | 6                     | 4                  | 5                               | 16                           | 2           | Yes     | Yes  | Yes   | PT,<br>PF,<br>BG        |

| Legend: PF, PT = | TQFP | MR = Q                  | FN               |     | BG = | TFBG/                  | 4                                        | TL =                  | VTLA               | (5)                             |                              |             |         |      |       |                         |

Note 1: This device features 12 KB boot Flash memory.

2: CTS and RTS pins may not be available for all UART modules. Refer to the "Device Pin Tables" section for more information.

**3:** Some pins between the UART, SPI and I<sup>2</sup>C modules may be shared. Refer to the "**Device Pin Tables**" section for more information.

4: Refer to 34.0 "Packaging Information" for more information.

5: 100-pin devices in the VTLA package are available upon request. Please contact your local Microchip Sales Office for details.

#### TABLE 6:PIN NAMES FOR 64-PIN USB, ETHERNET, AND CAN DEVICES

## 64-PIN QFN<sup>(3)</sup> AND TQFP (TOP VIEW)

## PIC32MX764F128H PIC32MX775F256H PIC32MX775F512H PIC32MX795F512H

|       | 64                                                        | 1                  |                                               |

|-------|-----------------------------------------------------------|--------------------|-----------------------------------------------|

|       |                                                           | QFN <sup>(3)</sup> | 64<br>TQFP                                    |

| Pin # | Full Pin Name                                             | Pin #              | Full Pin Name                                 |

| 1     | ETXEN/PMD5/RE5                                            | 33                 | USBID/RF3                                     |

| 2     | ETXD0/PMD6/RE6                                            | 34                 | VBUS                                          |

| 3     | ETXD1/PMD7/RE7                                            | 35                 | VUSB3V3                                       |

| 4     | SCK2/U6TX/U3RTS/PMA5/CN8/RG6                              | 36                 | D-/RG3                                        |

| 5     | SDA4/SDI2/U3RX/PMA4/CN9/RG7                               | 37                 | D+/RG2                                        |

| 6     | SCL4/SDO2/U3TX/PMA3/CN10/RG8                              | 38                 | Vdd                                           |

| 7     | MCLR                                                      | 39                 | OSC1/CLKI/RC12                                |

| 8     | SS2/U6RX/U3CTS/PMA2/CN11/RG9                              | 40                 | OSC2/CLKO/RC15                                |

| 9     | Vss                                                       | 41                 | Vss                                           |

| 10    | Vdd                                                       | 42                 | RTCC/AERXD1/ETXD3/IC1/INT1/RD8                |

| 11    | AN5/C1IN+/VBUSON/CN7/RB5                                  | 43                 | AERXD0/ETXD2/SS3/U4RX/U1CTS/SDA1/IC2/INT2/RD9 |

| 12    | AN4/C1IN-/CN6/RB4                                         | 44                 | ECOL/AECRSDV/SCL1/IC3/PMCS2/PMA15/INT3/RD10   |

| 13    | AN3/C2IN+/CN5/RB3                                         | 45                 | ECRS/AEREFCLK/IC4/PMCS1/PMA14/INT4/RD11       |

| 14    | AN2/C2IN-/CN4/RB2                                         | 46                 | OC1/INT0/RD0                                  |

| 15    | PGEC1/AN1/VREF-/CVREF-/CN3/RB1                            | 47                 | SOSCI/CN1/RC13                                |

| 16    | PGED1/AN0/VREF+/CVREF+/PMA6/CN2/RB0                       | 48                 | SOSCO/T1CK/CN0/RC14                           |

| 17    | PGEC2/AN6/OCFA/RB6                                        | 49                 | EMDIO/AEMDIO/SCK3/U4TX/U1RTS/OC2/RD1          |

| 18    | PGED2/AN7/RB7                                             | 50                 | SDA3/SDI3/U1RX/OC3/RD2                        |

| 19    | AVdd                                                      | 51                 | SCL3/SDO3/U1TX/OC4/RD3                        |

| 20    | AVss                                                      | 52                 | OC5/IC5/PMWR/CN13/RD4                         |

| 21    | AN8/C2TX <sup>(2)</sup> /SS4/U5RX/U2CTS/C1OUT/RB8         | 53                 | PMRD/CN14/RD5                                 |

| 22    | AN9/C2OUT/PMA7/RB9                                        | 54                 | AETXEN/ETXERR/CN15/RD6                        |

| 23    | TMS/AN10/CVREFOUT/PMA13/RB10                              | 55                 | ETXCLK/AERXERR/CN16/RD7                       |

| 24    | TDO/AN11/PMA12/RB11                                       | 56                 | VCAP                                          |

| 25    | Vss                                                       | 57                 | VDD                                           |

| 26    | Vdd                                                       | 58                 | C1RX/AETXD1/ERXD3/RF0                         |

| 27    | TCK/AN12/PMA11/RB12                                       | 59                 | C1TX/AETXD0/ERXD2/RF1                         |

| 28    | TDI/AN13/PMA10/RB13                                       | 60                 | ERXD1/PMD0/RE0                                |

| 29    | AN14/C2RX <sup>(2)</sup> /SCK4/U5TX/U2RTS/PMALH/PMA1/RB14 | 61                 | ERXD0/PMD1/RE1                                |

| 30    | AN15/EMDC/AEMDC/OCFB/PMALL/PMA0/CN12/RB15                 | 62                 | ERXDV/ECRSDV/PMD2/RE2                         |

| 31    | AC1TX/SDA5/SDI4/U2RX/PMA9/CN17/RF4                        | 63                 | ERXCLK/EREFCLKPMD3/RE3                        |

| 32    | AC1RX/SCL5/SDO4/U2TX/PMA8/CN18/RF5                        | 64                 | ERXERR/PMD4/RE4                               |

| Note  | 1: Shaded pins are 5V tolerant.                           |                    |                                               |

**Note 1:** Shaded pins are 5V tolerant.

2: This pin is not available on PIC32MX765F128H devices.

3: The metal plane at the bottom of the QFN device is not connected to any pins and is recommended to be connected to Vss externally.

## 2.9 Configuration of Analog and Digital Pins During ICSP Operations

If MPLAB ICD 3 or REAL ICE is selected as a debugger, it automatically initializes all of the Analog-to-Digital input pins (ANx) as "digital" pins by setting all bits in the AD1PCFG register.

The bits in this register that correspond to the Analogto-Digital pins that are initialized by MPLAB ICD 3 or REAL ICE, must not be cleared by the user application firmware; otherwise, communication errors will result between the debugger and the device.

If your application needs to use certain ADC pins as analog input pins during the debug session, the user application must clear the corresponding bits in the AD1PCFG register during initialization of the ADC module.

When MPLAB ICD 3 or REAL ICE is used as a programmer, the user application firmware must correctly configure the AD1PCFG register. Automatic initialization of this register is only done during debugger operation. Failure to correctly configure the register(s) will result in all ADC pins being recognized as analog input pins, resulting in the port value being read as a logic '0', which may affect user application functionality.

## 2.10 Unused I/Os

Unused I/O pins should not be allowed to float as inputs. They can be configured as outputs and driven to a logic-low state.

Alternatively, inputs can be reserved by connecting the pin to Vss through a 1k to 10k resistor and configuring the pin as an input.

## 2.11 EMI/EMC/EFT (IEC 61000-4-4 and IEC 61000-4-2) Suppression Considerations

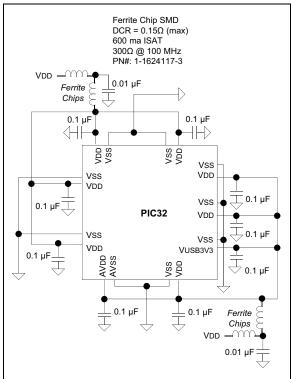

The use of LDO regulators is preferred to reduce overall system noise and provide a cleaner power source. However, when utilizing switching Buck/ Boost regulators as the local power source for PIC32 devices, as well as in electrically noisy environments or test conditions required for IEC 61000-4-4 and IEC 61000-4-2, users should evaluate the use of T-Filters (i.e., L-C-L) on the power pins, as shown in Figure 2-4. In addition to a more stable power source, use of this type of T-Filter can greatly reduce susceptibility to EMI sources and events.

## FIGURE 2-4: EMI/EMC/EFT SUPPRESSION CIRCUIT

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2    | Bit<br>25/17/9/1         | Bit<br>24/16/8/0 |  |  |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|----------------------|--------------------------|------------------|--|--|

| 24.24        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0                  | U-0                      | U-0              |  |  |

| 31:24        |                   | _                 |                   |                   | _                 |                      | _                        |                  |  |  |

| 23:16        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0                  | U-0                      | U-0              |  |  |

| 23.10        |                   | _                 | _                 | —                 | -                 | _                    | —                        | _                |  |  |

| 45.0         | U-0               | U-0               | U-0               | U-0               | U-0               | R/W-0                | R/W-0                    | R/W-0            |  |  |

| 15:8         | —                 | —                 | —                 | —                 | _                 |                      | RIPL<2:0> <sup>(1)</sup> |                  |  |  |

| 7.0          | U-0               | U-0               | R/W-0             | R/W-0             | R/W-0             | R/W-0                | R/W-0                    | R/W-0            |  |  |

| 7:0          |                   | —                 |                   |                   | VEC               | <5:0> <sup>(1)</sup> |                          |                  |  |  |

## REGISTER 7-2: INTSTAT: INTERRUPT STATUS REGISTER

## Legend:

| Legena.           |                  |                           |                    |

|-------------------|------------------|---------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, re | ead as '0'         |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared      | x = Bit is unknown |

bit 31-11 Unimplemented: Read as '0'

- bit 10-8 **RIPL<2:0>:** Requested Priority Level bits<sup>(1)</sup> 111-000 = The priority level of the latest interrupt presented to the CPU

- bit 7-6 Unimplemented: Read as '0'

- bit 5-0 VEC<5:0>: Interrupt Vector bits<sup>(1)</sup> 11111-00000 = The interrupt vector that is presented to the CPU

- **Note 1:** This value should only be used when the interrupt controller is configured for Single-vector mode.

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |  |  |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|--|--|--|

| 04-04        | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |  |

| 31:24        | TPTMR<31:24>      |                   |                   |                   |                   |                   |                  |                  |  |  |  |

| 00.40        | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |  |

| 23:16        | TPTMR<23:16>      |                   |                   |                   |                   |                   |                  |                  |  |  |  |

| 15.0         | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |  |

| 15:8         | TPTMR<15:8>       |                   |                   |                   |                   |                   |                  |                  |  |  |  |

| 7.0          | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |  |

| 7:0          |                   |                   |                   | TPTM              | 1R<7:0>           |                   |                  | •                |  |  |  |

### REGISTER 7-3: TPTMR: TEMPORAL PROXIMITY TIMER REGISTER

| Legend:           |                  |                                             |                    |  |  |

|-------------------|------------------|---------------------------------------------|--------------------|--|--|

| R = Readable bit  | W = Writable bit | able bit U = Unimplemented bit, read as '0' |                    |  |  |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared                        | x = Bit is unknown |  |  |

bit 31-0 TPTMR<31:0>: Temporal Proximity Timer Reload bits

Used by the Temporal Proximity Timer as a reload value when the Temporal Proximity timer is triggered by an interrupt event.

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |  |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|--|--|

| 31:24        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |  |  |

|              |                   | —                 |                   |                   | —                 |                   | —                | —                |  |  |

| 23:16        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |  |  |

| 23.10        |                   | —                 |                   |                   | —                 |                   | —                | —                |  |  |

| 15:8         | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |

| 10.0         | LMASK<10:3>       |                   |                   |                   |                   |                   |                  |                  |  |  |

| 7:0          | R/W-0             | R/W-0             | R/W-0             | U-0               | U-0               | U-0               | U-0              | U-0              |  |  |

| 7.0          | l                 | LMASK<2:0>        |                   | —                 | —                 | —                 | —                | —                |  |  |

## REGISTER 9-4: CHEMSK: CACHE TAG MASK REGISTER

## Legend:

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read as '0' |                    |  |  |  |

|-------------------|------------------|------------------------------------|--------------------|--|--|--|

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared               | x = Bit is unknown |  |  |  |

bit 31-16 Unimplemented: Write '0'; ignore read

#### bit 15-5 LMASK<10:0>: Line Mask bits

- 1 = Enables mask logic to force a match on the corresponding bit position in LTAG<19:0> bits (CHETAG<23:4>) and the physical address

- 0 = Only writeable for values of CHEIDX<3:0> bits (CHEACC<3:0>) equal to 0x0A and 0x0B (disables mask logic)

- bit 4-0 **Unimplemented:** Write '0'; ignore read

|              |                   |                   |                   | •                 |                   |                   |                  |                  |  |  |  |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|--|--|--|

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |  |  |

| 04.04        | R/W-x             | R/W-x             | R/W-x             | R/W-x             | R/W-x             | R/W-x             | R/W-x            | R/W-x            |  |  |  |

| 31:24        | CHEW0<31:24>      |                   |                   |                   |                   |                   |                  |                  |  |  |  |

| 00.40        | R/W-x             | R/W-x             | R/W-x             | R/W-x             | R/W-x             | R/W-x             | R/W-x            | R/W-x            |  |  |  |

| 23:16        | CHEW0<23:16>      |                   |                   |                   |                   |                   |                  |                  |  |  |  |

| 45.0         | R/W-x             | R/W-x             | R/W-x             | R/W-x             | R/W-x             | R/W-x             | R/W-x            | R/W-x            |  |  |  |

| 15:8         | CHEW0<15:8>       |                   |                   |                   |                   |                   |                  |                  |  |  |  |

| 7.0          | R/W-x             | R/W-x             | R/W-x             | R/W-x             | R/W-x             | R/W-x             | R/W-x            | R/W-x            |  |  |  |

| 7:0          |                   |                   |                   | CHEWO             | <7:0>             |                   |                  |                  |  |  |  |

### REGISTER 9-5: CHEW0: CACHE WORD 0

| Legend:           |                                                     |                      |                    |  |

|-------------------|-----------------------------------------------------|----------------------|--------------------|--|

| R = Readable bit  | W = Writable bit U = Unimplemented bit, read as '0' |                      |                    |  |

| -n = Value at POR | '1' = Bit is set                                    | '0' = Bit is cleared | x = Bit is unknown |  |

bit 31-0 **CHEW0<31:0>:** Word 0 of the cache line selected by CHEIDX<3:0> bits (CHEACC<3:0>) Readable only if the device is not code-protected.

| Bit<br>Range | Bit<br>31/23/15/7   | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0      |

|--------------|---------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|-----------------------|

| 31:24        | U-0                 | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0                   |

|              |                     | —                 | —                 | —                 | _                 | _                 | —                | —                     |

| 00.40        | U-0                 | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0                   |

| 23:16        | —                   | —                 | —                 | —                 | —                 | _                 | —                | —                     |

| 45.0         | R/W-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | R/W-0                 |

| 15:8         | CHBUSY              | —                 | —                 | _                 | —                 | _                 | —                | CHCHNS <sup>(1)</sup> |

| 7.0          | R/W-0               | R/W-0             | R/W-0             | R/W-0             | U-0               | R-0               | R/W-0            | R/W-0                 |

| 7:0          | CHEN <sup>(2)</sup> | CHAED             | CHCHN             | CHAEN             | _                 | CHEDET            | CHPF             | RI<1:0>               |

## REGISTER 10-7: DCHxCON: DMA CHANNEL 'x' CONTROL REGISTER

#### Legend:

| 0                 |                  |                                    |                    |

|-------------------|------------------|------------------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read as '0' |                    |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared               | x = Bit is unknown |

## bit 31-16 Unimplemented: Read as '0'

- bit 15 **CHBUSY:** Channel Busy bit 1 = Channel is active or has been enabled 0 = Channel is inactive or has been disabled

- bit 14-9 **Unimplemented:** Read as '0'

- bit 8 CHCHNS: Chain Channel Selection bit<sup>(1)</sup>

- 1 Chain to channel lower in patteral priority (CH1 will be enabled by C

- 1 = Chain to channel lower in natural priority (CH1 will be enabled by CH2 transfer complete)

0 = Chain to channel higher in natural priority (CH1 will be enabled by CH0 transfer complete)

- bit 7 CHEN: Channel Enable bit<sup>(2)</sup>

- 1 = Channel is enabled

- 0 =Channel is disabled

- bit 6 CHAED: Channel Allow Events If Disabled bit

- 1 = Channel start/abort events will be registered, even if the channel is disabled

- 0 = Channel start/abort events will be ignored if the channel is disabled

### bit CHCHN: Channel Chain Enable bit

- 1 = Allow channel to be chained

- 0 = Do not allow channel to be chained

### bit 4 CHAEN: Channel Automatic Enable bit

- 1 = Channel is continuously enabled, and not automatically disabled after a block transfer is complete

- 0 = Channel is disabled on block transfer complete

- bit 3 Unimplemented: Read as '0'

- bit 2 CHEDET: Channel Event Detected bit

- 1 = An event has been detected

- 0 = No events have been detected

### bit 1-0 CHPRI<1:0>: Channel Priority bits

- 11 = Channel has priority 3 (highest)

- 10 = Channel has priority 2

- 01 = Channel has priority 1

- 00 = Channel has priority 0

- **Note 1:** The chain selection bit takes effect when chaining is enabled (CHCHN = 1).

- 2: When the channel is suspended by clearing this bit, the user application should poll the CHBUSY bit (if available on the device variant) to see when the channel is suspended, as it may take some clock cycles to complete a current transaction before the channel is suspended.

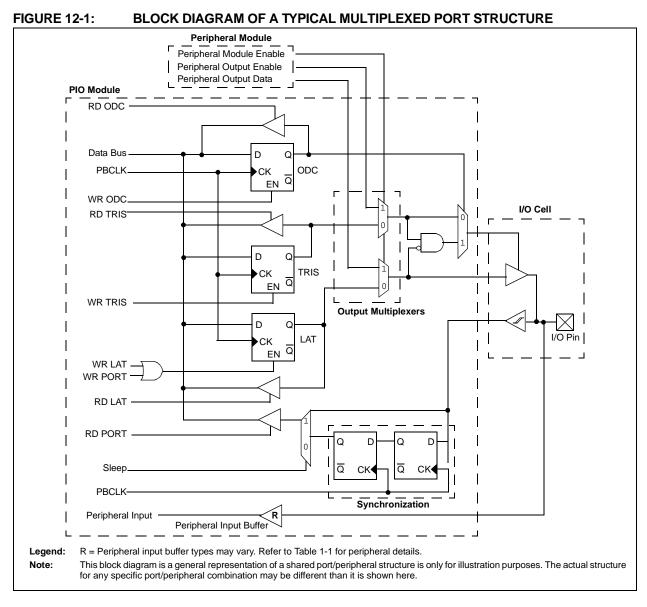

## 12.0 I/O PORTS

Note: This data sheet summarizes the features of the PIC32MX5XX/6XX/7XX family of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to Section 12. "I/O Ports" (DS60001120) in the "PIC32 Family Reference Manual", which is available from the Microchip web site (www.microchip.com/PIC32).

General purpose I/O pins are the simplest of peripherals. They allow the PIC32 MCU to monitor and control other devices. To add flexibility and functionality, some pins are multiplexed with alternate function(s). These functions depend on which peripheral features are on the device. In general, when a peripheral is functioning, that pin may not be used as a general purpose I/O pin. Following are some of the key features of this module:

- · Individual output pin open-drain enable/disable

- Individual input pin weak pull-up enable/disable

- Monitor selective inputs and generate interrupt when change in pin state is detected

- · Operation during Sleep and Idle modes

- Fast bit manipulation using CLR, SET and INV registers

Figure 12-1 illustrates a block diagram of a typical multiplexed I/O port.

## 18.1 Control Registers

## TABLE 18-1: SPI1 THROUGH SPI4 REGISTER MAP

| SS                          |                                 |               |       |         |        |        |         |          |           | Bi     | ts     |        |        |          |        |          |        |         |            |

|-----------------------------|---------------------------------|---------------|-------|---------|--------|--------|---------|----------|-----------|--------|--------|--------|--------|----------|--------|----------|--------|---------|------------|

| Virtual Address<br>(BF80_#) | Register<br>Name <sup>(1)</sup> | Bit Range     | 31/15 | 30/14   | 29/13  | 28/12  | 27/11   | 26/10    | 25/9      | 24/8   | 23/7   | 22/6   | 21/5   | 20/4     | 19/3   | 18/2     | 17/1   | 16/0    | All Resets |

|                             | SPI1CON <sup>(2)</sup>          | 31:16         | FRMEN | FRMSYNC | FRMPOL | MSSEN  | FRMSYPW | F        | RMCNT<2:0 | )>     | _      | _      | —      | _        | _      |          | SPIFE  | ENHBUF  | 0000       |

| 5E00                        | SPITCON-                        | 15:0          | ON    | _       | SIDL   | DISSDO | MODE32  | MODE16   | SMP       | CKE    | SSEN   | CKP    | MSTEN  | —        | STXISE | L<1:0>   | SRXISE | L<1:0>  | 0000       |

| 5E10                        | SPI1STAT <sup>(2)</sup>         | 31:16         | —     | _       | _      |        | RX      | BUFELM<4 | :0>       |        | —      | —      | —      |          | TX     | BUFELM<4 | :0>    |         | 0000       |

| 5E 10                       | SPIISIAL                        | 15:0          | —     | _       | _      | _      | SPIBUSY |          | -         | SPITUR | SRMT   | SPIROV | SPIRBE | —        | SPITBE | -        | SPITBF | SPIRBF  | 0008       |

| 5E20                        | SPI1BUF <sup>(2)</sup>          | 31:16<br>15:0 |       |         |        |        |         |          |           | DATA<  | :31:0> |        |        |          |        |          |        |         | 0000       |

| 5E30                        | SPI1BRG <sup>(2)</sup>          | 31:16         | —     | _       | -      | _      | _       |          |           | _      | —      | —      | _      | _        | _      |          | _      | _       | 0000       |

| 3E30                        | SFIIDKG                         | 15:0          | —     | —       | _      | _      | _       |          |           |        |        |        |        | BRG<8:0> |        |          |        |         | 0000       |

| 5800                        | SPI3CON                         | 31:16         | FRMEN | FRMSYNC | FRMPOL | MSSEN  | FRMSYPW | F        | RMCNT<2:0 | )>     | _      | —      | -      | -        | _      | _        | SPIFE  | ENHBUF  | 0000       |

| 5600                        | SPISCON                         | 15:0          | ON    | _       | SIDL   | DISSDO | MODE32  | MODE16   | SMP       | CKE    | SSEN   | CKP    | MSTEN  | _        | STXISE | L<1:0>   | SRXISE | EL<1:0> | 0000       |

| 5810                        | SPI3STAT                        | 31:16         | —     | _       | _      |        | RX      | BUFELM<4 | :0>       |        | —      | —      | _      |          | TX     | BUFELM<4 | :0>    |         | 0000       |

| 5810                        | SFISSIAI                        | 15:0          | —     | _       | _      | _      | SPIBUSY |          |           | SPITUR | SRMT   | SPIROV | SPIRBE | _        | SPITBE |          | SPITBF | SPIRBF  | 0008       |

| 5820                        | SPI3BUF                         | 31:16<br>15:0 |       |         |        |        |         |          |           | DATA<  | :31:0> |        |        |          |        |          |        |         | 0000       |

|                             | SPI3BRG                         | 31:16         | _     | _       | _      | _      | _       | _        | _         | _      | _      | _      | _      | _        | _      | _        | _      |         | 0000       |

| 5830                        | SPI3BRG                         | 15:0          | _     | _       | _      | _      | _       |          | -         |        |        |        |        | BRG<8:0> |        |          |        |         | 0000       |

| 5400                        | SPI2CON                         | 31:16         | FRMEN | FRMSYNC | FRMPOL | MSSEN  | FRMSYPW | F        | RMCNT<2:0 | )>     | _      | _      | _      | —        | _      | _        | SPIFE  | ENHBUF  | 0000       |

| 5A00                        | SPIZCON                         | 15:0          | ON    | _       | SIDL   | DISSDO | MODE32  | MODE16   | SMP       | CKE    | SSEN   | CKP    | MSTEN  | _        | STXISE | L<1:0>   | SRXISE | L<1:0>  | 0000       |

| 5440                        | SPI2STAT                        | 31:16         | _     | _       | -      |        | RX      | BUFELM<4 | :0>       |        | _      | _      | -      |          | TX     | BUFELM<4 | :0>    |         | 0000       |

| 5A10                        | SFIZSTAT                        | 15:0          | _     | —       | —      | —      | SPIBUSY | _        | _         | SPITUR | SRMT   | SPIROV | SPIRBE | —        | SPITBE | -        | SPITBF | SPIRBF  | 0008       |

| 5A20                        | SPI2BUF                         | 31:16<br>15:0 |       |         |        |        |         |          |           | DATA<  | :31:0> |        |        |          |        |          |        |         | 0000       |

| 5A30                        | SPI2BRG                         | 31:16         | _     | —       | —      | —      | —       | _        | _         | —      | —      | —      | —      | —        | —      | -        | —      | _       | 0000       |

| 5A30                        | SFIZERG                         | 15:0          | —     | _       | -      | _      | _       |          |           |        |        |        |        | BRG<8:0> |        |          |        |         | 0000       |

| 5C00                        | SPI4CON                         | 31:16         | FRMEN | FRMSYNC | FRMPOL | MSSEN  | FRMSYPW | F        | RMCNT<2:0 | )>     | —      | —      | _      | —        | -      |          | SPIFE  | ENHBUF  | 0000       |

| 5000                        | 51 140010                       | 15:0          | ON    | —       | SIDL   | DISSDO | MODE32  | MODE16   | SMP       | CKE    | SSEN   | CKP    | MSTEN  | _        | STXISE | L<1:0>   | SRXISE | EL<1:0> | 0000       |

| 5C10                        | SPI4STAT                        | 31:16         | _     | —       |        |        |         | BUFELM<4 | :0>       | -      | _      |        |        |          |        | BUFELM<4 | :0>    | -       | 0000       |

| 5010                        |                                 | 15:0          | —     | —       | —      | —      | SPIBUSY | —        | —         | SPITUR | SRMT   | SPIROV | SPIRBE | —        | SPITBE | —        | SPITBF | SPIRBF  | 0008       |

| 5C20                        | SPI4BUF                         | 31:16<br>15:0 |       |         |        |        |         |          |           | DATA<  | :31:0> |        |        |          |        |          |        |         | 0000       |

| 5C30                        | SPI4BRG                         | 31:16         |       | _       | _      | —      | —       | _        | _         | —      | _      | _      | —      | _        | _      | _        | _      | _       | 0000       |

| 5030                        |                                 | 15:0          | _     | _       | _      | -      | _       | —        | —         |        |        |        |        | BRG<8:0> |        |          |        |         | 0000       |

Legend: x = unknown value on Reset; - = unimplemented, read as '0'. Reset values are shown in hexadecimal.

Note 1: All registers in this table except SPIxBUF have corresponding CLR, SET and INV registers at their virtual addresses, plus offsets of 0x4, 0x8 and 0xC, respectively. See Section 12.1.1 "CLR, SET and INV Registers" for more information.

2: This register is not available on 64-pin devices.

| REGIST    | ER 18-1: SPIxCON: SPI CONTROL REGISTER (CONTINUED)                                                                                                                                              |  |  |  |  |  |  |

|-----------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|

| bit 15    | <b>ON:</b> SPI Peripheral On bit <sup>(1)</sup>                                                                                                                                                 |  |  |  |  |  |  |

|           | 1 = SPI Peripheral is enabled                                                                                                                                                                   |  |  |  |  |  |  |

| bit 11    | ) = SPI Peripheral is disabled                                                                                                                                                                  |  |  |  |  |  |  |

| bit 14    | Inimplemented: Read as '0'                                                                                                                                                                      |  |  |  |  |  |  |

| bit 13    | SIDL: Stop in Idle Mode bit<br>1 = Discontinue operation when CPU enters in Idle mode                                                                                                           |  |  |  |  |  |  |

|           | 0 = Continue operation in Idle mode                                                                                                                                                             |  |  |  |  |  |  |

| bit 12    | <b>DISSDO:</b> Disable SDOx pin bit                                                                                                                                                             |  |  |  |  |  |  |

|           | 1 = SDOx pin is not used by the module (pin is controlled by associated PORT register)                                                                                                          |  |  |  |  |  |  |

|           | 0 = SDOx pin is controlled by the module                                                                                                                                                        |  |  |  |  |  |  |

| bit 11-10 | MODE<32,16>: 32/16-Bit Communication Select bits                                                                                                                                                |  |  |  |  |  |  |

|           | MODE32 MODE16 Communication                                                                                                                                                                     |  |  |  |  |  |  |

|           | 1 x 32-bit<br>0 1 16-bit                                                                                                                                                                        |  |  |  |  |  |  |

|           | 0 1 16-bit<br>0 0 8-bit                                                                                                                                                                         |  |  |  |  |  |  |

| bit 9     | SMP: SPI Data Input Sample Phase bit                                                                                                                                                            |  |  |  |  |  |  |

|           | Master mode (MSTEN = 1):                                                                                                                                                                        |  |  |  |  |  |  |

|           | 1 = Input data sampled at end of data output time                                                                                                                                               |  |  |  |  |  |  |

|           | 0 = Input data sampled at middle of data output time                                                                                                                                            |  |  |  |  |  |  |

|           | Slave mode (MSTEN = 0):                                                                                                                                                                         |  |  |  |  |  |  |

|           | SMP value is ignored when SPI is used in Slave mode. The module always uses SMP = 0.                                                                                                            |  |  |  |  |  |  |

| bit 8     | CKE: SPI Clock Edge Select bit <sup>(3)</sup>                                                                                                                                                   |  |  |  |  |  |  |

|           | 1 = Serial output data changes on transition from active clock state to Idle clock state (see CKP bit)                                                                                          |  |  |  |  |  |  |

| h:+ 7     | 0 = Serial output data changes on transition from Idle clock state to active clock state (see CKP bit)                                                                                          |  |  |  |  |  |  |

| bit 7     | SSEN: Slave Select Enable (Slave mode) bit<br>1 = SSx pin used for Slave mode                                                                                                                   |  |  |  |  |  |  |

|           | 0 = SSx pin not used for Slave mode (pin is controlled by port function)                                                                                                                        |  |  |  |  |  |  |

| bit 6     | CKP: Clock Polarity Select bit                                                                                                                                                                  |  |  |  |  |  |  |

|           | 1 = Idle state for clock is a high level; active state is a low level                                                                                                                           |  |  |  |  |  |  |

|           | 0 = Idle state for clock is a low level; active state is a high level                                                                                                                           |  |  |  |  |  |  |

| bit 5     | MSTEN: Master Mode Enable bit                                                                                                                                                                   |  |  |  |  |  |  |

|           | 1 = Master mode<br>0 = Slave mode                                                                                                                                                               |  |  |  |  |  |  |

| bit 4     | Unimplemented: Read as '0'                                                                                                                                                                      |  |  |  |  |  |  |

| bit 3-2   | STXISEL<1:0>: SPI Transmit Buffer Empty Interrupt Mode bits                                                                                                                                     |  |  |  |  |  |  |

| Dit 0-2   | 11 = Interrupt is generated when the buffer is not full (has one or more empty elements)                                                                                                        |  |  |  |  |  |  |

|           | 10 = Interrupt is generated when the buffer is empty by one-half or more                                                                                                                        |  |  |  |  |  |  |

|           | 01 = Interrupt is generated when the buffer is completely empty                                                                                                                                 |  |  |  |  |  |  |

|           | 00 = Interrupt is generated when the last transfer is shifted out of SPISR and transmit operations are                                                                                          |  |  |  |  |  |  |

|           | complete                                                                                                                                                                                        |  |  |  |  |  |  |

| bit 1-0   | SRXISEL<1:0>: SPI Receive Buffer Full Interrupt Mode bits<br>11 = Interrupt is generated when the buffer is full                                                                                |  |  |  |  |  |  |

|           | 10 = Interrupt is generated when the buffer is full by one-half or more                                                                                                                         |  |  |  |  |  |  |

|           | 01 = Interrupt is generated when the buffer is not empty                                                                                                                                        |  |  |  |  |  |  |

|           | 00 = Interrupt is generated when the last word in the receive buffer is read (i.e., buffer is empty)                                                                                            |  |  |  |  |  |  |

|           | When using the 1.1 DPOLK divisor the user's activises should not used anywrite the mentation " OPP i                                                                                            |  |  |  |  |  |  |

| Note 1:   | When using the 1:1 PBCLK divisor, the user's software should not read or write the peripheral's SFRs in the SYSCLK cycle immediately following the instruction that clears the module's ON bit. |  |  |  |  |  |  |

| 2:        | This bit can only be written when the ON bit = $0$ .                                                                                                                                            |  |  |  |  |  |  |

| 3:        | This bit is not used in the Framed SPI mode. The user should program this bit to '0' for the Framed SPI                                                                                         |  |  |  |  |  |  |

| 0.        | mode (FRMEN = 1).                                                                                                                                                                               |  |  |  |  |  |  |

|           |                                                                                                                                                                                                 |  |  |  |  |  |  |

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |  |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|--|--|

| 04.04        | U-0               | U-0               | U-0               | R-0               | R-0               | R-0               | R-0              | R-0              |  |  |

| 31:24        | —                 | —                 | —                 |                   | R                 | XBUFELM<4:0       | 0>               |                  |  |  |

| 00.40        | U-0               | U-0               | U-0               | R-0               | R-0               | R-0               | R-0              | R-0              |  |  |

| 23:16        | —                 | —                 | —                 | TXBUFELM<4:0>     |                   |                   |                  |                  |  |  |

| 45.0         | U-0               | U-0               | U-0               | U-0               | R-0               | U-0               | U-0              | R-0              |  |  |

| 15:8         | —                 | —                 | —                 | _                 | SPIBUSY           | _                 | _                | SPITUR           |  |  |

| 7.0          | R-0               | R/W-0             | R-0               | U-0               | R-1               | U-0               | R-0              | R-0              |  |  |

| 7:0          | SRMT              | SPIROV            | SPIRBE            |                   | SPITBE            |                   | SPITBF           | SPIRBF           |  |  |

## **REGISTER 18-2: SPIxSTAT: SPI STATUS REGISTER**

| Legend:           | C = Clearable bit | HS = Set in hardware      |                    |

|-------------------|-------------------|---------------------------|--------------------|

| R = Readable bit  | W = Writable bit  | U = Unimplemented bit, re | ead as '0'         |

| -n = Value at POR | '1' = Bit is set  | '0' = Bit is cleared      | x = Bit is unknown |

- bit 31-29 Unimplemented: Read as '0'

- bit 28-24 **RXBUFELM<4:0>:** Receive Buffer Element Count bits (only valid when ENHBUF = 1)

- bit 23-21 Unimplemented: Read as '0'

- bit 20-16 **TXBUFELM<4:0>:** Transmit Buffer Element Count bits (only valid when ENHBUF = 1)

- bit 15-12 Unimplemented: Read as '0'

- bit 11 SPIBUSY: SPI Activity Status bit 1 = SPI peripheral is currently busy with some transactions 0 = SPI peripheral is currently idle

- Unimplemented: Read as '0'

- bit 10-9

- bit 8 SPITUR: Transmit Under Run bit

- 1 = Transmit buffer has encountered an underrun condition

- 0 = Transmit buffer has no underrun condition

This bit is only valid in Framed Sync mode; the underrun condition must be cleared by disabling/re-enabling the module.

- bit 7 **SRMT:** Shift Register Empty bit (only valid when ENHBUF = 1)

- 1 = When SPI module shift register is empty

- 0 = When SPI module shift register is not empty

- bit 6 SPIROV: Receive Overflow Flag bit

- 1 = A new data is completely received and discarded. The user software has not read the previous data in the SPIxBUF register.

- 0 = No overflow has occurred

- This bit is set in hardware; can only be cleared (= 0) in software.

- bit 5 **SPIRBE:** RX FIFO Empty bit (only valid when ENHBUF = 1) 1 = RX FIFO is empty (CRPTR = SWPTR) 0 = RX FIFO is not empty (CRPTR  $\neq$  SWPTR)

- bit 4 Unimplemented: Read as '0'

- bit 3 SPITBE: SPI Transmit Buffer Empty Status bit

- 1 = Transmit buffer, SPIxTXB is empty

- 0 = Transmit buffer, SPIxTXB is not empty

- Automatically set in hardware when SPI transfers data from SPIxTXB to SPIxSR.

- Automatically cleared in hardware when SPIxBUF is written to, loading SPIxTXB.

- bit 2 Unimplemented: Read as '0'

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4             | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |

|--------------|-------------------|-------------------|-------------------|-------------------------------|-------------------|-------------------|------------------|------------------|--|

| 31:24        | R/W-0             | R/W-0             | R/W-0             | R/W-0                         | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |

| 31.24        | FLTEN11           | MSEL11<1:0>       |                   | TEN11 MSEL11<1:0> FSEL11<4:0> |                   |                   |                  |                  |  |

| 23:16        | R/W-0             | R/W-0             | R/W-0             | R/W-0                         | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |

| 23.10        | FLTEN10           | MSEL1             | 0<1:0>            | FSEL10<4:0>                   |                   |                   |                  |                  |  |

| 15:8         | R/W-0             | R/W-0             | R/W-0             | R/W-0                         | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |

| 10.0         | FLTEN9            | MSEL9<1:0>        |                   |                               | F                 | SEL9<4:0>         |                  |                  |  |

| 7.0          | R/W-0             | R/W-0             | R/W-0             | R/W-0                         | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |

| 7:0          | FLTEN8 MSEL8<1:0> |                   |                   |                               | F                 | SEL8<4:0>         |                  |                  |  |

## REGISTER 24-12: CIFLTCON2: CAN FILTER CONTROL REGISTER 2

#### Legend:

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, re | ead as '0'         |

|-------------------|------------------|---------------------------|--------------------|

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared      | x = Bit is unknown |

| bit 31    | FLTEN11: Filter 11 Enable bit                                                                                                                                                  |

|-----------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|           | 1 = Filter is enabled<br>0 = Filter is disabled                                                                                                                                |

| bit 30-29 | MSEL11<1:0>: Filter 11 Mask Select bits                                                                                                                                        |

|           | <ul> <li>11 = Acceptance Mask 3 selected</li> <li>10 = Acceptance Mask 2 selected</li> <li>01 = Acceptance Mask 1 selected</li> <li>00 = Acceptance Mask 0 selected</li> </ul> |

| bit 28-24 | FSEL11<4:0>: FIFO Selection bits                                                                                                                                               |

|           | 11111 = Message matching filter is stored in FIFO buffer 31<br>11110 = Message matching filter is stored in FIFO buffer 30                                                     |

|           |                                                                                                                                                                                |

|           | 00001 = Message matching filter is stored in FIFO buffer 1<br>00000 = Message matching filter is stored in FIFO buffer 0                                                       |

| bit 23    | FLTEN10: Filter 10 Enable bit                                                                                                                                                  |

|           | <ul><li>1 = Filter is enabled</li><li>0 = Filter is disabled</li></ul>                                                                                                         |

| bit 22-21 | MSEL10<1:0>: Filter 10 Mask Select bits                                                                                                                                        |

|           | <ul> <li>11 = Acceptance Mask 3 selected</li> <li>10 = Acceptance Mask 2 selected</li> <li>01 = Acceptance Mask 1 selected</li> <li>00 = Acceptance Mask 0 selected</li> </ul> |

| bit 20-16 | FSEL10<4:0>: FIFO Selection bits                                                                                                                                               |

|           | 11111 = Message matching filter is stored in FIFO buffer 31                                                                                                                    |

|           | 11110 = Message matching filter is stored in FIFO buffer 30                                                                                                                    |

|           | •                                                                                                                                                                              |

|           | •                                                                                                                                                                              |

|           | 00001 = Message matching filter is stored in FIFO buffer 1<br>00000 = Message matching filter is stored in FIFO buffer 0                                                       |

|           |                                                                                                                                                                                |

Note: The bits in this register can only be modified if the corresponding filter enable (FLTENn) bit is '0'.

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |  |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|--|--|

| 21.24        | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |

| 31:24        | FLTEN19           | MSEL1             | 9<1:0>            |                   | FSEL19<4:0>       |                   |                  |                  |  |  |

| 00.40        | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |

| 23:16        | FLTEN18           | MSEL1             | 8<1:0>            | FSEL18<4:0>       |                   |                   |                  |                  |  |  |

| 45.0         | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |

| 15:8         | FLTEN17           | MSEL17<1:0>       |                   |                   | F                 | SEL17<4:0>        | >                |                  |  |  |

| 7.0          | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |

| 7:0          | FLTEN16           | MSEL16<1:0>       |                   | FSEL16<4:0>       |                   |                   |                  |                  |  |  |

## REGISTER 24-14: CIFLTCON4: CAN FILTER CONTROL REGISTER 4

### Legend:

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read as '0' |                    |

|-------------------|------------------|------------------------------------|--------------------|

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared               | x = Bit is unknown |

| bit 31    | <b>FLTEN19:</b> Filter 19 Enable bit<br>1 = Filter is enabled<br>0 = Filter is disabled                                                                                             |

|-----------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| bit 30-29 | MSEL19<1:0>: Filter 19 Mask Select bits<br>11 = Acceptance Mask 3 selected<br>10 = Acceptance Mask 2 selected<br>01 = Acceptance Mask 1 selected<br>00 = Acceptance Mask 0 selected |

| bit 28-24 | <pre>11111 = Message matching filter is stored in FIFO buffer 31 11110 = Message matching filter is stored in FIFO buffer 30</pre>                                                  |

|           | 00001 = Message matching filter is stored in FIFO buffer 1<br>00000 = Message matching filter is stored in FIFO buffer 0                                                            |

| bit 23    | FLTEN18: Filter 18 Enable bit                                                                                                                                                       |

|           | <ul><li>1 = Filter is enabled</li><li>0 = Filter is disabled</li></ul>                                                                                                              |

| bit 22-21 | MSEL18<1:0>: Filter 18 Mask Select bits                                                                                                                                             |

|           | <ul> <li>11 = Acceptance Mask 3 selected</li> <li>10 = Acceptance Mask 2 selected</li> <li>01 = Acceptance Mask 1 selected</li> <li>00 = Acceptance Mask 0 selected</li> </ul>      |

| bit 20-16 | FSEL18<4:0>: FIFO Selection bits                                                                                                                                                    |

|           | 11111 = Message matching filter is stored in FIFO buffer 31                                                                                                                         |

|           | 11110 = Message matching filter is stored in FIFO buffer 30                                                                                                                         |

|           |                                                                                                                                                                                     |

|           | •                                                                                                                                                                                   |

|           | 00001 = Message matching filter is stored in FIFO buffer 1<br>00000 = Message matching filter is stored in FIFO buffer 0                                                            |

|           |                                                                                                                                                                                     |

Note: The bits in this register can only be modified if the corresponding filter enable (FLTENn) bit is '0'.

## REGISTER 24-14: CIFLTCON4: CAN FILTER CONTROL REGISTER 4 (CONTINUED)

|           | (                                                           |

|-----------|-------------------------------------------------------------|

| bit 15    | FLTEN17: Filter 13 Enable bit                               |

|           | 1 = Filter is enabled                                       |

|           | 0 = Filter is disabled                                      |

| bit 14-13 | MSEL17<1:0>: Filter 17 Mask Select bits                     |

|           | 11 = Acceptance Mask 3 selected                             |

|           | 10 = Acceptance Mask 2 selected                             |

|           | 01 = Acceptance Mask 1 selected                             |

|           | 00 = Acceptance Mask 0 selected                             |

| bit 12-8  | FSEL17<4:0>: FIFO Selection bits                            |

|           | 11111 = Message matching filter is stored in FIFO buffer 31 |

|           | 11110 = Message matching filter is stored in FIFO buffer 30 |

|           | •                                                           |

|           |                                                             |

|           | 00001 = Message matching filter is stored in FIFO buffer 1  |

|           | 00000 = Message matching filter is stored in FIFO buffer 0  |

| bit 7     | FLTEN16: Filter 16 Enable bit                               |

|           | 1 = Filter is enabled                                       |

|           | 0 = Filter is disabled                                      |

| bit 6-5   | MSEL16<1:0>: Filter 16 Mask Select bits                     |

|           | 11 = Acceptance Mask 3 selected                             |

|           | 10 = Acceptance Mask 2 selected                             |

|           | 01 = Acceptance Mask 1 selected                             |

|           | 00 = Acceptance Mask 0 selected                             |

| bit 4-0   | FSEL16<4:0>: FIFO Selection bits                            |

|           | 11111 = Message matching filter is stored in FIFO buffer 31 |

|           | 11110 = Message matching filter is stored in FIFO buffer 30 |

|           | •                                                           |

|           | •                                                           |

|           | 00001 = Message matching filter is stored in FIFO buffer 1  |

|           | 00000 = Message matching filter is stored in FIFO buffer 0  |

| ·         |                                                             |

Note: The bits in this register can only be modified if the corresponding filter enable (FLTENn) bit is '0'.

#### **REGISTER 25-11: ETHRXFC: ETHERNET CONTROLLER RECEIVE FILTER CONFIGURATION REGISTER (CONTINUED)** bit 7 **CRCERREN:** CRC Error Collection Enable bit 1 = The received packet CRC must be invalid for the packet to be accepted 0 = Disable CRC Error Collection filtering This bit allows the user to collect all packets that have an invalid CRC. CRCOKEN: CRC OK Enable bit bit 6 1 = The received packet CRC must be valid for the packet to be accepted 0 = Disable CRC filtering This bit allows the user to reject all packets that have an invalid CRC. RUNTERREN: Runt Error Collection Enable bit bit 5 1 = The received packet must be a runt packet for the packet to be accepted 0 = Disable Runt Error Collection filtering This bit allows the user to collect all packets that are runt packets. For this filter, a runt packet is defined as any packet with a size of less than 64 bytes (when CRCOKEN = 0) or any packet with a size of less than 64 bytes that has a valid CRC (when CRCOKEN = 1). bit 4 RUNTEN: Runt Enable bit 1 = The received packet must not be a runt packet for the packet to be accepted 0 = Disable Runt filtering This bit allows the user to reject all runt packets. For this filter, a runt packet is defined as any packet with a size of less than 64 bytes. bit 3 UCEN: Unicast Enable bit 1 = Enable Unicast Filtering 0 = Disable Unicast Filtering This bit allows the user to accept all unicast packets whose Destination Address matches the Station Address. bit 2 NOTMEEN: Not Me Unicast Enable bit 1 = Enable Not Me Unicast Filtering 0 = Disable Not Me Unicast Filtering This bit allows the user to accept all unicast packets whose Destination Address does not match the Station Address. bit 1 MCEN: Multicast Enable bit 1 = Enable Multicast Filtering 0 = Disable Multicast Filtering This bit allows the user to accept all Multicast Address packets.

#### bit 0 BCEN: Broadcast Enable bit

- 1 = Enable Broadcast Filtering

- 0 = Disable Broadcast Filtering

This bit allows the user to accept all Broadcast Address packets.

- **Note 1:** XOR = True when either one or the other conditions are true, but not both.

- 2: This Hash Table Filter match is active regardless of the value of the HTEN bit.

- 3: This Magic Packet Filter match is active regardless of the value of the MPEN bit.

```

Note 1:

This register is only used for RX operations.

2:

The bits in this register may only be changed while the RXEN bit (ETHCON1<8>) = 0.

```

## REGISTER 25-22: ETHALGNERR: ETHERNET CONTROLLER ALIGNMENT ERRORS STATISTICS REGISTER

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|

|              | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 31:24        | —                 | —                 | _                 | _                 | _                 | _                 | _                | —                |

| 00.40        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 23:16        | —                 | —                 | _                 | _                 | _                 | _                 | _                | —                |

| 15:8         | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |

|              | ALGNERRCNT<15:8>  |                   |                   |                   |                   |                   |                  |                  |

| 7:0          | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |

|              |                   |                   |                   | ALGNERRO          | CNT<7:0>          |                   |                  |                  |

## Legend:

| Logona.           |                  |                           |                    |  |

|-------------------|------------------|---------------------------|--------------------|--|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, re | ead as '0'         |  |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared      | x = Bit is unknown |  |

### bit 31-16 Unimplemented: Read as '0'

bit 15-0 ALGNERRCNT<15:0>: Alignment Error Count bits

Increment count for frames with alignment errors. Note that an alignment error is a frame that has an FCS error and the frame length in bits is not an integral multiple of 8 bits (a.k.a., dribble nibble)

#### **Note 1:** This register is only used for RX operations.

2: This register is automatically cleared by hardware after a read operation, unless the byte enables for bytes 0/1 are '0'.

3: It is recommended to use the SET, CLR, or INV registers to set or clear any bit in this register. Setting or clearing any bits in this register should be only done for debug/test purposes.

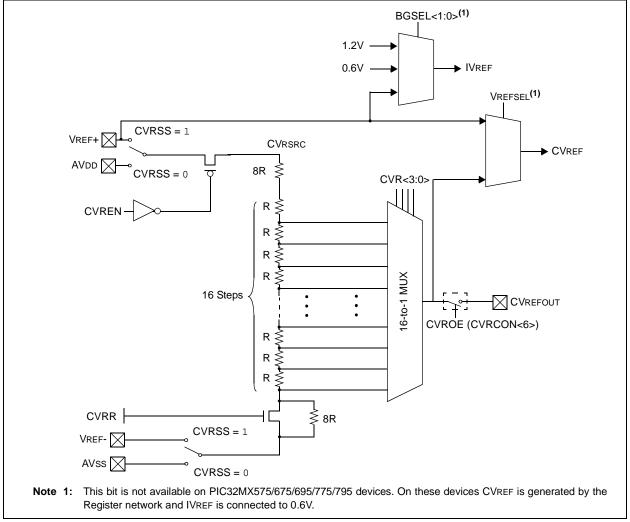

## 27.0 COMPARATOR VOLTAGE REFERENCE (CVREF)

Note: This data sheet summarizes the features of the PIC32MX5XX/6XX/7XX family of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to Section 20. "Comparator Voltage Reference (CVREF)" (DS60001109) in the "PIC32 Family Reference Manual", which is available from the Microchip web site (www.microchip.com/PIC32).

The CVREF module is a 16-tap, resistor ladder network that provides a selectable reference voltage. Although its primary purpose is to provide a reference for the analog comparators, it also may be used independently of them. A block diagram of the module is illustrated in Figure 27-1. The resistor ladder is segmented to provide two ranges of voltage reference values and has a power-down function to conserve power when the reference is not being used. The module's supply reference can be provided from either device VDD/Vss or an external voltage reference. The CVREF output is available for the comparators and typically available for pin output.

Key features of the CVREF module include:

- High and low range selection

- Sixteen output levels available for each range

- Internally connected to comparators to conserve device pins

- · Output can be connected to a pin

## REGISTER 29-1: DEVCFG0: DEVICE CONFIGURATION WORD 0 (CONTINUED)

- bit 3 ICESEL: In-Circuit Emulator/Debugger Communication Channel Select bit

- 1 = PGEC2/PGED2 pair is used

- 0 = PGEC1/PGED1 pair is used

- bit 2 Reserved: Write '1'

- bit 1-0 DEBUG<1:0>: Background Debugger Enable bits (forced to '11' if code-protect is enabled)

- 11 = Debugger is disabled

- 10 = Debugger is enabled

- 01 = Reserved (same as '11' setting)

- 00 = Reserved (same as '11' setting)

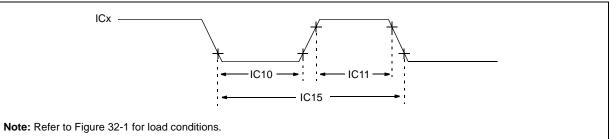

## FIGURE 32-7: INPUT CAPTURE (CAPx) TIMING CHARACTERISTICS

## TABLE 32-25: INPUT CAPTURE MODULE TIMING REQUIREMENTS

| AC CHARACTERISTICS |        | $\begin{array}{ll} \mbox{Standard Operating Conditions: 2.3V to 3.6V} \\ \mbox{(unless otherwise stated)} \\ \mbox{Operating temperature} & -40^{\circ}C \leq TA \leq +85^{\circ}C \mbox{ for Industrial} \\ & -40^{\circ}C \leq TA \leq +105^{\circ}C \mbox{ for V-Temp} \end{array}$ |  |                                   |      |       |                                         |                                  |