Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFl

| Details                    |                                                                                  |

|----------------------------|----------------------------------------------------------------------------------|

| Product Status             | Active                                                                           |

| Core Processor             | MIPS32® M4K™                                                                     |

| Core Size                  | 32-Bit Single-Core                                                               |

| Speed                      | 80MHz                                                                            |

| Connectivity               | CANbus, Ethernet, I <sup>2</sup> C, SPI, UART/USART, USB OTG                     |

| Peripherals                | Brown-out Detect/Reset, DMA, POR, PWM, WDT                                       |

| Number of I/O              |                                                                                  |

| Program Memory Size        | 256KB (256K x 8)                                                                 |

| Program Memory Type        | FLASH                                                                            |

| EEPROM Size                | -                                                                                |

| RAM Size                   | 64K x 8                                                                          |

| Voltage - Supply (Vcc/Vdd) | 2.3V ~ 3.6V                                                                      |

| Data Converters            | A/D 16x10b                                                                       |

| Oscillator Type            | Internal                                                                         |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                                |

| Mounting Type              | Surface Mount                                                                    |

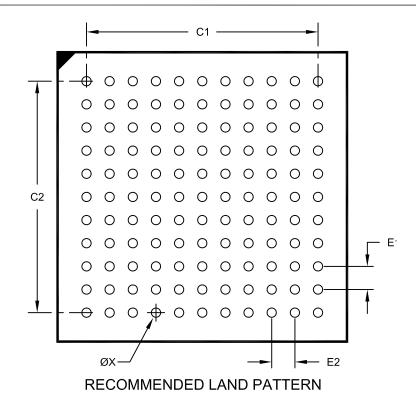

| Package / Case             | 121-TFBGA                                                                        |

| Supplier Device Package    | 121-TFBGA (10x10)                                                                |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic32mx775f256l-80i-bg |

|                            |                                                                                  |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

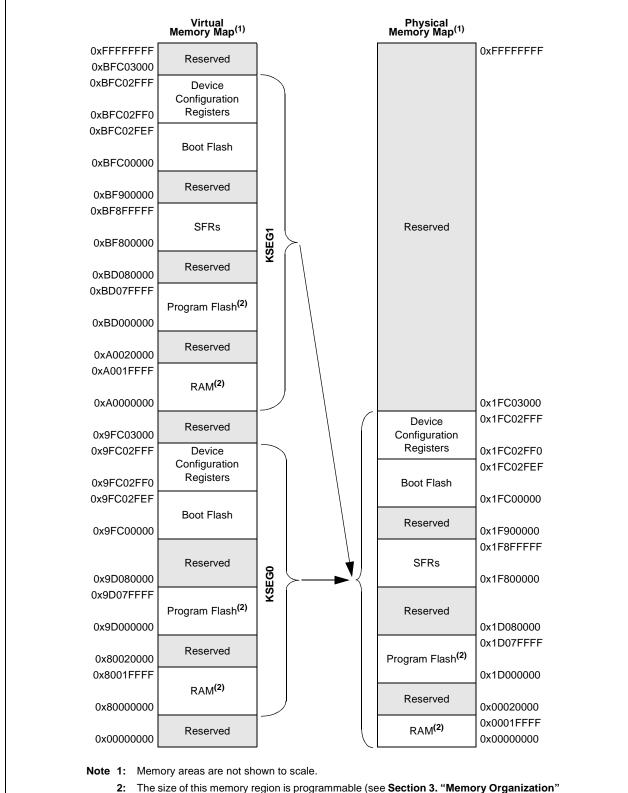

#### FIGURE 4-6: MEMORY MAP ON RESET FOR PIC32MX695F512H, PIC32MX695F512L, PIC32MX795F512H AND PIC32MX795F512L DEVICES

2: The size of this memory region is programmable (see Section 3. "Memory Organization" (DS60001115)) and can be changed by initialization code provided by end user development tools (refer to the specific development tool documentation for information).

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|

| 04.04        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 31:24        | —                 | —                 | —                 | —                 | _                 | —                 | —                | —                |

|              | U-0               | U-0               | U-0               | R/W-1             | R/W-1             | R/W-1             | R/W-1            | R/W-1            |

| 23:16        | _                 | _                 | —                 | BMX<br>ERRIXI     | BMX<br>ERRICD     | BMX<br>ERRDMA     | BMX<br>ERRDS     | BMX<br>ERRIS     |

| 45.0         | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 15:8         | —                 | —                 | —                 | —                 | _                 | —                 | —                | —                |

|              | U-0               | R/W-1             | U-0               | U-0               | U-0               | R/W-0             | R/W-0            | R/W-1            |

| 7:0          | _                 | BMX<br>WSDRM      | —                 | —                 | _                 | E                 | 3MXARB<2:0       | >                |

#### REGISTER 4-1: BMXCON: BUS MATRIX CONFIGURATION REGISTER

#### Legend:

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read as '0' |

|-------------------|------------------|------------------------------------|

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared               |

### bit 31-21 **Unimplemented:** Read as '0'

| bit 20   | BMXERRIXI: Enable Bus Error from IXI bit                                                                                                                                                                                              |

|----------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|          | <ul> <li>1 = Enable bus error exceptions for unmapped address accesses initiated from IXI shared bus</li> <li>0 = Disable bus error exceptions for unmapped address accesses initiated from IXI shared bus</li> </ul>                 |

| bit 19   | BMXERRICD: Enable Bus Error from ICD Debug Unit bit                                                                                                                                                                                   |

|          | <ul> <li>1 = Enable bus error exceptions for unmapped address accesses initiated from ICD</li> <li>0 = Disable bus error exceptions for unmapped address accesses initiated from ICD</li> </ul>                                       |

| bit 18   | BMXERRDMA: Bus Error from DMA bit                                                                                                                                                                                                     |

|          | <ul> <li>1 = Enable bus error exceptions for unmapped address accesses initiated from DMA</li> <li>0 = Disable bus error exceptions for unmapped address accesses initiated from DMA</li> </ul>                                       |

| bit 17   | BMXERRDS: Bus Error from CPU Data Access bit (disabled in Debug mode)                                                                                                                                                                 |

|          | <ul> <li>1 = Enable bus error exceptions for unmapped address accesses initiated from CPU data access</li> <li>0 = Disable bus error exceptions for unmapped address accesses initiated from CPU data access</li> </ul>               |

| bit 16   | BMXERRIS: Bus Error from CPU Instruction Access bit (disabled in Debug mode)                                                                                                                                                          |

|          | <ul> <li>1 = Enable bus error exceptions for unmapped address accesses initiated from CPU instruction access</li> <li>0 = Disable bus error exceptions for unmapped address accesses initiated from CPU instruction access</li> </ul> |

| bit 15-7 | Unimplemented: Read as '0'                                                                                                                                                                                                            |

| bit 6    | BMXWSDRM: CPU Instruction or Data Access from Data RAM Wait State bit                                                                                                                                                                 |

|          | <ul> <li>1 = Data RAM accesses from CPU have one wait state for address setup</li> <li>0 = Data RAM accesses from CPU have zero wait states for address setup</li> </ul>                                                              |

| bit 5-3  | Unimplemented: Read as '0'                                                                                                                                                                                                            |

| bit 2-0  | BMXARB<2:0>: Bus Matrix Arbitration Mode bits                                                                                                                                                                                         |

|          | 111 = Reserved (using these Configuration modes will produce undefined behavior)                                                                                                                                                      |

|          |                                                                                                                                                                                                                                       |

|          | •                                                                                                                                                                                                                                     |

|          | 011 = Reserved (using these Configuration modes will produce undefined behavior)                                                                                                                                                      |

|          | 010 = Arbitration Mode 2<br>001 = Arbitration Mode 1 (default)                                                                                                                                                                        |

|          | 000 = Arbitration Mode 0                                                                                                                                                                                                              |

#### 11.1 **Control Registers**

#### TABLE 11-1: USB REGISTER MAP

| Signature         Signature           5040         U10TGIR <sup>(2)</sup> 5050         U10TGIR <sup>(2)</sup> 5060         U10TGSTAT           5070         U10TGCO           5080         U11PWRC           5200         U11R <sup>(2)</sup> 5210         U11EIR <sup>(2)</sup> 5220         U1EIR <sup>(2)</sup> 5220         U1EIR <sup>(2)</sup> | 2) 31:<br>15:<br>15:<br>15:<br>15:<br>15:<br>15:<br>15:<br>1                                | i:16       5:0       1:16       5:0       1:16       5:0       1:16       5:0       1:16 | 31/15<br>        | 30/14<br> | 29/13<br> | 28/12 | 27/11 | 26/10 | 25/9 | 24/8 | Bits<br>23/7           | 22/6               | 04/5                 |            |           |          |                 | r        | Resets |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------|------------------|-----------|-----------|-------|-------|-------|------|------|------------------------|--------------------|----------------------|------------|-----------|----------|-----------------|----------|--------|

| 5040         U10TGIR <sup>(2)</sup> 5050         U10TGIE           5060         U10TGSTAT           5070         U10TGCO           5080         U1PWRC           5200         U1IR <sup>(2)</sup> 5210         U1IE           5220         U1EIR <sup>(2)</sup>                                                                                      | 2) 31:<br>15:<br>15:<br>15:<br>15:<br>15:<br>15:<br>15:<br>1                                | 1:16<br>5:0<br>1:16<br>5:0<br>1:16<br>5:0<br>1:16                                        |                  | -         |           | -     |       |       | 25/9 | 24/8 | 23/7                   | 22/6               | 04/5                 |            |           | ļ        |                 |          | eset   |

| 5050         U10TGIE           5060         U10TGSTAT           5070         U10TGCO           5080         U1PWRC           5200         U1IR <sup>(2)</sup> 5210         U1IE           5220         U1EIR <sup>(2)</sup>                                                                                                                          | 2) 15<br>31:<br>15<br>(3) 31:<br>(3) 31:<br>15<br>15<br>31:<br>Ν 31:<br>31                  | 5:0<br>1:16<br>5:0<br>1:16<br>5:0<br>1:16                                                | —<br>—<br>—<br>— | -         | _         |       | _     |       |      |      |                        | 22/0               | 21/5                 | 20/4       | 19/3      | 18/2     | 17/1            | 16/0     | All Re |

| 5050         U10TGIE           5060         U10TGSTAT           5070         U10TGCO           5080         U1PWRC           5200         U1IR <sup>(2)</sup> 5210         U1IE           5220         U1EIR <sup>(2)</sup>                                                                                                                          | 15<br>31:<br>15<br>(3)<br>31:<br>15<br>31:<br>Ν<br>31:<br>31:                               | 1:16<br>5:0<br>1:16<br>5:0<br>1:16                                                       | -<br>-<br>-      |           |           |       |       | —     | -    | _    | _                      | —                  | —                    | —          | _         | —        | —               | —        | 0000   |

| 5060         U1OTGSTAT           5070         U1OTGCO           5080         U1PWRC           5200         U1IR <sup>(2)</sup> 5210         U1IE           5220         U1EIR <sup>(2)</sup>                                                                                                                                                         | 15<br>(3) 31:<br>15:<br>Ν 31:<br>15:<br>31:<br>31:<br>31:<br>31:<br>31:<br>31:<br>31:<br>31 | 5:0<br>1:16<br>5:0<br>1:16                                                               | -                | —         |           |       | _     |       |      | —    | IDIF                   | T1MSECIF           | LSTATEIF             | ACTVIF     | SESVDIF   | SESENDIF | _               | VBUSVDIF | 0000   |

| 5060         U1OTGSTAT           5070         U1OTGCO           5080         U1PWRC           5200         U1IR <sup>(2)</sup> 5210         U1IE           5220         U1EIR <sup>(2)</sup>                                                                                                                                                         | 15:<br>T <sup>(3)</sup> 31:<br>15:<br>N 31:<br>15:<br>31:<br>31:                            | 1:16<br>5:0<br>1:16                                                                      | -                | -         | —         |       | _     |       |      | —    | _                      | —                  | _                    | -          | _         | —        | _               | _        | 0000   |

| 5070         U1OTGCO           5080         U1PWRC           5200         U1IR <sup>(2)</sup> 5210         U1IE           5220         U1EIR <sup>(2)</sup>                                                                                                                                                                                          | N 15:<br>31:<br>31:<br>31:                                                                  | 5:0<br>1:16                                                                              |                  |           |           | _     | _     |       | _    | _    | IDIE                   | T1MSECIE           | LSTATEIE             | ACTVIE     | SESVDIE   | SESENDIE | _               | VBUSVDIE | 0000   |

| 5070         U1OTGCO           5080         U1PWRC           5200         U1IR <sup>(2)</sup> 5210         U1IE           5220         U1EIR <sup>(2)</sup>                                                                                                                                                                                          | N 31:<br>31:<br>31:<br>31:                                                                  | 1:16                                                                                     |                  | -         | _         |       | _     |       |      | —    | _                      | —                  | _                    | -          | —         | —        |                 | —        | 0000   |

| 5080         U1PWRC           5200         U1IR <sup>(2)</sup> 5210         U1IE           5220         U1EIR <sup>(2)</sup>                                                                                                                                                                                                                         | N 15                                                                                        |                                                                                          | _                | -         | _         |       | _     |       |      | —    | ID                     | —                  | LSTATE               | -          | SESVD     | SESEND   |                 | VBUSVD   | 0000   |

| 5080         U1PWRC           5200         U1IR <sup>(2)</sup> 5210         U1IE           5220         U1EIR <sup>(2)</sup>                                                                                                                                                                                                                         | 31                                                                                          | E:0                                                                                      | _                | _         | _         | _     | —     | _     | _    | -    |                        | _                  | —                    | —          | —         | —        | —               | —        | 0000   |

| 5200         U1IR <sup>(2)</sup> 5210         U1IE           5220         U1EIR <sup>(2)</sup>                                                                                                                                                                                                                                                       | 31:                                                                                         | 5.0                                                                                      | _                | _         | _         | _     | —     | _     |      |      | DPPULUP                | DMPULUP            | DPPULDWN             | DMPULDWN   | VBUSON    | OTGEN    | VBUSCHG         | VBUSDIS  | 0000   |

| 5200         U1IR <sup>(2)</sup> 5210         U1IE           5220         U1EIR <sup>(2)</sup>                                                                                                                                                                                                                                                       |                                                                                             | 1:16                                                                                     | _                | -         | _         |       | -     |       |      | —    | _                      | —                  | _                    | -          | —         | _        |                 | —        | 0000   |

| 5210 U1IE<br>5220 U1EIR <sup>(2)</sup>                                                                                                                                                                                                                                                                                                               | 15                                                                                          | 5:0                                                                                      | _                | _         | _         | _     | —     | _     | _    | -    | UACTPND <sup>(4)</sup> | _                  | —                    | USLPGRD    | USBBUSY   | —        | USUSPEND        | USBPWR   | 0000   |

| 5210 U1IE<br>5220 U1EIR <sup>(2)</sup>                                                                                                                                                                                                                                                                                                               | 31:                                                                                         | 1:16                                                                                     | _                | _         | _         | _     | —     | _     |      |      |                        | _                  | —                    | —          | —         | —        | —               | —        | 0000   |

| 5220 U1EIR <sup>(2)</sup>                                                                                                                                                                                                                                                                                                                            | 15                                                                                          | 5:0                                                                                      | _                | _         | _         |       | _     |       |      | _    | STALLIF                | ATTACHIF           | RESUMEIF             | IDLEIF     | TRNIF     | SOFIF    | UERRIF          | URSTIF   | 0000   |

| 5220 U1EIR <sup>(2)</sup>                                                                                                                                                                                                                                                                                                                            | _                                                                                           |                                                                                          |                  |           |           |       |       |       |      |      | -                      |                    |                      |            |           |          |                 | DETACHIF | 0000   |

| 5220 U1EIR <sup>(2)</sup>                                                                                                                                                                                                                                                                                                                            | 31:                                                                                         | 1:16                                                                                     | _                | _         | —         | —     | —     | —     | —    | _    | —                      | —                  | —                    | —          | —         | —        | —               |          | 0000   |

|                                                                                                                                                                                                                                                                                                                                                      | 15                                                                                          | 5:0                                                                                      | _                | _         | _         | _     | _     | _     | _    | _    | STALLIE                | ATTACHIE           | RESUMEIE             | IDLEIE     | TRNIE     | SOFIE    | UERRIE          | URSTIE   | 0000   |

|                                                                                                                                                                                                                                                                                                                                                      |                                                                                             |                                                                                          |                  |           |           |       |       |       |      |      |                        |                    |                      |            |           |          |                 |          | 0000   |

|                                                                                                                                                                                                                                                                                                                                                      | 31:                                                                                         | 1:16                                                                                     | _                | _         | _         | _     | _     | _     | _    | _    | —                      |                    | —                    | —          | _         |          | _               | —        | 0000   |

| 5230 U1EIE                                                                                                                                                                                                                                                                                                                                           | 15                                                                                          | 5:0                                                                                      | _                | _         | _         | _     | _     | _     | _    | —    | BTSEF                  | BMXEF              | DMAEF                | BTOEF      | DFN8EF    | CRC16EF  | CRC5EF<br>EOFEF | PIDEF    | 0000   |

| 5230 U1EIE                                                                                                                                                                                                                                                                                                                                           | 31.                                                                                         | 1:16                                                                                     | _                | _         | _         | _     | _     | _     | _    |      | _                      | _                  | _                    | _          | _         | _        | _               | _        | 0000   |

| SZSG OTELE                                                                                                                                                                                                                                                                                                                                           | 51.                                                                                         | 1.10                                                                                     |                  |           |           |       |       |       |      |      |                        |                    |                      |            |           |          | CRC5EE          |          | 0000   |

|                                                                                                                                                                                                                                                                                                                                                      | 15                                                                                          | 5:0                                                                                      | —                | —         | —         | —     | —     | —     | —    | —    | BTSEE                  | BMXEE              | DMAEE                | BTOEE      | DFN8EE    | CRC16EE  | EOFEE           | PIDEE    | 0000   |

| (2)                                                                                                                                                                                                                                                                                                                                                  | 、 31:                                                                                       | 1:16                                                                                     | _                | _         | _         | _     | _     |       | _    | _    | _                      | _                  | _                    | _          | _         |          | _               | _        | 0000   |

| 5240 U1STAT <sup>(3)</sup>                                                                                                                                                                                                                                                                                                                           | ,                                                                                           | 5:0                                                                                      | _                | _         | _         | _     | _     | _     | _    | _    |                        | ENDPT              | <3:0> <sup>(4)</sup> |            | DIR       | PPBI     | _               | _        | 0000   |

|                                                                                                                                                                                                                                                                                                                                                      | -                                                                                           | 1:16                                                                                     | _                | _         | _         | _     | _     | _     | _    | _    | _                      | _                  | _                    | _          | _         | _        | _               | _        | 0000   |

| 5250 U1CON                                                                                                                                                                                                                                                                                                                                           |                                                                                             |                                                                                          |                  |           |           |       |       |       |      |      | 10TATE(4)              | 0.5 0(4)           | PKTDIS               |            |           |          |                 | USBEN    | 0000   |

|                                                                                                                                                                                                                                                                                                                                                      |                                                                                             | 5:0                                                                                      | —                | _         | _         | —     | —     | —     | —    |      | JSTATE <sup>(4)</sup>  | SE0 <sup>(4)</sup> | TOKBUSY              | USBRST     | HOSTEN    | RESUME   | PPBRST          | SOFEN    | 0000   |

| 5260 U1ADDR                                                                                                                                                                                                                                                                                                                                          | 15                                                                                          | 1:16                                                                                     | _                | _         | _         | _     | _     | _     | _    | _    |                        | —                  | _                    | _          | —         | —        | _               | —        | 0000   |

| 5200 UTADDR                                                                                                                                                                                                                                                                                                                                          | 31:                                                                                         | 5:0                                                                                      | —                | _         | —         | _     | _     | _     | _    | _    | LSPDEN                 |                    |                      | DE         | VADDR<6:0 | 1>       |                 |          | 0000   |

| 5270 U1BDTP1                                                                                                                                                                                                                                                                                                                                         | 31:                                                                                         |                                                                                          | —                | _         | —         | _     | _     | _     | _    | _    | _                      | _                  | —                    | _          | _         | —        | _               | —        | 0000   |

| JZIU UIBDIPI                                                                                                                                                                                                                                                                                                                                         | 31:<br>15:                                                                                  | 1:16                                                                                     |                  | _         | _         | _     | _     | _     |      | _    |                        |                    | BD                   | TPTRL<7:1> |           |          |                 |          | 0000   |

x = unknown value on Reset; — = unimplemented, read as '0'. Reset values are shown in hexadecimal. Legend:

All registers in this table (except as noted) have corresponding CLR, SET and INV registers at its virtual address, plus an offset of 0x4, 0x8 and 0xC respectively. See Section 12.1.1 "CLR, SET and INV Registers" for Note 1: more information.

2:

This register does not have associated SET and INV registers. This register does not have associated CLR, SET and INV registers. 3:

4: Reset value for this bit is undefined.

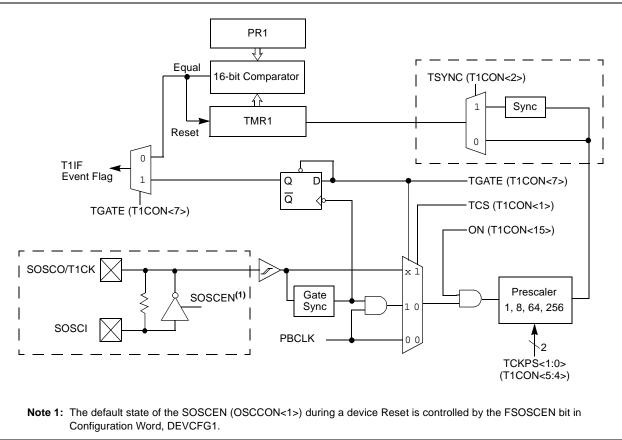

#### 13.0 TIMER1

Note: This data sheet summarizes the features of the PIC32MX5XX/6XX/7XX family of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to **Section 14. "Timers"** (DS60001105) in the *"PIC32 Family Reference Manual"*, which is available from the Microchip web site (www.microchip.com/PIC32).

This family of PIC32 devices features one synchronous/ asynchronous 16-bit timer that can operate as a free-running interval timer for various timing applications and counting external events. This timer can also be used with the low-power Secondary Oscillator (Sosc) for Real-Time Clock (RTC) applications. The following modes are supported:

- Synchronous Internal Timer

- Synchronous Internal Gated Timer

- Synchronous External Timer

- Asynchronous External Timer

#### FIGURE 13-1: TIMER1 BLOCK DIAGRAM

#### 13.1 Additional Supported Features

- Selectable clock prescaler

- Timer operation during Idle and Sleep mode

- Fast bit manipulation using CLR, SET and INV registers

- Asynchronous mode can be used with the Sosc to function as a Real-Time Clock (RTC)

A simplified block diagram of the Timer1 module is illustrated in Figure 13-1.

#### 16.1 Control Registers

| ess                         |                       |               |       |       |       |       |       |       |       | Bi      | ts      |      |      |      |        |      |            |      |              |

|-----------------------------|-----------------------|---------------|-------|-------|-------|-------|-------|-------|-------|---------|---------|------|------|------|--------|------|------------|------|--------------|

| Virtual Address<br>(BF80_#) | Register<br>Name      | Bit Range     | 31/15 | 30/14 | 29/13 | 28/12 | 27/11 | 26/10 | 25/9  | 24/8    | 23/7    | 22/6 | 21/5 | 20/4 | 19/3   | 18/2 | 17/1       | 16/0 | All Resets   |

| 2000                        | IC1CON <sup>(1)</sup> | 31:16         |       | —     | —     | —     | _     | —     | _     | _       | _       | —    | —    | _    | —      | —    | _          | _    | 0000         |

| 2000                        | IC ICON.              | 15:0          | ON    | _     | SIDL  | _     | _     | _     | FEDGE | C32     | ICTMR   | ICI< | 1:0> | ICOV | ICBNE  |      | ICM<2:0>   |      | 0000         |

| 2010                        | IC1BUF                | 31:16         |       |       |       |       |       |       |       | IC1BUF  | ~31.0>  |      |      |      |        |      |            |      | xxxx         |

| 2010                        |                       | 15:0          |       |       |       |       |       |       |       | 101201  |         |      |      | -    |        |      |            |      | xxxx         |

| 2200                        | IC2CON <sup>(1)</sup> | 31:16         |       | _     | —     | —     | _     | _     | —     | _       | _       | _    | _    | —    | —      |      | —          | —    | 0000         |

| 2200                        | .0200.1               | 15:0          | ON    | —     | SIDL  | —     | —     | —     | FEDGE | C32     | ICTMR   | ICI< | 1:0> | ICOV | ICBNE  |      | ICM<2:0>   |      | 0000         |

| 2210                        | IC2BUF                | 31:16         |       |       |       |       |       |       |       | IC2BUF  | <31:0>  |      |      |      |        |      |            |      | xxxx         |

|                             |                       | 15:0          |       |       | -     |       |       |       |       |         |         |      |      |      | -      |      |            |      | xxxx         |

| 2400                        | IC3CON <sup>(1)</sup> | 31:16         | -     | _     | -     | _     | _     | —     | _     | _       | -       | -    | —    | —    | —      |      | -          |      | 0000         |

|                             |                       | 15:0          | ON    | —     | SIDL  | —     | —     | —     | FEDGE | C32     | ICTMR   | ICI< | 1:0> | ICOV | ICBNE  |      | ICM<2:0>   |      | 0000         |

| 2410                        | IC3BUF                | 31:16         |       |       |       |       |       |       |       | IC3BUF  | <31:0>  |      |      |      |        |      |            |      | XXXX         |

|                             |                       | 15:0          |       |       | 1     |       |       |       |       |         |         |      |      |      | 1      |      |            |      | XXXX         |

| 2600                        | IC4CON <sup>(1)</sup> | 31:16         | -     |       | -     | _     |       |       | -     | -       | -       | -    |      | —    |        | —    | -          | _    | 0000         |

|                             |                       | 15:0          | ON    | _     | SIDL  | —     | —     | —     | FEDGE | C32     | ICTMR   | ICI< | 1:0> | ICOV | ICBNE  |      | ICM<2:0>   |      | 0000         |

| 2610                        | IC4BUF                | 31:16<br>15:0 |       |       |       |       |       |       |       | IC4BUF  | <31:0>  |      |      |      |        |      |            |      | XXXX         |

|                             |                       | 31:16         |       | _     | _     | _     | _     |       | _     | _       | _       | _    |      |      | _      |      | _          | _    | xxxx<br>0000 |

| 2800                        | IC5CON <sup>(1)</sup> | 15:0          | ON    | _     |       | _     |       |       | FEDGE | <br>C32 | ICTMR   | ICI< |      | ICOV | ICBNE  |      | ICM<2:0>   |      |              |

|                             |                       | 31:16         | UN    |       | SIDL  | —     | _     |       | FEDGE | 632     | ICTIVIR |      | 1.0> | 1000 | ICDINE | l    | 10101<2.0> |      | 0000         |

| 2810                        | IC5BUF                | 15:0          |       |       |       |       |       |       |       | IC5BUF  | <31:0>  |      |      |      |        |      |            |      | XXXX         |

|                             |                       | 15.0          |       |       |       |       |       |       |       |         |         |      |      |      |        |      |            |      | XXXX         |

#### TABLE 16-1: INPUT CAPTURE 1-INPUT CAPTURE 5 REGISTER MAP

Legend: x = unknown value on Reset; — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

Note 1: This register has corresponding CLR, SET and INV registers at its virtual address, plus an offset of 0x4, 0x8 and 0xC, respectively. See Section 12.1.1 "CLR, SET and INV Registers" for more information.

| REGIST    | ER 18-1: SPIxCON: SPI CONTROL REGISTER (CONTINUED)                                                                                                                                              |

|-----------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| bit 15    | <b>ON:</b> SPI Peripheral On bit <sup>(1)</sup>                                                                                                                                                 |

|           | 1 = SPI Peripheral is enabled                                                                                                                                                                   |

| bit 11    | 0 = SPI Peripheral is disabled                                                                                                                                                                  |

| bit 14    | Unimplemented: Read as '0'                                                                                                                                                                      |

| bit 13    | SIDL: Stop in Idle Mode bit<br>1 = Discontinue operation when CPU enters in Idle mode                                                                                                           |

|           | 0 = Continue operation in Idle mode                                                                                                                                                             |

| bit 12    | <b>DISSDO:</b> Disable SDOx pin bit                                                                                                                                                             |

|           | 1 = SDOx pin is not used by the module (pin is controlled by associated PORT register)                                                                                                          |

|           | 0 = SDOx pin is controlled by the module                                                                                                                                                        |

| bit 11-10 | MODE<32,16>: 32/16-Bit Communication Select bits                                                                                                                                                |

|           | MODE32 MODE16 Communication                                                                                                                                                                     |

|           | 1 x 32-bit<br>0 1 16-bit                                                                                                                                                                        |

|           | 0 1 16-bit<br>0 0 8-bit                                                                                                                                                                         |

| bit 9     | SMP: SPI Data Input Sample Phase bit                                                                                                                                                            |

|           | Master mode (MSTEN = 1):                                                                                                                                                                        |

|           | 1 = Input data sampled at end of data output time                                                                                                                                               |

|           | 0 = Input data sampled at middle of data output time                                                                                                                                            |

|           | Slave mode (MSTEN = 0):                                                                                                                                                                         |

|           | SMP value is ignored when SPI is used in Slave mode. The module always uses SMP = 0.                                                                                                            |

| bit 8     | CKE: SPI Clock Edge Select bit <sup>(3)</sup>                                                                                                                                                   |

|           | 1 = Serial output data changes on transition from active clock state to Idle clock state (see CKP bit)                                                                                          |

| h:+ 7     | 0 = Serial output data changes on transition from Idle clock state to active clock state (see CKP bit)                                                                                          |

| bit 7     | SSEN: Slave Select Enable (Slave mode) bit<br>1 = SSx pin used for Slave mode                                                                                                                   |

|           | 0 = SSx pin not used for Slave mode (pin is controlled by port function)                                                                                                                        |

| bit 6     | CKP: Clock Polarity Select bit                                                                                                                                                                  |

|           | 1 = Idle state for clock is a high level; active state is a low level                                                                                                                           |

|           | 0 = Idle state for clock is a low level; active state is a high level                                                                                                                           |

| bit 5     | MSTEN: Master Mode Enable bit                                                                                                                                                                   |

|           | 1 = Master mode<br>0 = Slave mode                                                                                                                                                               |

| bit 4     | Unimplemented: Read as '0'                                                                                                                                                                      |

| bit 3-2   | STXISEL<1:0>: SPI Transmit Buffer Empty Interrupt Mode bits                                                                                                                                     |

| Dit 0-2   | 11 = Interrupt is generated when the buffer is not full (has one or more empty elements)                                                                                                        |

|           | 10 = Interrupt is generated when the buffer is empty by one-half or more                                                                                                                        |

|           | 01 = Interrupt is generated when the buffer is completely empty                                                                                                                                 |

|           | 00 = Interrupt is generated when the last transfer is shifted out of SPISR and transmit operations are                                                                                          |

|           | complete                                                                                                                                                                                        |

| bit 1-0   | SRXISEL<1:0>: SPI Receive Buffer Full Interrupt Mode bits<br>11 = Interrupt is generated when the buffer is full                                                                                |

|           | 10 = Interrupt is generated when the buffer is full by one-half or more                                                                                                                         |

|           | 01 = Interrupt is generated when the buffer is not empty                                                                                                                                        |

|           | 00 = Interrupt is generated when the last word in the receive buffer is read (i.e., buffer is empty)                                                                                            |

|           | When using the 1.1 DROLK divisor the user's activisity should not used anywrite the mentation " OFR i                                                                                           |

| Note 1:   | When using the 1:1 PBCLK divisor, the user's software should not read or write the peripheral's SFRs in the SYSCLK cycle immediately following the instruction that clears the module's ON bit. |

| 2:        | This bit can only be written when the ON bit = $0$ .                                                                                                                                            |

| 3:        | This bit is not used in the Framed SPI mode. The user should program this bit to '0' for the Framed SPI                                                                                         |

| 0.        | mode (FRMEN = 1).                                                                                                                                                                               |

|           |                                                                                                                                                                                                 |

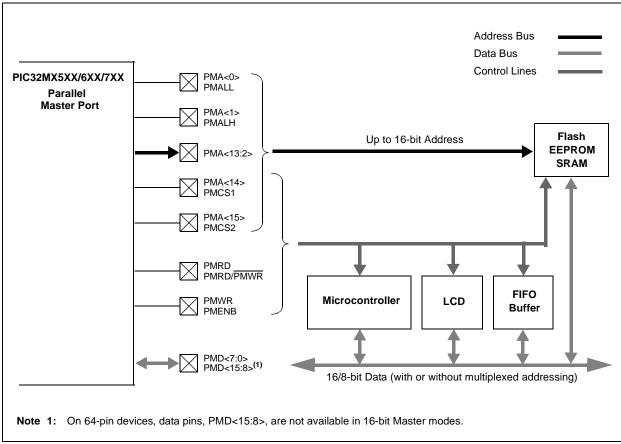

#### 21.0 PARALLEL MASTER PORT (PMP)

Note: This data sheet summarizes the features of the PIC32MX5XX/6XX/7XX family of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to Section 13. "Parallel Master Port (PMP)" (DS60001128) in the "PIC32 Family Reference Manual", which is available from the Microchip web site (www.microchip.com/PIC32).

The PMP is a parallel 8-bit/16-bit input/output module specifically designed to communicate with a wide variety of parallel devices, such as communications peripherals, LCDs, external memory devices and microcontrollers. Because the interface to parallel peripherals varies significantly, the PMP module is highly configurable. Figure 21-1 shows the PMP module pinout and its connections to external devices.

**FIGURE 21-1:**

The following are key features of the PMP module:

- 8-bit and 16-bit interface

- Up to 16 programmable address lines

- Up to two Chip Select lines

- Programmable strobe options

- Individual read and write strobes, or

- Read/Write strobe with enable strobe

- · Address auto-increment/auto-decrement

- · Programmable address/data multiplexing

- Programmable polarity on control signals

- · Parallel Slave Port support

- Legacy addressable

- Address support

- 4-byte deep auto-incrementing buffer

- · Programmable wait states

- · Operates during Sleep and Idle modes

- Fast bit manipulation using CLR, SET and INV registers

Note: On 64-pin devices, the PMD<15:8> data pins are not available.

PMP MODULE PINOUT AND CONNECTIONS TO EXTERNAL DEVICES

# TABLE 24-1: CAN1 REGISTER SUMMARY FOR PIC32MX534F064H, PIC32MX564F064H, PIC32MX564F128H, PIC32MX575F256H, PIC32MX575F512H, PIC32MX764F128H, PIC32MX775F256H, PIC32MX775F512H, PIC32MX795F512H, PIC32MX534F064L, PIC32MX564F064L, PIC32MX564F128L, PIC32MX575F256L, PIC32MX575F512L, PIC32MX764F128L, PIC32MX775F256L, PIC32MX775F512L AND PIC32MX795F512L DEVICES (CONTINUED)

| <i>(</i> 0                  |                                 |               |                                 | -                                                                                    |                                                                                        |                                                                                   |                                                                     |            |          |           | ,       |        |            |       |          |            |          |                | <b>T</b> |

|-----------------------------|---------------------------------|---------------|---------------------------------|--------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------|---------------------------------------------------------------------|------------|----------|-----------|---------|--------|------------|-------|----------|------------|----------|----------------|----------|

| ess                         |                                 | -             |                                 |                                                                                      |                                                                                        |                                                                                   |                                                                     |            |          | Bits      | 5       |        |            |       |          |            |          |                |          |

| Virtual Address<br>(BF88_#) | Register<br>Name <sup>(1)</sup> | Bit Range     | 31/15                           | 1/15 30/14 29/13 28/12 27/11 26/10 25/9 24/8 23/7 22/6 21/5 20/4 19/3 18/2 17/1 16/0 |                                                                                        |                                                                                   |                                                                     |            |          |           |         |        | All Resets |       |          |            |          |                |          |

| DOEO                        | C1FLTCON3                       | 31:16         | FLTEN15                         | MSEL1                                                                                | 5<1:0>                                                                                 |                                                                                   |                                                                     | FSEL15<4:0 | >        |           | FLTEN14 | MSEL1  | 4<1:0>     |       | F        | SEL14<4:0> | >        |                | 0000     |

| DUFU                        | CIFLICONS                       | 15:0          | FLTEN13                         | MSEL1                                                                                | 3<1:0>                                                                                 |                                                                                   | FSEL13<4:0>         FLTEN12         MSEL12<1:0>         FSEL12<4:0> |            |          |           |         |        |            |       |          | >          |          | 0000           |          |

| P100                        | C1FLTCON4                       | 31:16         | FLTEN19                         | MSEL1                                                                                | 9<1:0>                                                                                 |                                                                                   | FSEL19<4:0> FLTEN18 MSEL18<1:0> FSEL18<4:0>                         |            |          |           |         |        |            |       |          | >          |          | 0000           |          |

| ыю                          | CIFEICON4                       | 15:0          | FLTEN17                         | MSEL1                                                                                | 7<1:0>                                                                                 |                                                                                   | FSEL17<4:0>         FLTEN16         MSEL16<1:0>         FSEL16<4:0> |            |          |           |         |        |            |       |          |            |          | 0000           |          |

| <b>B</b> 110                | C1FLTCON5                       | 31:16         | FLTEN23                         | MSEL2                                                                                | MSEL23<1:0> FSEL23<4:0> FLTEN22 MSEL22<1:0> FSEL22<4:0> 000                            |                                                                                   |                                                                     |            |          |           |         |        |            |       | 0000     |            |          |                |          |

| ыно                         | CIFLICONS                       | 15:0          | FLTEN21                         | MSEL2                                                                                | SEL21<1:0> FSEL21<4:0> FLTEN20 MSEL20<1:0> FSEL20<4:0> (                               |                                                                                   |                                                                     |            |          |           |         |        |            |       | 0000     |            |          |                |          |

| P120                        | C1FLTCON6                       | 31:16         | FLTEN27                         | MSEL2                                                                                | 7<1:0>                                                                                 | FSEL27<4:0> FLTEN26 MSEL26<1:0> FSEL26<4:0>                                       |                                                                     |            |          |           |         |        |            |       |          | 0000       |          |                |          |

| D120                        | CIFLICON                        | 15:0          | FLTEN25                         | MSEL2                                                                                | 5<1:0>                                                                                 | FSEL25<4:0>         FLTEN24         MSEL24<1:0>         FSEL24<4:0>               |                                                                     |            |          |           |         |        |            |       |          | 0000       |          |                |          |

| B130                        | C1FLTCON7                       |               | FLTEN31                         | MSEL3                                                                                | SEL31<1:0>         FSEL31<4:0>         FLTEN30         MSEL30<1:0>         FSEL30<4:0> |                                                                                   |                                                                     |            |          |           |         |        |            |       | 0000     |            |          |                |          |

| D130                        | CILECON                         | 15:0          | FLTEN29                         | MSEL2                                                                                | 9<1:0>                                                                                 | K1:0>         FSEL29<4:0>         FLTEN28         MSEL28<1:0>         FSEL28<4:0> |                                                                     |            |          |           |         |        |            |       |          | 0000       |          |                |          |

| B140                        | 0                               | 31:16         |                                 |                                                                                      | SID<10:0> EXID EID<17:16>                                                              |                                                                                   |                                                                     |            |          |           |         |        | 7:16>      | xxxx  |          |            |          |                |          |

| DING                        |                                 | 15:0          |                                 |                                                                                      |                                                                                        |                                                                                   |                                                                     |            |          | EID<1     | 5:0>    |        |            |       |          |            |          |                | xxxx     |

| B340                        | C1FIFOBA                        | 31:16<br>15:0 |                                 |                                                                                      |                                                                                        |                                                                                   |                                                                     |            |          | C1FIFOBA  | <31:0>  |        |            |       |          |            |          |                | 0000     |

|                             | C1FIFOCONn                      | 31:16         |                                 | _                                                                                    | _                                                                                      |                                                                                   | _                                                                   | _          | _        | _         | _       | _      | _          |       |          | -SIZE<4:0> |          |                | 0000     |

| B350                        | (n = 0-31)                      | 15:0          | _                               | FRESET                                                                               | UINC                                                                                   | DONLY                                                                             | _                                                                   | _          | _        | _         | TXEN    | TXABAT | TXLARB     | TXERR | TXREQ    | RTREN      | TXPRI    | <1:0>          | 0000     |

| Dooo                        | C1FIFOINTn                      | 31:16         | _                               | _                                                                                    |                                                                                        | _                                                                                 | _                                                                   | TXNFULLIE  | TXHALFIE | TXEMPTYIE | _       | _      | _          | _     | RXOVFLIE | RXFULLIE   | RXHALFIE | RXN<br>EMPTYIE | 0000     |

| B360                        | (n = 0-31)                      | 15:0          | _                               | _                                                                                    |                                                                                        | _                                                                                 | _                                                                   | TXNFULLIF  | TXHALFIF | TXEMPTYIF | _       | -      | -          | _     | RXOVFLIF | RXFULLIF   | RXHALFIF | RXN<br>EMPTYIF | 0000     |

| B370                        | C1FIFOUAn                       |               |                                 |                                                                                      |                                                                                        |                                                                                   |                                                                     |            |          |           | 0000    |        |            |       |          |            |          |                |          |

| 2010                        |                                 | 15:0          | 5:0                             |                                                                                      |                                                                                        |                                                                                   |                                                                     |            |          |           |         | 0000   |            |       |          |            |          |                |          |

| B380                        | C1FIFOCIn                       |               |                                 |                                                                                      |                                                                                        |                                                                                   |                                                                     |            |          |           |         | 0000   |            |       |          |            |          |                |          |

|                             |                                 | 15:0          | <u> C1FIFOCI&lt;4:0&gt;</u> 000 |                                                                                      |                                                                                        |                                                                                   |                                                                     |            |          |           |         | 0000   |            |       |          |            |          |                |          |

Legend: x = unknown value on Reset; — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

Note 1: All registers in this table have corresponding CLR, SET and INV registers at their virtual addresses, plus offsets of 0x4, 0x8 and 0xC, respectively. See Section 12.1.1 "CLR, SET and INV Registers" for more information.

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |  |  |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|--|--|--|

| 31:24        | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |  |

| 31.24        | FLTEN11           | MSEL1             | 1<1:0>            | FSEL11<4:0>       |                   |                   |                  |                  |  |  |  |

| 23:16        | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |  |

| 23.10        | FLTEN10           | MSEL1             | 0<1:0>            |                   | F                 | SEL10<4:0>        |                  |                  |  |  |  |

| 15:8         | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |  |

| 10.0         | FLTEN9            | MSEL              | 9<1:0>            | FSEL9<4:0>        |                   |                   |                  |                  |  |  |  |

| 7.0          | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |  |

| 7:0          | FLTEN8            | MSEL              | 8<1:0>            |                   | F                 | SEL8<4:0>         |                  |                  |  |  |  |

#### REGISTER 24-12: CIFLTCON2: CAN FILTER CONTROL REGISTER 2

#### Legend:

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, re | ead as '0'         |

|-------------------|------------------|---------------------------|--------------------|

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared      | x = Bit is unknown |

| bit 31    | FLTEN11: Filter 11 Enable bit                                                                                                                                                  |

|-----------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|           | 1 = Filter is enabled<br>0 = Filter is disabled                                                                                                                                |

| bit 30-29 | MSEL11<1:0>: Filter 11 Mask Select bits                                                                                                                                        |

|           | <ul> <li>11 = Acceptance Mask 3 selected</li> <li>10 = Acceptance Mask 2 selected</li> <li>01 = Acceptance Mask 1 selected</li> <li>00 = Acceptance Mask 0 selected</li> </ul> |

| bit 28-24 | FSEL11<4:0>: FIFO Selection bits                                                                                                                                               |

|           | 11111 = Message matching filter is stored in FIFO buffer 31<br>11110 = Message matching filter is stored in FIFO buffer 30                                                     |

|           |                                                                                                                                                                                |

|           | 00001 = Message matching filter is stored in FIFO buffer 1<br>00000 = Message matching filter is stored in FIFO buffer 0                                                       |

| bit 23    | FLTEN10: Filter 10 Enable bit                                                                                                                                                  |

|           | <ul><li>1 = Filter is enabled</li><li>0 = Filter is disabled</li></ul>                                                                                                         |

| bit 22-21 | MSEL10<1:0>: Filter 10 Mask Select bits                                                                                                                                        |

|           | <ul> <li>11 = Acceptance Mask 3 selected</li> <li>10 = Acceptance Mask 2 selected</li> <li>01 = Acceptance Mask 1 selected</li> <li>00 = Acceptance Mask 0 selected</li> </ul> |

| bit 20-16 | FSEL10<4:0>: FIFO Selection bits                                                                                                                                               |

|           | 11111 = Message matching filter is stored in FIFO buffer 31                                                                                                                    |

|           | 11110 = Message matching filter is stored in FIFO buffer 30                                                                                                                    |

|           | •                                                                                                                                                                              |

|           | •                                                                                                                                                                              |

|           | 00001 = Message matching filter is stored in FIFO buffer 1<br>00000 = Message matching filter is stored in FIFO buffer 0                                                       |

|           |                                                                                                                                                                                |

Note: The bits in this register can only be modified if the corresponding filter enable (FLTENn) bit is '0'.

#### REGISTER 24-17: CIFLTCON7: CAN FILTER CONTROL REGISTER 7 (CONTINUED)

| bit 15    | FLTEN29: Filter 29 Enable bit<br>1 = Filter is enabled<br>0 = Filter is disabled                                                                                               |

|-----------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| bit 14-13 | MSEL29<1:0>: Filter 29 Mask Select bits                                                                                                                                        |

|           | <ul> <li>11 = Acceptance Mask 3 selected</li> <li>10 = Acceptance Mask 2 selected</li> <li>01 = Acceptance Mask 1 selected</li> <li>00 = Acceptance Mask 0 selected</li> </ul> |

| bit 12-8  | FSEL29<4:0>: FIFO Selection bits                                                                                                                                               |

|           | 11111 = Message matching filter is stored in FIFO buffer 31                                                                                                                    |