Welcome to E-XFL.COM

### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

### Details

E·XFI

| Details                    |                                                                                  |

|----------------------------|----------------------------------------------------------------------------------|

| Product Status             | Active                                                                           |

| Core Processor             | MIPS32® M4K™                                                                     |

| Core Size                  | 32-Bit Single-Core                                                               |

| Speed                      | 80MHz                                                                            |

| Connectivity               | CANbus, Ethernet, I <sup>2</sup> C, SPI, UART/USART, USB OTG                     |

| Peripherals                | Brown-out Detect/Reset, DMA, POR, PWM, WDT                                       |

| Number of I/O              | -                                                                                |

| Program Memory Size        | 256KB (256K x 8)                                                                 |

| Program Memory Type        | FLASH                                                                            |

| EEPROM Size                | -                                                                                |

| RAM Size                   | 64K x 8                                                                          |

| Voltage - Supply (Vcc/Vdd) | 2.3V ~ 3.6V                                                                      |

| Data Converters            | A/D 16x10b                                                                       |

| Oscillator Type            | Internal                                                                         |

| Operating Temperature      | -40°C ~ 105°C (TA)                                                               |

| Mounting Type              | Surface Mount                                                                    |

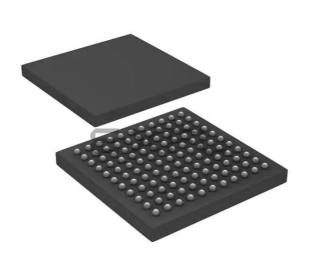

| Package / Case             | 121-TFBGA                                                                        |

| Supplier Device Package    | 121-TFBGA (10x10)                                                                |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic32mx775f256l-80v-bg |

|                            |                                                                                  |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

|                  |      |                         |                  |     | USE      | B and E                | therne                                   | t                     |                    |                                 |                              |             |         |      |       |                         |

|------------------|------|-------------------------|------------------|-----|----------|------------------------|------------------------------------------|-----------------------|--------------------|---------------------------------|------------------------------|-------------|---------|------|-------|-------------------------|

| Device           | Pins | Program Memory (KB)     | Data Memory (KB) | USB | Ethernet | Timers/Capture/Compare | DMA Channels<br>(Programmable/Dedicated) | UART <sup>(2,3)</sup> | SPI <sup>(3)</sup> | I <sup>2</sup> C <sup>(3)</sup> | 10-bit 1 Msps ADC (Channels) | Comparators | dSP/PMP | JTAG | Trace | Packages <sup>(4)</sup> |

| PIC32MX664F064H  | 64   | 64 + 12 <sup>(1)</sup>  | 32               | 1   | 1        | 5/5/5                  | 4/4                                      | 6                     | 3                  | 4                               | 16                           | 2           | Yes     | Yes  | No    | PT,<br>MR               |

| PIC32MX664F128H  | 64   | 128 + 12 <sup>(1)</sup> | 32               | 1   | 1        | 5/5/5                  | 4/4                                      | 6                     | 3                  | 4                               | 16                           | 2           | Yes     | Yes  | No    | PT,<br>MR               |

| PIC32MX675F256H  | 64   | 256 + 12 <sup>(1)</sup> | 64               | 1   | 1        | 5/5/5                  | 8/4                                      | 6                     | 3                  | 4                               | 16                           | 2           | Yes     | Yes  | No    | PT,<br>MR               |

| PIC32MX675F512H  | 64   | 512 + 12 <sup>(1)</sup> | 64               | 1   | 1        | 5/5/5                  | 8/4                                      | 6                     | 3                  | 4                               | 16                           | 2           | Yes     | Yes  | No    | PT,<br>MR               |

| PIC32MX695F512H  | 64   | 512 + 12 <sup>(1)</sup> | 128              | 1   | 1        | 5/5/5                  | 8/4                                      | 6                     | 3                  | 4                               | 16                           | 2           | Yes     | Yes  | No    | PT,<br>MR               |

| PIC32MX664F064L  | 100  | 64 + 12 <sup>(1)</sup>  | 32               | 1   | 1        | 5/5/5                  | 4/4                                      | 6                     | 4                  | 5                               | 16                           | 2           | Yes     | Yes  | Yes   | PT, PF,<br>BG           |

| PIC32MX664F128L  | 100  | 128 + 12 <sup>(1)</sup> | 32               | 1   | 1        | 5/5/5                  | 4/4                                      | 6                     | 4                  | 5                               | 16                           | 2           | Yes     | Yes  | Yes   | PT, PF,<br>BG           |

| PIC32MX675F256L  | 100  | 256 + 12 <sup>(1)</sup> | 64               | 1   | 1        | 5/5/5                  | 8/4                                      | 6                     | 4                  | 5                               | 16                           | 2           | Yes     | Yes  | Yes   | PT, PF,<br>BG           |

| PIC32MX675F512L  | 100  | 512 + 12 <sup>(1)</sup> | 64               | 1   | 1        | 5/5/5                  | 8/4                                      | 6                     | 4                  | 5                               | 16                           | 2           | Yes     | Yes  | Yes   | PT, PF,<br>BG, TL       |

| PIC32MX695F512L  | 100  | 512 + 12 <sup>(1)</sup> | 128              | 1   | 1        | 5/5/5                  | 8/4                                      | 6                     | 4                  | 5                               | 16                           | 2           | Yes     | Yes  | Yes   | PT, PF,<br>BG, TL       |

| Legend: PF, PT = | TQFP | MR = QF                 | N                |     | BG =     | TFBGA                  | 4                                        | TL =                  | VTL/               | ų( <del>5</del> )               |                              |             |         |      |       |                         |

| TABLE 2: PIC32MX6XX USB AND ETHERNET FEATURES |

|-----------------------------------------------|

|-----------------------------------------------|

Legend: PF, PT = TQFP MR = QFN BG = Note 1: This device features 12 KB boot Flash memory.

2: CTS and RTS pins may not be available for all UART modules. Refer to the "Device Pin Tables" section for more information.

3: Some pins between the UART, SPI and I<sup>2</sup>C modules may be shared. Refer to the "Device Pin Tables" section for more information.

4: Refer to 34.0 "Packaging Information" for more information.

5: 100-pin devices other than those listed here are available in the VTLA package upon request. Please contact your local Microchip Sales Office for details.

# TABLE 11: PIN NAMES FOR USB AND ETHERNET DEVICES (CONTINUED)

| 1     | 21-PIN TFBGA (BOTTOM VIEW                                                                   | /)         | L11                                         |    |

|-------|---------------------------------------------------------------------------------------------|------------|---------------------------------------------|----|

|       | PIC32MX664F064L<br>PIC32MX664F128L<br>PIC32MX675F256L<br>PIC32MX675F512L<br>PIC32MX695F512L |            |                                             | 11 |

| No    | te: The TFBGA package skips from row                                                        | / "H" to r | ow "J" and has no "I" row. A1               |    |

| Pin # | Full Pin Name                                                                               | Pin #      | Full Pin Name                               |    |

| J3    | PGED2/AN7/RB7                                                                               | K8         | VDD                                         |    |

| J4    | AVdd                                                                                        | K9         | AETXD1/SCK3/U4TX/U1RTS/CN21/RD15            |    |

| J5    | AN11/ERXERR/AETXERR/PMA12/RB11                                                              | K10        | USBID/RF3                                   |    |

| J6    | TCK/RA1                                                                                     | K11        | SDA3/SDI3/U1RX/RF2                          |    |

| J7    | AN12/ERXD0/AECRS/PMA11/RB12                                                                 | L1         | PGEC2/AN6/OCFA/RB6                          |    |

| J8    | No Connect (NC)                                                                             | L2         | VREF-/CVREF-/AERXD2/PMA7/RA9                |    |

| J9    | No Connect (NC)                                                                             | L3         | AVss                                        |    |

| J10   | SCL3/SDO3/U1TX/RF8                                                                          | L4         | AN9/C2OUT/RB9                               |    |

| J11   | D-/RG3                                                                                      | L5         | AN10/CVREFOUT/PMA13/RB10                    |    |

| K1    | PGEC1/AN1/CN3/RB1                                                                           | L6         | SCK4/U5TX/U2RTS/RF13                        |    |

| K2    | PGED1/AN0/CN2/RB0                                                                           | L7         | AN13/ERXD1/AECOL/PMA10/RB13                 |    |

| K3    | VREF+/CVREF+/AERXD3/PMA6/RA10                                                               | L8         | AN15/ERXD3/AETXD2/OCFB/PMALL/PMA0/CN12/RB15 |    |

| K4    | AN8/C1OUT/RB8                                                                               | L9         | AETXD0/SS3/U4RX/U1CTS/CN20/RD14             |    |

| K5    | No Connect (NC)                                                                             | L10        | SDA5/SDI4/U2RX/PMA9/CN17/RF4                |    |

| K6    | SS4/U5RX/U2CTS/RF12                                                                         | L11        | SCL5/SDO4/U2TX/PMA8/CN18/RF5                |    |

| K7    | AN14/ERXD2/AETXD3/PMALH/PMA1/RB14                                                           |            |                                             |    |

Note 1: Shaded pins are 5V tolerant.

### **Referenced Sources**

This device data sheet is based on the following individual chapters of the *"PIC32 Family Reference Manual"*. These documents should be considered as the general reference for the operation of a particular module or device feature.

- Note 1: To access the documents listed below, browse to the documentation section of the PIC32MX795F512L product page on the Microchip web site (www.microchip.com) or select a family reference manual section from the following list. In addition to parameters, features, and other documentation, the resulting page provides links to the related family

- Section 1. "Introduction" (DS60001127)

- Section 2. "CPU" (DS60001113)

- Section 4. "Prefetch Cache" (DS60001119)

- Section 3. "Memory Organization" (DS60001115)

reference manual sections.

- Section 5. "Flash Program Memory" (DS60001121)

- Section 6. "Oscillator Configuration" (DS60001112)

- Section 7. "Resets" (DS60001118)

- Section 8. "Interrupt Controller" (DS60001108)

- Section 9. "Watchdog Timer and Power-up Timer (DS60001114)

- Section 10. "Power-Saving Features" (DS60001130)

- Section 12. "I/O Ports" (DS60001120)

- Section 13. "Parallel Master Port (PMP)" (DS60001128)

- Section 14. "Timers" (DS60001105)

- Section 15. "Input Capture" (DS60001122)

- Section 16. "Output Capture" (DS60001111)

- Section 17. "10-bit Analog-to-Digital Converter (ADC)" (DS60001104)

- Section 19. "Comparator" (DS60001110)

- Section 20. "Comparator Voltage Reference (CVREF)" (DS60001109)

- Section 21. "Universal Asynchronous Receiver Transmitter (UART)" (DS60001107)

- Section 23. "Serial Peripheral Interface (SPI)" (DS60001106)

- Section 24. "Inter-Integrated Circuit (I2C)" (DS60001116)

- Section 27. "USB On-The-Go (OTG)" (DS60001126)

- Section 29. "Real-Time Clock and Calendar (RTCC)" (DS60001125)

- Section 31. "Direct Memory Access (DMA) Controller" (DS60001117)

- Section 32. "Configuration" (DS60001124)

- Section 33. "Programming and Diagnostics" (DS60001129)

- Section 34. "Controller Area Network (CAN)" (DS60001154)

- Section 35. "Ethernet Controller" (DS60001155)

|          |                    | Pin Nur         | nber <sup>(1)</sup> |                 | <b>D</b> '  | D ((           |                                                                                                                                                                                                |

|----------|--------------------|-----------------|---------------------|-----------------|-------------|----------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Pin Name | 64-Pin<br>QFN/TQFP | 100-Pin<br>TQFP | 121-Pin<br>TFBGA    | 124-pin<br>VTLA | Pin<br>Type | Buffer<br>Type | Description                                                                                                                                                                                    |

| AN0      | 16                 | 25              | K2                  | B14             | I           | Analog         | Analog input channels                                                                                                                                                                          |

| AN1      | 15                 | 24              | K1                  | A15             | I           | Analog         |                                                                                                                                                                                                |

| AN2      | 14                 | 23              | J2                  | B13             | I           | Analog         |                                                                                                                                                                                                |

| AN3      | 13                 | 22              | J1                  | A13             | I           | Analog         |                                                                                                                                                                                                |

| AN4      | 12                 | 21              | H2                  | B11             | I           | Analog         |                                                                                                                                                                                                |

| AN5      | 11                 | 20              | H1                  | A12             | I           | Analog         |                                                                                                                                                                                                |

| AN6      | 17                 | 26              | L1                  | A20             | I           | Analog         |                                                                                                                                                                                                |

| AN7      | 18                 | 27              | J3                  | B16             | I           | Analog         |                                                                                                                                                                                                |

| AN8      | 21                 | 32              | K4                  | A23             | I           | Analog         |                                                                                                                                                                                                |

| AN9      | 22                 | 33              | L4                  | B19             | I           | Analog         |                                                                                                                                                                                                |

| AN10     | 23                 | 34              | L5                  | A24             | I           | Analog         |                                                                                                                                                                                                |

| AN11     | 24                 | 35              | J5                  | B20             | I           | Analog         |                                                                                                                                                                                                |

| AN12     | 27                 | 41              | J7                  | B23             | I           | Analog         |                                                                                                                                                                                                |

| AN13     | 28                 | 42              | L7                  | A28             | I           | Analog         |                                                                                                                                                                                                |

| AN14     | 29                 | 43              | K7                  | B24             | I           | Analog         |                                                                                                                                                                                                |

| AN15     | 30                 | 44              | L8                  | A29             | I           | Analog         |                                                                                                                                                                                                |

| CLKI     | 39                 | 63              | F9                  | B34             | I           | ST/<br>CMOS    | External clock source input. Always associated with OSC1 pin function.                                                                                                                         |

| CLKO     | 40                 | 64              | F11                 | A42             | 0           | _              | Oscillator crystal output. Connects to<br>crystal or resonator in Crystal Oscillator<br>mode. Optionally functions as CLKO in<br>RC and EC modes. Always associated<br>with OSC2 pin function. |

| OSC1     | 39                 | 63              | F9                  | B34             | I           | ST/<br>CMOS    | Oscillator crystal input. ST buffer when configured in RC mode; CMOS otherwise.                                                                                                                |

| OSC2     | 40                 | 64              | F11                 | A42             | I/O         |                | Oscillator crystal output. Connects to<br>crystal or resonator in Crystal Oscillator<br>mode. Optionally functions as CLKO in<br>RC and EC modes.                                              |

| SOSCI    | 47                 | 73              | C10                 | A47             | I           | ST/<br>CMOS    | 32.768 kHz low-power oscillator crystal<br>input; CMOS otherwise                                                                                                                               |

| SOSCO    | 48                 | 74              | B11                 | B40             | 0           | _              | 32.768 kHz low-power oscillator crystal<br>output                                                                                                                                              |

# TABLE 1-1: PINOUT I/O DESCRIPTIONS

ST = Schmitt Trigger input with CMOS levels O = Output I = Input I = Input I = Input I = TTL = TTL input buffer

Note 1: Pin numbers are only provided for reference. See the "Device Pin Tables" section for device pin availability.

2: See 25.0 "Ethernet Controller" for more information.

#### 11.1 **Control Registers**

### TABLE 11-1: USB REGISTER MAP

| Signature         Signature           5040         U10TGIR <sup>(2)</sup> 5050         U10TGIR <sup>(2)</sup> 5060         U10TGSTAT           5070         U10TGCO           5080         U11PWRC           5200         U11R <sup>(2)</sup> 5210         U11EIR <sup>(2)</sup> 5220         U1EIR <sup>(2)</sup> 5220         U1EIR <sup>(2)</sup> | 2) 31:<br>15:<br>15:<br>15:<br>15:<br>15:<br>15:<br>15:<br>1                                | i:16       5:0       1:16       5:0       1:16       5:0       1:16       5:0       1:16 | 31/15<br>        | 30/14<br> | 29/13<br> | 28/12 | 27/11 | 26/10 | 25/9 | 24/8 | Bits<br>23/7           | 22/6               | 04/5                 |            |           |          |                 | r        | Resets |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------|------------------|-----------|-----------|-------|-------|-------|------|------|------------------------|--------------------|----------------------|------------|-----------|----------|-----------------|----------|--------|

| 5040         U10TGIR <sup>(2)</sup> 5050         U10TGIE           5060         U10TGSTAT           5070         U10TGCO           5080         U1PWRC           5200         U1IR <sup>(2)</sup> 5210         U1IE           5220         U1EIR <sup>(2)</sup>                                                                                      | 2) 31:<br>15:<br>15:<br>15:<br>15:<br>15:<br>15:<br>15:<br>1                                | 1:16<br>5:0<br>1:16<br>5:0<br>1:16<br>5:0<br>1:16                                        |                  | _<br>_    |           | -     |       |       | 25/9 | 24/8 | 23/7                   | 22/6               | 04/5                 |            |           | ļ        |                 |          | eset   |

| 5050         U10TGIE           5060         U10TGSTAT           5070         U10TGCO           5080         U1PWRC           5200         U1IR <sup>(2)</sup> 5210         U1IE           5220         U1EIR <sup>(2)</sup>                                                                                                                          | 2) 15<br>31:<br>15<br>(3) 31:<br>(3) 31:<br>15<br>15<br>31:<br>31:<br>31                    | 5:0<br>1:16<br>5:0<br>1:16<br>5:0<br>1:16                                                | —<br>—<br>—<br>— | -         | _         |       | _     |       |      |      |                        | 22/0               | 21/5                 | 20/4       | 19/3      | 18/2     | 17/1            | 16/0     | All Re |

| 5050         U10TGIE           5060         U10TGSTAT           5070         U10TGCO           5080         U1PWRC           5200         U1IR <sup>(2)</sup> 5210         U1IE           5220         U1EIR <sup>(2)</sup>                                                                                                                          | 15<br>31:<br>15<br>(3)<br>31:<br>15<br>31:<br>Ν<br>31:<br>31:                               | 1:16<br>5:0<br>1:16<br>5:0<br>1:16                                                       | -<br>-<br>-      |           |           |       |       | —     | -    | _    | _                      | —                  | _                    | —          | _         | —        | —               | —        | 0000   |

| 5060         U1OTGSTAT           5070         U1OTGCO           5080         U1PWRC           5200         U1IR <sup>(2)</sup> 5210         U1IE           5220         U1EIR <sup>(2)</sup>                                                                                                                                                         | 15<br>(3) 31:<br>15:<br>Ν 31:<br>15:<br>31:<br>31:<br>31:<br>31:<br>31:<br>31:<br>31:<br>31 | 5:0<br>1:16<br>5:0<br>1:16                                                               | -                | —         |           |       | -     |       |      | —    | IDIF                   | T1MSECIF           | LSTATEIF             | ACTVIF     | SESVDIF   | SESENDIF | _               | VBUSVDIF | 0000   |

| 5060         U1OTGSTAT           5070         U1OTGCO           5080         U1PWRC           5200         U1IR <sup>(2)</sup> 5210         U1IE           5220         U1EIR <sup>(2)</sup>                                                                                                                                                         | 15:<br>T <sup>(3)</sup> 31:<br>15:<br>N 31:<br>15:<br>31:<br>31:                            | 1:16<br>5:0<br>1:16                                                                      | -                | -         | —         |       | -     |       |      | —    | _                      | —                  | _                    | -          | _         | —        | _               | _        | 0000   |

| 5070         U1OTGCO           5080         U1PWRC           5200         U1IR <sup>(2)</sup> 5210         U1IE           5220         U1EIR <sup>(2)</sup>                                                                                                                                                                                          | N 15:<br>31:<br>31:<br>31:                                                                  | 5:0<br>1:16                                                                              |                  |           |           | _     | _     |       | _    | _    | IDIE                   | T1MSECIE           | LSTATEIE             | ACTVIE     | SESVDIE   | SESENDIE | _               | VBUSVDIE | 0000   |

| 5070         U1OTGCO           5080         U1PWRC           5200         U1IR <sup>(2)</sup> 5210         U1IE           5220         U1EIR <sup>(2)</sup>                                                                                                                                                                                          | N 31:<br>31:<br>31:<br>31:                                                                  | 1:16                                                                                     |                  | -         | _         |       | -     |       |      | —    | _                      | —                  | _                    | -          | —         | —        |                 | —        | 0000   |

| 5080         U1PWRC           5200         U1IR <sup>(2)</sup> 5210         U1IE           5220         U1EIR <sup>(2)</sup>                                                                                                                                                                                                                         | N 15                                                                                        |                                                                                          | _                | -         | _         |       | -     |       |      | —    | ID                     | —                  | LSTATE               | -          | SESVD     | SESEND   |                 | VBUSVD   | 0000   |

| 5080         U1PWRC           5200         U1IR <sup>(2)</sup> 5210         U1IE           5220         U1EIR <sup>(2)</sup>                                                                                                                                                                                                                         | 31                                                                                          | E:0                                                                                      | _                | _         | _         | _     | —     | _     | _    | _    |                        | _                  | —                    | —          | —         | —        | —               | —        | 0000   |

| 5200 U1IR <sup>(2)</sup><br>5210 U1IE<br>5220 U1EIR <sup>(2)</sup>                                                                                                                                                                                                                                                                                   | 31:                                                                                         | 5.0                                                                                      | _                | _         | _         | _     | —     | _     |      |      | DPPULUP                | DMPULUP            | DPPULDWN             | DMPULDWN   | VBUSON    | OTGEN    | VBUSCHG         | VBUSDIS  | 0000   |

| 5200         U1IR <sup>(2)</sup> 5210         U1IE           5220         U1EIR <sup>(2)</sup>                                                                                                                                                                                                                                                       |                                                                                             | 1:16                                                                                     | _                | -         | _         |       | -     |       |      | —    | _                      | —                  | _                    | -          | —         | _        |                 | —        | 0000   |

| 5210 U1IE<br>5220 U1EIR <sup>(2)</sup>                                                                                                                                                                                                                                                                                                               | 15                                                                                          | 5:0                                                                                      | _                | _         | _         | _     | —     | _     | _    | -    | UACTPND <sup>(4)</sup> | _                  | —                    | USLPGRD    | USBBUSY   | —        | USUSPEND        | USBPWR   | 0000   |

| 5210 U1IE<br>5220 U1EIR <sup>(2)</sup>                                                                                                                                                                                                                                                                                                               | 31:                                                                                         | 1:16                                                                                     | _                | _         | _         | _     | —     | _     |      |      |                        | _                  | —                    | —          | —         | —        | —               | —        | 0000   |

| 5220 U1EIR <sup>(2)</sup>                                                                                                                                                                                                                                                                                                                            | 15                                                                                          | 5:0                                                                                      | _                | _         | _         |       | _     |       |      | _    | STALLIF                | ATTACHIF           | RESUMEIF             | IDLEIF     | TRNIF     | SOFIF    | UERRIF          | URSTIF   | 0000   |

| 5220 U1EIR <sup>(2)</sup>                                                                                                                                                                                                                                                                                                                            | _                                                                                           |                                                                                          |                  |           |           |       |       |       |      |      | -                      |                    |                      |            |           |          |                 | DETACHIF | 0000   |

| 5220 U1EIR <sup>(2)</sup>                                                                                                                                                                                                                                                                                                                            | 31:                                                                                         | 1:16                                                                                     | _                | _         | —         | —     | —     | —     | —    | _    | —                      | —                  | —                    | —          | —         | —        | —               |          | 0000   |

|                                                                                                                                                                                                                                                                                                                                                      | 15                                                                                          | 5:0                                                                                      | _                | _         | _         | _     | _     | _     | _    | _    | STALLIE                | ATTACHIE           | RESUMEIE             | IDLEIE     | TRNIE     | SOFIE    | UERRIE          | URSTIE   | 0000   |

|                                                                                                                                                                                                                                                                                                                                                      |                                                                                             |                                                                                          |                  |           |           |       |       |       |      |      |                        |                    |                      |            |           |          |                 |          | 0000   |

|                                                                                                                                                                                                                                                                                                                                                      | 31:                                                                                         | 1:16                                                                                     | _                | _         | _         | _     | _     | _     | _    | _    | —                      |                    | —                    | —          | _         |          | _               | —        | 0000   |

| 5230 U1EIE                                                                                                                                                                                                                                                                                                                                           | 15                                                                                          | 5:0                                                                                      | _                | _         | _         | _     | _     | _     | _    | —    | BTSEF                  | BMXEF              | DMAEF                | BTOEF      | DFN8EF    | CRC16EF  | CRC5EF<br>EOFEF | PIDEF    | 0000   |

| 5230 U1EIE                                                                                                                                                                                                                                                                                                                                           | 31.                                                                                         | 1:16                                                                                     | _                | _         | _         | _     | _     | _     | _    |      | _                      | _                  | _                    | _          | _         | _        | _               | _        | 0000   |

| SZSO OTELE                                                                                                                                                                                                                                                                                                                                           | 51.                                                                                         | 1.10                                                                                     |                  |           |           |       |       |       |      |      |                        |                    |                      |            |           |          | CRC5EE          |          | 0000   |

|                                                                                                                                                                                                                                                                                                                                                      | 15                                                                                          | 5:0                                                                                      | —                | —         | —         | —     | —     | —     | —    | —    | BTSEE                  | BMXEE              | DMAEE                | BTOEE      | DFN8EE    | CRC16EE  | EOFEE           | PIDEE    | 0000   |

| (2)                                                                                                                                                                                                                                                                                                                                                  | 、 31:                                                                                       | 1:16                                                                                     | _                | _         | _         | _     | _     |       | _    | _    | _                      | _                  | _                    | _          | _         |          | _               | _        | 0000   |

| 5240 U1STAT <sup>(3)</sup>                                                                                                                                                                                                                                                                                                                           | ,                                                                                           | 5:0                                                                                      | _                | _         | _         | _     | _     | _     | _    | _    |                        | ENDPT              | <3:0> <sup>(4)</sup> |            | DIR       | PPBI     | _               | _        | 0000   |

|                                                                                                                                                                                                                                                                                                                                                      | -                                                                                           | 1:16                                                                                     | _                | _         | _         | _     | _     | _     | _    | _    | _                      | _                  | _                    | _          | _         | _        | _               | _        | 0000   |

| 5250 U1CON                                                                                                                                                                                                                                                                                                                                           |                                                                                             |                                                                                          |                  |           |           |       |       |       |      |      | 10TATE(4)              | 0.5 0(4)           | PKTDIS               |            |           |          |                 | USBEN    | 0000   |

|                                                                                                                                                                                                                                                                                                                                                      |                                                                                             | 5:0                                                                                      | —                | _         | _         | —     | —     | —     | —    |      | JSTATE <sup>(4)</sup>  | SE0 <sup>(4)</sup> | TOKBUSY              | USBRST     | HOSTEN    | RESUME   | PPBRST          | SOFEN    | 0000   |

| 5260 U1ADDR                                                                                                                                                                                                                                                                                                                                          | 15                                                                                          | 1:16                                                                                     | _                | _         | _         | _     | _     | _     | _    | _    |                        | —                  | _                    | _          | —         | —        | _               | —        | 0000   |

| 5200 UTADDR                                                                                                                                                                                                                                                                                                                                          | 31:                                                                                         | 5:0                                                                                      | _                | _         | —         | _     | —     | _     | _    | _    | LSPDEN                 |                    |                      | DE         | VADDR<6:0 | 1>       |                 |          | 0000   |

| 5270 U1BDTP1                                                                                                                                                                                                                                                                                                                                         | 31:                                                                                         |                                                                                          | _                | _         | —         | _     | —     | _     | _    | _    | _                      | _                  | —                    | _          | _         | —        | _               | —        | 0000   |

| JZIU UIBDIPI                                                                                                                                                                                                                                                                                                                                         | 31:<br>15:                                                                                  | 1:16                                                                                     |                  | _         | _         | _     | _     | _     |      | _    |                        |                    | BD                   | TPTRL<7:1> |           |          |                 |          | 0000   |

x = unknown value on Reset; — = unimplemented, read as '0'. Reset values are shown in hexadecimal. Legend:

All registers in this table (except as noted) have corresponding CLR, SET and INV registers at its virtual address, plus an offset of 0x4, 0x8 and 0xC respectively. See Section 12.1.1 "CLR, SET and INV Registers" for Note 1: more information.

2:

This register does not have associated SET and INV registers. This register does not have associated CLR, SET and INV registers. 3:

4: Reset value for this bit is undefined.

# 19.0 INTER-INTEGRATED CIRCUIT (I<sup>2</sup>C)

Note: This data sheet summarizes the features of the PIC32MX5XX/6XX/7XX family of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to Section 24. "Inter-Integrated Circuit (I<sup>2</sup>C)" (DS60001116) in the "*PIC32 Family Reference Manual*", which is available from the Microchip web site (www.microchip.com/PIC32). The  $l^2C$  module provides complete hardware support for both Slave and Multi-Master modes of the  $l^2C$  serial communication standard. Figure 19-1 illustrates the  $l^2C$  module block diagram.

Each  $I^2C$  module has a 2-pin interface: the SCLx pin is clock and the SDAx pin is data.

Each I<sup>2</sup>C module offers the following key features:

- I<sup>2</sup>C interface supporting both master and slave operation

- I<sup>2</sup>C Slave mode supports 7-bit and 10-bit addressing

- I<sup>2</sup>C Master mode supports 7-bit and 10-bit addressing

- I<sup>2</sup>C port allows bidirectional transfers between master and slaves

- Serial clock synchronization for the I<sup>2</sup>C port can be used as a handshake mechanism to suspend and resume serial transfer (SCLREL control)

- I<sup>2</sup>C supports multi-master operation; detects bus collision and arbitrates accordingly

- Provides support for address bit masking

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6   | Bit<br>29/21/13/5  | Bit<br>28/20/12/4 | Bit<br>27/19/11/3   | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

|--------------|-------------------|---------------------|--------------------|-------------------|---------------------|-------------------|------------------|------------------|

| 24.24        | U-0               | U-0                 | U-0                | U-0               | U-0                 | U-0               | U-0              | U-0              |

| 31:24        |                   | _                   | _                  |                   | _                   |                   |                  | —                |

| 00.40        | U-0               | U-0                 | U-0                | U-0               | U-0                 | U-0               | U-0              | U-0              |

| 23:16        | —                 | _                   | _                  | -                 | -                   | _                 | _                | —                |

| 45.0         | R/W-0             | U-0                 | R/W-0              | R/W-0             | R/W-0               | R/W-0             | R/W-0            | R/W-0            |

| 15:8         | 0N <sup>(1)</sup> | _                   | SIDL               | ADRML             | JX<1:0>             | PMPTTL            | PTWREN           | PTRDEN           |

| 7.0          | R/W-0             | R/W-0               | R/W-0              | U-0               | R/W-0               | U-0               | R/W-0            | R/W-0            |

| 7:0          | CSF<              | 1:0> <sup>(2)</sup> | ALP <sup>(2)</sup> | _                 | CS1P <sup>(2)</sup> |                   | WRSP             | RDSP             |

### REGISTER 21-1: PMCON: PARALLEL PORT CONTROL REGISTER

#### Legend:

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, | read as '0'        |

|-------------------|------------------|------------------------|--------------------|

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared   | x = Bit is unknown |

### bit 31-16 Unimplemented: Read as '0'

- bit 15 **ON:** Parallel Master Port Enable bit<sup>(1)</sup>

- 1 = PMP is enabled

- 0 = PMP is disabled, no off-chip access performed

- bit 14 Unimplemented: Read as '0'

- bit 13 **SIDL:** Stop in Idle Mode bit

- 1 = Discontinue module operation when device enters Idle mode

- 0 = Continue module operation when device enters Idle mode

### bit 12-11 ADRMUX<1:0>: Address/Data Multiplexing Selection bits

- 11 = All 16 bits of address are multiplexed on PMD<15:0> pins

- 10 = All 16 bits of address are multiplexed on PMD<7:0> pins

- 01 = Lower 8 bits of address are multiplexed on PMD<7:0> pins, upper bits are on PMA<15:8>

- 00 = Address and data appear on separate pins

- bit 10 **PMPTTL:** PMP Module TTL Input Buffer Select bit

- 1 = PMP module uses TTL input buffers

- 0 = PMP module uses Schmitt Trigger input buffer

- bit 9 **PTWREN:** Write Enable Strobe Port Enable bit

- 1 = PMWR/PMENB port is enabled

- 0 = PMWR/PMENB port is disabled

- bit 8 **PTRDEN:** Read/Write Strobe Port Enable bit

- 1 = PMRD/PMWR port is enabled

- 0 = PMRD/PMWR port is disabled

- bit 7-6 CSF<1:0>: Chip Select Function bits<sup>(2)</sup>

- 11 = Reserved

- 10 = PMCS2 and PMCS1 function as Chip Select

- 01 = PMCS2 functions as Chip Select, PMCS1 functions as address bit 14

- 00 = PMCS2 and PMCS1 function as address bits 15 and  $14^{(2)}$

- bit 5 ALP: Address Latch Polarity bit<sup>(2)</sup>

- 1 = Active-high (PMALL and PMALH)

- $0 = \text{Active-low} (\overline{\text{PMALL}} \text{ and } \overline{\text{PMALH}})$

- bit 4 Unimplemented: Read as '0'

- **Note 1:** When using the 1:1 PBCLK divisor, the user's software should not read/write the peripheral's SFRs in the SYSCLK cycle immediately following the instruction that clears the module's ON control bit.

- 2: These bits have no effect when their corresponding pins are used as address lines.

# 22.1 Control Registers

### TABLE 22-1: RTCC REGISTER MAP

| ess                         |                                 |           |              |         |            |               |              |             |             | В     | its          |          |        |      |              |                   |         |       |            |

|-----------------------------|---------------------------------|-----------|--------------|---------|------------|---------------|--------------|-------------|-------------|-------|--------------|----------|--------|------|--------------|-------------------|---------|-------|------------|

| Virtual Address<br>(BF80_#) | Register<br>Name <sup>(1)</sup> | Bit Range | 31/15        | 30/14   | 29/13      | 28/12         | 27/11        | 26/10       | 25/9        | 24/8  | 23/7         | 22/6     | 21/5   | 20/4 | 19/3         | 18/2              | 17/1    | 16/0  | All Resets |

| 0200                        | RTCCON                          | 31:16     |              |         |            | —             |              |             |             |       |              | CAL<9:0> |        |      |              |                   |         |       | 0000       |

| 0200                        | RICCON                          | 15:0      | ON           | -       | SIDL       | —             | —            | F           |             |       |              | RTCCLKON | —      |      | RTCWREN      | RTCSYNC           | HALFSEC | RTCOE | 0000       |

| 0210                        | RTCALRM                         | 31:16     | _            | -       | _          | —             | —            | —           |             | _     | —            | _        | —      |      | _            | _                 | _       | —     | 0000       |

| 0210                        | RICALKI                         | 15:0      | ALRMEN       | CHIME   | PIV        | ALRMSYNC      |              | AMASK<3:0>  |             |       |              |          |        | ARPT | <7:0>        |                   |         |       | 0000       |

| 0220                        | RTCTIME                         | 31:16     |              | HR10    | 0<3:0>     |               |              | HR01<3:0>   |             |       |              | MIN10<   | 3:0>   |      |              | MIN0 <sup>2</sup> | <3:0>   |       | xxxx       |

| 0220                        | RICTIVIE                        | 15:0      |              | SEC1    | 0<3:0>     |               |              | SEC01<3:0>  |             |       |              | _        | —      | -    | _            | —                 | —       | —     | xx00       |

| 0000                        | DTODATE                         | 31:16     |              | YEAR'   | 10<3:0>    |               |              | YEAR0       | 1<3:0>      |       | MONTH10<3:0> |          |        |      |              | MONTH             | 01<3:0> |       | xxxx       |

| 0230                        | RTCDATE                         | 15:0      |              | DAY1    | 0<3:0>     |               |              | DAY01<3:0>  |             |       |              | _        | _      | _    |              | WDAY(             | )1<3:0> |       | xx00       |

| 0040                        |                                 | 31:16     |              | HR10    | )<3:0>     |               |              | HR01<3:0>   |             |       |              | MIN10<   | 3:0>   |      |              | MIN0 <sup>2</sup> | <3:0>   |       | xxxx       |

| 0240                        | ALRMTIME                        | 15:0      |              | SEC1    | 0<3:0>     |               |              | SEC01<3:0>  |             |       | _            | —        | _      | _    | _            | _                 | _       | _     | xx00       |

| 0050                        |                                 | 31:16     | _            | _       | _          | —             | _            |             |             |       |              | MONTH1   | )<3:0> |      | MONTH01<3:0> |                   |         |       | 00xx       |

| 0250                        | ALRMDATE                        | 15:0      |              | DAY1    | 0<3:0>     |               |              | DAY01       | <3:0>       |       |              |          |        |      | WDAY01<3:0>  |                   |         |       | xx0x       |

|                             | ، بام                           | unknow    | n voluo on D | aaati u | nimploment | 0' ac hear ha | , Depet volu | an ara ahau | un in hoved | aimal |              |          |        |      |              |                   |         |       |            |

PIC32MX5XX/6XX/7XX

Legend: x = unknown value on Reset; — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

Note 1: All registers in this table have corresponding CLR, SET and INV registers at its virtual address, plus an offset of 0x4, 0x8 and 0xC, respectively. See Section 12.1.1 "CLR, SET and INV Registers" for more information.

# REGISTER 22-1: RTCCON: RTC CONTROL REGISTER (CONTINUED)

- bit 3 RTCWREN: RTC Value Registers Write Enable bit<sup>(4)</sup>

- 1 = RTC Value registers can be written to by the user

- 0 = RTC Value registers are locked out from being written to by the user

- bit 2 RTCSYNC: RTCC Value Registers Read Synchronization bit

- 1 = RTC Value registers can change while reading, due to a rollover ripple that results in an invalid data read. If the register is read twice and results in the same data, the data can be assumed to be valid.

- 0 = RTC Value registers can be read without concern about a rollover ripple

- bit 1 HALFSEC: Half-Second Status bit<sup>(5)</sup>

- 1 = Second half period of a second

- 0 = First half period of a second

- bit 0 RTCOE: RTCC Output Enable bit

- 1 = RTCC clock output is enabled (clock presented onto an I/O)

- 0 = RTCC clock output is disabled

- **Note 1:** The ON bit is only writable when RTCWREN = 1.

- 2: When using the 1:1 PBCLK divisor, the user's software should not read/write the peripheral's SFRs in the SYSCLK cycle immediately following the instruction that clears the module's ON bit.

- **3:** Requires RTCOE = 1 (RTCCON<0>) for the output to be active.

- 4: The RTCWREN bit can only be set when the write sequence is enabled.

- 5: This bit is read-only. It is cleared to '0' on a write to the seconds bit fields (RTCTIME<14:8>).

Note: This register is only reset on a Power-on Reset (POR).

# TABLE 23-1: ADC REGISTER MAP (CONTINUED)

| ess                         |                  |               |       |                                    |       |       |       |       |      | Bi   | ts   |      |      |      |      |      |      |      |            |

|-----------------------------|------------------|---------------|-------|------------------------------------|-------|-------|-------|-------|------|------|------|------|------|------|------|------|------|------|------------|

| Virtual Address<br>(BF80_#) | Register<br>Name | Bit Range     | 31/15 | 30/14                              | 29/13 | 28/12 | 27/11 | 26/10 | 25/9 | 24/8 | 23/7 | 22/6 | 21/5 | 20/4 | 19/3 | 18/2 | 17/1 | 16/0 | All Resets |

| 9120                        | ADC1BUFB         | 31:16<br>15:0 |       | ADC Result Word B (ADC1BUFB<31:0>) |       |       |       |       |      |      |      |      |      |      |      |      |      |      |            |

| 9130                        | ADC1BUFC         | 31:16<br>15:0 |       | ADC Result Word C (ADC1BUFC<31:0>) |       |       |       |       |      |      |      |      |      |      |      |      |      |      |            |

| 9140                        | ADC1BUFD         | 31:16<br>15:0 |       | ADC Result Word D (ADC1BUED<31:0>) |       |       |       |       |      |      |      |      |      |      |      |      |      |      |            |

| 9150                        | ADC1BUFE         | 31:16<br>15:0 |       | ADC Result Word E (ADC1BUFE<31:0>) |       |       |       |       |      |      |      |      |      |      |      |      |      |      |            |

| 9160                        | ADC1BUFF         | 31:16<br>15:0 |       | ADC Result Word F (ADC1BUFF<31:0>) |       |       |       |       |      |      |      |      |      |      |      |      |      |      |            |

= unimplemented, read as '0'. Reset values are shown in hexadecimal. Legend: x = unknown value on Reset

This register has corresponding CLR, SET and INV registers at their virtual addresses, plus offsets of 0x4, 0x8 and 0xC, respectively. See Section 12.1.1 "CLR, SET and INV Registers" for more information. Note 1:

# PIC32MX5XX/6XX/7XX

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|

| 31:24        | R-0               | R-0               | R-0               | R-0               | R-0               | R-0               | R-0              | R-0              |

| 31.24        | RXOVF31           | RXOVF30           | RXOVF29           | RXOVF28           | RXOVF27           | RXOVF26           | RXOVF25          | RXOVF24          |

| 22:16        | R-0               | R-0               | R-0               | R-0               | R-0               | R-0               | R-0              | R-0              |

| 23:16        | RXOVF23           | RXOVF22           | RXOVF21           | RXOVF20           | RXOVF19           | RXOVF18           | RXOVF17          | RXOVF16          |

| 15:8         | R-0               | R-0               | R-0               | R-0               | R-0               | R-0               | R-0              | R-0              |

| 10.0         | RXOVF15           | RXOVF14           | RXOVF13           | RXOVF12           | RXOVF11           | RXOVF10           | RXOVF9           | RXOVF8           |

| 7:0          | R-0               | R-0               | R-0               | R-0               | R-0               | R-0               | R-0              | R-0              |

| 7.0          | RXOVF7            | RXOVF6            | RXOVF5            | RXOVF4            | RXOVF3            | RXOVF2            | RXOVF1           | RXOVF0           |

# REGISTER 24-7: CIRXOVF: CAN RECEIVE FIFO OVERFLOW STATUS REGISTER

### Legend:

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, r | ead as '0'         |

|-------------------|------------------|--------------------------|--------------------|

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared     | x = Bit is unknown |

bit 31-0 RXOVF<31:0>: FIFOn Receive Overflow Interrupt Pending bit

1 = FIFO has overflowed

0 = FIFO has not overflowed

# REGISTER 24-8: CITMR: CAN TIMER REGISTER

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|

| 31:24        | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |

| 31.24        |                   |                   |                   | CANTS<            | :15:8>            |                   |                  |                  |

| 23:16        | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |

| 23.10        |                   |                   |                   | CANTS             | <7:0>             |                   |                  |                  |

| 15:8         | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |

| 10.6         | CANTSPRE<15:8>    |                   |                   |                   |                   |                   |                  |                  |

| 7.0          | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |

| 7:0          |                   |                   |                   | CANTSPF           | RE<7:0>           |                   |                  |                  |

| Legend:           |                  |                                    |                    |  |  |

|-------------------|------------------|------------------------------------|--------------------|--|--|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read as '0' |                    |  |  |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared               | x = Bit is unknown |  |  |

bit 31-0 CANTS<15:0>: CAN Time Stamp Timer bits

This is a free-running timer that increments every CANTSPRE system clocks when the CANCAP bit (CiCON<20>) is set.

# bit 15-0 CANTSPRE<15:0>: CAN Time Stamp Timer Prescaler bits

1111 1111 1111 = CAN time stamp timer (CANTS) increments every 65,535 system clocks

.

0000 0000 0000 = CAN time stamp timer (CANTS) increments every system clock

**Note 1:** CiTMR will be paused when CANCAP = 0.

2: The CiTMR prescaler count will be reset on any write to CiTMR (CANTSPRE will be unaffected).

# PIC32MX5XX/6XX/7XX

### REGISTER 25-9: ETHPMCS: ETHERNET CONTROLLER PATTERN MATCH CHECKSUM REGISTER

| Bit Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

|-----------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|

| 31:24     | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 31.24     | —                 | —                 | —                 | —                 | _                 | —                 | —                | —                |

| 23:16     | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 23.10     | —                 | —                 | —                 | —                 | —                 | —                 | —                | —                |

| 15:8      | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |

| 15.6      |                   |                   |                   | PMCS              | <15:8>            |                   |                  |                  |

| 7:0       | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |

| 7.0       |                   |                   |                   | PMCS              | S<7:0>            |                   |                  |                  |

| Legend:           |                  |                        |                    |

|-------------------|------------------|------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, | read as '0'        |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared   | x = Bit is unknown |

bit 31-16 Unimplemented: Read as '0'

bit 15-8 PMCS<15:8>: Pattern Match Checksum 1 bits

bit 7-0 PMCS<7:0>: Pattern Match Checksum 0 bits

**Note 1:** This register is only used for RX operations.

2: The bits in this register may only be changed while the RXEN bit (ETHCON1<8>) = 0 or the PMMODE bit (ETHRXFC<11:8>) = 0.

### REGISTER 25-10: ETHPMO: ETHERNET CONTROLLER PATTERN MATCH OFFSET REGISTER

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|

| 31:24        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 51.24        | —                 | _                 | _                 | _                 | _                 | _                 | _                | _                |

| 23:16        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 23.10        | —                 | —                 | —                 | —                 | —                 | —                 | —                | —                |

| 15:8         | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |

| 15.0         |                   |                   |                   | PMO<              | :15:8>            |                   |                  |                  |

| 7:0          | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |

| 7.0          |                   |                   |                   | PMO               | <7:0>             |                   |                  |                  |

| Legend:           |                  |                          |                    |

|-------------------|------------------|--------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, r | read as '0'        |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared     | x = Bit is unknown |

bit 31-16 Unimplemented: Read as '0'

bit 15-0 **PMO<15:0>:** Pattern Match Offset 1 bits

Note 1: This register is only used for RX operations.

2: The bits in this register may only be changed while the RXEN bit (ETHCON1<8>) = 0 or the PMMODE bit (ETHRXFC<11:8>) = 0.

#### **REGISTER 25-11: ETHRXFC: ETHERNET CONTROLLER RECEIVE FILTER CONFIGURATION REGISTER (CONTINUED)** bit 7 **CRCERREN:** CRC Error Collection Enable bit 1 = The received packet CRC must be invalid for the packet to be accepted 0 = Disable CRC Error Collection filtering This bit allows the user to collect all packets that have an invalid CRC. CRCOKEN: CRC OK Enable bit bit 6 1 = The received packet CRC must be valid for the packet to be accepted 0 = Disable CRC filtering This bit allows the user to reject all packets that have an invalid CRC. RUNTERREN: Runt Error Collection Enable bit bit 5 1 = The received packet must be a runt packet for the packet to be accepted 0 = Disable Runt Error Collection filtering This bit allows the user to collect all packets that are runt packets. For this filter, a runt packet is defined as any packet with a size of less than 64 bytes (when CRCOKEN = 0) or any packet with a size of less than 64 bytes that has a valid CRC (when CRCOKEN = 1). bit 4 RUNTEN: Runt Enable bit 1 = The received packet must not be a runt packet for the packet to be accepted 0 = Disable Runt filtering This bit allows the user to reject all runt packets. For this filter, a runt packet is defined as any packet with a size of less than 64 bytes. bit 3 UCEN: Unicast Enable bit 1 = Enable Unicast Filtering 0 = Disable Unicast Filtering This bit allows the user to accept all unicast packets whose Destination Address matches the Station Address. bit 2 NOTMEEN: Not Me Unicast Enable bit 1 = Enable Not Me Unicast Filtering 0 = Disable Not Me Unicast Filtering This bit allows the user to accept all unicast packets whose Destination Address does not match the Station Address. bit 1 MCEN: Multicast Enable bit 1 = Enable Multicast Filtering 0 = Disable Multicast Filtering This bit allows the user to accept all Multicast Address packets.

#### bit 0 BCEN: Broadcast Enable bit

- 1 = Enable Broadcast Filtering

- 0 = Disable Broadcast Filtering

This bit allows the user to accept all Broadcast Address packets.

- **Note 1:** XOR = True when either one or the other conditions are true, but not both.

- 2: This Hash Table Filter match is active regardless of the value of the HTEN bit.

- 3: This Magic Packet Filter match is active regardless of the value of the MPEN bit.

```

Note 1:

This register is only used for RX operations.

2:

The bits in this register may only be changed while the RXEN bit (ETHCON1<8>) = 0.

```

# PIC32MX5XX/6XX/7XX

### **REGISTER 25-13: ETHIEN: ETHERNET CONTROLLER INTERRUPT ENABLE REGISTER**

| Bit<br>Range | Bit<br>31/23/15/7       | Bit<br>30/22/14/6        | Bit<br>29/21/13/5       | Bit<br>28/20/12/4 | Bit<br>27/19/11/3       | Bit<br>26/18/10/2        | Bit<br>25/17/9/1         | Bit<br>24/16/8/0         |

|--------------|-------------------------|--------------------------|-------------------------|-------------------|-------------------------|--------------------------|--------------------------|--------------------------|

| 31:24        | U-0                     | U-0                      | U-0                     | U-0               | U-0                     | U-0                      | U-0                      | U-0                      |

| 31.24        |                         | —                        | _                       |                   | —                       | —                        |                          | —                        |

| 23:16        | U-0                     | U-0                      | U-0                     | U-0               | U-0                     | U-0                      | U-0                      | U-0                      |

| 23.10        | —                       | —                        | —                       | _                 | —                       | —                        | —                        | —                        |

| 15:8         | U-0                     | R/W-0                    | R/W-0                   | U-0               | U-0                     | U-0                      | R/W-0                    | R/W-0                    |

| 10.0         | —                       | TXBUSEIE <sup>(1)</sup>  | RXBUSEIE <sup>(2)</sup> | _                 | —                       | —                        | EWMARKIE <sup>(2)</sup>  | FWMARKIE <sup>(2)</sup>  |

| 7:0          | R/W-0                   | R/W-0                    | R/W-0                   | U-0               | R/W-0                   | R/W-0                    | R/W-0                    | R/W-0                    |

| 7.0          | RXDONEIE <sup>(2)</sup> | PKTPENDIE <sup>(2)</sup> | RXACTIE <sup>(2)</sup>  |                   | TXDONEIE <sup>(1)</sup> | TXABORTIE <sup>(1)</sup> | RXBUFNAIE <sup>(2)</sup> | RXOVFLWIE <sup>(2)</sup> |

### Legend: