Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

## Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFI

| Product Status             | Active                                                                            |

|----------------------------|-----------------------------------------------------------------------------------|

| Core Processor             | MIPS32® M4K™                                                                      |

| Core Size                  | 32-Bit Single-Core                                                                |

| Speed                      | 80MHz                                                                             |

| Connectivity               | CANbus, Ethernet, I <sup>2</sup> C, SPI, UART/USART, USB OTG                      |

| Peripherals                | Brown-out Detect/Reset, DMA, POR, PWM, WDT                                        |

| Number of I/O              | 85                                                                                |

| Program Memory Size        | 256KB (256K x 8)                                                                  |

| Program Memory Type        | FLASH                                                                             |

| EEPROM Size                | -                                                                                 |

| RAM Size                   | 64K x 8                                                                           |

| Voltage - Supply (Vcc/Vdd) | 2.3V ~ 3.6V                                                                       |

| Data Converters            | A/D 16x10b                                                                        |

| Oscillator Type            | Internal                                                                          |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                                 |

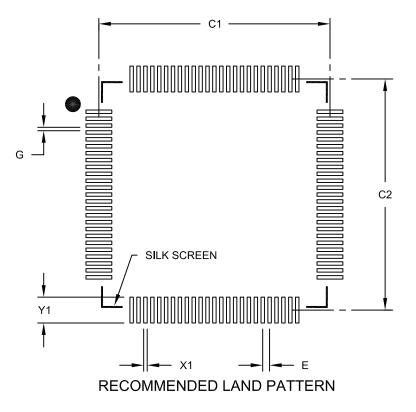

| Mounting Type              | Surface Mount                                                                     |

| Package / Case             | 100-TQFP                                                                          |

| Supplier Device Package    | 100-TQFP (14x14)                                                                  |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic32mx775f256lt-80i-pf |

|                            |                                                                                   |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

|          |                    | Pin Nur         | nber <sup>(1)</sup> |                 | Dia         | Duffer         |                                                                                                                                                                                                |

|----------|--------------------|-----------------|---------------------|-----------------|-------------|----------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Pin Name | 64-Pin<br>QFN/TQFP | 100-Pin<br>TQFP | 121-Pin<br>TFBGA    | 124-pin<br>VTLA | Pin<br>Type | Buffer<br>Type | Description                                                                                                                                                                                    |

| AN0      | 16                 | 25              | K2                  | B14             | I           | Analog         | Analog input channels                                                                                                                                                                          |

| AN1      | 15                 | 24              | K1                  | A15             | I           | Analog         |                                                                                                                                                                                                |

| AN2      | 14                 | 23              | J2                  | B13             | I           | Analog         |                                                                                                                                                                                                |

| AN3      | 13                 | 22              | J1                  | A13             | I           | Analog         |                                                                                                                                                                                                |

| AN4      | 12                 | 21              | H2                  | B11             | I           | Analog         |                                                                                                                                                                                                |

| AN5      | 11                 | 20              | H1                  | A12             | I           | Analog         |                                                                                                                                                                                                |

| AN6      | 17                 | 26              | L1                  | A20             | I           | Analog         |                                                                                                                                                                                                |

| AN7      | 18                 | 27              | J3                  | B16             | I           | Analog         |                                                                                                                                                                                                |

| AN8      | 21                 | 32              | K4                  | A23             | I           | Analog         |                                                                                                                                                                                                |

| AN9      | 22                 | 33              | L4                  | B19             | I           | Analog         |                                                                                                                                                                                                |

| AN10     | 23                 | 34              | L5                  | A24             | I           | Analog         |                                                                                                                                                                                                |

| AN11     | 24                 | 35              | J5                  | B20             | I           | Analog         |                                                                                                                                                                                                |

| AN12     | 27                 | 41              | J7                  | B23             | I           | Analog         |                                                                                                                                                                                                |

| AN13     | 28                 | 42              | L7                  | A28             | I           | Analog         |                                                                                                                                                                                                |

| AN14     | 29                 | 43              | K7                  | B24             | I           | Analog         |                                                                                                                                                                                                |

| AN15     | 30                 | 44              | L8                  | A29             | I           | Analog         |                                                                                                                                                                                                |

| CLKI     | 39                 | 63              | F9                  | B34             | I           | ST/<br>CMOS    | External clock source input. Always associated with OSC1 pin function.                                                                                                                         |

| CLKO     | 40                 | 64              | F11                 | A42             | 0           | _              | Oscillator crystal output. Connects to<br>crystal or resonator in Crystal Oscillator<br>mode. Optionally functions as CLKO in<br>RC and EC modes. Always associated<br>with OSC2 pin function. |

| OSC1     | 39                 | 63              | F9                  | B34             | I           | ST/<br>CMOS    | Oscillator crystal input. ST buffer when configured in RC mode; CMOS otherwise.                                                                                                                |

| OSC2     | 40                 | 64              | F11                 | A42             | I/O         |                | Oscillator crystal output. Connects to<br>crystal or resonator in Crystal Oscillator<br>mode. Optionally functions as CLKO in<br>RC and EC modes.                                              |

| SOSCI    | 47                 | 73              | C10                 | A47             | I           | ST/<br>CMOS    | 32.768 kHz low-power oscillator crystal<br>input; CMOS otherwise                                                                                                                               |

| SOSCO    | 48                 | 74              | B11                 | B40             | 0           | _              | 32.768 kHz low-power oscillator crystal<br>output                                                                                                                                              |

## TABLE 1-1: PINOUT I/O DESCRIPTIONS

ST = Schmitt Trigger input with CMOS levels O = Output I = Input I = Input I = Input I = TTL = TTL input buffer

Note 1: Pin numbers are only provided for reference. See the "Device Pin Tables" section for device pin availability.

2: See 25.0 "Ethernet Controller" for more information.

## 3.2 Architecture Overview

The MIPS32 M4K processor core contains several logic blocks working together in parallel, providing an efficient high-performance computing engine. The following blocks are included with the core:

- Execution Unit

- Multiply/Divide Unit (MDU)

- System Control Coprocessor (CP0)

- Fixed Mapping Translation (FMT)

- Dual Internal Bus interfaces

- Power Management

- MIPS16e<sup>®</sup> Support

- Enhanced JTAG (EJTAG) Controller

## 3.2.1 EXECUTION UNIT

The MIPS32 M4K processor core execution unit implements a load/store architecture with single-cycle ALU operations (logical, shift, add, subtract) and an autonomous multiply/divide unit. The core contains thirty-two 32-bit General Purpose Registers (GPRs) used for integer operations and address calculation. One additional register file shadow set (containing thirty-two registers) is added to minimize context switching overhead during interrupt/exception processing. The register file consists of two read ports and one write port and is fully bypassed to minimize operation latency in the pipeline.

The execution unit includes:

- 32-bit adder used for calculating the data address

- Address unit for calculating the next instruction address

- Logic for branch determination and branch target address calculation

- · Load aligner

- Bypass multiplexers used to avoid stalls when executing instruction streams where data producing instructions are followed closely by consumers of their results

- Leading Zero/One detect unit for implementing the CLZ and CLO instructions

- Arithmetic Logic Unit (ALU) for performing bit-wise logical operations

- Shifter and store aligner

## 3.2.2 MULTIPLY/DIVIDE UNIT (MDU)

MIPS32 M4K processor core includes a Multiply/Divide Unit (MDU) that contains a separate pipeline for multiply and divide operations. This pipeline operates in parallel with the Integer Unit (IU) pipeline and does not stall when the IU pipeline stalls. This allows MDU operations to be partially masked by system stalls and/or other integer unit instructions.

The high-performance MDU consists of a 32x16 booth recoded multiplier, result/accumulation registers (HI and LO), a divide state machine, and the necessary multiplexers and control logic. The first number shown ('32' of 32x16) represents the *rs* operand. The second number ('16' of 32x16) represents the *rt* operand. The PIC32 core only checks the value of the latter (*rt*) operand to determine how many times the operation must pass through the multiplier. The 16x16 and 32x16 operations pass through the multiplier once. A 32x32 operation passes through the multiplier twice.

The MDU supports execution of one 16x16 or 32x16 multiply operation every clock cycle; 32x32 multiply operations can be issued every other clock cycle. Appropriate interlocks are implemented to stall the issuance of back-to-back 32x32 multiply operations. The multiply operand size is automatically determined by logic built into the MDU.

Divide operations are implemented with a simple 1 bit per clock iterative algorithm. An early-in detection checks the sign extension of the dividend (*rs*) operand. If *rs* is 8 bits wide, 23 iterations are skipped. For a 16 bit wide *rs*, 15 iterations are skipped and for a 24 bit wide *rs*, 7 iterations are skipped. Any attempt to issue a subsequent MDU instruction while a divide is still active causes an IU pipeline stall until the divide operation is completed.

Table 3-1 lists the repeat rate (peak issue rate of cycles until the operation can be reissued) and latency (number of cycles until a result is available) for the PIC32 core multiply and divide instructions. The approximate latency and repeat rates are listed in terms of pipeline clocks.

| Opcode                  | Operand Size (mul rt) (div rs) | Latency | Repeat Rate |

|-------------------------|--------------------------------|---------|-------------|

| MULT/MULTU, MADD/MADDU, | 16 bits                        | 1       | 1           |

| MSUB/MSUBU              | 32 bits                        | 2       | 2           |

| MUL                     | 16 bits                        | 2       | 1           |

|                         | 32 bits                        | 3       | 2           |

| DIV/DIVU                | 8 bits                         | 12      | 11          |

|                         | 16 bits                        | 19      | 18          |

|                         | 24 bits                        | 26      | 25          |

|                         | 32 bits                        | 33      | 32          |

## TABLE 3-1:MIPS32<sup>®</sup> M4K<sup>®</sup> CORE HIGH-PERFORMANCE INTEGER MULTIPLY/DIVIDE UNIT<br/>LATENCIES AND REPEAT RATES

# PIC32MX5XX/6XX/7XX

NOTES:

NOTES:

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|

| 24.24        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 31:24        |                   |                   | _                 | —                 | -                 | _                 | _                | _                |

| 23:16        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | R/W-0            |

| 23.10        | —                 | —                 | —                 | —                 | _                 | —                 | —                | SS0              |

| 45.0         | U-0               | U-0               | U-0               | R/W-0             | U-0               | R/W-0             | R/W-0            | R/W-0            |

| 15:8         | _                 | —                 | —                 | MVEC              | _                 |                   | TPC<2:0>         |                  |

| 7.0          | U-0               | U-0               | U-0               | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |

| 7:0          |                   | _                 | _                 | INT4EP            | INT3EP            | INT2EP            | INT1EP           | INT0EP           |

## REGISTER 7-1: INTCON: INTERRUPT CONTROL REGISTER

#### Legend:

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, re | ad as '0'          |

|-------------------|------------------|---------------------------|--------------------|

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared      | x = Bit is unknown |

## bit 31-17 Unimplemented: Read as '0'

- bit 16 **SS0:** Single Vector Shadow Register Set bit

- 1 = Single vector is presented with a shadow register set

- 0 = Single vector is not presented with a shadow register set

- bit 15-13 Unimplemented: Read as '0'

- bit 12 MVEC: Multiple Vector Configuration bit

- 1 = Interrupt controller configured for Multi-vector mode

- 0 = Interrupt controller configured for Single-vector mode

- bit 11 Unimplemented: Read as '0'

- bit 10-8 TPC<2:0>: Interrupt Proximity Timer Control bits

- 111 = Interrupts of group priority 7 or lower start the Interrupt Proximity timer 110 = Interrupts of group priority 6 or lower start the Interrupt Proximity timer 101 = Interrupts of group priority 5 or lower start the Interrupt Proximity timer 100 = Interrupts of group priority 4 or lower start the Interrupt Proximity timer 011 = Interrupts of group priority 3 or lower start the Interrupt Proximity timer

- 010 = Interrupts of group priority 2 or lower start the Interrupt Proximity timer

- 001 = Interrupts of group priority 1 start the Interrupt Proximity timer

- 000 = Disables Interrupt Proximity timer

- bit 7-5 Unimplemented: Read as '0'

- bit 4 INT4EP: External Interrupt 4 Edge Polarity Control bit

- 1 = Rising edge

- 0 = Falling edge

- bit 3 INT3EP: External Interrupt 3 Edge Polarity Control bit

- 1 = Rising edge

- 0 = Falling edge

- bit 2 INT2EP: External Interrupt 2 Edge Polarity Control bit

- 1 = Rising edge

- 0 = Falling edge

- bit 1 **INT1EP:** External Interrupt 1 Edge Polarity Control bit

- 1 = Rising edge

- 0 = Falling edge

- bit 0 INTOEP: External Interrupt 0 Edge Polarity Control bit

- 1 = Rising edge

- 0 = Falling edge

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|

| 24.24        | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |

| 31:24        | IFS31             | IFS30             | IFS29             | IFS28             | IFS27             | IFS26             | IFS25            | IFS24            |

| 23:16        | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |

| 23.10        | IFS23             | IFS22             | IFS21             | IFS20             | IFS19             | IFS18             | IFS17            | IFS16            |

| 15:8         | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |

| 15.0         | IFS15             | IFS14             | IFS13             | IFS12             | IFS11             | IFS10             | IFS09            | IFS08            |

| 7.0          | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |

| 7:0          | IFS07             | IFS06             | IFS05             | IFS04             | IFS03             | IFS02             | IFS01            | IFS00            |

## REGISTER 7-4: IFSx: INTERRUPT FLAG STATUS REGISTER

## Legend:

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read as '0' |                    |  |  |  |

|-------------------|------------------|------------------------------------|--------------------|--|--|--|

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared               | x = Bit is unknown |  |  |  |

#### bit 31-0 IFS31-IFS00: Interrupt Flag Status bits

- 1 = Interrupt request has occurred

- 0 = Interrupt request has not occurred

**Note:** This register represents a generic definition of the IFSx register. Refer to Table 7-1 for the exact bit definitions.

## REGISTER 7-5: IECx: INTERRUPT ENABLE CONTROL REGISTER

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|

| 04.04        | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |

| 31:24        | IEC31             | IEC30             | IEC29             | IEC28             | IEC27             | IEC26             | IEC25            | IEC24            |

| 23:16        | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |

| 23.10        | IEC23             | IEC22             | IEC21             | IEC20             | IEC19             | IEC18             | IEC17            | IEC16            |

| 15.0         | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |

| 15:8         | IEC15             | IEC14             | IEC13             | IEC12             | IEC11             | IEC10             | IEC09            | IEC08            |

| 7.0          | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |

| 7:0          | IEC07             | IEC06             | IEC05             | IEC04             | IEC03             | IEC02             | IEC01            | IEC00            |

## Legend:

| · J · · ·         |                  |                           |                    |

|-------------------|------------------|---------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, re | ad as '0'          |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared      | x = Bit is unknown |

bit 31-0 IEC31-IEC00: Interrupt Enable bits

1 = Interrupt is enabled

0 = Interrupt is disabled

**Note:** This register represents a generic definition of the IECx register. Refer to Table 7-1 for the exact bit definitions.

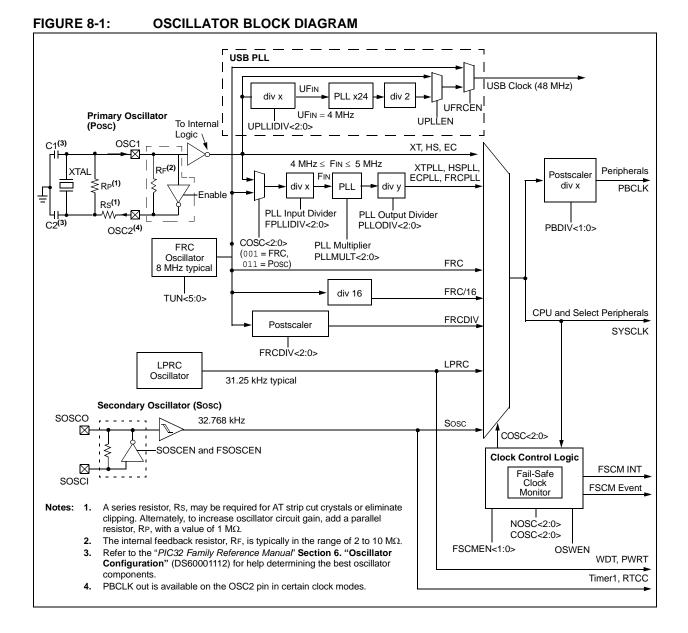

## 8.0 OSCILLATOR CONFIGURATION

Note: This data sheet summarizes the features of the PIC32MX5XX/6XX/7XX family of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to Section 6. "Oscillator" (DS60001112) in the "PIC32 Family Reference Manual", which is available from the Microchip web site (www.microchip.com/PIC32). The Oscillator module has the following features:

- A total of four external and internal oscillator options as clock sources

- On-chip PLL with user-selectable input divider, multiplier and output divider to boost operating frequency on select internal and external oscillator sources

- On-chip user-selectable divisor postscaler on select oscillator sources

- Software-controllable switching between various clock sources

- A Fail-Safe Clock Monitor (FSCM) that detects clock failure and permits safe application recovery or shutdown

- Dedicated On-Chip PLL for USB peripheral

Figure 8-1shows the Oscillator module block diagram.

| Bit<br>Range         | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2  | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |  |

|----------------------|-------------------|-------------------|-------------------|-------------------|-------------------|--------------------|------------------|------------------|--|--|

| 04.04                | U-0               | U-0               | R/W-y             | R/W-y             | R/W-y             | R/W-0              | R/W-0            | R/W-1            |  |  |

| 31:24 — PLLODIV<2:0> |                   |                   |                   |                   |                   | FRCDIV<2:0>        |                  |                  |  |  |

| 00.40                | U-0               | R-0               | R-1               | R/W-y             | R/W-y             | R/W-y              | R/W-y            | R/W-y            |  |  |

| 23:16                | —                 | SOSCRDY           | PBDIVRDY          | PBDIV             | /<1:0>            | <1:0> PLLMULT<2:0> |                  |                  |  |  |

| 45.0                 | U-0               | R-0               | R-0               | R-0               | U-0               | R/W-y              | R/W-y            | R/W-y            |  |  |

| 15:8                 | —                 |                   | COSC<2:0>         |                   | —                 | NOSC<2:0>          |                  |                  |  |  |

| 7.0                  | R/W-0             | R-0               | R-0               | R/W-0             | R/W-0             | R/W-0              | R/W-y            | R/W-0            |  |  |

| 7:0                  | CLKLOCK           | ULOCK             | SLOCK             | SLPEN             | CF                | UFRCEN             | SOSCEN           | OSWEN            |  |  |

## REGISTER 8-1: OSCCON: OSCILLATOR CONTROL REGISTER

Legend:

y = Value set from Configuration bits on POR

- R = Readable bit -n = Value at POR

- W = Writable bit U = Unimplemented bit, read as '0'

- '1' = Bit is set

- 0' = Bit is cleared x = Bit is unknown

bit 31-30 Unimplemented: Read as '0'

bit 29-27 PLLODIV<2:0>: Output Divider for PLL

- 111 = PLL output divided by 256

- 110 = PLL output divided by 64

- 101 = PLL output divided by 32

- 100 = PLL output divided by 16

- 011 = PLL output divided by 8

- 010 = PLL output divided by 4

- 001 = PLL output divided by 2

- 000 = PLL output divided by 1

#### bit 26-24 FRCDIV<2:0>: Internal Fast RC (FRC) Oscillator Clock Divider bits

- 111 = FRC divided by 256

- 110 = FRC divided by 64

- 101 = FRC divided by 32

- 100 = FRC divided by 16

- 011 = FRC divided by 8

- 010 = FRC divided by 4

- 001 = FRC divided by 2 (default setting)

- 000 = FRC divided by 1

- bit 23 Unimplemented: Read as '0'

- bit 22 SOSCRDY: Secondary Oscillator (Sosc) Ready Indicator bit

- 1 = Indicates that the Secondary Oscillator is running and is stable

- 0 = Secondary Oscillator is still warming up or is turned off

- bit 21 PBDIVRDY: Peripheral Bus Clock (PBCLK) Divisor Ready bit

- 1 = PBDIV<1:0> bits can be written

- 0 = PBDIV<1:0> bits cannot be written

- bit 20-19 **PBDIV<1:0>:** Peripheral Bus Clock (PBCLK) Divisor bits

- 11 = PBCLK is SYSCLK divided by 8 (default)

- 10 = PBCLK is SYSCLK divided by 4

- 01 = PBCLK is SYSCLK divided by 2

- 00 = PBCLK is SYSCLK divided by 1

**Note:** Writes to this register require an unlock sequence. Refer to **Section 6. "Oscillator"** (DS60001112) in the *"PIC32 Family Reference Manual"* for details.

## TABLE 11-1: USB REGISTER MAP (CONTINUED)

| ess                         |                                 |           |       |       | · · · |       |       |       |      |      | Bits  |          |       |          |        |        |           |          |            |

|-----------------------------|---------------------------------|-----------|-------|-------|-------|-------|-------|-------|------|------|-------|----------|-------|----------|--------|--------|-----------|----------|------------|

| Virtual Address<br>(BF88_#) | Register<br>Name <sup>(1)</sup> | Bit Range | 31/15 | 30/14 | 29/13 | 28/12 | 27/11 | 26/10 | 25/9 | 24/8 | 23/7  | 22/6     | 21/5  | 20/4     | 19/3   | 18/2   | 17/1      | 16/0     | All Resets |

| 5280                        | U1FRML <sup>(3)</sup>           | 31:16     |       | —     | —     | —     | —     | —     | —    | —    | _     | —        | _     | —        | —      | —      | _         | _        | 0000       |

| 5200                        | OTTRIME                         | 15:0      | —     |       | —     | —     | —     | —     | —    | —    |       |          |       | FRML<    | 7:0>   |        |           |          | 0000       |

| 5290                        | U1FRMH <sup>(3)</sup>           | 31:16     | —     | —     | —     | —     | —     | —     | —    | —    | —     | —        | —     | —        | —      | —      | —         | —        | 0000       |

| 0200                        | 01110                           | 15:0      | —     | —     | —     | —     | —     | —     | —    | —    | _     | —        | _     | -        | —      |        | FRMH<2:0> | •        | 0000       |

| 52A0                        | U1TOK                           | 31:16     | —     | —     | —     | —     | —     | —     | —    | —    | —     | —        | —     | —        | —      | —      | —         | —        | 0000       |

| 02/10                       | orron                           | 15:0      | —     | —     | —     | —     | —     | —     | —    | —    |       | PID      | <3:0> |          |        | EP     | <3:0>     |          | 0000       |

| 52B0                        | U1SOF                           | 31:16     | —     | —     | —     | —     | —     | —     | —    | —    | _     | —        | _     | —        | —      | —      | _         | —        | 0000       |

| 5260                        | 0130F                           | 15:0      | —     | _     | _     | —     | _     | _     | _    |      |       |          |       | CNT<7    | 7:0>   |        |           |          | 0000       |

| 52C0                        | U1BDTP2                         | 31:16     | —     | -     | —     | —     | _     | _     | -    |      | —     | —        |       | —        | —      | _      |           | _        | 0000       |

| 5200                        | OIBDIF2                         | 15:0      | —     | —     | —     | —     | —     | —     | —    | —    |       |          |       | BDTPTRH  | H<7:0> |        |           |          | 0000       |

| 52D0                        | U1BDTP3                         | 31:16     | —     | _     | _     | —     | _     | _     | _    |      | —     | _        |       | —        | _      | _      |           | _        | 0000       |

| 5200                        | UIBDIF3                         | 15:0      | —     | _     | _     | _     | _     | _     | -    |      |       |          |       | BDTPTRU  | J<7:0> |        |           |          | 0000       |

| 52E0                        | U1CNFG1                         | 31:16     | —     | _     | _     | —     | _     | _     | _    |      | —     | _        |       | —        | _      | _      |           | _        | 0000       |

| 52E0                        |                                 | 15:0      | —     | _     | _     | —     | _     | _     | _    |      | UTEYE | UOEMON   |       | USBSIDL  | —      | _      |           | UASUSPND | 0001       |

| 5300                        | U1EP0                           | 31:16     | —     | _     | _     | _     | _     | _     | -    |      | —     | _        |       | —        | _      | _      |           | _        | 0000       |

| 5300                        | UIEPU                           | 15:0      | —     | _     | _     | —     | _     | _     | _    |      | LSPD  | RETRYDIS |       | EPCONDIS | EPRXEN | EPTXEN | EPSTALL   | EPHSHK   | 0000       |

| 5310                        | U1EP1                           | 31:16     | —     | _     | _     | —     | _     | _     | _    |      | —     | _        |       | —        | _      | _      |           | _        | 0000       |

| 5310                        | UIEPI                           | 15:0      | —     | _     | _     | _     | _     | _     | _    | _    | —     | _        | -     | EPCONDIS | EPRXEN | EPTXEN | EPSTALL   | EPHSHK   | 0000       |

| 5320                        | U1EP2                           | 31:16     | —     | _     | _     | —     | _     | _     | _    |      | —     | _        |       | —        | _      | _      |           | _        | 0000       |

| 5520                        | UIEFZ                           | 15:0      | _     | _     | _     | _     | _     | _     | _    |      | —     | _        | -     | EPCONDIS | EPRXEN | EPTXEN | EPSTALL   | EPHSHK   | 0000       |

| 5330                        | U1EP3                           | 31:16     | —     | _     | _     | _     | _     | _     | _    | _    | —     | _        | -     | —        | _      |        |           | _        | 0000       |

| 5330                        | UIEP3                           | 15:0      | —     | _     | _     | —     | _     | _     | _    |      | —     | _        |       | EPCONDIS | EPRXEN | EPTXEN | EPSTALL   | EPHSHK   | 0000       |

| 5340                        | U1EP4                           | 31:16     | _     | _     | -     | -     | -     | -     | -    | _    | _     | _        | _     | —        | -      | _      | _         | _        | 0000       |

| 5540                        | UTEP4                           | 15:0      | —     | _     | _     | _     | _     | _     | _    | _    | —     | _        | -     | EPCONDIS | EPRXEN | EPTXEN | EPSTALL   | EPHSHK   | 0000       |

| 5350                        | U1EP5                           | 31:16     | _     | _     | -     | -     | -     | -     | -    | _    | _     | _        | _     | —        | -      | _      | _         | _        | 0000       |

| 5350                        | UIEP5                           | 15:0      | _     | _     | -     | -     | -     | -     | -    | _    | _     | _        | _     | EPCONDIS | EPRXEN | EPTXEN | EPSTALL   | EPHSHK   | 0000       |

| 5260                        | U1EP6                           | 31:16     |       |       | _     | —     | _     |       |      | _    | —     |          |       | —        | _      | —      |           |          | 0000       |

| 5360                        | UTEP6                           | 15:0      | _     | _     | -     | -     | -     | -     | -    | _    | _     | _        | _     | EPCONDIS | EPRXEN | EPTXEN | EPSTALL   | EPHSHK   | 0000       |

| 5270                        | U1EP7                           | 31:16     | _     | _     | _     | _     | _     | _     | _    | _    | _     | —        | -     | —        | _      | _      | -         | _        | 0000       |

| 5370                        | UTEPT                           | 15:0      |       |       | _     | _     | _     |       |      | _    | —     |          |       | EPCONDIS | EPRXEN | EPTXEN | EPSTALL   | EPHSHK   | 0000       |

| 5200                        |                                 | 31:16     | _     | _     | _     | _     | _     | _     | _    | —    | -     | —        | _     | —        | _      | —      | _         | _        | 0000       |

| 5380                        | U1EP8                           | 15:0      | —     | _     | —     | —     | _     | _     | —    | _    | _     | _        | -     | EPCONDIS | EPRXEN | EPTXEN | EPSTALL   | EPHSHK   | 0000       |

| 5000                        |                                 | 31:16     | _     | —     | _     | _     | _     | _     | —    | —    | _     | —        | _     | —        | —      | —      | —         | —        | 0000       |

| 5390                        | U1EP9                           | 15:0      | _     | —     | _     | _     | _     | _     | _    | _    | _     | _        | _     | EPCONDIS | EPRXEN | EPTXEN | EPSTALL   | EPHSHK   | 0000       |

5390

U1EP9

Legend:

x =

Note

1:

All n

end: x = unknown value on Reset; — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

1: All registers in this table (except as noted) have corresponding CLR, SET and INV registers at its virtual address, plus an offset of 0x4, 0x8 and 0xC respectively. See Section 12.1.1 "CLR, SET and INV Registers" for more information.

2: This register does not have associated SET and INV registers.

3: This register does not have associated CLR, SET and INV registers.

4: Reset value for this bit is undefined.

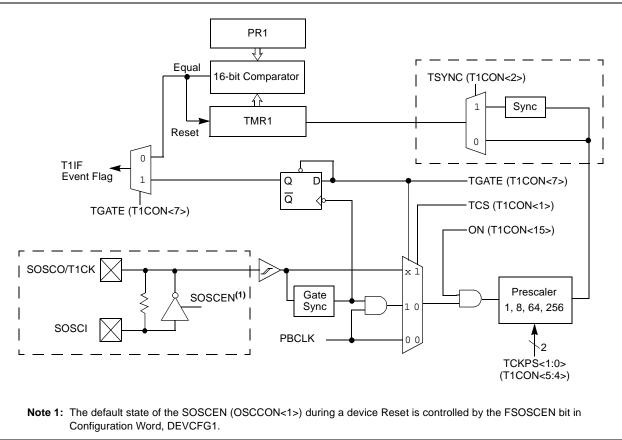

## 13.0 TIMER1

Note: This data sheet summarizes the features of the PIC32MX5XX/6XX/7XX family of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to **Section 14. "Timers"** (DS60001105) in the *"PIC32 Family Reference Manual"*, which is available from the Microchip web site (www.microchip.com/PIC32).

This family of PIC32 devices features one synchronous/ asynchronous 16-bit timer that can operate as a free-running interval timer for various timing applications and counting external events. This timer can also be used with the low-power Secondary Oscillator (Sosc) for Real-Time Clock (RTC) applications. The following modes are supported:

- Synchronous Internal Timer

- Synchronous Internal Gated Timer

- Synchronous External Timer

- Asynchronous External Timer

## FIGURE 13-1: TIMER1 BLOCK DIAGRAM

## 13.1 Additional Supported Features

- Selectable clock prescaler

- Timer operation during Idle and Sleep mode

- Fast bit manipulation using CLR, SET and INV registers

- Asynchronous mode can be used with the Sosc to function as a Real-Time Clock (RTC)

A simplified block diagram of the Timer1 module is illustrated in Figure 13-1.

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4    | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

|--------------|-------------------|-------------------|-------------------|----------------------|-------------------|-------------------|------------------|------------------|

| 24.24        | U-0               | U-0               | U-0               | U-0                  | U-0               | U-0               | U-0              | U-0              |

| 31:24        |                   | —                 | _                 | -                    | —                 | —                 | —                | —                |

| 00.40        | U-0               | U-0               | U-0               | U-0                  | U-0               | U-0               | U-0              | U-0              |

| 23:16        |                   | —                 | _                 | —                    | —                 | —                 | —                | —                |

| 45.0         | R/W-0             | U-0               | R/W-0             | U-0                  | U-0               | U-0               | U-0              | U-0              |

| 15:8         | 0N <sup>(1)</sup> | —                 | SIDL              | —                    | —                 | —                 | —                | —                |

| 7.0          | U-0               | U-0               | R/W-0             | R-0                  | R/W-0             | R/W-0             | R/W-0            | R/W-0            |

| 7:0          | _                 | —                 | OC32              | OCFLT <sup>(2)</sup> | OCTSEL            |                   | OCM<2:0>         |                  |

## REGISTER 17-1: OCxCON: OUTPUT COMPARE 'x' CONTROL REGISTER

#### Legend:

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, r | read as '0'        |

|-------------------|------------------|--------------------------|--------------------|

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared     | x = Bit is unknown |

#### bit 31-16 Unimplemented: Read as '0'

- bit 15 **ON:** Output Compare Module On bit<sup>(1)</sup>

- 1 = Output Compare module is enabled

- 0 = Output Compare module is disabled

- bit 14 Unimplemented: Read as '0'

- bit 13 SIDL: Stop in Idle Mode bit

- 1 = Discontinue operation when CPU enters Idle mode

- 0 = Continue operation when CPU is in Idle mode

- bit 12-6 Unimplemented: Read as '0'

- bit 5 **OC32:** 32-bit Compare Mode bit

- 1 = OCxR<31:0> and/or OCxRS<31:0> are used for comparisons to the 32-bit timer source

- 0 = OCxR<15:0> and OCxRS<15:0> are used for comparisons to the 16-bit timer source

- bit 4 **OCFLT:** PWM Fault Condition Status bit<sup>(2)</sup>

- 1 = PWM Fault condition has occurred (only cleared in hardware)

- 0 = PWM Fault condition has not occurred

#### bit 3 OCTSEL: Output Compare Timer Select bit

- 1 = Timer3 is the clock source for this Output Compare module

- 0 = Timer2 is the clock source for this Output Compare module

- bit 2-0 OCM<2:0>: Output Compare Mode Select bits

- 111 = PWM mode on OCx; Fault pin enabled

- 110 = PWM mode on OCx; Fault pin disabled

- 101 = Initialize OCx pin low; generate continuous output pulses on OCx pin

- 100 = Initialize OCx pin low; generate single output pulse on OCx pin

- 011 = Compare event toggles OCx pin

- 010 = Initialize OCx pin high; compare event forces OCx pin low

- 001 = Initialize OCx pin low; compare event forces OCx pin high

- 000 = Output compare peripheral is disabled but continues to draw current

- **Note 1:** When using the 1:1 PBCLK divisor, the user's software should not read/write the peripheral's SFRs in the SYSCLK cycle immediately following the instruction that clears the module's ON bit.

- **2:** This bit is only used when OCM < 2:0 > = 111. It is read as '0' in all other modes.

## 19.0 INTER-INTEGRATED CIRCUIT (I<sup>2</sup>C)

Note: This data sheet summarizes the features of the PIC32MX5XX/6XX/7XX family of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to Section 24. "Inter-Integrated Circuit (I<sup>2</sup>C)" (DS60001116) in the "*PIC32 Family Reference Manual*", which is available from the Microchip web site (www.microchip.com/PIC32). The  $l^2C$  module provides complete hardware support for both Slave and Multi-Master modes of the  $l^2C$  serial communication standard. Figure 19-1 illustrates the  $l^2C$  module block diagram.

Each  $I^2C$  module has a 2-pin interface: the SCLx pin is clock and the SDAx pin is data.

Each I<sup>2</sup>C module offers the following key features:

- I<sup>2</sup>C interface supporting both master and slave operation

- I<sup>2</sup>C Slave mode supports 7-bit and 10-bit addressing

- I<sup>2</sup>C Master mode supports 7-bit and 10-bit addressing

- I<sup>2</sup>C port allows bidirectional transfers between master and slaves

- Serial clock synchronization for the I<sup>2</sup>C port can be used as a handshake mechanism to suspend and resume serial transfer (SCLREL control)

- I<sup>2</sup>C supports multi-master operation; detects bus collision and arbitrates accordingly

- Provides support for address bit masking

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|

| 04.04        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 31:24        |                   | —                 | _                 |                   | —                 |                   | —                | _                |

| 00.40        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 23:16        | —                 | —                 | _                 | —                 | —                 | _                 | —                | _                |

| 45.0         | R-0, HSC          | R-0, HSC          | U-0               | U-0               | U-0               | R/C-0, HS         | R-0, HSC         | R-0, HSC         |

| 15:8         | ACKSTAT           | TRSTAT            | _                 | —                 | —                 | BCL               | GCSTAT           | ADD10            |

| 7.0          | R/C-0, HS         | R/C-0, HS         | R-0, HSC          | R/C-0, HSC        | R/C-0, HSC        | R-0, HSC          | R-0, HSC         | R-0, HSC         |

| 7:0          | IWCOL             | I2COV             | D_A               | Р                 | S                 | R_W               | RBF              | TBF              |

## REGISTER 19-2: I2CxSTAT: I<sup>2</sup>C STATUS REGISTER

| Legend:           | HS = Set by hardware | HSC = Hardware set/clea            | red               |

|-------------------|----------------------|------------------------------------|-------------------|

| R = Readable bit  | W = Writable bit     | U = Unimplemented bit, read as '0' |                   |

| -n = Value at POR | '1' = Bit is set     | '0' = Bit is cleared               | C = Clearable bit |

## bit 31-16 Unimplemented: Read as '0'

- bit 15 **ACKSTAT:** Acknowledge Status bit (when operating as I<sup>2</sup>C master, applicable to master transmit operation) This bit is set or cleared by hardware at the end of a slave Acknowledge.

- 1 = NACK received from slave

- 0 = ACK received from slave

- bit 14 **TRSTAT:** Transmit Status bit (when operating as I<sup>2</sup>C master, applicable to master transmit operation) This bit is set by hardware at the beginning of a master transmission, and is cleared by hardware at the end of a slave Acknowledge.

- 1 = Master transmit is in progress (8 bits + ACK)

- 0 = Master transmit is not in progress

- bit 13-11 Unimplemented: Read as '0'

- bit 10 BCL: Master Bus Collision Detect bit

This bit is set by hardware at the detection of a bus collision.

- 1 = A bus collision has been detected during a master operation

- 0 = No collision

- bit 9 GCSTAT: General Call Status bit

This bit is set by hardware when the address matches the general call address, and is cleared by hardware clear at a Stop detection.

- 1 = General call address was received

- 0 = General call address was not received

## bit 8 ADD10: 10-bit Address Status bit

This bit is set by hardware upon a match of the 2nd byte of the matched 10-bit address, and is cleared by hardware at a Stop detection.

- 1 = 10-bit address was matched

- 0 = 10-bit address was not matched

## bit 7 IWCOL: Write Collision Detect bit

- This bit is set by hardware at the occurrence of a write to I2CxTRN while busy (cleared by software).

- 1 = An attempt to write the I2CxTRN register failed because the  $I^2C$  module is busy

- 0 = No collision

## bit 6 I2COV: Receive Overflow Flag bit

- This bit is set by hardware at an attempt to transfer I2CxRSR to I2CxRCV (cleared by software).

- 1 = A byte was received while the I2CxRCV register is still holding the previous byte

- 0 = No overflow

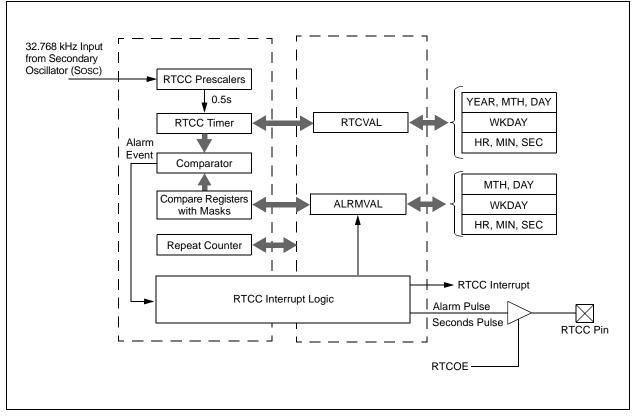

## 22.0 REAL-TIME CLOCK AND CALENDAR (RTCC)

Note: This data sheet summarizes the features of the PIC32MX5XX/6XX/7XX family of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to Section 29. "Real-Time Clock and Calendar (RTCC)" (DS60001125) in the "PIC32 Family Reference Manual", which is available from the Microchip web site (www.microchip.com/PIC32).

The PIC32 RTCC module is intended for applications in which accurate time must be maintained for extended periods of time with minimal or no CPU intervention. Low-power optimization provides extended battery lifetime while keeping track of time. A simplified block diagram of the RTCC module is illustrated in Figure 22-1. Key features of the RTCC module include:

- Time: hours, minutes and seconds

- 24-hour format (military time)

- · Visibility of one-half second period

- Provides calendar: Weekday, date, month and year

- Alarm intervals are configurable for half of a second, one second, 10 seconds, one minute, 10 minutes, one hour, one day, one week, one month and one year

- Alarm repeat with decrementing counter

- Alarm with indefinite repeat: Chime

- Year range: 2000 to 2099

- Leap year correction

- · BCD format for smaller firmware overhead

- Optimized for long-term battery operation

- Fractional second synchronization

- User calibration of the clock crystal frequency with auto-adjust

- Calibration range: ±0.66 seconds error per month

- · Calibrates up to 260 ppm of crystal error

- Requirements: External 32.768 kHz clock crystal

- Alarm pulse or seconds clock output on RTCC pin

## FIGURE 22-1: RTCC BLOCK DIAGRAM

| Bit<br>Range | Bit<br>31/23/15/7       | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3      | Bit<br>26/18/10/2 | Bit<br>25/17/9/1       | Bit<br>24/16/8/0 |

|--------------|-------------------------|-------------------|-------------------|-------------------|------------------------|-------------------|------------------------|------------------|

| 24.24        | U-0                     | U-0               | U-0               | U-0               | U-0                    | U-0               | R/W-0                  | R/W-0            |

| 31:24        | —                       | —                 | —                 | —                 | —                      | —                 | CAL<9                  | ):8>             |

| 23:16        | R/W-0                   | R/W-0             | R/W-0             | R/W-0             | R/W-0                  | R/W-0             | R/W-0                  | R/W-0            |

| 23.10        | CAL<7:0>                |                   |                   |                   |                        |                   |                        |                  |

| 15:8         | R/W-0                   | U-0               | R/W-0             | U-0               | U-0                    | U-0               | U-0                    | U-0              |

| 0.61         | ON <sup>(1,2)</sup>     |                   | SIDL              | —                 | —                      | -                 |                        | _                |

| 7.0          | R/W-0                   | R-0               | U-0               | U-0               | R/W-0                  | R-0               | R-0                    | R/W-0            |

| 7:0          | RTSECSEL <sup>(3)</sup> | RTCCLKON          | _                 | —                 | RTCWREN <sup>(4)</sup> | RTCSYNC           | HALFSEC <sup>(5)</sup> | RTCOE            |

|              |                         |                   |                   |                   |                        |                   |                        |                  |

## REGISTER 22-1: RTCCON: RTC CONTROL REGISTER

## Legend:

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, re | ad as '0'          |  |

|-------------------|------------------|---------------------------|--------------------|--|

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared      | x = Bit is unknown |  |

## bit 31-26 Unimplemented: Read as '0'

bit 25-16 **CAL<9:0>:** RTC Drift Calibration bits, which contain a signed 10-bit integer value

| ~0 10    |                                                                                                          |

|----------|----------------------------------------------------------------------------------------------------------|

|          | 1111111111 = Minimum negative adjustment, subtracts 1 RTC clock pulse every one minute                   |

|          | •                                                                                                        |

|          | •                                                                                                        |

|          | •<br>1000000000 = Maximum negative adjustment, subtracts 512 clock pulses every one minute               |

|          | 0111111111 = Maximum positive adjustment, adds 511 RTC clock pulses every one minute                     |

|          | •                                                                                                        |

|          | •                                                                                                        |

|          | •                                                                                                        |

|          | 000000001 = Minimum positive adjustment, adds 1 RTC clock pulse every one minute                         |

|          | 000000000 = No adjustment                                                                                |

| bit 15   | ON: RTCC On bit <sup>(1,2)</sup>                                                                         |

|          | 1 = RTCC module is enabled                                                                               |

|          | 0 = RTCC module is disabled                                                                              |

| bit 14   | Unimplemented: Read as '0'                                                                               |

| bit 13   | SIDL: Stop in Idle Mode bit                                                                              |

|          | 1 = Disables the PBCLK to the RTCC when CPU enters in Idle mode                                          |

|          | 0 = Continue normal operation in Idle mode                                                               |

| bit 12-8 | Unimplemented: Read as '0'                                                                               |

| bit 7    | RTSECSEL: RTCC Seconds Clock Output Select bit <sup>(3)</sup>                                            |

|          | 1 = RTCC Seconds Clock is selected for the RTCC pin                                                      |

|          | 0 = RTCC Alarm Pulse is selected for the RTCC pin                                                        |

| bit 6    | RTCCLKON: RTCC Clock Enable Status bit                                                                   |

|          | 1 = RTCC Clock is actively running                                                                       |

|          | 0 = RTCC Clock is not running                                                                            |

| bit 5-4  | Unimplemented: Read as '0'                                                                               |

|          | •                                                                                                        |

| Note 1:  | The ON bit is only writable when RTCWREN = 1.                                                            |

| 2:       | When using the 1:1 PBCLK divisor, the user's software should not read/write the peripheral's SFRs in the |

|          | SYSCLK cycle immediately following the instruction that clears the module's ON bit.                      |

| 3:       | Requires $RTCOE = 1$ (RTCCON<0>) for the output to be active.                                            |

| 4:       | The RTCWREN bit can only be set when the write sequence is enabled.                                      |

| 5:       | This bit is read-only. It is cleared to '0' on a write to the seconds bit fields (RTCTIME<14:8>).        |

|          |                                                                                                          |

|          |                                                                                                          |

Note: This register is only reset on a Power-on Reset (POR).

© 2009-2016 Microchip Technology Inc.

| REGISTER 23-2: AD1CON2: ADC CONTROL REGISTER 2 |

|------------------------------------------------|

|------------------------------------------------|

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|

| 24.24        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 31:24        | —                 | —                 | —                 | —                 | —                 | —                 | —                | —                |

| 00.40        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 23:16        |                   |                   | —                 | _                 | —                 | —                 | —                | —                |

| 45.0         | R/W-0             | R/W-0             | R/W-0             | R/W-0             | U-0               | R/W-0             | U-0              | U-0              |

| 15:8         | VCFG<2:0>         |                   | OFFCAL            | —                 | CSCNA             | —                 | —                |                  |

| 7.0          | R-0               | U-0               | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |

| 7:0          | BUFS              | _                 | SMPI<3:0>         |                   |                   | BUFM              | ALTS             |                  |

#### Legend:

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, re | ad as '0'          |

|-------------------|------------------|---------------------------|--------------------|

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared      | x = Bit is unknown |

## bit 31-16 Unimplemented: Read as '0'

bit 15-13 VCFG<2:0>: Voltage Reference Configuration bits

| Bit Value | VREFH              | VREFL              |

|-----------|--------------------|--------------------|

| lxx       | AVdd               | AVss               |

| 011       | External VREF+ pin | External VREF- pin |

| 010       | AVdd               | External VREF- pin |

| 001       | External VREF+ pin | AVss               |

| 000       | AVDD               | AVss               |

## bit 12 **OFFCAL:** Input Offset Calibration Mode Select bit

1 = Enable Offset Calibration mode

Positive and negative inputs of the S&H circuit are connected to VREFL.

0 = Disable Offset Calibration mode

The inputs to the S&H circuit are controlled by AD1CHS or AD1CSSL.

## bit 11 Unimplemented: Read as '0'

- bit 10 **CSCNA:** Input Scan Select bit

- 1 = Scan inputs

0 = Do not scan inputs

- bit 9-8 Unimplemented: Read as '0'

- bit 7 BUFS: Buffer Fill Status bit

- Only valid when BUFM = 1.

- 1 = ADC is currently filling buffer 0x8-0xF, user should access data in 0x0-0x7

- 0 = ADC is currently filling buffer 0x0-0x7, user should access data in 0x8-0xF

## bit 6 Unimplemented: Read as '0'

## bit 5-2 SMPI<3:0>: Sample/Convert Sequences Per Interrupt Selection bits

- 1111 = Interrupts at the completion of conversion for each 16<sup>th</sup> sample/convert sequence 1110 = Interrupts at the completion of conversion for each 15<sup>th</sup> sample/convert sequence

- 1110 = Interrupts at the completion of conversion for each 15" sample/convert sequence

- •

0001 = Interrupts at the completion of conversion for each 2<sup>nd</sup> sample/convert sequence 0000 = Interrupts at the completion of conversion for each sample/convert sequence

- bit 1 BUFM: ADC Result Buffer Mode Select bit

- 1 = Buffer configured as two 8-word buffers, ADC1BUF7-ADC1BUF0, ADC1BUFF-ADCBUF8

- 0 = Buffer configured as one 16-word buffer ADC1BUFF-ADC1BUF0

- bit 0 ALTS: Alternate Input Sample Mode Select bit

- 1 = Uses Sample A input multiplexer settings for first sample, and then alternates between Sample B and Sample A input multiplexer settings for all subsequent samples

- 0 = Always use Sample A input multiplexer settings

# PIC32MX5XX/6XX/7XX

|              |                   |                       |                       |                      |                   | •                         |                  | ,                |

|--------------|-------------------|-----------------------|-----------------------|----------------------|-------------------|---------------------------|------------------|------------------|

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6     | Bit<br>29/21/13/5     | Bit<br>28/20/12/4    | Bit<br>27/19/11/3 | Bit<br>26/18/10/2         | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

| 31:24        | U-0               | U-0                   | U-0                   | U-0                  | U-0               | U-0                       | U-0              | U-0              |

| 31.24        | —                 | —                     | —                     | _                    | —                 | _                         | _                | —                |

| 00.40        | U-0               | U-0                   | U-0                   | R/W-0                | R/W-0             | R/W-0                     | R/W-0            | R/W-0            |

| 23:16        | —                 | —                     | —                     |                      |                   | FSIZE<4:0> <sup>(1)</sup> | )                |                  |

| 15.0         | U-0               | S/HC-0                | S/HC-0                | R/W-0                | U-0               | U-0                       | U-0              | U-0              |

| 15:8         | —                 | FRESET                | UINC                  | DONLY <sup>(1)</sup> | —                 | _                         | _                | —                |

| 7.0          | R/W-0             | R-0                   | R-0                   | R-0                  | R/W-0             | R/W-0                     | R/W-0            | R/W-0            |

| 7:0          | TXEN              | TXABAT <sup>(2)</sup> | TXLARB <sup>(3)</sup> | TXERR <sup>(3)</sup> | TXREQ             | RTREN                     | TXPR             | <1:0>            |

## **REGISTER 24-20:** CiFIFOCONn: CAN FIFO CONTROL REGISTER 'n' (n = 0 THROUGH 31)

## Legend:

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read as '0' |                    |

|-------------------|------------------|------------------------------------|--------------------|

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared               | x = Bit is unknown |

## bit 31-21 Unimplemented: Read as '0'

| bit 20-16 FSIZE<4:0>: FIFO Size bits' | bit 20-16 | FSIZE<4:0>: FIFO Size bits <sup>(1)</sup> |

|---------------------------------------|-----------|-------------------------------------------|

|---------------------------------------|-----------|-------------------------------------------|

- 11111 = FIFO is 32 messages deep

- •

- 00010 = FIFO is 3 messages deep 00001 = FIFO is 2 messages deep

00000 = FIFO is 1 message deep

## bit 15 Unimplemented: Read as '0'

## bit 14 FRESET: FIFO Reset bits

1 = FIFO will be reset when bit is set, cleared by hardware when FIFO is reset. After setting, the user should poll whether this bit is clear before taking any action.

## 0 = No effect

## bit 13 UINC: Increment Head/Tail bit

$\frac{TXEN = 1:}{When this bit is set the FIFO head will increment by a single message$  $<math display="block">\frac{TXEN = 0:}{When this bit is set the FIFO tail will increment by a single message$ When this bit is set the FIFO tail will increment by a single message $<math display="block">\frac{TXEN = 0}{When this bit is set the FIFO tail will increment by a single message }$

## bit 12 DONLY: Store Message Data Only bit<sup>(1)</sup>

$\frac{\text{TXEN} = 1:}{\text{TXEN} = 1:}$  (FIFO configured as a Transmit FIFO) This bit is not used and has no effect.  $\frac{\text{TXEN} = 0:}{\text{TXEN} = 0:}$  (FIFO configured as a Receive FIFO)

- 1 =Only data bytes will be stored in the FIFO

- 0 = Full message is stored, including identifier

## bit 11-8 Unimplemented: Read as '0'

- bit 7 **TXEN:** TX/RX Buffer Selection bit

- 1 = FIFO is a Transmit FIFO

- 0 = FIFO is a Receive FIFO

- **Note 1:** These bits can only be modified when the CAN module is in Configuration mode (OPMOD<2:0> bits (CiCON<23:21>) = 100).

- 2: This bit is updated when a message completes (or aborts) or when the FIFO is reset.

- 3: This bit is reset on any read of this register or when the FIFO is reset.

## REGISTER 25-11: ETHRXFC: ETHERNET CONTROLLER RECEIVE FILTER CONFIGURATION REGISTER

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|--|

| 31:24        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |  |

|              |                   | —                 | _                 | —                 | _                 | _                 | —                | _                |  |

| 23:16        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |  |

|              |                   | _                 |                   | _                 |                   |                   | —                |                  |  |

| 15:8         | R/W-0             | R/W-0             | U-0               | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |

|              | HTEN              | MPEN              | _                 | NOTPM             | PMMODE<3:0>       |                   |                  |                  |  |

| 7:0          | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |

| 7.0          | CRCERREN          | CRCOKEN           | RUNTERREN         | RUNTEN            | UCEN              | NOTMEEN           | MCEN             | BCEN             |  |

#### Legend:

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read as '0' |                    |  |

|-------------------|------------------|------------------------------------|--------------------|--|

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared               | x = Bit is unknown |  |

## bit 31-16 Unimplemented: Read as '0'

- bit 15 **HTEN:** Enable Hash Table Filtering bit

- 1 = Enable Hash Table Filtering

- 0 = Disable Hash Table Filtering

- bit 14 **MPEN:** Magic Packet<sup>™</sup> Enable bit 1 = Enable Magic Packet Filtering 0 = Disable Magic Packet Filtering

- bit 13 Unimplemented: Read as '0'

- bit 12 **NOTPM:** Pattern Match Inversion bit

- 1 = The Pattern Match Checksum must not match for a successful Pattern Match to occur

- 0 = The Pattern Match Checksum must match for a successful Pattern Match to occur

This bit determines whether Pattern Match Checksum must match in order for a successful Pattern Match to occur.

- bit 11-8 PMMODE<3:0>: Pattern Match Mode bits

- 1001 = Pattern match is successful if (NOTPM = 1 XOR Pattern Match Checksum matches) AND (Packet = Magic Packet)<sup>(1,3)</sup>

- 1000 = Pattern match is successful if (NOTPM = 1 XOR Pattern Match Checksum matches) AND (Hash Table Filter match)<sup>(1,2)</sup>

- 0111 = Pattern match is successful if (NOTPM = 1 XOR Pattern Match Checksum matches) AND (Destination Address = Broadcast Address)<sup>(1)</sup>

- 0110 = Pattern match is successful if (NOTPM = 1 XOR Pattern Match Checksum matches) AND (Destination Address = Broadcast Address)<sup>(1)</sup>

- 0101 = Pattern match is successful if (NOTPM = 1 XOR Pattern Match Checksum matches) AND (Destination Address = Unicast Address)<sup>(1)</sup>

- 0100 = Pattern match is successful if (NOTPM = 1 XOR Pattern Match Checksum matches) AND (Destination Address = Unicast Address)<sup>(1)</sup>

- 0011 = Pattern match is successful if (NOTPM = 1 XOR Pattern Match Checksum matches) AND (Destination Address = Station Address)<sup>(1)</sup>

- 0010 = Pattern match is successful if (NOTPM = 1 XOR Pattern Match Checksum matches) AND (Destination Address = Station Address)<sup>(1)</sup>

- 0001 = Pattern match is successful if (NOTPM = 1 XOR Pattern Match Checksum matches)<sup>(1)</sup>

- 0000 = Pattern Match is disabled; pattern match is always unsuccessful

## **Note 1:** XOR = True when either one or the other conditions are true, but not both.

- 2: This Hash Table Filter match is active regardless of the value of the HTEN bit.

- 3: This Magic Packet Filter match is active regardless of the value of the MPEN bit.

**Note 1:** This register is only used for RX operations.

2: The bits in this register may only be changed while the RXEN bit (ETHCON1<8>) = 0.

# PIC32MX5XX/6XX/7XX

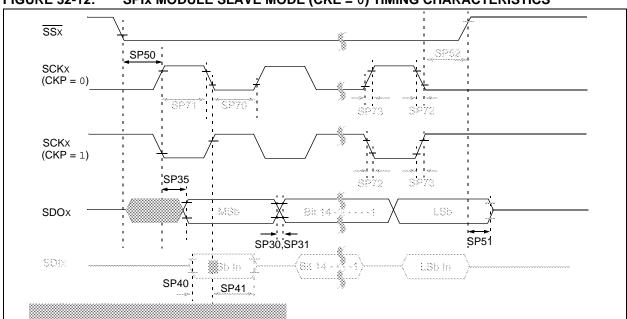

## FIGURE 32-12: SPIX MODULE SLAVE MODE (CKE = 0) TIMING CHARACTERISTICS

## TABLE 32-30: SPIX MODULE SLAVE MODE (CKE = 0) TIMING REQUIREMENTS

| AC CHARACTERISTICS |                       |                                                                     | $\begin{array}{l} \mbox{Standard Operating Conditions: 2.3V to 3.6V} \\ \mbox{(unless otherwise stated)} \\ \mbox{Operating temperature} & -40^{\circ}C \leq TA \leq +85^{\circ}C \mbox{ for Industrial} \\ -40^{\circ}C \leq TA \leq +105^{\circ}C \mbox{ for V-Temp} \end{array}$ |                     |      |       |                    |

|--------------------|-----------------------|---------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------|------|-------|--------------------|

| Param.<br>No.      | Symbol                | Characteristics <sup>(1)</sup>                                      | Min.                                                                                                                                                                                                                                                                                | Тур. <sup>(2)</sup> | Max. | Units | Conditions         |

| SP70               | TscL                  | SCKx Input Low Time <sup>(3)</sup>                                  | Тѕск/2                                                                                                                                                                                                                                                                              | _                   |      | ns    | —                  |

| SP71               | TscH                  | SCKx Input High Time <sup>(3)</sup>                                 | Tsck/2                                                                                                                                                                                                                                                                              | _                   |      | ns    | —                  |

| SP72               | TscF                  | SCKx Input Fall Time                                                | —                                                                                                                                                                                                                                                                                   | —                   | _    | ns    | See parameter DO32 |

| SP73               | TscR                  | SCKx Input Rise Time                                                | —                                                                                                                                                                                                                                                                                   | —                   | _    | ns    | See parameter DO31 |

| SP30               | TDOF                  | SDOx Data Output Fall Time <sup>(4)</sup>                           | —                                                                                                                                                                                                                                                                                   | _                   | _    | ns    | See parameter DO32 |

| SP31               | TdoR                  | SDOx Data Output Rise Time <sup>(4)</sup>                           | —                                                                                                                                                                                                                                                                                   | _                   | _    | ns    | See parameter DO31 |

| SP35               | TscH2doV,             | SDOx Data Output Valid after                                        | —                                                                                                                                                                                                                                                                                   | —                   | 15   | ns    | VDD > 2.7V         |