Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFl

| Product Status             | Active                                                                            |

|----------------------------|-----------------------------------------------------------------------------------|

| Core Processor             | MIPS32® M4K™                                                                      |

| Core Size                  | 32-Bit Single-Core                                                                |

| Speed                      | 80MHz                                                                             |

| Connectivity               | CANbus, Ethernet, I <sup>2</sup> C, SPI, UART/USART, USB OTG                      |

| Peripherals                | Brown-out Detect/Reset, DMA, POR, PWM, WDT                                        |

| Number of I/O              | 53                                                                                |

| Program Memory Size        | 512KB (512K x 8)                                                                  |

| Program Memory Type        | FLASH                                                                             |

| EEPROM Size                | -                                                                                 |

| RAM Size                   | 64K x 8                                                                           |

| Voltage - Supply (Vcc/Vdd) | 2.3V ~ 3.6V                                                                       |

| Data Converters            | A/D 16x10b                                                                        |

| Oscillator Type            | Internal                                                                          |

| Operating Temperature      | -40°C ~ 105°C (TA)                                                                |

| Mounting Type              | Surface Mount                                                                     |

| Package / Case             | 64-VFQFN Exposed Pad                                                              |

| Supplier Device Package    | 64-VQFN (9x9)                                                                     |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic32mx775f512ht-80v-mr |

|                            |                                                                                   |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

#### TABLE 6:PIN NAMES FOR 64-PIN USB, ETHERNET, AND CAN DEVICES

# 64-PIN QFN<sup>(3)</sup> AND TQFP (TOP VIEW)

# PIC32MX764F128H PIC32MX775F256H PIC32MX775F512H PIC32MX795F512H

|       | 64 1                                                      |                    |                                               |  |  |  |  |  |  |  |  |

|-------|-----------------------------------------------------------|--------------------|-----------------------------------------------|--|--|--|--|--|--|--|--|

|       |                                                           | QFN <sup>(3)</sup> | 64<br>TQFP                                    |  |  |  |  |  |  |  |  |

| Pin # | Full Pin Name                                             | Pin #              | Full Pin Name                                 |  |  |  |  |  |  |  |  |

| 1     | ETXEN/PMD5/RE5                                            | 33                 | USBID/RF3                                     |  |  |  |  |  |  |  |  |

| 2     | ETXD0/PMD6/RE6                                            | 34                 | VBUS                                          |  |  |  |  |  |  |  |  |

| 3     | ETXD1/PMD7/RE7                                            | 35                 | VUSB3V3                                       |  |  |  |  |  |  |  |  |

| 4     | SCK2/U6TX/U3RTS/PMA5/CN8/RG6                              | 36                 | D-/RG3                                        |  |  |  |  |  |  |  |  |

| 5     | SDA4/SDI2/U3RX/PMA4/CN9/RG7                               | 37                 | D+/RG2                                        |  |  |  |  |  |  |  |  |

| 6     | SCL4/SDO2/U3TX/PMA3/CN10/RG8                              | 38                 | Vdd                                           |  |  |  |  |  |  |  |  |

| 7     | MCLR                                                      | 39                 | OSC1/CLKI/RC12                                |  |  |  |  |  |  |  |  |

| 8     | SS2/U6RX/U3CTS/PMA2/CN11/RG9                              | 40                 | OSC2/CLKO/RC15                                |  |  |  |  |  |  |  |  |

| 9     | Vss                                                       | 41                 | Vss                                           |  |  |  |  |  |  |  |  |

| 10    | Vdd                                                       | 42                 | RTCC/AERXD1/ETXD3/IC1/INT1/RD8                |  |  |  |  |  |  |  |  |

| 11    | AN5/C1IN+/VBUSON/CN7/RB5                                  | 43                 | AERXD0/ETXD2/SS3/U4RX/U1CTS/SDA1/IC2/INT2/RD9 |  |  |  |  |  |  |  |  |

| 12    | AN4/C1IN-/CN6/RB4                                         | 44                 | ECOL/AECRSDV/SCL1/IC3/PMCS2/PMA15/INT3/RD10   |  |  |  |  |  |  |  |  |

| 13    | AN3/C2IN+/CN5/RB3                                         | 45                 | ECRS/AEREFCLK/IC4/PMCS1/PMA14/INT4/RD11       |  |  |  |  |  |  |  |  |

| 14    | AN2/C2IN-/CN4/RB2                                         | 46                 | OC1/INT0/RD0                                  |  |  |  |  |  |  |  |  |

| 15    | PGEC1/AN1/VREF-/CVREF-/CN3/RB1                            | 47                 | SOSCI/CN1/RC13                                |  |  |  |  |  |  |  |  |

| 16    | PGED1/AN0/VREF+/CVREF+/PMA6/CN2/RB0                       | 48                 | SOSCO/T1CK/CN0/RC14                           |  |  |  |  |  |  |  |  |

| 17    | PGEC2/AN6/OCFA/RB6                                        | 49                 | EMDIO/AEMDIO/SCK3/U4TX/U1RTS/OC2/RD1          |  |  |  |  |  |  |  |  |

| 18    | PGED2/AN7/RB7                                             | 50                 | SDA3/SDI3/U1RX/OC3/RD2                        |  |  |  |  |  |  |  |  |

| 19    | AVdd                                                      | 51                 | SCL3/SDO3/U1TX/OC4/RD3                        |  |  |  |  |  |  |  |  |

| 20    | AVss                                                      | 52                 | OC5/IC5/PMWR/CN13/RD4                         |  |  |  |  |  |  |  |  |

| 21    | AN8/C2TX <sup>(2)</sup> /SS4/U5RX/U2CTS/C1OUT/RB8         | 53                 | PMRD/CN14/RD5                                 |  |  |  |  |  |  |  |  |

| 22    | AN9/C2OUT/PMA7/RB9                                        | 54                 | AETXEN/ETXERR/CN15/RD6                        |  |  |  |  |  |  |  |  |

| 23    | TMS/AN10/CVREFOUT/PMA13/RB10                              | 55                 | ETXCLK/AERXERR/CN16/RD7                       |  |  |  |  |  |  |  |  |

| 24    | TDO/AN11/PMA12/RB11                                       | 56                 | VCAP                                          |  |  |  |  |  |  |  |  |

| 25    | Vss                                                       | 57                 | VDD                                           |  |  |  |  |  |  |  |  |

| 26    | Vdd                                                       | 58                 | C1RX/AETXD1/ERXD3/RF0                         |  |  |  |  |  |  |  |  |

| 27    | TCK/AN12/PMA11/RB12                                       | 59                 | C1TX/AETXD0/ERXD2/RF1                         |  |  |  |  |  |  |  |  |

| 28    | TDI/AN13/PMA10/RB13                                       | 60                 | ERXD1/PMD0/RE0                                |  |  |  |  |  |  |  |  |

| 29    | AN14/C2RX <sup>(2)</sup> /SCK4/U5TX/U2RTS/PMALH/PMA1/RB14 | 61                 | ERXD0/PMD1/RE1                                |  |  |  |  |  |  |  |  |

| 30    | AN15/EMDC/AEMDC/OCFB/PMALL/PMA0/CN12/RB15                 | 62                 | ERXDV/ECRSDV/PMD2/RE2                         |  |  |  |  |  |  |  |  |

| 31    | AC1TX/SDA5/SDI4/U2RX/PMA9/CN17/RF4                        | 63                 | ERXCLK/EREFCLKPMD3/RE3                        |  |  |  |  |  |  |  |  |

| 32    | AC1RX/SCL5/SDO4/U2TX/PMA8/CN18/RF5                        | 64                 | ERXERR/PMD4/RE4                               |  |  |  |  |  |  |  |  |

| Note  | 1: Shaded pins are 5V tolerant.                           |                    |                                               |  |  |  |  |  |  |  |  |

Note 1: Shaded pins are 5V tolerant.

2: This pin is not available on PIC32MX765F128H devices.

3: The metal plane at the bottom of the QFN device is not connected to any pins and is recommended to be connected to Vss externally.

#### PIN NAMES FOR 124-PIN USB, ETHERNET, AND CAN DEVICES **TABLE 13:**

| 12                | 4-PIN VTLA (BOTTOM VIEW) <sup>(2,3)</sup>                   |     |                   | A34                             |

|-------------------|-------------------------------------------------------------|-----|-------------------|---------------------------------|

|                   | AI7                                                         | B13 | B29               | Conductive<br>Thermal Pad       |

|                   | PIC32MX675F512L<br>PIC32MX695F512L<br>PIC32MX795F512L       | B1  | B56               | B41<br>A51                      |

|                   | A1                                                          |     |                   |                                 |

|                   | Polarity Indicator                                          |     | A68               |                                 |

| Package<br>Bump # | Full Pin Name                                               |     | Package<br>Bump # | Full Pin Name                   |

| A1                | No Connect (NC)                                             |     | A38               | D-/RG3                          |

| A2                | AERXERR/RG15                                                |     | A39               | SCL2/RA2                        |

| A3                | Vss                                                         |     | A40               | TDI/RA4                         |

| A4                | PMD6/RE6                                                    |     | A41               | Vdd                             |

| A5                | T2CK/RC1                                                    |     | A42               | OSC2/CLKO/RC15                  |

| A6                | T4CK/AC2RX <sup>(1)</sup> /RC3                              |     | A43               | Vss                             |

| A7                | ECOL/SCK2/U6TX/U3RTS/PMA5/CN8/RG6                           |     | A44               | AETXEN/SDA1/INT4/RA15           |

| A8                | ERXDV/AERXDV/ECRSDV/AECRSDV/SCL4/SDO2/U3TX/PMA3/CN10/RG8    |     | A45               | SS1/IC2/RD9                     |

| A9                | ERXCLK/AERXCLK/EREFCLK/AEREFCLK/SS2/U6RX/U3CTS/PMA2/CN11/R0 | G9  | A46               | EMDC/AEMDC/IC4/PMCS1/PMA14/RD1  |

| A10               | Vdd                                                         |     | A47               | SOSCI/CN1/RC13                  |

| A11               | AERXD0/INT1/RE8                                             |     | A48               | Vdd                             |

| A12               | AN5/C1IN+/VBUSON/CN7/RB5                                    |     | A49               | No Connect (NC)                 |

| A13               | AN3/C2IN+/CN5/RB3                                           |     | A50               | No Connect (NC)                 |

| A14               | Vdd                                                         |     | A51               | No Connect (NC)                 |

| A15               | PGEC1/AN1/CN3/RB1                                           |     | A52               | OC2/RD1                         |

| A16               | No Connect (NC)                                             |     | A53               | OC4/RD3                         |

| A17               | No Connect (NC)                                             |     | A54               | ETXD3/PMD13/CN19/RD13           |

| A18               | No Connect (NC)                                             |     | A55               | PMRD/CN14/RD5                   |

| A19               | No Connect (NC)                                             |     | A56               | ETXCLK/PMD15/CN16/RD7           |

| A20               | PGEC2/AN6/OCFA/RB6                                          |     | A57               | No Connect (NC)                 |

| A21               | VREF-/CVREF-/AERXD2/PMA7/RA9                                |     | A58               | No Connect (NC)                 |

| A22               | AVDD                                                        |     | A59               | Vdd                             |

| A23               | AN8/C1OUT/RB8                                               |     | A60               | C1TX/ETXD0/PMD10/RF1            |

| A24               | AN10/CVREFOUT/PMA13/RB10                                    |     | A61               | C2RX <sup>(1)</sup> /PMD8/RG0   |

| A25               | Vss                                                         |     | A62               | TRD3/RA7                        |

| A26               | TCK/RA1                                                     |     | A63               | Vss                             |

| A27               | AC1RX <sup>(1)</sup> /SS4/U5RX/U2CTS/RF12                   |     | A64               | PMD1/RE1                        |

| A28               | AN13/ERXD1/AECOL/PMA10/RB13                                 |     | A65               | TRD1/RG12                       |

| A29               | AN15/ERXD3/AETXD2/OCFB/PMALL/PMA0/CN12/RB15                 |     | A66               | PMD2/RE2                        |

| A30               | VDD                                                         |     | A67               | PMD4/RE4                        |

| A31               | AETXD1/SCK3/U4TX/U1RTS/CN21/RD15                            |     | A68               | No Connect (NC)                 |

| A32               | SCL5/SDO4/U2TX/PMA8/CN18/RF5                                |     | B1                | Vdd                             |

| A33               | No Connect (NC)                                             |     | B2                | PMD5/RE5                        |

| A34               | No Connect (NC)                                             |     | B3                | PMD7/RE7                        |

| A35               | USBID/RF3                                                   |     | B4                | T3CK/AC2TX <sup>(1)</sup> /RC2  |

| A36               | SDA3/SDI3/U1RX/RF2                                          |     | B5                | T5CK/SDI1/RC4                   |

| A37               | VBUS                                                        |     | B6                | ECRS/SDA4/SDI2/U3RX/PMA4/CN9/RG |

| B7                | MCLR                                                        |     | B32               | SDA2/RA3                        |

1: 2:

This pin is only available on PIC32MX795F512L devices. Shaded package bumps are 5V tolerant. It is recommended that the user connect the printed circuit board (PCB) ground to the conductive thermal pad on the bottom of the package. And to not run non-Vss PCB traces under the conductive thermal pad on the same side of the PCB layout. 3:

# PIC32MX5XX/6XX/7XX

Coprocessor 0 also contains the logic for identifying and managing exceptions. Exceptions can be caused by a variety of sources, including alignment errors in data, external events or program errors. Table 3-3 lists the exception types in order of priority.

# TABLE 3-3: PIC32MX5XX/6XX/7XX FAMILY CORE EXCEPTION TYPES

| Exception | Description                                                                                                                             |

|-----------|-----------------------------------------------------------------------------------------------------------------------------------------|

| Reset     | Assertion MCLR or a Power-on Reset (POR).                                                                                               |

| DSS       | EJTAG debug single step.                                                                                                                |

| DINT      | EJTAG debug interrupt. Caused by the assertion of the external <i>EJ_DINT</i> input or by setting the EjtagBrk bit in the ECR register. |

| NMI       | Assertion of NMI signal.                                                                                                                |

| Interrupt | Assertion of unmasked hardware or software interrupt signal.                                                                            |

| DIB       | EJTAG debug hardware instruction break matched.                                                                                         |

| AdEL      | Fetch address alignment error.<br>Fetch reference to protected address.                                                                 |

| IBE       | Instruction fetch bus error.                                                                                                            |

| DBp       | EJTAG breakpoint (execution of SDBBP instruction).                                                                                      |

| Sys       | Execution of SYSCALL instruction.                                                                                                       |

| Вр        | Execution of BREAK instruction.                                                                                                         |

| RI        | Execution of a reserved instruction.                                                                                                    |

| CpU       | Execution of a coprocessor instruction for a coprocessor that is not enabled.                                                           |

| CEU       | Execution of a CorExtend instruction when CorExtend is not enabled.                                                                     |

| Ov        | Execution of an arithmetic instruction that overflowed.                                                                                 |

| Tr        | Execution of a trap (when trap condition is true).                                                                                      |

| DDBL/DDBS | EJTAG Data Address Break (address only) or EJTAG data value break on store (address + value).                                           |

| AdEL      | Load address alignment error.<br>Load reference to protected address.                                                                   |

| AdES      | Store address alignment error.<br>Store to protected address.                                                                           |

| DBE       | Load or store bus error.                                                                                                                |

| DDBL      | EJTAG data hardware breakpoint matched in load data compare.                                                                            |

# 11.0 USB ON-THE-GO (OTG)

Note: This data sheet summarizes the features of the PIC32MX5XX/6XX/7XX family of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to Section 27. "USB On-The-Go (OTG)" (DS60001126) in the "PIC32 Family Reference Manual", which is available from the Microchip web site (www.microchip.com/PIC32).

The Universal Serial Bus (USB) module contains analog and digital components to provide a USB 2.0 full-speed and low-speed embedded Host, full-speed Device or OTG implementation with a minimum of external components. This module in Host mode is intended for use as an embedded host and therefore does not implement a UHCI or OHCI controller.

The USB module consists of the clock generator, the USB voltage comparators, the transceiver, the Serial Interface Engine (SIE), a dedicated USB DMA controller, pull-up and pull-down resistors, and the register interface. A block diagram of the PIC32 USB OTG module is presented in Figure 11-1.

The clock generator provides the 48 MHz clock required for USB full-speed and low-speed communication. The voltage comparators monitor the voltage on the VBUS pin to determine the state of the bus. The transceiver provides the analog translation between the USB bus and the digital logic. The SIE is a state machine that transfers data to and from the endpoint buffers and generates the hardware protocol for data transfers. The USB DMA controller transfers data between the data buffers in RAM and the SIE. The integrated pull-up and pull-down resistors eliminate the need for external signaling components. The register interface allows the CPU to configure and communicate with the module.

The USB module includes the following features:

- USB Full-speed support for host and device

- Low-speed host support

- USB OTG support

- Integrated signaling resistors

- Integrated analog comparators for VBUS monitoring

- Integrated USB transceiver

- Transaction handshaking performed by hardware

- Endpoint buffering anywhere in system RAM

- Integrated DMA to access system RAM and Flash

- The implementation and use of the USB Note: specifications, as well as other third party may specifications or technologies, require licensing; including, but not limited to, USB Implementers Forum, Inc. (also referred to as USB-IF). The user is fully responsible for investigating and satisfying any applicable licensing obligations.

#### 12.2 Control Registers

# TABLE 12-1: PORTA REGISTER MAP FOR PIC32MX534F064L, PIC32MX564F064L, PIC32MX564F128L, PIC32MX575F512L, PIC32MX664F064L, PIC32MX664F128L, PIC32MX675F512L, PIC32MX695F512L, PIC32MX695F512L, PIC32MX764F128L, PIC32MX775F512L, PIC32MX775F512L, PIC32MX775F512L, PIC32MX775F512L, PIC32MX795F512L, PIC32MX764F128L, PIC32MX775F512L, PIC32MX775F512L, PIC32MX795F512L, PIC32MX795F512L, PIC32MX775F512L, PIC32MX795F512L, PIC32MX79F5F512L, PIC32MX79FF512L, PIC32MX79FF512MX79FF512L, PIC32MX79FF512MX79FF512MX79FF512L, PIC32

| ess                        |                                 |           |         |         |       |       |       |         |        | Bi   | ts     |        |        |        |        |        |        |        | 6          |

|----------------------------|---------------------------------|-----------|---------|---------|-------|-------|-------|---------|--------|------|--------|--------|--------|--------|--------|--------|--------|--------|------------|

| Virtual Addres<br>(BF88_#) | Register<br>Name <sup>(1)</sup> | Bit Range | 31/15   | 30/14   | 29/13 | 28/12 | 27/11 | 26/10   | 25/9   | 24/8 | 23/7   | 22/6   | 21/5   | 20/4   | 19/3   | 18/2   | 17/1   | 16/0   | All Resets |

| 6000                       | TRISA                           | 31:16     |         | —       |       | _     | —     | —       | _      | _    |        | —      |        | _      |        | —      | —      | —      | 0000       |

| 6000                       | IRISA                           | 15:0      | TRISA15 | TRISA14 |       | _     |       | TRISA10 | TRISA9 | _    | TRISA7 | TRISA6 | TRISA5 | TRISA4 | TRISA3 | TRISA2 | TRISA1 | TRISA0 | C6FF       |

| 6010                       | PORTA                           | 31:16     |         | _       |       | _     |       | _       | _      | _    |        | _      |        | _      |        | _      | _      | _      | 0000       |

| 0010                       | FURIA                           | 15:0      | RA15    | RA14    |       | -     |       | RA10    | RA9    | _    | RA7    | RA6    | RA5    | RA4    | RA3    | RA2    | RA1    | RA0    | xxxx       |

| 6020                       | LATA                            | 31:16     | -       | _       | -     | —     | _     | _       |        |      | -      | —      | -      |        | -      | —      | —      | —      | 0000       |

| 0020                       | LAIA                            | 15:0      | LATA15  | LATA14  | -     | —     | _     | LATA10  | LATA9  |      | LATA7  | LATA6  | LATA5  | LATA4  | LATA3  | LATA2  | LATA1  | LATA0  | xxxx       |

| 6030                       | ODCA                            | 31:16     |         | _       |       | -     |       | —       | _      | _    |        | _      |        | _      | _      | _      | -      | -      | 0000       |

| 6030                       | UDCA                            | 15:0      | ODCA15  | ODCA14  | _     | _     | —     | ODCA10  | ODCA9  | _    | ODCA7  | ODCA6  | ODCA5  | ODCA4  | ODCA3  | ODCA2  | ODCA1  | ODCA0  | 0000       |

Legend: x = unknown value on Reset; — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

Note 1: All registers in this table have corresponding CLR, SET and INV registers at their virtual addresses, plus offsets of 0x4, 0x8 and 0xC, respectively. See Section 12.1.1 "CLR, SET and INV Registers" for more information.

#### TABLE 12-2:PORTB REGISTER MAP

|                           |                                 |           | -       |         |         |         |         |         |        |        |        |        |        |        |        |        |        |        |            |

|---------------------------|---------------------------------|-----------|---------|---------|---------|---------|---------|---------|--------|--------|--------|--------|--------|--------|--------|--------|--------|--------|------------|

| ess                       |                                 |           |         |         |         |         |         |         |        | Bi     | its    |        |        |        |        |        |        |        |            |

| Virtual Addre<br>(BF88_#) | Register<br>Name <sup>(1)</sup> | Bit Range | 31/15   | 30/14   | 29/13   | 28/12   | 27/11   | 26/10   | 25/9   | 24/8   | 23/7   | 22/6   | 21/5   | 20/4   | 19/3   | 18/2   | 17/1   | 16/0   | All Resets |

| 00.40                     | TRIOR                           | 31:16     |         |         | _       | _       | _       | _       | _      | _      | _      | _      | _      | _      | _      | _      | _      | _      | 0000       |

| 6040                      | TRISB                           | 15:0      | TRISB15 | TRISB14 | TRISB13 | TRISB12 | TRISB11 | TRISB10 | TRISB9 | TRISB8 | TRISB7 | TRISB6 | TRISB5 | TRISB4 | TRISB3 | TRISB2 | TRISB1 | TRISB0 | FFFF       |

| COEO                      | PORTB                           | 31:16     | _       | _       | _       | _       | _       | -       | _      | _      | _      | _      | _      | _      | _      | _      | _      | _      | 0000       |

| 6050                      | PURID                           | 15:0      | RB15    | RB14    | RB13    | RB12    | RB11    | RB10    | RB9    | RB8    | RB7    | RB6    | RB5    | RB4    | RB3    | RB2    | RB1    | RB0    | xxxx       |

| 6060                      | LATB                            | 31:16     | _       | —       | _       | _       | _       | _       | _      | _      | _      | _      | —      | _      | _      | _      | _      | _      | 0000       |

| 6060                      | LAID                            | 15:0      | LATB15  | LATB14  | LATB13  | LATB12  | LATB11  | LATB10  | LATB9  | LATB8  | LATB7  | LATB6  | LATB5  | LATB4  | LATB3  | LATB2  | LATB1  | LATB0  | xxxx       |

| 6070                      | ODCB                            | 31:16     | _       |         | —       | —       | —       | —       | —      | _      | —      | —      | —      | —      | —      | _      | —      | —      | 0000       |

| 6070                      | ODCB                            | 15:0      | ODCB15  | ODCB14  | ODCB13  | ODCB12  | ODCB11  | ODCB10  | ODCB9  | ODCB8  | ODCB7  | ODCB6  | ODCB5  | ODCB4  | ODCB3  | ODCB2  | ODCB1  | ODCB0  | 0000       |

Legend: x = unknown value on Reset; - = unimplemented, read as '0'. Reset values are shown in hexadecimal.

Note 1: All registers in this table have corresponding CLR, SET and INV registers at their virtual addresses, plus offsets of 0x4, 0x8 and 0xC, respectively. See Section 12.1.1 "CLR, SET and INV Registers" for more information.

# REGISTER 16-1: ICxCON: INPUT CAPTURE 'x' CONTROL REGISTER (CONTINUED)

- bit 2-0 ICM<2:0>: Input Capture Mode Select bits

- 111 = Interrupt-Only mode (only supported while in Sleep mode or Idle mode)

- 110 = Simple Capture Event mode every edge, specified edge first and every edge thereafter

- 101 = Prescaled Capture Event mode every sixteenth rising edge

- 100 = Prescaled Capture Event mode every fourth rising edge

- 011 = Simple Capture Event mode every rising edge

- 010 = Simple Capture Event mode every falling edge

- 001 = Edge Detect mode every edge (rising and falling)

- 000 = Input Capture module is disabled

- **Note 1:** When using the 1:1 PBCLK divisor, the user's software should not read/write the peripheral's SFRs in the SYSCLK cycle immediately following the instruction that clears the module's ON bit.

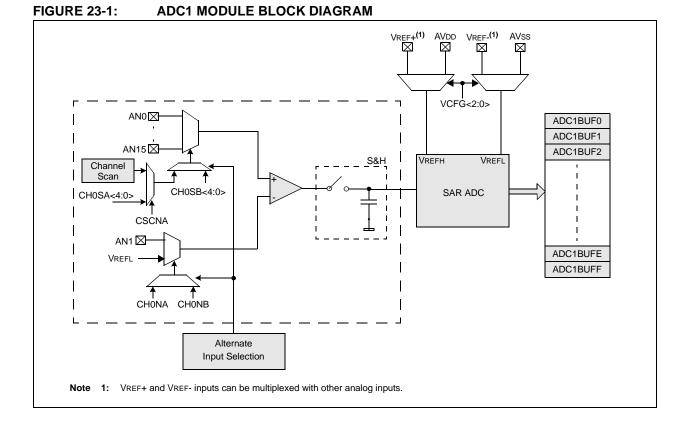

# 23.0 10-BIT ANALOG-TO-DIGITAL CONVERTER (ADC)

Note: This data sheet summarizes the features of the PIC32MX5XX/6XX/7XX family of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to Section 17. "10-bit Analog-to-Digital Converter (ADC)" (DS60001104) in the "PIC32 Family Reference Manual", which is available from Microchip web the site (www.microchip.com/PIC32).

The PIC32MX5XX/6XX/7XX 10-bit Analog-to-Digital Converter (ADC) includes the following features:

- Successive Approximation Register (SAR) conversion

- Up to 1 Msps conversion speed

- Up to 16 analog input pins

- External voltage reference input pins

- One unipolar, differential Sample and Hold (S&H) circuit

- Automatic Channel Scan mode

- Selectable conversion trigger source

- 16-word conversion result buffer

- · Selectable buffer fill modes

- Eight conversion result format options

- · Operation during Sleep and Idle modes

A block diagram of the 10-bit ADC is illustrated in Figure 23-1. The 10-bit ADC has up to 16 analog input pins, designated AN0-AN15. In addition, there are two analog input pins for external voltage reference connections. These voltage reference inputs may be shared with other analog input pins and may be common to other analog module references.

The analog inputs are connected through two multiplexers to one S&H. The analog input multiplexers can be switched between two sets of analog inputs between conversions. Unipolar differential conversions are possible on all channels, other than the pin used as the reference, using a reference input pin (see Figure 23-1).

The Analog Input Scan mode sequentially converts user-specified channels. A control register specifies which analog input channels will be included in the scanning sequence.

The 10-bit ADC is connected to a 16-word result buffer. Each 10-bit result is converted to one of eight 32-bit output formats when it is read from the result buffer.

| REGISTER 23-2: AD1CON2: ADC CONTROL REGISTER 2 |

|------------------------------------------------|

|------------------------------------------------|

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |  |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|--|--|

| 24.24        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |  |  |

| 31:24        | —                 | —                 | —                 | —                 | —                 | —                 | —                | —                |  |  |

| 00.40        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |  |  |

| 23:16        |                   |                   | —                 | _                 | —                 | —                 | —                | —                |  |  |

| 45.0         | R/W-0             | R/W-0             | R/W-0             | R/W-0             | U-0               | R/W-0             | U-0              | U-0              |  |  |

| 15:8         |                   | VCFG<2:0>         |                   | OFFCAL            | —                 | CSCNA             | —                | —                |  |  |

| 7.0          | R-0               | U-0               | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |

| 7:0          | BUFS              | _                 |                   | SMP               | l<3:0>            | BUFM              | ALTS             |                  |  |  |

#### Legend:

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, re | ad as '0'          |

|-------------------|------------------|---------------------------|--------------------|

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared      | x = Bit is unknown |

#### bit 31-16 Unimplemented: Read as '0'

bit 15-13 VCFG<2:0>: Voltage Reference Configuration bits

| Bit Value | VREFH              | VREFL              |  |  |

|-----------|--------------------|--------------------|--|--|

| lxx       | AVdd               | AVss               |  |  |

| 011       | External VREF+ pin | External VREF- pin |  |  |

| 010       | AVdd               | External VREF- pin |  |  |

| 001       | External VREF+ pin | AVss               |  |  |

| 000       | AVDD               | AVss               |  |  |

#### bit 12 **OFFCAL:** Input Offset Calibration Mode Select bit

1 = Enable Offset Calibration mode

Positive and negative inputs of the S&H circuit are connected to VREFL.

- 0 = Disable Offset Calibration mode

- The inputs to the S&H circuit are controlled by AD1CHS or AD1CSSL.

# bit 11 Unimplemented: Read as '0'

- bit 10 CSCNA: Input Scan Select bit

- 1 = Scan inputs

- 0 = Do not scan inputs

- bit 9-8 Unimplemented: Read as '0'

- bit 7 BUFS: Buffer Fill Status bit

- Only valid when BUFM = 1.

- 1 = ADC is currently filling buffer 0x8-0xF, user should access data in 0x0-0x7

- 0 = ADC is currently filling buffer 0x0-0x7, user should access data in 0x8-0xF

# bit 6 Unimplemented: Read as '0'

# bit 5-2 SMPI<3:0>: Sample/Convert Sequences Per Interrupt Selection bits

- 1111 = Interrupts at the completion of conversion for each 16<sup>th</sup> sample/convert sequence 1110 = Interrupts at the completion of conversion for each 15<sup>th</sup> sample/convert sequence

- $\pm\pm\pm\pm$  = interrupts at the completion of conversion for each 15"' sample/convert sequence

- •

- 0001 = Interrupts at the completion of conversion for each  $2^{nd}$  sample/convert sequence 0000 = Interrupts at the completion of conversion for each sample/convert sequence

- bit 1 BUFM: ADC Result Buffer Mode Select bit

- 1 = Buffer configured as two 8-word buffers, ADC1BUF7-ADC1BUF0, ADC1BUFF-ADCBUF8

- 0 = Buffer configured as one 16-word buffer ADC1BUFF-ADC1BUF0

- bit 0 ALTS: Alternate Input Sample Mode Select bit

- 1 = Uses Sample A input multiplexer settings for first sample, and then alternates between Sample B and Sample A input multiplexer settings for all subsequent samples

- 0 = Always use Sample A input multiplexer settings

# REGISTER 24-1: CICON: CAN MODULE CONTROL REGISTER (CONTINUED)

bit 13 **SIDLE:** CAN Stop in Idle bit 1 = CAN Stops operation when system enters Idle mode 0 = CAN continues operation when system enters Idle mode

# bit 12 Unimplemented: Read as '0'

- bit 11 CANBUSY: CAN Module is Busy bit

- 1 = The CAN module is active

- 0 = The CAN module is completely disabled

- bit 10-5 Unimplemented: Read as '0'

### bit 4-0 **DNCNT<4:0>:** Device Net Filter Bit Number bits

10011-11111 = Invalid Selection (compare up to 18-bits of data with EID)

- 10010 = Compare up to data byte 2 bit 6 with EID17 (CiRXFn<17>)

- •

- •

- •

00001 = Compare up to data byte 0 bit 7 with EID0 (CiRXFn<0>) 00000 = Do not compare data bytes

**Note 1:** If the user application clears this bit, it may take a number of cycles before the CAN module completes the current transaction and responds to this request. The user application should poll the CANBUSY bit to verify that the request has been honored.

# REGISTER 24-2: CiCFG: CAN BAUD RATE CONFIGURATION REGISTER (CONTINUED)

```

bit 10-8 PRSEG<2:0>: Propagation Time Segment bits<sup>(4)</sup>

111 = \text{Length is 8 x Tq}

000 = \text{Length is 1 x Tq}

SJW<1:0>: Synchronization Jump Width bits<sup>(3)</sup>

bit 7-6

11 = \text{Length is } 4 \times \text{Tq}

10 = Length is 3 x TQ

01 = Length is 2 x TQ

00 = \text{Length is } 1 \times TQ

BRP<5:0>: Baud Rate Prescaler bits

bit 5-0

111111 = TQ = (2 x 64)/FSYS

111110 = TQ = (2 x 63)/FSYS

000001 = TQ = (2 \times 2)/FSYS

000000 = TQ = (2 \times 1)/FSYS

Note 1: SEG2PH \leq SEG1PH. If SEG2PHTS is clear, SEG2PH will be set automatically.

2: 3 Time bit sampling is not allowed for BRP < 2.

```

- $\textbf{3:} \quad SJW \leq SEG2PH.$

- **4:** The Time Quanta per bit must be greater than 7 (that is, TQBIT > 7).

Note: This register can only be modified when the CAN module is in Configuration mode (OPMOD<2:0> (CiCON<23:21>) = 100).

# PIC32MX5XX/6XX/7XX

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3       | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------------|-------------------|------------------|------------------|

| 24.24        | U-0               | U-0               | U-0               | U-0               | U-0                     | U-0               | U-0              | U-0              |

| 31:24        | _                 | _                 | _                 | —                 | —                       |                   | _                | —                |

| 23:16        | U-0               | U-0               | U-0               | U-0               | U-0                     | U-0               | U-0              | U-0              |

| 23.10        | —                 | —                 | _                 | —                 | _                       | _                 | —                | —                |

| 15.0         | U-0               | U-0               | U-0               | R-0               | R-0                     | R-0               | R-0              | R-0              |

| 15:8         | —                 | —                 | _                 |                   |                         | FILHIT<4:0>       |                  |                  |

| 7.0          | U-0               | R-1               | R-0               | R-0               | R-0                     | R-0               | R-0              | R-0              |

| 7:0          | _                 |                   |                   | l                 | CODE<6:0> <sup>(1</sup> | )                 |                  |                  |

# REGISTER 24-4: CiVEC: CAN INTERRUPT CODE REGISTER

# Legend:

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, r | read as '0'        |

|-------------------|------------------|--------------------------|--------------------|

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared     | x = Bit is unknown |

# bit 31-13 Unimplemented: Read as '0'

| bit 12-8 | FILHIT<4:0>: Filter Hit Number bit                  |

|----------|-----------------------------------------------------|

|          | 11111 = Filter 31                                   |

|          | 11110 = Filter 30                                   |

|          | •                                                   |

|          | •                                                   |

|          | 00001 = Filter 1                                    |

|          | 00000 = Filter 0                                    |

| bit 7    | Unimplemented: Read as '0'                          |

| bit 6-0  | ICODE<6:0>: Interrupt Flag Code bits <sup>(1)</sup> |

|          | 11111111 = Reserved                                 |

|          | •                                                   |

|          | •                                                   |

|          | •<br>1001001 = Reserved                             |

|          | 1001000 = Invalid message received (IVRIF)          |

|          | 1001111 = CAN module mode change (MODIF)            |

|          | 1000110 = CAN timestamp timer (CTMRIF)              |

|          | 1000101 = Bus bandwidth error (SERRIF)              |

|          | 1000100 = Address error interrupt (SERRIF)          |

|          | 1000011 = Receive FIFO overflow interrupt (RBOVIF)  |

|          | 1000010 = Wake-up interrupt (WAKIF)                 |

|          | 1000001 = Error Interrupt (CERRIF)                  |

|          | 1000000 = No interrupt                              |

|          | 0111111 = Reserved                                  |

|          | •                                                   |

|          | •                                                   |

|          | 0100000 = Reserved                                  |

|          | 0011111 = FIFO31 Interrupt (CiFSTAT<31> set)        |

|          | 0011110 = FIFO30 Interrupt (CiFSTAT<30> set)        |

|          | •                                                   |

|          | •                                                   |

|          | 0000001 = FIFO1 Interrupt (CiFSTAT<1> set)          |

|          | 0000000 = FIFO0 Interrupt (CiFSTAT<0> set)          |

|          |                                                     |

Note 1: These bits are only updated for enabled interrupts.

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|

| 31:24        | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |

| 31.24        | FLTEN7            | MSEL7<1:0>        |                   |                   | F                 | SEL7<4:0>         |                  |                  |

| 22:16        | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |

| 23:16        | FLTEN6            | MSEL6<1:0>        |                   | FSEL6<4:0>        |                   |                   |                  |                  |

| 15:8         | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |

| 10.0         | FLTEN5            | MSEL5<1:0>        |                   | FSEL5<4:0>        |                   |                   |                  |                  |

| 7.0          | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |

| 7:0          | FLTEN4            | MSEL4<1:0>        |                   | FSEL4<4:0>        |                   |                   |                  |                  |

# **REGISTER 24-11: CIFLTCON1: CAN FILTER CONTROL REGISTER 1**

#### Legend:

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, r | ead as '0'         |

|-------------------|------------------|--------------------------|--------------------|

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared     | x = Bit is unknown |

| bit 31    | FLTEN7: Filter 7 Enable bit                                 |

|-----------|-------------------------------------------------------------|

|           | 1 = Filter is enabled                                       |

|           | 0 = Filter is disabled                                      |

| bit 30-29 | MSEL7<1:0>: Filter 7 Mask Select bits                       |

|           | 11 = Acceptance Mask 3 selected                             |

|           | 10 = Acceptance Mask 2 selected                             |

|           | 01 = Acceptance Mask 1 selected                             |

|           | 00 = Acceptance Mask 0 selected                             |

| bit 28-24 | FSEL7<4:0>: FIFO Selection bits                             |

|           | 11111 = Message matching filter is stored in FIFO buffer 31 |

|           | 11110 = Message matching filter is stored in FIFO buffer 30 |

|           | •                                                           |

|           | •                                                           |

|           | 00001 = Message matching filter is stored in FIFO buffer 1  |

|           | 00000 = Message matching filter is stored in FIFO buffer 0  |

| bit 23    | FLTEN6: Filter 6 Enable bit                                 |

|           | 1 = Filter is enabled                                       |

|           | 0 = Filter is disabled                                      |

| bit 22-21 | MSEL6<1:0>: Filter 6 Mask Select bits                       |

|           | 11 = Acceptance Mask 3 selected                             |

|           | 10 = Acceptance Mask 2 selected                             |

|           | 01 = Acceptance Mask 1 selected                             |

|           | 00 = Acceptance Mask 0 selected                             |

| bit 20-16 | FSEL6<4:0>: FIFO Selection bits                             |

|           | 11111 = Message matching filter is stored in FIFO buffer 31 |

|           | 11110 - Massage matching filter is stored in EIEO buffer 30 |

uffer 31 11110 = Message matching filter is stored in FIFO buffer 30

•

•

00001 = Message matching filter is stored in FIFO buffer 1 00000 = Message matching filter is stored in FIFO buffer 0

Note: The bits in this register can only be modified if the corresponding filter enable (FLTENn) bit is '0'.

# PIC32MX5XX/6XX/7XX

| REGISTER 24-21: CiFIFOINTn: CAN FIFO INTERRUPT REGISTER 'n' (n = 0 THROUGH 31) |            |            |            |            |            |            |           |           |  |

|--------------------------------------------------------------------------------|------------|------------|------------|------------|------------|------------|-----------|-----------|--|

| Bit                                                                            | Bit        | Bit        | Bit        | Bit        | Bit        | Bit        | Bit       | Bit       |  |

| Range                                                                          | 31/23/15/7 | 30/22/14/6 | 29/21/13/5 | 28/20/12/4 | 27/19/11/3 | 26/18/10/2 | 25/17/9/1 | 24/16/8/0 |  |

| Range | 31/23/15/7 | 30/22/14/6 | 29/21/13/5 | 28/20/12/4 | 27/19/11/3 | 26/18/10/2               | 25/17/9/1               | 24/16/8/0                 |

|-------|------------|------------|------------|------------|------------|--------------------------|-------------------------|---------------------------|

| 24.24 | U-0        | U-0        | U-0        | U-0        | U-0        | R/W-0                    | R/W-0                   | R/W-0                     |

| 31:24 | —          | _          |            |            |            | TXNFULLIE                | TXHALFIE                | TXEMPTYIE                 |

| 00.40 | U-0        | U-0        | U-0        | U-0        | R/W-0      | R/W-0                    | R/W-0                   | R/W-0                     |

| 23:16 | —          | —          | —          | _          | RXOVFLIE   | RXFULLIE                 | RXHALFIE                | RXNEMPTYIE                |

| 15.0  | U-0        | U-0        | U-0        | U-0        | U-0        | R-0                      | R-0                     | R-0                       |

| 15:8  | —          | —          |            |            | _          | TXNFULLIF <sup>(1)</sup> | TXHALFIF                | TXEMPTYIF <sup>(1)</sup>  |

| 7.0   | U-0        | U-0        | U-0        | U-0        | R/W-0      | R-0                      | R-0                     | R-0                       |

| 7:0   | _          | _          | _          | _          | RXOVFLIF   | RXFULLIF <sup>(1)</sup>  | RXHALFIF <sup>(1)</sup> | RXNEMPTYIF <sup>(1)</sup> |

# Legend:

| R = Readable bit  | W = Writable bit | U = Unimplemented bit | t, read as '0'     |

|-------------------|------------------|-----------------------|--------------------|

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared  | x = Bit is unknown |

# bit 31-27 Unimplemented: Read as '0'

| bit 26    | <b>TXNFULLIE:</b> Transmit FIFO Not Full Interrupt Enable bit<br>1 = Interrupt enabled for FIFO not full<br>0 = Interrupt disabled for FIFO not full   |

|-----------|--------------------------------------------------------------------------------------------------------------------------------------------------------|

| bit 25    | <b>TXHALFIE:</b> Transmit FIFO Half Full Interrupt Enable bit<br>1 = Interrupt enabled for FIFO half full<br>0 = Interrupt disabled for FIFO half full |

| bit 24    | <b>TXEMPTYIE:</b> Transmit FIFO Empty Interrupt Enable bit<br>1 = Interrupt enabled for FIFO empty<br>0 = Interrupt disabled for FIFO empty            |

| bit 23-20 | Unimplemented: Read as '0'                                                                                                                             |

| bit 19    | RXOVFLIE: Overflow Interrupt Enable bit                                                                                                                |

|           | <ul><li>1 = Interrupt enabled for overflow event</li><li>0 = Interrupt disabled for overflow event</li></ul>                                           |

| bit 18    | RXFULLIE: Full Interrupt Enable bit                                                                                                                    |

|           | <ol> <li>1 = Interrupt enabled for FIFO full</li> <li>0 = Interrupt disabled for FIFO full</li> </ol>                                                  |

| bit 17    | RXHALFIE: FIFO Half Full Interrupt Enable bit                                                                                                          |

|           | <ul><li>1 = Interrupt enabled for FIFO half full</li><li>0 = Interrupt disabled for FIFO half full</li></ul>                                           |

| bit 16    | <b>RXNEMPTYIE:</b> Empty Interrupt Enable bit                                                                                                          |

|           | <ul><li>1 = Interrupt enabled for FIFO not empty</li><li>0 = Interrupt disabled for FIFO not empty</li></ul>                                           |

| bit 15-11 | Unimplemented: Read as '0'                                                                                                                             |

| bit 10    | TXNFULLIF: Transmit FIFO Not Full Interrupt Flag bit <sup>(1)</sup>                                                                                    |

|           | <u>TXEN = 1:</u> (FIFO configured as a transmit buffer)<br>1 = FIFO is not full<br>0 = FIFO is full                                                    |

|           | <u>TXEN = 0:</u> (FIFO configured as a receive buffer)<br>Unused, reads '0'                                                                            |

**Note 1:** This bit is read-only and reflects the status of the FIFO.

### REGISTER 25-18: ETHSCOLFRM: ETHERNET CONTROLLER SINGLE COLLISION FRAMES STATISTICS REGISTER

| Bit Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |

|-----------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|--|

| 31:24     | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |  |

| 31.24     | -                 | —                 | _                 | —                 | -                 | —                 | _                | —                |  |

| 00.40     | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |  |

| 23:16     | _                 | —                 | _                 | _                 | _                 | —                 | _                | —                |  |

| 15.0      | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |

| 15:8      | SCOLFRMCNT<15:8>  |                   |                   |                   |                   |                   |                  |                  |  |

| 7.0       | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |

| 7:0       | SCOLFRMCNT<7:0>   |                   |                   |                   |                   |                   |                  |                  |  |

# Legend:

| R = Readable bit W = Writable bit |                  | U = Unimplemented bit, read as '0' |                    |  |

|-----------------------------------|------------------|------------------------------------|--------------------|--|

| -n = Value at POR                 | '1' = Bit is set | '0' = Bit is cleared               | x = Bit is unknown |  |

#### bit 31-16 Unimplemented: Read as '0'

bit 15-0 **SCOLFRMCNT<15:0>:** Single Collision Frame Count bits Increment count for frames that were successfully transmitted on the second try.

Note 1: This register is only used for TX operations.

2: This register is automatically cleared by hardware after a read operation, unless the byte enables for bytes 0/1 are '0'.

**3:** It is recommended to use the SET, CLR, or INV registers to set or clear any bit in this register. Setting or clearing any bits in this register should only be done for debug/test purposes.

#### REGISTER 29-3: DEVCFG2: DEVICE CONFIGURATION WORD 2

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|

| 04.04        | r-1               | r-1               | r-1               | r-1               | r-1               | r-1               | r-1              | r-1              |

| 31:24        |                   | -                 |                   | —                 | _                 | _                 | _                | —                |

| 00.40        | r-1               | r-1               | r-1               | r-1               | r-1               | R/P               | R/P              | R/P              |

| 23:16        |                   | _                 |                   | —                 | —                 | FPLLODIV<2:0>     |                  |                  |

| 45.0         | R/P               | r-1               | r-1               | r-1               | r-1               | R/P               | R/P              | R/P              |

| 15:8         | UPLLEN            | _                 | _                 | _                 | _                 | UPLLIDIV<2:0>     |                  |                  |

| 7.0          | r-1               | R/P-1             | R/P               | R/P-1             | r-1               | R/P               | R/P              | R/P              |

| 7:0          |                   | FPLLMUL<2:0>      |                   |                   |                   | FPLLIDIV<2:0>     |                  |                  |

| Legend:           | r = Reserved bit |                                    |                    |

|-------------------|------------------|------------------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read as '0' |                    |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared               | x = Bit is unknown |

#### bit 31-19 Reserved: Write '1'

bit 18-16 **FPLLODIV<2:0>:** PLL Output Divider bits 111 = PLL output divided by 256

- 110 = PLL output divided by 64 101 = PLL output divided by 32 100 = PLL output divided by 16 011 = PLL output divided by 8 010 = PLL output divided by 4 001 = PLL output divided by 2

- 000 = PLL output divided by 1

- bit 15 UPLLEN: USB PLL Enable bit 1 = Disable and bypass USB PLL 0 = Enable USB PLL

- bit 14-11 Reserved: Write '1'

- bit 10-8 UPLLIDIV<2:0>: USB PLL Input Divider bits

- 111 = 12x divider

- 110 = 10x divider

- 101 = 6x divider

- 100 = 5x divider

- 011 = 4x divider

- 010 = 3x divider

- 001 = 2x divider 000 = 1x divider

- bit 7 **Reserved:** Write '1'

- bit 6-4 FPLLMUL<2:0>: PLL Multiplier bits

- 111 = 24x multiplier

- 110 = 21x multiplier

- 101 = 20x multiplier

- 100 = 19x multiplier

- 011 = 18x multiplier

- 010 = 17x multiplier 001 = 16x multiplier

- 001 = 10x multiplier

- bit 3 **Reserved:** Write '1'

# **30.0 INSTRUCTION SET**

The PIC32MX5XX/6XX/7XX family instruction set complies with the MIPS32 Release 2 instruction set architecture. The PIC32 device family does not support the following features:

- Core Extend instructions

- Coprocessor 1 instructions

- Coprocessor 2 instructions

Note: Refer to "MIPS32<sup>®</sup> Architecture for Programmers Volume II: The MIPS32<sup>®</sup> Instruction Set" at www.imgtec.com for more information.

### TABLE 32-4: DC TEMPERATURE AND VOLTAGE SPECIFICATIONS

| DC CHARACTERISTICS |        |                                                               | $\begin{tabular}{lllllllllllllllllllllllllllllllllll$ |         |       |       |            |

|--------------------|--------|---------------------------------------------------------------|-------------------------------------------------------|---------|-------|-------|------------|

| Param.<br>No.      | Symbol | Characteristics                                               | Min.                                                  | Typical | Max.  | Units | Conditions |

| Operating Voltage  |        |                                                               |                                                       |         |       |       |            |

| DC10               | Vdd    | Supply Voltage                                                | 2.3                                                   |         | 3.6   | V     |            |

| DC12               | Vdr    | RAM Data Retention Voltage <sup>(1)</sup>                     | 1.75                                                  |         |       | V     |            |

| DC16               | VPOR   | VDD Start Voltage to Ensure<br>Internal Power-on Reset Signal | 1.75                                                  |         | 2.1   | V     |            |

| DC17               | SVDD   | VDD Rise Rate to Ensure<br>Internal Power-on Reset Signal     | 0.00005                                               |         | 0.115 | V/µs  | —          |

**Note 1:** This is the limit to which VDD can be lowered without losing RAM data.

2: Overall functional device operation at VBORMIN < VDD < VDDMIN is tested, but not characterized. All device Analog modules, such as ADC, etc., will function, but with degraded performance below VDDMIN. Refer to parameter BO10 in Table 32-10 for BOR values.

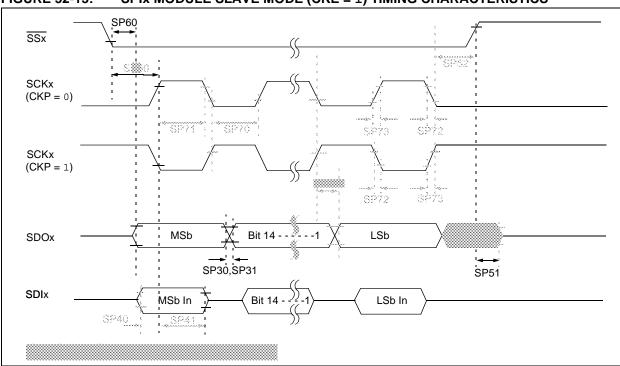

# FIGURE 32-13: SPIX MODULE SLAVE MODE (CKE = 1) TIMING CHARACTERISTICS

# TABLE 32-31: SPIX MODULE SLAVE MODE (CKE = 1) TIMING REQUIREMENTS

| AC CHARACTERISTICS |                            |                                                                           | $\begin{array}{l} \mbox{Standard Operating Conditions: 2.3V to 3.6V} \\ \mbox{(unless otherwise stated)} \\ \mbox{Operating temperature} & -40^{\circ}C \leq TA \leq +85^{\circ}C \mbox{ for Industrial} \\ & -40^{\circ}C \leq TA \leq +105^{\circ}C \mbox{ for V-Temp} \end{array}$ |                        |      |       |                    |

|--------------------|----------------------------|---------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------|------|-------|--------------------|

| Param.<br>No.      | Symbol                     | Characteristics <sup>(1)</sup>                                            | Min.                                                                                                                                                                                                                                                                                  | Typical <sup>(2)</sup> | Max. | Units | Conditions         |

| SP70               | TscL                       | SCKx Input Low Time <sup>(3)</sup>                                        | Tsck/2                                                                                                                                                                                                                                                                                |                        | —    | ns    | —                  |

| SP71               | TscH                       | SCKx Input High Time <sup>(3)</sup>                                       | Tsck/2                                                                                                                                                                                                                                                                                | —                      | _    | ns    | —                  |

| SP72               | TscF                       | SCKx Input Fall Time                                                      | _                                                                                                                                                                                                                                                                                     | 5                      | 10   | ns    | —                  |

| SP73               | TscR                       | SCKx Input Rise Time                                                      |                                                                                                                                                                                                                                                                                       | 5                      | 10   | ns    | —                  |

| SP30               | TDOF                       | SDOx Data Output Fall Time <sup>(4)</sup>                                 | —                                                                                                                                                                                                                                                                                     | —                      | _    | ns    | See parameter DO32 |

| SP31               | TDOR                       | SDOx Data Output Rise Time <sup>(4)</sup>                                 |                                                                                                                                                                                                                                                                                       | —                      | _    | ns    | See parameter DO31 |

| SP35               | SP35 TscH2doV,<br>TscL2doV | SDOx Data Output Valid after<br>SCKx Edge                                 |                                                                                                                                                                                                                                                                                       | _                      | 20   | ns    | VDD > 2.7V         |

|                    |                            |                                                                           |                                                                                                                                                                                                                                                                                       | _                      | 30   | ns    | VDD < 2.7V         |

| SP40               | TDIV2SCH,<br>TDIV2SCL      | Setup Time of SDIx Data Input to SCKx Edge                                | 10                                                                                                                                                                                                                                                                                    | —                      | —    | ns    | —                  |

| SP41               | TscH2diL,<br>TscL2diL      | Hold Time of SDIx Data Input to SCKx Edge                                 | 10                                                                                                                                                                                                                                                                                    | —                      | —    | ns    | —                  |

| SP50               | TssL2scH,<br>TssL2scL      | $\overline{SSx} \downarrow$ to SCKx $\downarrow$ or SCKx $\uparrow$ Input | 175                                                                                                                                                                                                                                                                                   | —                      | —    | ns    | —                  |

Note 1: These parameters are characterized, but not tested in manufacturing.

2: Data in "Typical" column is at 3.3V, 25°C unless otherwise stated. Parameters are for design guidance only and are not tested.

- 3: The minimum clock period for SCKx is 40 ns.

- 4: Assumes 50 pF load on all SPIx pins.

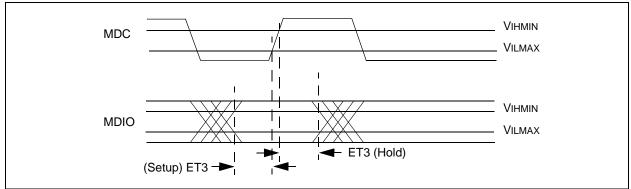

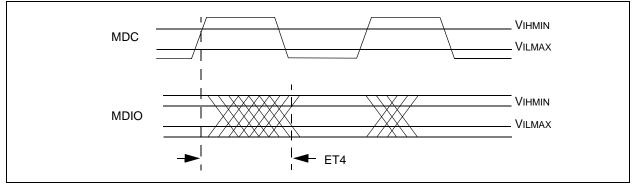

# TABLE 32-35: ETHERNET MODULE SPECIFICATIONS

| AC CHARACTERISTICS |                                     | $\begin{tabular}{lllllllllllllllllllllllllllllllllll$ |         |      |       |                  |  |

|--------------------|-------------------------------------|-------------------------------------------------------|---------|------|-------|------------------|--|

| Param.<br>No.      | Characteristic                      | Min.                                                  | Typical | Max. | Units | Conditions       |  |

| MIIM Tin           | ning Requirements                   |                                                       |         |      |       |                  |  |

| ET1                | MDC Duty Cycle                      | 40                                                    |         | 60   | %     | —                |  |

| ET2                | MDC Period                          | 400                                                   | —       | _    | ns    | —                |  |

| ET3                | MDIO Output Setup and Hold          | 10                                                    | —       | 10   | ns    | See Figure 32-19 |  |

| ET4                | MDIO Input Setup and Hold           | 0                                                     | —       | 300  | ns    | See Figure 32-20 |  |

| MII Timi           | ng Requirements                     |                                                       |         |      |       |                  |  |

| ET5                | TX Clock Frequency                  | —                                                     | 25      | _    | MHz   | —                |  |

| ET6                | TX Clock Duty Cycle                 | 35                                                    | —       | 65   | %     | —                |  |

| ET7                | ETXDx, ETEN, ETXERR Output Delay    | 0                                                     | —       | 25   | ns    | See Figure 32-21 |  |

| ET8                | RX Clock Frequency                  | _                                                     | 25      |      | MHz   | —                |  |

| ET9                | RX Clock Duty Cycle                 | 35                                                    | —       | 65   | %     | —                |  |

| ET10               | ERXDx, ERXDV, ERXERR Setup and Hold | 10                                                    | —       | 30   | ns    | See Figure 32-22 |  |

| <b>RMII</b> Tin    | ning Requirements                   |                                                       |         |      |       |                  |  |

| ET11               | Reference Clock Frequency           | —                                                     | 50      | _    | MHz   | —                |  |

| ET12               | Reference Clock Duty Cycle          | 35                                                    |         | 65   | %     | —                |  |

| ET13               | ETXDx, ETEN, Setup and Hold         | 2                                                     | —       | 4    | ns    | —                |  |

| ET14               | ERXDx, ERXDV, ERXERR Setup and Hold | 2                                                     | —       | 4    | ns    | —                |  |

**Note 1:** The Ethernet module is functional at VBORMIN < VDD < 2.9V, but with degraded performance. Unless otherwise stated, module functionality is tested, but not characterized.

# FIGURE 32-19: MDIO SOURCED BY THE PIC32 DEVICE

# FIGURE 32-20: MDIO SOURCED BY THE PHY

# **Revision H (March 2013)**

This revision includes the following global updates:

- Where applicable, control register tables have been added to the document

- All references to VCORE were removed

- All occurrences of XBGA have been updated to: TFBGA

# TABLE B-6: MAJOR SECTION UPDATES

• All occurrences of VUSB have been updated to: VUSB3V3

This revision also includes minor typographical and formatting changes throughout the data sheet text.

All other significant changes are referenced by their respective section in Table B-6.

| Section Name                                                        | Update Description                                                                                                                              |

|---------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------|

| "32-bit Microcontrollers                                            | Updated Core features.                                                                                                                          |

| (up to 512 KB Flash and 128                                         | Added the VTLA to the Packages table.                                                                                                           |

| KB SRAM) with Graphics<br>Interface, USB, CAN, and<br>Ethernet"     | Added Note 5 to the Feature tables (see Table 1, Table 2, and Table 3).                                                                         |

|                                                                     | The Decommended Minimum Connection was undeted (see Figure 2.4)                                                                                 |

| Section 2.0 "Guidelines for<br>Getting Started with 32-bit<br>MCUs" | The Recommended Minimum Connection was updated (see Figure 2-1).                                                                                |

| Section 5.0 "Flash Program<br>Memory"                               | A note regarding Flash page size and row size was added.                                                                                        |

| Section 8.0 "Oscillator<br>Configuration"                           | The RP resistor was added and Note 1 was updated in the Oscillator Diagram (see Figure 8-1).                                                    |

| Section 31.0 "Electrical                                            | Added Note 1 to Operating MIPS vs. Voltage (see Table 31-1).                                                                                    |

| Characteristics"                                                    | Added the VTLA package to Thermal Packaging Characteristics (see Table 31-3).                                                                   |

|                                                                     | Added Note 2 to DC Temperature and Voltage Specifications (see Table 31-4).                                                                     |

|                                                                     | Updated Note 2 in the Operating Current DC Characteristics (see Table 31-5).                                                                    |

|                                                                     | Updated Note 1 in the Idle Current DC Characteristics (see Table 31-6).                                                                         |

|                                                                     | Updated Note 1 in the Power-Down Current DC Characteristics (see Table 31-7).                                                                   |

|                                                                     | Updated the I/O Pin Output Specifications (see Table 31-9).                                                                                     |

|                                                                     | Added Note 2 to the BOR Electrical Characteristics (see Table 31-10).                                                                           |