Welcome to E-XFL.COM

### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

### Details

| Details                    |                                                                                   |

|----------------------------|-----------------------------------------------------------------------------------|

| Product Status             | Active                                                                            |

| Core Processor             | MIPS32® M4K™                                                                      |

| Core Size                  | 32-Bit Single-Core                                                                |

| Speed                      | 80MHz                                                                             |

| Connectivity               | CANbus, Ethernet, I <sup>2</sup> C, SPI, UART/USART, USB OTG                      |

| Peripherals                | Brown-out Detect/Reset, DMA, POR, PWM, WDT                                        |

| Number of I/O              | 53                                                                                |

| Program Memory Size        | 512KB (512K x 8)                                                                  |

| Program Memory Type        | FLASH                                                                             |

| EEPROM Size                | -                                                                                 |

| RAM Size                   | 64K × 8                                                                           |

| Voltage - Supply (Vcc/Vdd) | 2.3V ~ 3.6V                                                                       |

| Data Converters            | A/D 16x10b                                                                        |

| Oscillator Type            | Internal                                                                          |

| Operating Temperature      | -40°C ~ 105°C (TA)                                                                |

| Mounting Type              | Surface Mount                                                                     |

| Package / Case             | 64-TQFP                                                                           |

| Supplier Device Package    | 64-TQFP (10x10)                                                                   |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic32mx775f512ht-80v-pt |

|                            |                                                                                   |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

|                  | USB and Ethernet |                         |                  |     |          |                        |                                          |                       |                    |                                 |                              |             |         |      |       |                         |

|------------------|------------------|-------------------------|------------------|-----|----------|------------------------|------------------------------------------|-----------------------|--------------------|---------------------------------|------------------------------|-------------|---------|------|-------|-------------------------|

| Device           | Pins             | Program Memory (KB)     | Data Memory (KB) | USB | Ethernet | Timers/Capture/Compare | DMA Channels<br>(Programmable/Dedicated) | UART <sup>(2,3)</sup> | SPI <sup>(3)</sup> | I <sup>2</sup> C <sup>(3)</sup> | 10-bit 1 Msps ADC (Channels) | Comparators | dSP/PMP | JTAG | Trace | Packages <sup>(4)</sup> |

| PIC32MX664F064H  | 64               | 64 + 12 <sup>(1)</sup>  | 32               | 1   | 1        | 5/5/5                  | 4/4                                      | 6                     | 3                  | 4                               | 16                           | 2           | Yes     | Yes  | No    | PT,<br>MR               |

| PIC32MX664F128H  | 64               | 128 + 12 <sup>(1)</sup> | 32               | 1   | 1        | 5/5/5                  | 4/4                                      | 6                     | 3                  | 4                               | 16                           | 2           | Yes     | Yes  | No    | PT,<br>MR               |

| PIC32MX675F256H  | 64               | 256 + 12 <sup>(1)</sup> | 64               | 1   | 1        | 5/5/5                  | 8/4                                      | 6                     | 3                  | 4                               | 16                           | 2           | Yes     | Yes  | No    | PT,<br>MR               |

| PIC32MX675F512H  | 64               | 512 + 12 <sup>(1)</sup> | 64               | 1   | 1        | 5/5/5                  | 8/4                                      | 6                     | 3                  | 4                               | 16                           | 2           | Yes     | Yes  | No    | PT,<br>MR               |

| PIC32MX695F512H  | 64               | 512 + 12 <sup>(1)</sup> | 128              | 1   | 1        | 5/5/5                  | 8/4                                      | 6                     | 3                  | 4                               | 16                           | 2           | Yes     | Yes  | No    | PT,<br>MR               |

| PIC32MX664F064L  | 100              | 64 + 12 <sup>(1)</sup>  | 32               | 1   | 1        | 5/5/5                  | 4/4                                      | 6                     | 4                  | 5                               | 16                           | 2           | Yes     | Yes  | Yes   | PT, PF,<br>BG           |

| PIC32MX664F128L  | 100              | 128 + 12 <sup>(1)</sup> | 32               | 1   | 1        | 5/5/5                  | 4/4                                      | 6                     | 4                  | 5                               | 16                           | 2           | Yes     | Yes  | Yes   | PT, PF,<br>BG           |

| PIC32MX675F256L  | 100              | 256 + 12 <sup>(1)</sup> | 64               | 1   | 1        | 5/5/5                  | 8/4                                      | 6                     | 4                  | 5                               | 16                           | 2           | Yes     | Yes  | Yes   | PT, PF,<br>BG           |

| PIC32MX675F512L  | 100              | 512 + 12 <sup>(1)</sup> | 64               | 1   | 1        | 5/5/5                  | 8/4                                      | 6                     | 4                  | 5                               | 16                           | 2           | Yes     | Yes  | Yes   | PT, PF,<br>BG, TL       |

| PIC32MX695F512L  | 100              | 512 + 12 <sup>(1)</sup> | 128              | 1   | 1        | 5/5/5                  | 8/4                                      | 6                     | 4                  | 5                               | 16                           | 2           | Yes     | Yes  | Yes   | PT, PF,<br>BG, TL       |

| Legend: PF, PT = | TQFP             | MR = QF                 | N                |     | BG =     | TFBGA                  | 4                                        | TL =                  | VTL/               | ų( <del>5</del> )               |                              |             |         |      |       |                         |

| TABLE 2: PIC32MX6XX USB AND ETHERNET FEATURES |

|-----------------------------------------------|

|-----------------------------------------------|

Legend: PF, PT = TQFP MR = QFN BG = Note 1: This device features 12 KB boot Flash memory.

2: CTS and RTS pins may not be available for all UART modules. Refer to the "Device Pin Tables" section for more information.

3: Some pins between the UART, SPI and I<sup>2</sup>C modules may be shared. Refer to the "Device Pin Tables" section for more information.

4: Refer to 34.0 "Packaging Information" for more information.

5: 100-pin devices other than those listed here are available in the VTLA package upon request. Please contact your local Microchip Sales Office for details.

### PIN NAMES FOR 100-PIN USB, ETHERNET, AND CAN DEVICES TABLE 9:

### **100-PIN TQFP (TOP VIEW)**

PIC32MX764F128L PIC32MX775F256L PIC32MX775F512L PIC32MX795F512L

100

| Pin # | Full Pin Name                                                |

|-------|--------------------------------------------------------------|

| 1     | AERXERR/RG15                                                 |

| 2     | VDD                                                          |

| 3     | PMD5/RE5                                                     |

| 4     | PMD6/RE6                                                     |

| 5     | PMD7/RE7                                                     |

| 6     | T2CK/RC1                                                     |

| 7     | T3CK/AC2TX <sup>(1)</sup> /RC2                               |

| 8     | T4CK/AC2RX <sup>(1)</sup> /RC3                               |

| 9     | T5CK/SDI1/RC4                                                |

| 10    | ECOL/SCK2/U6TX/U3RTS/PMA5/CN8/RG6                            |

| 11    | ECRS/SDA4/SDI2/U3RX/PMA4/CN9/RG7                             |

| 12    | ERXDV/AERXDV/ECRSDV/AECRSDV/SCL4/SDO2/U3TX/PMA3/CN10/RG8     |

| 13    | MCLR                                                         |

| 14    | ERXCLK/AERXCLK/EREFCLK/AEREFCLK/SS2/U6RX/U3CTS/PMA2/CN11/RG9 |

| 15    | Vss                                                          |

| 16    | VDD                                                          |

| 17    | TMS/RA0                                                      |

| 18    | AERXD0/INT1/RE8                                              |

| 19    | AERXD1/INT2/RE9                                              |

| 20    | AN5/C1IN+/VBUSON/CN7/RB5                                     |

| 21    | AN4/C1IN-/CN6/RB4                                            |

| 22    | AN3/C2IN+/CN5/RB3                                            |

| 23    | AN2/C2IN-/CN4/RB2                                            |

| 24    | PGEC1/AN1/CN3/RB1                                            |

| 25    | PGED1/AN0/CN2/RB0                                            |

| 26    | PGEC2/AN6/OCFA/RB6                                           |

| 27    | PGED2/AN7/RB7                                                |

| 28    | VREF-/CVREF-/AERXD2/PMA7/RA9                                 |

| 29    | VREF+/CVREF+/AERXD3/PMA6/RA10                                |

| 30    | AVdd                                                         |

| 31    | AVss                                                         |

| 32    | AN8/C1OUT/RB8                                                |

| 33    | AN9/C2OUT/RB9                                                |

| 34    | AN10/CVREFOUT/PMA13/RB10                                     |

| 35    | AN11/ERXERR/AETXERR/PMA12/RB11                               |

| Note  | 1: This pin is not available on PIC32MX764F128L devices.     |

| Pin # | Full Pin Name                               |

|-------|---------------------------------------------|

| 36    | Vss                                         |

| 37    | Vdd                                         |

| 38    | TCK/RA1                                     |

| 39    | AC1TX/SCK4/U5TX/U2RTS/RF13                  |

| 40    | AC1RX/SS4/U5RX/U2CTS/RF12                   |

| 41    | AN12/ERXD0/AECRS/PMA11/RB12                 |

| 42    | AN13/ERXD1/AECOL/PMA10/RB13                 |

| 43    | AN14/ERXD2/AETXD3/PMALH/PMA1/RB14           |

| 44    | AN15/ERXD3/AETXD2/OCFB/PMALL/PMA0/CN12/RB15 |

| 45    | Vss                                         |

| 46    | VDD                                         |

| 47    | AETXD0/SS3/U4RX/U1CTS/CN20/RD14             |

| 48    | AETXD1/SCK3/U4TX/U1RTS/CN21/RD15            |

| 49    | SDA5/SDI4/U2RX/PMA9/CN17/RF4                |

| 50    | SCL5/SDO4/U2TX/PMA8/CN18/RF5                |

| 51    | USBID/RF3                                   |

| 52    | SDA3/SDI3/U1RX/RF2                          |

| 53    | SCL3/SDO3/U1TX/RF8                          |

| 54    | VBUS                                        |

| 55    | VUSB3V3                                     |

| 56    | D-/RG3                                      |

| 57    | D+/RG2                                      |

| 58    | SCL2/RA2                                    |

| 59    | SDA2/RA3                                    |

| 60    | TDI/RA4                                     |

| 61    | TDO/RA5                                     |

| 62    | Vdd                                         |

| 63    | OSC1/CLKI/RC12                              |

| 64    | OSC2/CLKO/RC15                              |

| 65    | Vss                                         |

| 66    | AETXCLK/SCL1/INT3/RA14                      |

| 67    | AETXEN/SDA1/INT4/RA15                       |

| 68    | RTCC/EMDIO/AEMDIO/IC1/RD8                   |

| 69    | SS1/IC2/RD9                                 |

| 70    | SCK1/IC3/PMCS2/PMA15/RD10                   |

1

2: Shaded pins are 5V tolerant.

## TABLE 1-1: PINOUT I/O DESCRIPTIONS (CONTINUED)

|           |                    | Pin Nun         | nber <sup>(1)</sup> |                 |             |                |                                                            |

|-----------|--------------------|-----------------|---------------------|-----------------|-------------|----------------|------------------------------------------------------------|

| Pin Name  | 64-Pin<br>QFN/TQFP | 100-Pin<br>TQFP | 121-Pin<br>TFBGA    | 124-pin<br>VTLA | Pin<br>Type | Buffer<br>Type | Description                                                |

| AC2TX     | —                  | 7               | E4                  | B4              | 0           | —              | Alternate CAN2 bus transmit pin                            |

| ERXD0     | 61                 | 41              | J7                  | B23             | I           | ST             | Ethernet Receive Data 0 <sup>(2)</sup>                     |

| ERXD1     | 60                 | 42              | L7                  | A28             | I           | ST             | Ethernet Receive Data 1 <sup>(2)</sup>                     |

| ERXD2     | 59                 | 43              | K7                  | B24             | I           | ST             | Ethernet Receive Data 2 <sup>(2)</sup>                     |

| ERXD3     | 58                 | 44              | L8                  | A29             | I           | ST             | Ethernet Receive Data 3 <sup>(2)</sup>                     |

| ERXERR    | 64                 | 35              | J5                  | B20             | I           | ST             | Ethernet receive error input <sup>(2)</sup>                |

| ERXDV     | 62                 | 12              | F2                  | A8              | I           | ST             | Ethernet receive data valid <sup>(2)</sup>                 |

| ECRSDV    | 62                 | 12              | F2                  | A8              | I           | ST             | Ethernet carrier sense data valid <sup>(2)</sup>           |

| ERXCLK    | 63                 | 14              | F3                  | A9              | I           | ST             | Ethernet receive clock <sup>(2)</sup>                      |

| EREFCLK   | 63                 | 14              | F3                  | A9              | I           | ST             | Ethernet reference clock <sup>(2)</sup>                    |

| ETXD0     | 2                  | 88              | A6                  | A60             | 0           | _              | Ethernet Transmit Data 0 <sup>(2)</sup>                    |

| ETXD1     | 3                  | 87              | B6                  | B49             | 0           | _              | Ethernet Transmit Data 1 <sup>(2)</sup>                    |

| ETXD2     | 43                 | 79              | A9                  | B43             | 0           | _              | Ethernet Transmit Data 2 <sup>(2)</sup>                    |

| ETXD3     | 42                 | 80              | D8                  | A54             | 0           | _              | Ethernet Transmit Data 3 <sup>(2)</sup>                    |

| ETXERR    | 54                 | 89              | E6                  | B50             | 0           | _              | Ethernet transmit error <sup>(2)</sup>                     |

| ETXEN     | 1                  | 83              | D7                  | B45             | 0           | _              | Ethernet transmit enable <sup>(2)</sup>                    |

| ETXCLK    | 55                 | 84              | C7                  | A56             | I           | ST             | Ethernet transmit clock <sup>(2)</sup>                     |

| ECOL      | 44                 | 10              | E3                  | A7              | I           | ST             | Ethernet collision detect <sup>(2)</sup>                   |

| ECRS      | 45                 | 11              | F4                  | B6              | I           | ST             | Ethernet carrier sense <sup>(2)</sup>                      |

| EMDC      | 30                 | 71              | C11                 | A46             | 0           | _              | Ethernet management data clock <sup>(2)</sup>              |

| EMDIO     | 49                 | 68              | E9                  | B37             | I/O         | _              | Ethernet management data <sup>(2)</sup>                    |

| AERXD0    | 43                 | 18              | G1                  | A11             | I           | ST             | Alternate Ethernet Receive Data 0 <sup>(2)</sup>           |

| AERXD1    | 42                 | 19              | G2                  | B10             | I           | ST             | Alternate Ethernet Receive Data 1 <sup>(2)</sup>           |

| AERXD2    | —                  | 28              | L2                  | A21             | I           | ST             | Alternate Ethernet Receive Data 2(2)                       |

| AERXD3    | —                  | 29              | K3                  | B17             | I           | ST             | Alternate Ethernet Receive Data 3 <sup>(2)</sup>           |

| AERXERR   | 55                 | 1               | B2                  | A2              | I           | ST             | Alternate Ethernet receive error input <sup>(2)</sup>      |

| AERXDV    | —                  | 12              | F2                  | A8              | I           | ST             | Alternate Ethernet receive data valid <sup>(2)</sup>       |

| AECRSDV   | 44                 | 12              | F2                  | A8              | I           | ST             | Alternate Ethernet carrier sense data valid <sup>(2)</sup> |

| AERXCLK   | —                  | 14              | F3                  | A9              | I           | ST             | Alternate Ethernet receive clock <sup>(2)</sup>            |

| AEREFCLK  | 45                 | 14              | F3                  | A9              | I           | ST             | Alternate Ethernet reference clock <sup>(2)</sup>          |

| AETXD0    | 59                 | 47              | L9                  | B26             | 0           |                | Alternate Ethernet Transmit Data 0 <sup>(2)</sup>          |

| AETXD1    | 58                 | 48              | K9                  | A31             | 0           |                | Alternate Ethernet Transmit Data 1 <sup>(2)</sup>          |

| AETXD2    |                    | 44              | L8                  | A29             | 0           |                | Alternate Ethernet Transmit Data 2 <sup>(2)</sup>          |

| AETXD3    |                    | 43              | K7                  | B24             | 0           |                | Alternate Ethernet Transmit Data 3 <sup>(2)</sup>          |

| AETXERR   |                    | 35              | J5                  | B20             | 0           |                | Alternate Ethernet transmit error <sup>(2)</sup>           |

| AETXEN    | 54                 | 67              | E8                  | A44             | 0           |                | Alternate Ethernet transmit enable <sup>(2)</sup>          |

| AETXCLK   | _                  | 66              | E11                 | B36             | 1           | ST             | Alternate Ethernet transmit clock <sup>(2)</sup>           |

| AECOL     |                    | 42              | L7                  | A28             | 1           | ST             | Alternate Ethernet collision detect <sup>(2)</sup>         |

| Leaend: C | MOS = CMO          | S compatib      | le input or c       | butput          | A           | nalog = A      | Analog input P = Power                                     |

Legend: CMOS = CMOS compatible input or output ST = Schmitt Trigger input with CMOS levels

Analog = Analog input P = PowerO = Output I = Input

TTL = TTL input buffer

Note 1: Pin numbers are only provided for reference. See the "Device Pin Tables" section for device pin availability.

2: See 25.0 "Ethernet Controller" for more information.

# 2.5 ICSP Pins

The PGECx and PGEDx pins are used for In-Circuit Serial Programming<sup>TM</sup> (ICSP<sup>TM</sup>) and debugging. It is recommended to keep the trace length between the ICSP connector and the ICSP pins on the device as short as possible. If the ICSP connector is expected to experience an ESD event, a series resistor is recommended, with the value in the range of a few tens of Ohms, not to exceed 100 Ohms.

Pull-up resistors, series diodes and capacitors on the PGECx and PGEDx pins are not recommended as they will interfere with the programmer/debugger communications to the device. If such discrete components are an application requirement, they should be removed from the circuit during programming and debugging. Alternatively, refer to the AC/DC characteristics and timing requirements information in the respective device Flash programming specification for information on capacitive loading limits and pin input voltage high (VIH) and input low (VIL) requirements.

Ensure that the "Communication Channel Select" (i.e., PGECx/PGEDx pins) programmed into the device matches the physical connections for the ICSP to MPLAB<sup>®</sup> ICD 3 or MPLAB<sup>®</sup> REAL ICE<sup>TM</sup>.

For more information on ICD 3 and REAL ICE connection requirements, refer to the following documents that are available on the Microchip web site.

- "Using MPLAB<sup>®</sup> ICD 3" (poster) (DS50001765)

- "MPLAB<sup>®</sup> ICD 3 Design Advisory" (DS50001764)

- "MPLAB<sup>®</sup> REAL ICE<sup>™</sup> In-Circuit Emulator User's Guide" (DS50001616)

- "Using MPLAB<sup>®</sup> REAL ICE™ Emulator" (poster) (DS50001749)

# 2.6 JTAG

The TMS, TDO, TDI and TCK pins are used for testing and debugging according to the Joint Test Action Group (JTAG) standard. It is recommended to keep the trace length between the JTAG connector and the JTAG pins on the device as short as possible. If the JTAG connector is expected to experience an ESD event, a series resistor is recommended, with the value in the range of a few tens of Ohms, not to exceed 100 Ohms.

Pull-up resistors, series diodes and capacitors on the TMS, TDO, TDI and TCK pins are not recommended as they will interfere with the programmer/debugger communications to the device. If such discrete components are an application requirement, they should be removed from the circuit during programming and debugging. Alternatively, refer to the AC/DC characteristics and timing requirements information in the respective device Flash programming specification for information on capacitive loading limits and pin input voltage high (VIH) and input low (VIL) requirements.

# 2.7 Trace

The trace pins can be connected to a hardware-traceenabled programmer to provide a compress real time instruction trace. When used for trace the TRD3, TRD2, TRD1, TRD0 and TRCLK pins should be dedicated for this use. The trace hardware requires a  $22\Omega$  series resistor between the trace pins and the trace connector.

# 2.8 External Oscillator Pins

Many MCUs have options for at least two oscillators: a high-frequency primary oscillator and a low-frequency secondary oscillator. Refer to **Section 8.0 "Oscillator Configuration"** for details.

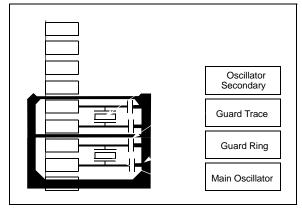

The oscillator circuit should be placed on the same side of the board as the device. Also, place the oscillator circuit close to the respective oscillator pins, not exceeding one-half inch (12 mm) distance between them. The load capacitors should be placed next to the oscillator itself, on the same side of the board. Use a grounded copper pour around the oscillator circuit to isolate them from surrounding circuits. The grounded copper pour should be routed directly to the MCU ground. Do not run any signal traces or power traces inside the ground pour. Also, if using a two-sided board, avoid any traces on the other side of the board where the crystal is placed. A suggested layout is illustrated in Figure 2-3.

### FIGURE 2-3: SUGGESTED OSCILLATOR CIRCUIT PLACEMENT

# 6.0 RESETS

Note: This data sheet summarizes the features of the PIC32MX5XX/6XX/7XX family of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to **Section 7.** "**Resets**" (DS60001118) in the "*PIC32 Family Reference Manual*", which is available from the Microchip web site (www.microchip.com/PIC32).

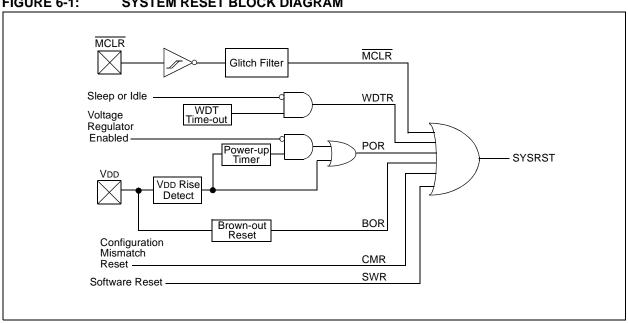

The Reset module combines all Reset sources and controls the device Master Reset signal, SYSRST. The following is a list of device Reset sources:

- Power-on Reset (POR)

- Master Clear Reset pin (MCLR)

- Software Reset (SWR)

- Watchdog Timer Reset (WDTR)

- Brown-out Reset (BOR)

- Configuration Mismatch Reset (CMR)

A simplified block diagram of the Reset module is illustrated in Figure 6-1.

# FIGURE 6-1: SYSTEM RESET BLOCK DIAGRAM

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |  |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|--|--|

| 31:24        | R/W-0             | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |  |  |

|              | LTAGBOOT          | —                 | _                 | -                 | —                 | _                 | _                | —                |  |  |

| 23:16        | R/W-x             | R/W-x             | R/W-x             | R/W-x             | R/W-x             | R/W-x             | R/W-x            | R/W-x            |  |  |

| 23.10        | LTAG<19:12>       |                   |                   |                   |                   |                   |                  |                  |  |  |

| 15:8         | R/W-x             | R/W-x             | R/W-x             | R/W-x             | R/W-x             | R/W-x             | R/W-x            | R/W-x            |  |  |

| 10.0         | LTAG<11:4>        |                   |                   |                   |                   |                   |                  |                  |  |  |

| 7.0          | R/W-x             | R/W-x             | R/W-x             | R/W-x             | R/W-0             | R/W-0             | R/W-1            | U-0              |  |  |

| 7:0          |                   | LTAG<             | <3:0>             |                   | LVALID            | LLOCK             | LTYPE            | —                |  |  |

### REGISTER 9-3: CHETAG: CACHE TAG REGISTER

# Legend:

| 3                                 |                                 |                                    |                    |  |  |  |

|-----------------------------------|---------------------------------|------------------------------------|--------------------|--|--|--|

| R = Readable bit W = Writable bit |                                 | U = Unimplemented bit, read as '0' |                    |  |  |  |

| -n = Value at POR                 | = Value at POR '1' = Bit is set |                                    | x = Bit is unknown |  |  |  |

### bit 31 LTAGBOOT: Line Tag Address Boot bit

- 1 = The line is in the 0x1D000000 (physical) area of memory

- 0 = The line is in the 0x1FC00000 (physical) area of memory

### bit 30-24 Unimplemented: Write '0'; ignore read

### bit 23-4 LTAG<19:0>: Line Tag Address bits

LTAG<19:0> bits are compared against physical address to determine a hit. Because its address range and position of PFM in kernel space and user space, the LTAG PFM address is identical for virtual addresses, (system) physical addresses, and PFM physical addresses.

### bit 3 LVALID: Line Valid bit

- 1 = The line is valid and is compared to the physical address for hit detection

- 0 = The line is not valid and is not compared to the physical address for hit detection

### bit 2 LLOCK: Line Lock bit

- 1 = The line is locked and will not be replaced

- 0 = The line is not locked and can be replaced

### bit 1 LTYPE: Line Type bit

- 1 = The line caches instruction words

- 0 = The line caches data words

- bit 0 Unimplemented: Write '0'; ignore read

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |  |  |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|--|--|--|

| 04.04        | R/W-x             | R/W-x             | R/W-x             | R/W-x             | R/W-x             | R/W-x             | R/W-x            | R/W-x            |  |  |  |

| 31:24        | CHEW3<31:24>      |                   |                   |                   |                   |                   |                  |                  |  |  |  |

| 00.40        | R/W-x             | R/W-x             | R/W-x             | R/W-x             | R/W-x             | R/W-x             | R/W-x            | R/W-x            |  |  |  |

| 23:16        | CHEW3<23:16>      |                   |                   |                   |                   |                   |                  |                  |  |  |  |

| 45.0         | R/W-x             | R/W-x             | R/W-x             | R/W-x             | R/W-x             | R/W-x             | R/W-x            | R/W-x            |  |  |  |

| 15:8         | CHEW3<15:8>       |                   |                   |                   |                   |                   |                  |                  |  |  |  |

| 7:0          | R/W-x             | R/W-x             | R/W-x             | R/W-x             | R/W-x             | R/W-x             | R/W-x            | R/W-x            |  |  |  |

|              |                   | •                 | •                 | CHEW3             | <7:0>             |                   | •                |                  |  |  |  |

### REGISTER 9-8: CHEW3: CACHE WORD 3

| Legend:           |                  |                      |                    |

|-------------------|------------------|----------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bi | t, read as '0'     |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared | x = Bit is unknown |

bit 31-0 **CHEW3<31:0>:** Word 3 of the cache line selected by CHEIDX<3:0> bits (CHEACC<3:0>) Readable only if the device is not code-protected.

Note: This register is a window into the cache data array and is only readable if the device is not code-protected.

### REGISTER 9-9: CHELRU: CACHE LRU REGISTER

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |  |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|--|--|

| 31:24        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | R-0              |  |  |

|              | —                 | —                 | _                 | —                 | —                 | _                 | —                | CHELRU<24>       |  |  |

| 00.40        | R-0               | R-0               | R-0               | R-0               | R-0               | R-0               | R-0              | R-0              |  |  |

| 23:16        | CHELRU<23:16>     |                   |                   |                   |                   |                   |                  |                  |  |  |

| 45.0         | R-0               | R-0               | R-0               | R-0               | R-0               | R-0               | R-0              | R-0              |  |  |

| 15:8         | CHELRU<15:8>      |                   |                   |                   |                   |                   |                  |                  |  |  |

| 7.0          | R-0               | R-0               | R-0               | R-0               | R-0               | R-0               | R-0              | R-0              |  |  |

| 7:0          |                   |                   |                   | CHELF             | RU<7:0>           |                   |                  |                  |  |  |

| Legend:           |                  |                                    |                    |  |  |  |

|-------------------|------------------|------------------------------------|--------------------|--|--|--|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read as '0' |                    |  |  |  |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared               | x = Bit is unknown |  |  |  |

bit 31-25 Unimplemented: Write '0'; ignore read

bit 24-0 **CHELRU<24:0>:** Cache Least Recently Used State Encoding bits Indicates the pseudo-LRU state of the cache.

## REGISTER 11-1: U1OTGIR: USB OTG INTERRUPT STATUS REGISTER

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|

| 31:24        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 31.24        | _                 | _                 |                   | _                 | —                 | —                 |                  |                  |

| 23:16        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 23.10        |                   |                   |                   |                   | —                 | _                 |                  | —                |

| 15:8         | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 15.0         | -                 | —                 | —                 | _                 | —                 | —                 | -                | —                |

| 7:0          | R/WC-0, HS        | U-0              | R/WC-0, HS       |

| 7.0          | IDIF              | T1MSECIF          | LSTATEIF          | ACTVIF            | SESVDIF           | SESENDIF          |                  | VBUSVDIF         |

| Legend:           | WC = Write '1' to clear | HS = Hardware Settable bit         |        |  |

|-------------------|-------------------------|------------------------------------|--------|--|

| R = Readable bit  | W = Writable bit        | U = Unimplemented bit, read as '0' |        |  |

| -n = Value at POR | '1' = Bit is set        | '0' = Bit is cleared x = Bit is un | nknown |  |

### bit 31-8 Unimplemented: Read as '0'

- bit 7 IDIF: ID State Change Indicator bit

- 1 = Change in ID state detected

- 0 = No change in ID state detected

### bit 6 T1MSECIF: 1 Millisecond Timer bit

- 1 = 1 millisecond timer has expired

- 0 = 1 millisecond timer has not expired

- bit 5 LSTATEIF: Line State Stable Indicator bit

- 1 = USB line state has been stable for 1 ms, but different from last time

- 0 = USB line state has not been stable for 1 ms

### bit 4 ACTVIF: Bus Activity Indicator bit

- 1 = Activity on the D+, D-, ID or VBUS pins has caused the device to wake-up

- 0 = Activity has not been detected

- bit 3 SESVDIF: Session Valid Change Indicator bit

- 1 = VBUS voltage has dropped below the session end level

- 0 = VBUS voltage has not dropped below the session end level

### bit 2 SESENDIF: B-Device VBUS Change Indicator bit

- 1 = A change on the session end input was detected

- 0 = No change on the session end input was detected

### bit 1 Unimplemented: Read as '0'

- bit 0 VBUSVDIF: A-Device VBUS Change Indicator bit

- 1 = Change on the session valid input detected

- 0 = No change on the session valid input detected

| Bit<br>31/23/15/7 | Bit<br>30/22/14/6                             | Bit<br>29/21/13/5                                                                                                                                                                                                                                                                                                     | Bit<br>28/20/12/4                                                                                                                                                                                                                                                                                                                                                                                                                                                         | Bit<br>27/19/11/3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | Bit<br>26/18/10/2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | Bit<br>25/17/9/1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | Bit<br>24/16/8/0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |  |  |

|-------------------|-----------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| U-0               | U-0                                           | U-0                                                                                                                                                                                                                                                                                                                   | U-0                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | U-0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | U-0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | U-0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | U-0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |  |  |

|                   | _                                             | _                                                                                                                                                                                                                                                                                                                     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | —                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | —                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | —                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | —                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |  |  |

| U-0               | U-0                                           | U-0                                                                                                                                                                                                                                                                                                                   | U-0                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | U-0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | U-0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | U-0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | U-0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |  |  |

| —                 | —                                             | —                                                                                                                                                                                                                                                                                                                     | —                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | —                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | —                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | —                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | —                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |  |  |

| U-0               | U-0                                           | U-0                                                                                                                                                                                                                                                                                                                   | U-0                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | U-0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | U-0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | U-0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | U-0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |  |  |

|                   | _                                             | _                                                                                                                                                                                                                                                                                                                     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | —                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | —                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | —                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | —                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |  |  |

| R/WC-0, HS        | R/WC-0, HS                                    | R/WC-0, HS                                                                                                                                                                                                                                                                                                            | R/WC-0, HS                                                                                                                                                                                                                                                                                                                                                                                                                                                                | R/WC-0, HS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | R/WC-0, HS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | R-0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | R/WC-0, HS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |  |  |