Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

## Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFI

| Product Status             | Active                                                                           |

|----------------------------|----------------------------------------------------------------------------------|

| Core Processor             | MIPS32® M4K™                                                                     |

| Core Size                  | 32-Bit Single-Core                                                               |

| Speed                      | 80MHz                                                                            |

| Connectivity               | CANbus, Ethernet, I <sup>2</sup> C, SPI, UART/USART, USB OTG                     |

| Peripherals                | Brown-out Detect/Reset, DMA, POR, PWM, WDT                                       |

| Number of I/O              | 85                                                                               |

| Program Memory Size        | 512KB (512K x 8)                                                                 |

| Program Memory Type        | FLASH                                                                            |

| EEPROM Size                | -                                                                                |

| RAM Size                   | 64K x 8                                                                          |

| Voltage - Supply (Vcc/Vdd) | 2.3V ~ 3.6V                                                                      |

| Data Converters            | A/D 16x10b                                                                       |

| Oscillator Type            | Internal                                                                         |

| Operating Temperature      | -40°C ~ 105°C (TA)                                                               |

| Mounting Type              | Surface Mount                                                                    |

| Package / Case             | 100-TQFP                                                                         |

| Supplier Device Package    | 100-TQFP (14x14)                                                                 |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic32mx775f512l-80v-pf |

|                            |                                                                                  |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

## 1.0 DEVICE OVERVIEW

**Note:** This data sheet summarizes the features of the PIC32MX5XX/6XX/7XX family of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to the documents listed in the *Documentation* > *Reference Manual* section of the Microchip PIC32 web site (www.microchip.com/pic32).

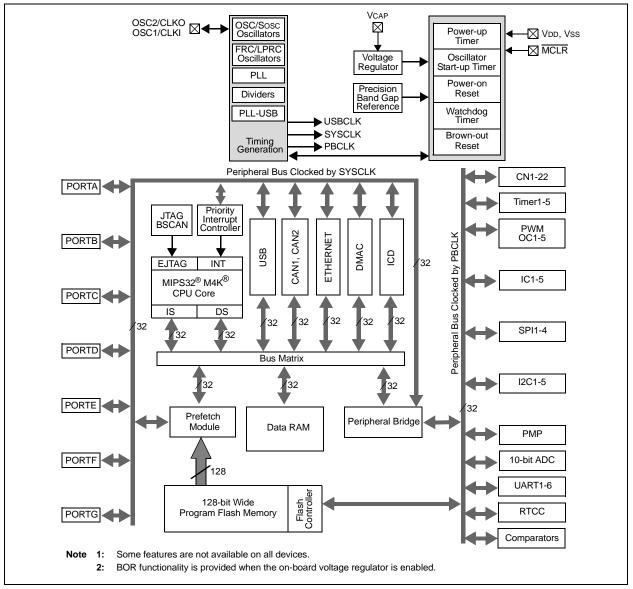

FIGURE 1-1: BLOCK DIAGRAM<sup>(1,2)</sup>

This document contains device-specific information for PIC32MX5XX/6XX/7XX devices.

Figure 1-1 illustrates a general block diagram of the core and peripheral modules in the PIC32MX5XX/6XX/7XX family of devices.

Table 1-1 lists the functions of the various pins shown in the pinout diagrams.

## 2.0 GUIDELINES FOR GETTING STARTED WITH 32-BIT MCUS

**Note:** This data sheet summarizes the features of the PIC32MX5XX/6XX/7XX family of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to the related section of the *"PIC32 Family Reference Manual"*, which is available from the Microchip web site (www.microchip.com/PIC32).

## 2.1 Basic Connection Requirements

Getting started with the PIC32MX5XX/6XX/7XX family of 32-bit Microcontrollers (MCUs) requires attention to a minimal set of device pin connections before proceeding with development. The following is a list of pin names, which must always be connected:

- All VDD and Vss pins (see 2.2 "Decoupling Capacitors")

- All AVDD and AVss pins even if the ADC module is not used (see 2.2 "Decoupling Capacitors")

- VCAP pin (see 2.3 "Capacitor on Internal Voltage Regulator (VCAP)")

- MCLR pin (see 2.4 "Master Clear (MCLR) Pin")

- PGECx/PGEDx pins used for In-Circuit Serial Programming<sup>™</sup> (ICSP<sup>™</sup>) and debugging purposes (see **2.5** "ICSP Pins")

- OSC1 and OSC2 pins when external oscillator source is used (see 2.8 "External Oscillator Pins")

The following pin may be required, as well: VREF+/ VREF- pins used when external voltage reference for ADC module is implemented.

**Note:** The AVDD and AVSS pins must be connected, regardless of the ADC use and the ADC voltage reference source.

## 2.2 Decoupling Capacitors

The use of decoupling capacitors on power supply pins, such as VDD, VSS, AVDD and AVSS is required. See Figure 2-1.

Consider the following criteria when using decoupling capacitors:

- Value and type of capacitor: A value of 0.1  $\mu$ F (100 nF), 10-20V is recommended. The capacitor should be a low Equivalent Series Resistance (low-ESR) capacitor and have resonance frequency in the range of 20 MHz and higher. It is further recommended to use ceramic capacitors.

- Placement on the printed circuit board: The decoupling capacitors should be placed as close to the pins as possible. It is recommended that the capacitors be placed on the same side of the board as the device. If space is constricted, the capacitor can be placed on another layer on the PCB using a via; however, ensure that the trace length from the pin to the capacitor is within one-quarter inch (6 mm) in length.

- Handling high frequency noise: If the board is experiencing high frequency noise, upward of tens of MHz, add a second ceramic-type capacitor in parallel to the above described decoupling capacitor. The value of the second capacitor can be in the range of 0.01  $\mu$ F to 0.001  $\mu$ F. Place this second capacitor next to the primary decoupling capacitor. In high-speed circuit designs, consider implementing a decade pair of capacitances as close to the power and ground pins as possible. For example, 0.1  $\mu$ F in parallel with 0.001  $\mu$ F.

- Maximizing performance: On the board layout from the power supply circuit, run the power and return traces to the decoupling capacitors first, and then to the device pins. This ensures that the decoupling capacitors are first in the power chain. Equally important is to keep the trace length between the capacitor and the power pins to a minimum, thereby reducing PCB track inductance.

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |  |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|--|--|

| 31:24        | R/W-x             | R/W-x             | R/W-x             | R/W-x             | R/W-x             | R/W-x             | R/W-x            | R/W-x            |  |  |

| 31:24        | CHEW1<31:24>      |                   |                   |                   |                   |                   |                  |                  |  |  |

| 00.40        | R/W-x             | R/W-x             | R/W-x             | R/W-x             | R/W-x             | R/W-x             | R/W-x            | R/W-x            |  |  |

| 23:16        | CHEW1<23:16>      |                   |                   |                   |                   |                   |                  |                  |  |  |

| 45.0         | R/W-x             | R/W-x             | R/W-x             | R/W-x             | R/W-x             | R/W-x             | R/W-x            | R/W-x            |  |  |

| 15:8         | CHEW1<15:8>       |                   |                   |                   |                   |                   |                  |                  |  |  |

| 7.0          | R/W-x             | R/W-x             | R/W-x             | R/W-x             | R/W-x             | R/W-x             | R/W-x            | R/W-x            |  |  |

| 7:0          | CHEW1<7:0>        |                   |                   |                   |                   |                   |                  |                  |  |  |

## REGISTER 9-6: CHEW1: CACHE WORD 1

| Legend:           |                  |                           |                    |

|-------------------|------------------|---------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, re | ead as '0'         |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared      | x = Bit is unknown |

bit 31-0 **CHEW1<31:0>:** Word 1 of the cache line selected by CHEIDX<3:0> bits (CHEACC<3:0>) Readable only if the device is not code-protected.

## REGISTER 9-7: CHEW2: CACHE WORD 2

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |  |  |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|--|--|--|

| 31:24        | R/W-x             | R/W-x             | R/W-x             | R/W-x             | R/W-x             | R/W-x             | R/W-x            | R/W-x            |  |  |  |

| 31:24        |                   | CHEW2<31:24>      |                   |                   |                   |                   |                  |                  |  |  |  |

| 00.40        | R/W-x             | R/W-x             | R/W-x             | R/W-x             | R/W-x             | R/W-x             | R/W-x            | R/W-x            |  |  |  |

| 23:16        | CHEW2<23:16>      |                   |                   |                   |                   |                   |                  |                  |  |  |  |

| 45.0         | R/W-x             | R/W-x             | R/W-x             | R/W-x             | R/W-x             | R/W-x             | R/W-x            | R/W-x            |  |  |  |

| 15:8         | CHEW2<15:8>       |                   |                   |                   |                   |                   |                  |                  |  |  |  |

| 7.0          | R/W-x             | R/W-x             | R/W-x             | R/W-x             | R/W-x             | R/W-x             | R/W-x            | R/W-x            |  |  |  |

| 7:0          |                   | CHEW2<7:0>        |                   |                   |                   |                   |                  |                  |  |  |  |

| Legend:           |                  |                          |                    |

|-------------------|------------------|--------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, r | ead as '0'         |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared     | x = Bit is unknown |

bit 31-0 **CHEW2<31:0>:** Word 2 of the cache line selected by CHEIDX<3:0> bits (CHEACC<3:0>) Readable only if the device is not code-protected.

## TABLE 10-3: DMA CHANNELS 0-7 REGISTER MAP

| ess                             |                                 |               |             |       |       |       |        |       |      | Bi     | its     |        |        |        |         |        |        |        |            |

|---------------------------------|---------------------------------|---------------|-------------|-------|-------|-------|--------|-------|------|--------|---------|--------|--------|--------|---------|--------|--------|--------|------------|

| Virtual Address<br>(BF88_#)     | Register<br>Name <sup>(1)</sup> | Bit Range     | 31/15       | 30/14 | 29/13 | 28/12 | 27/11  | 26/10 | 25/9 | 24/8   | 23/7    | 22/6   | 21/5   | 20/4   | 19/3    | 18/2   | 17/1   | 16/0   | All Resets |

| 3060                            | DCH0CON                         | 31:16         | _           |       | _     | _     | —      | _     | —    | _      | —       | _      | —      | —      | —       | _      | _      | _      | 0000       |

| 3000                            | DCHUCON                         | 15:0          | CHBUSY      |       | —     | —     | _      | _     | —    | CHCHNS | CHEN    | CHAED  | CHCHN  | CHAEN  | —       | CHEDET | CHPR   | l<1:0> | 0000       |

| 3070                            | DCH0ECON                        | 31:16         | —           | —     | —     | —     | —      | —     |      | —      |         |        | 1      | CHAIR  |         |        |        |        | 00FF       |

| 00.0                            | 5011020011                      | 15:0          |             |       |       | CHSIR | Q<7:0> | -     |      |        | CFORCE  | CABORT | PATEN  | SIRQEN | AIRQEN  | —      | _      | —      | FF00       |

| 3080                            | DCH0INT                         | 31:16         | -           | _     | —     | —     | —      | —     | —    | —      | CHSDIE  | CHSHIE | CHDDIE | CHDHIE | CHBCIE  | CHCCIE | CHTAIE | CHERIE | 0000       |

| 0000                            | 20110111                        | 15:0          | —           | -     | -     | -     | —      | —     | —    | —      | CHSDIF  | CHSHIF | CHDDIF | CHDHIF | CHBCIF  | CHCCIF | CHTAIF | CHERIF | 0000       |

| 3090                            | DCH0SSA                         | 31:16<br>15:0 |             |       |       |       |        |       |      | CHSSA  | <31:0>  |        |        |        |         |        |        |        | 0000       |

| 30A0                            | DCH0DSA                         | 31:16<br>15:0 |             |       |       |       |        |       |      | CHDSA  | A<31:0> |        |        |        |         |        |        |        | 0000       |

|                                 |                                 | 31:16         | _           | _     |       | _     | _      | _     |      | _      |         | _      | _      | _      |         |        | _      | _      | 0000       |

| 30B0                            | DCH0SSIZ                        | 15:0          |             |       |       |       |        |       |      | CHSSIZ | 7<15:0> |        |        |        |         |        |        |        | 0000       |

|                                 |                                 | 31:16         | _           | _     | _     | _     | _      | _     |      | _      | _       | _      | _      | _      |         | _      | _      | _      | 0000       |

| 30C0                            | 0 DCH0DSIZ CHDSIZ<15:0>         |               |             |       |       |       |        |       |      | 0000   |         |        |        |        |         |        |        |        |            |

|                                 |                                 | 31:16         | _           | _     | _     | _     | _      | _     |      | _      | _       | _      | _      | _      | _       | _      | _      | _      | 0000       |

| 30D0 DCH0SPTR 15:0 CHSPTR<15:0> |                                 |               |             |       |       |       |        | 0000  |      |        |         |        |        |        |         |        |        |        |            |

|                                 |                                 |               |             |       |       |       |        | —     | 0000 |        |         |        |        |        |         |        |        |        |            |

| 30E0                            | DCH0DPTR                        | 15:0          |             |       | •     |       |        |       |      | CHDPT  | R<15:0> | •      |        |        |         |        |        |        | 0000       |

| 2050                            | DCH0CSIZ                        | 31:16         | —           | _     | —     | —     | _      | _     | —    | —      | —       | —      | _      | —      | —       | —      | —      | _      | 0000       |

| 30F0                            | DCHUCSIZ                        | 15:0          |             |       |       |       |        |       |      | CHCSIZ | Z<15:0> |        |        |        |         |        |        |        | 0000       |

| 3100                            | DCH0CPTR                        | 31:16         | —           | _     | —     | —     | —      | —     | —    | —      | —       | —      | —      | —      | —       | —      | _      | —      | 0000       |

| 3100                            | DCHOCI III                      | 15:0          |             |       |       |       |        |       | -    | CHCPT  | R<15:0> |        |        |        | -       |        |        |        | 0000       |

| 3110                            | DCH0DAT                         | 31:16         | —           | —     | —     | —     | —      | —     | —    | —      | —       | —      | —      | —      | —       | —      | —      | —      | 0000       |

| 5110                            | DOI IODAI                       | 15:0          | —           | -     | —     | —     | —      | —     | —    | —      |         |        |        | CHPDA  | AT<7:0> |        |        |        | 0000       |

| 3120                            | DCH1CON                         | 31:16         | -           | _     | —     | —     | —      | —     | —    | —      | _       | —      | —      | —      | —       | —      | —      | —      | 0000       |

| 0.20                            | 50                              | 15:0          | CHBUSY      | _     | _     |       | _      | _     |      | CHCHNS | CHEN    | CHAED  | CHCHN  | CHAEN  | —       | CHEDET | CHPR   | l<1:0> | 0000       |

| 3130                            | DCH1ECON                        | 31:16         | —           | —     | —     | —     | —      | —     |      | —      |         | 1      |        | CHAIR  |         |        |        |        | 00FF       |

|                                 |                                 | 15:0          |             |       | -     |       | Q<7:0> |       |      | -      | CFORCE  | CABORT | PATEN  | SIRQEN | AIRQEN  | —      | —      | —      | FF00       |

| 3140                            | DCH1INT                         | 31:16         | -           |       | _     |       | _      | -     | _    |        | CHSDIE  | CHSHIE | CHDDIE | CHDHIE | CHBCIE  | CHCCIE | CHTAIE | CHERIE | 0000       |

| -                               |                                 | 15:0          |             | —     | —     | _     | —      | —     | _    | —      | CHSDIF  | CHSHIF | CHDDIF | CHDHIF | CHBCIF  | CHCCIF | CHTAIF | CHERIF | 0000       |

| 3150                            | DCH1SSA                         | 31:16<br>15:0 | CHSSA<31:0> |       |       |       |        |       |      |        | 0000    |        |        |        |         |        |        |        |            |

| 3160                            | DCH1DSA                         | 31:16<br>15:0 |             |       |       |       |        |       |      | CHDSA  | <31:0>  |        |        |        |         |        |        |        | 0000       |

| 3170                            | DCH1SSIZ                        | 31:16         | _           | _     | _     | —     | —      | —     | —    | —      | —       | —      | —      | _      | —       | —      | _      | _      | 0000       |

| 5.70                            | 20110012                        | 15:0          |             |       |       |       |        |       |      | CHSSIZ | Z<15:0> |        |        |        |         |        |        |        | 0000       |

All registers in this table have corresponding CLR, SET and INV registers at their virtual addresses, plus offsets of 0x4, 0x8 and 0xC, respectively. See Section 12.1.1 "CLR, SET and INV Registers" for more Note 1: information.

PIC32MX5XX/6XX/7XX

2: DMA channels 4-7 are not available on PIC32MX534/564/664/764 devices.

## 11.0 USB ON-THE-GO (OTG)

Note: This data sheet summarizes the features of the PIC32MX5XX/6XX/7XX family of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to Section 27. "USB On-The-Go (OTG)" (DS60001126) in the "PIC32 Family Reference Manual", which is available from the Microchip web site (www.microchip.com/PIC32).

The Universal Serial Bus (USB) module contains analog and digital components to provide a USB 2.0 full-speed and low-speed embedded Host, full-speed Device or OTG implementation with a minimum of external components. This module in Host mode is intended for use as an embedded host and therefore does not implement a UHCI or OHCI controller.

The USB module consists of the clock generator, the USB voltage comparators, the transceiver, the Serial Interface Engine (SIE), a dedicated USB DMA controller, pull-up and pull-down resistors, and the register interface. A block diagram of the PIC32 USB OTG module is presented in Figure 11-1.

The clock generator provides the 48 MHz clock required for USB full-speed and low-speed communication. The voltage comparators monitor the voltage on the VBUS pin to determine the state of the bus. The transceiver provides the analog translation between the USB bus and the digital logic. The SIE is a state machine that transfers data to and from the endpoint buffers and generates the hardware protocol for data transfers. The USB DMA controller transfers data between the data buffers in RAM and the SIE. The integrated pull-up and pull-down resistors eliminate the need for external signaling components. The register interface allows the CPU to configure and communicate with the module.

The USB module includes the following features:

- USB Full-speed support for host and device

- Low-speed host support

- USB OTG support

- Integrated signaling resistors

- Integrated analog comparators for VBUS monitoring

- Integrated USB transceiver

- Transaction handshaking performed by hardware

- Endpoint buffering anywhere in system RAM

- Integrated DMA to access system RAM and Flash

- The implementation and use of the USB Note: specifications, as well as other third party may specifications or technologies, require licensing; including, but not limited to, USB Implementers Forum, Inc. (also referred to as USB-IF). The user is fully responsible for investigating and satisfying any applicable licensing obligations.

# PIC32MX5XX/6XX/7XX

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |  |  |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|--|--|--|

| 31:24        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |  |  |  |

| 31.24        | -                 | —                 | _                 | -                 | _                 | _                 | -                | —                |  |  |  |

| 23:16        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |  |  |  |

| 23.10        | -                 | —                 | _                 | -                 | _                 | _                 | -                | —                |  |  |  |

| 15:8         | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |  |  |  |

| 15.6         |                   | _                 |                   |                   |                   |                   |                  | —                |  |  |  |

| 7:0          | R-0               | U-0               | R-0               | U-0               | R-0               | R-0               | U-0              | R-0              |  |  |  |

| 7.0          | ID                | _                 | LSTATE            |                   | SESVD             | SESEND            |                  | VBUSVD           |  |  |  |

## REGISTER 11-3: U10TGSTAT: USB OTG STATUS REGISTER

## Legend:

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, r | ead as '0'         |  |

|-------------------|------------------|--------------------------|--------------------|--|

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared     | x = Bit is unknown |  |

## bit 31-8 Unimplemented: Read as '0'

- bit 7 ID: ID Pin State Indicator bit

- 1 = No cable is attached or a "type B" cable has been inserted into the USB receptacle

- 0 = A "type A" OTG cable has been inserted into the USB receptacle

- bit 6 Unimplemented: Read as '0'

- bit 5 LSTATE: Line State Stable Indicator bit

- 1 = USB line state (SE0 (U1CON<6> and JSTATE (U1CON<7>) has been stable for the previous 1 ms

- 0 = USB line state (SE0 (U1CON<6> and JSTATE (U1CON<7>) has not been stable for the previous 1 ms

#### bit 4 Unimplemented: Read as '0'

- bit 3 SESVD: Session Valid Indicator bit

- 1 = VBUS voltage is above Session Valid on the A or B device

- 0 = VBUS voltage is below Session Valid on the A or B device

- bit 2 SESEND: B-Device Session End Indicator bit

- 1 = VBUS voltage is below Session Valid on the B device

- 0 = VBUS voltage is above Session Valid on the B device

#### bit 1 Unimplemented: Read as '0'

- bit 0 VBUSVD: A-Device VBUS Valid Indicator bit

- 1 = VBUS voltage is above Session Valid on the A device

- 0 = VBUS voltage is below Session Valid on the A device

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|

| 24.24        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 31:24        | _                 | _                 |                   | _                 |                   |                   | —                | —                |

| 23:16        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 23.10        | _                 | -                 | _                 | _                 |                   | _                 | —                | _                |

| 15:8         | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 15.0         | _                 | -                 | _                 | _                 |                   | _                 | —                | _                |

| 7.0          | R-0               | U-0               | U-0               | R/W-0             | R/W-0             | U-0               | R/W-0            | R/W-0            |

| 7:0          | UACTPND           | _                 |                   | USLPGRD           | USBBUSY           |                   | USUSPEND         | USBPWR           |

## REGISTER 11-5: U1PWRC: USB POWER CONTROL REGISTER

## Legend:

| Logona.           |                  |                                    |                    |  |  |  |

|-------------------|------------------|------------------------------------|--------------------|--|--|--|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read as '0' |                    |  |  |  |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared               | x = Bit is unknown |  |  |  |

### bit 31-8 Unimplemented: Read as '0'

- bit 7 UACTPND: USB Activity Pending bit

- 1 = USB bus activity has been detected; but an interrupt is pending, it has not been generated yet

- 0 = An interrupt is not pending

#### bit 6-5 Unimplemented: Read as '0'

- bit 4 USLPGRD: USB Sleep Entry Guard bit

- 1 = Sleep entry is blocked if USB bus activity is detected or if a notification is pending

- 0 = USB module does not block Sleep entry

#### bit 3 USBBUSY: USB Module Busy bit

- 1 = USB module is active or disabled, but not ready to be enabled

- 0 = USB module is not active and is ready to be enabled

- **Note:** When USBPWR = 0 and USBBUSY = 1, status from all other registers is invalid and writes to all USB module registers produce undefined results.

#### bit 2 Unimplemented: Read as '0'

## bit 1 USUSPEND: USB Suspend Mode bit

- 1 = USB module is placed in Suspend mode

- (The 48 MHz USB clock will be gated off. The transceiver is placed in a low-power state.)

- 0 = USB module operates normally

- bit 0 USBPWR: USB Operation Enable bit

- 1 = USB module is turned on

- 0 = USB module is disabled

(Outputs held inactive, device pins not used by USB, analog features are shut down to reduce power consumption.)

# PIC32MX5XX/6XX/7XX

## REGISTER 11-7: U1IE: USB INTERRUPT ENABLE REGISTER

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1      | Bit<br>24/16/8/0        |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|-----------------------|-------------------------|

| 31:24        | U-0                   | U-0                     |

|              | —                 | —                 | —                 | —                 | _                 | —                 | _                     |                         |

| 23:16        | U-0                   | U-0                     |

| 23.10        | —                 | —                 | —                 | —                 | _                 | —                 | _                     |                         |

| 15:8         | U-0                   | U-0                     |

| 15.6         | —                 | —                 | —                 | —                 | _                 | —                 | _                     |                         |

|              | R/W-0                 | R/W-0                   |

| 7:0          | STALLE            |                   | RESUMEIE          | IDLEIE            | TRNIE             | SOFIE             | UERRIE <sup>(1)</sup> | URSTIE <sup>(2)</sup>   |

|              | STALLIE           | ATTACHIE          | RESUMEIE          | IDLEIE            | IRNE              | SOFIE             | UERRIE                | DETACHIE <sup>(3)</sup> |

## Legend:

| R = Readable bit  | adable bit W = Writable bit |                      | read as '0'        |

|-------------------|-----------------------------|----------------------|--------------------|

| -n = Value at POR | '1' = Bit is set            | '0' = Bit is cleared | x = Bit is unknown |

## bit 31-8 Unimplemented: Read as '0'

|       | •·····                                                          |

|-------|-----------------------------------------------------------------|

| bit 7 | STALLIE: STALL Handshake Interrupt Enable bit                   |

|       | 1 = STALL interrupt is enabled                                  |

|       | 0 = STALL interrupt is disabled                                 |

| bit 6 | ATTACHIE: ATTACH Interrupt Enable bit                           |

|       | 1 = ATTACH interrupt is enabled                                 |

|       | 0 = ATTACH interrupt is disabled                                |

| bit 5 | RESUMEIE: RESUME Interrupt Enable bit                           |

|       | 1 = RESUME interrupt is enabled                                 |

|       | 0 = RESUME interrupt is disabled                                |

| bit 4 | IDLEIE: Idle Detect Interrupt Enable bit                        |

|       | 1 = Idle interrupt is enabled                                   |

|       | 0 = Idle interrupt is disabled                                  |

| bit 3 | TRNIE: Token Processing Complete Interrupt Enable bit           |

|       | 1 = TRNIF interrupt is enabled                                  |

|       | 0 = TRNIF interrupt is disabled                                 |

| bit 2 | SOFIE: SOF Token Interrupt Enable bit                           |

|       | 1 = SOFIF interrupt is enabled                                  |

|       | 0 = SOFIF interrupt is disabled                                 |

| bit 1 | UERRIE: USB Error Interrupt Enable bit <sup>(1)</sup>           |

|       | 1 = USB Error interrupt is enabled                              |

|       | 0 = USB Error interrupt is disabled                             |

| bit 0 | URSTIE: USB Reset Interrupt Enable bit <sup>(2)</sup>           |

|       | 1 = URSTIF interrupt is enabled                                 |

|       | 0 = URSTIF interrupt is disabled                                |

|       | <b>DETACHIE:</b> USB Detach Interrupt Enable bit <sup>(3)</sup> |

|       | 1 = DATTCHIF interrupt is enabled                               |

|       | 0 = DATTCHIF interrupt is disabled                              |

|       |                                                                 |

**Note 1:** For an interrupt to propagate USBIF, the UERRIE bit (U1IE<1>) must be set.

- 2: Device mode.

- 3: Host mode.

# PIC32MX5XX/6XX/7XX

## REGISTER 11-12: U1ADDR: USB ADDRESS REGISTER

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|

| 31:24        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 51.24        | _                 | _                 | -                 |                   | _                 | -                 |                  | —                |

| 22:46        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 23:16        |                   | -                 |                   |                   |                   |                   |                  | —                |

| 15:8         | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 15.6         | —                 | _                 |                   |                   | _                 |                   |                  | —                |

| 7:0          | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |

| 7.0          | LSPDEN            |                   |                   | D                 | EVADDR<6:0        | >                 |                  |                  |

### Legend:

| R = Readable bit  | W = Writable bit | U = Unimplemented bit | , read as '0'      |  |

|-------------------|------------------|-----------------------|--------------------|--|

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared  | x = Bit is unknown |  |

### bit 31-8 Unimplemented: Read as '0'

- bit 7 **LSPDEN:** Low-Speed Enable Indicator bit

- 1 = Next token command to be executed at low-speed

- 0 = Next token command to be executed at full-speed

- bit 6-0 DEVADDR<6:0>: 7-bit USB Device Address bits

## REGISTER 11-13: U1FRML: USB FRAME NUMBER LOW REGISTER

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|

| 24.24        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 31:24        | -                 | -                 |                   | —                 |                   |                   |                  | -                |

| 23:16        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 23.10        | -                 | -                 |                   | —                 |                   |                   |                  | -                |

| 15.0         | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 15:8         | _                 | _                 | —                 | —                 | -                 | _                 |                  | _                |

| 7.0          | R-0               | R-0               | R-0               | R-0               | R-0               | R-0               | R-0              | R-0              |

| 7:0          |                   |                   |                   | FRML              | .<7:0>            |                   |                  |                  |

| Legend:           |                  |                          |                    |

|-------------------|------------------|--------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, r | read as '0'        |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared     | x = Bit is unknown |

## bit 31-8 Unimplemented: Read as '0'

bit 7-0 **FRML<7:0>:** 11-bit Frame Number Lower bits The register bits are updated with the current frame number whenever a SOF TOKEN is received.

## 19.0 INTER-INTEGRATED CIRCUIT (I<sup>2</sup>C)

Note: This data sheet summarizes the features of the PIC32MX5XX/6XX/7XX family of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to Section 24. "Inter-Integrated Circuit (I<sup>2</sup>C)" (DS60001116) in the "*PIC32 Family Reference Manual*", which is available from the Microchip web site (www.microchip.com/PIC32). The  $l^2C$  module provides complete hardware support for both Slave and Multi-Master modes of the  $l^2C$  serial communication standard. Figure 19-1 illustrates the  $l^2C$  module block diagram.

Each  $I^2C$  module has a 2-pin interface: the SCLx pin is clock and the SDAx pin is data.

Each I<sup>2</sup>C module offers the following key features:

- I<sup>2</sup>C interface supporting both master and slave operation

- I<sup>2</sup>C Slave mode supports 7-bit and 10-bit addressing

- I<sup>2</sup>C Master mode supports 7-bit and 10-bit addressing

- I<sup>2</sup>C port allows bidirectional transfers between master and slaves

- Serial clock synchronization for the I<sup>2</sup>C port can be used as a handshake mechanism to suspend and resume serial transfer (SCLREL control)

- I<sup>2</sup>C supports multi-master operation; detects bus collision and arbitrates accordingly

- Provides support for address bit masking

## REGISTER 21-1: PMCON: PARALLEL PORT CONTROL REGISTER (CONTINUED)

- bit 3 **CS1P:** Chip Select 0 Polarity bit<sup>(2)</sup>

- 1 = Active-high (PMCS1)

- $0 = \text{Active-low}(\overline{\text{PMCS1}})$

- bit 2 Unimplemented: Read as '0'

- bit 1 WRSP: Write Strobe Polarity bit

- For Slave Modes and Master mode 2 (PMMODE<9:8> = 00,01,10):

- 1 = Write strobe active-high (PMWR)

- $0 = Write strobe active-low (\overline{PMWR})$

For Master mode 1 (PMMODE<9:8> = 11):

- 1 = Enable strobe active-high (PMENB)

- 0 = Enable strobe active-low (PMENB)

- bit 0 RDSP: Read Strobe Polarity bit

- For Slave modes and Master mode 2 (PMMODE<9:8> = 00,01,10):

- 1 = Read Strobe active-high (PMRD)

- 0 = Read Strobe active-low (PMRD)

For Master mode 1 (PMMODE<9:8> = 11):

- 1 = Read/write strobe active-high (PMRD/ $\overline{PMWR}$ )

- 0 = Read/write strobe active-low (PMRD/PMWR)

- **Note 1:** When using the 1:1 PBCLK divisor, the user's software should not read/write the peripheral's SFRs in the SYSCLK cycle immediately following the instruction that clears the module's ON control bit.

- 2: These bits have no effect when their corresponding pins are used as address lines.

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|

| 24.24        | U-0               | U-0               | U-0               | U-0               | S/HC-0            | R/W-1             | R/W-0            | R/W-0            |

| 31:24        | —                 | —                 | _                 | -                 | ABAT              | F                 | REQOP<2:0>       | >                |

| 22:16        | R-1               | R-0               | R-0               | R/W-0             | U-0               | U-0               | U-0              | U-0              |

| 23:16        | C                 | OPMOD<2:0>        |                   | CANCAP            | —                 | _                 | —                | —                |

| 45.0         | R/W-0             | U-0               | R/W-0             | U-0               | R-0               | U-0               | U-0              | U-0              |

| 15:8         | ON <sup>(1)</sup> | —                 | SIDLE             | -                 | CANBUSY           | _                 | —                | —                |

| 7.0          | U-0               | U-0               | U-0               | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |

| 7:0          |                   | _                 | _                 |                   |                   | DNCNT<4:0>        |                  |                  |

## REGISTER 24-1: CICON: CAN MODULE CONTROL REGISTER

| Legend: HC = Hardware Clear |                  | S = Settable bit          |                    |  |

|-----------------------------|------------------|---------------------------|--------------------|--|

| R = Readable bit            | W = Writable bit | U = Unimplemented bit, re | ead as '0'         |  |

| -n = Value at POR           | '1' = Bit is set | '0' = Bit is cleared      | x = Bit is unknown |  |

## bit 31-28 Unimplemented: Read as '0'

- bit 27 **ABAT:** Abort All Pending Transmissions bit

- 1 = Signal all transmit buffers to abort transmission

- 0 = Module will clear this bit when all transmissions aborted

#### bit 26-24 REQOP<2:0>: Request Operation Mode bits

- 111 = Set Listen All Messages mode

- 110 = Reserved

- 101 = Reserved

- 100 = Set Configuration mode

- 011 = Set Listen Only mode

- 010 = Set Loopback mode

- 001 = Set Disable mode

- 000 = Set Normal Operation mode

#### bit 23-21 OPMOD<2:0>: Operation Mode Status bits

- 111 = Module is in Listen All Messages mode

- 110 = Reserved

- 101 = Reserved

- 100 = Module is in Configuration mode

- 011 = Module is in Listen Only mode

- 010 = Module is in Loopback mode

- 001 = Module is in Disable mode

- 000 = Module is in Normal Operation mode

## bit 20 CANCAP: CAN Message Receive Time Stamp Timer Capture Enable bit

- 1 = CANTMR value is stored on valid message reception and is stored with the message

- 0 = Disable CAN message receive time stamp timer capture and stop CANTMR to conserve power

- bit 19-16 Unimplemented: Read as '0'

- bit 15 ON: CAN On bit<sup>(1)</sup>

- 1 = CAN module is enabled

- 0 = CAN module is disabled

- bit 14 Unimplemented: Read as '0'

- **Note 1:** If the user application clears this bit, it may take a number of cycles before the CAN module completes the current transaction and responds to this request. The user application should poll the CANBUSY bit to verify that the request has been honored.

## PIC32MX5XX/6XX/7XX

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|

| 31:24        | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |

| 31.24        |                   |                   |                   | HT<3              | 1:24>             |                   |                  |                  |

| 22.10        | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |

| 23:16        |                   |                   |                   | HT<2              | 3:16>             |                   |                  |                  |

| 45.0         | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |

| 15:8         |                   |                   |                   | HT<1              | 5:8>              |                   |                  |                  |

| 7.0          | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |

| 7:0          |                   |                   |                   | HT<               | 7:0>              |                   |                  |                  |

## REGISTER 25-5: ETHHT0: ETHERNET CONTROLLER HASH TABLE 0 REGISTER

| Legend:           |                  |                           |                    |

|-------------------|------------------|---------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, re | ead as '0'         |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared      | x = Bit is unknown |

bit 31-0 HT<31:0>: Hash Table Bytes 0-3 bits

Note 1: This register is only used for RX operations.

2: The bits in this register may only be changed while the RXEN bit (ETHCON1<8>) = 0 or the HTEN bit (ETHRXFC<15>) = 0.

## REGISTER 25-6: ETHHT1: ETHERNET CONTROLLER HASH TABLE 1 REGISTER

| Bit Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

|-----------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|

| 04.04     | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |

| 31:24     |                   |                   |                   | HT<6              | 3:56>             |                   |                  |                  |

| 00.40     | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |

| 23:16     |                   |                   |                   | HT<5              | 5:48>             |                   |                  |                  |

| 45.0      | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |

| 15:8      |                   |                   |                   | HT<4              | 7:40>             |                   |                  |                  |

| 7.0       | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |

| 7:0       |                   |                   |                   | HT<3              | 9:32>             |                   |                  |                  |

| Legend:           |                  |                          |                    |

|-------------------|------------------|--------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, I | ead as '0'         |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared     | x = Bit is unknown |

## bit 31-0 HT<63:32>: Hash Table Bytes 4-7 bits

Note 1: This register is only used for RX operations.

2: The bits in this register may only be changed while the RXEN bit (ETHCON1<8>) = 0 or the HTEN bit (ETHRXFC<15>) = 0.

| Bit Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

|-----------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|

| 31:24     | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 31.24     | —                 | —                 |                   | —                 |                   | —                 |                  | _                |

| 23:16     | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |

| 23.10     |                   |                   |                   | RXFW              | M<7:0>            |                   |                  |                  |

| 15:8      | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 15.0      | —                 | —                 |                   | —                 |                   | —                 |                  | _                |

| 7:0       | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |

| 7.0       |                   |                   |                   | RXEW              | M<7:0>            |                   |                  |                  |

## REGISTER 25-12: ETHRXWM: ETHERNET CONTROLLER RECEIVE WATERMARKS REGISTER

## Legend:

| Legena.           |                  |                        |                    |

|-------------------|------------------|------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, | read as '0'        |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared   | x = Bit is unknown |

- bit 31-24 Unimplemented: Read as '0'

- bit 23-16 **RXFWM<7:0>:** Receive Full Watermark bits

The software controlled RX Buffer Full Watermark Pointer is compared against the RX BUFCNT to determine the full watermark condition for the FWMARK interrupt and for enabling Flow Control when automatic Flow Control is enabled. The Full Watermark Pointer should always be greater than the Empty Watermark Pointer.

- bit 15-8 Unimplemented: Read as '0'

- bit 7-0 **RXEWM<7:0>:** Receive Empty Watermark bits

The software controlled RX Buffer Empty Watermark Pointer is compared against the RX BUFCNT to determine the empty watermark condition for the EWMARK interrupt and for disabling Flow Control when automatic Flow Control is enabled. The Empty Watermark Pointer should always be less than the Full Watermark Pointer.

Note: This register is only used for RX operations.

## REGISTER 25-20: ETHFRMRXOK: ETHERNET CONTROLLER FRAMES RECEIVED OK STATISTICS REGISTER

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|

| 24.24        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 31:24        | _                 | _                 | _                 | _                 | _                 | _                 | _                | 24/16/8/0        |

| 00.40        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 23:16        | _                 | _                 | _                 | _                 | _                 | _                 | _                | _                |

| 45.0         | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |

| 15:8         |                   |                   |                   | FRMRXOK           | CNT<15:8>         |                   |                  |                  |

| 7.0          | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |

| 7:0          |                   |                   |                   | FRMRXOK           | (CNT<7:0>         |                   |                  |                  |

## Legend:

| 3                 |                  |                        |                    |  |

|-------------------|------------------|------------------------|--------------------|--|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, | read as '0'        |  |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared   | x = Bit is unknown |  |

### bit 31-16 Unimplemented: Read as '0'

bit 15-0 FRMRXOKCNT<15:0>: Frames Received OK Count bits

Increment count for frames received successfully by the RX Filter. This count will not be incremented if there is a Frame Check Sequence (FCS) or Alignment error.

Note 1: This register is only used for RX operations.

- 2: This register is automatically cleared by hardware after a read operation, unless the byte enables for bytes 0/1 are '0'.

- **3:** It is recommended to use the SET, CLR, or INV registers to set or clear any bit in this register. Setting or clearing any bits in this register should only be done for debug/test purposes.

## REGISTER 25-27: EMAC1CLRT: ETHERNET CONTROLLER MAC COLLISION WINDOW/RETRY LIMIT REGISTER

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|

| 31:24        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 31.24        |                   | —                 |                   |                   |                   | —                 |                  | —                |

| 22.16        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 23:16        |                   | —                 |                   |                   |                   | —                 |                  | —                |

| 15:8         | U-0               | U-0               | R/W-1             | R/W-1             | R/W-0             | R/W-1             | R/W-1            | R/W-1            |

| 10.0         |                   | —                 |                   |                   | CWINDO            | W<5:0>            |                  |                  |

| 7:0          | U-0               | U-0               | U-0               | U-0               | R/W-1             | R/W-1             | R/W-1            | R/W-1            |

| 7.0          | _                 |                   | _                 | _                 |                   | RETX<             | <3:0>            |                  |

#### Legend:

| Logonal           |                  |                      |                    |

|-------------------|------------------|----------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented b  | it, read as '0'    |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared | x = Bit is unknown |

#### bit 31-14 Unimplemented: Read as '0'

bit 13-8 **CWINDOW<5:0>:** Collision Window bits

This is a programmable field representing the slot time or collision window during which collisions occur in properly configured networks. Since the collision window starts at the beginning of transmission, the preamble and SFD is included. Its default of 0x37 (55d) corresponds to the count of frame bytes at the end of the window.

bit 7-4 Unimplemented: Read as '0'

### bit 3-0 RETX<3:0>: Retransmission Maximum bits

This is a programmable field specifying the number of retransmission attempts following a collision before aborting the packet due to excessive collisions. The Standard specifies the maximum number of attempts (attemptLimit) to be 0xF (15d). Its default is '0xF'.

**Note:** Both 16-bit and 32-bit accesses are allowed to these registers (including the SET, CLR and INV registers). 8-bit accesses are not allowed and are ignored by the hardware.

## REGISTER 25-36: EMAC1MIND: ETHERNET CONTROLLER MAC MII MANAGEMENT INDICATORS REGISTER

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0                                        |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|---------------------------------------------------------|

| 31:24        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0                                                     |

| 31.24        |                   |                   | —                 | _                 | —                 | —                 | -                | —                                                       |

| 22.16        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0                                                     |

| 23:16        | —                 | —                 | —                 | _                 | _                 | —                 | —                | —                                                       |

| 15:8         | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0                                                     |

| 0.61         | —                 | —                 | —                 | _                 | _                 | —                 | —                | 24/16/8/0       U-0       —       U-0       —       U-0 |

| 7.0          | U-0               | U-0               | U-0               | U-0               | R/W-0             | R/W-0             | R/W-0            | R/W-0                                                   |

| 7:0          | _                 |                   | —                 |                   | LINKFAIL          | NOTVALID          | SCAN             | MIIMBUSY                                                |

## Legend:

| 5                 |                  |                          |                    | 1 |

|-------------------|------------------|--------------------------|--------------------|---|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, r | read as '0'        |   |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared     | x = Bit is unknown |   |

### bit 31-4 Unimplemented: Read as '0'

bit 3 LINKFAIL: Link Fail bit

When '1' is returned - indicates link fail has occurred. This bit reflects the value last read from the PHY status register.

bit 2 NOTVALID: MII Management Read Data Not Valid bit When '1' is returned - indicates an MII management read cycle has not completed and the Read Data is not yet valid.

## bit 1 SCAN: MII Management Scanning bit When '1' is returned - indicates a scan operation (continuous MII Management Read cycles) is in progress.

## bit 0 MIIMBUSY: MII Management Busy bit

When '1' is returned - indicates MII Management module is currently performing an MII Management Read or Write cycle.

**Note:** Both 16-bit and 32-bit accesses are allowed to these registers (including the SET, CLR and INV registers). 8-bit accesses are not allowed and are ignored by the hardware.

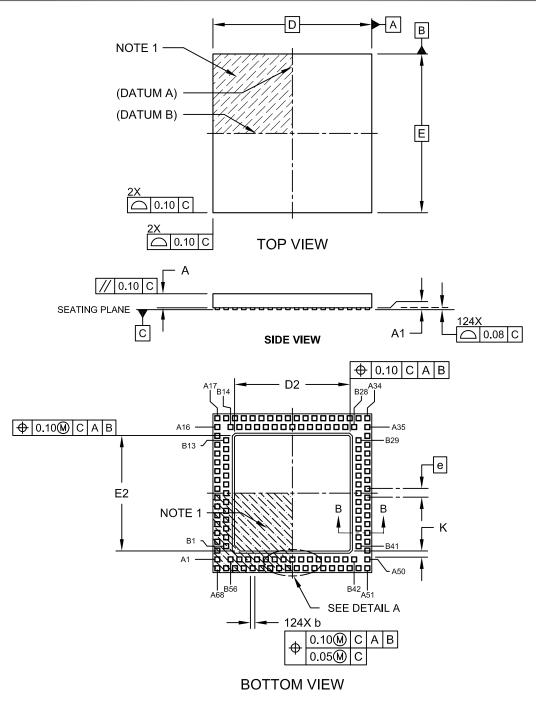

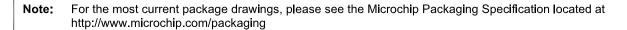

## 124-Terminal Very Thin Leadless Array Package (TL) – 9x9x0.9 mm Body [VTLA]

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

Microchip Technology Drawing C04-193A Sheet 1 of 2

## 124-Terminal Very Thin Leadless Array Package (TL) – 9x9x0.9 mm Body [VTLA]

|                                      | Units  |          |          | S    |

|--------------------------------------|--------|----------|----------|------|

| Dimension                            | Limits | MIN      | NOM      | MAX  |

| Number of Pins                       | N      |          | 124      |      |

| Pitch                                | еT     |          | 0.50 BSC |      |

| Pitch (Inner to outer terminal ring) | eR     |          | 0.50 BSC |      |

| Overall Height                       | A      | 0.80     | 0.85     | 0.90 |

| Standoff                             | A1     | 0.00     | -        | 0.05 |

| Overall Width                        | E      | 9.00 BSC |          |      |

| Exposed Pad Width                    | E2     | 6.40     | 6.55     | 6.70 |

| Overall Length                       | D      |          | 9.00 BSC |      |

| Exposed Pad Length                   | D2     | 6.40     | 6.55     | 6.70 |

| Contact Width                        | b      | 0.20     | 0.25     | 0.30 |

| Contact Length                       | L      | 0.20     | 0.25     | 0.30 |

| Contact-to-Exposed Pad               | K      | 0.20     | -        | -    |

Notes:

1. Pin 1 visual index feature may vary, but must be located within the hatched area.

2. Package is saw singulated.

3. Dimensioning and tolerancing per ASME Y14.5M.

BSC: Basic Dimension. Theoretically exact value shown without tolerances.

REF: Reference Dimension, usually without tolerance, for information purposes only.

Microchip Technology Drawing C04-193A Sheet 2 of 2

## TABLE B-4: SECTION UPDATES (CONTINUED)

| Section Name                                                 | Update Description                                                                                                                                                                            |

|--------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7.0 "Interrupt Controller"                                   | Updated the following Interrupt Sources in Table 7-1:                                                                                                                                         |

|                                                              | - Changed IC2AM – I2C4 Master Event to: IC4M – I2C4 Master Event                                                                                                                              |

|                                                              | - Changed IC3AM – I2C5 Master Event to: IC5M – I2C4 Master Event                                                                                                                              |

|                                                              | <ul> <li>Changed U1E – UART1A Error to: U1E – UART1 Error</li> </ul>                                                                                                                          |

|                                                              | - Changed U4E – UART1B Error to: U4E – UART4 Error                                                                                                                                            |

|                                                              | - Changed U1RX – UART1A Receiver to: U1RX – UART1 Receiver                                                                                                                                    |

|                                                              | <ul> <li>Changed U4RX – UART1B Receiver to: U4RX – UART4 Receiver</li> <li>Changed U1TX – UART1A Transmitter to: U1TX – UART1 Transmitter</li> </ul>                                          |

|                                                              | <ul> <li>Changed UTTX – UART1A Transmitter to: UTTX – UART4 Transmitter</li> <li>Changed U4TX – UART1B Transmitter to: U4TX – UART4 Transmitter</li> </ul>                                    |

|                                                              | <ul> <li>Changed U6E – UART2B Error to: U6E – UART6 Error</li> </ul>                                                                                                                          |

|                                                              | - Changed U6RX – UART2B Receiver to: U6RX – UART6 Receiver                                                                                                                                    |

|                                                              | - Changed U6TX – UART2B Transmitter to: U6TX – UART6 Transmitter                                                                                                                              |

|                                                              | <ul> <li>Changed U5E – UART3B Error to: U5E – UART5 Error</li> </ul>                                                                                                                          |

|                                                              | <ul> <li>Changed U5RX – UART3B Receiver to: U5RX – UART5 Receiver</li> </ul>                                                                                                                  |

|                                                              | - Changed U5TX – UART3B Transmitter to: U5TX – UART5 Transmitter                                                                                                                              |

| 1.0 "Oscillator Configuration"                               | Updated Figure 1-1                                                                                                                                                                            |

| 1.0 "Output Compare"                                         | Updated Figure 1-1                                                                                                                                                                            |

| 1.0 "Ethernet Controller"                                    | Added a note on using the Ethernet controller pins (see note above Table 1-3)                                                                                                                 |

| 1.0 "Comparator Voltage Reference<br>(CVREF)"                | Updated the note in Figure 1-1                                                                                                                                                                |

| 1.0 "Special Features"                                       | Updated the bit description for bit 10 in Register 1-2                                                                                                                                        |

|                                                              | Added notes 1 and 2 to Register 1-4                                                                                                                                                           |

| 1.0 "Electrical Characteristics"                             | Updated the Absolute Maximum Ratings:                                                                                                                                                         |

|                                                              | <ul> <li>Voltage on any 5V tolerant pin with respect to Vss when VDD &lt; 2.3V -<br/>0.3V to +3.6V was updated</li> </ul>                                                                     |

|                                                              | <ul> <li>Voltage on VBUS with respect to VSS - 0.3V to +5.5V was added</li> </ul>                                                                                                             |

|                                                              | Updated the maximum value of DC16 as 2.1 in Table 1-4                                                                                                                                         |

|                                                              | Updated the Typical values for the following parameters: DC20b, DC20c, DC21c, DC22c and DC23c (see Table 1-5)                                                                                 |

|                                                              | Updated Table 1-11:                                                                                                                                                                           |

|                                                              | <ul> <li>Removed the following DC Characteristics: Programming temperature<br/>0°C ≤ TA ≤ +70°C (25°C recommended)</li> </ul>                                                                 |

|                                                              | <ul> <li>Updated the Minimum value for the Parameter number D131 as 2.3</li> <li>Removed the Conditions for the following Parameter numbers: D130, D131, D132, D135, D136 and D137</li> </ul> |

|                                                              | Updated the condition for the parameter number D130a and D132a                                                                                                                                |

|                                                              | Updated the Minimum, Typical and Maximum values for parameter D305 in Table 1-13                                                                                                              |

|                                                              | Added note 2 to Table 1-18                                                                                                                                                                    |

|                                                              | Updated the Minimum and Maximum values for parameter F20b (see Table 1-19)                                                                                                                    |

|                                                              | Updated the following figures:                                                                                                                                                                |

|                                                              | • Figure 1-4                                                                                                                                                                                  |

|                                                              | • Figure 1-9                                                                                                                                                                                  |

|                                                              | • Figure 1-22                                                                                                                                                                                 |

|                                                              | • Figure 1-23                                                                                                                                                                                 |

| Appendix A: "Migrating from<br>PIC32MX3XX/4XX to PIC32MX5XX/ | Removed the A.3 Pin Assignments sub-section.                                                                                                                                                  |

| 6XX/7XX Devices"                                             |                                                                                                                                                                                               |