Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XE

| Product Status             | Active                                                                            |

|----------------------------|-----------------------------------------------------------------------------------|

| Core Processor             | MIPS32® M4K™                                                                      |

| Core Size                  | 32-Bit Single-Core                                                                |

| Speed                      | 80MHz                                                                             |

| Connectivity               | CANbus, Ethernet, I <sup>2</sup> C, SPI, UART/USART, USB OTG                      |

| Peripherals                | Brown-out Detect/Reset, DMA, POR, PWM, WDT                                        |

| Number of I/O              | 85                                                                                |

| Program Memory Size        | 512KB (512K x 8)                                                                  |

| Program Memory Type        | FLASH                                                                             |

| EEPROM Size                |                                                                                   |

| RAM Size                   | 64K x 8                                                                           |

| Voltage - Supply (Vcc/Vdd) | 2.3V ~ 3.6V                                                                       |

| Data Converters            | A/D 16x10b                                                                        |

| Oscillator Type            | Internal                                                                          |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                                 |

| Mounting Type              | Surface Mount                                                                     |

| Package / Case             | 100-TQFP                                                                          |

| Supplier Device Package    | 100-TQFP (12x12)                                                                  |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic32mx775f512lt-80i-pt |

|                            |                                                                                   |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

#### **TABLE 13:** PIN NAMES FOR 124-PIN USB, ETHERNET, AND CAN DEVICES (CONTINUED)

| 124               | 4-PIN VTLA (BOTTOM VIEW) <sup>(2,3)</sup>             |     |                   | A34                       |                           |  |

|-------------------|-------------------------------------------------------|-----|-------------------|---------------------------|---------------------------|--|

|                   |                                                       | B13 | B29               |                           | Conductive<br>Thermal Pad |  |

|                   | PIC32MX675F512L<br>PIC32MX695F512L<br>PIC32MX795F512L | B1  | B56               | B41                       | A51                       |  |

|                   | A1                                                    |     |                   |                           |                           |  |

|                   | Polarity Indicator                                    |     | A68               |                           |                           |  |

| Package<br>Bump # | Full Pin Name                                         |     | Package<br>Bump # | F                         | ull Pin Name              |  |

| B8                | Vss                                                   |     | B33               | TDO/RA5                   |                           |  |

| B9                | TMS/RA0                                               |     | B34               | OSC1/CLKI/RC              | 212                       |  |

| B10               | AERXD1/INT2/RE9                                       |     | B35               | No Connect (N             | C)                        |  |

| B11               | AN4/C1IN-/CN6/RB4                                     |     | B36               | AETXCLK/SCL               | .1/INT3/RA14              |  |

| B12               | Vss                                                   |     | B37               | RTCC/EMDIO/               | AEMDIO/IC1/RD8            |  |

| B13               | AN2/C2IN-/CN4/RB2                                     |     | B38               | SCK1/IC3/PMC              | CS2/PMA15/RD10            |  |

| B14               | PGED1/AN0/CN2/RB0                                     |     | B39               | SDO1/OC1/INT              | [0/RD0                    |  |

| B15               | No Connect (NC)                                       |     | B40               | SOSCO/T1CK/               | CN0/RC14                  |  |

| B16               | PGED2/AN7/RB7                                         |     | B41               | Vss                       |                           |  |

| B17               | VREF+/CVREF+/AERXD3/PMA6/RA10                         |     | B42               | OC3/RD2                   |                           |  |

| B18               | AVss                                                  |     | B43               | ETXD2/IC5/PN              | ID12/RD12                 |  |

| B19               | AN9/C2OUT/RB9                                         |     | B44               | OC5/PMWR/CI               | N13/RD4                   |  |

| B20               | AN11/ERXERR/AETXERR/PMA12/RB11                        |     | B45               | ETXEN/PMD14               | 4/CN15/RD6                |  |

| B21               | Vdd                                                   |     | B46               | Vss                       |                           |  |

| B22               | AC1TX/SCK4/U5TX/U2RTS/RF13                            |     | B47               | No Connect (N             | C)                        |  |

| B23               | AN12/ERXD0/AECRS/PMA11/RB12                           |     | B48               | VCAP                      |                           |  |

| B24               | AN14/ERXD2/AETXD3/PMALH/PMA1/RB14                     |     | B49               | C1RX <sup>(1)</sup> /ETXD | 1/PMD11/RF0               |  |

| B25               | Vss                                                   |     | B50               | C2TX <sup>(1)</sup> /ETXE | RR/PMD9/RG1               |  |

| B26               | AETXD0/SS3/U4RX/U1CTS/CN20/RD14                       |     | B51               | TRCLK/RA6                 |                           |  |

| B27               | SDA5/SDI4/U2RX/PMA9/CN17/RF4                          |     | B52               | PMD0/RE0                  |                           |  |

| B28               | No Connect (NC)                                       |     | B53               | Vdd                       |                           |  |

| B29               | SCL3/SDO3/U1TX/RF8                                    |     | B54               | TRD2/RG14                 |                           |  |

| B30               | VUSB3V3                                               |     | B55               | TRD0/RG13                 |                           |  |

| B31               | D+/RG2                                                |     | B56               | PMD3/RE3                  |                           |  |

This pin is only available on PIC32MX795F512L devices. Note 1:

2:

Shaded package bumps are 5V tolerant. It is recommended that the user connect the printed circuit board (PCB) ground to the conductive thermal pad on the bottom of the package. And to not run non-Vss PCB traces under the conductive thermal pad on the same side of the PCB layout. 3:

|         |                      | Pin Number <sup>(1)</sup> |                  |                 |             |                |                                   |  |  |

|---------|----------------------|---------------------------|------------------|-----------------|-------------|----------------|-----------------------------------|--|--|

| Pin Nam | e 64-Pin<br>QFN/TQFP | 100-Pin<br>TQFP           | 121-Pin<br>TFBGA | 124-pin<br>VTLA | Pin<br>Type | Buffer<br>Type | Description                       |  |  |

| RA0     | _                    | 17                        | G3               | B9              | I/O         | ST             | PORTA is a bidirectional I/O port |  |  |

| RA1     | —                    | 38                        | J6               | A26             | I/O         | ST             |                                   |  |  |

| RA2     | —                    | 58                        | H11              | A39             | I/O         | ST             |                                   |  |  |

| RA3     | —                    | 59                        | G10              | B32             | I/O         | ST             |                                   |  |  |

| RA4     | —                    | 60                        | G11              | A40             | I/O         | ST             |                                   |  |  |

| RA5     | —                    | 61                        | G9               | B33             | I/O         | ST             |                                   |  |  |

| RA6     | —                    | 91                        | C5               | B51             | I/O         | ST             |                                   |  |  |

| RA7     | —                    | 92                        | B5               | A62             | I/O         | ST             |                                   |  |  |

| RA9     | —                    | 28                        | L2               | A21             | I/O         | ST             |                                   |  |  |

| RA10    |                      | 29                        | K3               | B17             | I/O         | ST             | ]                                 |  |  |

| RA14    |                      | 66                        | E11              | B36             | I/O         | ST             | ]                                 |  |  |

| RA15    | —                    | 67                        | E8               | A44             | I/O         | ST             |                                   |  |  |

| RB0     | 16                   | 25                        | K2               | B14             | I/O         | ST             | PORTB is a bidirectional I/O port |  |  |

| RB1     | 15                   | 24                        | K1               | A15             | I/O         | ST             |                                   |  |  |

| RB2     | 14                   | 23                        | J2               | B13             | I/O         | ST             |                                   |  |  |

| RB3     | 13                   | 22                        | J1               | A13             | I/O         | ST             |                                   |  |  |

| RB4     | 12                   | 21                        | H2               | B11             | I/O         | ST             |                                   |  |  |

| RB5     | 11                   | 20                        | H1               | A12             | I/O         | ST             |                                   |  |  |

| RB6     | 17                   | 26                        | L1               | A20             | I/O         | ST             |                                   |  |  |

| RB7     | 18                   | 27                        | J3               | B16             | I/O         | ST             |                                   |  |  |

| RB8     | 21                   | 32                        | K4               | A23             | I/O         | ST             |                                   |  |  |

| RB9     | 22                   | 33                        | L4               | B19             | I/O         | ST             |                                   |  |  |

| RB10    | 23                   | 34                        | L5               | A24             | I/O         | ST             | 1                                 |  |  |

| RB11    | 24                   | 35                        | J5               | B20             | I/O         | ST             | ]                                 |  |  |

| RB12    | 27                   | 41                        | J7               | B23             | I/O         | ST             | ]                                 |  |  |

| RB13    | 28                   | 42                        | L7               | A28             | I/O         | ST             | ]                                 |  |  |

| RB14    | 29                   | 43                        | K7               | B24             | I/O         | ST             |                                   |  |  |

| RB15    | 30                   | 44                        | L8               | A29             | I/O         | ST             |                                   |  |  |

| RC1     | —                    | 6                         | D1               | A5              | I/O         | ST             | PORTC is a bidirectional I/O port |  |  |

| RC2     | —                    | 7                         | E4               | B4              | I/O         | ST             |                                   |  |  |

| RC3     | —                    | 8                         | E2               | A6              | I/O         | ST             |                                   |  |  |

| RC4     |                      | 9                         | E1               | B5              | I/O         | ST             | ]                                 |  |  |

| RC12    | 39                   | 63                        | F9               | B34             | I/O         | ST             | ]                                 |  |  |

| RC13    | 47                   | 73                        | C10              | A47             | I/O         | ST             | ]                                 |  |  |

| RC14    | 48                   | 74                        | B11              | B40             | I/O         | ST             | ]                                 |  |  |

|         | -                    | 64                        | F11              | A42             | I/O         | ST             | 1                                 |  |  |

TTL = TTL input buffer

Note 1: Pin numbers are only provided for reference. See the "Device Pin Tables" section for device pin availability.

2: See 25.0 "Ethernet Controller" for more information.

| AECRS  | 64-Pin<br>QFN/TQFP | 100-Pin                  |                                                      |                                                        | Pin  | Ruttor         |                                                                                    |

|--------|--------------------|--------------------------|------------------------------------------------------|--------------------------------------------------------|------|----------------|------------------------------------------------------------------------------------|

|        |                    | TQFP                     | 121-Pin<br>TFBGA                                     | 124-pin<br>VTLA                                        | Туре | Buffer<br>Type | Description                                                                        |

|        |                    | 41                       | J7                                                   | B23                                                    | I    | ST             | Alternate Ethernet carrier sense <sup>(2)</sup>                                    |

| AEMDC  | 30                 | 71                       | C11                                                  | A46                                                    | 0    |                | Alternate Ethernet Management Data clock <sup>(2)</sup>                            |

| AEMDIO | 49                 | 68                       | E9                                                   | B37                                                    | I/O  |                | Alternate Ethernet Management Data <sup>(2</sup>                                   |

| TRCLK  | _                  | 91                       | C5                                                   | B51                                                    | 0    |                | Trace clock                                                                        |

| TRD0   |                    | 97                       | A3                                                   | B55                                                    | 0    | _              | Trace Data bits 0-3                                                                |

| TRD1   | _                  | 96                       | C3                                                   | A65                                                    | 0    | _              |                                                                                    |

| TRD2   | _                  | 95                       | C4                                                   | B54                                                    | 0    | _              |                                                                                    |

| TRD3   | _                  | 92                       | B5                                                   | A62                                                    | 0    |                |                                                                                    |

| PGED1  | 16                 | 25                       | K2                                                   | B14                                                    | I/O  | ST             | Data I/O pin for Programming/<br>Debugging Communication Channel 1                 |

| PGEC1  | 15                 | 24                       | K1                                                   | A15                                                    | I    | ST             | Clock input pin for Programming/<br>Debugging Communication Channel 1              |

| PGED2  | 18                 | 27                       | J3                                                   | B16                                                    | I/O  | ST             | Data I/O pin for Programming/<br>Debugging Communication Channel 2                 |

| PGEC2  | 17                 | 26                       | L1                                                   | A20                                                    | Ι    | ST             | Clock input pin for Programming/<br>Debugging Communication Channel 2              |

| MCLR   | 7                  | 13                       | F1                                                   | B7                                                     | I/P  | ST             | Master Clear (Reset) input. This pin is an active-low Reset to the device.         |

| AVdd   | 19                 | 30                       | J4                                                   | A22                                                    | Р    | Р              | Positive supply for analog modules.<br>This pin must be connected at all times     |

| AVss   | 20                 | 31                       | L3                                                   | B18                                                    | Р    | Р              | Ground reference for analog modules                                                |

| Vdd    | 10, 26, 38,<br>57  | 2, 16, 37,<br>46, 62, 86 | A7, C2,<br>C9, E5,<br>K8, F8,<br>G5, H4,<br>H6       | A10, A14,<br>A30, A41,<br>A48, A59,<br>B1, B21,<br>B53 | Ρ    | _              | Positive supply for peripheral logic and I/O pins                                  |

| VCAP   | 56                 | 85                       | B7                                                   | B48                                                    | Р    |                | Capacitor for Internal Voltage Regulato                                            |

| Vss    | 9, 25, 41          | 15, 36, 45,<br>65, 75    | A8, B10,<br>D4, D5,<br>E7, F5,<br>F10, G6,<br>G7, H3 | A3, A25,<br>A43, A63,<br>B8, B12,<br>B25, B41,<br>B46  | Ρ    | _              | Ground reference for logic and I/O pins<br>This pin must be connected at all times |

| Vref+  | 16                 | 29                       | K3                                                   | B17                                                    | I    | Analog         | Analog voltage reference (high) input                                              |

| Vref-  | 15                 | 28                       | L2                                                   | A21                                                    | I    | Analog         | Analog voltage reference (low) input                                               |

#### TABLE 1-1: PINOUT I/O DESCRIPTIONS (CONTINUED)

TTL = TTL input buffer

Note 1: Pin numbers are only provided for reference. See the "Device Pin Tables" section for device pin availability.

2: See 25.0 "Ethernet Controller" for more information.

#### 5.0 FLASH PROGRAM MEMORY

Note: This data sheet summarizes the features of the PIC32MX5XX/6XX/7XX family of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to Section 5. "Flash Program Memory" (DS60001121) in the "PIC32 Family Reference Manual", which is available from the Microchip web site (www.microchip.com/PIC32). PIC32MX5XX/6XX/7XX devices contain an internal Flash program memory for executing user code. There are three methods by which the user can program this memory:

- Run-Time Self-Programming (RTSP)

- EJTAG Programming

- In-Circuit Serial Programming<sup>™</sup> (ICSP<sup>™</sup>)

RTSP is performed by software executing from either Flash or RAM memory. Information about RTSP techniques is available in **Section 5. "Flash Program Memory"** (DS60001121) in the *"PIC32 Family Reference Manual"*.

EJTAG is performed using the EJTAG port of the device and an EJTAG capable programmer.

ICSP is performed using a serial data connection to the device and allows much faster programming times than RTSP.

The EJTAG and ICSP methods are described in the "*PIC32 Flash Programming Specification*" (DS60001145), which can be downloaded from the Microchip web site.

Note: For PIC32MX5XX/6XX/7XX devices, the Flash page size is 4 KB and the row size is 512 bytes (1024 IW and 128 IW, respectively).

#### REGISTER 8-1: OSCCON: OSCILLATOR CONTROL REGISTER (CONTINUED)

- bit 2 UFRCEN: USB FRC Clock Enable bit

- 1 = Enable FRC as the clock source for the USB clock source

- 0 = Use the Primary Oscillator or USB PLL as the USB clock source

- bit 1 **SOSCEN:** Secondary Oscillator (Sosc) Enable bit

- 1 = Enable Secondary Oscillator

- 0 = Disable Secondary Oscillator

#### bit 0 **OSWEN:** Oscillator Switch Enable bit

- 1 = Initiate an oscillator switch to selection specified by NOSC<2:0> bits

- 0 = Oscillator switch is complete

Note: Writes to this register require an unlock sequence. Refer to Section 6. "Oscillator" (DS60001112) in the "PIC32 Family Reference Manual" for details.

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |  |  |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|--|--|--|

| 04.04        | R/W-x             | R/W-x             | R/W-x             | R/W-x             | R/W-x             | R/W-x             | R/W-x            | R/W-x            |  |  |  |

| 31:24        |                   |                   |                   | CHEW3<            | :31:24>           |                   |                  |                  |  |  |  |

| 00.40        | R/W-x             | R/W-x             | R/W-x             | R/W-x             | R/W-x             | R/W-x             | R/W-x            | R/W-x            |  |  |  |

| 23:16        |                   |                   |                   | CHEW3<            | :23:16>           |                   |                  |                  |  |  |  |

| 45.0         | R/W-x             | R/W-x             | R/W-x             | R/W-x             | R/W-x             | R/W-x             | R/W-x            | R/W-x            |  |  |  |

| 15:8         | CHEW3<15:8>       |                   |                   |                   |                   |                   |                  |                  |  |  |  |

| 7.0          | R/W-x             | R/W-x             | R/W-x             | R/W-x             | R/W-x             | R/W-x             | R/W-x            | R/W-x            |  |  |  |

| 7:0          | CHEW3<7:0>        |                   |                   |                   |                   |                   |                  |                  |  |  |  |

#### REGISTER 9-8: CHEW3: CACHE WORD 3

| Legend:           |                  |                      |                    |

|-------------------|------------------|----------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bi | t, read as '0'     |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared | x = Bit is unknown |

bit 31-0 **CHEW3<31:0>:** Word 3 of the cache line selected by CHEIDX<3:0> bits (CHEACC<3:0>) Readable only if the device is not code-protected.

Note: This register is a window into the cache data array and is only readable if the device is not code-protected.

#### REGISTER 9-9: CHELRU: CACHE LRU REGISTER

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|

| 31:24        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | R-0              |

| 31.24        | —                 | —                 | _                 | —                 | —                 | _                 | —                | CHELRU<24>       |

| 22:16        | R-0               | R-0               | R-0               | R-0               | R-0               | R-0               | R-0              | R-0              |

| 23:16        |                   |                   |                   | CHELRI            | J<23:16>          |                   |                  |                  |

| 45.0         | R-0               | R-0               | R-0               | R-0               | R-0               | R-0               | R-0              | R-0              |

| 15:8         |                   |                   |                   | CHELR             | U<15:8>           |                   |                  |                  |

| 7:0          | R-0               | R-0               | R-0               | R-0               | R-0               | R-0               | R-0              | R-0              |

| 7.0          |                   |                   |                   | CHELF             | RU<7:0>           |                   |                  |                  |

| Legend:           |                  |                        |                    |

|-------------------|------------------|------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, | read as '0'        |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared   | x = Bit is unknown |

bit 31-25 Unimplemented: Write '0'; ignore read

bit 24-0 **CHELRU<24:0>:** Cache Least Recently Used State Encoding bits Indicates the pseudo-LRU state of the cache.

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|

| 04.04        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 31:24        | _                 | _                 | _                 | —                 | —                 | —                 | —                | _                |

| 23:16        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 23.10        | _                 | _                 |                   | —                 | —                 |                   | —                | —                |

| 45.0         | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 15:8         | _                 | _                 | _                 | —                 | —                 | _                 | —                | —                |

| 7.0          | U-0               | U-0               | U-0               | U-0               | R-0               | R-0               | R-0              | R-0              |

| 7:0          |                   |                   |                   | —                 | RDWR              | [                 | DMACH<2:0>       | •                |

#### REGISTER 10-2: DMASTAT: DMA STATUS REGISTER

#### Legend:

| 0                 |                  |                      |                    |  |

|-------------------|------------------|----------------------|--------------------|--|

| R = Readable bit  | W = Writable bit | U = Unimplemented b  | it, read as '0'    |  |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared | x = Bit is unknown |  |

#### bit 31-4 Unimplemented: Read as '0'

#### bit 3 RDWR: Read/Write Status bit

1 = Last DMA bus access was a read

0 = Last DMA bus access was a write

#### bit 2-0 **DMACH<2:0>:** DMA Channel bits These bits contain the value of the most recent active DMA channel.

#### REGISTER 10-3: DMAADDR: DMA ADDRESS REGISTER

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |  |  |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|--|--|--|

| 04-04        | R-0               | R-0               | R-0               | R-0               | R-0               | R-0               | R-0              | R-0              |  |  |  |

| 31:24        | DMAADDR<31:24>    |                   |                   |                   |                   |                   |                  |                  |  |  |  |

| 00.40        | R-0               | R-0               | R-0               | R-0               | R-0               | R-0               | R-0              | R-0              |  |  |  |

| 23:16        | DMAADDR<23:16>    |                   |                   |                   |                   |                   |                  |                  |  |  |  |

| 45.0         | R-0               | R-0               | R-0               | R-0               | R-0               | R-0               | R-0              | R-0              |  |  |  |

| 15:8         |                   |                   |                   | DMAADDI           | R<15:8>           |                   |                  |                  |  |  |  |

| 7.0          | R-0               | R-0               | R-0               | R-0               | R-0               | R-0               | R-0              | R-0              |  |  |  |

| 7:0          |                   |                   |                   | DMAADD            | R<7:0>            |                   |                  |                  |  |  |  |

### Legend:

| Logona.           |                  |                                    |                    |  |

|-------------------|------------------|------------------------------------|--------------------|--|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read as '0' |                    |  |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared               | x = Bit is unknown |  |

#### bit 31-0 DMAADDR<31:0>: DMA Module Address bits

These bits contain the address of the most recent DMA access.

#### REGISTER 11-7: U1IE: USB INTERRUPT ENABLE REGISTER

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1      | Bit<br>24/16/8/0        |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|-----------------------|-------------------------|

| 31:24        | U-0                   | U-0                     |

| 31.24        | —                 | —                 | —                 | —                 | _                 | —                 | _                     |                         |

| 23:16        | U-0                   | U-0                     |

| 23.10        | —                 | —                 | —                 | —                 | _                 | —                 | _                     |                         |

| 15:8         | U-0                   | U-0                     |

| 15.6         | —                 | —                 | —                 | —                 | _                 | —                 | _                     |                         |

|              | R/W-0                 | R/W-0                   |

| 7:0          | STALLIE           | ATTACHIE          | RESUMEIE          | IDLEIE            | TRNIE             | SOFIE             | UERRIE <sup>(1)</sup> | URSTIE <sup>(2)</sup>   |

|              | STALLIE           | ATTACHIE          | RESUMEIE          | IDLEIE            |                   | SOFIE             | UERRIE'               | DETACHIE <sup>(3)</sup> |

#### Legend:

| R = Readable bit W = Writable bit |                  | U = Unimplemented bit, read as '0' |                    |  |

|-----------------------------------|------------------|------------------------------------|--------------------|--|

| -n = Value at POR                 | '1' = Bit is set | '0' = Bit is cleared               | x = Bit is unknown |  |

#### bit 31-8 Unimplemented: Read as '0'

|       | •·····                                                          |

|-------|-----------------------------------------------------------------|

| bit 7 | STALLIE: STALL Handshake Interrupt Enable bit                   |

|       | 1 = STALL interrupt is enabled                                  |

|       | 0 = STALL interrupt is disabled                                 |

| bit 6 | ATTACHIE: ATTACH Interrupt Enable bit                           |

|       | 1 = ATTACH interrupt is enabled                                 |

|       | 0 = ATTACH interrupt is disabled                                |

| bit 5 | RESUMEIE: RESUME Interrupt Enable bit                           |

|       | 1 = RESUME interrupt is enabled                                 |

|       | 0 = RESUME interrupt is disabled                                |

| bit 4 | IDLEIE: Idle Detect Interrupt Enable bit                        |

|       | 1 = Idle interrupt is enabled                                   |

|       | 0 = Idle interrupt is disabled                                  |

| bit 3 | TRNIE: Token Processing Complete Interrupt Enable bit           |

|       | 1 = TRNIF interrupt is enabled                                  |

|       | 0 = TRNIF interrupt is disabled                                 |

| bit 2 | SOFIE: SOF Token Interrupt Enable bit                           |

|       | 1 = SOFIF interrupt is enabled                                  |

|       | 0 = SOFIF interrupt is disabled                                 |

| bit 1 | UERRIE: USB Error Interrupt Enable bit <sup>(1)</sup>           |

|       | 1 = USB Error interrupt is enabled                              |

|       | 0 = USB Error interrupt is disabled                             |

| bit 0 | URSTIE: USB Reset Interrupt Enable bit <sup>(2)</sup>           |

|       | 1 = URSTIF interrupt is enabled                                 |

|       | 0 = URSTIF interrupt is disabled                                |

|       | <b>DETACHIE:</b> USB Detach Interrupt Enable bit <sup>(3)</sup> |

|       | 1 = DATTCHIF interrupt is enabled                               |

|       | 0 = DATTCHIF interrupt is disabled                              |

|       |                                                                 |

**Note 1:** For an interrupt to propagate USBIF, the UERRIE bit (U1IE<1>) must be set.

- 2: Device mode.

- 3: Host mode.

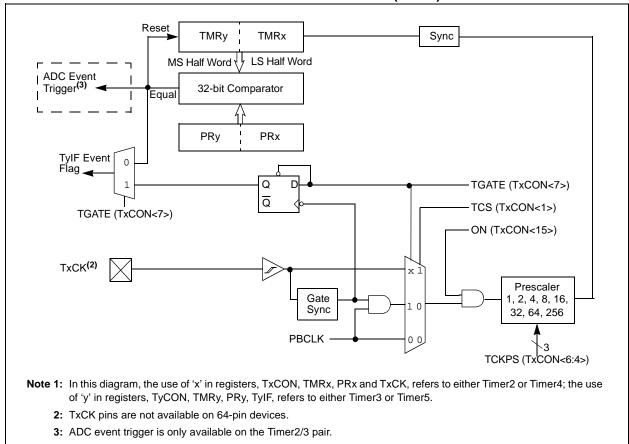

#### FIGURE 14-2: TIMER2/3 AND TIMER4/5 BLOCK DIAGRAM (32-BIT)

NOTES:

#### REGISTER 20-2: UxSTA: UARTx STATUS AND CONTROL REGISTER (CONTINUED)

- bit 8 **TRMT:** Transmit Shift Register is Empty bit (read-only) 1 = Transmit shift register is empty and transmit buffer is empty (the last transmission has completed) 0 = Transmit shift register is not empty, a transmission is in progress or queued in the transmit buffer bit 7-6 URXISEL<1:0>: Receive Interrupt Mode Selection bit 11 = Reserved 10 = Interrupt flag bit is asserted while receive buffer is 3/4 or more full (has 6 or more data characters) 01 = Interrupt flag bit is asserted while receive buffer is 1/2 or more full (has 4 or more data characters) 00 = Interrupt flag bit is asserted while receive buffer is not empty (has at least 1 data character) **ADDEN:** Address Character Detect bit (bit 8 of received data = 1) bit 5 1 = Address Detect mode is enabled. If 9-bit mode is not selected, this control bit has no effect. 0 = Address Detect mode is disabled bit 4 **RIDLE:** Receiver Idle bit (read-only) 1 =Receiver is idle 0 = Data is being received bit 3 PERR: Parity Error Status bit (read-only) 1 = Parity error has been detected for the current character 0 = Parity error has not been detected FERR: Framing Error Status bit (read-only) bit 2 1 = Framing error has been detected for the current character 0 = Framing error has not been detected bit 1 **OERR:** Receive Buffer Overrun Error Status bit. This bit is set in hardware and can only be cleared (= 0) in software. Clearing a previously set OERR bit resets the receiver buffer and RSR to an empty state.

- 1 = Receive buffer has overflowed

- 0 = Receive buffer has not overflowed

- bit 0 **URXDA:** Receive Buffer Data Available bit (read-only)

- 1 = Receive buffer has data, at least one more character can be read

- 0 = Receive buffer is empty

| REGISTER 23-3: AD1CON3: ADC CONTROL REGISTER 3 |                   |                          |                   |                          |                   |                   |                  |                  |  |  |

|------------------------------------------------|-------------------|--------------------------|-------------------|--------------------------|-------------------|-------------------|------------------|------------------|--|--|

| Bit<br>Range                                   | Bit<br>31/23/15/7 | Bit<br>30/22/14/6        | Bit<br>29/21/13/5 | Bit<br>28/20/12/4        | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |  |

| 31:24                                          | U-0               | U-0                      | U-0               | U-0                      | U-0               | U-0               | U-0              | U-0              |  |  |

| 31.24                                          | —                 | —                        | —                 | —                        | _                 |                   | —                | —                |  |  |

| 00.40                                          | U-0               | U-0                      | U-0               | U-0                      | U-0               | U-0               | U-0              | U-0              |  |  |

| 23:16                                          | —                 | —                        | —                 | —                        | _                 |                   | —                | —                |  |  |

| 45.0                                           | R/W-0             | U-0                      | U-0               | R/W-0                    | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |

| 15:8                                           | ADRC              | —                        | —                 | SAMC<4:0> <sup>(1)</sup> |                   |                   |                  |                  |  |  |

| 7.0                                            | R/W-0             | R/W-0                    | R/W-0             | R/W-0                    | R/W-0             | R/W-0             | R/W              | R/W-0            |  |  |

| 7:0                                            |                   | ADCS<7:0> <sup>(2)</sup> |                   |                          |                   |                   |                  |                  |  |  |

#### Legend:

| 0                 |                  |                                    |                    |  |

|-------------------|------------------|------------------------------------|--------------------|--|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read as '0' |                    |  |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared               | x = Bit is unknown |  |

bit 31-16 Unimplemented: Read as '0'

| bit 15    | ADRC: ADC Conversion Clock Source bit               |

|-----------|-----------------------------------------------------|

|           | 1 = Clock derived from FRC                          |

|           | 0 = Clock derived from Peripheral Bus Clock (PBCLK) |

| bit 14-13 | Unimplemented: Read as '0'                          |

```

bit 12-8 SAMC<4:0>: Auto-Sample Time bits<sup>(1)</sup>

11111 = 31 TAD

00001 = 1 TAD

00000 = 0 TAD (Not allowed)

ADCS<7:0>: ADC Conversion Clock Select bits<sup>(2)</sup>

bit 7-0

11111111 =TPB • 2 • (ADCS<7:0> + 1) = 512 • TPB = TAD

```

```

00000001 =TPB • 2 • (ADCS<7:0> + 1) = 4 • TPB = TAD

00000000 =TPB • 2 • (ADCS<7:0> + 1) = 2 • TPB = TAD

```

- **Note 1:** This bit is only used if the SSRC<2:0> bits (AD1CON1<7:5>) = 111.

- 2: This bit is not used if the ADRC bit (AD1CON3<15>) = 1.

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|

| 31:24        | R-0               | R-0               | R-0               | R-0               | R-0               | R-0               | R-0              | R-0              |

| 31.24        | RXOVF31           | RXOVF30           | RXOVF29           | RXOVF28           | RXOVF27           | RXOVF26           | RXOVF25          | RXOVF24          |

| 22:16        | R-0               | R-0               | R-0               | R-0               | R-0               | R-0               | R-0              | R-0              |

| 23:16        | RXOVF23           | RXOVF22           | RXOVF21           | RXOVF20           | RXOVF19           | RXOVF18           | RXOVF17          | RXOVF16          |

| 15:8         | R-0               | R-0               | R-0               | R-0               | R-0               | R-0               | R-0              | R-0              |

| 10.0         | RXOVF15           | RXOVF14           | RXOVF13           | RXOVF12           | RXOVF11           | RXOVF10           | RXOVF9           | RXOVF8           |

| 7:0          | R-0               | R-0               | R-0               | R-0               | R-0               | R-0               | R-0              | R-0              |

| 7.0          | RXOVF7            | RXOVF6            | RXOVF5            | RXOVF4            | RXOVF3            | RXOVF2            | RXOVF1           | RXOVF0           |

#### REGISTER 24-7: CIRXOVF: CAN RECEIVE FIFO OVERFLOW STATUS REGISTER

#### Legend:

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, r | ead as '0'         |

|-------------------|------------------|--------------------------|--------------------|

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared     | x = Bit is unknown |

bit 31-0 RXOVF<31:0>: FIFOn Receive Overflow Interrupt Pending bit

1 = FIFO has overflowed

0 = FIFO has not overflowed

#### REGISTER 24-8: CITMR: CAN TIMER REGISTER

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |  |  |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|--|--|--|

| 31:24        | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |  |

| 51.24        |                   | CANTS<15:8>       |                   |                   |                   |                   |                  |                  |  |  |  |

| 23:16        | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |  |

| 23.10        | CANTS<7:0>        |                   |                   |                   |                   |                   |                  |                  |  |  |  |

| 15.0         | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |  |

| 15:8         | CANTSPRE<15:8>    |                   |                   |                   |                   |                   |                  |                  |  |  |  |

| 7.0          | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |  |

| 7:0          |                   |                   |                   | CANTSPF           | RE<7:0>           |                   |                  |                  |  |  |  |

| Legend:           |                  |                                    |                    |  |

|-------------------|------------------|------------------------------------|--------------------|--|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read as '0' |                    |  |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared               | x = Bit is unknown |  |

bit 31-0 CANTS<15:0>: CAN Time Stamp Timer bits

This is a free-running timer that increments every CANTSPRE system clocks when the CANCAP bit (CiCON<20>) is set.

#### bit 15-0 CANTSPRE<15:0>: CAN Time Stamp Timer Prescaler bits

1111 1111 1111 = CAN time stamp timer (CANTS) increments every 65,535 system clocks

.

0000 0000 0000 = CAN time stamp timer (CANTS) increments every system clock

**Note 1:** CiTMR will be paused when CANCAP = 0.

2: The CiTMR prescaler count will be reset on any write to CiTMR (CANTSPRE will be unaffected).

#### 31.2 MPLAB XC Compilers

The MPLAB XC Compilers are complete ANSI C compilers for all of Microchip's 8, 16, and 32-bit MCU and DSC devices. These compilers provide powerful integration capabilities, superior code optimization and ease of use. MPLAB XC Compilers run on Windows, Linux or MAC OS X.

For easy source level debugging, the compilers provide debug information that is optimized to the MPLAB X IDE.

The free MPLAB XC Compiler editions support all devices and commands, with no time or memory restrictions, and offer sufficient code optimization for most applications.

MPLAB XC Compilers include an assembler, linker and utilities. The assembler generates relocatable object files that can then be archived or linked with other relocatable object files and archives to create an executable file. MPLAB XC Compiler uses the assembler to produce its object file. Notable features of the assembler include:

- Support for the entire device instruction set

- Support for fixed-point and floating-point data

- Command-line interface

- Rich directive set

- Flexible macro language

- MPLAB X IDE compatibility

#### 31.3 MPASM Assembler

The MPASM Assembler is a full-featured, universal macro assembler for PIC10/12/16/18 MCUs.

The MPASM Assembler generates relocatable object files for the MPLINK Object Linker, Intel<sup>®</sup> standard HEX files, MAP files to detail memory usage and symbol reference, absolute LST files that contain source lines and generated machine code, and COFF files for debugging.

The MPASM Assembler features include:

- Integration into MPLAB X IDE projects

- User-defined macros to streamline assembly code

- Conditional assembly for multipurpose source files

- Directives that allow complete control over the assembly process

#### 31.4 MPLINK Object Linker/ MPLIB Object Librarian

The MPLINK Object Linker combines relocatable objects created by the MPASM Assembler. It can link relocatable objects from precompiled libraries, using directives from a linker script.

The MPLIB Object Librarian manages the creation and modification of library files of precompiled code. When a routine from a library is called from a source file, only the modules that contain that routine will be linked in with the application. This allows large libraries to be used efficiently in many different applications.

The object linker/library features include:

- Efficient linking of single libraries instead of many smaller files

- Enhanced code maintainability by grouping related modules together

- Flexible creation of libraries with easy module listing, replacement, deletion and extraction

#### 31.5 MPLAB Assembler, Linker and Librarian for Various Device Families

MPLAB Assembler produces relocatable machine code from symbolic assembly language for PIC24, PIC32 and dsPIC DSC devices. MPLAB XC Compiler uses the assembler to produce its object file. The assembler generates relocatable object files that can then be archived or linked with other relocatable object files and archives to create an executable file. Notable features of the assembler include:

- · Support for the entire device instruction set

- · Support for fixed-point and floating-point data

- Command-line interface

- · Rich directive set

- Flexible macro language

- MPLAB X IDE compatibility

| DC CHARACTERISTICS |                        | $\begin{array}{l} \mbox{Standard Operating Conditions: 2.3V to 3.6V} \\ \mbox{(unless otherwise stated)} \\ \mbox{Operating temperature} & -40^\circ C \leq TA \leq +85^\circ C \mbox{ for Industrial} \\ & -40^\circ C \leq TA \leq +105^\circ C \mbox{ for V-Temp} \end{array}$ |          |                              |                           |                                  |               |  |       |

|--------------------|------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|------------------------------|---------------------------|----------------------------------|---------------|--|-------|

| Param.<br>No.      | Typical <sup>(3)</sup> | Max.                                                                                                                                                                                                                                                                              | Units    |                              | Conditions                | i                                |               |  |       |

| Operatir           | ng Current (I          | DD) <sup>(1,2,4)</sup> f <b>O</b> I                                                                                                                                                                                                                                               | PIC32MX5 | 575/675/695/775/795 Family D | )evices                   |                                  |               |  |       |

| DC20               | 6                      | 9                                                                                                                                                                                                                                                                                 | mA       | -40°C,<br>+25°C,<br>+85°C    |                           | Code executing from Flash +25°C, |               |  | 4 MHz |

| DC20b              | 7                      | 10                                                                                                                                                                                                                                                                                |          |                              | +105⁰C                    |                                  |               |  |       |

| DC20a              | 4                      |                                                                                                                                                                                                                                                                                   |          | Code executing from SRAM     | _                         |                                  |               |  |       |

| DC21               | 37                     | 40                                                                                                                                                                                                                                                                                | mA       | Code executing from Flash    |                           |                                  | 25 MHz        |  |       |

| DC21a              | 25                     |                                                                                                                                                                                                                                                                                   | IIIA     | Code executing from SRAM     | _                         |                                  | 23 1011 12    |  |       |

| DC22               | 64                     | 70                                                                                                                                                                                                                                                                                | mA       | Code executing from Flash    |                           |                                  |               |  |       |

| DC22a              | 61                     | _                                                                                                                                                                                                                                                                                 | IIIA     | Code executing from SRAM     |                           | _                                | 60 MHz        |  |       |

| DC23               | 85                     | 98                                                                                                                                                                                                                                                                                | mA       | Code executing from Flash    | -40ºC,<br>+25ºC,<br>+85ºC |                                  | 80 MHz        |  |       |

| DC23b              | 90                     | 120                                                                                                                                                                                                                                                                               | ]        |                              | +105⁰C                    |                                  |               |  |       |

| DC23a              | 85                     |                                                                                                                                                                                                                                                                                   | ]        | Code executing from SRAM     | —                         |                                  |               |  |       |

| DC25a              | 125                    | 150                                                                                                                                                                                                                                                                               | μA       | —                            | +25°C                     | 3.3V                             | LPRC (31 kHz) |  |       |

#### TABLE 32-5: DC CHARACTERISTICS: OPERATING CURRENT (IDD)

**Note 1:** A device's IDD supply current is mainly a function of the operating voltage and frequency. Other factors, such as PBCLK (Peripheral Bus Clock) frequency, number of peripheral modules enabled, internal code execution pattern, execution from Program Flash memory vs. SRAM, I/O pin loading and switching rate, oscillator type, as well as temperature, can have an impact on the current consumption.

- 2: The test conditions for IDD measurements are as follows:

- Oscillator mode is EC (for 8 MHz and below) and EC+PLL (for above 8 MHz) with OSC1 driven by external square wave from rail-to-rail, (OSC1 input clock input over/undershoot < 100 mV required)</li>

- OSC2/CLKO is configured as an I/O input pin

- USB PLL oscillator is disabled if the USB module is implemented, PBCLK divisor = 1:8

- CPU, program Flash, and SRAM data memory are operational, program Flash memory Wait states = 111, Program Cache and Prefetch are disabled and SRAM data memory Wait states = 1

- No peripheral modules are operating, (ON bit = 0)

- WDT, Clock Switching, Fail-Safe Clock Monitor, and Secondary Oscillator are disabled

- All I/O pins are configured as inputs and pulled to Vss

- MCLR = VDD

- CPU executing while(1) statement from Flash

- RTCC and JTAG are disabled

- **3:** Data in "Typical" column is at 3.3V, 25°C at specified operating frequency unless otherwise stated. Parameters are for design guidance only and are not tested.

- **4:** All parameters are characterized, but only those parameters listed for 4 MHz and 80 MHz are tested at 3.3V in manufacturing.

| DC CHA        | RACTER | ISTICS                                                                | $\begin{tabular}{lllllllllllllllllllllllllllllllllll$ |                        |                          |          |                                                                                                                                                                         |

|---------------|--------|-----------------------------------------------------------------------|-------------------------------------------------------|------------------------|--------------------------|----------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Param.<br>No. | Symbol | Characteristics                                                       | Min.                                                  | Typical <sup>(1)</sup> | Max.                     | Units    | Conditions                                                                                                                                                              |

| DI50          | lil    | Input Leakage Current <sup>(3)</sup><br>I/O Ports                     | _                                                     | _                      | <u>+</u> 1               | μA       | Vss $\leq$ VPIN $\leq$ VDD,<br>Pin at high-impedance                                                                                                                    |

| DI51          |        | Analog Input Pins                                                     | —                                                     | —                      | <u>+</u> 1               | μΑ       | VSS $\leq$ VPIN $\leq$ VDD,<br>Pin at high-impedance                                                                                                                    |

| DI55<br>DI56  |        | MCLR <sup>(2)</sup><br>OSC1                                           | —                                                     | _                      | <u>+</u> 1<br><u>+</u> 1 | μΑ<br>μΑ | $\label{eq:VSS} \begin{array}{l} \forall SS \leq VPIN \leq VDD \\ \forall SS \leq VPIN \leq VDD, \\ XT \text{ and } HS \text{ modes} \end{array}$                       |

| DI60a         | licl   | Input Low Injection<br>Current                                        | 0                                                     | _                      | <sub>-5</sub> (7,10)     | mA       | This parameter applies<br>to all pins, with the<br>exception of RB10.<br>Maximum IICH current<br>for this exception is<br>0 mA.                                         |

| DI60b         | ІІСН   | Input High Injection<br>Current                                       | 0                                                     | _                      | +5 <sup>(8,9,10)</sup>   | mA       | This parameter applies<br>to all pins, with the<br>exception of all 5V toler-<br>ant pins, SOSCI, and<br>RB10. Maximum IICH<br>current for these<br>exceptions is 0 mA. |

| DI60c         | ∑IICT  | Total Input Injection<br>Current (sum of all I/O<br>and control pins) | -20 <sup>(11)</sup>                                   | _                      | +20 <sup>(11)</sup>      | mA       | Absolute instantaneous<br>sum of all $\pm$ input<br>injection currents from<br>all I/O pins<br>(   IICL +   IICH   ) $\leq \sum$ IICT                                   |

#### TABLE 32-8: DC CHARACTERISTICS: I/O PIN INPUT SPECIFICATIONS

Note 1: Data in "Typical" column is at 3.3V, 25°C unless otherwise stated. Parameters are for design guidance only and are not tested.

- 2: The leakage current on the MCLR pin is strongly dependent on the applied voltage level. The specified levels represent normal operating conditions. Higher leakage current may be measured at different input voltages.

- 3: Negative current is defined as current sourced by the pin.

- 4: This parameter is characterized, but not tested in manufacturing.

- 5: See the "Device Pin Tables" section for the 5V-tolerant pins.

- 6: The VIH specification is only in relation to externally applied inputs and not with respect to the user-selectable pull-ups. Externally applied high impedance or open drain input signals utilizing the PIC32 internal pullups are guaranteed to be recognized as a logic "high" internally to the PIC32 device, provided that the external load does not exceed the maximum value of ICNPU.

- 7: VIL source < (VSS 0.3). Characterized but not tested.

- 8: VIH source > (VDD + 0.3) for non-5V tolerant pins only.

- **9:** Digital 5V tolerant pins do not have an internal high side diode to VDD, and therefore, cannot tolerate any "positive" input injection current.

- **10:** Injection currents > | 0 | can affect the ADC results by approximately 4 to 6 counts (i.e., VIH Source > (VDD + 0.3) or VIL source < (VSS 0.3)).

- 11: Any number and/or combination of I/O pins not excluded under IICL or IICH conditions are permitted provided the "absolute instantaneous" sum of the input injection currents from all pins do not exceed the specified limit. If Note 7, IICL = (((Vss 0.3) VIL source) / Rs). If Note 8, IICH = ((IICH source (VDD + 0.3)) / RS). RS = Resistance between input source voltage and device pin. If (Vss 0.3) ≤ VSOURCE ≤ (VDD + 0.3), injection current = 0.

#### TABLE 32-24: TIMER2, 3, 4, 5 EXTERNAL CLOCK TIMING REQUIREMENTS

| AC CHARACTERISTICS |           |                          |                        | (unless          | 0 1                                          | ; ≤ TA ≤ | +85°C | <b>6∨</b><br>for Industrial<br>C for V-Temp |                       |  |

|--------------------|-----------|--------------------------|------------------------|------------------|----------------------------------------------|----------|-------|---------------------------------------------|-----------------------|--|

| Param.<br>No.      | Symbol    | Chai                     | racteristic            | s <sup>(1)</sup> | Min.                                         | Max.     | Units | Conditions                                  |                       |  |

| TB10               | ТтхН      | TxCK<br>High Time        | Synchrono<br>prescaler | ous, with        | [(12.5 ns or 1 TPB)/N]<br>+ 25 ns            | —        | ns    | Must also meet<br>parameter<br>TB15         | value<br>(1, 2, 4, 8, |  |

| TB11               | ΤτxL      | TxCK<br>Low Time         | Synchrono<br>prescaler | ous, with        | [(12.5 ns or 1 ТРВ)/N]<br>+ 25 ns            |          | ns    | Must also meet<br>parameter<br>TB15         | 16, 32, 64,<br>256)   |  |

| TB15               | ΤτχΡ      | TxCK<br>Input            | Synchrono<br>prescaler | ous, with        | [(Greater of [(25 ns or<br>2 Трв)/N] + 30 ns | _        | ns    | VDD > 2.7V                                  |                       |  |

|                    |           | Period                   |                        |                  | [(Greater of [(25 ns or<br>2 Трв)/N] + 50 ns | —        | ns    | VDD < 2.7V                                  |                       |  |

| TB20               | TCKEXTMRL | Delay from<br>Clock Edge |                        |                  | _                                            | 1        | Трв   | _                                           |                       |  |

Note 1: These parameters are characterized, but not tested in manufacturing.

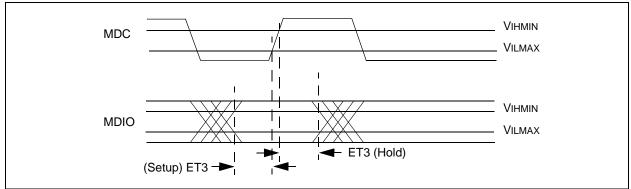

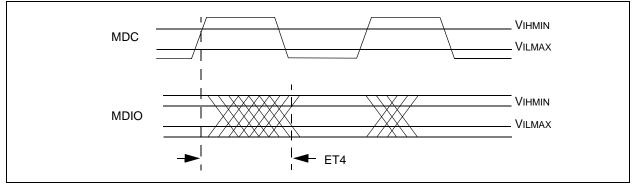

#### TABLE 32-35: ETHERNET MODULE SPECIFICATIONS

| АС СНА          | RACTERISTICS                        | $\begin{tabular}{ l l l l l l l l l l l l l l l l l l l$ |    |     | 85°C for Industrial |                  |

|-----------------|-------------------------------------|----------------------------------------------------------|----|-----|---------------------|------------------|

| Param.<br>No.   | Characteristic                      | Min. Typical Max. Units Conditions                       |    |     |                     |                  |

| MIIM Tin        | ning Requirements                   |                                                          |    |     |                     |                  |

| ET1             | MDC Duty Cycle                      | 40                                                       |    | 60  | %                   | —                |

| ET2             | MDC Period                          | 400                                                      | —  | —   | ns                  | —                |

| ET3             | MDIO Output Setup and Hold          | 10                                                       | —  | 10  | ns                  | See Figure 32-19 |

| ET4             | MDIO Input Setup and Hold           | 0                                                        | —  | 300 | ns                  | See Figure 32-20 |

| MII Timi        | ng Requirements                     |                                                          |    |     |                     |                  |

| ET5             | TX Clock Frequency                  | —                                                        | 25 | _   | MHz                 | —                |

| ET6             | TX Clock Duty Cycle                 | 35                                                       | —  | 65  | %                   | —                |

| ET7             | ETXDx, ETEN, ETXERR Output Delay    | 0                                                        | —  | 25  | ns                  | See Figure 32-21 |

| ET8             | RX Clock Frequency                  | —                                                        | 25 | _   | MHz                 | —                |

| ET9             | RX Clock Duty Cycle                 | 35                                                       | —  | 65  | %                   | —                |

| ET10            | ERXDx, ERXDV, ERXERR Setup and Hold | 10                                                       | —  | 30  | ns                  | See Figure 32-22 |

| <b>RMII</b> Tin | ning Requirements                   |                                                          |    |     |                     |                  |

| ET11            | Reference Clock Frequency           |                                                          | 50 | —   | MHz                 | —                |

| ET12            | Reference Clock Duty Cycle          | 35                                                       |    | 65  | %                   | —                |

| ET13            | ETXDx, ETEN, Setup and Hold         | 2                                                        | —  | 4   | ns                  | —                |

| ET14            | ERXDx, ERXDV, ERXERR Setup and Hold | 2                                                        | —  | 4   | ns                  | —                |

**Note 1:** The Ethernet module is functional at VBORMIN < VDD < 2.9V, but with degraded performance. Unless otherwise stated, module functionality is tested, but not characterized.

#### FIGURE 32-19: MDIO SOURCED BY THE PIC32 DEVICE

#### FIGURE 32-20: MDIO SOURCED BY THE PHY

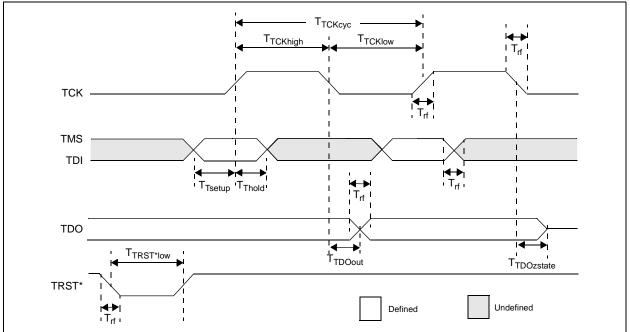

#### FIGURE 32-28: EJTAG TIMING CHARACTERISTICS

#### TABLE 32-43: EJTAG TIMING REQUIREMENTS

| AC CHA        | RACTERISTI | CS                                               | $\label{eq:standard} \begin{array}{l} \mbox{Standard Operating Conditions: 2.3V to 3.6V} \\ \mbox{(unless otherwise stated)} \\ \mbox{Operating temperature} & -40^\circ C \leq TA \leq +85^\circ C \mbox{ for Industrial} \\ & -40^\circ C \leq TA \leq +105^\circ C \mbox{ for V-Temp} \end{array}$ |   |            |   |  |

|---------------|------------|--------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---|------------|---|--|

| Param.<br>No. | Symbol     | Description <sup>(1)</sup>                       | Min. Max. Units Conditions                                                                                                                                                                                                                                                                            |   | Conditions |   |  |

| EJ1           | Ттсксүс    | TCK Cycle Time                                   | 25                                                                                                                                                                                                                                                                                                    | _ | ns         |   |  |

| EJ2           | Ттскнідн   | TCK High Time                                    | 10                                                                                                                                                                                                                                                                                                    |   | ns         | — |  |

| EJ3           | TTCKLOW    | TCK Low Time                                     | 10                                                                                                                                                                                                                                                                                                    |   | ns         | — |  |

| EJ4           | TTSETUP    | TAP Signals Setup Time Before<br>Rising TCK      | 5                                                                                                                                                                                                                                                                                                     | — | ns         | _ |  |

| EJ5           | TTHOLD     | TAP Signals Hold Time After<br>Rising TCK        | 3                                                                                                                                                                                                                                                                                                     | — | ns         | _ |  |

| EJ6           | Ττροουτ    | TDO Output Delay Time from<br>Falling TCK        | —                                                                                                                                                                                                                                                                                                     | 5 | ns         | _ |  |

| EJ7           | TTDOZSTATE | TDO 3-State Delay Time from<br>Falling TCK       | -                                                                                                                                                                                                                                                                                                     | 5 | ns         | — |  |

| EJ8           | TTRSTLOW   | TRST Low Time                                    | 25                                                                                                                                                                                                                                                                                                    | _ | ns         | — |  |

| EJ9           | Trf        | TAP Signals Rise/Fall Time, All Input and Output | —                                                                                                                                                                                                                                                                                                     | — | ns         | _ |  |